OKI MSM9223GS-BK Datasheet

E2C0044-19-96

¡ Semiconductor

¡ Semiconductor

This version: Sep. 1999

Previous version: Aug. 1999

MSM9223

MSM9223

27-Bit Duplex/Triplex VFD Controller/Driver with Digital Dimming, ADC and Keyscan

GENERAL DESCRIPTION

The MSM9223 is a full CMOS controller/driver for Duplex or Triplex vacuum fluorescent

display tube. It conststs of 27-segment driver outputs and 3-grid pre-driver outputs, so that it

can drive directly up to 81-segment VFD.

MSM9223 features a digital dimming function, a 6-ch ADC, a 5 ¥ 5 keyscan circuit and an encoder

type switch interface.

MSM9223 provides an interface with a microcontroller only by three signal lines: DATA I/O,

CLOCK and CS.

FEATURES

• Supply voltage (VDD) : 8 to 18.5V (Built-in 5V regulator for logic)

• Duplex/Triplex selectable

• Applicable VFD tube : 2 Grids ¥ 27 Anodes VFD tube

: 3 Grids ¥ 27 Anodes VFD tube

• 27-segment driver outputs : IOH=–5mA at VOH=VDD–0.8V (SEG1 to 19)

IOH=–10mA at VOH=VDD–0.8V (SEG20 to 27)

• 3-grid pre-driver outputs : IOL=10mA at VOL=2V

• Built-in digital dimming circuit (10-bit resolution)

• Built-in 6-ch A/D converter

• Built-in 5 ¥ 5 keyscan circuit

• Interface circuit for an encoder type rotary switch

• Built-in oscillation circuit (external R and C)

• Built-in Power-On-Reset circuit

• Package:

64-pin plastic QFP (QFP64-P-1420-1.00-BK) Product name: MSM9223GS-BK

1/24

¡ Semiconductor

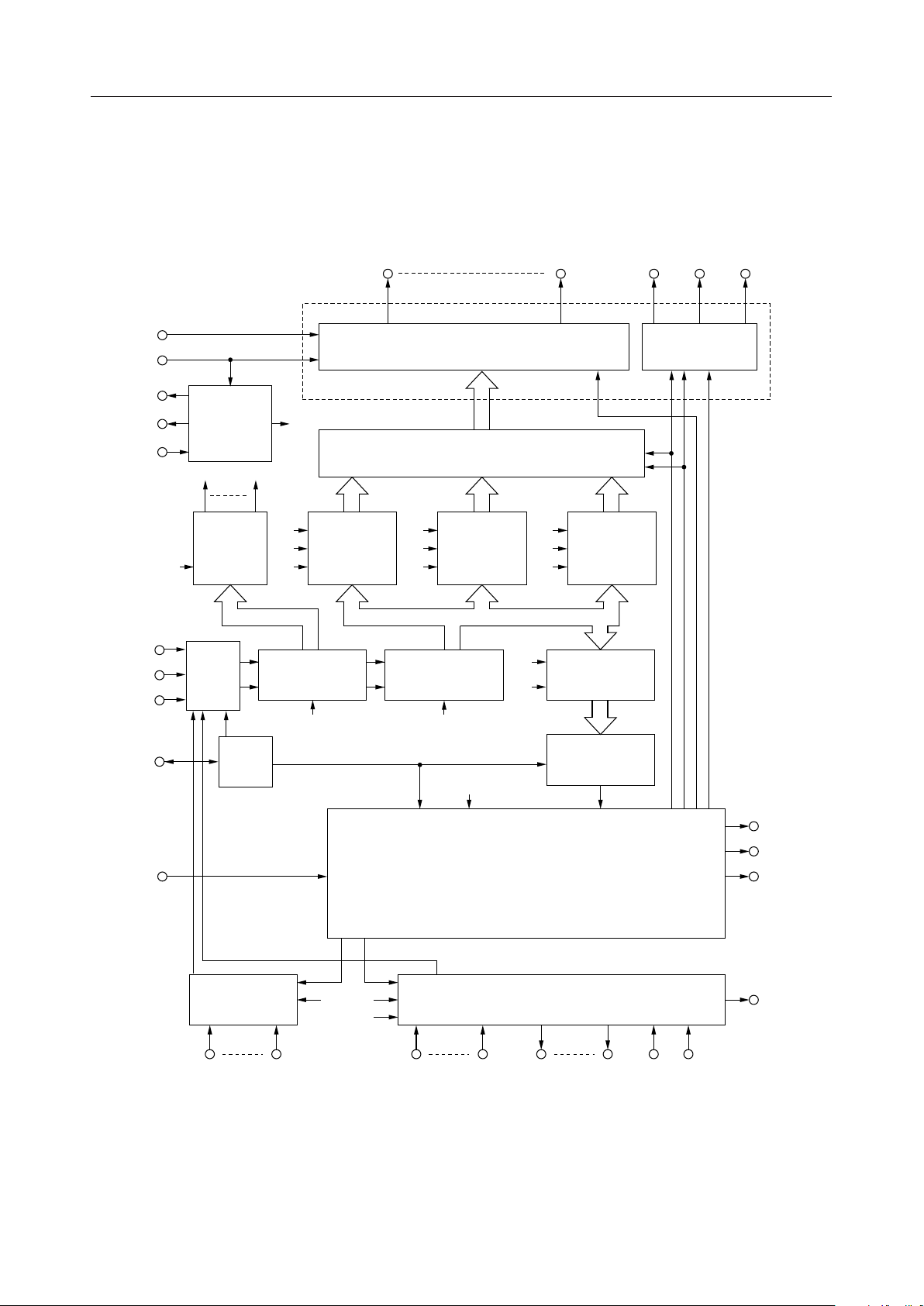

BLOCK DIAGRAM

MSM9223

GRID2 GRID3GRID1SEG27SEG1

D-GND

V

V

(5V)

VREG

(5V)

L-GND

CS

CLOCK

DATA I/O

OSCO

DD

CC

POR

5V

Regulator

&

Power On

Reset

0H 7H

Mode Select

in1-3

Control

OSC

POR

1H

0H

POR

Out1-27

Segment Latch

1

in1-27

Out1-3

3bit Shift Register

POR

27 Segment Driver

Out1-27

81 to 27 Segment Control

in1-27 in1-27in1-27

2H

0H

POR

Out1-27

Segment Latch

2

in1-27

Out1-27

27bit Shift Register

POR

POR

4H

POR

3H

Segment Latch

0H

POR

Dimming Latch

Out1-10

10bit Digital

Dimming

3 Grid pre Driver

Out1-27

3

in1-27

in1-10

Timing Generator

6ch, 8bit

A/D Converter

7H

5H

6H

5 ¥ 5 Key Scan and Encoder Switch Interface

CH1 CH6 COL1 COL5 ROW1 ROW5 A1 B1

DIM OUT

SYNC OUT1

SYNC OUT2DUP/TRI

INT

2/24

¡ Semiconductor

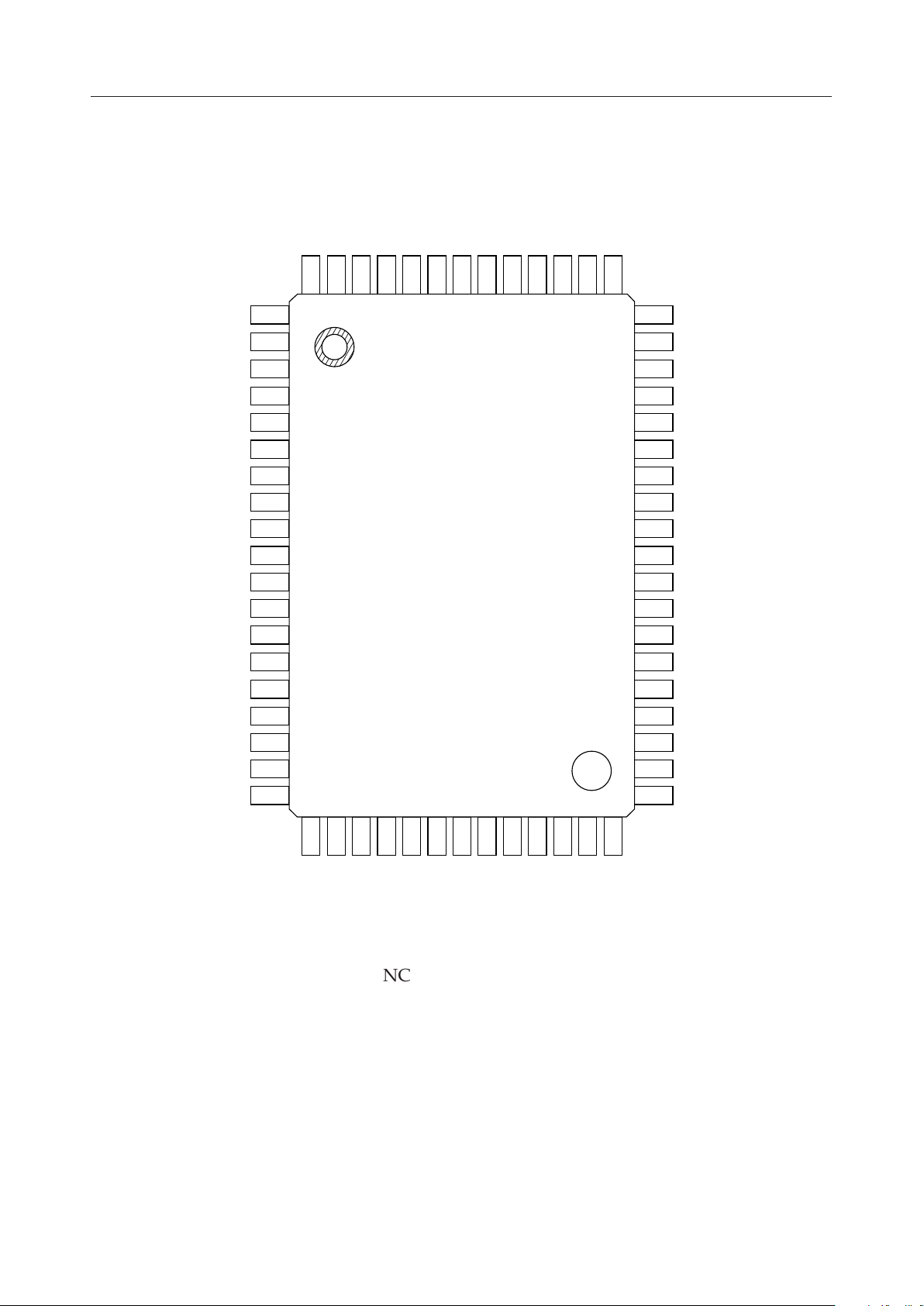

PIN CONFIGURATION (TOP VIEW)

MSM9223

V

DD

SEG25

SEG26

SEG27

GRID1

GRID2

GRID3

D-GND

ROW1

ROW2

ROW3

ROW4

ROW5

COL1

COL2

COL3

COL4

COL5

NC

10

11

12

13

14

15

16

17

18

19

SEG18

SEG21

SEG22

SEG23

SEG24

64

63

62

61

1

2

3

4

5

6

7

8

9

SEG19

SEG20

60

59

58

SEG16

SEG17

57

56

SEG15

SEG14

55

54

SEG13

SEG12

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

V

DD

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

CH6

CH5

CH4

CH3

CH2

CH1

VREG

20A121B122

INT

23

24

25

26

27

28

CC

V

OSCO

DUP/TRI

L-GND

CLOCK

DATA I/O

NC: No connection

64-pin Plastic QFP

29

30

CS

SYNC OUT2

31

32

DIM OUT

SYNC OUT1

3/24

¡ Semiconductor

PIN DESCRIPTIONS

MSM9223

Pin Type Description

1, 51 —

8—

26 —

24 OV

33 OV

40 to 50,

52 to 59

Symbol

V

DD

D-GND

L-GND

CC

REG

SEG1 to 19

Power supply pins.

Pin1 and pin51 should be connected externally.

D-GND is ground pin for the VFD driver circuit. L-GND is ground pin for the

logic circuit. Pins 8 and 26 should be connected externally.

5V output pin for internal logic portion and external logic circuit.

Reference voltage (5V) output pin for A/D converter.

Segment (anode) signal output pins for a VFD tube.

These pins can be directly connected to the VFD tube. External circuit is not required.

O

IOH£–5 mA

Segment (anode) signal output pins for a VFD tube.

60 to 64,

These pins can be directly connected to the VFD tube. External circuit is not required.

2 to 4

SEG20 to 27

O

IOH£–10 mA

Inverted Grid signal output pins.

5, 6, 7 O

GRID1 to 3

For pre-driver, the external circuit is requiend.

IOL£10 mA

29 I

CS

Chip Select input pin.

Data input/output operation is valid when this pin is set at a High level.

28 I

27 I/O

CLOCK

DATA I/O

Serial clock input pin.

Data is input and/or output through the DATA I/O pin at the rising edge of the serial clock.

Serial data input/output pin.

Data is input to / comes out from the shift register at the rising edge of the serial clock.

Interrupt signal output to microcontroller. When any key of key matrix is pressed

22 O

INT

or released, key scanning is started. After the completion of the one cycle, this pin

goes to high level and keeps the high level until keyscan stop mode is selected.

Duplex/Triplex operation select input pin.

23 I

DUP/TRI

Duplex (1/2 duty) operation is selected when this pin is set at a V

Triplex (1/3 duty) operation is selected when this pin is set at a GND level.

34 to 39 ICH1 to 6

Analog voltage input pin for the 8-bit A/D converter.

Input pin for the encoder type rotary switch. Each input has chattering

20, 21

A1, B1

O

absorption function of 620ns typical.

CC

level.

14 to 18 I

9 to 13 O

COL1 to 5

ROW1 to 5

Return inputs from the key matrix.

These pins are active low. When key matrix are in the inactive sate, these

pins are at high level through the internal pull-up resistors. All the inputs do

not have the cahttering absorption function for the keyscans.

Key switch scanning outputs.

Normally low level is output through these pin. When any switch of key matrix

is depressed or released, key scanning is started and is continued until

keyscan stop mode is selected. When keyscan stop mode is selected, all

outputs of ROW1 to 5 go back to low level.

4/24

¡ Semiconductor

MSM9223

Pin Type Description

32 O

Symbol

DIM OUT

Dimming pulse output.

Connect this pin to the slave side DIM IN pin.

Synchronous signal input.

30, 31 O

SYNC OUT 1, 2

Connect these pins to the SYNC IN1 and SYNC IN2 pins

of a slave side.

RC oscillator connecting pins.

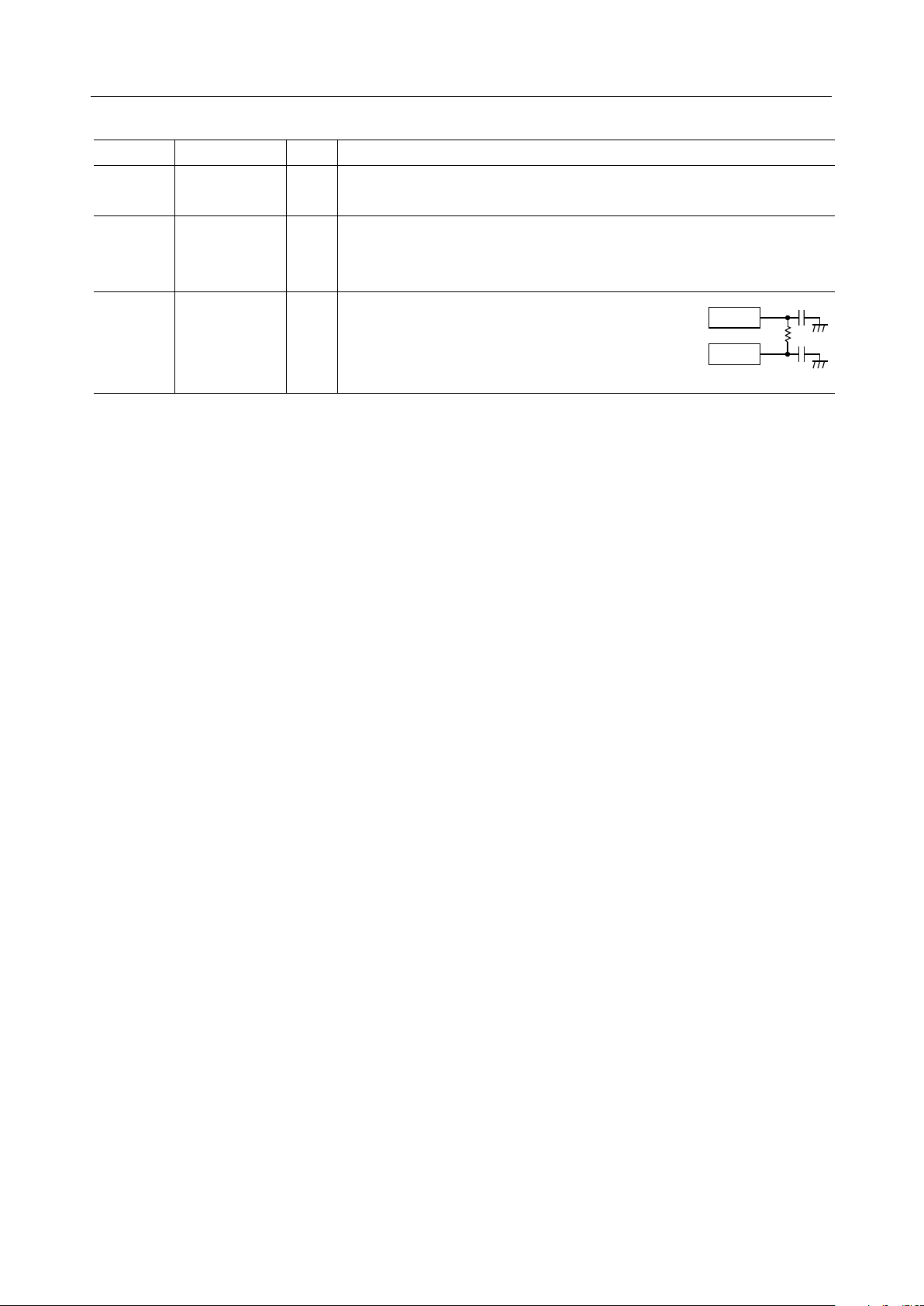

25 I/O

OSC0

Connect a resistor (R2) between the V

and OSC0 pins,

CC

and a capacitor (C2) between the OSC0 pin and the GND,

and a capacitor (C3) between the V

and the GND. C3 is for VCC stabilization.

CC

V

CC

OSC0

C

3

R

2

C

2

5/24

¡ Semiconductor

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Rating Unit

V

DD

V

IN

Ta = 85°C mWPower Dissipation

SEG1 to 19 mA

SEG20 to 27 mA

GRID1 to 3 mA

Output Current

T

P

STG

I

O1

I

O2

I

O3

I

O4

D

DIM OUT, SYNC OUT1, SYNC OUT2 mA

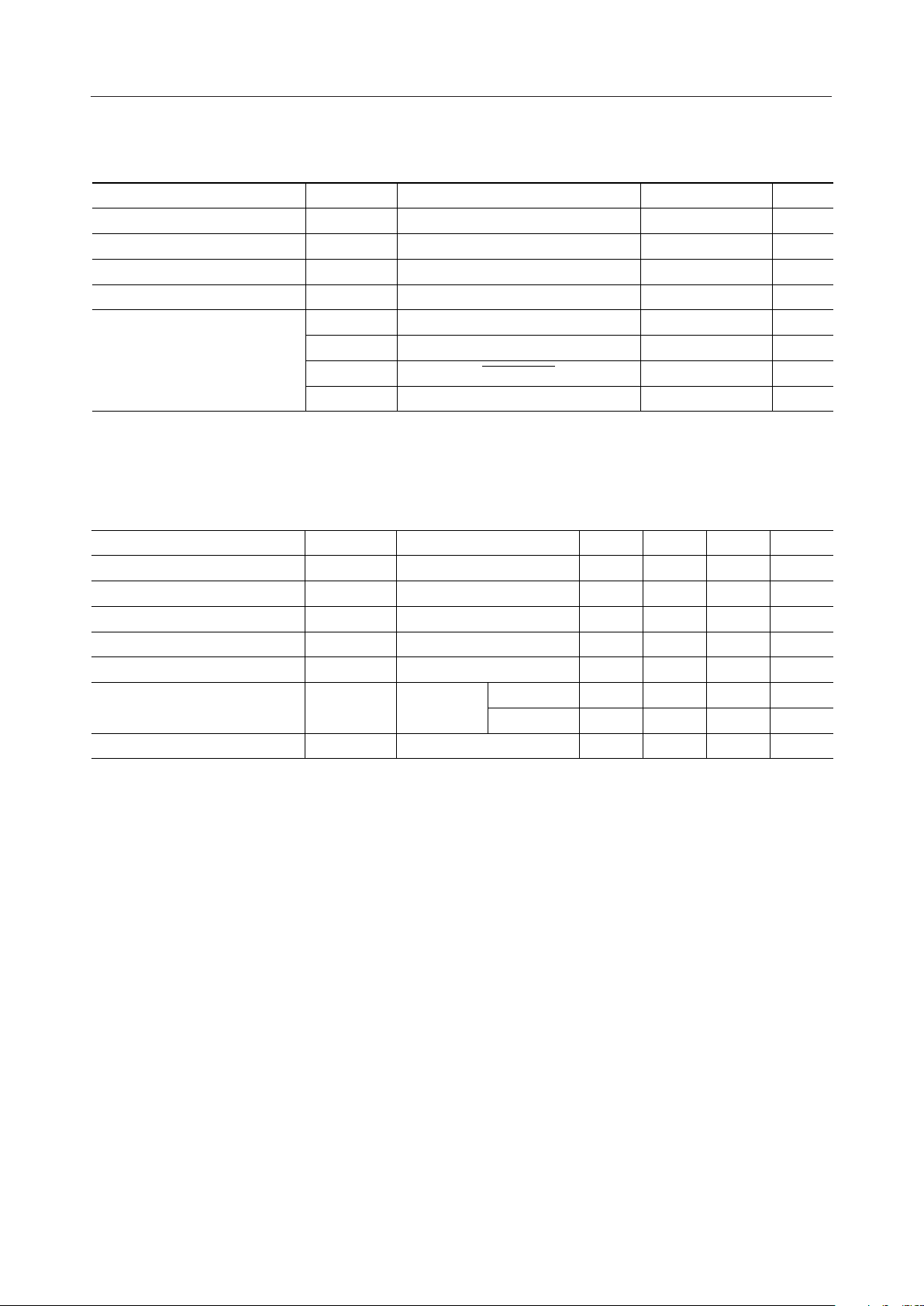

RECOMMENDED OPERATING CONDITIONS

MSM9223

—VSupply Voltage

—VInput Voltage

—°CStorage Temperature

–0.3 to +20

–0.3 to +6.0

590

–55 to +150

–10.0 to +2.0

–20.0 to +2.0

–7.0 to +20.0

–2.0 to +2.0

Parameter Symbol

Driver Supply Voltage

High Level Input Voltage

Low Level Input Voltage

Clock Frequency

Oscillation Frequency

Frame Frequency

Operating Temperature

V

V

V

f

f

OSC

f

T

FR

DD

IH

IL

C

OP

Condition Min. Typ. Max. Unit

— 8.0 13.0 18.5 V

All inputs except OSC0 3.8 — 5.5 V

All inputs except OSC0 0.0 — 0.8 V

— — — 1.0 MHz

R2 = 10kW±5%, C2 = 27pF±5%

R2 = 10kW±5%

= 27pF±5%

C

2

1/3 Duty 211 269 325 Hz

1/2 Duty 317 403 488 Hz

2.6 3.3 4.0 MHz

— –40 — +85 °C

6/24

¡ Semiconductor

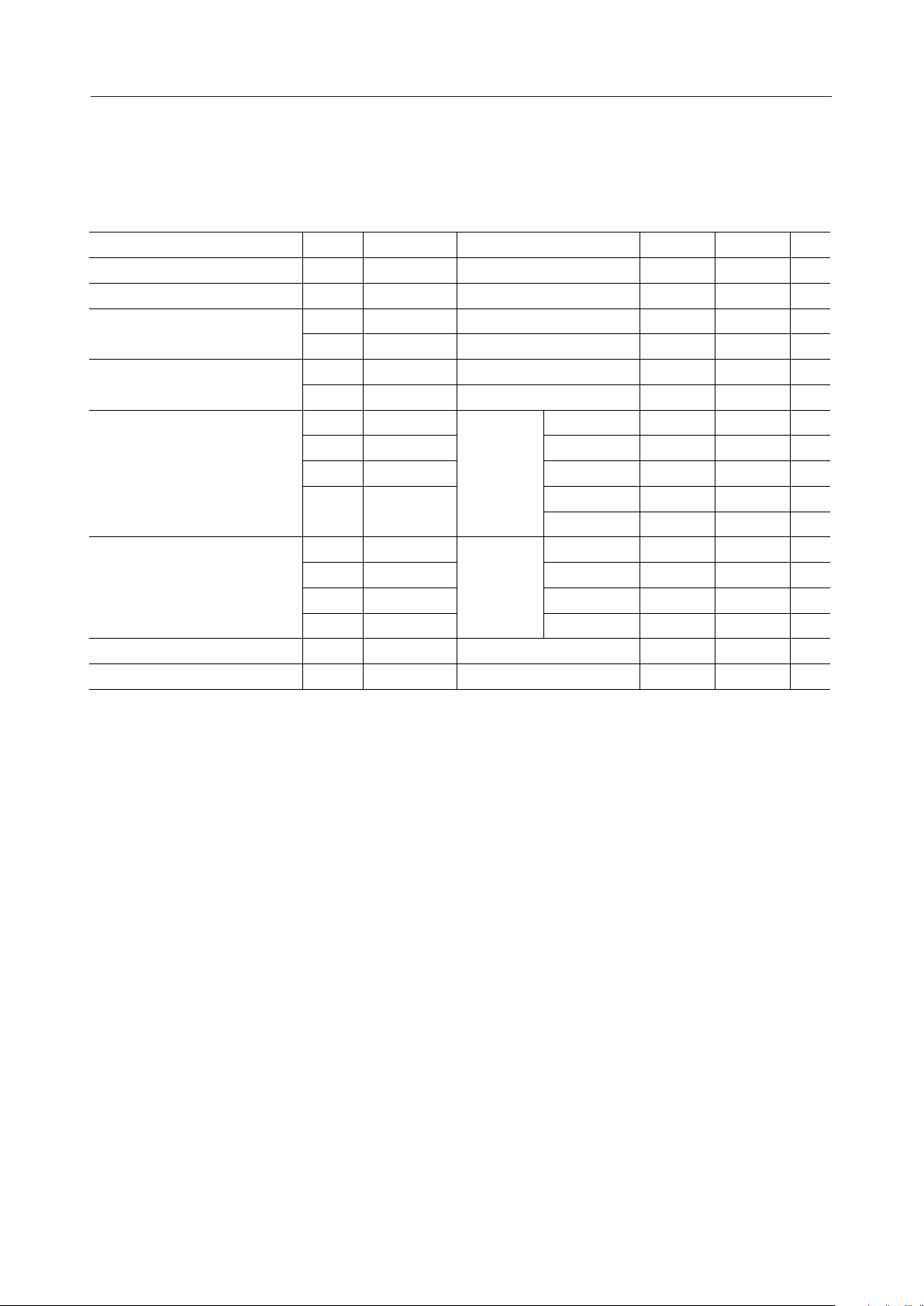

ELECTRICAL CHARACTERISTICS

DC Characteristics

MSM9223

V

V

I

IH1

I

IH2

I

IL1

I

IL2

OH1

OH2

OH3

OH4

OL1

OL2

OL3

OL4

IH

IL

DD

L

Applied pin

*1)

*1)

*2)

*3)

*2)

*3)

SEG1 to 19

SEG20 to 27

GRID1 to 3

*4)

SEG1 to 19

SEG20 to 27

GRID1 to 3

*5)

V

DD

V

CC

V

V

C3=0.01mF±10%, IO=0 to –10mA

Parameter Symbol

High Level Input Voltage

Low Level Input Voltage

High Level Input Current

Low Level Input Current

V

V

High Level Output Voltage

V

V

V

V

Low Level Output Voltage

V

V

Supply Current f

Supply Voltage for Logic

(Ta=–40 to +85°C, V

=8.0 to 18.5V)

DD

Condition Min. Max. Unit

— 3.8 5.5 V

— 0.0 0.8 V

=3.8V –5.0 +5.0 mA

V

IH

VIH=3.8V –100 –5.0 mA

=0.0V –5.0 +5.0 mA

V

IL

=0.0V –300 –70 mA

V

IL

–0.8 V

V

DD

–0.8 V

V

DD

–0.8 V

V

DD

4.0 5.5 V

4.5 5.5 V

— 2.0 V

— 2.0 V

— 2.0 V

— 0.8 V

—10mAI

=9.5V

DD

=9.5V

DD

=3.3MHz, no load

OSC

I

=–5mA

OH1

=–10mA

I

OH2

=–5mA

I

OH3

=–200mA

I

OH4

Output Open

I

=500mA

OL1

=500mA

I

OL2

=10mA

I

OL3

=300mA

I

OL4

4.5 5.5 VV

DD

DD

DD

V

V

V

*1) CS, CLOCK, DATA I/O DUP/TRI, A1, B1, COL1 to 5

*2) CS, CLOCK, DATA I/O DUP/TRI, A1, B1

*3) COL1 to 5

*4) DATA I/O, INT, DIM OUT, SYNC OUT1, SYNC OUT2

*5) DATA I/O, INT, DIM OUT, SYNC OUT1, SYNC OUT2, ROW1 to 5

7/24

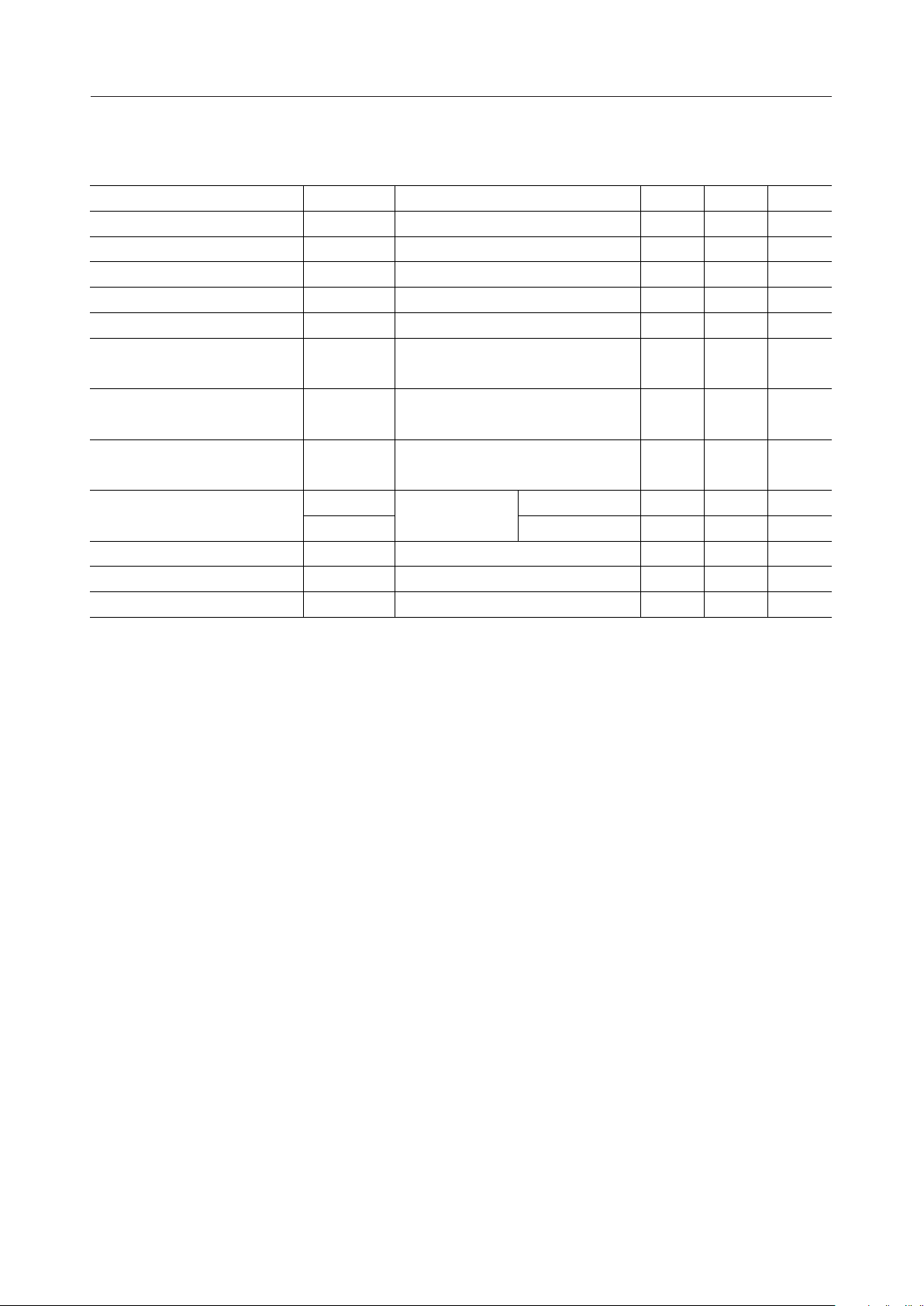

¡ Semiconductor

MSM9223

AC Characteristics

(Ta=–40 to +85°C, VDD=8.0 to 18.5V)

Parameter Symbol

Clock Frequency

Clock Pulse Width

Data Setup Time

Data Hold Time

CS Off Time

t

t

t

t

f

C

CW

DS

DH

CSL

R2=10kW±5%, C2=27pF±5% 20 — ms

CS Setup Time

t

(CS-Clock)

CSS

CS Hold Time

t

(Clock-CS)

CSH

DATA Output Delay Time

t

(Clock-DATA I/O)

Output Slew Rate Time

Rise Time

V

DD

V

Off Time Mounted in a unit, VDD=0.0V 5.0 — ms

DD

CS Wait Time — 400 — ms

PD

t

t

t

PRZ

t

POF

t

RSOFF

R

F

C

L

Condition Min. Max. Unit

— — 1.0 MHz

— 400 — ns

— 400 — ns

— 400 — ns

— 400 — ns

— 400 — ns

— — 1.0 ms

=20% to 80% — 4.0 ms

t

=100pF

R

=80% to 20% — 4.0 ms

t

F

Mounted in a unit — 100 ms

8/24

Loading...

Loading...