E2B0046-27-Y2

¡ Semiconductor MSM6794

¡ Semiconductor

This version: Nov. 1997

Previous version: Mar. 1996

MSM6794

DOT MATRIX LCD DRIVER WITH 128-CHANNEL RAM

GENERAL DESCRIPTION

The MSM6794 is a dot matrix graphic liquid crystal display LSI device to display bit maps.

It drives an LCD panel for dot matrix graphic display under the control of a 4- or 8-bit

microcomputer.

All necessary functions for driving a bit map type LCD are built in on one chip. Therefore,by

using the MSM6794, a bit map type dot matrix graphic liquid crystal display system can be

implemented with a small number of chips.

Since 1-bit data of the display RAM corresponds to the light-on/off of 1-dot of the LCD panel (bit

map system), a flexible display, including kanji display, is possible. One chip comprises a graphic

display system of a maximum of 128¥48 dots. This display can be expanded by using multiple

chips.

The MSM6794 uses CMOS process. Since it is an internal RAM type, the MSM 6794 features low

power consumption, and is suited to display for battery-driven portable equipment.

FEATURES

• Segment outputs : Maximum of 128

• Common outputs : Maximum of 48

• Display duty : 1/33, 1/41, 1/44, 1/48

• Bit map type internal RAM : 6,144 bits (128¥48 bits)

• Display data I/F : 8-bit parallel/serial switchable

• Standby function by program

• LCD drive bias resistor (externally connected)

• Built-in voltage multiplier circuit

• LOGIC voltage : 2.7 to 5.5V

• LCD driving voltage : VBI 5 to 12V (positive voltage)

• Low current consumption : Maximum of 10mA (in standby mode)

• Number of pads : 224

1/34

¡ Semiconductor MSM6794

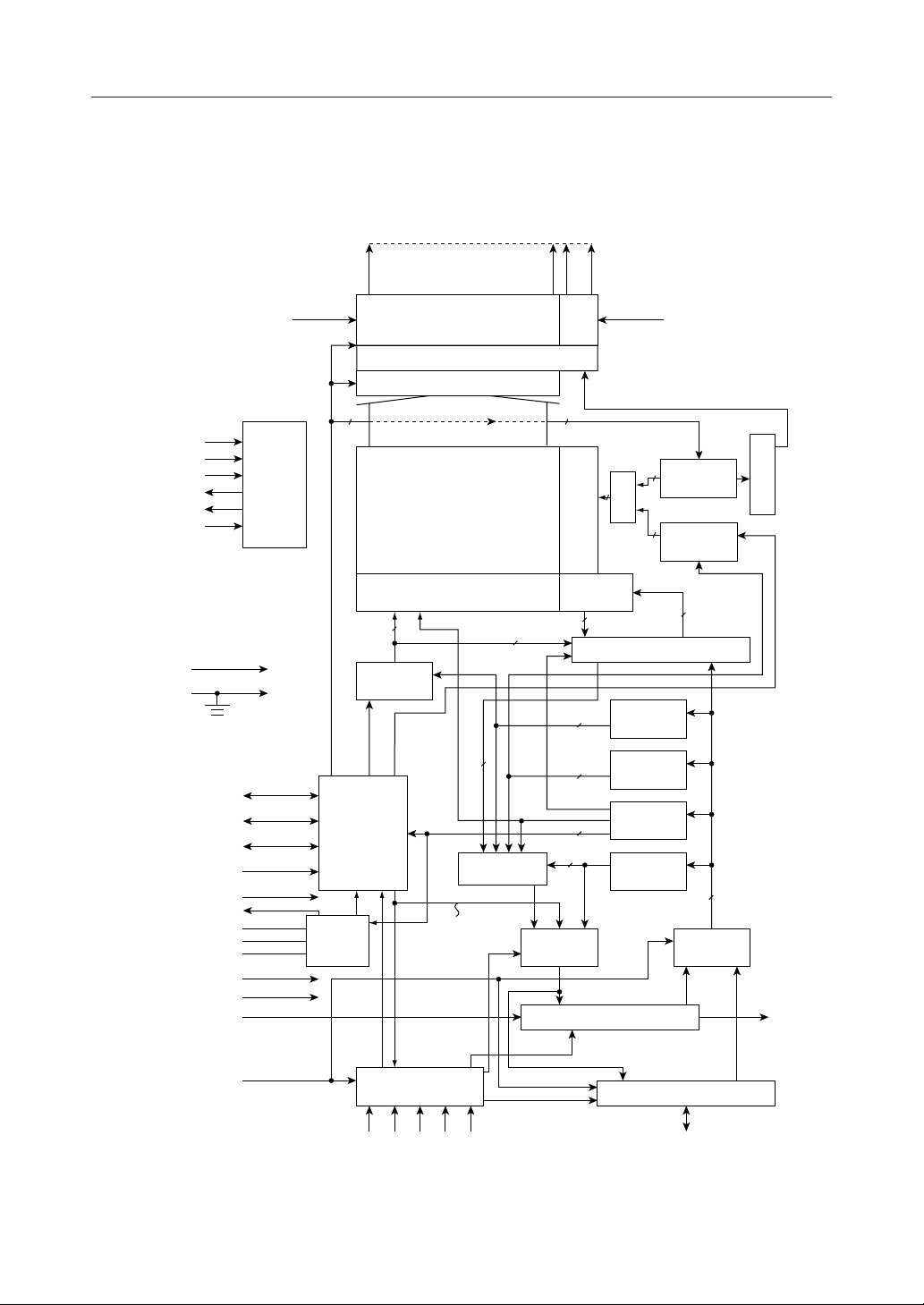

BLOCK DIAGRAM

COM48

SEG1

SEG128 COM1

LCD drive power supply

V1, V3, V4, V6

V

VC1

VC2

VS1

VS2

DT

to V

V

DD1

DD4

V

to V

SS1

SS3

IN

DF

LCDCK

FLM

M/S

RESET

CO

OSC1

OSC2

OSC3

TEST1

TEST2

multiplier

SI

Voltage

circuit

Segment driver

Level shifter

Data latch

2 2

RAM

128 × 48 bit

display memory

X decoder

5

X address

counter

8

Timing

generator

MPX

Clock

frequency

divider

circuit

BUSY

driver

Common

6

6

MPX

Y decoder

Memory

/output

2

8

input

buffer

6

8-, 6-bit conversion circuit

X address

5

register

Y address

6

register

Control

register

7

7

Address

register

MPX MPX

8-bit Serial register

LCD drive power supply

V1, V2, V5, V6

Common

counter

Decoder

Y address

counter

8

8

SO

P/S

I/O control

SHT CS WR RD RS

Input/output buffer

DB7 to DB0

2/34

¡ Semiconductor MSM6794

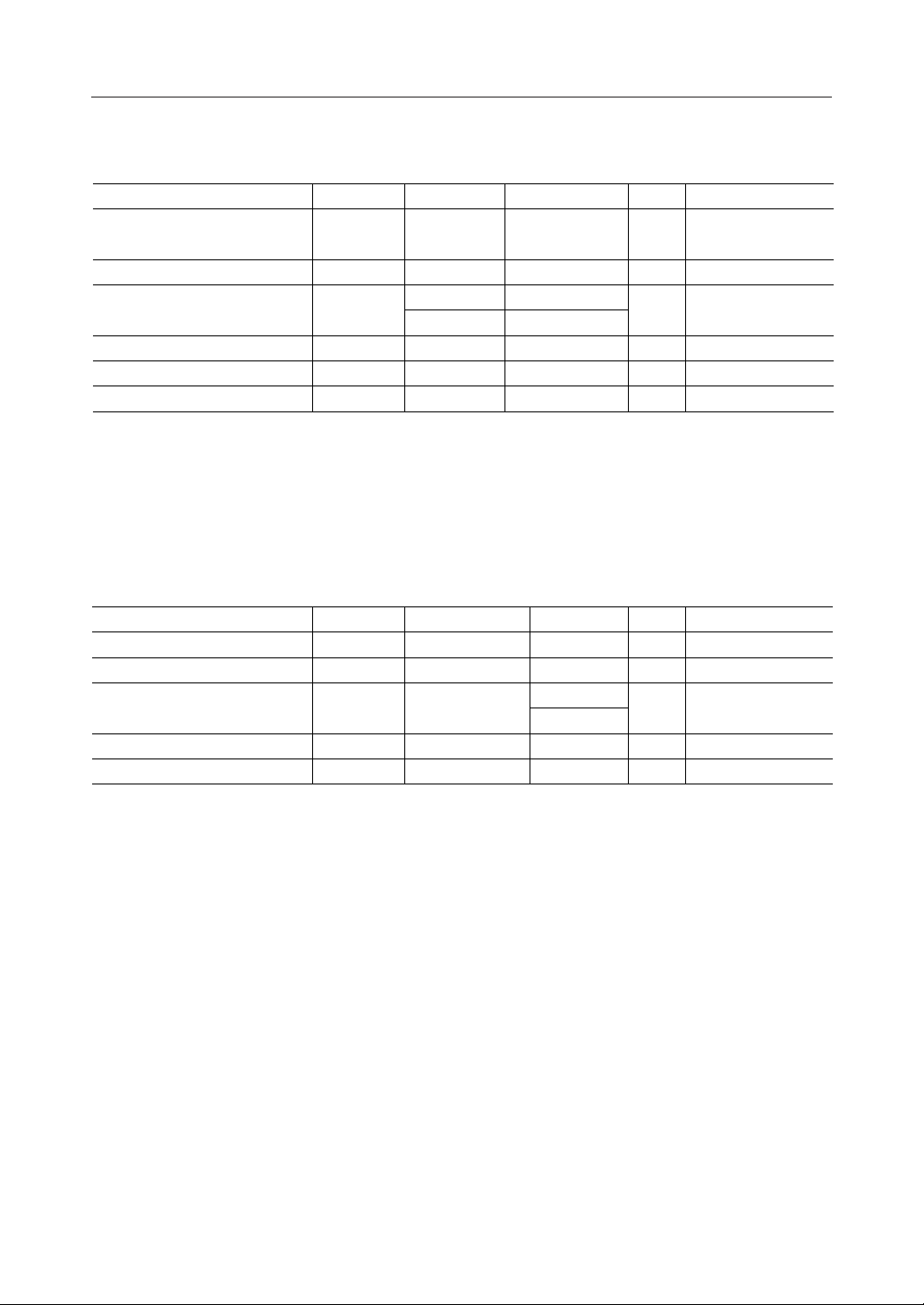

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Rating Unit Applicable Pins

Supply voltage

Bias voltage

Voltage multiplication

reference voltage

Input voltage

Power dissipation

Storage temperature

*2

*3

–0.3 to +7

–0.3 to +14

–0.3 to +7

–0.3 to +4.6

–0.3 to V

*1

–55 to +150

DD

+0.3

V

DD

V

BI

V

IN

V

I

P

D

T

STG

Ta=25˚C,

V

DD1-4–VSS1-3

Ta=25˚C,V1–V6

V

IN–VSS1-3

VIN–V

SS1-3

Ta=25˚C

—

—

V

V

V

V

mW

˚C

V

DD1-4

V1, V6

V

IN, VSS1-3

All Inputs

—

—

, V

SS1-3

Ta : ambient temperature

*1 Power dissipation depends on the heat radiation in a device attach condition. Set junction

temperature to 150˚C or lower.

*2 Ta = 25˚C; when doubler is used.

*3 Ta = 25˚C; when tripler is used.

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Condition Range Unit Applicable Pins

Supply voltage

Bias voltage

Voltage multiplicatipon

reference voltage

Operating frequency

Operating temperature

1

2.7 to 5.5

5 to 12

1 to V

DD

1 to 4

270 to 500

–25 to +85

V

V

V

kHz

˚C

V

DD

V

BI

V

IN

f

op

T

op

V

DD1-4–VSS1-3

V1–V6

VIN–V

SS1-3

See Note 1 on p.6

2

—

V

DD1-4, VSS1-3

V1, V6

V

, V

IN

SS1-3

OSC1

—

1 For bias potential, V1 has the highest potential and V6 has the lowest potential. Use V6 at the

same potential as V

SS1

to V

SS3

.

2 RC oscillation and external input clock frequency (when frequency dividing ratio is 1).

For divided frequency operation, clock frequency after dividing must be within this range.

3/34

¡ Semiconductor MSM6794

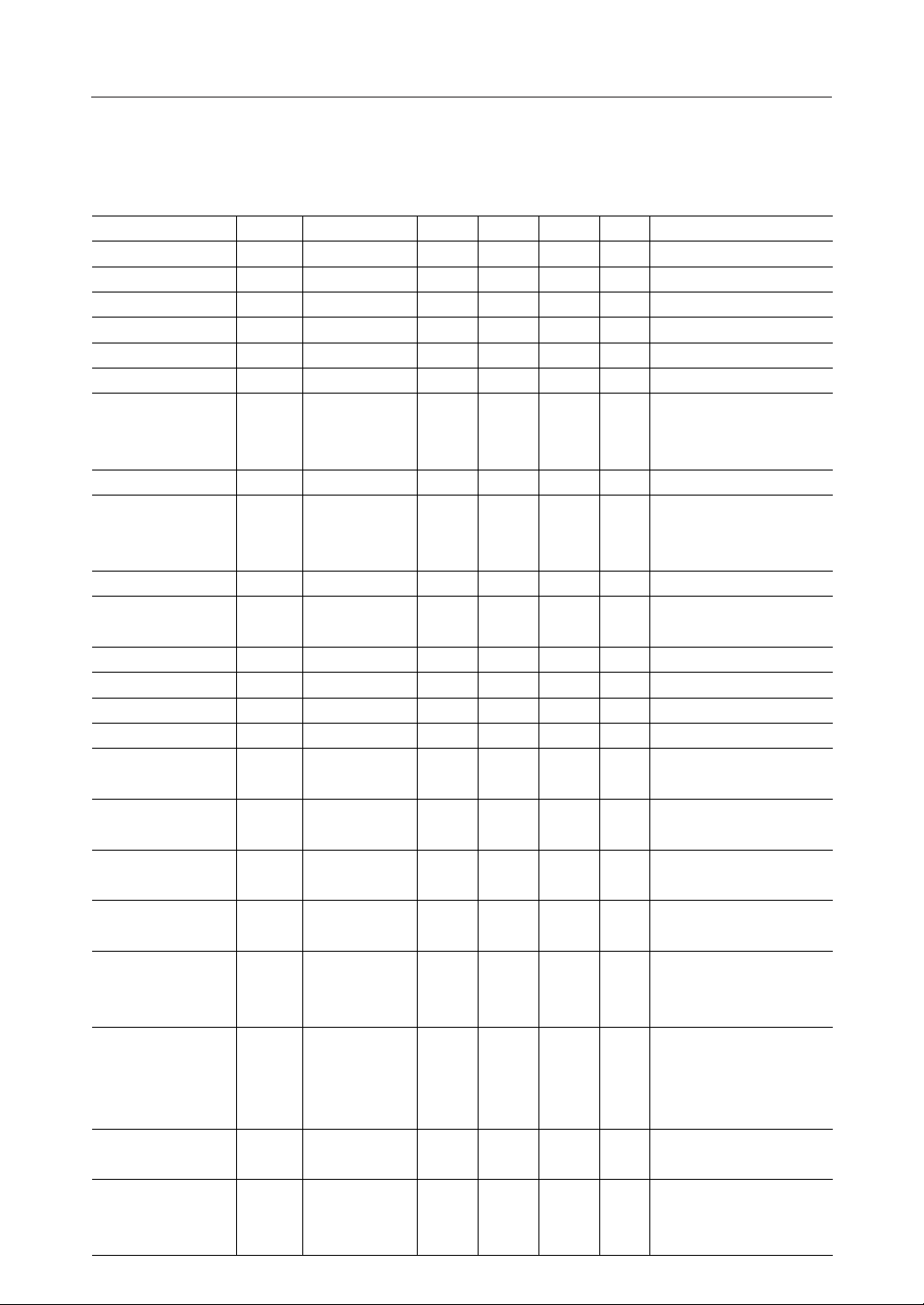

ELECTRICAL CHARACTERISTICS

DC Characteristics (1)

(V

=2.7 to 4.5V, VBI=5 to 12V, Ta=–25 to +85˚C)

DD

Parameter Symbol Condition Min. Typ. Max. Unit. Applicable Pin

"H" input voltage 1

"H" input voltage 2

"H" input voltage 3

"L" input voltage 1

"L" input voltage 2

"L" input voltage 3

DD

DD

DD

—

—

—

—

—

—

V

V

DD

V

0.2V

0.2V

0.2V

DD

DD

V

IH1

V

IH2

V

IH3

V

IL1

V

IL2

V

IL3

—

—

—

—

—

—

0.8V

0.8V

0.8V

0

0

0

DD

DD

DD

V

V

V

V

V

Unit.

DB0-7, LCDCK, FLM, DF

Other input pins

DB0-7, LCDCK, FLM, DF

Other input pins

Input pins excluding

"H" input current 1

I

IH1

V

I=VDD

—

—

5

µA

DB0-7

FLM and DF

"H" input current 2

I

IH2

VI=V

DD

–5

—

5

DB0-7, LCDCK, FLM, DF

µA

Input pins excluding

"L" input current I

I

IL1

VI=0V

–5

—

—

µA

DB0-7

FLM and DF

"L" input current 2

OFF leakage

current

"H" output voltage 1

"H" output voltage 2

"L" output voltage 1

"L" output voltage 2

Multiplied voltage 1

Doubler output

Multiplied voltage 2

Tripler output

COM output

resistance

SEG output

resistance

I

IL2

I

off

V

OH1

V

OH2

V

OL1

V

OL2

V

DB

V

TR

R

C

R

S

V

V

I=VDD

I

=–1.0mA

O

=–1.0mA

I

O

=1.0mA

I

O

=1.0mA

I

O

=–500µA

I

O

=350kHz

f

osc

=–500µA

I

O

=350kHz

f

osc

I

=±50µA

O

=±20µA

I

O

=0V

I

or 0V

–5

–5

0.9V

0.9V

—

—

V

IN

–0.5

V

IN

–1.0

—

—

×2

×3

DD

DD

—

—

—

—

—

—

—

—

—

—

—

—

0.1V

0.1V

—

—

10

20

5

5

DD

DD

DB0-7, LCDCK, FLM, DF

µA

µA

CO, LCDCK, FLM, DF, SO

V

V

V

V

DB0 to DB7

CO, LCDCK, FLM, DF, SO

DB0 to DB7

V

V

kΩ

kΩ

COM1 to COM48

SEG1 to SEG128

During display

Supply Current 1

I

DD1

External clock

= 350kHz

f

osc

—

—

450

µA

During display

Supply Current 2

I

DD2

Internal

oscillation

= 350kHz

f

osc

—

360

700

µA

OSC1

OSC1

, LCDCK,

, LCDCK,

SO

VS2

VS2

V

DD

V

DD

Supply Current 3

Oscillation

frequency

I

f

DDS

OSC

During standby

R

=18kΩ

f

=56pF

C

f

See Note 3 on p.6

—

292

—

350

10

437

µA

kHz

V

DD

OSC1, OSC2, OSC3

4/34

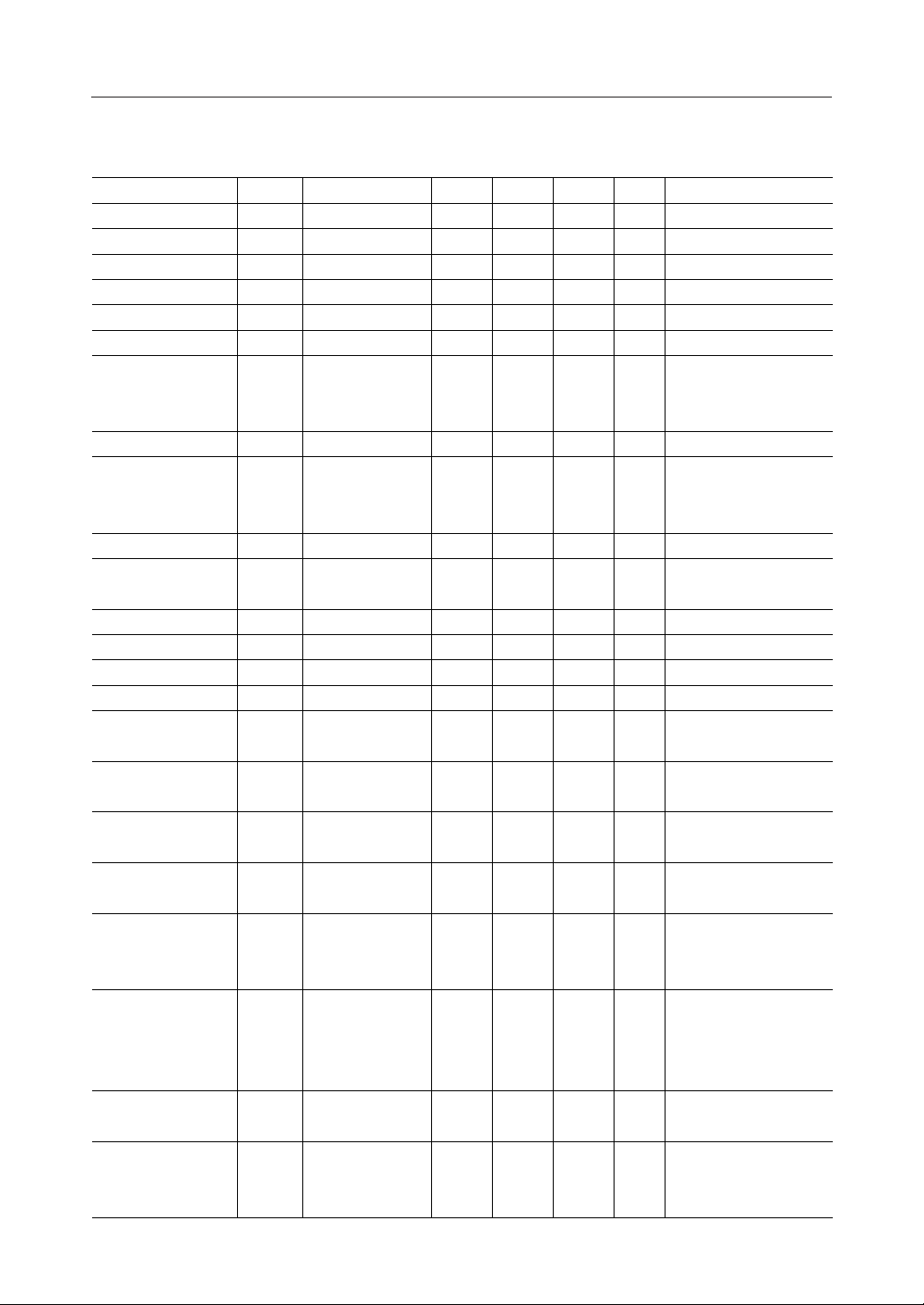

¡ Semiconductor MSM6794

DC Characteristics (2)

=4.5 to 5.5V, VBI=5 to 12V, Ta=–25 to +85˚C)

(V

DD

Parameter Symbol Condition Min. Typ. Max. Unit Applicable Pin

"H" input voltage 1

"H" input voltage 2

"H" input voltage 3

"L" input voltage 1

"L" input voltage 2

"L" input voltage 3

"H" input current 1

"H" input current 2

"L" input current I

"L" input current 2

OFF leakage

current

"H" output voltage 1

"H" output voltage 2

"L" output voltage 1

"L" output voltage 2

Multiplied voltage 1

Doubler output

Multiplied voltage 2

Tripler output

V

IH1

V

IH2

V

IH3

V

IL1

V

IL2

V

IL3

I

IH1

I

IH2

I

IL1

I

IL2

I

off

V

OH1

V

OH2

V

OL1

V

OL2

V

DB

V

TR

— 0.8V

— 0.8V

— 0.8V

— 0 — 0.2V

— 0 — 0.2V

— 0 — 0.2V

—VDDV OSC1

DD

—VDDV

DD

—VDDV Other input pins

DD

DD

DD

DD

DB0-7, LCDCK, FLM, DF

V OSC1

V

DB0-7, LCDCK, FLM, DF

V Other input pins

Input pins excluding

VI=V

DD

—— 5µA

DB0-7

FLM and DF

VI=V

DD

–5 — 5 µA

DB0-7, LCDCK, FLM, DF

Input pins excluding

V

=0V –5 — — µA

I

DB0-7

FLM and DF

V

=0V –5 — 5 µA

I

VI=V

/0V –5 — 5 µASO

DD

IO=–1.5mA 0.9V

IO=–1.5mA 0.9V

IO=1.5mA — — 0.1V

IO=1.5mA — — 0.1V

I

=–500µA

O

f

=350kHz

osc

I

=–500µA

O

f

=350kHz

osc

V

–0.5

V

–1.0

IN

IN

— — V CO, LCDCK, FLM, DF, SO

DD

— — V DB0 to DB7

DD

DD

DD

×2

— — V VS2

×3

— — V VS2

DB0-7, LCDCK, FLM, DF

V CO, LCDCK, FLM, DF, SO

V DB0 to DB7

, LCDCK,

, LCDCK,

COM output

resistance

SEG output

resistance

Supply Current 1

Supply Current 2

Supply Current 3

Oscillation

frequency

I

I

I

f

R

C

R

S

DD1

DD2

DDS

OSC

See Note 3 on p.6

I

=±50µA——10kΩCOM1 to COM48

O

I

=±20µA——20kΩSEG1 to SEG128

O

During display

External clock

f

= 350kHz

osc

— — 450 µA V

During display

Internal

oscillation

f

=350kHz

osc

During standby

R

=22kΩ

f

C

=56pF

f

— 360 700 µA V

——10µA V

292 350 437 kHz OSC1, OSC2, OSC3

DD

DD

DD

5/34

¡ Semiconductor MSM6794

g

g

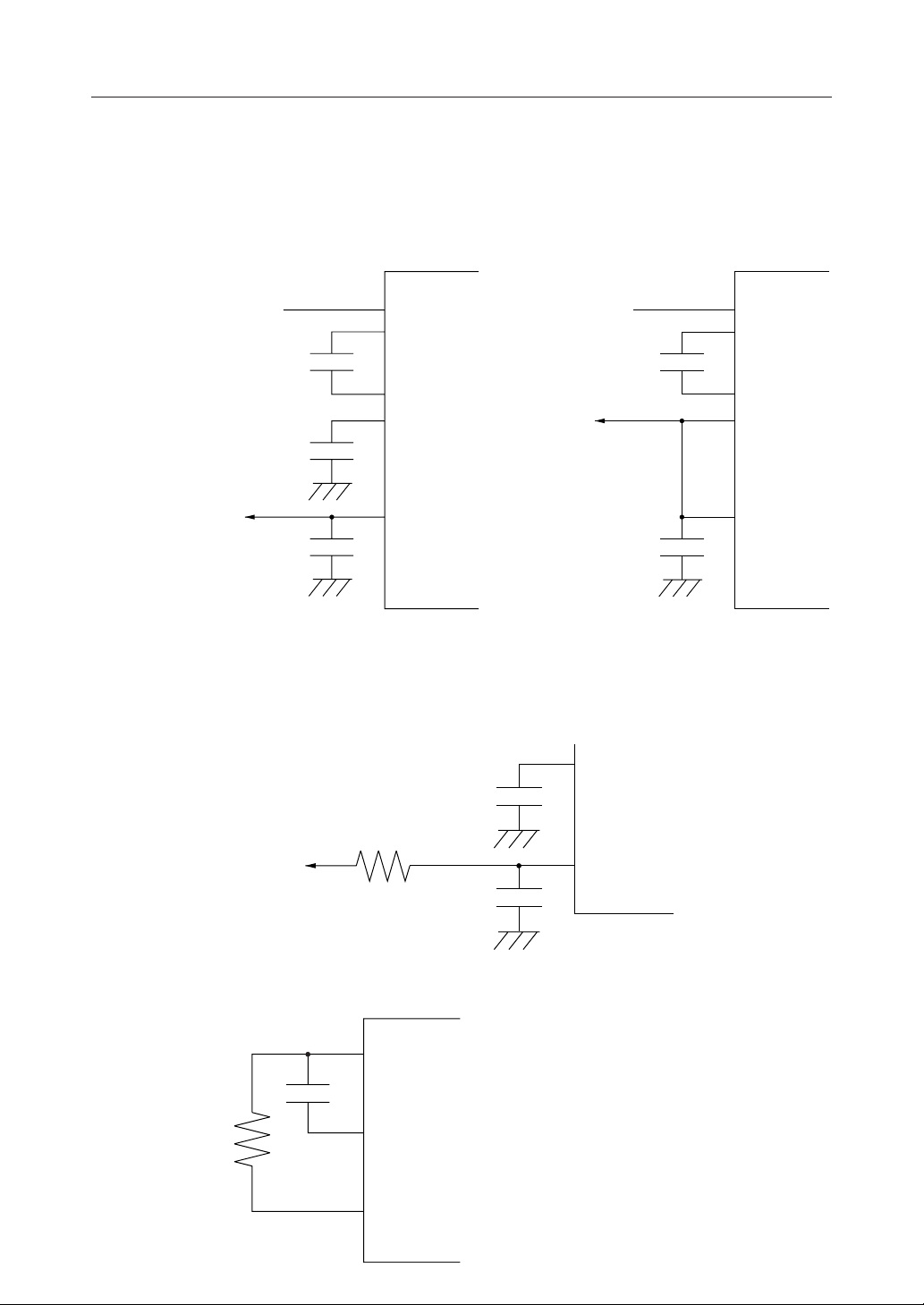

Notes: 1. Voltage multiplication reference voltage is = VDD maximum when the multiplied

voltage is 12V or less.

The voltage multiplication reference voltage is 4V maximum when the multiplied

voltage is 12V or more (tripler output).

Condition: f

= 350kHz

osc

Voltage multiplier circuit configuration: connect as in the following diagram.

<Usin

V

IN

VC1

VC2

VS1

VS2

tripler>

Voltage multiplication

reference voltage

Doubler output

4.7µF

4.7µF

+

+

<Usin

Voltage multiplication

reference voltage

Tripler output

4.7µF

4.7µF

4.7µF

+

+

+

2. If the multiplied voltage output and bias power supply are directly connected, the

voltage multiplier circuit operation may malfunction due to bias power supply noise.

A countermeasure for noise is necessary, such as inserting a series resistor to prevent

noise from entering multiplied voltage output (VS1, VS2).

+

4.7µF

VS1

V

IN

VC1

VC2

VS1

VS2

doubler>

100Ω

Tripler output

+

VS2

4.7µF

3. RC oscillation circuit configuration: connect as in the following diagram.

R

= 18kΩ ± 2 % (V

OSC1

C

f

R

f

OSC2

f

= 22kΩ ± 2 % (V

R

f

C

= 56pF ± 5 %

f

OSC3

= 2.7 to 4.5V)

DD

= 4.5 to 5.5V)

DD

6/34

¡ Semiconductor MSM6794

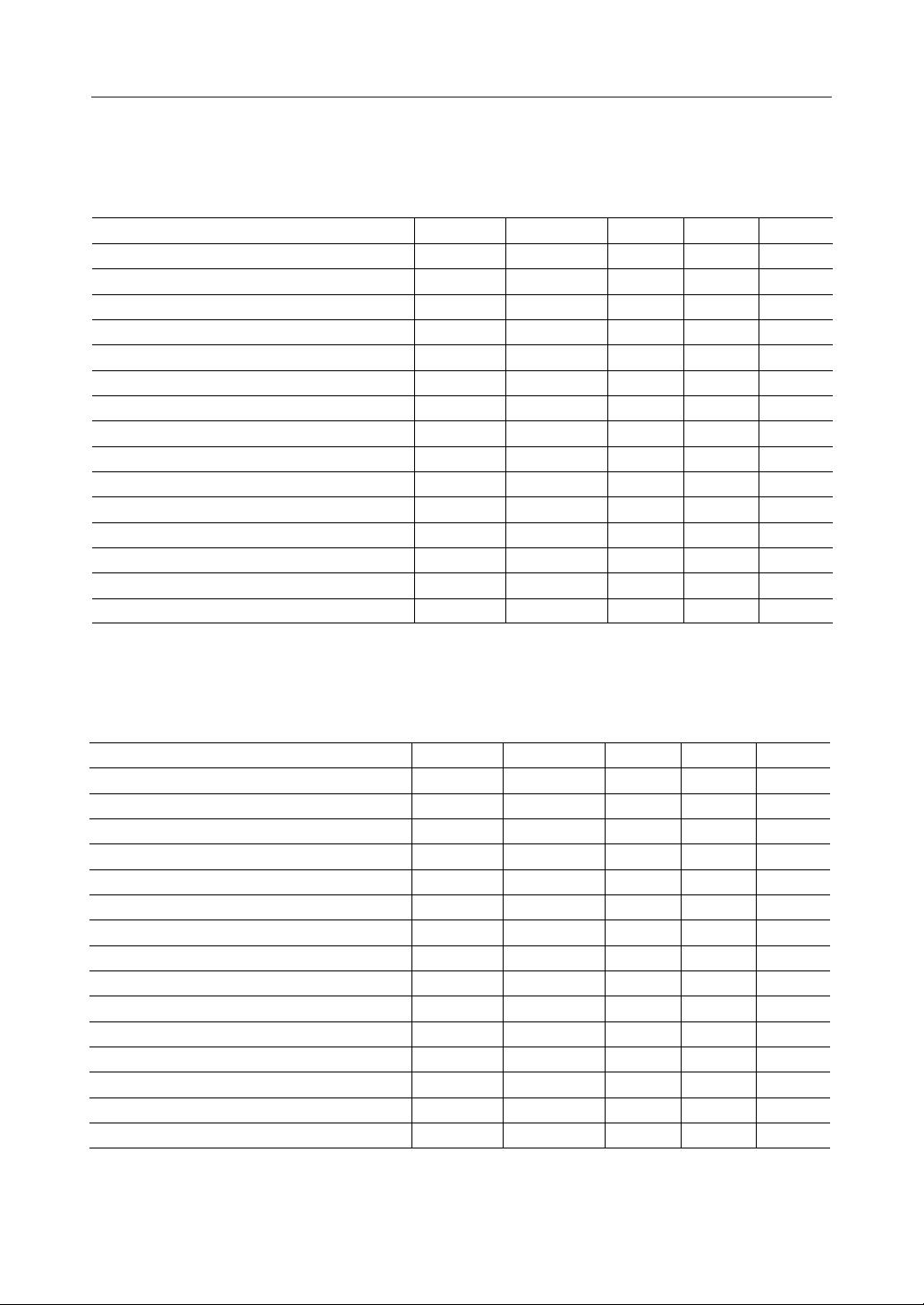

AC Characteristics

Parallel interface (1)

Parameter Symbol Condition Min Max Unit

RD "H" level width

RD "L" level width

WR "H" level width

WR "L" level width

WR-RD "H" level width

CS, RS setup time

CS, RS hold time

Write data setup time

Write data hold time

Read data output delay time

Read data hold time

External clock "H" level width

External clock "L" level width

RESET pulse width

External clock rise time, fall time

Parallel interface (2)

Parameter Symbol Condition Min Max Unit

RD "H" level width

RD "L" level width

WR "H" level width

WR "L" level width

WR-RD "H" level width

CS, RS setup time

CS, RS hold time

Write data setup time

Write data hold time

Read data output delay time

Read data hold time

External clock "H" level width

External clock "L" level width

RESET pulse width

External clock rise time, fall time tr, t

t

WRH

t

WRL

t

WWH

t

WWL

t

WWRH

t

AS

t

AH

t

DSW

t

DHW

t

DDR

t

DHR

t

WCH

t

WCL

t

WRE

t

, t

r

f

t

WRH

t

WRL

t

WWH

t

WWL

t

WWRH

t

AS

t

AH

t

DSW

t

DHW

t

DDR

t

DHR

t

WCH

t

WCL

t

WRE

f

(V

=2.7 to 4.5V, VBI=5 to 12V, Ta=–25 to +85˚C)

DD

— 200 — ns

— 200 — ns

— 200 — ns

— 200 — ns

— 200 — ns

—50—ns

—10—ns

—50—ns

—20—ns

CL=50pF — 170 ns

—20—ns

— 200 — ns

— 200 — ns

— 2.0 — µs

— — 100 ns

(V

=4.5 to 5.5V, VBI=5 to 12V, Ta=–25 to +85˚C)

DD

— 150 — ns

— 150 — ns

— 150 — ns

— 150 — ns

— 150 — ns

—50—ns

—10—ns

—50—ns

—20—ns

CL=50pF — 130 ns

—20—ns

— 150 — ns

— 150 — ns

— 2.0 — µs

— — 20 ns

7/34

¡ Semiconductor MSM6794

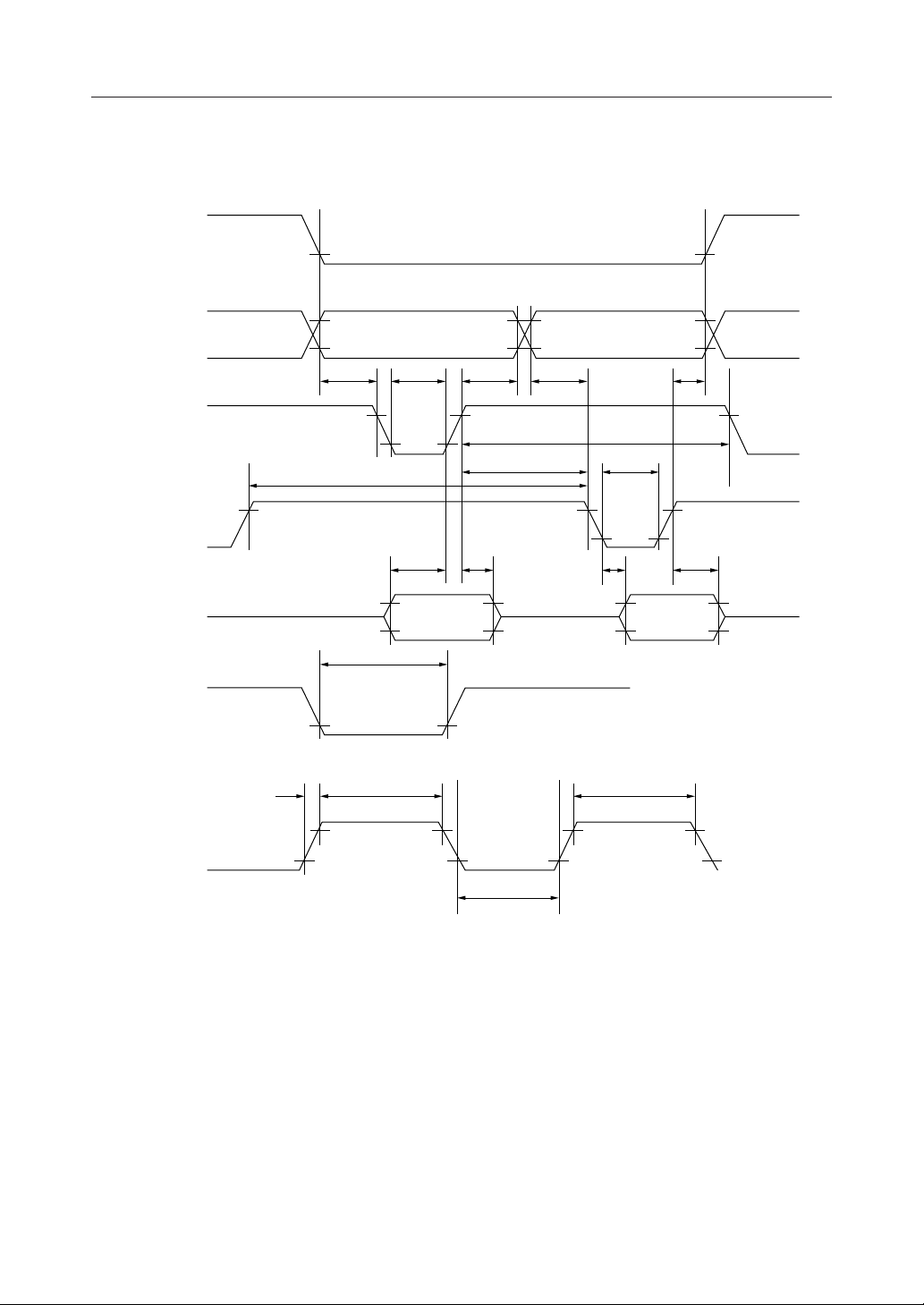

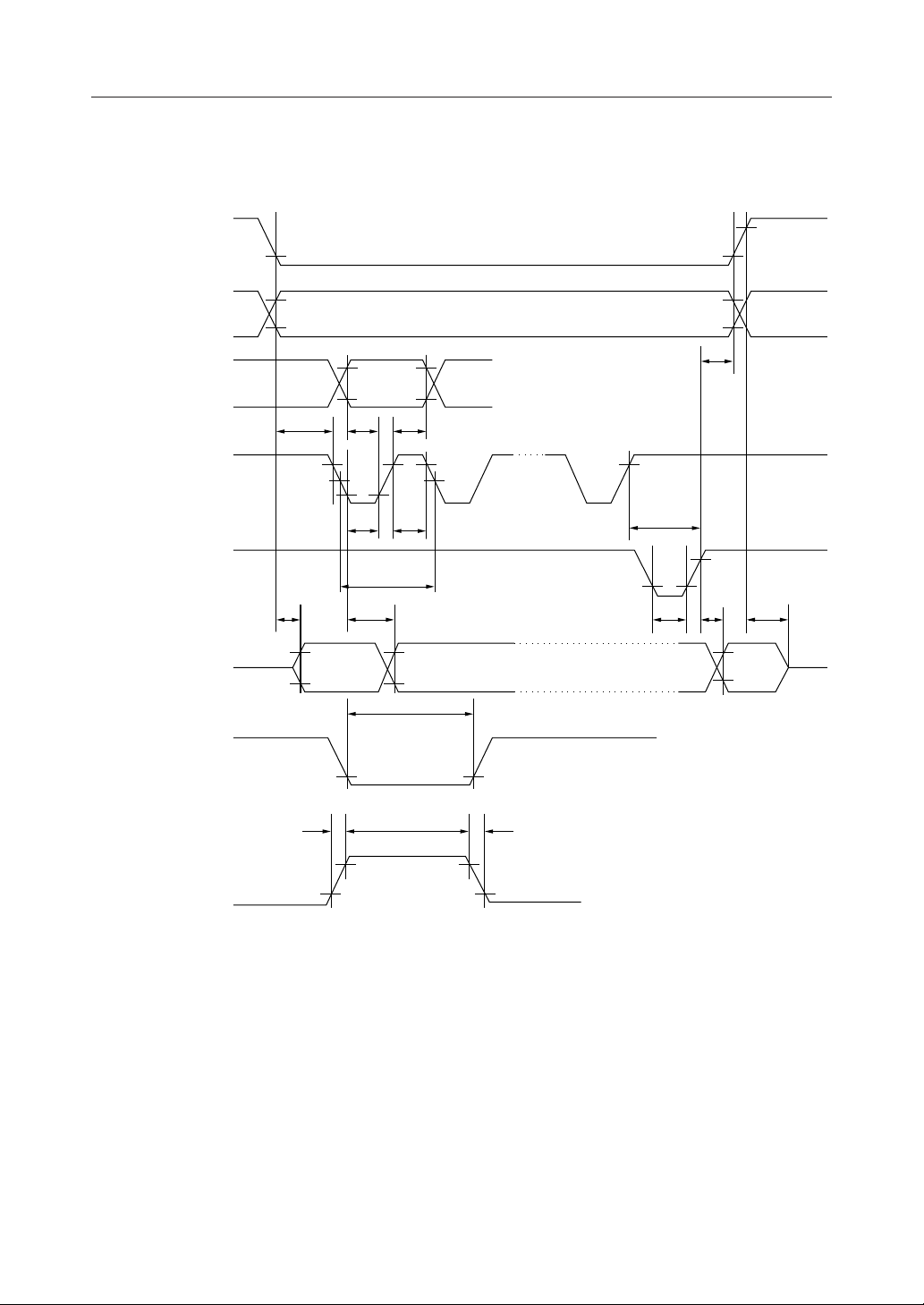

Parallel Interface Timing Diagram

—

V

IH

CS

RS

WR

RD

—

V

IL

—

V

IH

—

V

IL

t

AS

—

V

IH

—

V

IL

—

V

IH

—

V

IL

t

WRH

t

t

WWL

DSW

t

DHW

t

AH

t

WWH

t

WWRH

t

AS

t

WRL

t

DDR

t

AH

t

DHR

DB0-DB7

RESET

OSC1

V

IH

V

IL

t

WRE

—

V

IL

t

r

—

V

IH

—

V

IL

t

f

t

WCL

V

OH

V

OL

t

WCH

V

IH

V

OH

, V

0.8V

=

0.9V

=

= 0.2V

DD

IL

DD

, V

= 0.1V

DD

OL

DD

8/34

¡ Semiconductor MSM6794

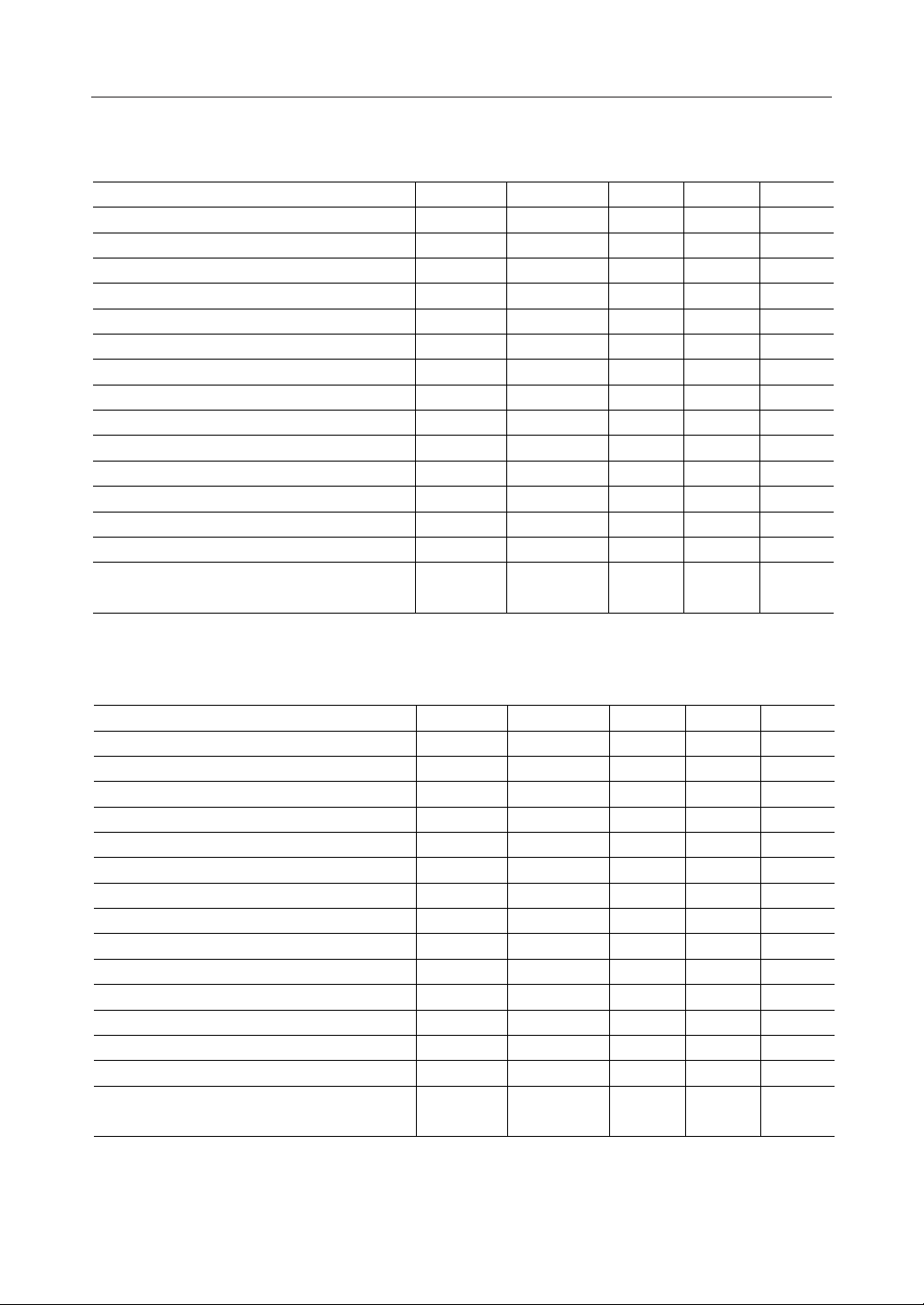

Serial interface (1)

=2.7 to 4.5V, VBI=5 to 12V, Ta=–25 to +85˚C)

(V

DD

Parameter Symbol Condition Min Max Unit

CS, RS setup time

CS, RS hold time

S1 setup time

S1 hold time

SHT "H" pulse width

SHT "L" pulse width

SHT clock cycle time

SO ON delay time

SO output delay time

SO OFF delay time

BUSY delay time

WR setup time

WR "L" pulse width

RESET pulse width

t

SAS

t

SAH

t

IS

t

IH

t

WSHH

t

WSHL

t

SYS

t

ON

t

DS

t

OFF

t

BUSY

t

SHS

t

WWL

t

WRE

—60—ns

—15—ns

— 100 — ns

—15—ns

— 100 — ns

— 100 — ns

— 400 — ns

CL=50pF — 200 ns

CL=50pF 0 200 ns

— — 50 ns

CL=50pF — 200 ns

— 100 — ns

— 120 — ns

— 2.0 — µs

External clock rise time, fall time tr, t

Serial interface (2)

Parameter Symbol Condition Min Max Unit

CS, RS setup time

CS, RS hold time

S1 setup time

S1 hold time

SHT "H" pulse width

SHT "L" pulse width

SHT clock cycle time

SO ON delay time

SO output delay time

SO OFF delay time

BUSY delay time

WR setup time

WR "L" pulse width

RESET pulse width

f

t

SAS

t

SAH

t

IS

t

IH

t

WSHH

t

WSHL

t

SYS

t

ON

t

DS

t

OFF

t

BUSY

t

SHS

t

WWL

t

WRE

— — 100 ns

=4.5 to 5.5V, VBI=5 to 12V, Ta=–25 to +85˚C)

(V

DD

—50—ns

—10—ns

—50—ns

—10—ns

—80—ns

—80—ns

— 200 — ns

CL=50pF — 100 ns

CL=50pF 0 100 ns

— — 20 ns

CL=50pF — 100 ns

—50—ns

—80—ns

— 2.0 — µs

External clock rise time, fall time tr, t

f

— — 20 ns

9/34

¡ Semiconductor MSM6794

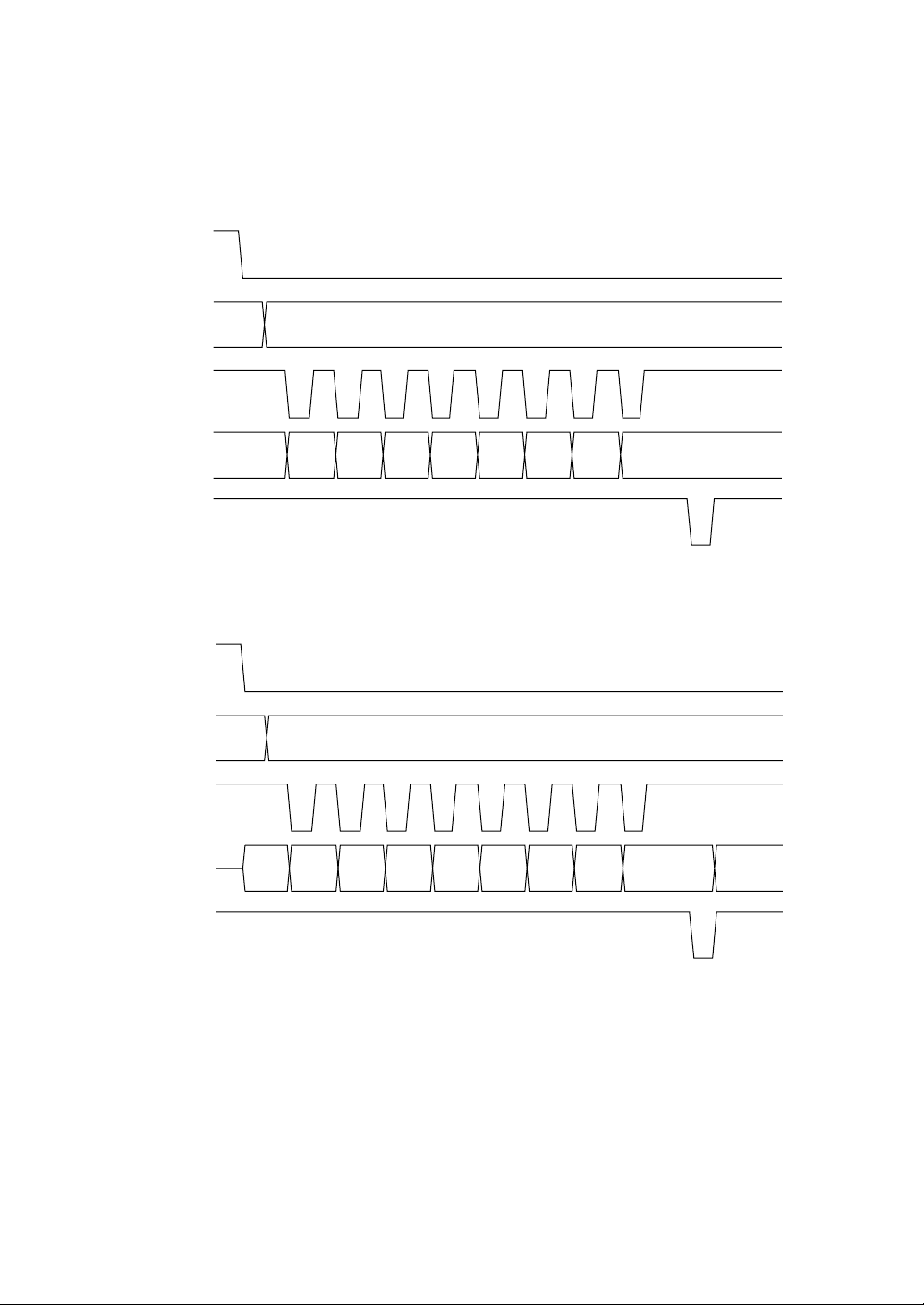

Serial Interface Timing Diagram

—

V

CS

RS

SI

SHT

WR

IH

—

V

IL

—

V

IH

—

V

IL

—

V

IH

—

V

IL

t

SAS

—

V

IH

—

V

IL

—

V

IH

—

V

IL

50%

t

ON

t

WSHL

t

t

IS

IH

t

WSHH

t

SYS

t

DS

t

SAH

t

SHS

t

WWLtBUSYtOFF

SO

RESET

OSC1

—

V

V

V

V

V

“Z”

OH

—

OL

t

WRE

—

IL

t

r

—

IH

—

IL

t

f

= 0.8VDD, VIL = 0.2V

V

IH

VOH = 0.9VDD, VOL = 0.1V

DD

DD

“Z”

10/34

¡ Semiconductor MSM6794

Serial Interface Input/Output Timing

Input timing

CS

RS

SHT

SI

WR

Output timing

RS

SO

CS

SHT

WR

D7 D6 D5 D4

BUSY BUSY

D7 D6 D5 D4

D3

D2 D1 D0

D3

D2 D1 D0

For SO output, 8 bits after input of the WR pulse are valid.

11/34

Loading...

Loading...