OKI MSM66Q589GS-BK, MSM66P589-xxxGS-BK, MSM66589-xxxGS-BK Datasheet

E2E1031-27-Y4

Preliminary

¡ Semiconductor MSM66589/66P589/66Q589

¡ Semiconductor

This version: Jan. 1998

Previous version: Nov. 1996

MSM66589/66P589/66Q589

OLMS-66K Series CMOS 16-Bit Microcontroller

GENERAL DESCRIPTION

The MSM66589/66P589/66Q589 is a high-speed, high-performance 16-bit microcontroller that

employs OKI original nX-8/500S CPU core.

The MSM66589/66P589/66Q589 includes a 16-bit CPU, ROM, RAM, a 10-bit A/D converter,

serial ports, flexible timers, pulse-width modulator (PWM), and I/O ports.

The MSM66Q589 is a Flash EEPROM version.

FEATURES

• Program memory space : 128K bytes

Internal ROM : 96K bytes (MSM66589/66P589)

: 128K bytes (MSM66Q589)

• Data memory space : 64K bytes

Internal RAM : 4K bytes

• High-speed execution

Minimum instruction execution time : 100 nsec (@ 20 MHz)

• Built-in multiplier

• Powerful instruction set : Instruction set superior in orthogonal matrix

8/16-bit data transfer instructions

8/16-bit arithmetic instructions

Multiplication and division operation instructions

Bit manipulation instructions

Bit logic instructions

ROM table reference instructions

• Abundant addressing modes : Register addressing

Page addressing

Pointing register indirect addressing

Stack addressing

Immediate addressing

• I/O port

Analog input only ports : 16 channels

Input-output ports : 11 ports ¥ 8 bits, 1 port ¥ 6 bits

(Each bit can be configured to be an input or output)

• Flexible timers

Free run counters : 19 bits ¥ 1, 16 bits ¥ 1

19-bit CAP with a divider : 4

16-bit double buffer RTO : 6

16-bit RTO/PWM : 2

16-bit CAP/RTO : 6

• 8-bit general timer : 1

8-bit event counter : 1

• 16-bit PWM : 8

Input clock divider : 1

• 8-bit serial ports

1/27

¡ Semiconductor MSM66589/66P589/66Q589

UART mode with BRG : 1

Synchronous/UART switchable mode

with BRG : 1

• 10-bit A/D converter : 16 channels

• Transition detector : 6

• Watchdog timer : 1

• Interrupts

Non-maskable : 1

Maskable : Internal 47/external 2

(4-level priority can be set)

• ROM window function

• Standby modes

HALT mode

STOP mode

• Package:

128-pin plastic QFP (QFP128-P-2828-BK) (Product name: MSM66589-¥¥¥GS-BK)

(Product name: MSM66P589-¥¥¥GS-BK)

(Product name: MSM66Q589GS-BK)

¥¥¥ indicates the code number.

2/27

¡ Semiconductor MSM66589/66P589/66Q589

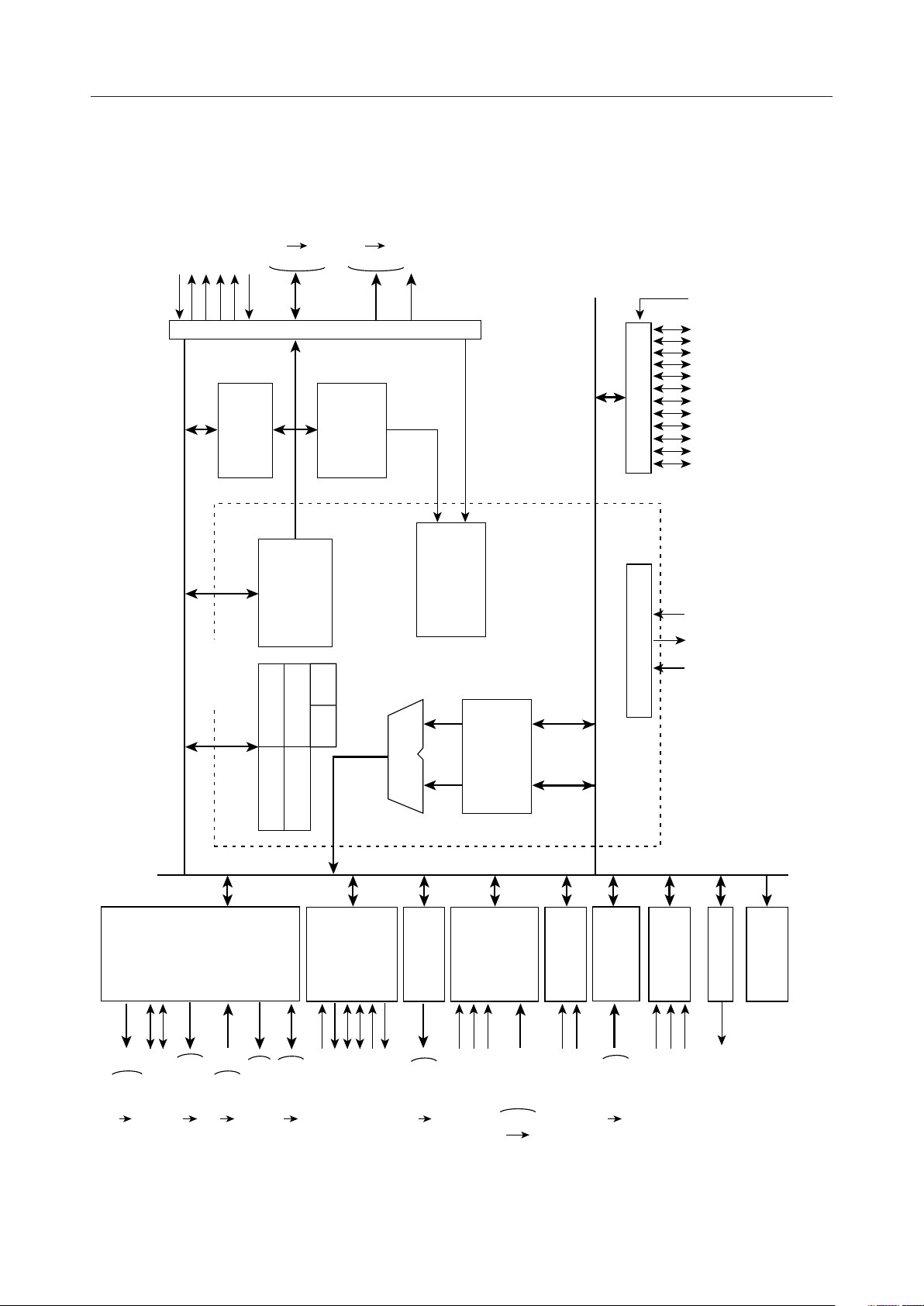

BLOCK DIAGRAM

EA

ALE/P5_5

PSEN/P5_4

RD/P7_1

WR/P7_0

WAIT/P7_2

AD0/P0_0

AD7/P0_7

A8/P1_0

A15/P1_7

A16/P9_0

E

O

1

1

BUS PORT CONTROL

RAM

4K bytes

ROM *

96K bytes

Port Control

P

1

0

P

9

P

8

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

P

Memory Control

CPU Core

PSW

SSP

Control

Registers

Flexible Timer

Pointing R.

Local R.

PC

TSR CSR

LRB

Serial Port

ALU

Instruction

Decoder

PWM

ALU Control

ACC

A/ D

Converter

Detector

Transition

Event Timer

E

S

R

S

C

O

S

C

O

System Control

Interrupt

Peripheral

1

0

WDT

* MSM66Q589 (Flash EEPROM version) contains 128K bytes Flash EEPROM.

P2_0/RTO4

P2_5/RTO9

P2_6/FTM10

P3_0/FTM11A

P3_1/FTM11B

P3_3/FTM11D

P3_4/CAP0

P3_7/CAP3

P10_0/RTO12

P6_2/RXD1

P10_1/RTO13

P10_2/FTM14

P6_3/TXD1

P10_5/FTM17

P6_4/RXC1

P6_5/TXC1

P6_6/RXD0

P6_7/TXD0

DD

P7_4/PWM0

REF

P8_3/PWM7

AV

V

AGND

AI0

AI15

P4_0/ETMCK

P4_1/ECTCK

P4_2/TRNS0

P4_7/TRNS5

P6_0/INT0

P6_1/INT1

NMI

P7_3/CLKOUT

3/27

4/27

¡ Semiconductor MSM66589/66P589/66Q589

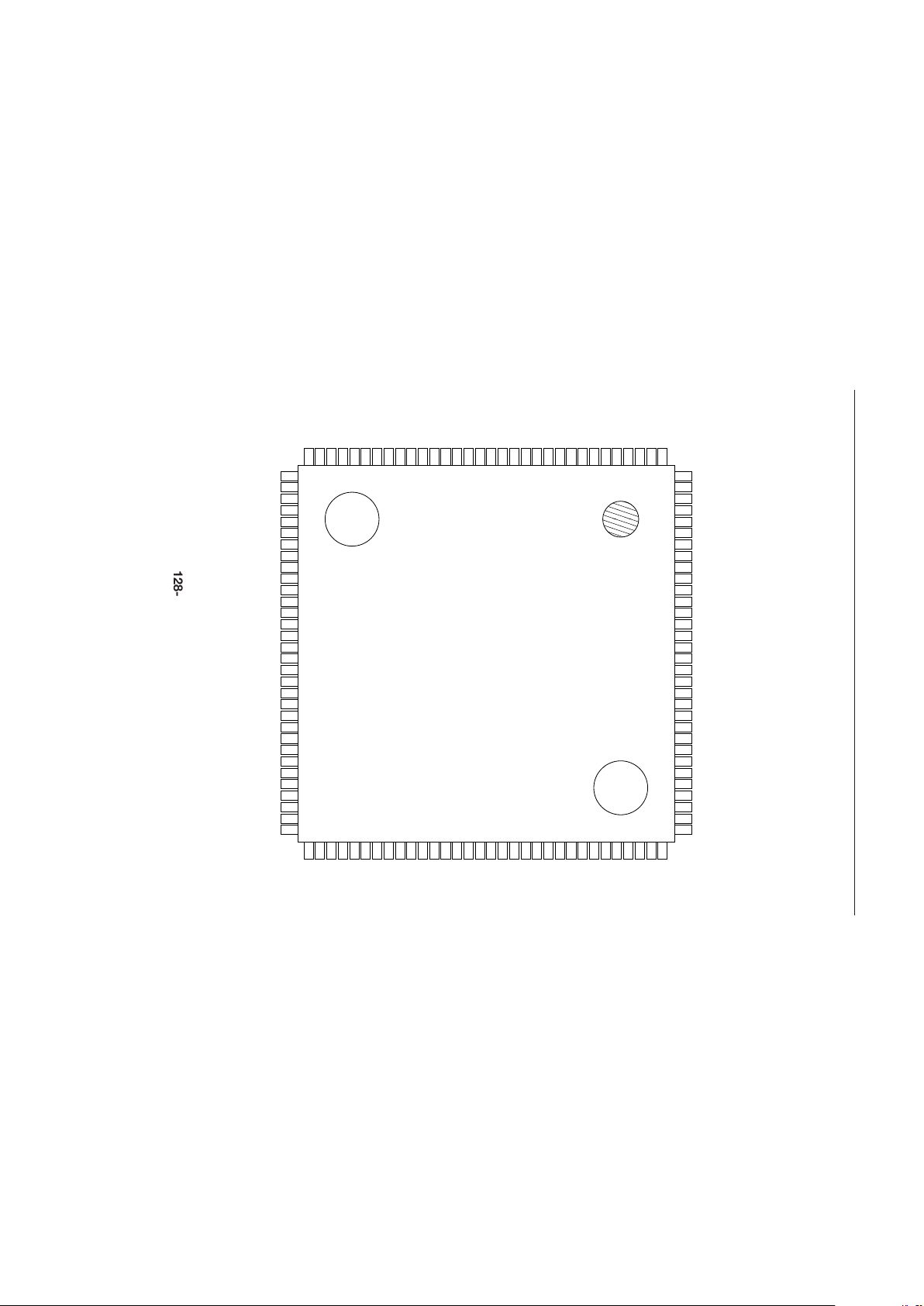

PIN CONFIGURATION (TOP VIEW)

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

1234567891011

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

P2_6/FTM10

P2_5/RTO9

P2_4/RTO8

P2_3/RTO7

P2_2/RTO6

P2_1/RTO5

P2_0/RTO4

V

DD

P9_7

P9_6

P9_5

P9_4

P9_3

P9_2

P9_1

P9_0/A16

P1_7/A15

P1_6/A14

P1_5/A13

P1_4/A12

P1_3/A11

P1_2/A10

P1_1/A9

P1_0/A8

GND

P0_7/AD7

P0_6/AD6

P0_5/AD5

P0_4/AD4

P0_3/AD3

P0_2/AD2

P0_1/AD1

TRNS3/P4_5

TRNS4/P4_6

TRNS5/P4_7

P5_0

P5_1

P5_2

P5_3

NMI

RES

EA

V

DDAVDD

V

REF

AI0

AI1

AI2

AI3

AI4

AI5

AI6

AI7

AI8

AI9

AI10

AI11

AI12

AI13

AI14

AI15

AGND

GND

INT0/P6_0

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

TRNS2/P4_4

TRNS1/P4_3

TRNS0/P4_2

ECTCK/P4_1

ETMCK/P4_0

P11_7

P11_6

P11_5

P11_4

P11_3

P11_2

P11_1

P11_0

V

DD

CAP3/P3_7

CAP2/P3_6

CAP1/P3_5

CAP0/P3_4

FTM11D/P3_3

FTM11C/P3_2

FTM11B/P3_1

FTM11A/P3_0

GND

P10_7

P10_6

FTM17/P10_5

FTM16/P10_4

FTM15/P10_3

FTM14/P10_2

RTO13/P10_1

RTO12/P10_0

P2_7

P6_1/INT1

P6_2/RXD1

P6_3/TXD1

P6_4/RXC1

P6_5/TXC1

P6_6/RXD0

P6_7/TXD0

GND

OSC0

OSC1

P5_5/ALE

P5_4/PSEN

P7_0/WR

P7_1/RD

P7_2/WAIT

P7_3/CLKOUT

P7_4/PWM0

P7_5/PWM1

P7_6/PWM2

P7_7/PWM3

V

DD

P8_0/PWM4

P8_1/PWM5

P8_2/PWM6

P8_3/PWM7

P8_4

P8_5

P8_6

P8_7

GND

OE

P0_0/AD0

128-Pin Plastic QFP (FLAT)

¡ Semiconductor MSM66589/66P589/66Q589

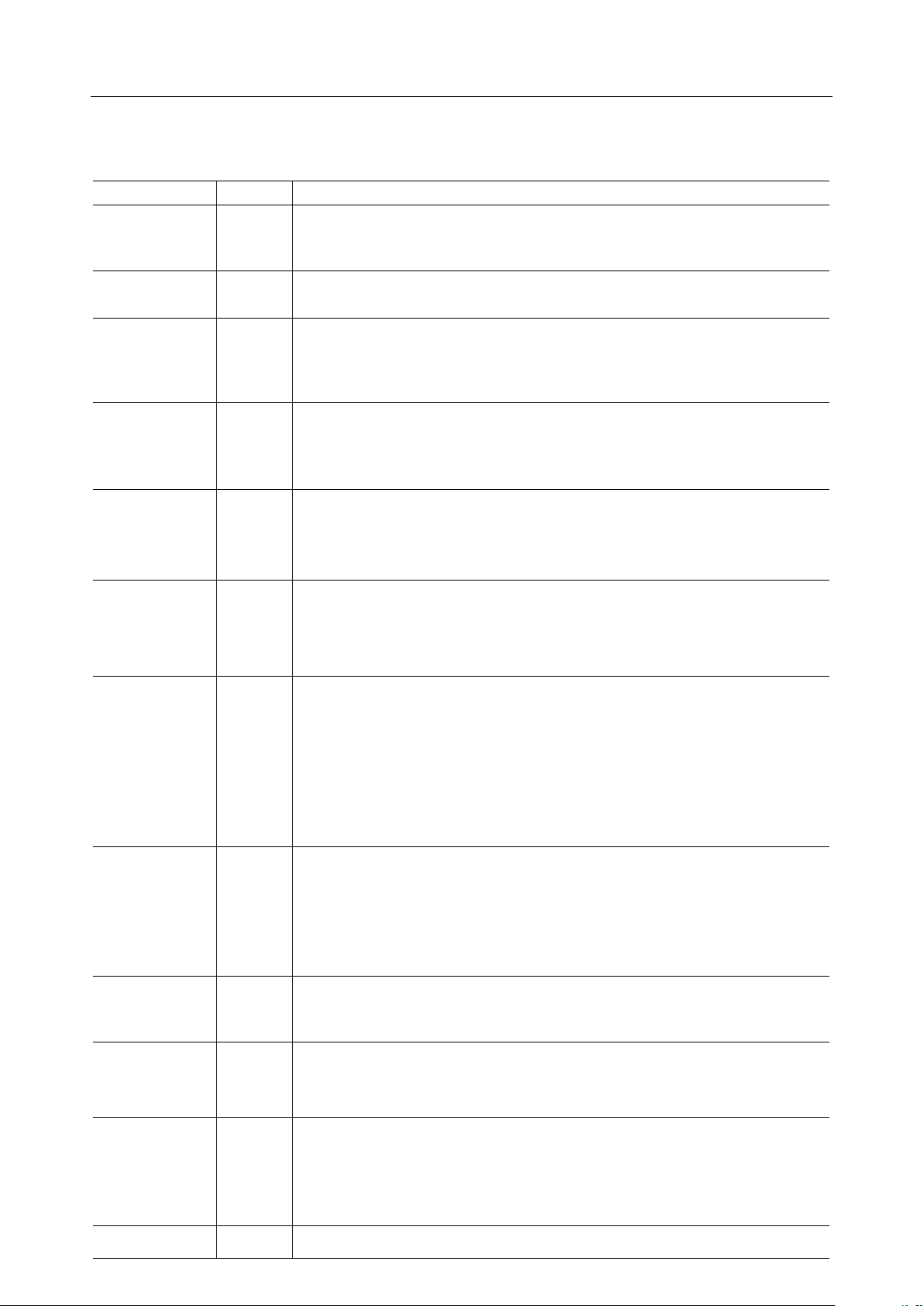

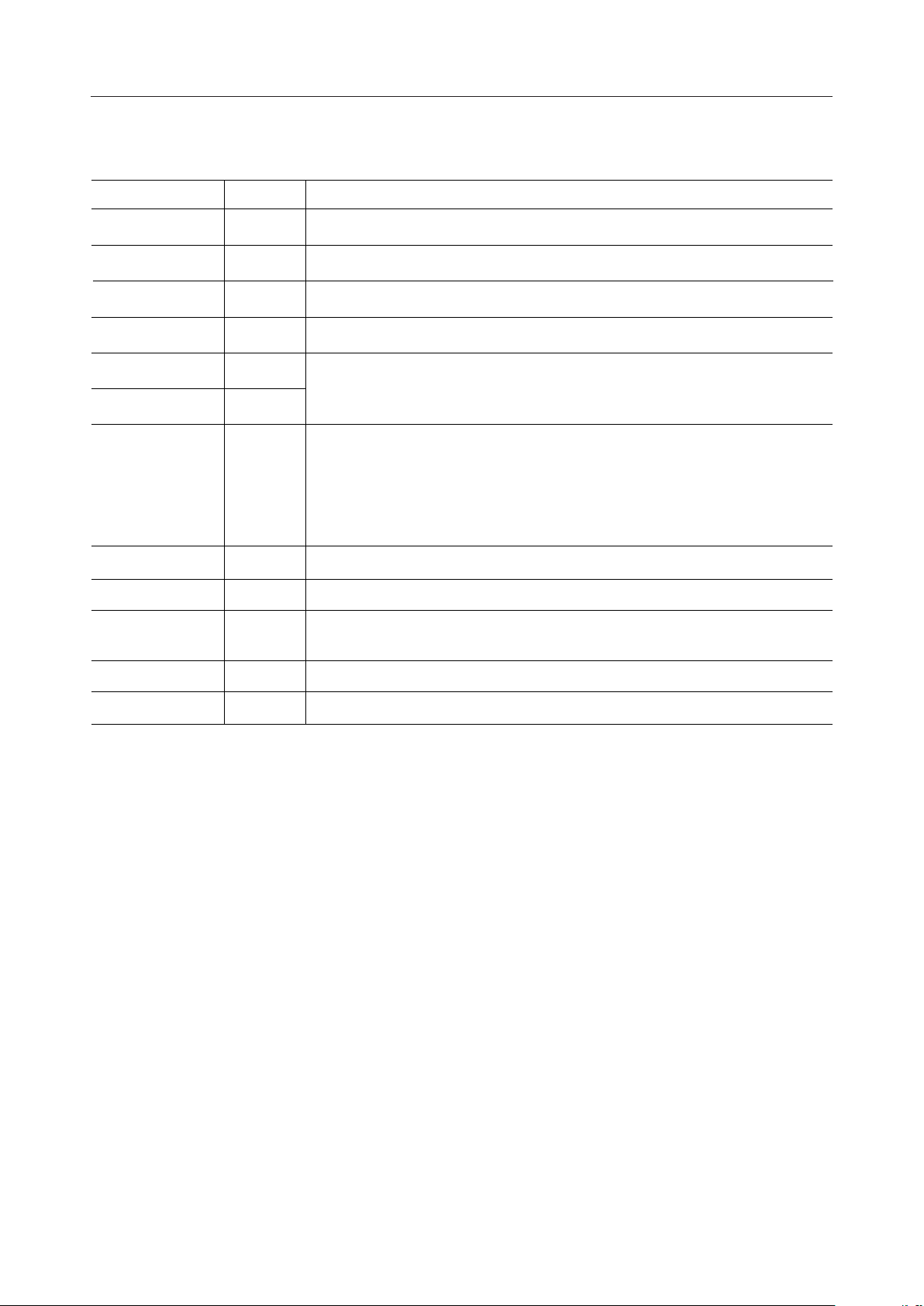

PIN DESCRIPTION

Symbol Type Description

P0_0-P0_7/

AD0-AD7

P1_0-P1_7/

A8-A15

P2_0-P2_5/

RTO4-RTO9

P2_6/FTM10

P2_7

P3_0-P3_3/

FTM11A-FTM11D

P3_4-P3_7/

CAP0-CAP3

P4_0/ETMCK

P4_1/ECTCK

P4_2-P4_7/

TRNS0-TRNS5

P5_0-P5_3

P5_4/PSEN

P5_5/ALE

I/O

I/O

I/O

I/O

I/O

I/O

P0: 8-bit input-output port. Each bit can be assigned to be an input or an output.

AD: When an external memory is used, these pins output the lower 8 bits of the address.

These pins also input or output the data.

P1: 8-bit input-output port. Each bit can be assigned to input or output.

A: When an external memory is used, these pins output the upper 8 bits of the address.

P2: 8-bit input-output port. Each bit can be assigned to input or output.

RTO: Output pin for real time output

FTM10: Capture input pin or real-time output pin

P3: 8-bit input-output port. Each bit can be assigned to input or output.

FTM11A: Capture input pin or real-time output pin

FTM11B-D: 4-port real-time output pin

CAP : Capture input pin

P4: 8-bit input-output port. Each bit can be assigned to input or output.

ETMCK: External clock input pin of 8-bit general timer

ECTCK: External clock input pin of 8-bit event counter

TRNS: Transition detector input pin

P5: 6-bit input-output port. Each bit can be assigned to input or output.

PSEN: Strobe pulse output pin to fetch to external program memory

ALE: Timing pulse output pin to latch the lower 8 bits of the address output from port 0

when the CPU accesses the external memory

P6_0/INT0

P6_1/INT1

P6_2/RXD1

P6_3/TXD1

P6_4/RXC1

P6_5/TXC1

P6_6/RXD0

P6_7/TXD0

P7_0/WR

P7_1/RD

P7_2/WAIT

P7_3/CLKOUT

P7_4-P7_7/

PWM0-PWM3

P8_0-P8_3/

PWM4-PWM7

P8_4-P8_7

P9_0/A16

P9_1-P9_7

P10_0-P10_1/

RTO12-RTO13

P10_2-P10_5/

FTM14-FTM17

P10_6-P10_7

I/O

I/O

I/O

I/O

I/O

P6: 8-bit input-output port. Each bit can be assigned to input or output.

INT0, 1: External interrupt request input pin

RXD1 : SCI1 Receiver data input pin

TXD1 : SCI1 Transmitter data output pin

RXC1 : SCI1 Receiver circuit clock pin

TXC1 : SCI1 Transmitter circuit clock pin

RXD0 : SCI0 Receiver data input pin

TXD0 : SCI0 Transmitter data output pin

P7: 8-bit input-output port. Each bit can be assigned to input or output.

WR: Write strobe output pin for external data memory

RD: Read strobe output pin for external data memory

WAIT: CPU wait request input pin when accessing external data memory

CLKOUT: Output pin to output clock pulse specified by PRPHF

PWM: PWM output pin

P8: 8-bit input-output port. Each bit can be assigned to input or output.

PWM: PWM output pin

P9: 8-bit input-output port. Each bit can be assigned to input or output.

A16: When an external program memory is used, this pin outputs the MSB of the

address.

P10: 8-bit input-output port. Each bit can be assigned to input or output.

RTO: Output pin for real time output.

FTM: Capture input pin or real-time output pin

P11_0-P11_7

I/O

P11: 8-bit input-output port. Each bit can be assigned to input or output.

5/27

¡ Semiconductor MSM66589/66P589/66Q589

PIN DESCRIPTION (Continued)

Symbol Type Description

AI0-AI15 Analog signal input pin for A/D converter

AV

DD

V

REF

AGND GND input pin for A/D converter

OSC0

I

I

I

Power supply input pin for A/D converter

Reference voltage input pin for A/D converter

I

I

Basic clock oscillation pin

OSC1

O

When P0, P1, P2, P7_4-P7_7, and P8-P11 are in an output state and OE pin is "H"

level, P0, P1, P2, P7_4-P7_7, and P8-P11 go to a high-impedance state.

OE

I

When P0, P1, P2, P7_4-P7_7, and P8-P11 are in an output state and OE pin is "L"

level, P0, P1, P2, P7_4-P7_7, and P8-P11 output "H" or "L" level.

However, when P0, P1, P2, P7_4-P7_7, and P8-P11 are in an input state, these

ports are not under the influence of OE pin.

NMI Nonmaskable interrupt request input pin

RES Low-active RESET input pin

I

I

Normally set to "H" level. If set to "L" level, the program memory goes into

I

I

external access mode and accesses external program memory

Power supply pin

V

EA

DD

GND Ground pin

I

6/27

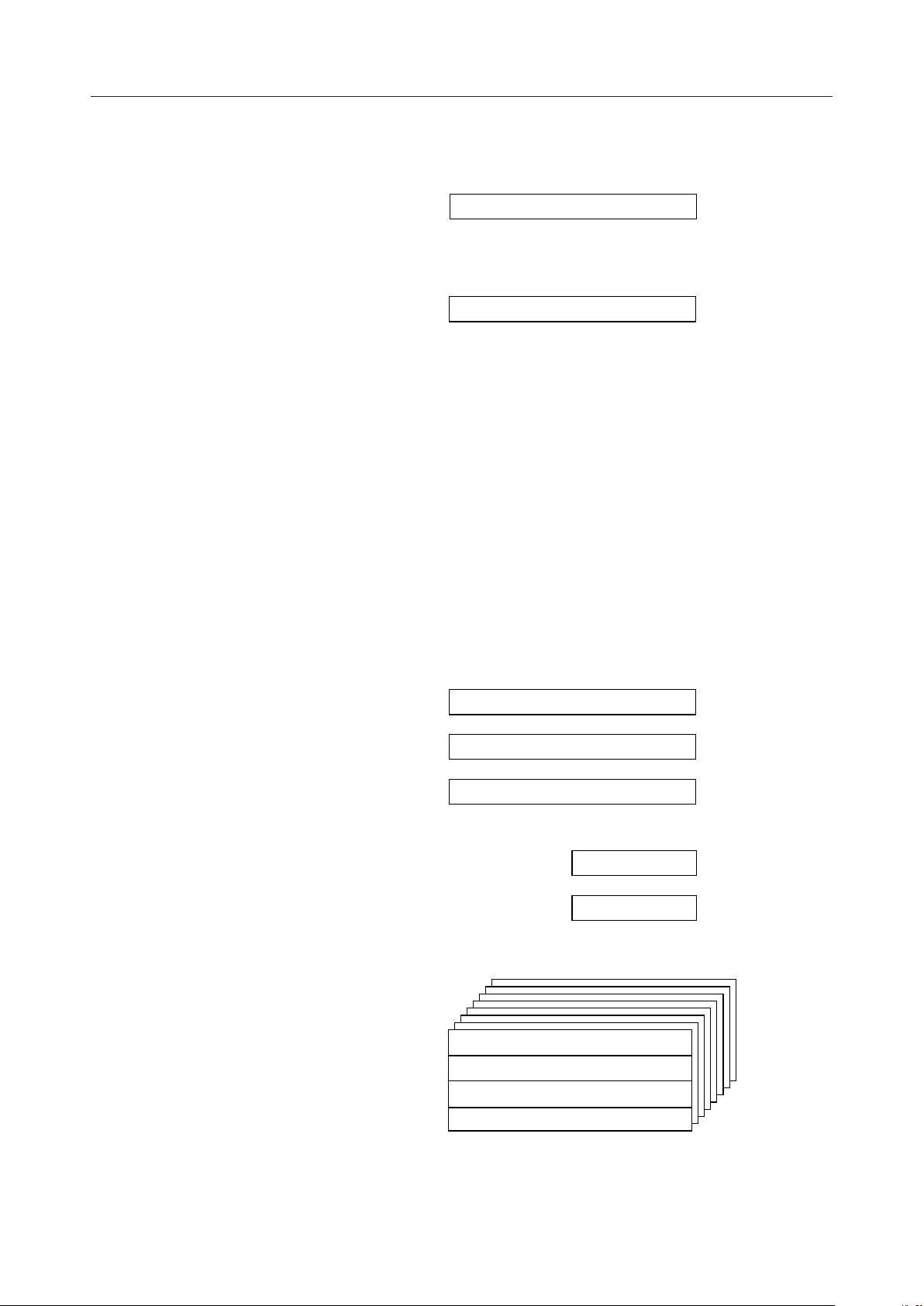

¡ Semiconductor MSM66589/66P589/66Q589

CSR

TSR

70

REGISTERS

Accumulator

Control Register (CR)

Program Status Word

15 0

ACC

15 0

PSW

Bit 15 : Carry flag (CY)

Bit 14 : Zero flag (ZF)

Bit 13 : Half carry flag (HC)

Bit 12 : Data descriptor (DD)

Bit 11 : Sign flag (S)

Bit 10 : Master interrupt priority flag (MIP)

Bit 9 : Overflow flag (OV)

Bit 8 : Master interrupt enable flag (MIE)

Bit 7 : Multiply and accumulate operation bank flag (MAB)*

Bit 6 : User flag (F1)

Bit 5 : Bank common base (BCB1)*

Bit 4 : Bank common base (BCB0)*

Bit 3 : User flag (F0)

Bit 2-0 : System control base 2-0 (SCB2-0)

* Bit 7 (MAB), Bit 5 (BCB1), and Bit 4 (BCB0) can be used

as the User flag.

Program Counter

Local Register Base

System Stack Pointer

Segment Register

Code Segment Register

Table Segment Register

Pointing Register (PR)

Index Register 1

Index Register 2

Data pointer

User Stack Pointer

15 0

PC

LRB

SSP

15 0

X1

X2

DP

USP

7/27

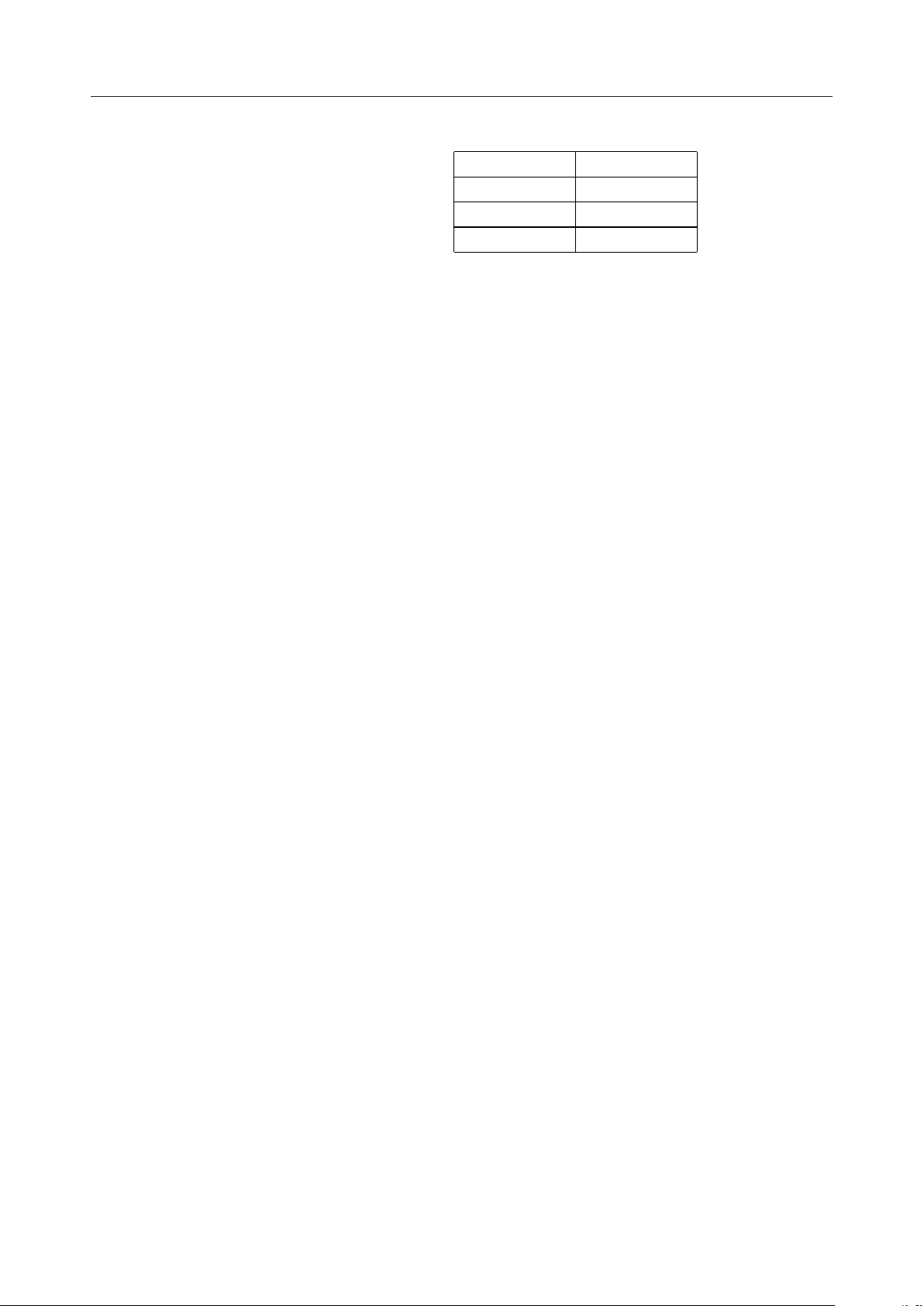

¡ Semiconductor MSM66589/66P589/66Q589

Local Register

7070

ER0

ER1

ER2

ER3

R1

R3

R5

R7

R0

R2

R4

R6

8/27

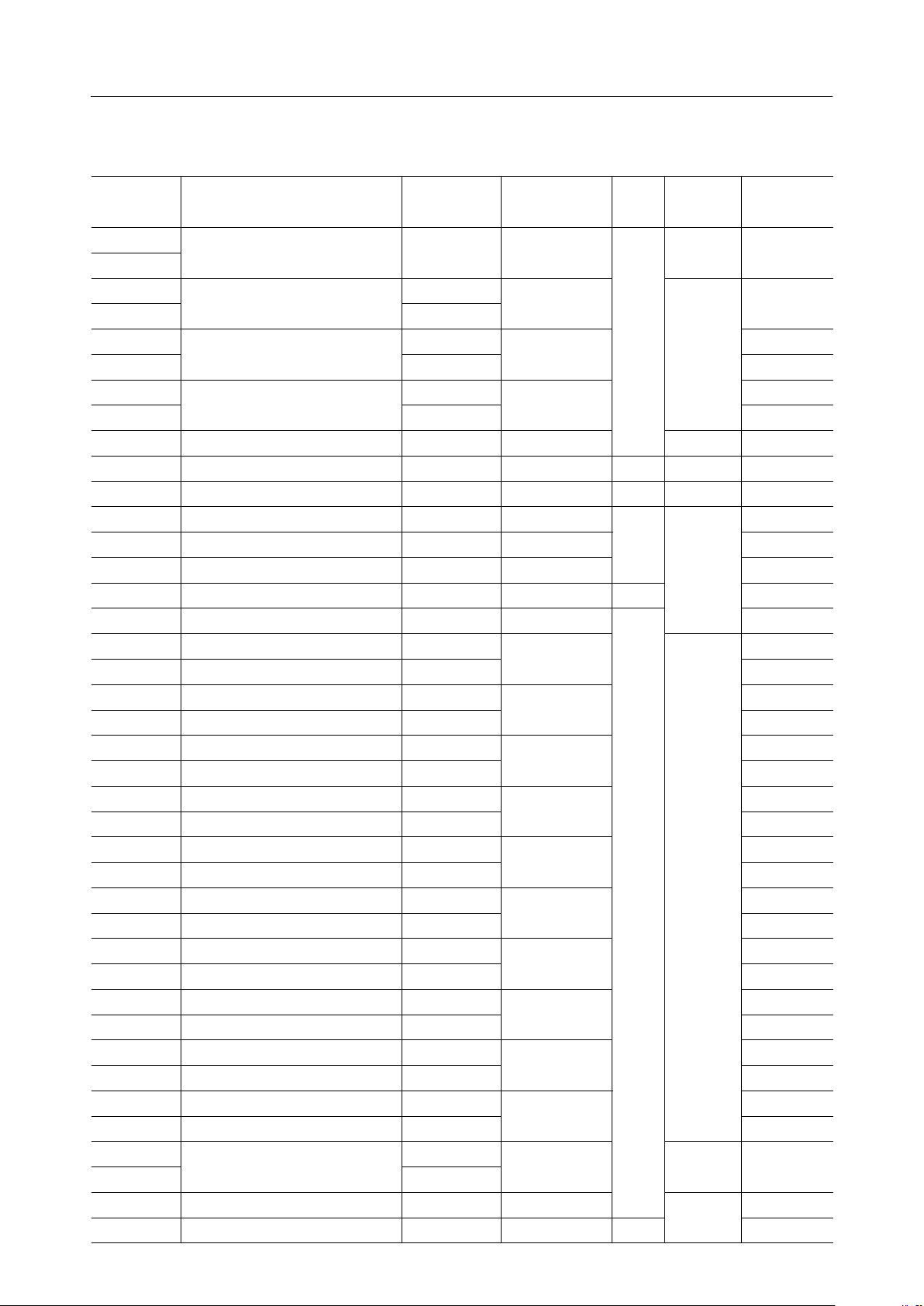

¡ Semiconductor MSM66589/66P589/66Q589

SFR

Address [H] Name

0000

0001

0002

0003

0004

0005

0006

0007

0008✩

0009

000A

000B

000C✩

000D✩

000E

000F✩

0010

0011

0012

0013

0014

0015✩

0016

0017

0018

0019

001A

001B

001C

001D✩

001E

001F

0020

0021

0022

0023

0024

0025✩

0026✩

0027

✩ mark in the address column indicates that there is a nonexistent bit in its register.

System Stack Pointer

Local Register Base

Program Status Word

Accumulator

Table Segment Register

ROM Window Register

ROM Ready Control Register

RAM Ready Control Register

Stop Code Acceptor

Standby Control Register

Port 0 Data Register

Port 1 Data Register

Port 2 Data Register

Port 3 Data Register

Port 4 Data Register

Port 5 Data Register

Port 6 Data Register

Port 7 Data Register

Port 0 Mode Register

Port 1 Mode Register

Port 2 Mode Register

Port 3 Mode Register

Port 4 Mode Register

Port 5 Mode Register

Port 6 Mode Register

Port 7 Mode Register

Port 8 Data Register

Port 9 Data Register

Port 10 Data Register

Port 11 Data Register

TRNS Control Register

Transition Detector

Watchdog Timer

Abbreviated

Name (BYTE)

—

LRBL

LRBH

PSWL

PSWH

ACCL

ACCH

TSR

ROMWIN

ROMRDY

RAMRDY

STPACP

SBYCON

P0

P1

P2

P3

P4

P5

P6

P7

P0IO

P1IO

P2IO

P3IO

P4IO

P5IO

P6IO

P7IO

P8

P9

P10

P11

—

—

TRNSIT

WDT

Abbreviated

Name (WORD)

SSP

LRB

PSW

ACC

—

—

—

—

—

—

P0P1

P2P3

P4P5

P6P7

P0P1IO

P2P3IO

P4P5IO

P6P7IO

P8P9

P10P11

TRNSCON

—

—

R/W

R/W

R/W

W

R/W

W

8/16

Operation

16

8/16

8

8

8/16

16

8

Reset

Status

FFFF

Undefined

00

00

00

00

00

00

FF

FF

"0"

C8

00

00

00

00

00

C0

00

00

00

00

00

00

00

C0

00

00

00

00

00

00

F000

C0

Stop

9/27

Loading...

Loading...