OKI MSM5116400B-70TS-K, MSM5116400B-60TS-K, MSM5116400B-50TS-L, MSM5116400B-70TS-L, MSM5116400B-60TS-L Datasheet

...

¡ Semiconductor MSM5116400B

¡ Semiconductor

E2G0033-17-41

MSM5116400B

4,194,304-Word ¥ 4-Bit DYNAMIC RAM : FAST PAGE MODE TYPE

DESCRIPTION

The MSM5116400B is a 4,194,304-word ¥ 4-bit dynamic RAM fabricated in Oki's silicon-gate CMOS

technology. The MSM5116400B achieves high integration, high-speed operation, and low-power

consumption because Oki manufactures the device in a quadruple-layer polysilicon/double-layer

metal CMOS process. The MSM5116400B is available in a 26/24-pin plastic SOJ or 26/24-pin plastic

TSOP.

FEATURES

• 4,194,304-word ¥ 4-bit configuration

• Single 5 V power supply, ±10% tolerance

• Input : TTL compatible, low input capacitance

• Output : TTL compatible, 3-state

• Refresh : 4096 cycles/64 ms

• Fast page mode, read modify write capability

• CAS before RAS refresh, hidden refresh, RAS-only refresh capability

• Multi-bit test mode capability

• Package options:

26/24-pin 300 mil plastic SOJ (SOJ26/24-P-300-1.27) (Product : MSM5116400B-xxSJ)

26/24-pin 300 mil plastic TSOP

(TSOPII26/24-P-300-1.27-K)

(TSOPII26/24-P-300-1.27-L)

(Product : MSM5116400B-xxTS-K)

(Product : MSM5116400B-xxTS-L)

xx indicates speed rank.

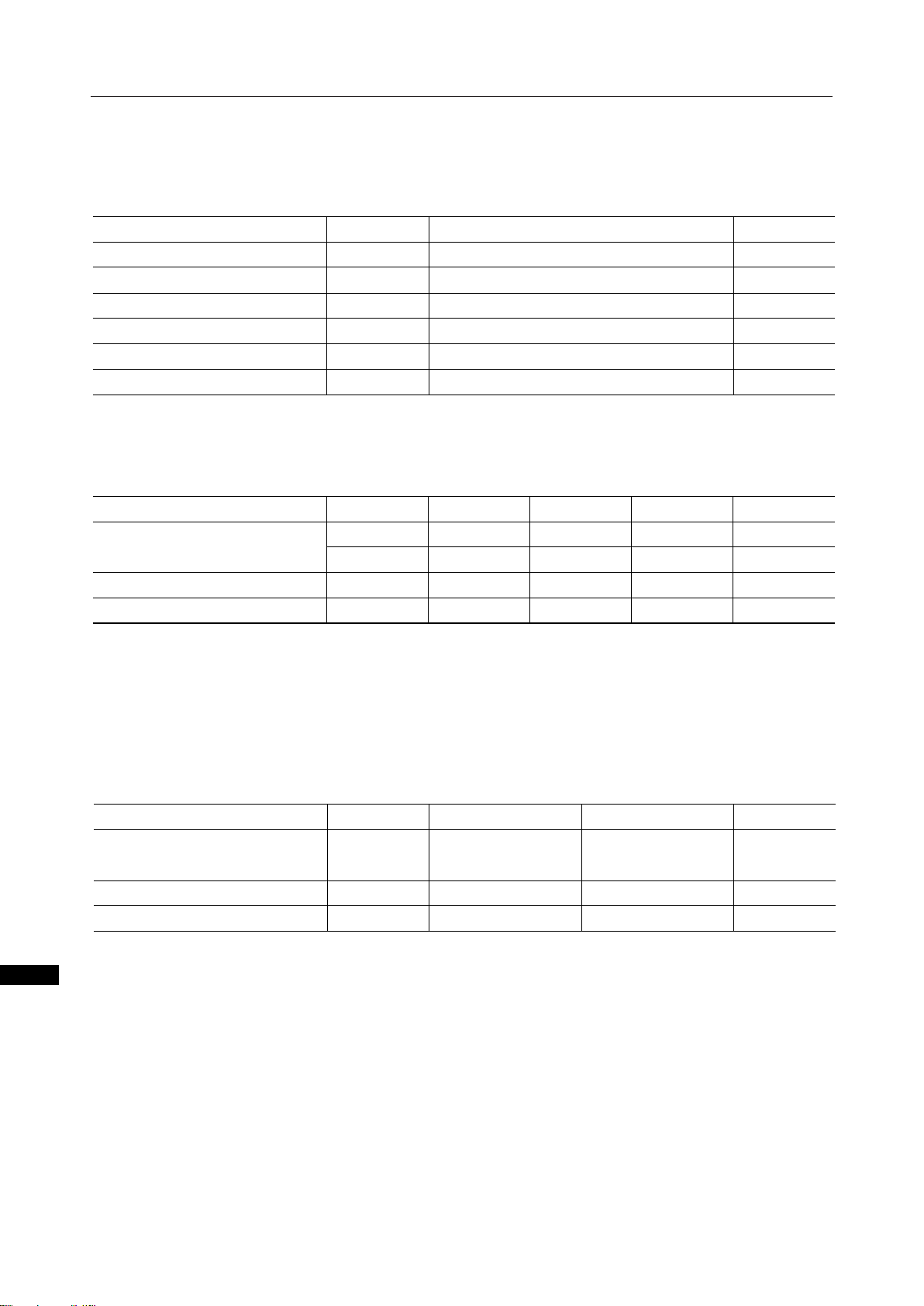

PRODUCT FAMILY

Family

MSM5116400B-50

MSM5116400B-60

MSM5116400B-70

Access Time (Max.)

t

RAC

50 ns

60 ns

70 ns

t

t

AA

CAC

25 ns

30 ns 15 ns 15 ns

35 ns

13 ns

20 ns

t

OEA

13 ns

20 ns

Cycle Time

(Min.)

90 ns

110 ns 495 mW

130 ns

Operating (Max.)

Power Dissipation

Standby (Max.)

550 mW

5.5 mW

440 mW

16M

207

MSM5116400B ¡ Semiconductor

PIN CONFIGURATION (TOP VIEW)

V

1

CC

2DQ1 25 DQ4

3

DQ2

WE CAS WE CAS CAS WE

4

5

RAS OE RAS OE OE RAS

6A11R 21 A9 21 21 6

8A10R 19 A8 19 19 8

9

A0

10

A1

11

A2

12

A3

13

V

CC

26/24-Pin Plastic SOJ 26/24-Pin Plastic TSOP

26 V

24

23

22

18

17

16

15

14

SS

DQ3

A7

A6

A5

A4

V

SS

V

CC

DQ1

DQ2

A11R

A10R

A0

A1

A2

A3

V

CC

10

11

12

13

1

2

3

4

5

6

8

9

26

25

24

23

22

18

17

16

15

14

V

SS

DQ4

DQ3

A9

A8

A7

A6

A5

A4

V

SS

V

SS

DQ4

DQ3

A9

A8

A7

A6

A5

A4

V

SS

26

25

24

23

22

18

17

16

15

14

10

11

12

13

1

V

CC

2

DQ1

DQ2

3

4

5

A11R

A10R

A0

9

A1

A2

A3

V

CC

26/24-Pin Plastic TSOP

(K Type)

(L Type)

16M

Pin Name Function

A0 - A9,

Address Input

A10R, A11R

RAS Row Address Strobe

CAS Column Address Strobe

DQ1 - DQ4 Data Input/Data Output

OE Output Enable

WE Write Enable

V

CC

V

SS

Power Supply (5 V)

Ground (0 V)

Note : The same power supply voltage must be provided to every VCC pin, and the same GND

voltage level must be provided to every VSS pin.

208

¡ Semiconductor MSM5116400B

BLOCK DIAGRAM

A0 - A9

A10R, A11R

V

CC

10

2

RAS

CAS

Address

Address

Counter

Address

Column

Buffers

Internal

Row

Buffers

Timing

Generator

Control Clock

Row

12

De-

coders

Refresh

Drivers

Word

1010

Column

Decoders

Sense

Amplifiers

Memory

Cells

Timing

Generator

Write

Clock

Generator

I/O

4

Selector

WE

OE

Output

4

Buffers

4

Input

4

Buffers

4

4

4

DQ1 - DQ4

On Chip

V

Generator

BB

On Chip

IV

Generator

CC

V

SS

16M

209

MSM5116400B ¡ Semiconductor

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

Parameter

Voltage on Any Pin Relative to V

Voltage on VCC Supply Relative to V

SS

Short Circuit Output Current

Power Dissipation

Operating Temperature

Storage Temperature

SS

Symbol

, V

V

IN

OUT

V

CC

I

OS

P

*

D

T

opr

T

stg

Rating

–0.5 to VCC + 0.5

–0.5 to 7 V

50

1

0 to 70

–55 to 150

Unit

V

mA

W

°C

°C

*: Ta = 25°C

Recommended Operating Conditions

(Ta = 0°C to 70°C)

Power Supply Voltage

Input High Voltage

Input Low Voltage

Symbol

V

CC

V

SS

V

IH

V

IL

Min.

4.5

0

2.4

–0.5

*2

Typ.Parameter

5.0

0

—

—

V

Max.

5.5

+ 0.5

CC

0.8

Unit

V

0

*1

V

V

V

Notes : *1. The input voltage is VCC + 2.0 V when the pulse width is less than 20 ns (the pulse width

is with respect to the point at which VCC is applied).

*2. The input voltage is VSS – 2.0 V when the pulse width is less than 20 ns (the pulse width

is with respect to the point at which VSS is applied).

16M

Capacitance

Parameter

Input Capacitance

(A0 - A9, A10R, A11R)

Input Capacitance (RAS, CAS, WE, OE)

Output Capacitance (DQ1 - DQ4)

Symbol

C

IN1

C

IN2

C

I/O

Typ.

—

—

—

= 5 V ±10%, Ta = 25°C, f = 1 MHz)

(V

CC

Max.

5

7

7

Unit

pF

pF

pF

210

¡ Semiconductor MSM5116400B

DC Characteristics

Parameter Condition

Output Leakage Current

Average Power

Supply Current

(Operating)

Power Supply

Current (Standby)

Power Supply

Current (Standby)

Average Power

Supply Current

(CAS before RAS Refresh)

Symbol

V

OH

V

OL

I

LI

I

LO

I

CC1

I

CC2

I

CC3

I

CC5

I

CC6

I

CC7

IOH = –5.0 mAOutput High Voltage

I

0 V £ V

All other pins notInput Leakage Current

under test = 0 V

DQ disable

0 V £ V

RAS, CAS cycling,

t

RAS, CAS = V

RAS, CAS

≥ VCC –0.2 V

RAS cycling,Average Power

CAS = V

t

RAS = V

CAS = V

DQ = enable

RAS cycling,

CAS before RAS

RAS = VIL,Average Power

CAS cycling,Supply Current

t

= 4.2 mAOutput Low Voltage

OL

= Min.

RC

= Min.(RAS-only Refresh)

RC

= Min.(Fast Page Mode)

PC

£ 6.5 V;

I

£ 5.5 V

O

,Supply Current

IH

,

IH

,

IL

MSM5116400

IH

Min.

2.4

0

–10

–10

—

—

—

—

—

—

—

B-50

Max.

V

CC

0.4

10

10

100

2

1

100

5

100

90

(VCC = 5 V ±10%, Ta = 0°C to 70°C)

MSM5116400

B-60

Min.

–10

–10

2.4

0

—

—

—

—

—

—

—

Max.

V

CC

0.4

10

10

90

2

1

90

5

90

80

MSM5116400

B-70

Min.

2.4

0

–10

–10

—

—

—

—

—

—

—

Max.

V

CC

0.4

10

10

80

2

1

80

5

80

70

Unit

V

V

mA

mA

mA

mA

mA

mA

mA

mA

Note

1, 2

1

1, 2

1

1, 2

1, 3

Notes : 1. ICC Max. is specified as ICC for output open condition.

2. The address can be changed once or less while RAS = VIL.

3. The address can be changed once or less while CAS = VIH.

16M

211

MSM5116400B ¡ Semiconductor

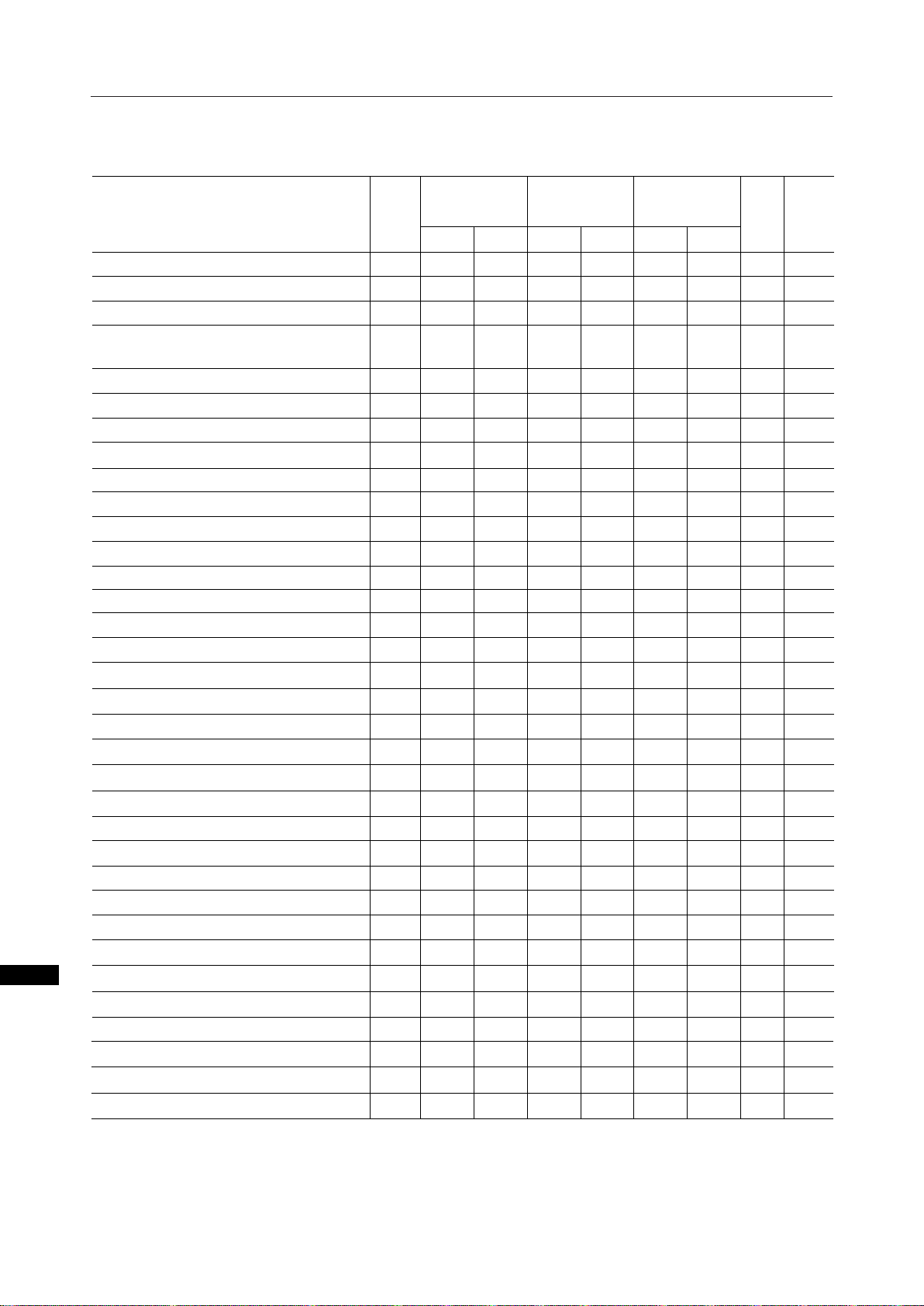

AC Characteristics (1/2)

(VCC = 5 V ±10%, Ta = 0°C to 70°C) Note 1, 2, 3, 11, 12

16M

Parameter

Symbol

Random Read or Write Cycle Time

Read Modify Write Cycle Time

Fast Page Mode Cycle Time

Fast Page Mode Read Modify Write

Cycle Time

Access Time from RAS

Access Time from CAS

Access Time from Column Address

Access Time from CAS Precharge

Access Time from OE

Output Low Impedance Time from CAS t

CAS to Data Output Buffer Turn-off Delay Time

OE to Data Output Buffer Turn-off Delay Time

Transition Time

Refresh Period

RAS Precharge Time

RAS Pulse Width

RAS Pulse Width (Fast Page Mode)

RAS Hold Time

RAS Hold Time referenced to OE

CAS Precharge Time (Fast Page Mode) t

CAS Pulse Width

CAS Hold Time

CAS to RAS Precharge Time

RAS Hold Time from CAS Precharge

RAS to CAS Delay Time

RAS to Column Address Delay Time

Row Address Set-up Time

Row Address Hold Time

Column Address Set-up Time

Column Address Hold Time

Column Address to RAS Lead Time

Read Command Set-up Time

Read Command Hold Time

Read Command Hold Time referenced to RAS

t

RC

t

RWC

t

PC

t

PRWC

t

RAC

t

CAC

t

AA

t

CPA

t

OEA

CLZ

t

OFF

t

OEZ

t

t

REF

t

RP

t

RAS

t

RASP

t

RSH

t

ROH

CP

t

CAS

t

CSH

t

CRP

t

RHCP

t

RCD

t

RAD

t

ASR

t

RAH

t

ASC

t

CAH

t

RAL

t

RCS

t

RCH

t

RRH

MSM5116400

Min.

90

131

35

76

—

—

—

—

—

0

0

0

T

3

—

30

50

50

13

13

7

13

50

5

30

17

12

0

7

0

7

25

0

0

0

B-50

10,000

100,000

10,000

Max.

—

—

—

—

50

13

25

30

13

—

13

13

50

64

—

—

—

—

—

—

—

37

25

—

—

—

—

—

—

—

—

MSM5116400

B-60

Min.

110

155

40

85

—

—

—

—

—

—

40

60

60

15

15

10

15

60

Max.

—

—

—

—

60

15

30

35

15

0

0

0

3

—

15

15

50

64

—

10,000

100,000

—

—

—

10,000

—

5

—

35 —

20

15

0

10

0

15

30

0

0

0

45

30

—

—

—

—

—

—

—

—

MSM5116400

B-70

Min.

130

185

100

45

—

—

—

—

—

—

50

70

70

20

20

10

20

70

40

20

15

10

15

35

Max.

—

—

—

—

70

20

35

40

20

0

0

0

3

—

20

20

50

64

—

10,000

100,000

—

—

—

10,000

—

5

—

—

50

35

0

—

—

0

—

—

—

0

0

0

—

—

—

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ms

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Note

4, 5, 6

4, 5

4, 6

4

4

4

7

7

3

5

6

8

8

212

¡ Semiconductor MSM5116400B

AC Characteristics (2/2)

(VCC = 5 V ±10%, Ta = 0°C to 70°C) Note 1, 2, 3, 11, 12

Parameter

Write Command Set-up Time

Write Command Hold Time

Write Command Pulse Width

OE Command Hold Time

Write Command to RAS Lead Time

Write Command to CAS Lead Time

Data-in Set-up Time

Data-in Hold Time

OE to Data-in Delay Time

CAS to WE Delay Time

Column Address to WE Delay Time

RAS to WE Delay Time

CAS Precharge WE Delay Time

CAS Active Delay Time from RAS Precharge

RAS to CAS Set-up Time (CAS before RAS)

RAS to CAS Hold Time (CAS before RAS)

WE to RAS Precharge Time (CAS before RAS)

WE Hold Time from RAS (CAS before RAS)

RAS to WE Set-up Time (Test Mode)

RAS to WE Hold Time (Test Mode)

Symbol

t

WCS

t

WCH

t

WP

t

OEH

t

RWL

t

CWL

t

DS

t

DH

t

OED

t

CWD

t

AWD

t

RWD

t

CPWD

t

RPC

t

CSR

t

CHR

t

WRP

t

WRH

t

WTS

t

WTH

MSM5116400

B-50

Min.

Max. Min.

0

7

7

13

13

13

0

7

13

36

48

73

53

5

10

10

10

10

10

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

MSM5116400

B-60

Min.

Max.

0

10

10

15

15

15

0

10

15

40

55

85

60

5

10

10

10

10

10

10 ns10 10

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

MSM5116400

B-70

Max.

0

15

10

20

20

20

0

15

20

50

65

100

70

5

10

10

10

10

10

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Note

9

10

10

9

9

9

9

213

16M

MSM5116400B ¡ Semiconductor

Notes: 1. A start-up delay of 200 µs is required after power-up, followed by a minimum of eight

initialization cycles (RAS-only refresh or CAS before RAS refresh) before proper device

operation is achieved.

2. The AC characteristics assume tT = 5 ns.

3. VIH (Min.) and VIL (Max.) are reference levels for measuring input timing signals.

Transition times (tT) are measured between VIH and VIL.

4. This parameter is measured with a load circuit equivalent to 2 TTL loads and 100 pF.

5. Operation within the t

t

(Max.) is specified as a reference point only. If t

RCD

t

(Max.) limit, then the access time is controlled by t

RCD

6. Operation within the t

t

(Max.) is specified as a reference point only. If t

RAD

t

(Max.) limit, then the access time is controlled by tAA.

RAD

7. t

(Max.) and t

OFF

OEZ

(Max.) limit ensures that t

RCD

(Max.) limit ensures that t

RAD

(Max.) can be met.

RAC

is greater than the specified

RCD

.

CAC

(Max.) can be met.

RAC

is greater than the specified

RAD

(Max.) define the time at which the output achieves the open

circuit condition and are not referenced to output voltage levels.

8. t

9. t

RCH

WCS

or t

, t

CWD

must be satisfied for a read cycle.

RRH

, t

RWD

, t

AWD

and t

are not restrictive operating parameters. They are

CPWD

included in the data sheet as electrical characteristics only. If t

WCS

≥ t

(Min.), then

WCS

the cycle is an early write cycle and the data out will remain open circuit (high

impedance) throughout the entire cycle. If t

t

AWD

≥ t

(Min.) and t

AWD

CPWD

≥ t

(Min.), then the cycle is a read modify write

CPWD

CWD

≥ t

CWD

(Min.) , t

RWD

≥ t

RWD

cycle and data out will contain data read from the selected cell; if neither of the above

sets of conditions is satisfied, then the condition of the data out (at access time) is

indeterminate.

(Min.),

16M

10. These parameters are referenced to the CAS leading edge in an early write cycle, and

to the WE leading edge in an OE control write cycle, or a read modify write cycle.

11. The test mode is initiated by performing a WE and CAS before RAS refresh cycle.

This mode is latched and remains in effect until the exit cycle is generated. In a test mode

CA0 and CA1 are not used and each DQ pin now accesses 4-bit locations. Since all 4 DQ

pins are used, a total of 16 data bits can be written in parallel into the memory array.

In a read cycle, if 4 data bits are equal, the DQ pin will indicate a high level. If the 4 data

bits are not equal, the DQ pin will indicate a low level. The test mode is cleared and the

memory device returned to its normal operating state by performing a RAS-only

refresh cycle or a CAS before RAS refresh cycle.

12. In a test mode read cycle, the value of access time parameters is delayed for 5 ns for the

specified value. These parameters should be specified in test mode cycle by adding the

above value to the specified value in this data sheet.

See ADDENDUM F for AC Timing Waveforms

214

Loading...

Loading...