Preliminary

ML696500 Series

ML696500 and ML69Q6500

32-Bit ARM946E™ Based Microcontroller

Description

The Oki ML69Q6500 microcontroller is a system LSI for digital audio players based on the ARM946E™ 32-bit CPU core .

The ML69Q6500 provides a 120-MHz ARM-9E CPU along

with:

• High speed USB 2.0 interface,

• Ultra DMA hard drive controller (ATA),

• NAND Flash controller

• 16-bit audio codec.

It is targeted for portable MP3 players. The ML69Q6500 also

contains 128KB of SRAM, 512KB of embedded Flash ROM as

well as an internal memory controller that can connect to

external ROM, SRAM and SDRAM.

Features

• ARM946E-S CPU

- 8-KB instruction Cache

- 8-KB Data Cache

- JTAG debug function

• Internal Memory

- 128-KB SRAM

- 16-KB Boot ROM

- 512-KB Flash ROM (ML69Q6500 only)

• USB 2.0 High Speed controller

• IDE (ATA) controller

- DMA / Ultra DMA support

• NAND Flash memory controller

- Smart Media 2000 Compliant

- Built in ECC circuit

• Audio DA/AD

- 2 stereo channels

- 16-bit resolution

- Built-in Headphone Amp

• Timers: 16-bit auto-reload x 4

• DMA Controller – 4-Channel

• PWM – 16-bit x 1-Channel

Tyical Applications

• Portable digital-audio players

• MP3 Juke Box

• Digital Audio Encoder/Decodeer

• 16-bit Watchdog T imer

- Interrupt or Reset control

• A/D Converter – Four, 10-bit Channels

2

S T ransceiver

•I

- 16-bit Data

- 32, 44.1 & 48-kHz sample rates

• Real-time Clock (RTC) Generation

• Serial Interfaces:

- SSIO

- UART

2

C

-I

• General Purpose I/O – 88 Programmable pins

• External Memory Controllers:

- ROM

- SRAM

- SDRAM

- Peripheral I/O Banks

• Advanced Power Management

- Clock Gears — 1/2 to 1/32

- Power-down and Halt modes

• Package – 272-pin LFBGA 0.65 mm pitch

January 2005, Rev 1.1b

Data Sheet

Product Selector

Part Number Clock Frequency Built-in Flash ROM Package

ML696500 120 MHz n/a 272-pin LFBGA 0.65 mm pitch

ML69Q6500 120 MHz 512 KB 272-pin LFBGA 0.65 mm pitch

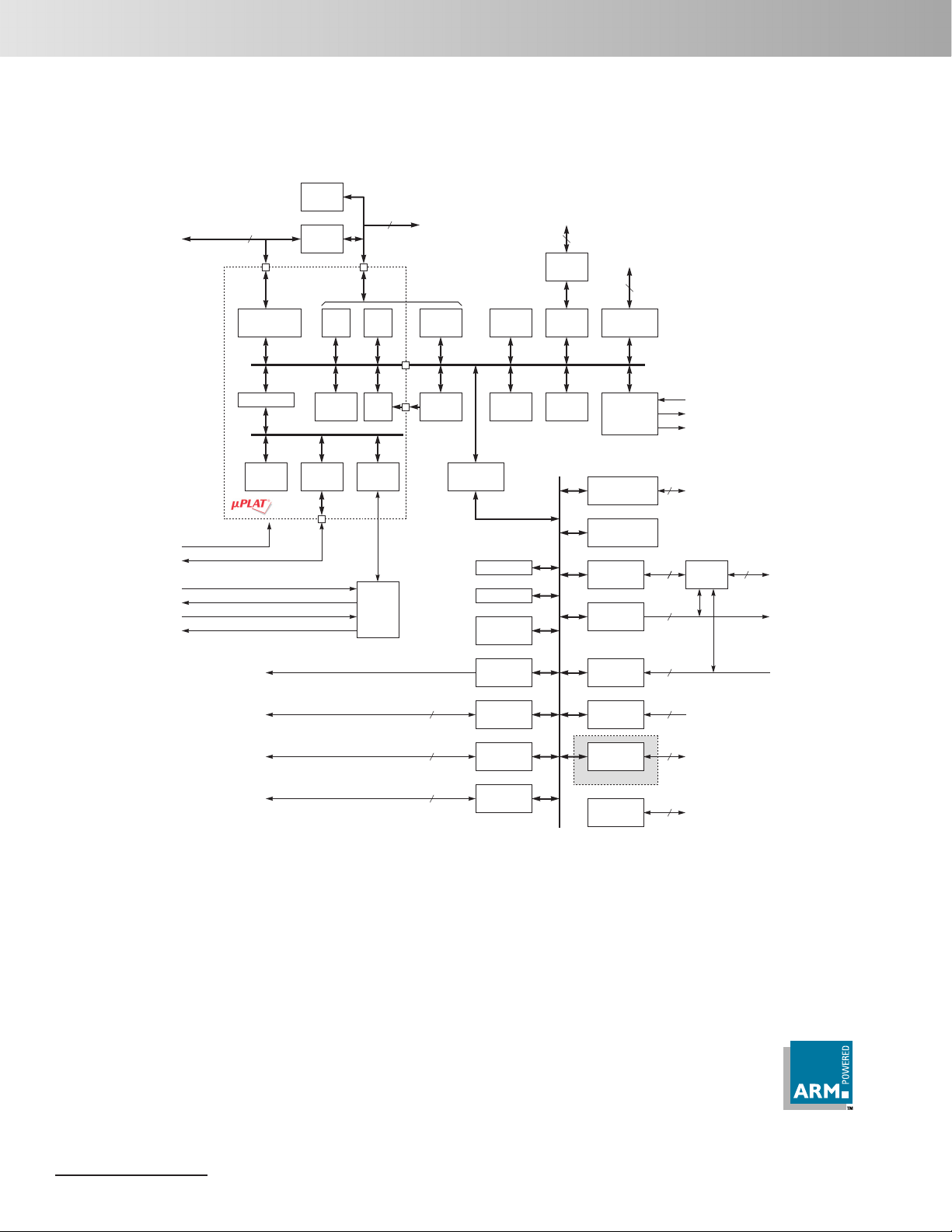

ML696500 and ML69Q6500

Block Diagram

TDI

TDO

nTRST

TMS

TCK

RTCK

RESET_N

TXD

RXD

OSC48M0

OSC48M1B

OSC11M0

OSC11M1B

SIORXD[1:0]

SIOTXD[1:0]

ARM946ES

APB Bridge

PWMOUT

SIOCK[1:0]

*For ML69Q6500 Only

6

AMBA

AHB Bus

AMBA

APB Bus

System

TIMER

MCP

FLASH

JTAG

FLASH

µPLAT946

SIO

TIC

Default

Slave

BIC

IRC

System

Control

CGB

52

XA[23:1]

XD[15:0]

XOE_N

XWE_N

XROMCS_N

XRAMCS_N

XIOCS_N[1:0]

XBS_N[1:0]

XCAS_N

XRAS_N

XSDCLK

XSDCKE

XDQM[1:0]

DRAMC

Exp. IRC

APB Bridge

with wait

6

Default

Slave

WDT

UNIV

TIMER

16 bit x 3ch

PWM

16 bit x 1ch

SSIO

2ch

USB_DP

USB_DM

USB_RPU

USB_REXT

USB_ATEST1

USB_ATEST0

USB_VOREF

6

PHY

HS-USB

AHBROMAHBRAM

APB Bus

29

VDD_CORE

GND_CORE

VDD_PLL

GND_PLL

VDD_IO

GND_IO

VDD_RTC

GND_RTC

AVDD

AGND

AVDD_RX

AGND_RX

AVDD_TX

AGND_TX

AVDD_C

AGND_C

13

3

3 13

4

4

4

IDEA[2:0]

IDED[15:0]

IDERE_N

IDEWE_N

IDERDY

IDERDY_CLK

IDECS_N[1:0]

IDEDREQ

IDEDACK_N

IDEIRQ

IDEDIR_N

IDE

Controller

DMAC

NAND FLASH

Controller

NAND FLASH

Buffer

SSIO

1ch

I2S

Trans

I2S

Receive

A/D AIN[3:0]

DREQ

DREQCLR

TCOUT

FRD_N

FFWR_N

FCLE

FALE

FRB

FD[7:0]

Audio

AD/DA

Preliminary

LLINEOUT

RLINEOUT

LLINEIN

RLINEIN

MICIN

LRADIOIN

RRADIOIN

LOUT

MOUT

ROUT

REFP

REFN

COMM

CKOUTD

SDD

WSD

SCLD

CKOUTA

SDA

WSA

SCLA

SDAT

SCL

PIOA[15:0], PIOB[15:0]

PIOC[15:0], PIOD[15:0]

PIOE[15:0], PIOF[6:0]

2

• Oki Semiconductor January 2005, Rev 1.1b

2

88

I2C

GPIO

RTC

Backup Area

Test Mode

2

12

OSC32K_IN

OSC32K_OUT

Preliminary

Functional Description

• CPU

- 32-bit RISC CPU (ARM946E)

- Built-in 8-KB instruction cache and 8-KB data cache

- Little-endian format

- Maximum operating frequency of 120 MHz

- Instruction structure – Highly dense 32-bit ARM instructions and a subset

16-bit Thumb instructions with high object code efficiency

- 31 General-purpose registers x 32 bits

- Built-in barrel shifter – The oper ations of the ALU and barrel shift can be

executed by one instruction.

- Built-in multiplier (32 bits x 16 bits)

- Built-in debug function (JTAG)

• Internal memory

- Built-in 128-KB SRAM (32 KWords x 32 bits)

- AHB bus connection

- Built-in 16-KB ROM for boot up (4 KWords x 32 bits)

- 512-KB Flash ROM(ML69Q6500 only)

• External memory and I/O controller (16-bit devices)

- ROM (Flash) access function

- SRAM access function

- SDRAM access function – supports distributed CBR

- External I/O interface – two 16-bit banks

• Interrupt controller / extended-interrupt controller

- FIQ: Used for an internal interrupt (IFIQ_N) from the AUDIO module.

- 27 IRQ sources (23 internal sources and 4 external sources)

- Seven interrupt priority levels can be set for each interrupt source

• µPLAT system timer

- 16-bit auto reload timer x 1 channel

• µPLAT-SIO (UART)

- Full-duplex start-stop synchronization method

- Built-in baud-rate generator

• DMA controller

- Four channels

- Fixed mode or round-robin mode priority can be selected

- Cycle-steal mode or burst-mode bus access privilege can be selected

- Software requests and external requests are supported as DMA transfer

requests

- Maximum transfer count is 65,536 (64K)

- Data transfer sizes are 8, 16, or 32 bits

• High speed USB Port

- USB 2.0 standard compliant

- High-speed (480 Mbps)

- Interface to AMBA high-speed bus

• IDE Controller

- ATA66 compliant

- DMA and Ultra DMA are supported.

- Switchable to NAND Flash + GPIO using the IDEMODE pin

• PWM

- PWM x 1 channel (16-bit resolution)

ML696500 and ML69Q6500

• Watchdog timer

- 16-bit timer

- Interval-mode or watchdog-mode can be selected

- An interrupt or a reset can be generated

• Analog-to-digital converter

- 10-bit successive approximation type x 4 channels

- Sample / hold function

- Shortest conversion time is 6.7 µs

2

•I

C Bus Controller

2

-I

C bus standard compliant controller x 1 channel

- Operates only as I

- Communication speed is 100-400 kbps

- Supports 7-bit and 10-bit addressing

• Timer

- 16-bit auto reload timer x 3 channels

- A different clock can be set for each channel.

- One-shot mode or interval mode can be set for each channel.

• Synchronous Serial I/O (SSIO)

- 3 channels of 8-bit clock synchronous serial port

- One-of-3 channels is used to control built-in audio Codec

- Configurable Clock polarity

- Select LSB first or MSB first

- Select Master or Slave mode

• Universal Registers

- Four 8-bit general-purpose internal status/setup registers

• NAND Flash memory controller

- SmartMedia Standard 2000 compliant (512-Bytes/sector)

- Supports SmartMedia of 8 MB to 128 MB

- Built-in ECC circuit

- 512-Byte/2048-Byte auto write/read function

•RTC

- 1-second clock generation function from 32.768 kHz

- Built-in 32-bit 1-second clock counter

- 32-bit compare interrupt function

• GPIO

- Built-in GPIO of 16 pin x 5 channels (GPIOA, GPIOB, GPIOC, GPIOD,

GPIOE) and 8 pin x 1 channel (GPIOF)

- Each port configurable at bit level

- Interrupt inputs can be set at bit level

- GPIOA[15:00], GPIOB[15:00] and GPIOC[15:00] can be set to an external bus by setting the EXTBUS pin

- GPIOD[15:00] can be used to select a secondary function in units of bits.

- GPIOE[15:11] can be used as external interrupts.

- GPIOE[15] is 5-V tolerant input

- GPIOF[06:00] function as IDE data, when the IDE controller mode is set

using the IDEMODE pin.

- GPIOF[7] is used as a control input to the internal audio Codec

2

C bus master device

January 2005, Rev 1.1b

Oki Semiconductor • 3

ML696500 and ML69Q6500

2

•I

S transmission/reception

- Sampling frequencies of 32, 44.1, and 48 kHz, as well as 1/2 and 1/4 of

these frequencies are supported

- System clock is 256 times the sampling rate

- Channel data length is 16 bits

- With or without 1-bit delay, left/right reversible

•

Audio DA/AD circuit

- 16-bit DAC resolution

- Two stereo channels

- Built-in headphone amplifier

- S/N ratio is 90 db (preliminary)

- 16-bit ADC resolution

- Two stereo channels

- Built-in amplifier/ALC

- S/N ratio: 90 db (preliminary)

• Flash

- ML69Q6500: (256-K x 16-bit) Flash ROM is embedded in the MCP

(Multi-chip Package)

- ML696500: Version without Flash ROM

Preliminary

• Clocks

- Can connect a 48-MHz crystal oscillator and input an external clock

directly.

- The RTC section can connect a 32.768-kHz crystal oscillator.

- Can connect an 11.2896-MHz crystal oscillator for audio and input an

external clock directly.

• Power Management

- Power down mode – The power supply can be disabled to all sections,

except for the RTC section.

- Stop mode – Software disables clock supply to the main section including

the processor

- Halt mode – Partially disables clock supply

- Clock gear – Software can dynamically change clock to 1/1, 1/2, 1/4,

1/8, 1/16 or 1/32 of the clock input frequency

- Clock control – Software can stop clock supply for each function

• Package

- 272-pin LFBGA, 0.65 mm ball pitch

4

• Oki Semiconductor January 2005, Rev 1.1b

Preliminary

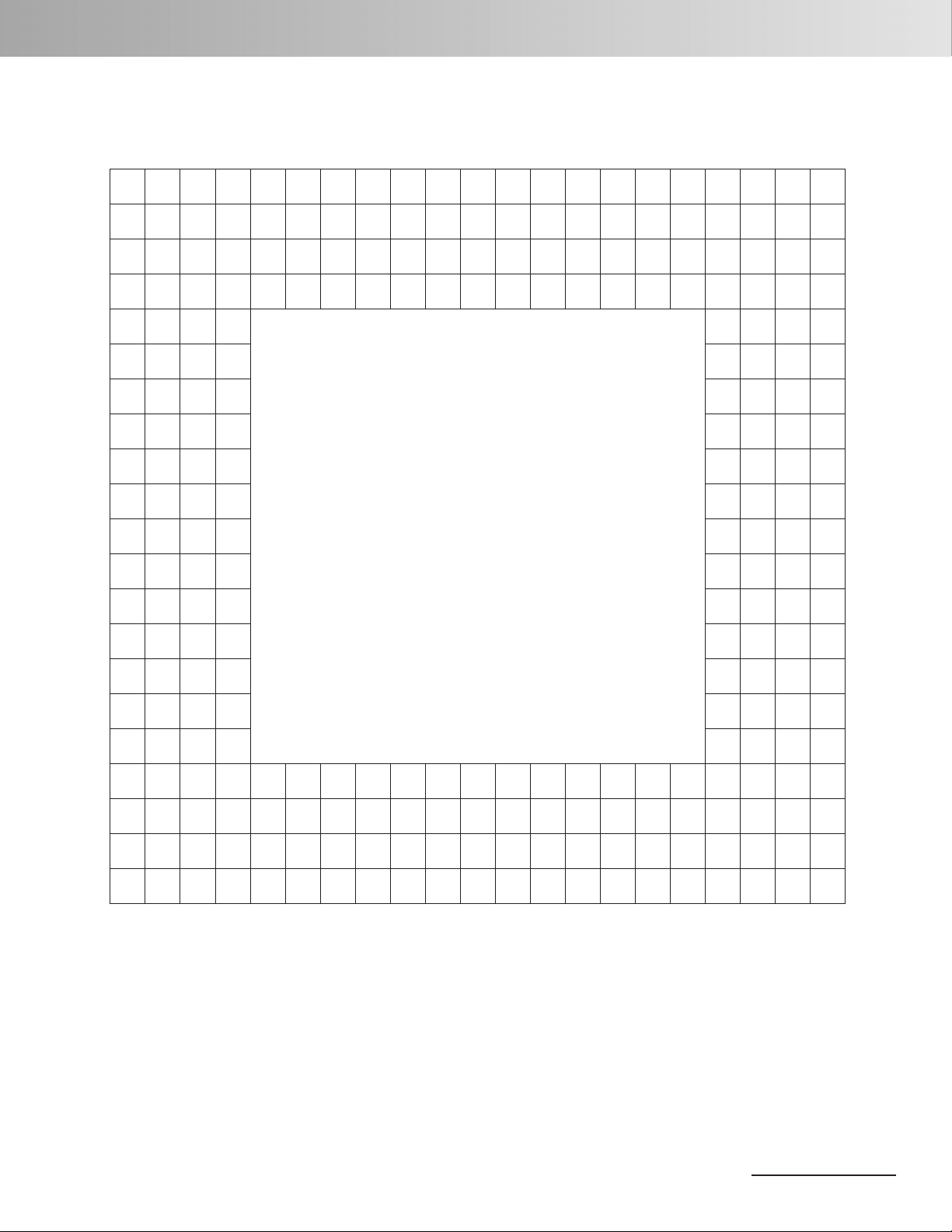

Pin Configuration

RLINEINREFPRRADIOIN

RLINE

VDD_HPLOUT

OUT

ADIN[3]ADIN[2]ROUT

OSC48M1BOSC48M0VDD_PLL

USB_

VOREF

ATEST[0]

OSC11M0VDD_PLLUSB_

MICINLLINEINVDD_ADCLRADIOIN

ADC

CORE

VDD_

CORE

ML696500 and ML69Q6500

2143567810 912 11131415161718192021

PIOD[12]/

PIOD[11]/

VDD_

CODEC

C

CODEC

SCLD

GND_IOVDD_CAPGND_IOGND_

GND_IORESET_NGND_IOCOMREFNVDD_DACLLINEOUT

GND_IOGND_IOGND_IOGND_DA

WSD

VDD_

CORE

VDD_

CORE

CORE

CKOUTD

PIOD[2]/

SDD

VDD_

CORE

SDA

SCLA/SCL

PIOD[5]/

WSA

VDD_IOVDD_IOVDD_

SSIOTXD

[0]

VDD_FLAPIOD[4]/

PIOD[7]/

CKOUTA/

CLKOUT

GND_

CORE

SSIOTXD

[1]

PIOD[9]/

SSIORXD

[0]

PIOD[10]/

SSIOCK[0]

CORE

SSIORXD

[1]

SSIOCK[1]

UP_RXD

UP_TXD

SCLPIOD[13]

SDATPIOD[15]/

VDD_IOVDD_IOGND_

RSV

BYPASS

CORE

PIOD[8]/

PIOD[6]/

PIOD[3]/

PIOD[1]/

PIOD[0]/

GND_

BOOT[1]TMODE[0]TMODE[2]PWMOUTPIOD[14]/

CORE

BOOT[0]EXTBUSTMODE[1]TEST_

CORE

CORE

CORE

VDD_

CORE

GND_IOGND_

nTRSTGND_IOVDD_IOVDD_IOVDD_

RTCKGND_IOAVDDADIN[1]GND_HPMOUT

TCKVDD_IOGND_

TMSVDD_IOVDD_IOVSSFLAAGNDADIN[0]

TDIVDD_

IDED[3]

IDEMODETMODE[3]PLL

IDED[0]

FD[2]/

IDED[2]

FD[6]/

IDED[6]

PIOF[0]/

IDED[8]

PIOF[3]/

IDED[11]

PIOF[5]/

IDED[13]

IDED[15]FD3/

GND_IOGND_IOGND_

TDOGND_IOGND_

VSSFLAFD[0]/

FD[1]/

IDED[1]

FD[4]/

IDED[4]

FD[7]/

IDED[7]

PIOF[2]/

IDED[10]

PIOF[4]/

IDED[12]

PIOF[6]/

IDED[14]

AA

Y

W

V

U

T

R

P

N

REXT

XWAIT

[1]

PIOC[2]/

XBS_N

[0]

PIOC[9]/

XROMCS

_N

XOE_N

GND_IO

AGND_CAVDDRX

XSDCS_NPIOC[1]/

PIOC[4]/

XIOCS_N

[0]

PIOC[10]/

XWE_N

GND_IOPIOC[11]/

PIOB[1]/

XD[1]

ATEST[1]

PIOC[0]/

XWAIT

[0]

PIOC[3]/

XBS_N

[1]

GND_IO

PIOB[0]/

XD[0]

PIOB[3]/

XD[3]

OSC11M1BGND_PLLAVDDCUSB_

XSYSCLKVDD_IOXRAS_NXCAS_N

XSDCLK

VDD_IO

GND_IOVDD_IOGND_IOGND_IO

PIOC[6]/

XIOCS_N

[10]

PIOB[2]/

XD[2]

PIOB[4]/

XD[4]

GND_

CORE

PIOC[5]/

XIOCS_N

[1]

PIOB[7]/

XD[7]

PIOB[6]/

XD[6]

GND_

CORE

PIOC[7]/

XIOCS_N

[11]

PIOB[10]/

XD[10]

PIOB[8]/

XD[8]

CORE

PIOC[8]/

XRAMCS_N

PIOB[12]/

XD[12]

PIOB[11]/

XD[11]

PIOB[5]/

XD[5]

PIOA[0]/

XA[1]

PIOB[14]/

XD[14]

PIOB[9]/

XD[9]

PIOB[15]/

XD[15]

PIOA[2]/

XA[3]

VDD_IOVDD_IOVDD_IOGND_

PIOB[13]/

XD[13]

PIOA[1]/

XA[2]

PIOA[4]/

XA[5]

272-Pin LFBGA

(TOP VIEW)

VDD_

CORE

PIOA[3]/

XA[4]

PIOA[5]/

XA[6]

PIOA[6]/

XA[7]

CORE

PIOA[7]/

XA[8]

PIOA[9]/

XA[10]

PIOA[8]/

XA[9]

PIOA[10]/

XA[11]

PIOA[12]/

XA[13]

PIOA[11]/

XA[12]

VDD_IOVDD_IOGND_

XA[17]

PIOA[15]/

XA[16]

PIOA[13]/

XA[14]

VDD_

CORE

XA[19]

PIOA[14]/

XA[15]

CORE

PIOC[13]/

XA[18]

XA[20]

VDD_IOGND_PLLUSB_

VDD_IOTCOUTDREQCLRAGND_TXUSB_DP

VDD_IOXDQM[1]XSDCKEAGND_RXAVDDTX

GND_

CORE

VDD_

CORE

CORE

GND_

CORE

IDED[5]

PIOF[1]/

IDED[9]

32K_

TESTMODE

VDDRTCVDD_IODREQXDQM[0]AGND_TXUSB_DM

FCLE/

IDECS_N

[0]

IDERST_

N

CORE

RTC_

TESTMODE

NPCBRID

_N

FRB/

IDERDY

FRD_N/

IDERE_N

PIOE[11]PIOE[14]XA[22]PIOC[15]/

2143567810 912 11131415161718192021

GND_RTCOSC32K1BFD[5]/

OSC32K

[0]

IDEIRQIDE

IDEDREQIDEDACK

FALE/

IDECS_N

[1]

FWR_N/

IDEWR_N

IDEA[0]IDEA[2]IDEA[1]VDD_

PIOE[0]PIOE[1]GND_

PIOE[2]PIOE[3]PIOE[5]GND_IOGND_IOVDD_

PIOE[7]PIOE[8]GND_IOPIOE[4]PIOE[6]PIOE[15]XA[21]PIOC[12]/

PIOE[9]GND_IOPIOE[10]PIOE[13]PIOE[12]XA[23]PIOC[14]/

GND_IO

M

L

K

J

H

G

F

E

D

C

B

A

Figure 1. 272-Pin LFBGA

Notes:

1. For pins that have multiple functions, the signals are noted by their primary / secondary functions.

January 2005, Rev 1.1b

Oki Semiconductor • 5

B1

C1

D1

E1

F1

G1

H1

J1

K1

L1

M1

ML696500 and ML69Q6500

Pin Assignment Definitions and Functions

Pin Definitions

Pin Name/Function Description

A/B A = Primary Function / B = Secondary Function

A/- A = Primary Function /

-/B

_N Active-Low Input or Output

No Primary Function

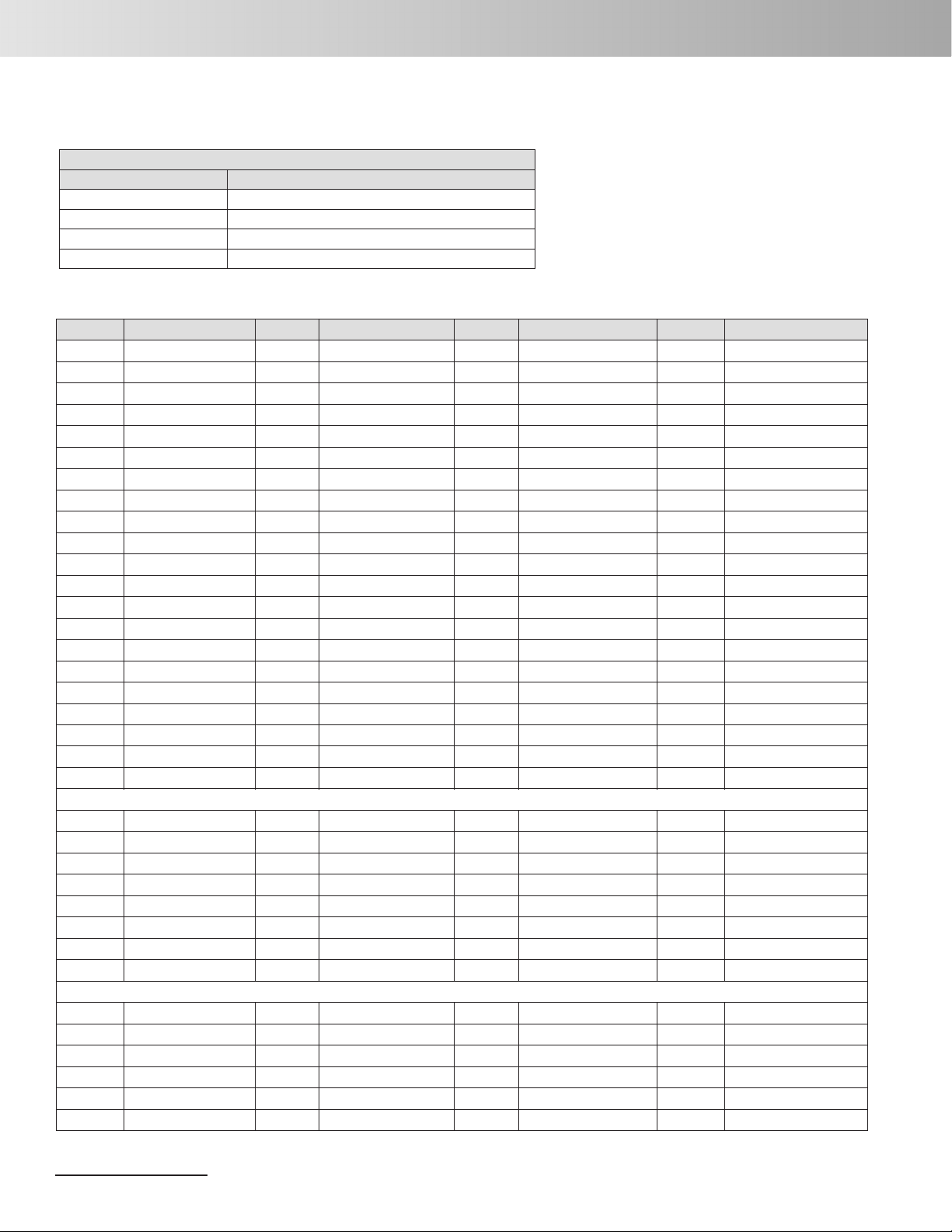

List of Pins

BGA Pin Symbol BGA Pin Symbol BGA Pin Symbol BGA Pin Symbol

A1

A2 PIOE[11]/- B2 GND_IO C2 PIOE[8]/- D2 PIOE[3]/A3 PIOE[14]/- B3 PIOE[10]/- C3 GND_IO D3 PIOE[5]/A4 -/XA[22] B4 PIOE[13]/- C4 PIOE[4]/- D4 GND_IO

A5 PIOC[15]/XA[20] B5 PIOE[12]/- C5 PIOE[6]/- D5 GND_IO

A6 PIOC[13]/XA[18] B6 -/XA[23] C6 PIOE[15]/- D6 VDD_CORE

A7 PIOA[14]/XA[15] B7 PIOC[14]/XA[19] C7 -/XA[21] D7 VDD_CORE

A8 PIOA[13]/XA[14] B8 PIOA[15]/XA[16] C8 PIOC[12]/XA[17] D8 VDD_IO

A9 PIOA[11]/XA[12] B9 PIOA[12]/XA[13] C9 PIOA[10]/XA[11] D9 VDD_IO

A10 PIOA[8]/XA[9] B10 PIOA[9]/XA[10] C10 PIOA[7]/XA[8] D10 GND_CORE

A11 PIOA[6]/XA[7] B11 PIOA[5]/XA[6] C11 PIOA[3]/XA[4] D11 VDD_CORE

A12 PIOA[4]/XA[5] B12 PIOA[1]/XA[2] C12 PIOB[13]/XD[13] D12 VDD_IO

A13 PIOA[2]/XA[3] B13 PIOB[15]/XD[15] C13 PIOB[9]/XD[9] D13 VDD_IO

A14 PIOB[14]/XD[14] B14 PIOA[0]/XA[1] C14 PIOB[5]/XD[5] D14 VDD_IO

A15 PIOB[11]/XD[11] B15 PIOB[12]/XD[12] C15 PIOC[8]/XRAMCS_N D15 GND_CORE

A16 PIOB[8]/XD[8] B16 PIOB[10]/XD[10] C16 PIOC[7]/XIOCS_N[11] D16 GND_CORE

A17 PIOB[6]/XD[6] B17 PIOB[7]/XD[7] C17 PIOC[5]/XIOCS_N[1] D17 GND_CORE

A18 PIOB[4]/XD[4] B18 PIOB[2]/XD[2] C18 PIOC[6]/XIOCS_N[10] D18 GND_IO

A19 PIOB[3]/XD[3] B19 PIOB[0]/XD[0] C19 GND_IO D19 VDD_IO

A20 PIOB[1]/XD[1] B20 GND_IO C20 PIOC[10]/XWE_N D20 GND_IO

A21 GND_IO B21 PIOC[11]/XOE_N C21 PIOC[9]/XROMCS_N D21 GND_IO

GND_IO

No Secondary Function

/ B = Secondary Function

PIOE[09]/-

PIOE[7]/-

Preliminary

PIOE[2]/-

PIOE[0]/E2 PIOE[1]/- F2 -/IDEA[2] G2 FRD_N/IDERE_N H2 FRB/IDERDY

E3 GND_CORE F3 -/IDEA[1] G3 -/IDERST_N H3 FCLE/IDECS_N[0]

E4 GND_CORE F4 VDD_CORE G4 VDD_CORE H4 VDD_IO

E18 VDD_IO F18 -/XSDCLK G18 -/XSYSCLK H18 -/XDQM[1]

E19 PIOC[3]/XBS_N[1] F19 PIOC[0]/XWAIT[0] G19 VDD_IO H19 -/XSDCKE

E20 PIOC[4]/XIOCS_N[0] F20 -/XSDCS_N G20 -/XRAS_N H20 AGND_RX/E21 PIOC[]2/XBS_N[0] F21 PIOC01/XWAIT[1] G21 -/XCAS_N H21 AVDD_TX/-

-/IDEDREQ

J2 -/IDEDACK_N K2 -/IDENPCBRID L2 RTC_TESTMODE/- M2 OSC32K1B/J3 VDD_RTC/- K3 32K_TESTMODE/- L3 PIOF[1]/IDED[9] M3 FD[5]/IDED[5]

J4 VDD_IO K4 VDD_IO L4 VDD_IO M4 GND_CORE

J18 -/DREQ K18 -/TCOUT L18 GND_PLL/- M18 OSC11M1B/J19 -/XDQM[0] K19 -/DREQCLR L19 USB_ATEST1/- M19 GND_PLL/-

6

• Oki Semiconductor January 2005, Rev 1.1b

-/IDEA[0]

-/IDEIRQ

FWR_N/IDEWR_N

OSC32K0/-

FALE/IDECS_N[1]

GND_RTC/-

N1

P1

R1

T1

U1

V1

W1

Y1

Preliminary

ML696500 and ML69Q6500

List of Pins (Continued)

BGA Pin Symbol BGA Pin Symbol BGA Pin Symbol BGA Pin Symbol

J20 AGND_TX/- K20 AGND_TX/- L20 AGND_C/- M20 AVDD_C/J21 USB_DM/- K21 USB_DP/- L21 AVDD_RX/- M21 USB_REXT/-

PIOF[6]/IDED[14]

N2 -/IDED[15] P2 PIOF[5]/IDED[13] R2 PIOF[3]/IDED[11] T2 PIOF[0]/IDED[8]

N3 FD[3]/IDED[3] P3 TDI/- R3 TMS/- T3 TCK/N4 VDD_CORE P4 VDD_CORE R4 VDD_IO T4 VDD_IO

N18 OSC11M0/- P18 VDD_CORE R18 VDD_IO T18 GND_CORE

N19 VDD_PLL/- P19 OSC48M1B/- R19 VSSFLA T19 ADIN[3]/N20 USB_ATEST[0]/- P20 OSC48M0/- R20 AGND/- T20 ADIN[2]/N21 USB_VOREF/- P21 VDD_PLL/- R21 ADIN[0]/- T21 ROUT/-

FD[4]/IDED[4]

U2 FD[6]/IDED[6]

U3 RTCK/U4 GND_IO

U18 AVDD/U19 ADIN1/U20 GND_HP/U21 MOUT/-

PIOF[4]/IDED[12]

PIOF[2]/IDED[10]

FD[7]/IDED[7]

FD[1]/IDED[1]

V2 FD[2]/IDED[2] W2 FD[0]/IDED[00] Y2 GND_IO AA2 GND_IO

V3 nTRST/- W3 GND_IO Y3 GND_CORE AA3 GND_CORE

V4 GND_IO W4 GND_CORE Y4 BOOT[0]/- AA4 BOOT[1]/V5 VDD_IO W5 IDEMODE/- Y5 EXTBUS/- AA5 TMODE[0]/V6 VDD_IO W6 TMODE[3]/- Y6 TMODE[1]/- AA6 TMODE[2]/V7 VDD_CORE W7 PLLBYPASS/- Y7 TEST_RSV/- AA7 PWMOUT/V8 VDD_IO W8 SDAT/- Y8 SCL/- AA8 PIOD[14]/UP_TXD

V9 VDD_IO W9 PIOD[15]/UP_RXD Y9 PIOD[13]/SSIOCK[1] AA9 PIOD[12]/SSIORXD[1]

V10 GND_CORE W10 PIOD[10]/SSIOCK[0] Y10 PIOD[9]/SSIORXD[0] AA10 PIOD[11]/SSIOTXD[1]

V11 GND_CORE W11 PIOD[7]/CKOUTA/CLKOUT Y11 VDD_FLA AA11 PIOD[8]/SSIOTXD[0]

V12 VDD_IO W12 PIOD[5]/WSA Y12 PIOD[4]/SCLA/SCL AA12 PIOD[6]/SDA

V13 VDD_IO W13 VDD_CORE Y13 PIOD[2]/SDD AA13 PIOD[3]/CKOUTD

V14 VDD_CORE W14 VDD_CORE Y14 VDD_CORE AA14 PIOD[1]/WSD

V15 GND_IO W15 GND_IO Y15 GND_IO AA15 PIOD[0]/SCLD

V16 GND_IO W16 RESET_N/- Y16 VDD_CAP/- AA16 GND_CODEC/V17 GND_IO W17 GND_IO Y17 GND_IO AA17 VDD_CODEC/V18 GND_DAC/- W18 COM/- Y18 GND_ADC/- AA18 MICIN/V19 RLINEOUT/- W19 REFN/- Y19 RLINEIN/- AA19 LLINEIN/V20 VDD_HP/- W20 VDD_DAC/- Y20 REFP/- AA20 VDD_ADC/V21 LOUT/- W21 LLINEOUT/- Y21 RRADIOIN/- AA21 LRADIOIN/-

VSSFLA

TDO/-

AA1

GND_IO

January 2005, Rev 1.1b

Oki Semiconductor • 7

ML696500 and ML69Q6500

Preliminary

Pin Descriptions

Primary/

Symbol I/O Description

System

OSC32K0 I 32-kHz oscillation input —

OSC32K1B O 32-kHz oscillation output —

OSC48M0 I 48-MHz oscillation input —

OSC48M1B O 48-MHz oscillation output —

OSC11M0 I 11-MHz oscillation input —

OSC11M1B O 11-MHz oscillation output —

RESET_N I System Reset (Active-Low) —

Mode

BOOT[1:0] I Controls boot devices —

BOOT[1] BOOT[0] Boot Device

0 0 MCP Flash

0 1 External Flash

1 0 AHBROM

1 1 AHBROM

Secondary

EXTBUS I Switches between external bus pin and GPIO. —

EXTBUS GPIO/External bus

0 GPIO0

1 External Bus

IDEMODE I Switches between IDE and NAND Flash pin —

IDEMODE NAND Flash/IDE controller

0 NAND Flash

1 IDE controller

PLLBYPASS I Sets PLL bypass mode —

PLLBYPASS PLL Mode

0 Use PLL

1 Bypass PLL – connect to GND

TEST_RSV This pin is used for testing. Always set TEST_RSV to GND level. —

TMODE [3:0] I These pins are used to switch test modes such as SCAN, TIC, JTAG-Flash, AUDIO A/D and D/A, and PLL.

Always set TMODE to GND level.

RTC_TESTMODE I This pin switches the Scan mode pin of the RTC section. —

32K_TESTMODE I This pin switches the test mode pin of a 32-kHz oscillator circuit. —

Debug Support

TCK I This pin is used during debugging. Normally connect this pin to GND. —

TMS I This pin is used during debugging. Normally set this input High —

nTRST I This pin is used during debugging. Normally connect this pin to GND. (n = Active Low) —

TDI I This pin is used during debugging. Normally set this input High —

TDO O This pin is used during debugging. Normally, do not connect this pin to any trace —

RTCK O This pin is used during debugging. Normally, do not connect this pin to any trace —

—

8

• Oki Semiconductor January 2005, Rev 1.1b

Preliminary

ML696500 and ML69Q6500

Pin Descriptions (Continued)

Primary/

Symbol I/O Description

External bus

XA [23:1] O Address of the bus that connects external RAM, external ROM, external IO and external DRAM Secondary

XD [15:0] I/O Data bus that connects external RAM, external ROM, external IO and external DRAM Secondary

External Bus Control Signal

XOE_N O External memory access read enable, Active-Low Secondary

XWE_N O External memory access write enable, Active-Low Secondary

XROMCS_N O External ROM chip select, Active-Low Secondary

XRAMCS_N O External RAM chip select, Active-Low Secondary

XBS1_N O External memory byte select (MSB), Active-Low Secondary

XBS0_N O External memory byte select (LSB), Active-Low Secondary

XIOCS11_N O I/O bank 1, chip select 1, Active-Low Secondary

XIOCS10_N O I/O bank 1, chip select 0, Active-Low Secondary

XIOCS01_N O I/O bank 0, chip select 1, Active-Low Secondary

XIOCS00_N O I/O bank 0, chip select 0, Active-Low Secondary

XWAIT [1:0] I Wait signal for I/O bank 0/1. A device slower than the register set value can be connected by inputting this signal (wait

when 1).

XSYSCLK O AHB clock for external bus Secondary

External Bus Control Signal (DRAM)

XSDCS_N O SDRAM chip select, Active-Low Secondary

XCAS_N O Column address strobe (SDRAM), Active-Low Secondary

XRAS_N O Row address strobe (SDRAM), Active-Low Secondary

XSDCLK O Clock for SDRAM Secondary

XSDCKE O Clock enable (SDRAM) Secondary

XDQM1 O Input/output mask (MSB) Secondary

XDQM0 O Input/output mask (LSB) Secondary

DMA control

DREQ I DMA request signal. This signal is used if the DREQ type is set by the DMA controller. Secondary

DREQCLR O DREQ signal clear request.

The DMA device turns off the DREQ signal when this signal is output.

TCOUT O This signal notifies the DAM device that the last transfer has been started. Secondary

General-purpose I/O Port

PIOA[15:0] I/O This is a general-purpose port – Because this port has a secondary function, it cannot be used as a port if its secondary

function is used.

PIOB[15:0] I/O This is a general-purpose port – Because this port has a secondary function, it cannot be used as a port if its secondary

function is used.

PIOC[15:0] I/O This is a general-purpose port – Because this port has a secondary function, it cannot be used as a port if its secondary

function is used.

PIOD [15:0] I/O This is a general-purpose port – Because this port has a secondary function, it cannot be used as a port if its secondary

function is used.

PIOE[15:0] I/O This is a general-purpose port.

PIOE[15] is 5-V tolerant.

PIOE[15:12] can be used as IRQ (interrupt requests)

PIOF[6:0] I/O This is a general-purpose port – Because this port has a secondary function, it cannot be used as a port if its secondary

function is used.

µPLAT-SIO

UP_RXD I µPLAT SIO (UART) receive data Secondary

UP_TXD O µPLAT SIO (UART) transmit data Secondary

IDE

Secondary

Secondary

Secondary

Primary

Primary

Primary

Primary

Primary

Primary

January 2005, Rev 1.1b

Oki Semiconductor • 9

C

ML696500 and ML69Q6500

Preliminary

Pin Descriptions (Continued)

Primary/

Symbol I/O Description

IDEA [2:0] O IDE controller address Secondary

IDED [15:0] I/O IDE controller data Secondary

IDERE_N O IDE controller read enable, Active-Low Secondary

IDEWR_N O IDE controller write enable, Active-Low Secondary

IDERDY I This allows the IDE controller's I/O cycle extension. Secondary

IDERST_N O Reset signal, Active-Low Secondary

IDECS1_N O IDE controller status/control select signal, Active-Low Secondary

IDECS0_N O IDE controller data/command select signal, Active-Low Secondary

IDEDREQ I IDE controller DMA request Secondary

IDEDACK_N O IDE controller, DMA acknowledge, Active-Low Secondary

IDEIRQ I IDE controller interrupt input Secondary

IDENPCBRID I This detects the IDE primary cable ID. Secondary

Flash

FD[7:0] I/O NAND Flash data Primary

FRD_N O NAND Flash read enable, Active-Low Primary

FWR_N O NAND Flash write enable, Active-Low Primary

FRB I NAND Flash ready/busy (1 = ready, 0 = busy) Primary

FALE O NAND Flash address latch enable Primary

FCLE O NAND Flash command latch enable Primary

USB

USB_DP I/O USB DP input/output Primary

USB_DM I/O USB DM input/output Primary

_REXT I USB REXT pin Primary

USB_VOREF O VoRef pin for USB TEST Primary

USB_ATEST [1:0] O USB ANALOG TEST pin 1-0 Primary

2

I

S Reception

ICLKOUTA/CLKOUT O I

2

S receive system clock Secondary

Secondary

SDA I I

WSA I/O I

SCLA/SCL I/O I

2

I

S Transmission

CKOUTD O I

SDD O I

WSD I/O I

SCLD I/O I

2

I

SDAT I/O I

SCL O I

2

S receive data Secondary

2

S receive channel select Secondary

2

S receive transfer clock Secondary

2

S transmit system clock Secondary

2

S transmit data Secondary

2

S transmit channel select Secondary

2

S transmit transfer clock Secondary

2

C transmit/receive data Primary

2

C clock output Primary

SSIO

SSIOCK [1:0] I/O SSIO clock pins 0 and 1 Secondary

SSIORXD [1:0] I SSIO receive data input 1 Secondary

SSIOTXD [1:0] O SSIO transmit data output 1 Secondary

PWM

PWMOUT O PWM output Primary

10

• Oki Semiconductor January 2005, Rev 1.1b

Preliminary

ML696500 and ML69Q6500

Pin Descriptions (Continued)

Primary/

Symbol I/O Description

A/D Converter

ADIN [3:0] I ADC input (CH3/2/1/0) Primary

Audio

LLINEOUT O Line-out L Primary

RLINEOUT O Line-out R Primary

LLINEIN I Line-in L Primary

RLINEIN I Line-in R Primary

MICIN I Microphone-in Primary

LRADIOIN I Radio-in L Primary

RRADIOIN I Radio-in R Primary

LOUT O L output Primary

MOUT O M output Primary

ROUT O R output Primary

Power Supply

REFP O Positive analog reference voltage —

REFN O Negative analog reference voltage —

COM O COM output —

VDD_DAC Power supply for AUDIO D/A (IO level) —

GND_DAC GND for AUDIO D/A —

VDD_ADC Power supply for AUDIO A/D (IO level) —

GND_ADC GND for AUDIO A/D —

VDD_HP Power supply for AUDIO HP (IO level) —

GND_HP GND for AUDIO HP —

VDD_CODEC Power supply for AUDIO logic regulator (IO level) —

GND_CODEC GND for AUDIO logic —

VDD_CAP Bypass capacitor connection pin —

VDD_CORE 1-8 Core logic power supply pin 1 —

GND_CORE 1-8 Core logic GND pin 1 —

VDD_PLL 1-2 PLL power supply pin 1(core level) —

GND_PLL 1-2 PLL GND pin 1 —

VDD_IO 1-14 IO power supply pin 1 —

GND_IO 1-14 IO GND pin 1 —

AVDD Power supply for 10-bit A/D C (IO level) —

AGND GND for 10-bit A/D C —

VDD_RTC Power supply for RTC (core level) —

GND_RTC GND for RTC —

AVDD_RX Power supply for USB (IO level) —

AGND_RX GND for USB —

AVDD_TX Power supply for USB (IO level) —

AGND_TX GND for USB —

AGND_TX GND for USB —

AVDD_C Power supply for USB (IO level) —

AGND_C GND for USB —

VDD_FLA Power supply for Flash (IO level) —

GND_FLA GND for Flash —

Secondary

January 2005, Rev 1.1b

Oki Semiconductor • 11

ML696500 and ML69Q6500

Electrical Characteristics

Absolute Maximum Ratings

Item Symbol Conditions Rating Unit

Digital power supply voltage (core)

Digital power supply voltage (I/O)

Audio power supply voltage

RTC power supply voltage

USB power supply voltage

Analog power supply voltage

Input Voltage V

Output Voltage V

Analog input voltage V

Power dissipation P

Storage temperature T

1. Exceeding these maximum ratings could cause damage or lead to permanent deterioration of the device

2. V

3. V

4. V

5. V

6. AV

7. AV

DD_CORE

DD_IO

DDAC

DDRTC

DDRX

DD

, V

DDPLL

, V

, V

, V

DDADC

DDHP

DDCODEC

, AV

, AV

DDTX

DDC

[3]

[4]

[5]

[6]

[7]

[1]

[2]

V

DD_CORE

V

DD_IO

V

DD_AUDIO

V

DD_RTC

V

DD_USB

AV

STG

DD

I

0

AI

D

Preliminary

All GND = 0V

T

= 25°C

A

TA = 70°C 400 mW

– -50 to +150 °C

-0.3 to 2.0 V

-0.3 to +4.6

-0.3 to +4.6

-0.3 to +2.0

-0.3 to +4.6

-0.3 to +4.6

-0.3 to V

-0.3 to V

-0.3 to AV

DD_IO

DD_IO

+0.3

+0.3

DD

Recommended Operating Conditions

(GND = 0 V)

Item Symbol Conditions Minimum Typical Maximum Units

Digital power supply voltage (core) V

Digital power supply voltage (I/O) V

Audio power supply voltage V

RTC power supply voltage V

USB power supply voltage V

Analog power supply voltage AV

CPU operating frequency f

HCLK operating frequency f

PCLK operating frequency f

OSC48M oscillating frequency f

OSC11M oscillating frequency f

OSC32K oscillating frequency F

Temperature of operation T

DD_COREVDD_IO

DD_IO

DD_AUDIO

DD_RTC

DD_USB

DD

OSC

HCLK

PCLK

C48

C11

C32

A

AV

– -30 25 +70 °C

DD

= V

≥ V

DD_CORE

DD_IO

1.45 1.5 1.55 V

2.7 3.3 3.6

2.7 3.3 3.6

1.45 1.5 1.55

3.0 3.3 3.6

2.7 3.3 3.6

– – 120 MHz

– – 60 MHz

– – 30 MHz

– 48.0 – MHz

– 11.2896 – MHz

– 32.768 – KHz

12

• Oki Semiconductor January 2005, Rev 1.1b

Preliminary

ML696500 and ML69Q6500

DC Characteristics

(V

1. Normal pins (including pulled-up and pulled-down pins).

2. 5-V tolerant pins.

3. OSC32K0, RTC_TESTMODE, and 32K_TESTMODE pins.

4. OSC48M0 and OSC11M0 pins.

5. Dependent on drive currents of pins.

6. IDE related pins.

7. Pins for 32-kHz oscillator.

8. Pins for 48-MHz and 11-MHz oscillators.

9. Normal pins.

10. Pulled-up pins.

11. Pulled-down pins.

= 1.45 to 1.55 V, V

DD_CORE

= 2.7 to 3.6 V, TA = 0 to +70 °C)

DD_IO

Parameter Symbol Condition Min. Typ. Max. Unit

“H” input voltage

“L” input voltage

“H” input voltage

“H” input voltage

“L” input voltage

“H” input voltage

“L” input voltage

“H” output voltage

“H” output voltage

“L” output voltage

“H” output voltage

“L” output voltage

“H” output voltage

“L” output voltage

Input leakage current

Input leakage current

Input leakage current

Input leakage current

Input leakage current

Input leakage current

Input leakage current

Input leakage current

Supply current (RTC section) I

[1]

[1]

[2]

[3]

[3]

[4]

[4]

[1]

[6]

[1]

[7]

[7]

[8]

[8]

[9]

[9]

[10]

[10]

[11]

[11]

[8]

[7]

V

IH1

V

IL1

V

IH2

V

IH3

V

IL3

V

IH4

V

IL4

V

OH1

V

OH2

V

OL1

V

OH3

V

OL3

V

OH4

V

OL4

I

IL1

I

IL2

I

IL3

I

IL4

I

IL5

I

IL6

I

IL7

I

IL8

DD_RTC

2.2 — V

-0.3 — 0.6

2.2 — 5.5

0.8 × V

DD_RTC

—V

-0.3 — 0.2 × V

0.8 × V

DD_IO

—V

-0.3 — 0.2×V

IOH = –2 mA/ –4 mA/ –6 mA

V

= 3.0 to 3.6 V 2.2 — —

DD_IO

IOL = –2 mA/ –4 mA/ –6 mA

[5]

[5]

2.2 — —

— 0.4

0.8 × V

DD_RTC

——

— 0.2 × V

0.8 × V

DD_IO

——

— 0.2 × V

VI = 0V / V

DD_IO

-10 — 10 µA

VI = 0V / 5.5 V -10 — 10

VI = 0V -200 –66 –10

VI = VDD_IO -10 — 10

VI = 0V -10 — 10

VI = V

VI = 0V / V

VO = 0V / V

V

= 2.5 V

DD_RTC

DD_IO

DD_IO

DD_IO

10 66 200

-1 — 1

-0.15 — 0.15

— — 50 µA

+0.3 V

DD_IO

+0.3

DD_RTC

DD_RTC

+0.3

DD_IO

DD_IO

DD_RTC

DD_IO

(Only the RTC section is powered on)

Supply current (Core section) I

DD_CORE

— — 200 mA

January 2005, Rev 1.1b

Oki Semiconductor • 13

ML696500 and ML69Q6500

Preliminary

Analog-to-Digital Converter Characteristics

(V

1. Resolution Minimum input analog value that can be discriminated. In a 10-bit converter, the number of discrete steps is equal to 210 (= 1024), where 10 is the resolution of the converter, so the voltage from V

2. Linearity error is the deviation between the ideal conversion characteristic and the actual conversion characteristic of a 10-bit analog-to-digital converter (not including quantization error). The ideal conversion characteristic can be

3. Differential linearity error indicates the smoothness of conversion characteristics. The range of the analog input voltage that corresponds to one converted bit of digital output is ideally 1 LSB = (VREF - AGND) /1024. The differential

4. Zero-scale error is the deviation between the ideal conversion characteristics and actual conversion characteristics at the point where the digital output changes from "000h" to "001h".

5. Full-scale error is the deviation between the ideal conversion characteristics and actual conversion characteristics at the point where the digital output changes from "3FEh" to "3FFh".

= 1.45 to 1.55 V, V

DD_CORE

= 2.7 to 3.6 V, TA = –30 to +70 °C)

DD_IO

Parameter Symbol Condition Min. Typ. Max. Unit

[1]

Resolution

Linearity error

Differential linearity error

Zero-scale error

Full-scale error

[2]

[3]

[4]

[5]

Conversion time t

n — — — 10 bit

E

E

D

E

ZS

E

FS

CONV

L

Analog input source

impedance

Ri ≤ tbd kΩ

— 6.7 — — µs

— tbd — lsb

— tbd —

— tbd —

— tbd —

Throughput rate — 10 — 200 kHz

to AGND can be

divided with 1024.

obtained by dividing the voltage from V

linearity error is the deviation between this ideal bit size and the bit size at an arbitrary point in the conversion range.

to AGND into 1024 equal steps.

REF

REF

14 • Oki Semiconductor January 2005, Rev 1.1b

Preliminary

Package Dimensions

ML696500 and ML69Q6500

• Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow

mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the

product name, package name, pin number, package code and desired

mounting conditions (reflow method, temperature and times).

January 2005, Rev 1.1b

Oki Semiconductor • 15

ML696500 and ML69Q6500

Related Oki Documents for the ML696500 and ML69Q6500

Document Date

Related ARM Documents for the ML696500 and ML69Q6500

Document

ARM946E™ Technical Reference Manual

ARM Architecture Reference Manual

Revision History

Revision Number Date Changes from Previous Revision

Revision 1.0 October, 2004 Preliminary release of the document

Revision 1.1 November, 2004 Corrections and clarifications made to some of the Descriptions and F eatures sections . Some pin names changed to make them consistent

in the document. DC operating voltage range changed to 1.45 V to 1.55 V

Preliminary

16 • Oki Semiconductor January 2005, Rev 1.1b

Preliminary

ML696500 and ML69Q6500

January 2005, Rev 1.1b

Oki Semiconductor • 17

ML696500 and ML69Q6500

Notice

The information contained herein can change without notice owing to product and/

or technical improvements.

Please make sure before using the product that the information you are referring

to is up-to-date.

The outline of action and examples of application circuits described herein have

been chosen as an explanation of the standard action and performance of the

product. When you actually plan to use the product, please ensure that the outside conditions are reflected in the actual circuit and assembly designs.

Oki assumes no responsibility or liability whatsoever for any failure or unusual or

unexpected operation resulting from misuse, neglect, improper installation, repair,

alteration or accident, improper handling, or unusual physical or electrical stress

including, but not limited to, exposure to parameters outside the specified maximum ratings or operation outside the specified operating range.

Neither indemnity against nor license of a third party's industrial and intellectual

property right,etc.is granted by us in connection with the use of product and/or the

information and drawings contained herein. No responsibility is assumed by us for

any infringement of a third party's right which may result from the use thereof.

When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges, including but not limited to

operating voltage, power dissipation, and operating temperature.

The products listed in this document are intended for use in general electronics

equipment for commercial applications (e.g., office automation, communication

equipment, measurement equipment, consumer electronics, etc.). These prod-

Preliminary

ucts are not, unless specifically authorized by Oki, authorized for use in any

system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or

application may result in the loss or damage of property, or death or injury to

humans. Such applications include, but are not limited to: traffic control, automotive, safety, aerospace, nuclear power control, and medical, including life support

and maintenance.

Certain parts in this document may need governmental approval before they can

be exported to certain countries. The purchaser assumes the responsibility of

determining the legality of export of these parts and will take appropriate and necessary steps, at their own expense, for export to another country.

Oki Semiconductor reserves the right to make changes in specifications at anytime and without notice. This information furnished by Oki Semiconductor in this

publication is believed to be accurate and reliable. However, no responsibility is

assumed by Oki Semiconductor for its use; nor for any infringements of patents or

other rights of third parties resulting from its use. No license is granted under any

patents or patent rights of Oki.

Trademarks:

µPlat is a trademark of Oki Semiconductor. ARM, ARM7TDMI, and the ARM Powered Logo are registered trademarks, and AMBA, ARM7, and Multi-ICE are

trademarks of Advanced RISC Machines, Ltd.

Copyright 2003 Oki Semiconductor

Regional Sales Offices – Semiconductor Products

Northwest Area

785 N. Mary Avenue

Sunnyvale, CA 94085

Tel: 408/720-1900

Fax:408/720-8965

Northeast Area

Shattuck Office Center

138 River Road

Andover, MA 01810

Tel: 978/688-8687

Fax:978/688-8896

North Central Area

1450 East American Lane, Suite 1400

Schaumburg, IL 60143

Tel: 847/330-4494

847/330-4498

Fax:847/330-4491

Southwest and

South Central Area

1902 Wright Place, Suite 200

Carlsbad, CA 92008

Tel: 760/918-5830

Fax:760/918-5505

Southeast Area

4800 Whitesburg Drive # 30

PMB 263

Huntsville, AL 35802

Tel: 256/520-8035

Fax:408/737-6417

Oki Web Site:

http://www.okisemi.com/us

January 2005, Rev 1.1b

Corporate Headquarters

785 N. Mary Avenue

Sunnyvale, CA 94085-2909

Tel: 408/720-1900

Fax:408/720-1918

Loading...

Loading...