Semiconductor

Version 2

Aug., 1999

ML670100

OKI’s High-Performance CMOS 32-Bit Single Chip Microcontroller

GENERAL DESCRIPTION

The ML670100 is a high-performance 32-bit microcontroller combining a RISC based, 32-bit CPU core the ARM7TDMITM - with memory and such peripheral circuits as timers, serial ports, and analog-todigital converter. This combination of 32-bit data processing, built-in memory, and on-chip peripherals

make it ideal for controlling equipment requiring both high speed and high functionality. An external

memory controller supports direct connection to memory and peripheral devices for adding even more

functionality.

FEATURES

Operating Voltage 2.7 to 3.6V

Operating Frequency 25MHz maximum(3.0 to 3.6V)

On-chip memory -ROM: 128 kilobytes

-RAM: 4 kilobytes

I/O Function I/O ports: 8 bits x 9, I/O directions are specified at the bit level

Timer -Flexible timer (16-bit multi-function timer with six channels)

Choice of operating modes: auto-reload timer, compare output, PWM

and capture

-Time base counter with WDT function

Serial Port -One asynchronous serial port (UART) with baud rate generator

-Two clock synchronous serial port

A-to-D Converter -8-bit resolution A-to-D converter with eight analog input ports

Interrupt

Controller

External Memory

Controller

Clock Generator -Built-in crystal oscillation circuit and PLL

Package 144-pin LQFP ( LQFP144-P-2020-0.50-K)

-Support for 28 interrupt sources: 9 external and 19 internal

-Choice of eight priority levels for each source

-Direct connection to ROM, SRAM, DRAM and peripheral devices

-Support for four banks: two for ROM, SRAM and I/O devices plus two for

DRAM

-User-configurable bus width (8/16 bits) and wait control and other

parameters for accessing memory and external devices

-Choice of divider ratio (1/1, 1/2, 1/4) for adjusting operating clock frequency

to match the load of processing

ARM POWERED logo is the registered trademark of ARM Limited. ARM7TDMI is the trademark of ARM Limited.

The Information contained herein can change without notice owing to product and/or technical improvement.

The signal name of negative logic is being changed to nXXX from XXX in this data sheet.

1 / 27

Semiconductor

TRST*

VCOM

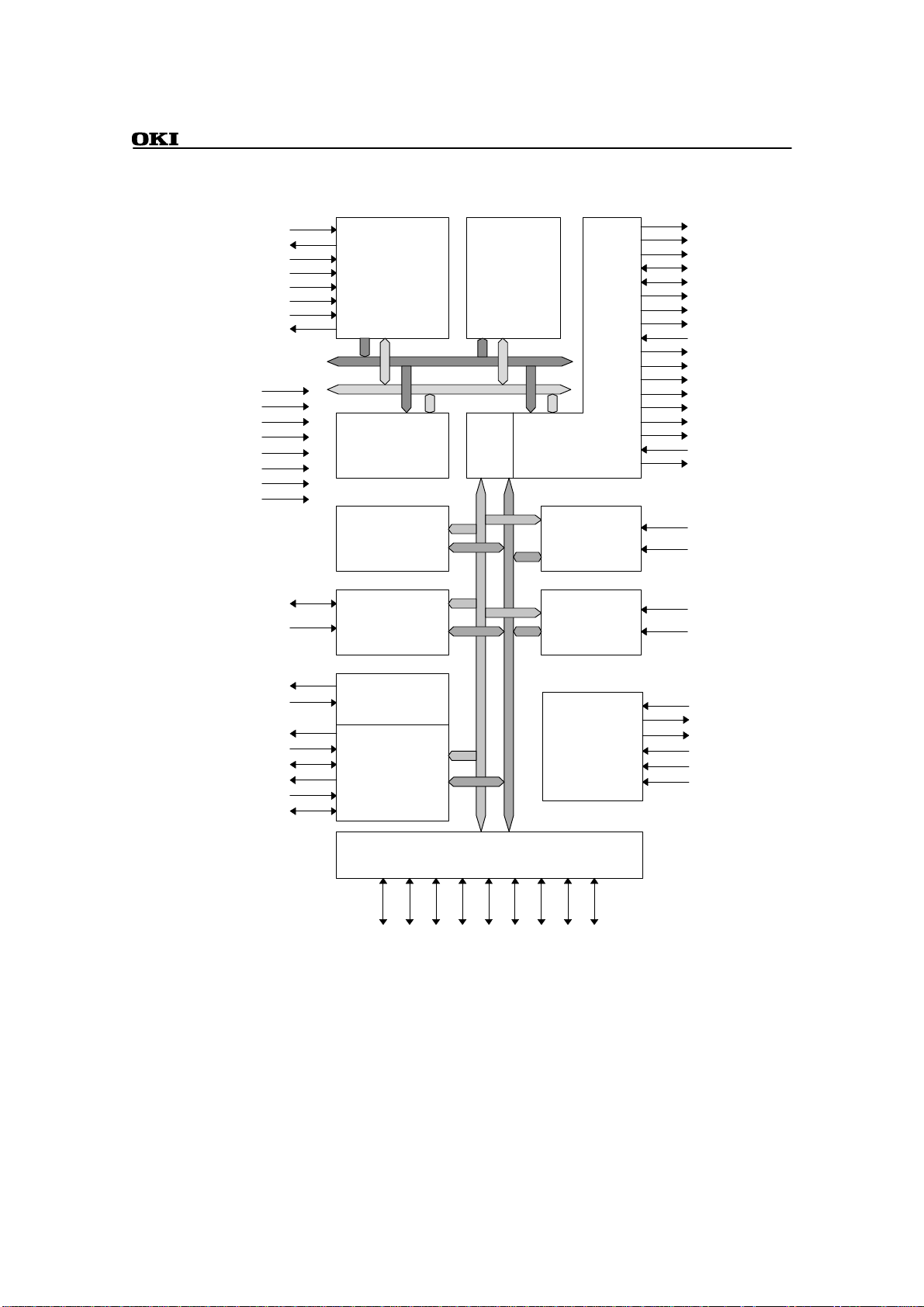

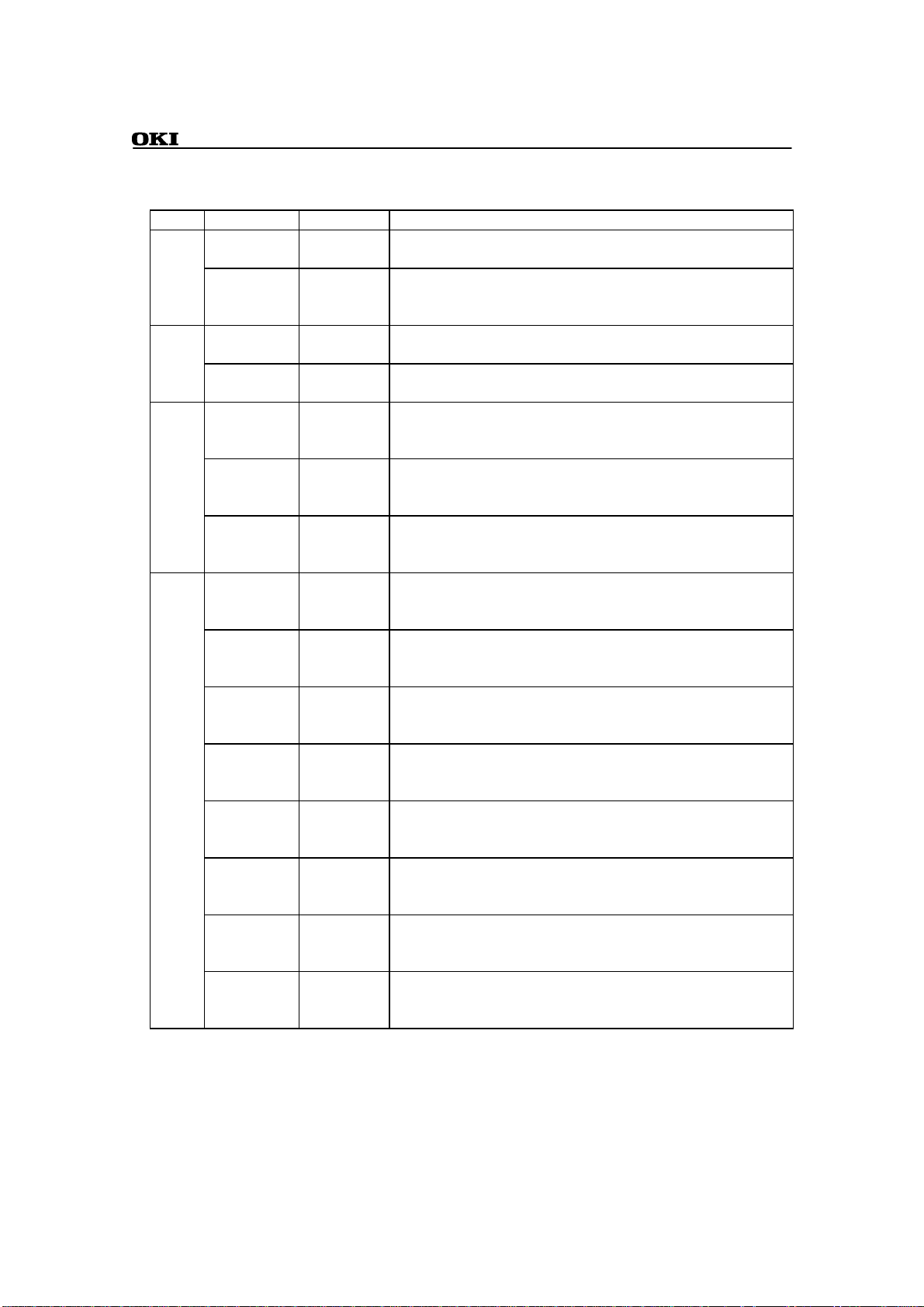

BLOCK DIAGRAM

ML670100

TDI*

TDO*

n

TMS*

TCK*

DBGEN*

DBGRQ*

DBGACK*

nRST

nEA

DBSEL

TEST

VDD

GND

AVDD

AGND

TMIN/TMOUT[5:0]*

TMCLK[1:0]*

ARM7TDMI

Core address bus

Core data bus (32b)

128 kilobytes

of ROM

Time Base

Generator

(TBG)

Flexible

Timer

4 kilobytes

of RAM

Internal

External Memory

Bus

Controller

Controller (XMC)

Interrupt

Controller

(INT)

Analog-to-digital

Converter

(ADC)

XA23-16*

XA15-1

nLB/XA0

XD15-8*

XD7-0

nCS0

nRD

nWRE/nWRL

nXWAIT*

nCS1*

nHB/nWRH*

nRAS1*

nWH/nCASH*

nRAS0*

nCAS/nCASL*

nWL/nWE*

nBREQ*

nBACK*

nEFIQ

nEIR[7:0]*

VREF

AI[7:0]

ASI_TXD*

ASI_RXD*

CSI1_TXD*

CSI1_RXD*

CSI1_SCLK*

CSI0_TXD*

CSI0_RXD*

CSI0_SCLK*

Asynchronous

Serial Interface

(ASI)

Clock

Synchronous

Interface

(CSI0 and CSI1)

Peripheral data bus 16b)

Peripheral address bus

I/O Ports

PIO8[7:0]

PIO7[7:0]

PIO6[7:0]

PIO5[7:0]

PIO4[7:0]

Asterisks indicate signals that aresecondary functions of I/O ports.

Brackets indicate bit ranges.

PIO3[7:0]

PIO2[7:0]

Clock

Control

PIO1[7:0]

PIO0[7:0]

OSC0

OSC1

CLKOUT

FSEL

PLLEN

/ 272

Semiconductor

TEST

PIO8[2]/DBGEN

nTRST

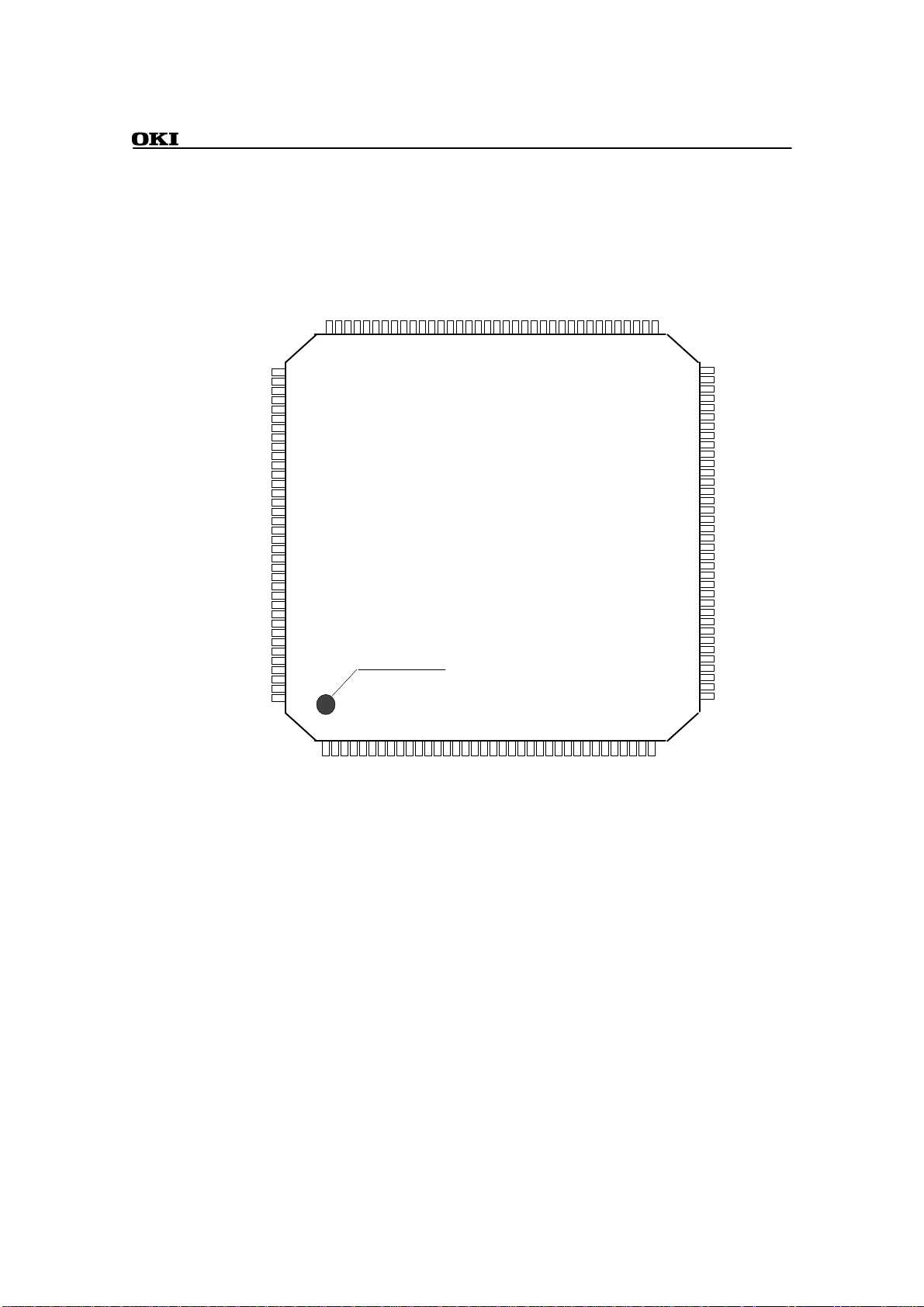

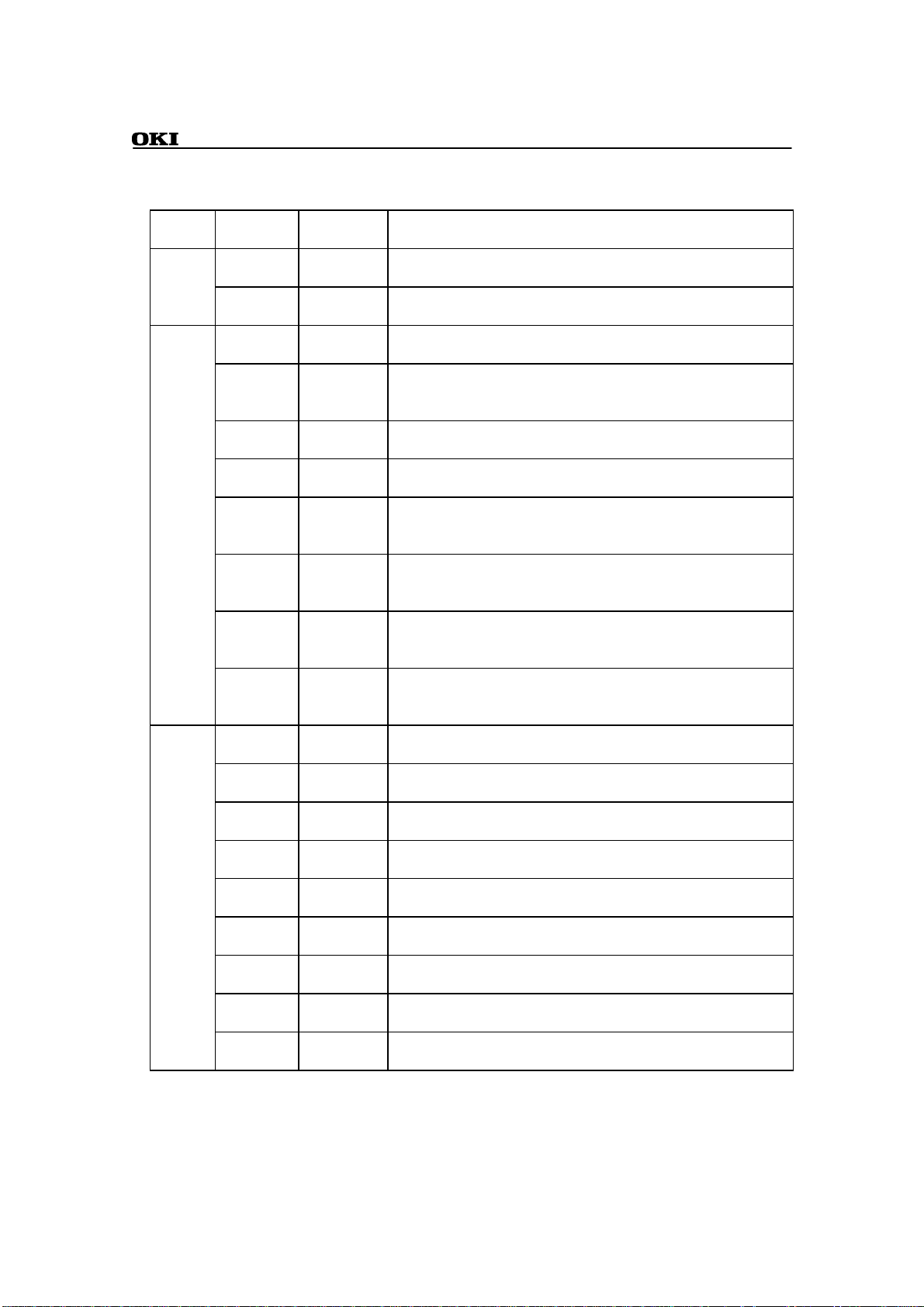

PIN CONFIGURATION (TOP VIEW)

ML670100

PIO3[5]/nEIR[5]

PIO3[6]/nEIR[6]

PIO3[7]/nEIR[7]

PIO4[0]/TMIN[0]/TMOUT[0]

PIO4[1]/TMIN[1]/TMOUT[1]

PIO4[2]/TMIN[2]/TMOUT[2]

PIO4[3]/TMIN[3]/TMOUT[3]

PIO4[4]/TMIN[4]/TMOUT[4]

PIO4[5]/TMIN[5]/TMOUT[5]

PIO4[6]/TMCLK[0]

PIO4[7]/TMCLK[1]

PIO5[0]/CSI0_SCLK

PIO5[1]/CSI0_RXD

PIO5[2]/CSI0_TXD

PIO5[3]/CSI1_SCLK

PIO5[4]/CSI1_RXD

PIO5[5]/CSI1_TXD

GND

GND

VDD

PIO5[6]/ASI_RXD

PIO5[5]/ASI_TXD

CLKOUT

GND

OSC0

OSC1

VDD

VCOM

FSEL

PLLEN

nRST

GND

AGND

AI[7]

AI[6]

AI[5]

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

VDD

GND

PIO3[0]/nEIR[0]

PIO3[1]/nEIR[1]

PIO3[2]/nEIR[2]

PIO3[4]/nEIR[4]

PIO3[3]/nEIR[3]

108

107

106

105

104

103

102

INDEX MARK

123456789

PIO2[7]/nXWAIT

999897969594939291908988878685848382818079787776757473

101

100

nCS0

nWRE/nWRL

VDD

nRD

GND

PIO2[0]/nWL/nWE

PIO2[1]/nCAS/nCASL

PIO2[2]/nRAS0

PIO2[3]/nWH/nCASH

PIO2[4]/nRAS1

PIO2[5]/nHB/nWRH

PIO2[6]/nCS1

PIO1[3]/XD11

PIO1[4]/XD12

PIO1[5]/XD13

PIO1[6]/XD14

PIO1[7]/XD15

PIO1[2]/XD10

GND

VDD

PIO1[0]/XD8

PIO1[1]/XD9

XD7

Top View

101112131415161718192021222324252627282930313233343536

XD6

XD5

XD4

XD3

XD2

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

XD1

XD0

VDD

GND

nEA

nEFIQ

PIO0[7]/XA23

PIO0[6]/XA22

PIO0[5]/XA21

PIO0[4]/XA20

PIO0[3]/XA19

PIO0[2]/XA18

PIO0[1]/XA17

PIO0[0]/XA16

VDD

GND

XA15

XA14

XA13

XA12

XA11

XA10

XA9

XA8

VDD

GND

XA7

XA6

XA5

XA4

XA3

XA2

XA1

XA0/nLB

VDD

GND

AI[4]

AI[3]

AI[2]

AI[1]

AI[0]

VREF

AVDD

VDD

DBSEL

PIO6[0]

PIO6[1]

PIO6[2]

PIO6[3]

/ 273

PIO6[4]]PIO6[5]]PIO6[6]

PIO6[7]

PIO7[0]

PIO7[1]

GND

PIO7[2]

VDD

PIO7[3]

PIO7[4]

PIO7[5]

PIO7[6]/nBREQ

PIO7[7]/nBACK

PIO8[3]/TCK

PIO8[4]/TMS

PIO8[5]/

PIO8[1]/DBGRQ

PIO8[0]/DBGACK

PIO8[7]/TDI

PIO8[6]/TDO

Semiconductor

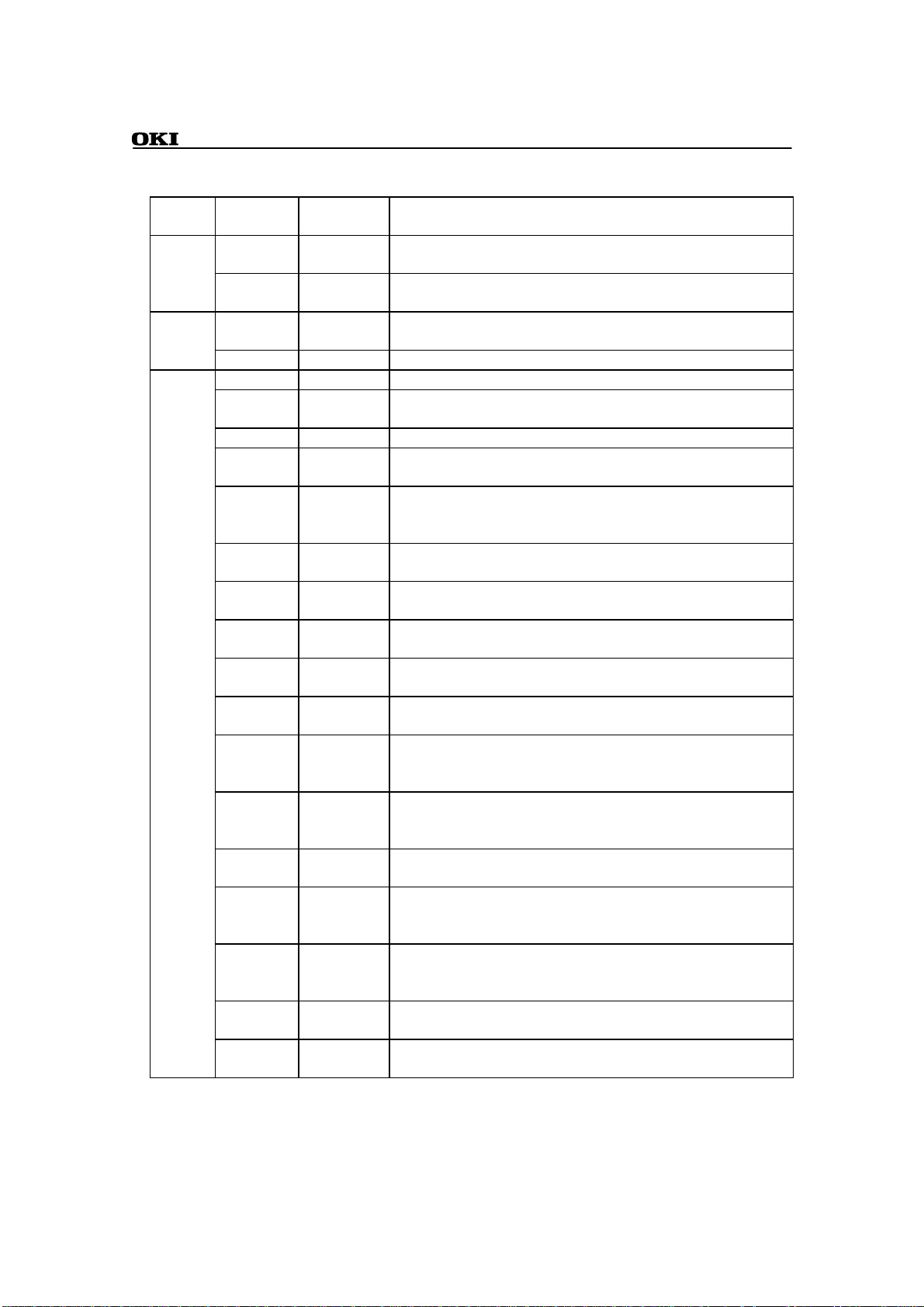

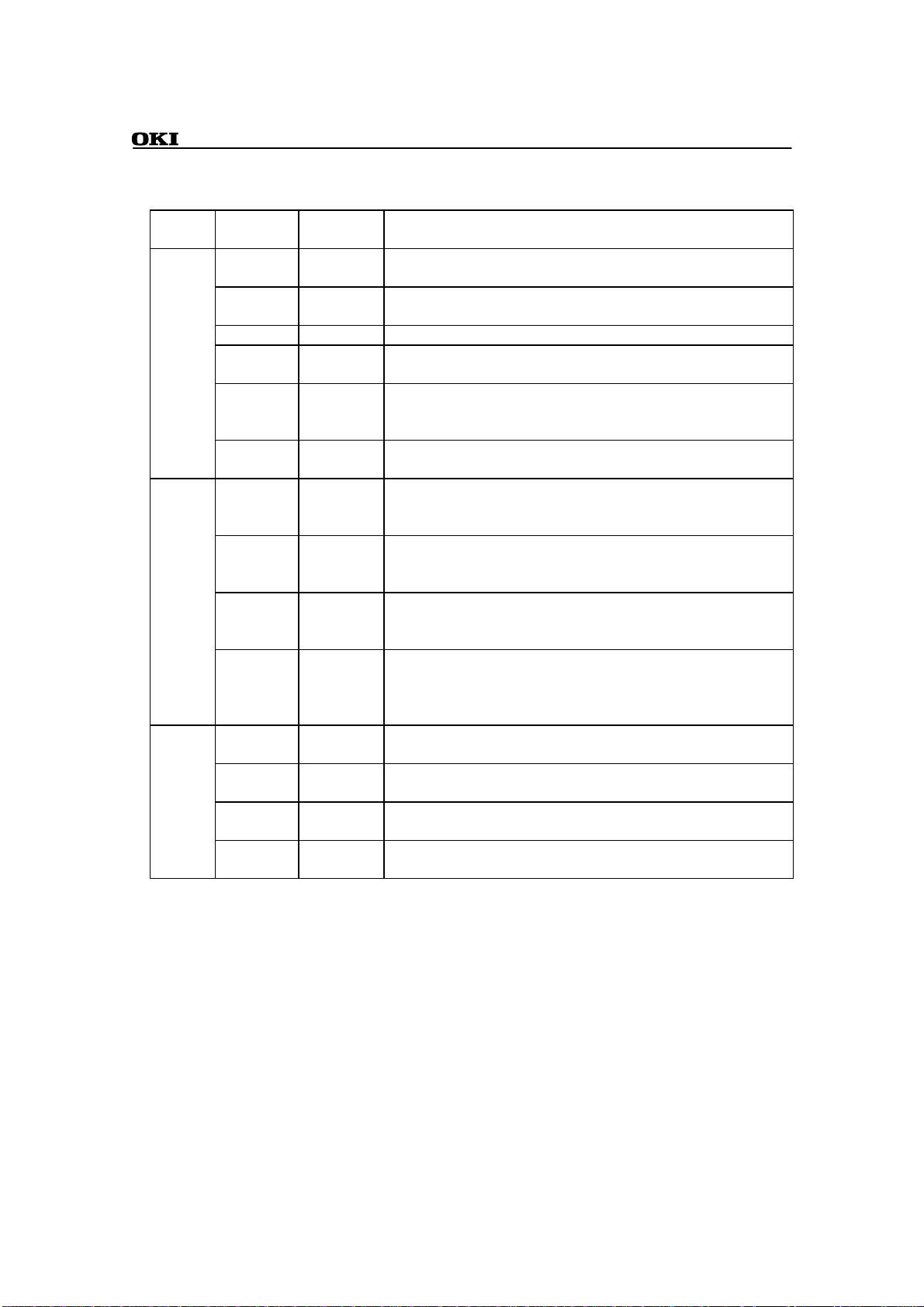

PIN DESCRIPTIONS

ML670100

Type Signal

Name

Address

bus

Data bus XD15 -

Bus nCS0 Output This output is the chip select signal for bank 0.

control

signals

XA23 -

XA16

XA15 -

XA0

XD8

XD7- -XD0 Bidirectional These are bits 7-0 of the external data bus.

nCS1 Output This output is the chip select signal for bank 1. It represents a

nRD Output This output is the read signal for SRAM banks (0 and 1).

nWRL Output This output is the Write Enable Low signal for SRAM banks (0

nWRH Output This output is the Write Enable High signal for SRAM banks (0

nWRE Output This output is the Write Enable signal for SRAM banks (0 and

nLB Output This output is the Low Byte Select signal for SRAM banks (0

nHB Output This output is the High Byte Select signal for SRAM banks (0

nRAS0 Output This output is the Row Address Strobe signal for bank 2.

nRAS1 Output This output is the Row Address Strobe signal for banks 3.

nCASL Output This output is the Column Address Strobe Low signal for

nCASH Output This output is the Column Address Strobe High signal for

nWE Output This output is the Write Enable signal for DRAM banks (2 and

nCAS Output This output is the Column Address Strobe signal for DRAM

nWH Output This output is the Write Enable High signal for DRAM banks

nWL Output This output is the Write Enable Low signal for DRAM banks (2

nXWAIT Input This input pin controls insertion of wait cycles. It represents a

I/O Direction Description

Output These are bits 23-16 of the external address bus. They represent

secondary functions for I/O port PIO0[7:0].

Output These are bits 15 - 0 of the external address bus.

Bidirectional These are bits 15-8 of the external data bus. They represent

secondary functions for I/O port PIO1[7:0].

secondary function for I/O port PIO2[6].

and 1).

and 1). It represents a secondary function for I/O port

PIO2[5].

1).

and 1).

and 1). It represents a secondary function for I/O port PIO2[5].

It represents a secondary function for I/O port PIO2[2].

It represents a secondary function for I/O port PIO2[4].

DRAM banks (2 and 3). It represents a secondary function for

I/O port PIO2[1].

DRAM banks (2 and 3). It represents a secondary function for

I/O port PIO2[3].

3). It represents a secondary function for I/O port PIO2[0].

banks (2 and 3). It represents a secondary function for I/O port

PIO2[1].

(2 and 3). It represents a secondary function for I/O port

PIO2[3].

and 3). It represents a secondary function for I/O port PIO2[0].

secondary function for I/O port PIO2[7].

/ 274

Semiconductor

ML670100

PIN DESCRIPTIONS (Cont.)

Type Signal Name I/O Direction Description

Bus

control

signals nBACK Output This output is an acknowledgment signal to a bus request signal

Interrupts

Timers TMIN[5:0] Input These pins function as capture trigger input pins for Flexible

Serial

ports

nBREQ Input This input is a bus request signal from an external device.

It represents a secondary function for I/O port PIO7[6].

from an external device. It represents a secondary function for

I/O port PIO7[7].

nEFIQ Input This input is an external fast interrupt request (FIQ). When

accepted, the request is processed as an FIQ exception.

nEIR[7:0] Input This inputs are external interrupt requests. They represent

secondary functions for I/O port PIO3[7:0].

Timer channels 5-0 in capture mode. They represent secondary

functions for I/O port PIO4[5:0].

TMOUT[5:0] Output These pins function as output pins for Flexible Timer channels

5-0 in compare output or PWM mode. They represent

secondary functions for I/O port PIO4[5:0].

TMCLK[1:0] Input These pins function as Flexible Timer channels 1 and 0 clock

input pins. They represent secondary functions for I/O port

PIO4[7:6].

ASI_TXD Output This output is the transmit data for the Asynchronous Serial

Interface. It represents a secondary function for I/O port

PIO5[7].

ASI_RXD Input This input is the receive data for the Asynchronous Serial

Interface. It represents a secondary function for I/O port

PIO5[6].

CSI0_TXD Output This output is the transmit data for the Clock Synchronous

Serial Interface 0. It represents a secondary function for I/O

port PIO5[2].

CSI0_RXD Input This input is the receive data for the Clock Synchronous Serial

Interface 0. It represents a secondary function for I/O port

PIO5[1].

CSI0_SCLK Bidirectional This pin accepts/provides clock signal for the Clock

Synchronous Serial Interface 0. It represents a secondary

function for I/O port PIO5[0].

CSI1_TXD Output This output is the transmit data for the Clock Synchronous

Serial Interface 1. It represents a secondary function for I/O

port PIO5[5].

CSI1_RXD Input This input is the receive data for the Clock Synchronous Serial

Interface 1. It represents a secondary function for I/O port

PIO5[4].

CSI1_SCLK Bidirectional This pin accepts/provides clock signal for the Clock

Synchronous Serial Interface 1. It represents a secondary

function for I/O port PIO5[3].

/ 275

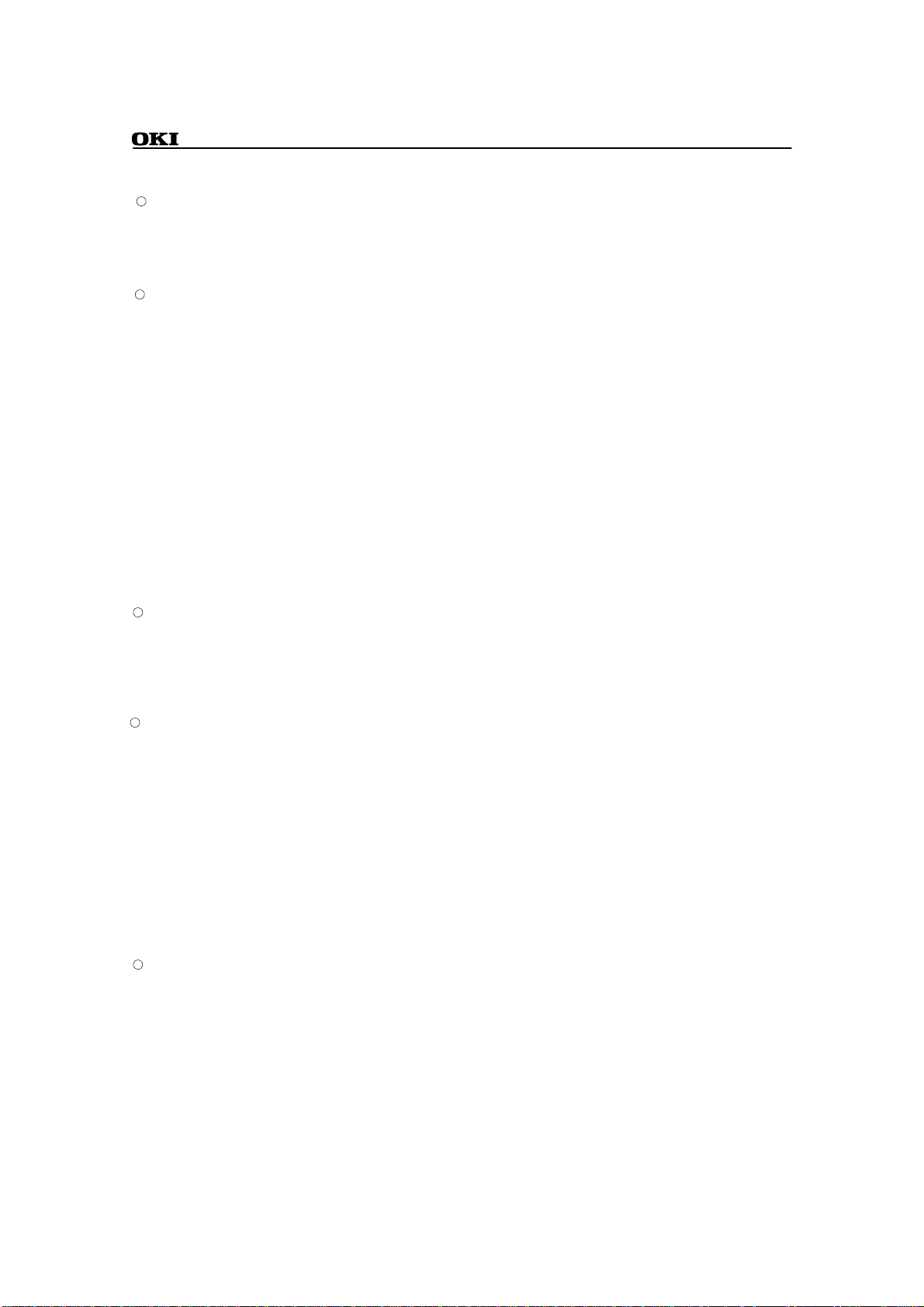

Semiconductor

PIN DESCRIPTIONS (Cont.)

ML670100

Type Signal

Name

Analogto-digital

converter AI[7:0] Input These are analog signal input pins for analog-to-digital

Debugging

interface TDO Output This output is the serial data output for the debugging scan

I/O ports PIO8[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

VREF Input This input is the reference voltage for the analog-to-digital

TDI Input This input is the serial data input for the debugging scan circuit.

nTRST Input "L" level input to this pin resets the debugging scan circuit.

TMS Input This input selects the mode for the debugging scan circuit.

TCK Input This input is the serial clock input for the debugging scan

DBGEN Input "H" level input to this pin enables the CPU's debugging

DBGRQ Input This input is a debugging request signal from an external

DBGACK Output This output is an acknowledgment signal to a debugging

PIO7[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

PIO6[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

PIO5[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

PIO4[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

PIO3[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

PIO2[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

PIO1[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

PIO0[7:0] Bidirectional These form an 8-bit I/O port. I/O directions are specified at the

I/O Direction Description

converter channels 7-0. Connect it to VDD.

converter channels 7-0.

It represents a secondary function for I/O port PIO8[7].

circuit. It represents a secondary function for I/O port

PIO8[6].

It represents a secondary function for I/O port PIO8[5].

It represents a secondary function for I/O port PIO8[4].

circuit. It represents a secondary function for I/O port

PIO8[3].

function. It represents a secondary function for I/O port

PIO8[2].

device. It represents a secondary function for I/O port

PIO8[1].

request signal from an external device. It represents a secondary

function for I/O port PIO8[0].

bit level.

bit level.

bit level.

bit level.

bit level.

bit level.

bit level.

bit level.

bit level.

/ 276

Semiconductor

PIN DESCRIPTIONS (Cont.)

ML670100

Type Signal

Name

Clock

control

System

control

Power

Supply

OSC0 Input This pin is for connecting a crystal oscillator. If an external

OSC1 Output This pin is for connecting a crystal oscillator. If an external

CLKOUT Output This output is the internal system clock signal.

FSEL Input Connect this pin to VDD or ground to indicate the frequency

PLLEN Input Connect this pin to VDD to enable the built-in phase-looked

VCOM Input This input controls the oscillation frequency of the PLL's

nRST Input "L" level input to this pin produces an external system reset for

DBSEL Input During a system reset of this LSI, this input specifies the width

nEA Input During a system reset of this LSI, this input controls the use of

TEST Input During a system reset of this LSI, this input controls the initial

VDD Input These pins are this LSI's power supply pins. Connect them all to

GND Input These pins are this LSI's ground pins. Connect them all to

AVDD Input This pin is the analog-to-digital converter's power supply.

AGND Input This pin is the analog-to-digital converter's ground pin.

I/O

Direction

Description

clock is used, supply it to this pin.

clock is used, leave this pin open.

range for the basic clock.

loop. If the PLL is not used because an external clock with a

guaranteed duty is available, connect this pin to ground.

voltage-controlled oscillator. Connect it to ground.

this LSI. "H" level input then causes execution to resume from

address 0x000000.

of the external data bus for bank 0. Connect this pin to VDD for

a data bus width of 16bits and to ground for 8bits.

the internal ROM. Connect this pin to VDD to enable the ROM

and to ground to disable it.

pin functions for the I/O port 8 pins(PIO8[7:0]). Connect this

pin to VDD to initialize the port for its secondary function, the

debugging interface, and to ground for I/O.

VDD.

ground.

Connect it to VDD.

Connect it to ground.

/ 277

Semiconductor

ML670100

OUTLINE of PERIPHERAL FUNCTIONS

I/O Ports

The I/O ports consist of nine 8-bit ports: PIOn(n=0 - 8). I/O directions are specified at the bit level. When

configured for input, the pins use high-impedance input.

Flexible Timer

The flexible timer consists of six 16-bit timer channels. Each channel offers independent choice of four

operating modes and of eight count clocks.

-Timer operating modes

- Auto-reload timer

- Compare output

- Pulse width modulation (PWM)

- Capture input

-Timer synchronization

- Timer channels can be started and stopped in union.

-External clocks

- Timer channels 0 and 1 accept external clock signals.

Time Base Generator

The time base generator consists of the time base counter, a frequency divider which derives the time base

signals for the on-chip peripherals from the system clock signals, and watchdog timer, which counts time

base clock cycles and produces a system reset signal when its internal counter overflows.

Asynchronous Serial Interface

The asynchronous serial interface is a serial port that frames each character of information with start and

stop elements. Parameters control transfer speed (using a dedicated baud rate generator), character length,

number of stop bits and use of parity.

-Built-in baud rate generator

-Character length: 7 or 8 bits

-Stop bits: 1 or 2

-Parity: none, odd, or even

-Error detection for receiving: parity, framing and overrun errors

-Full duplex operation

Clock Synchronous Serial Interface

The clock synchronous serial interface are two channels of serial ports that transmit 8-bit data

synchronized with internal or external clock signals.

/ 278

Semiconductor

Analog-to-Digital Converter

The analog-to-digital converter is an 8-bit successive approximation analog-to-digital converter with

eight input channels and four result registers. It offers two operating mode: scan mode, which

sequentially converts the inputs from the selected set of four input channels, and select mode, which

converts the input from a single input channel.

-Resolution: 8 bits

-Eight analog input channels

-Four result registers for holding conversion results

-Operating modes

- Scan modes: Sequential conversion of the analog inputs from the upper or lower set of four

input channels

- Select mode: Conversion of the analog inputs from a single input channel

Interrupt Controller

The interrupt controller manages interrupt requests from 9 external sources and 19 internal ones and

passes them on to the CPU as interrupt request (IRQ) or fast interrupt request (FIQ) exception requests. It

supports eight interrupt levels for each source for use in priority control.

-The interrupt controller supports 9 external interrupt sources connected to nEFIQ and nEIR[7:0] pins

and 19 internal interrupt sources, including the serial ports and the flexible timer channels.

-The interrupt controller simplifies interrupt priority control with a choice of eight interrupt levels for

each source.

-The interrupt controller assigns a unique interrupt number to each source to permit rapid branching

to the appropriate routine.

ML670100

External Memory Controller

The external memory controller generates control signals for accessing external memory (ROM, SRAM,

DRAM, etc.), and other devices with address in the external memory space.

-Support for direct connection of ROM, SRAM and I/O devices

- Strobe signal outputs for a variety of memory and I/O devices

-Support for direct connection of DRAM

- Multiplexed row and column addresses

- Random access and high-speed paged modes

- Programmable wait cycle insertion

-Memory space divided into four banks

- Two banks for ROM, SRAM and I/O devices

- Two banks for DRAM

- Address space of 16 megabytes for each bank

- Separate data bus width (8 or 16 bits), wait cycle, and off time setting for each bank

-Single-stage store buffer permitting internal access during a wait cycle to external memory or device

-Arbitration of external bus requests from external devices

/ 279

Loading...

Loading...