Page 1

QN902x

User Manual of QN902x

Rev. 1.3 — 05 November 2018

User Manual

Document information

Info

Content

Keywords

User manual, MCU, Register

Abstract

This document is a user manual of QN902x SoC.

Page 2

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

2 of 128

Contact information

For more information, please visit: http://www.nxp.com

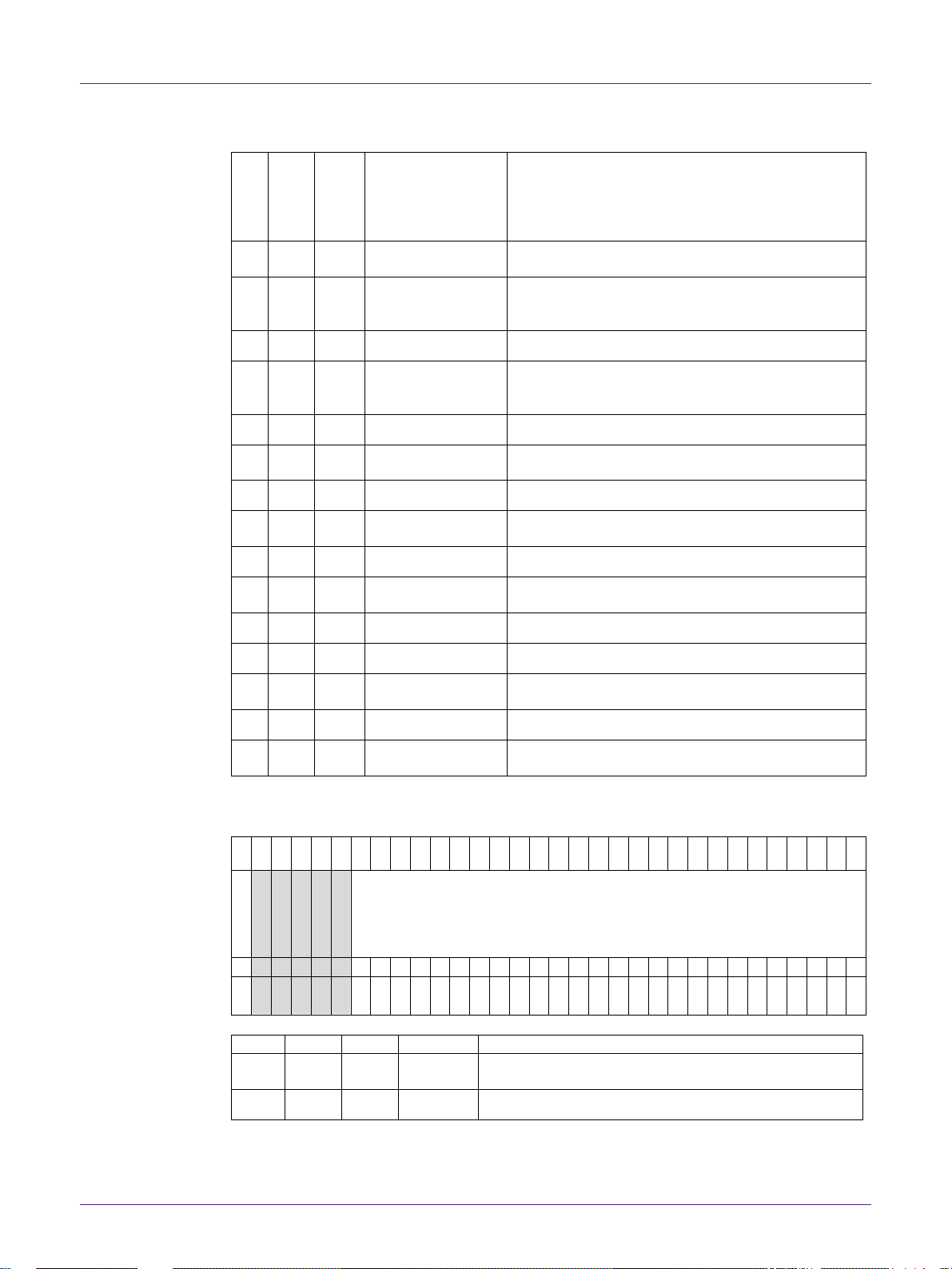

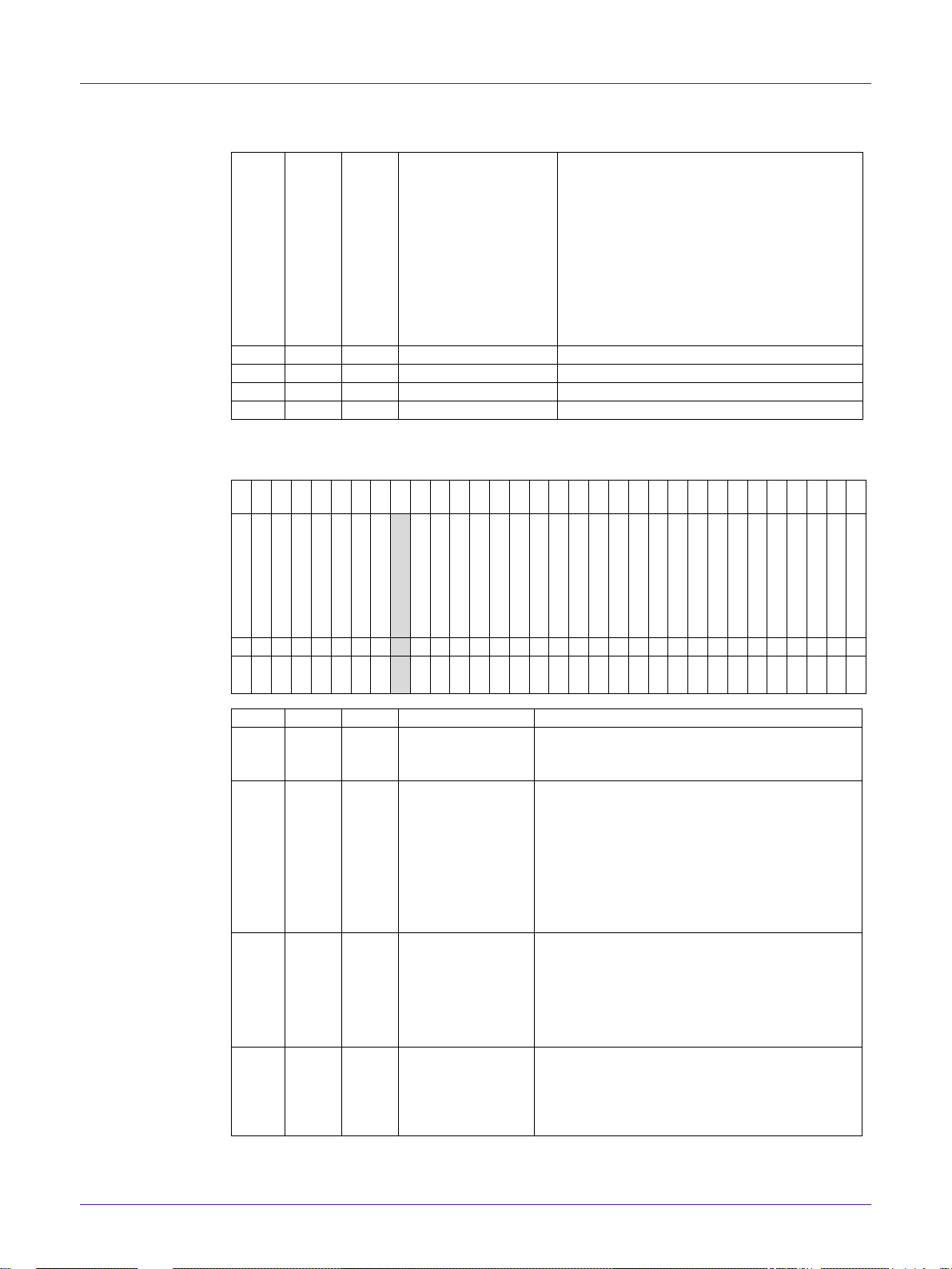

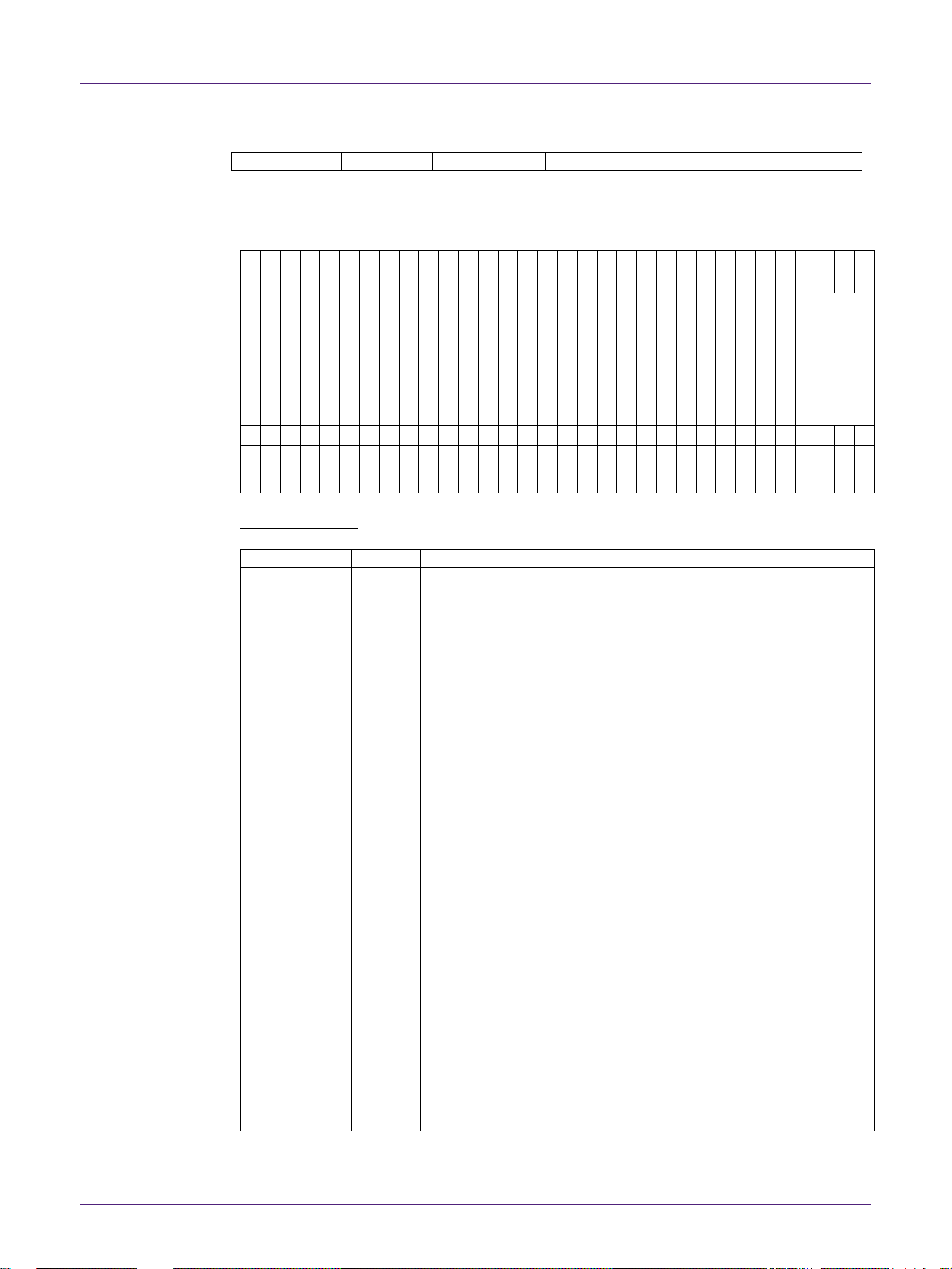

Revision history

Rev

Date

Description

1.0

20150715

First version.

1.1

20160408

Updated some register description.

1.2

20180423

Updated Section 2.3, “Memory Organization”.

1.3

20181105

Added description on fast boot function. Removed description on QN902x temperature sensor.

Page 3

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

3 of 128

1. Introduction

This document is a user manual for the QN902x SoC. It describes in detail the principle

and register information of the main components of the QN902x. The audience of this

document are technical and experienced engineers in design and development area

based on SoC.

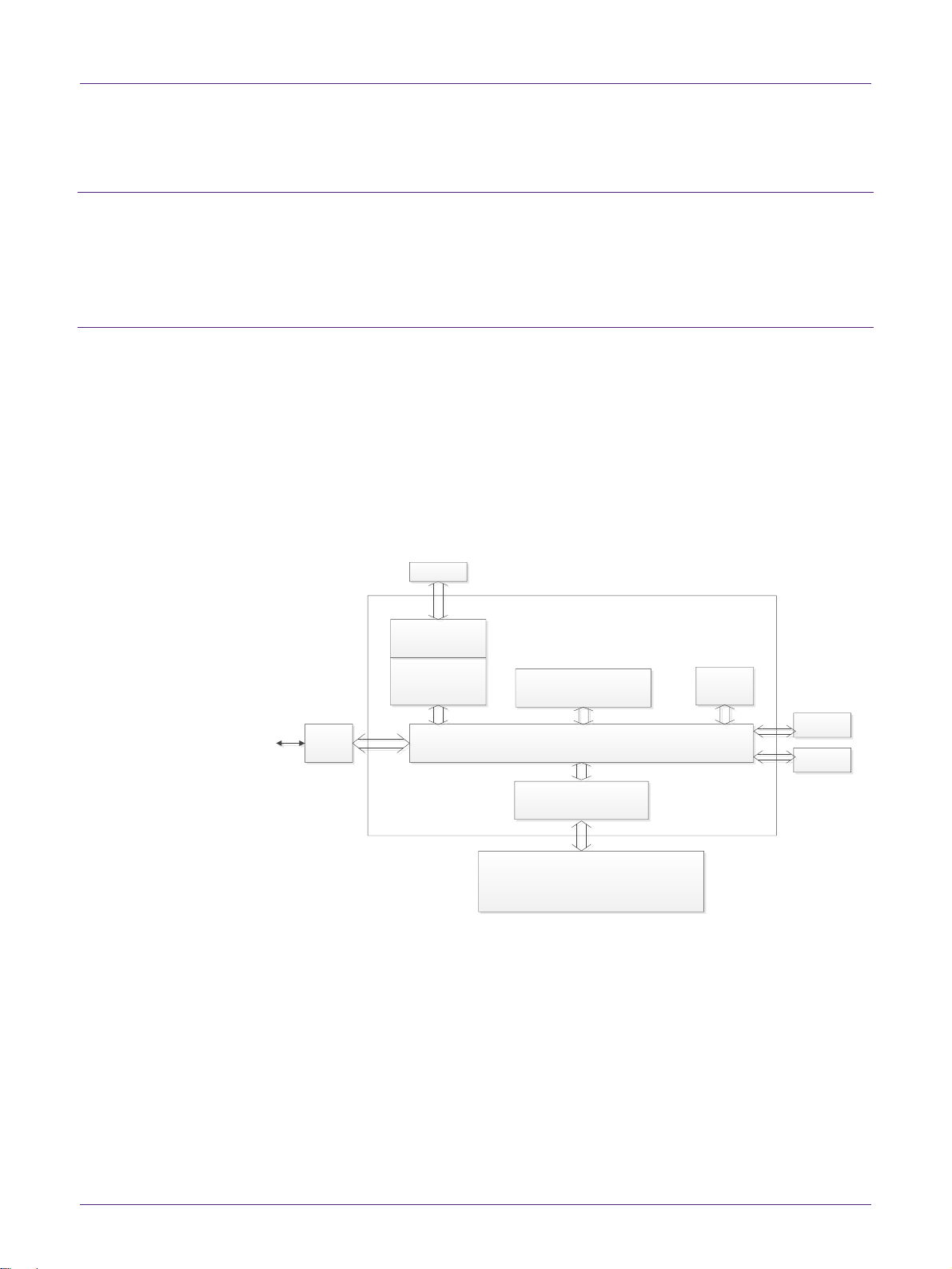

2. MCU Subsystem

The MCU system includes:

32-bit ARM Cortex-M0 MCU

AHB-Lite bus system

64kB system memory

Clock, reset and power management units

Two-wire debug interface (SWD)

24-bit system tick timer

Block diagram is shown as below figure.

ARM

CORTEX-M0

AHB-LITE BUS

DEBUG

INTERFACE

SWD

System Memory

64kB

ROM

AHB to APB BRIDGE

GPIO

ADC

AES-128

Periperals

MCU

Figure 1 QN902x MCU subsystem block diagram

2.1 MCU

The CPU core is a 32-bit ARM Cortex-M0 core, which offers significant benefits to

application development including:

Simple and easy-to-use programmer’s model

Highly efficient ultra-low power operation

Excellent code density

Page 4

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

4 of 128

Deterministic, high-performance interrupt handling of 32 external interrupt

inputs

The processor has been extensively optimized for low power, and delivers exceptional

power efficiency through its efficient instruction set, providing high-end processing

hardware including a single-cycle multiplier. The exceptional low power, small gate count

and code footprint of the processor makes it ideal for ultra-low power MCU and mixed

signal applications, delivering 32-bit performance and efficiency.

2.1.1 Nested Vectored Interrupt Controller (NVIC)

NVIC of QN902x supports 32 external interrupt inputs, each with four levels of priority. It

also supports both, level-sensitive and edge-sensitive interrupt lines.

External interrupt signals are connected to the NVIC, and the NVIC prioritizes the

interrupts. Software can set the priority of each interrupt. The NVIC and the Cortex-M0

processor core are closely coupled, providing low latency interrupt processing and

efficient processing of late arriving interrupts.

The Wake-up Interrupt Controller (WIC) supports ultra-low power sleep mode. This

enables the processor and NVIC to be put into a very low-power sleep mode leaving the

WIC to identify and prioritize the interrupts. The processor fully implements the WaitFor-Interrupt (WFI), Wait For Event (WFE) and the send Event (SEV) instructions. In

addition, the processor also supports the use of SLEEPONEXIT, which causes the

processor core to enter sleep mode when it returns from an exception handler in Thread

mode.

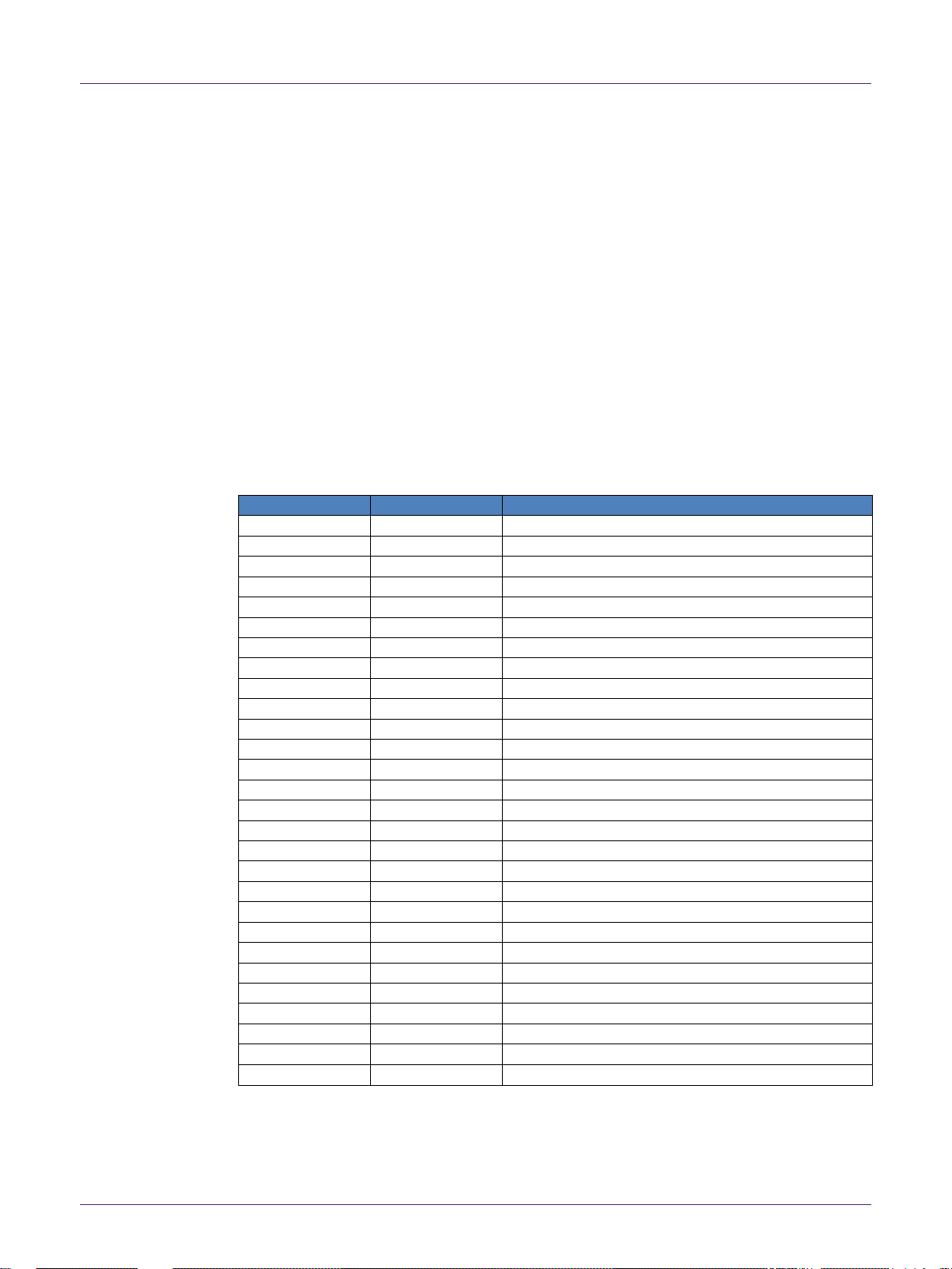

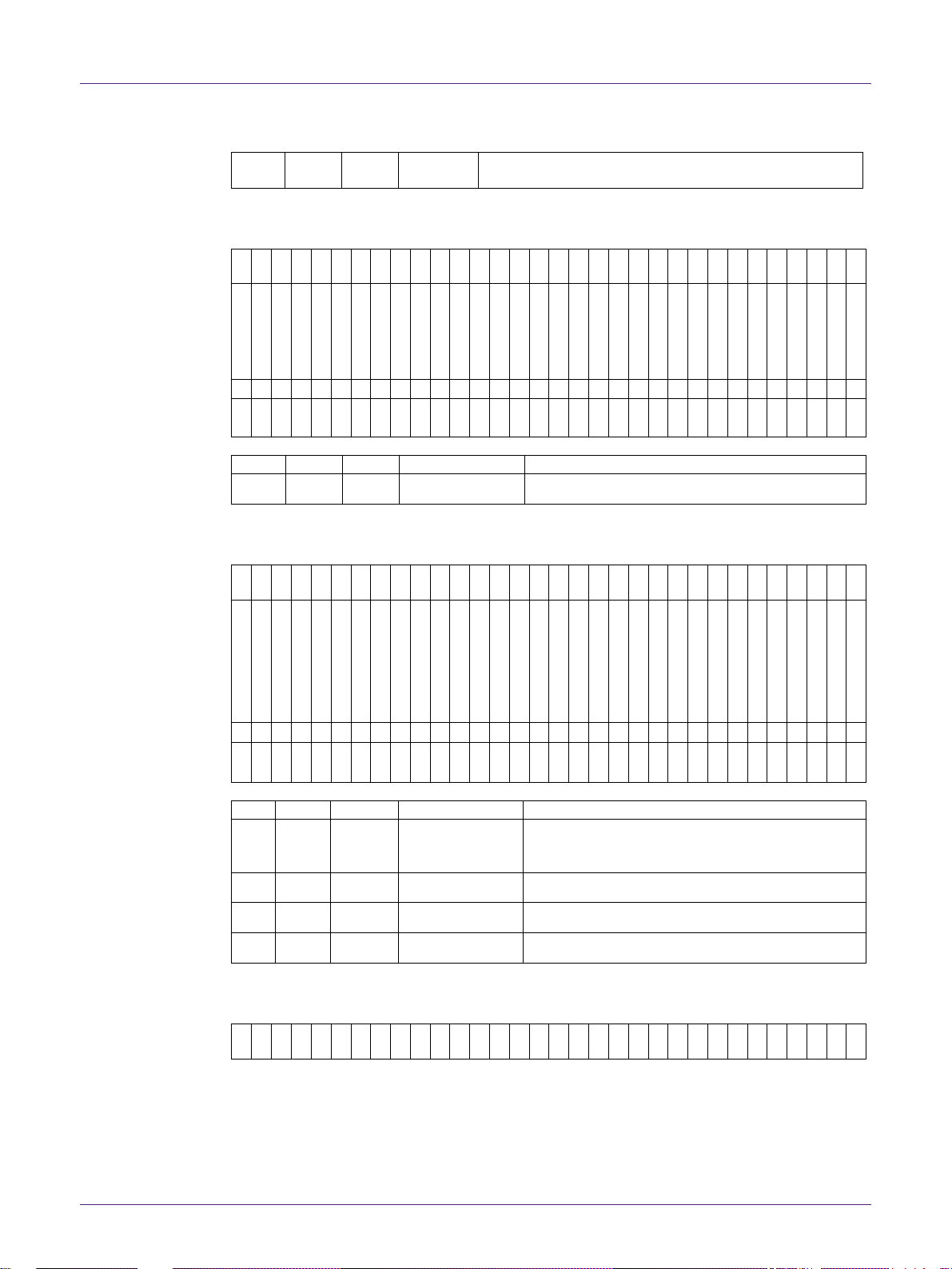

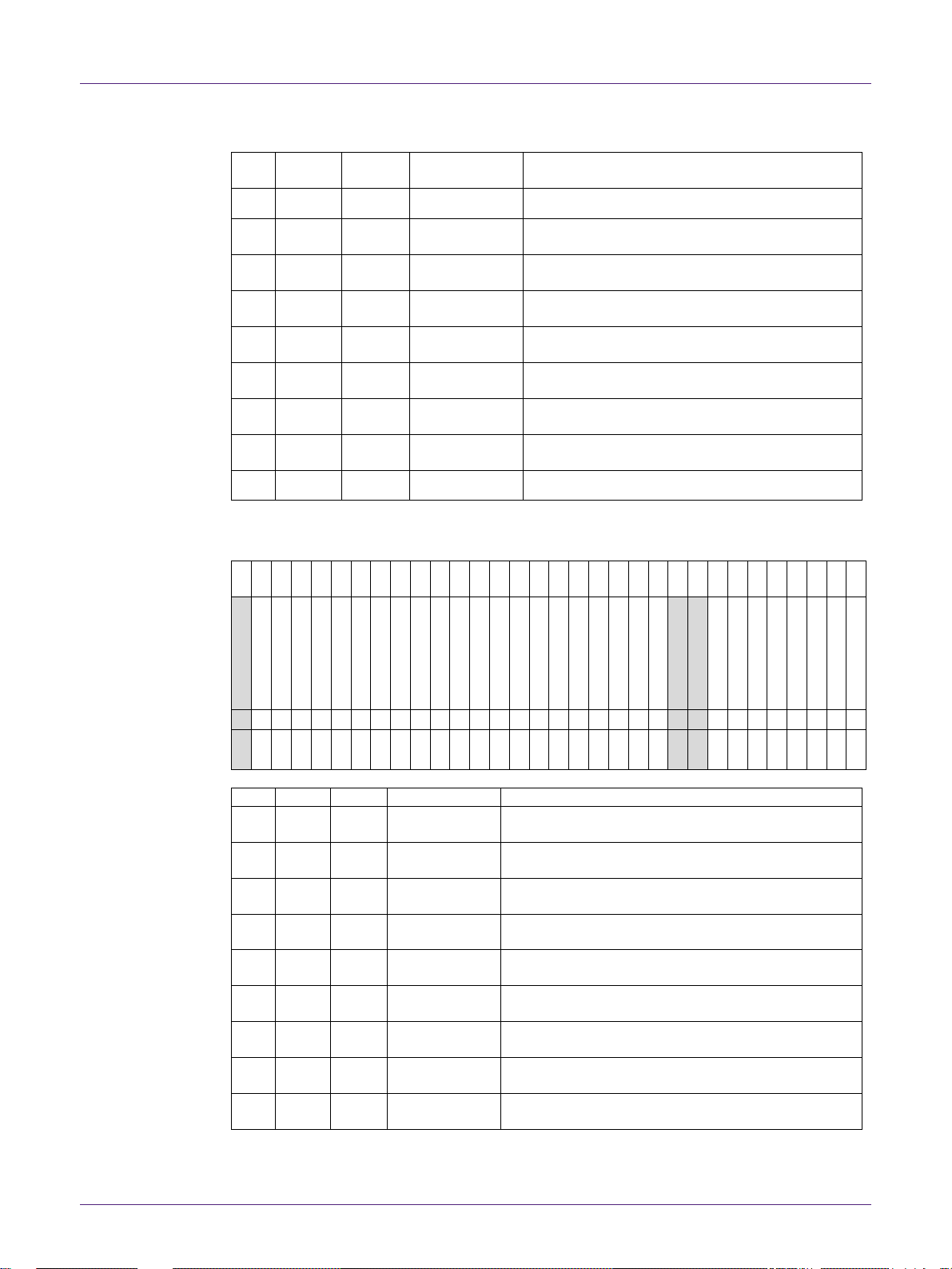

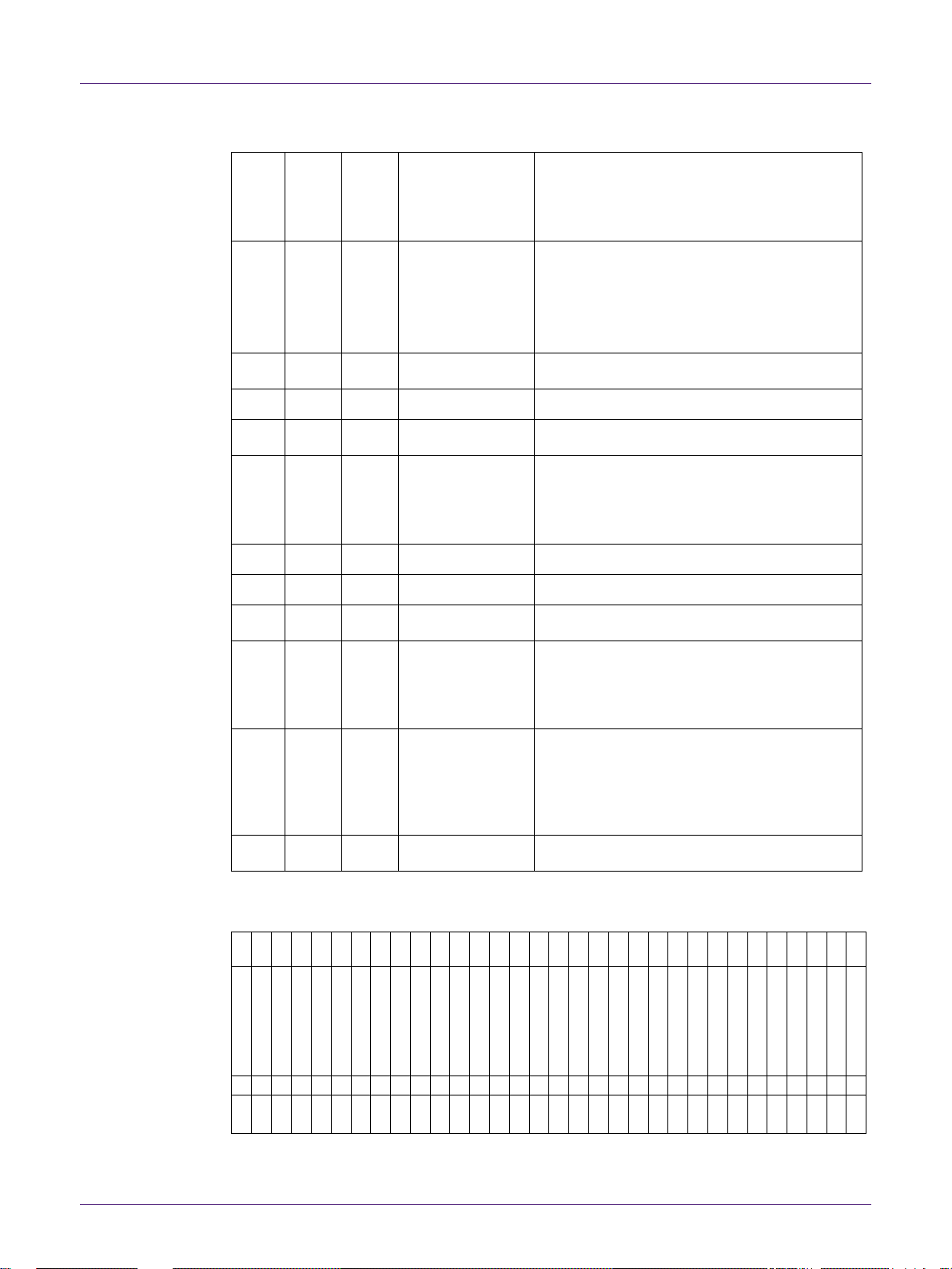

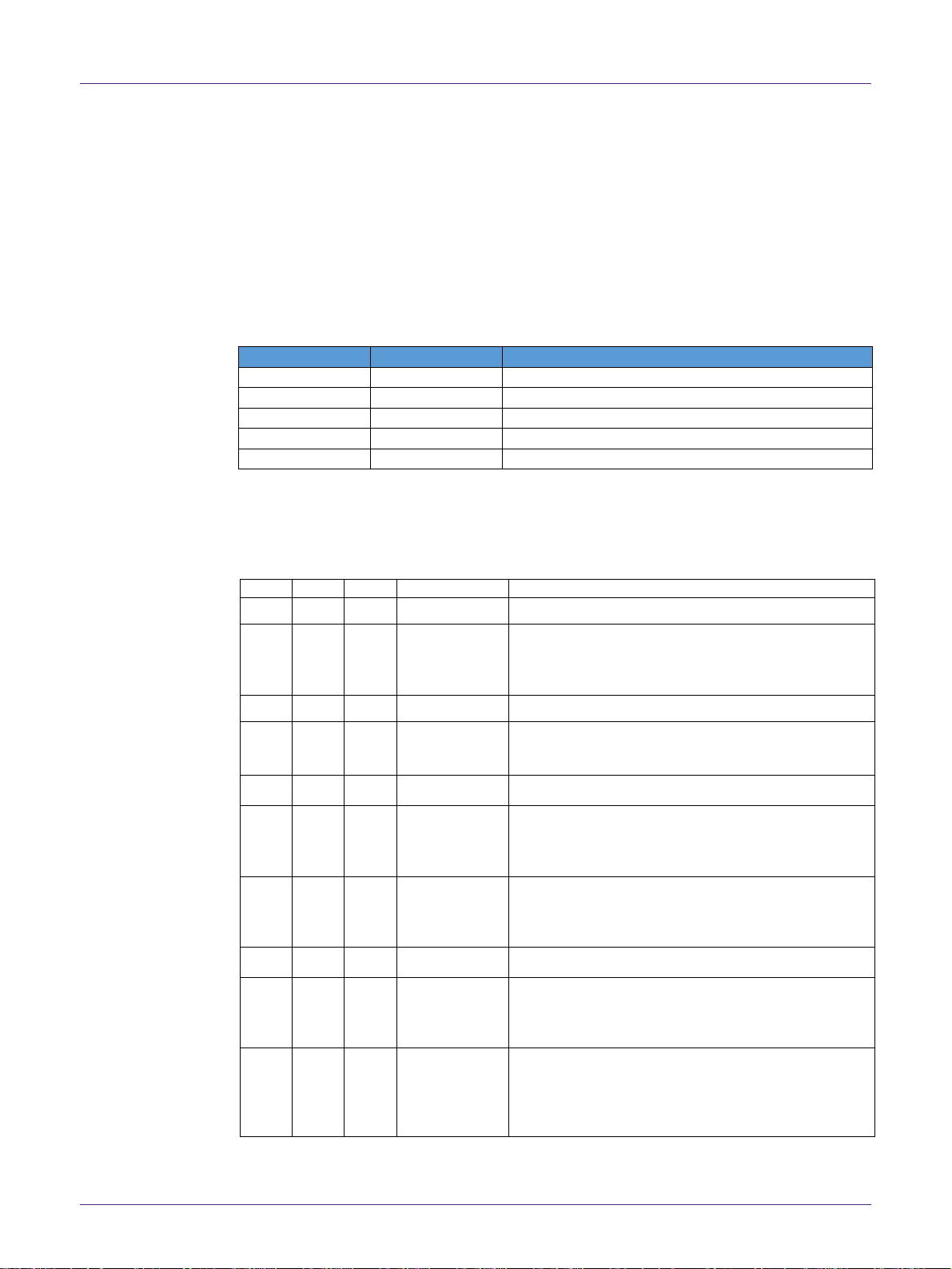

Table 1 Interrupt Sources

IRQ#

Source

IRQ#

Source

0

GPIO

16

SPI1_TX

1

ACMP0

17

SPI1_RX

2

ACMP1

18

I2C 3 BLE_Interrupt

19

TIMER0

4

RTC_Capture

20

TIMER1

5

OSC_EN

21

TIMER2

6

RTC Timeout

22

TIMER3

7

ADC

23

WatchDog

8

DMA

24

PWM0

9

ANT_RX

25

PWM1

10

UART0_TX

26

Calibration

11

UART0_RX

27

Proprietary_RX

12

SPI0_TX

28

Proprietary_TX

13

SPI0_RX

29

BLE_RX

14

UART1_TX

30

BLE_TX

15

UART1_RX

31

BLE_FRQ_JUMP

Page 5

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

5 of 128

2.1.2 Serial Wire Debug (SWD) interface

The QN902X supports Serial Wire Debug Port (SW-DP) interface. The debug pins (SWCLK,

SWDIO) share the pins with normal function pins, with debug being the default state.

In addition, it supports 4 hardware breakpoints and 2 watchpoints. The basic debug

functionality includes processor halt, single-step, processor core register access, Reset

and HardFault Vector Catch, unlimited software breakpoints, and full system memory and

register access.

For security purpose, the debug interface cannot read locked instruction memory content.

It can only read the unlocked instruction space. The security is controlled by the user.

2.1.3 System Timer (SYSTICK)

SYSTICK provides a simple, 24-bit clear-on-wire, decrementing, wrap-on-zero counter

with a flexible control mechanism, which is intended to generate a dedicated SYSTICK

exception at a fixed time interval.

2.2 System Bus

The QN902X contains an AHB-Lite bus system to allow bus masters to access the memory

mapped address space. A multilayer AHB bus matrix connects the 2 master bus interfaces

to the AHB slaves. The bus matrix allows several AHB slaves to be accessed

simultaneously. The 2 AHB bus master are: MCU and DMA.

An AHB-to-APB bridge is connected to the AHB bus matrix, to access the low speed

peripherals. The APB can run on lower clock than AHB for low power consumption.

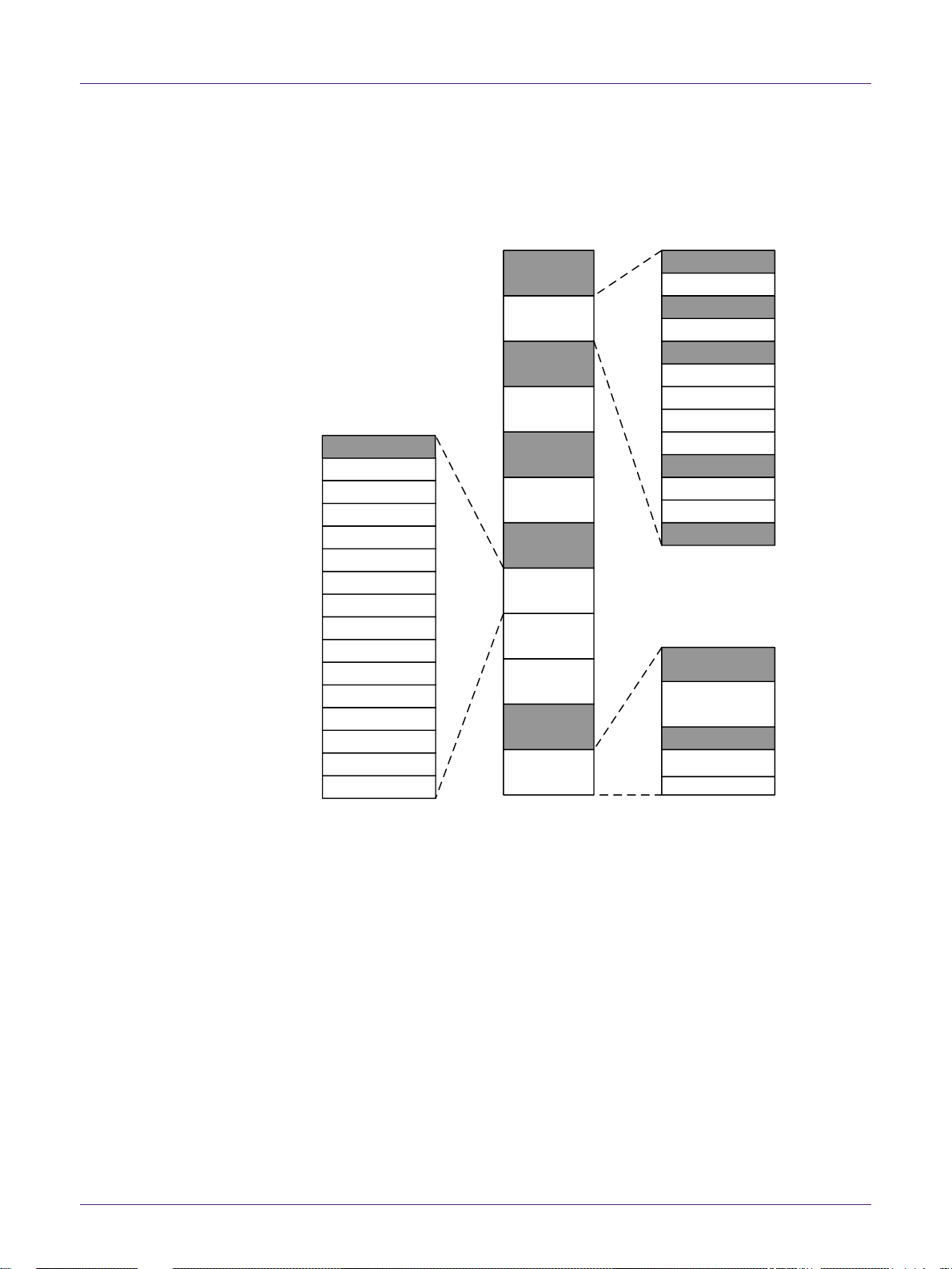

2.3 Memory Organization

The memory architecture is a ROM + Flash + RAM architecture, with the ROM storing the

BLE stack, the Flash being used for application program and data storage. During the boot,

the program is loaded from the Flash to the RAM. This allows execution with system clock

up to 32MHz and reduction of the active current consumption compared to the execution

from the Flash.

The QN902x supports 96 kB of ROM and 128 kB of flash (QN9020/1). The ROM space is

not accessible to users. The system RAM memory is 64kB in size for application program

and data, which consists of 8 blocks, addresses for them are allocated as below.

- Memory 0 : 10000000 ~ 10001fff

- Memory 1 : 10002000 ~ 10003fff

- Memory 2 : 10004000 ~ 10005fff

- Memory 3 : 10006000 ~ 10007fff

- Memory 4 : 10008000 ~ 10009fff

- Memory 5 : 1000a000 ~ 1000bfff

- Memory 6 : 1000c000 ~ 1000dfff

- Memory 7 : 1000e000 ~ 1000ffff

Page 6

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

6 of 128

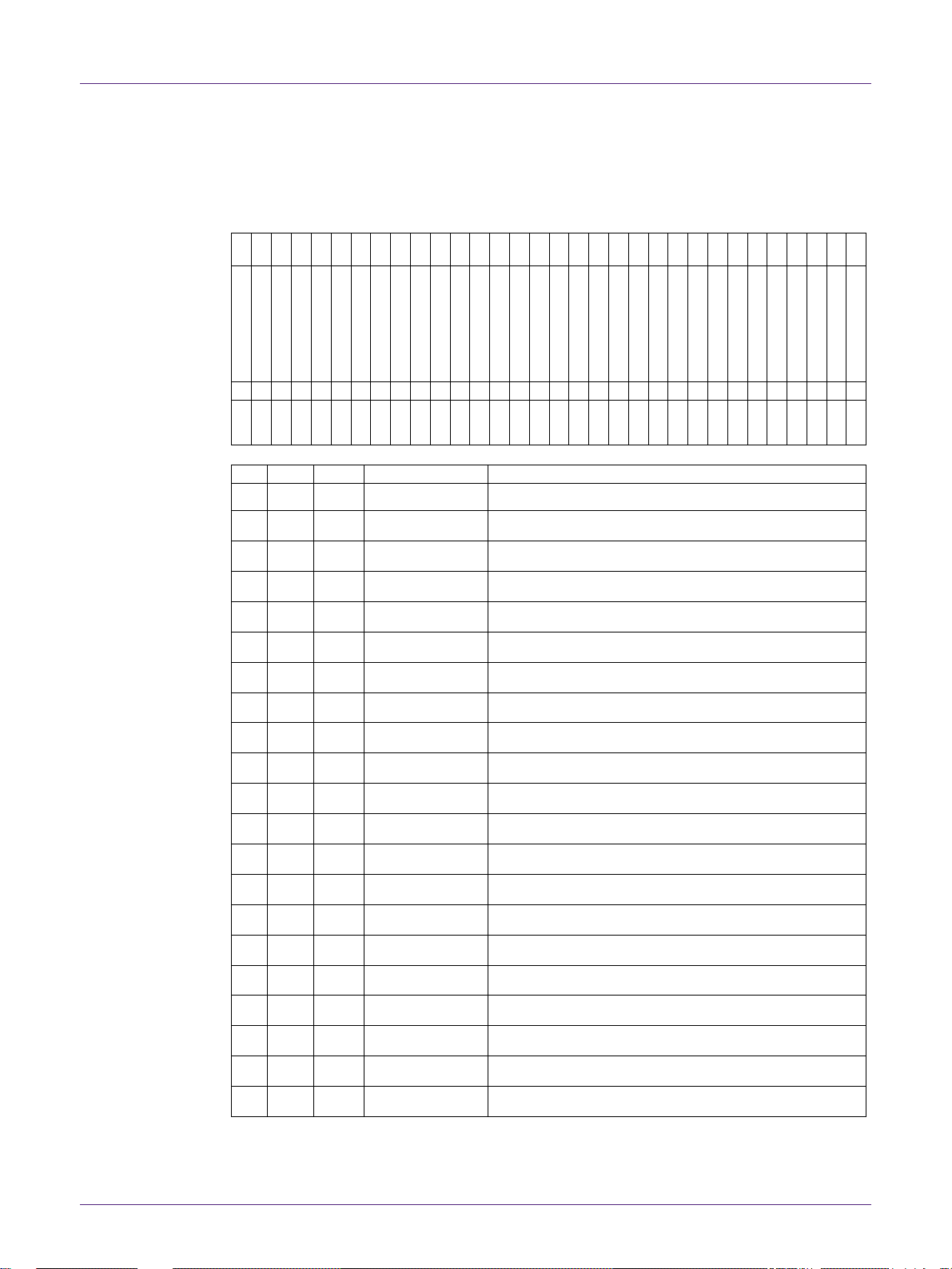

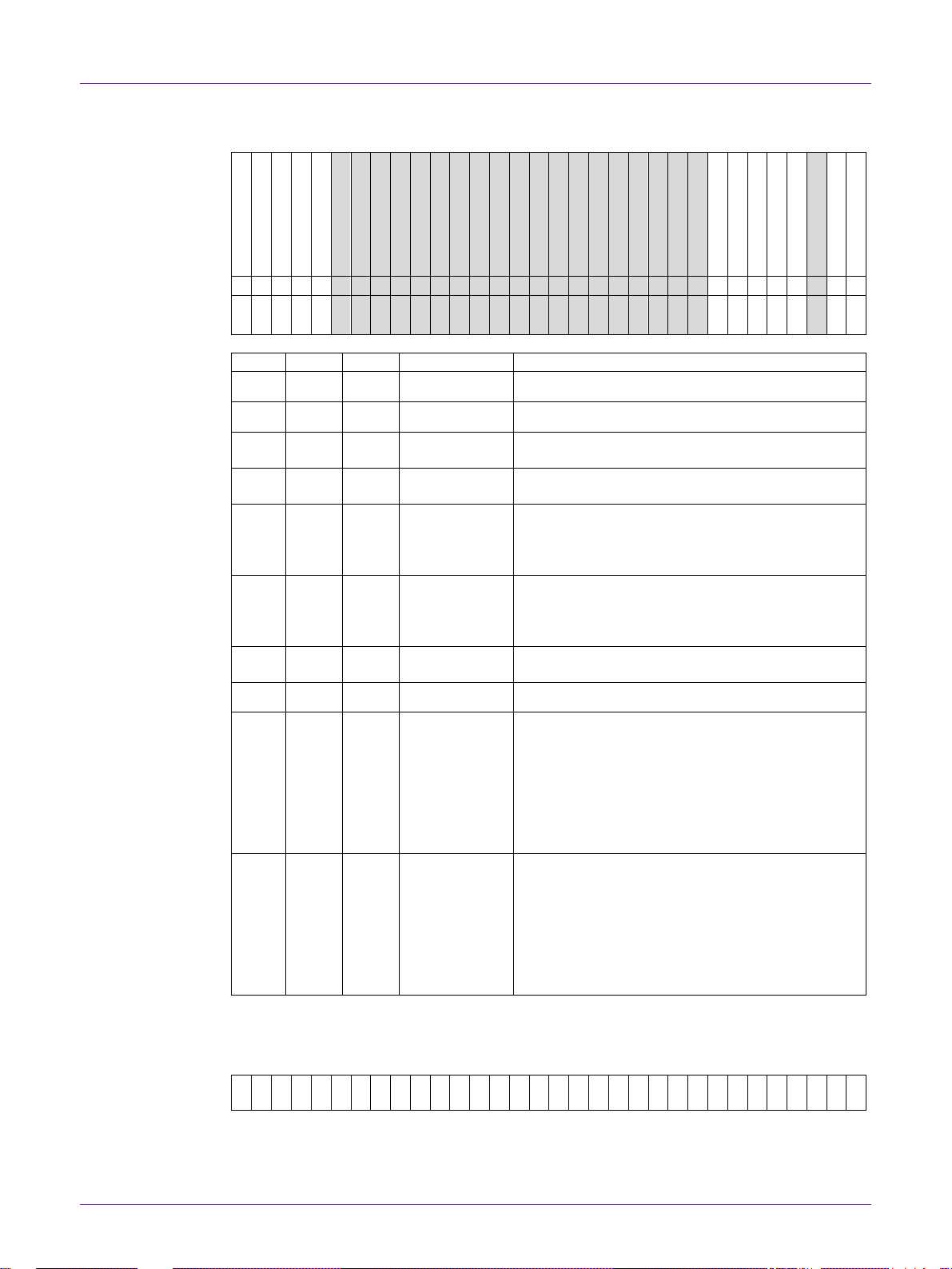

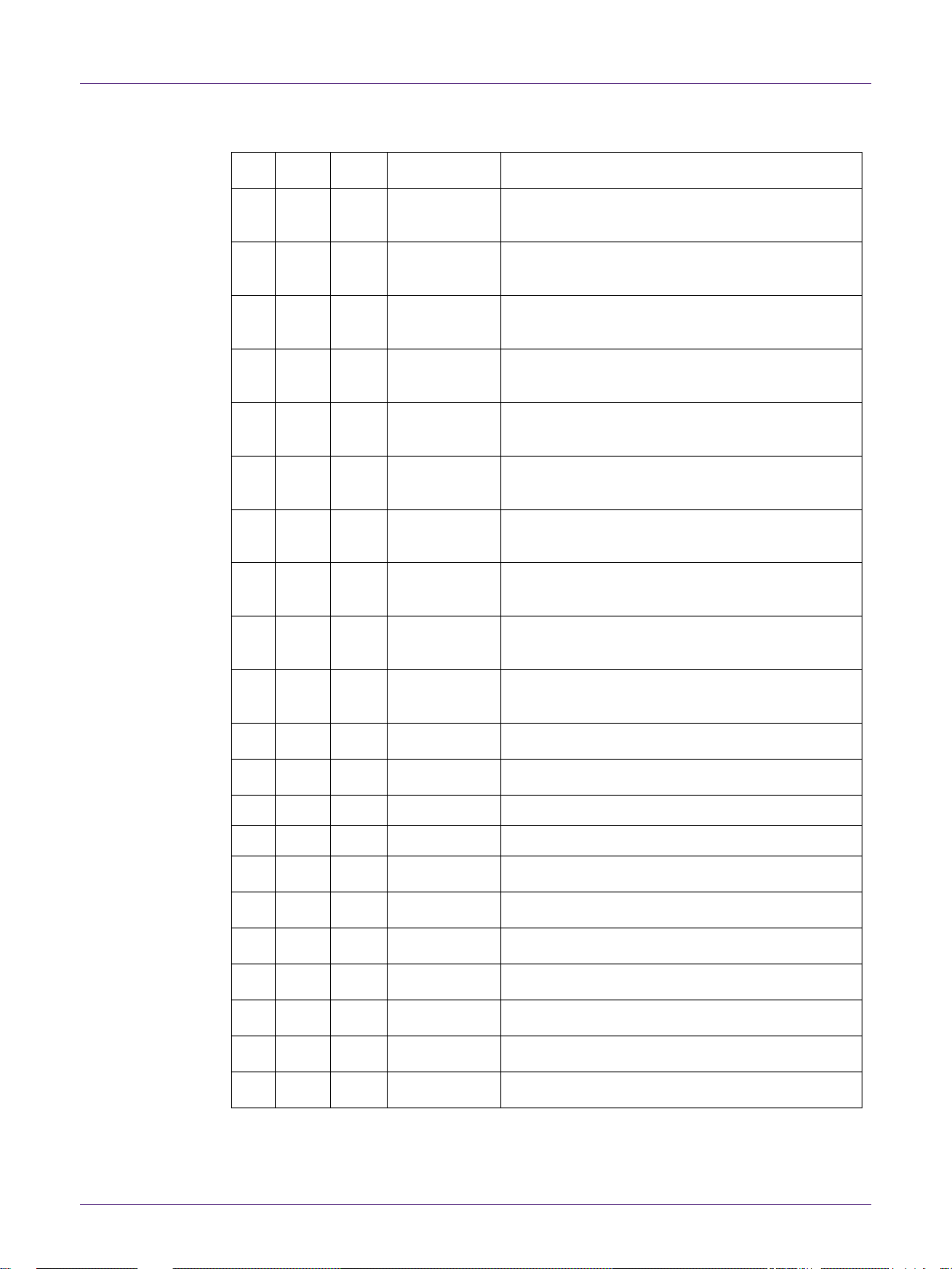

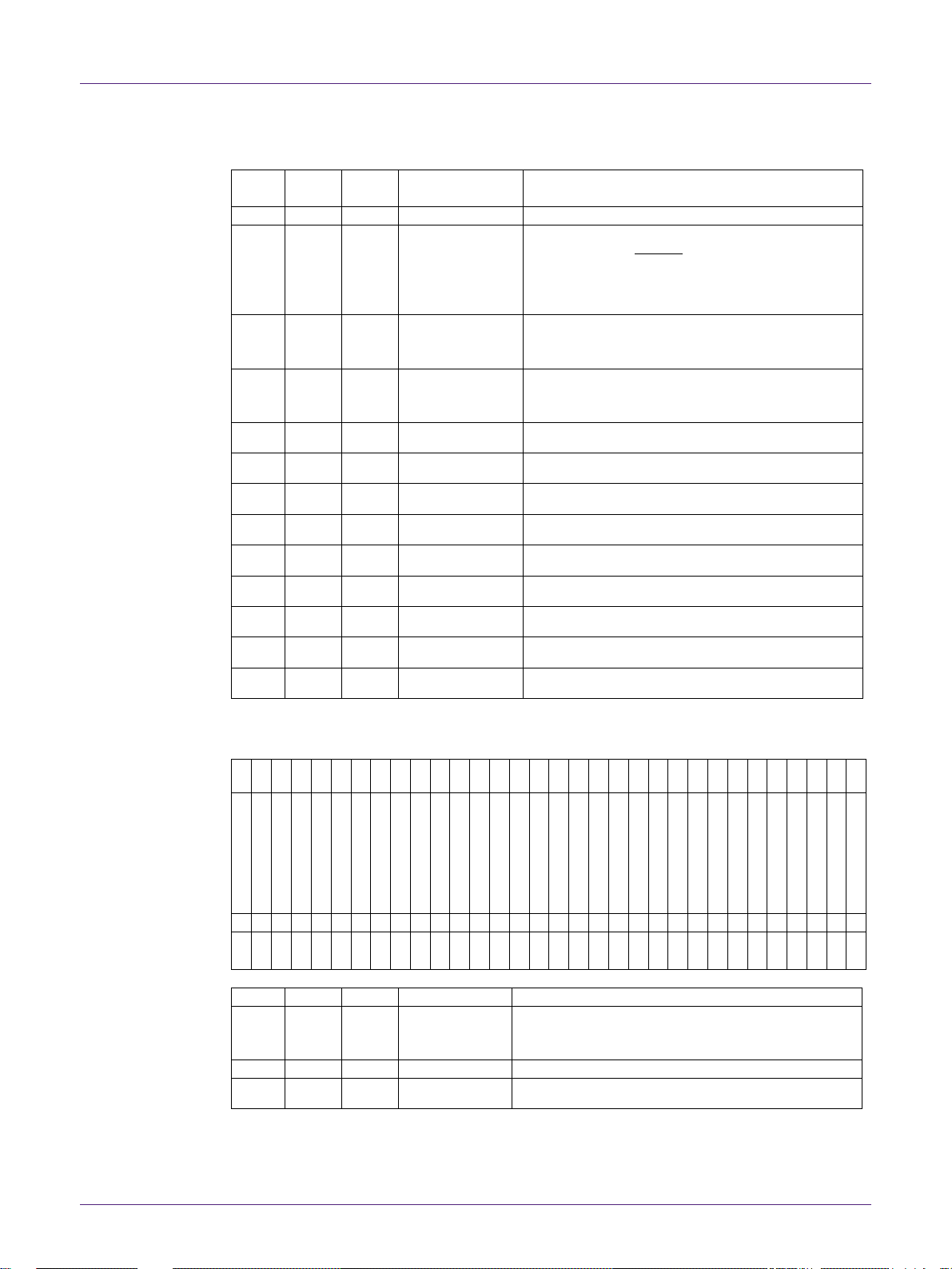

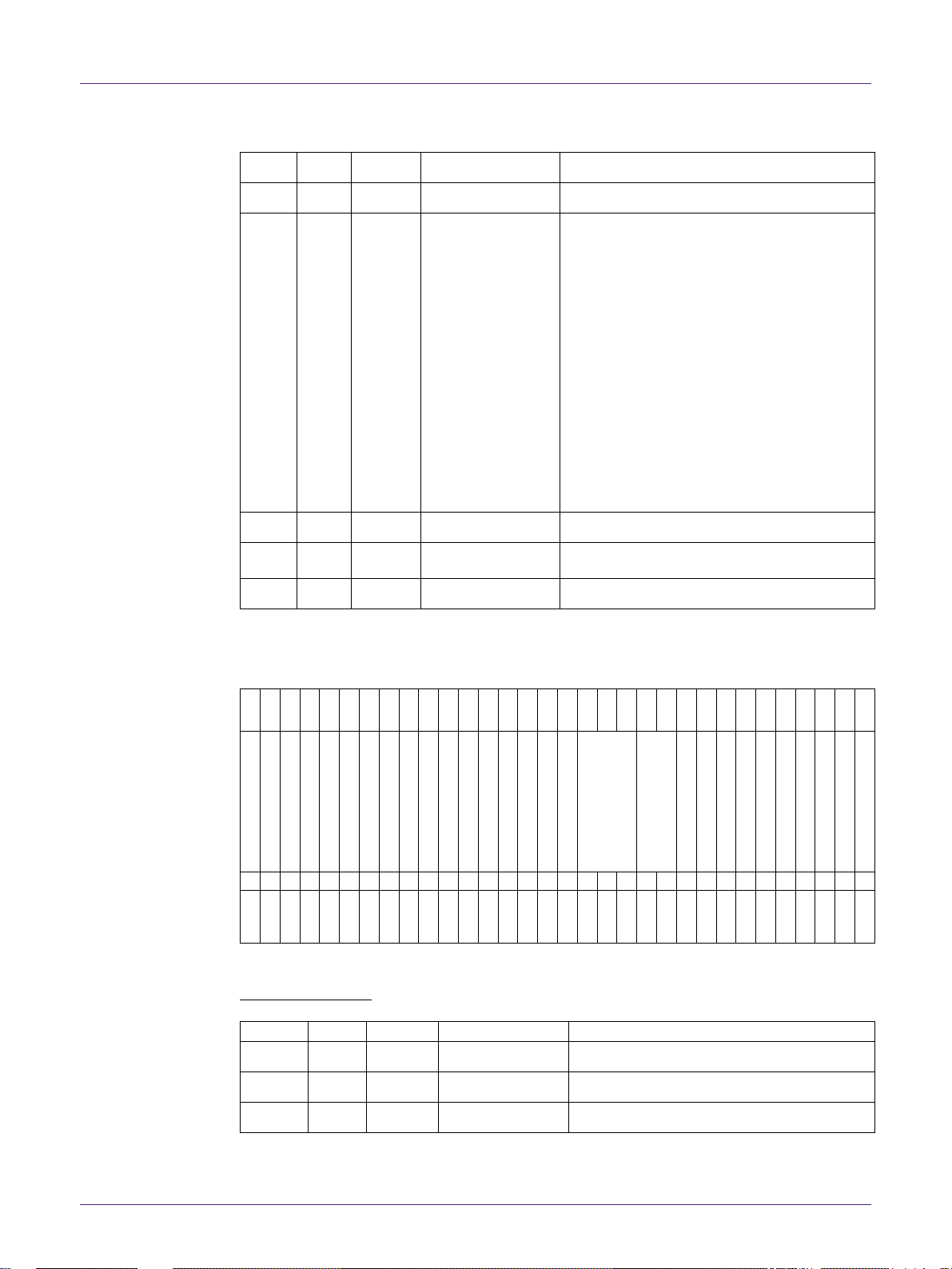

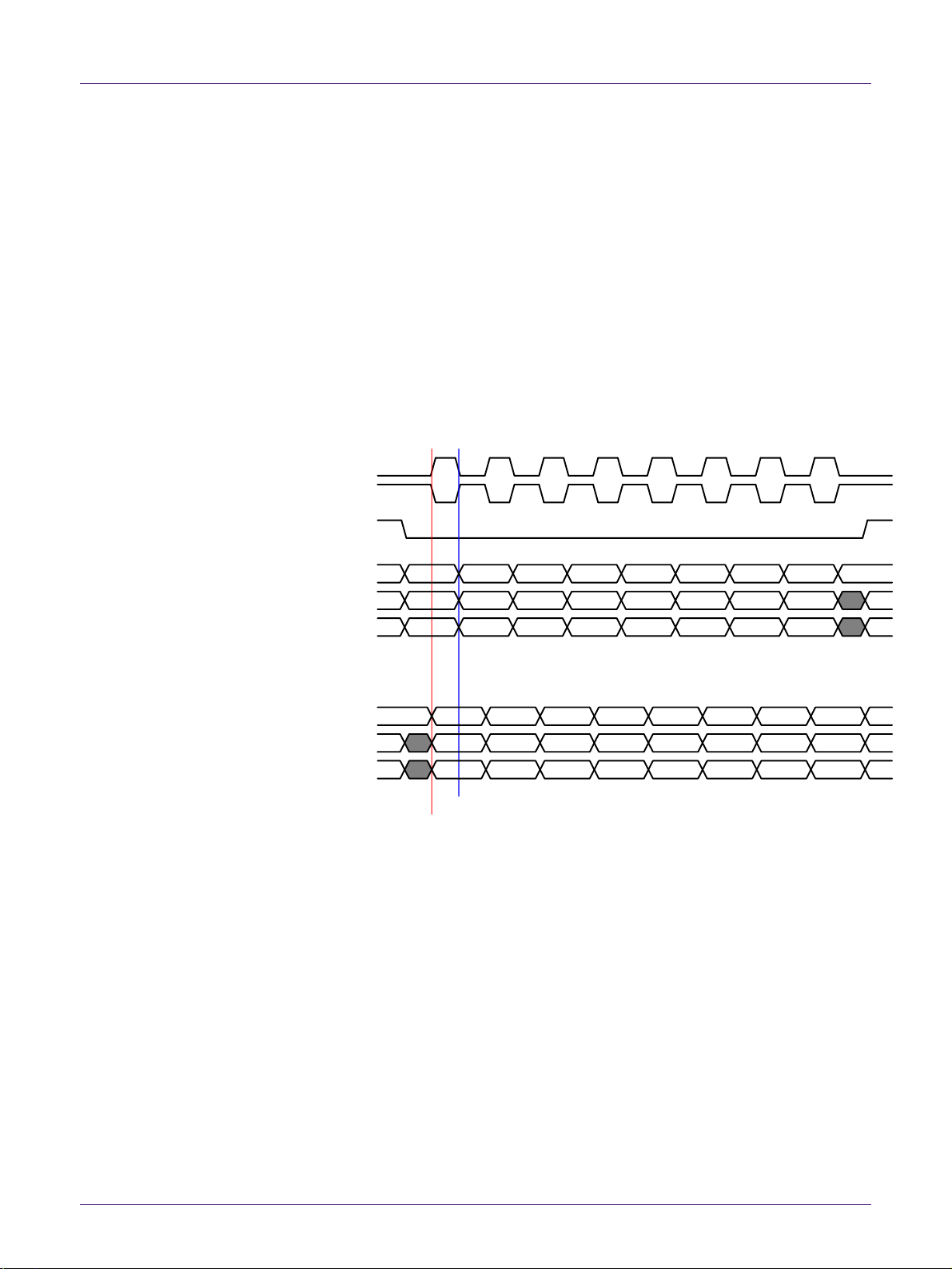

The system memory (ROM + SRAM + Flash), all registers and external devices are

allocated in the same memory map within 4GB, ranging from 0x00000000 to 0xFFFFFFFF,

which is shown in the following Figure 2. The system memory security is ensured with a

user controllable protection scheme, preventing un-authorized read out.

Code

0x00000000

0x1FFFFFFF

BLE Processor

Memory

0x2F000000

0x2FFFFFFF

Serial FLASH

0x30000000

0x3FFFFFFF

APB peripherals

0x40000000

0x400EFFFF

0x400F0000

0x4FFFFFFF

GPIO

0x50000000

0x50003FFF

0x50004000

0x50007FFF

ADC

0x50010000

0x50013FFF

0x50014000

0xDFFFFFFF

Private peripheral

0xE0000000

0xEFFFFFFF

0xF0000000

0xFFFFFFFF

ROM

(96 KB)

0x01000000

0x01018000

System SRAM

0x10000000

0x1000FFFF

System Registers

0x40000000

Watch Dog Timer

0x40001000

Timer0

0x40002000

Timer1

0x40003000

Timer2

0x40004000

Timer3

0x40005000

RTC

0x40006000

USART0

0x40007000

I2C

0x40008000

DMA

0x40009000

USART1

0x4000A000

BLE Physical DataPath

0x4000B000

PWM

0x4000C000

0xE0000000

Watchpoint unit

0xE0001000

Breakpoint unit

0xE0002000

0xE0003000

Auxiliary Control

Registers

0xE000E000

System Timer

0xE000E010

NVIC

0xE000E100

System Control Block

0xE000ED00

0xE000ED90

Debug Control Registers

0xE000EDF0

0xE000EF00

ROM Table

0xE00FF000

0xE0100000

0x20000000

0x2EFFFFFF

BootLoader

0x00000000

Calibration

Proprietary Interface

0x4000D000

0x4000E000

Figure 2 QN902X System Address Space

2.4 Reset Management Unit (RMU)

The RMU ensures correct reset operation. A correct reset sequence is needed to ensure

the safe startup. The RMU provides proper reset and startup, even in the case of error

situations such as power supply glitches or software crash.

Reset sources:

Power-on Reset (POR)

Brown-out Detection (BOD)

RESET pin

Watchdog timeout reset

Page 7

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

7 of 128

The Power-on Reset and Brown-out detectors provide power line monitoring with

exceptional low power consumption. The cause of the reset may be read by the

software from the registers.

The RST_CAUSE_SRC register indicates the reason for the last reset. The register should

be cleared after read at the startup. Otherwise the register may indicate multiple reset

causes at next startup. Note that it is possible to have multiple reset causes. For example,

an external reset and a watchdog reset may happen simultaneously. For more

information, please see RST_CAUSE_SRC (RCS) register description.

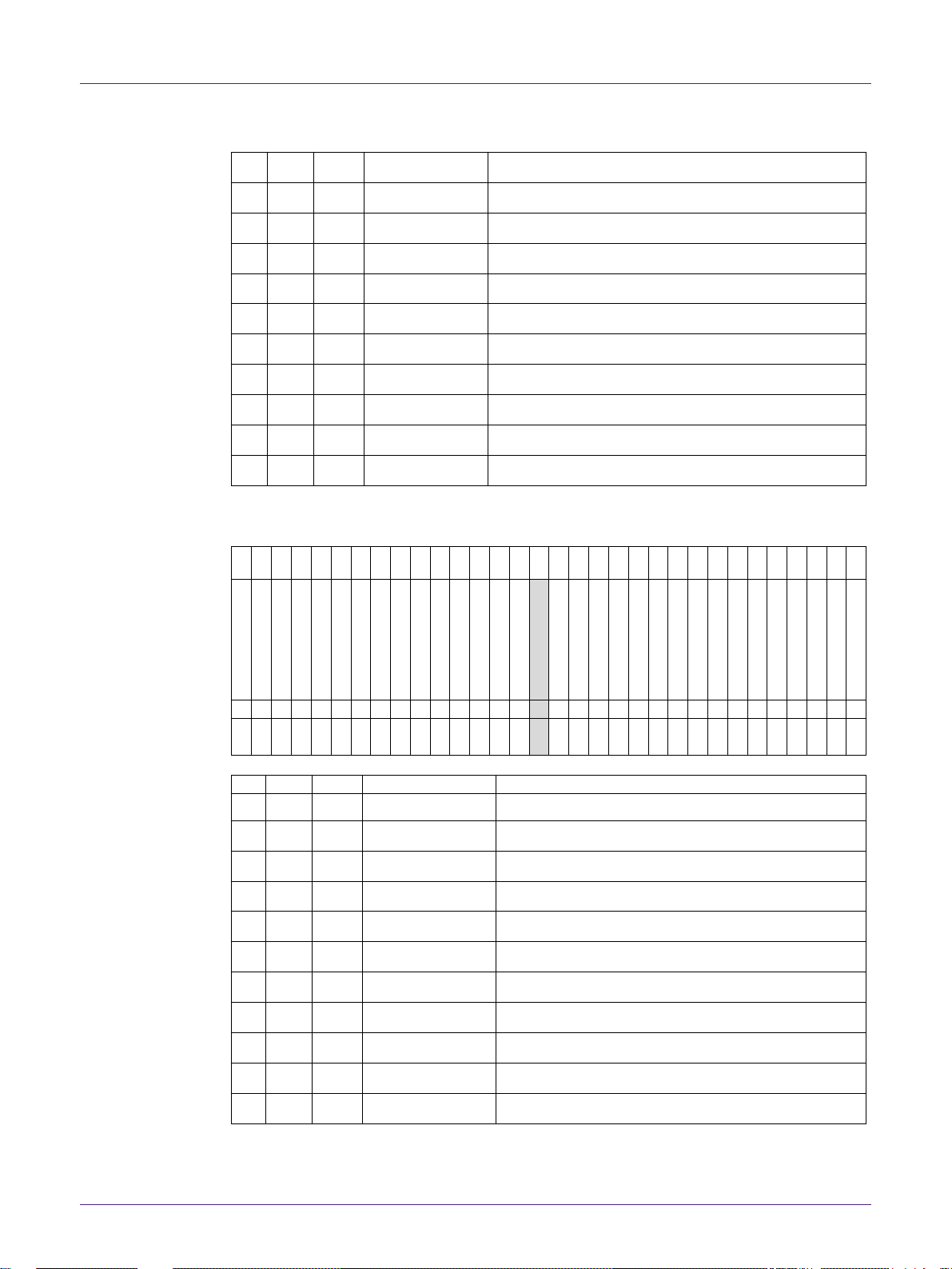

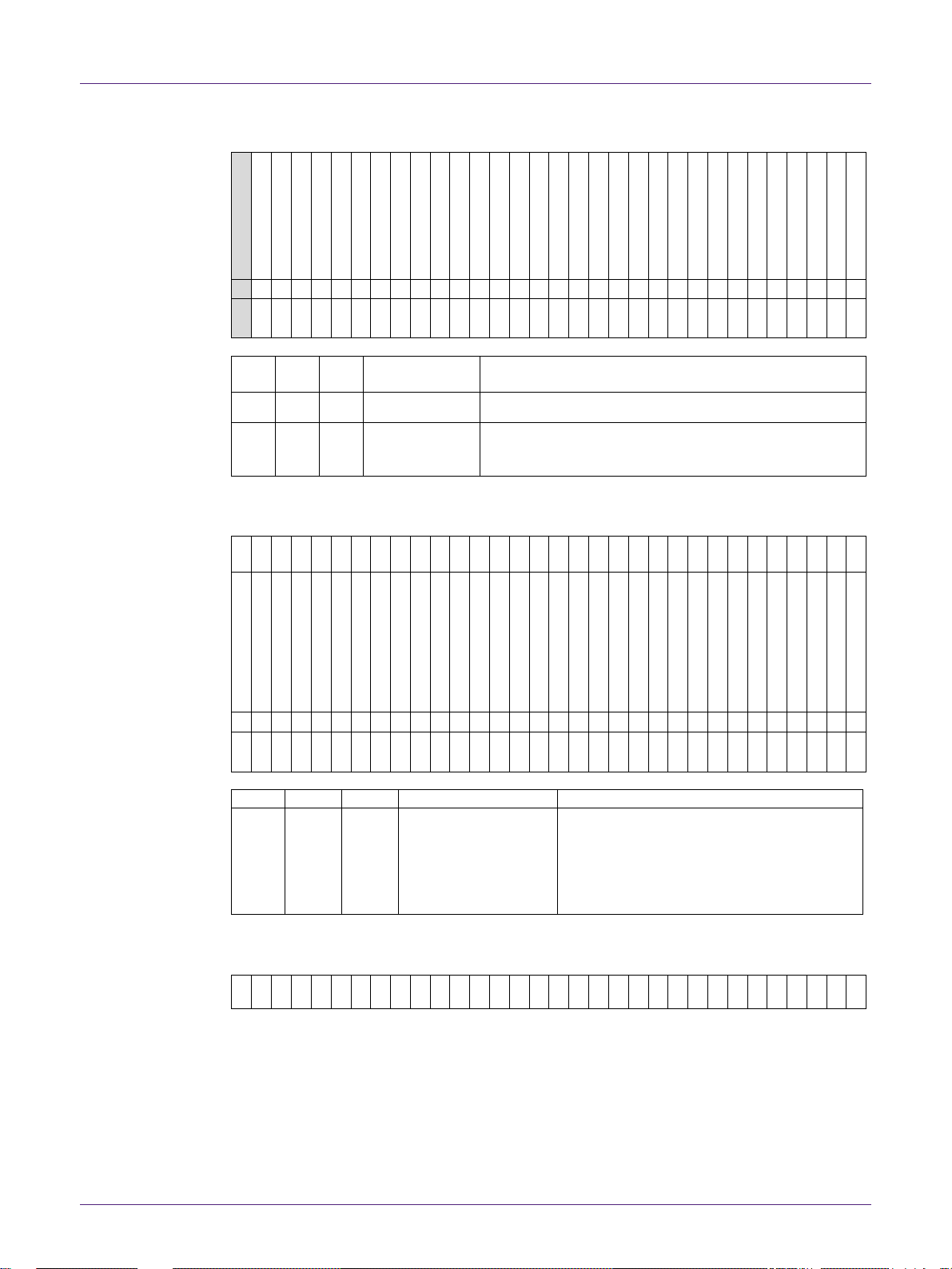

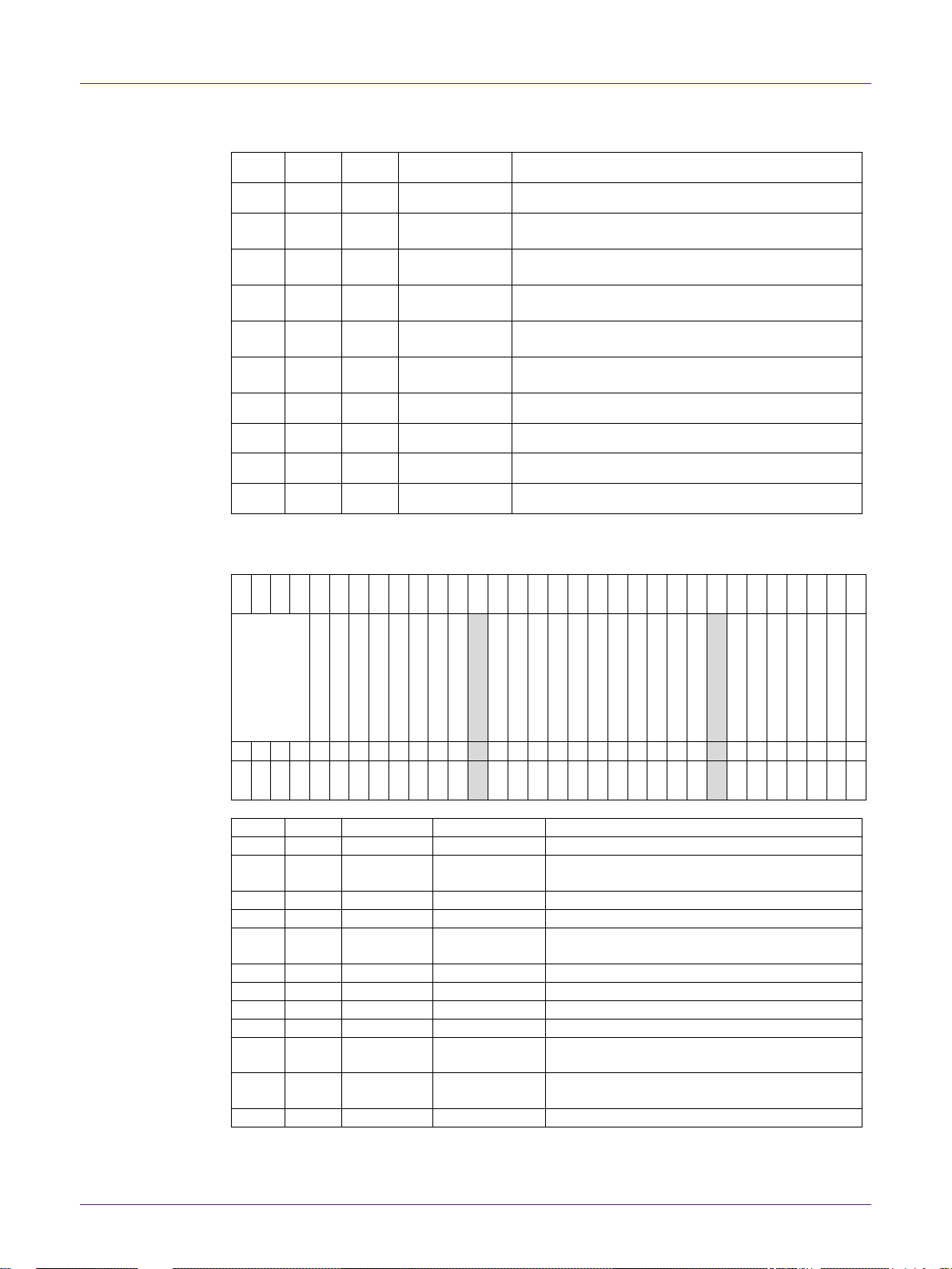

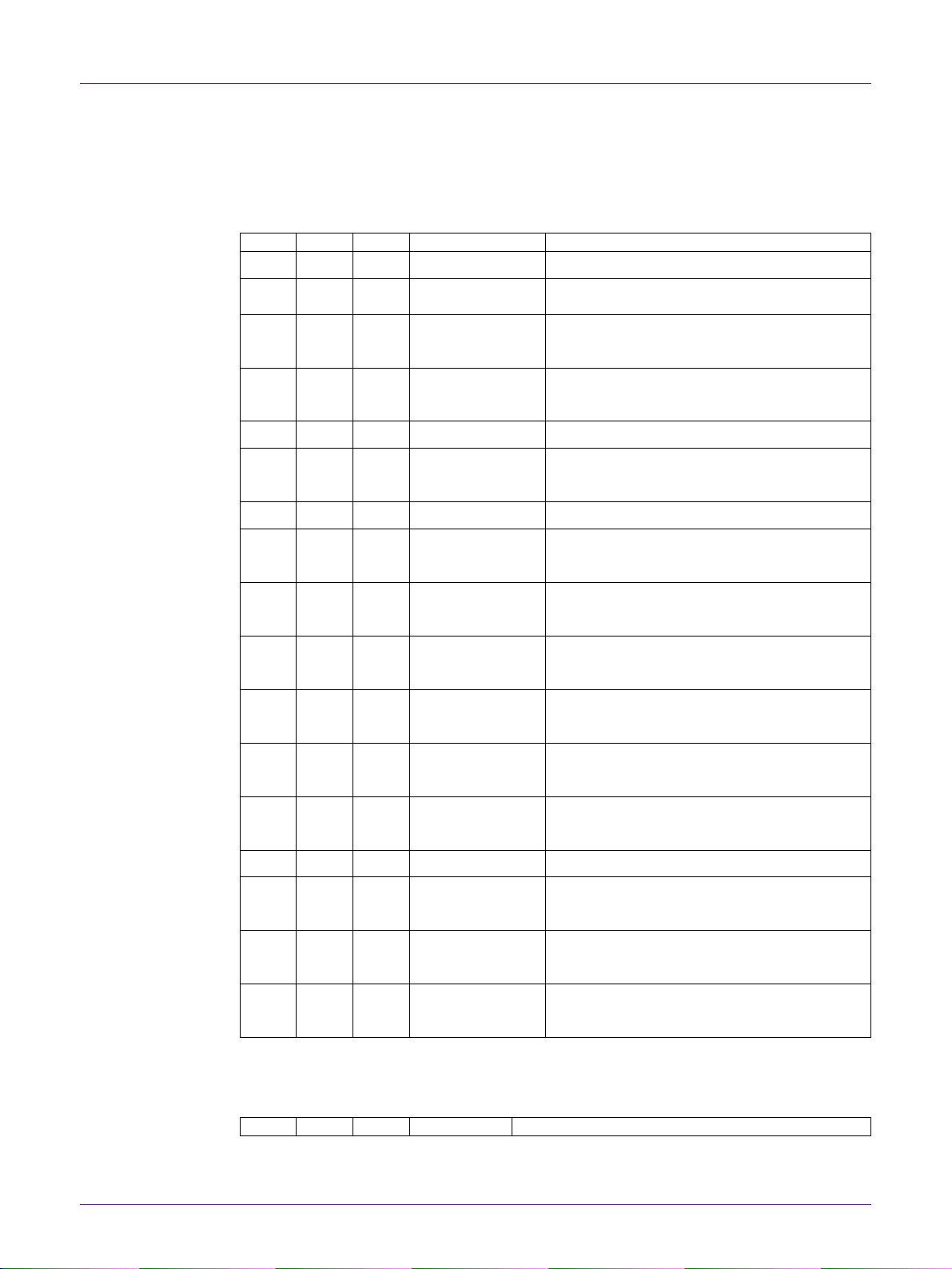

2.5 Register Description

2.5.1 Register Map

The MCU subsystem register base address is 0x40000000.

Table 2 Register Map

Offset

Name

Description

000h

CRSS

Enable clock gating and set block reset

004h

CRSC

Disable clock gating and clear block reset

008h

CMDCR

Set clock switch and clock divider

00Ch

STCR

Set systick timer STCALIB and STCLKEN

014h

SOCR

Reserved. Don’t change

020h

PMCR0

PIN Mux control 0

024h

PMCR1

PIN Mux control 1

028h

PMCR2

PIN Mux control 2

02Ch

PDCR

PAD Driver control

030h

PPCR0

PAD Pull-up and Pull-down control 0

034h

PPCR1

PAD Pull-up and Pull-down control 1

038h

RCS

Reset Cause source

03Ch

IOWCR

Controller IO as wakeup source

040h

BLESR

BLE status

080h

SMR

QN902X enter SCAN or test mode

088h

CHIP_ID

CHIP_ID

090h

PGCR0

Power gating control 0

094h

PGCR1

Power gating control 1

098h

PGCR2

Power gating control 2

09Ch

GCR

Control RF Gain

0A0h

IVREF_X32

Control XTAL32 and IVREF

0A4h

XTAL_BUCK

Control XTAL and BUCK

0A8h

LO1

Control analog LO

0ACh

LO2

Reserved. Don’t change

0B0h

RXCR

Reserved. Don’t’ change

0B4h

ADCCR

Control SAR ADC clock source

0B8h

ANACTRL

Control analog peripherals

0BCh

ADDITION

Other analog internal control

Page 8

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

8 of 128

2.5.2 Register Description

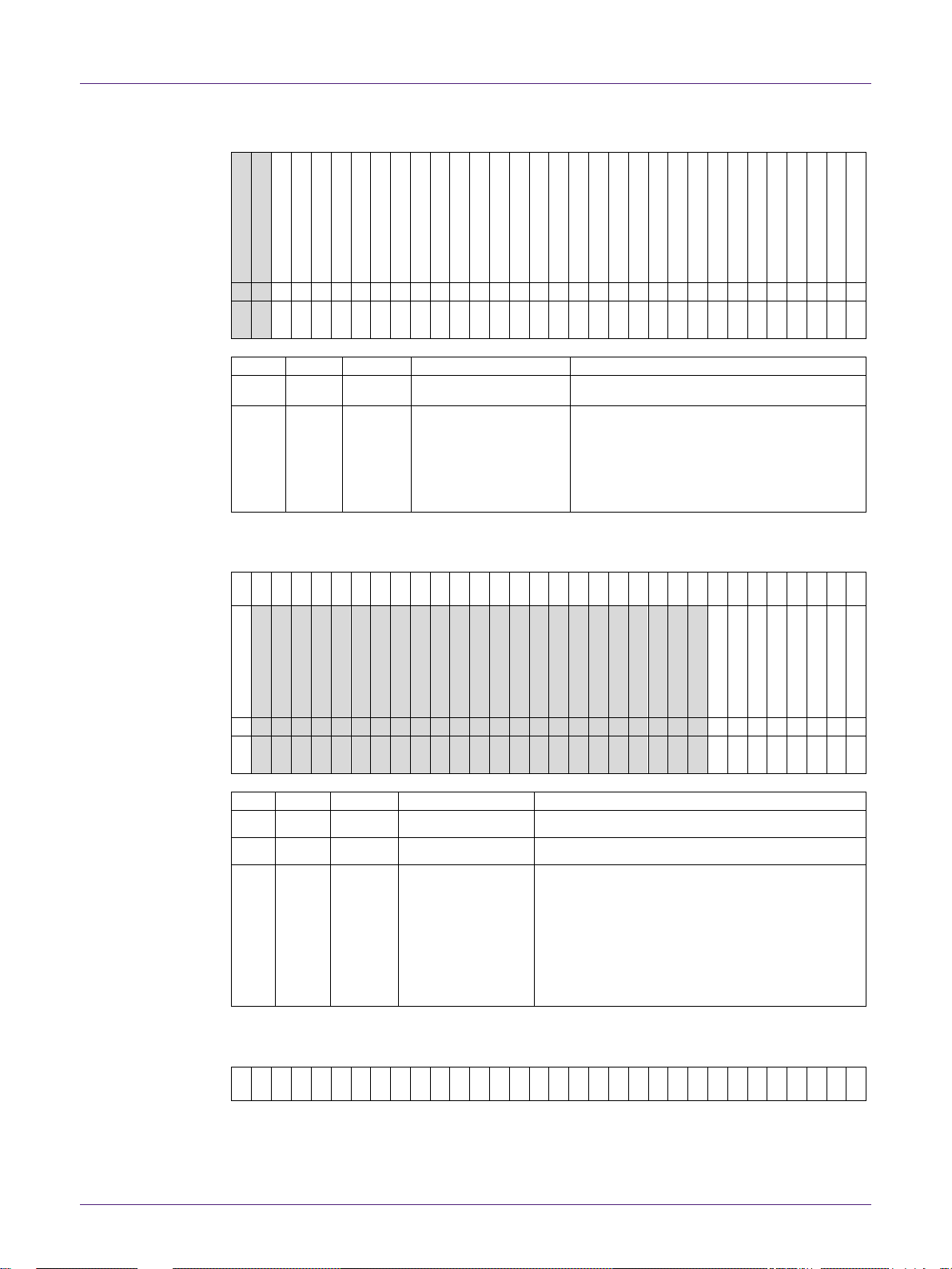

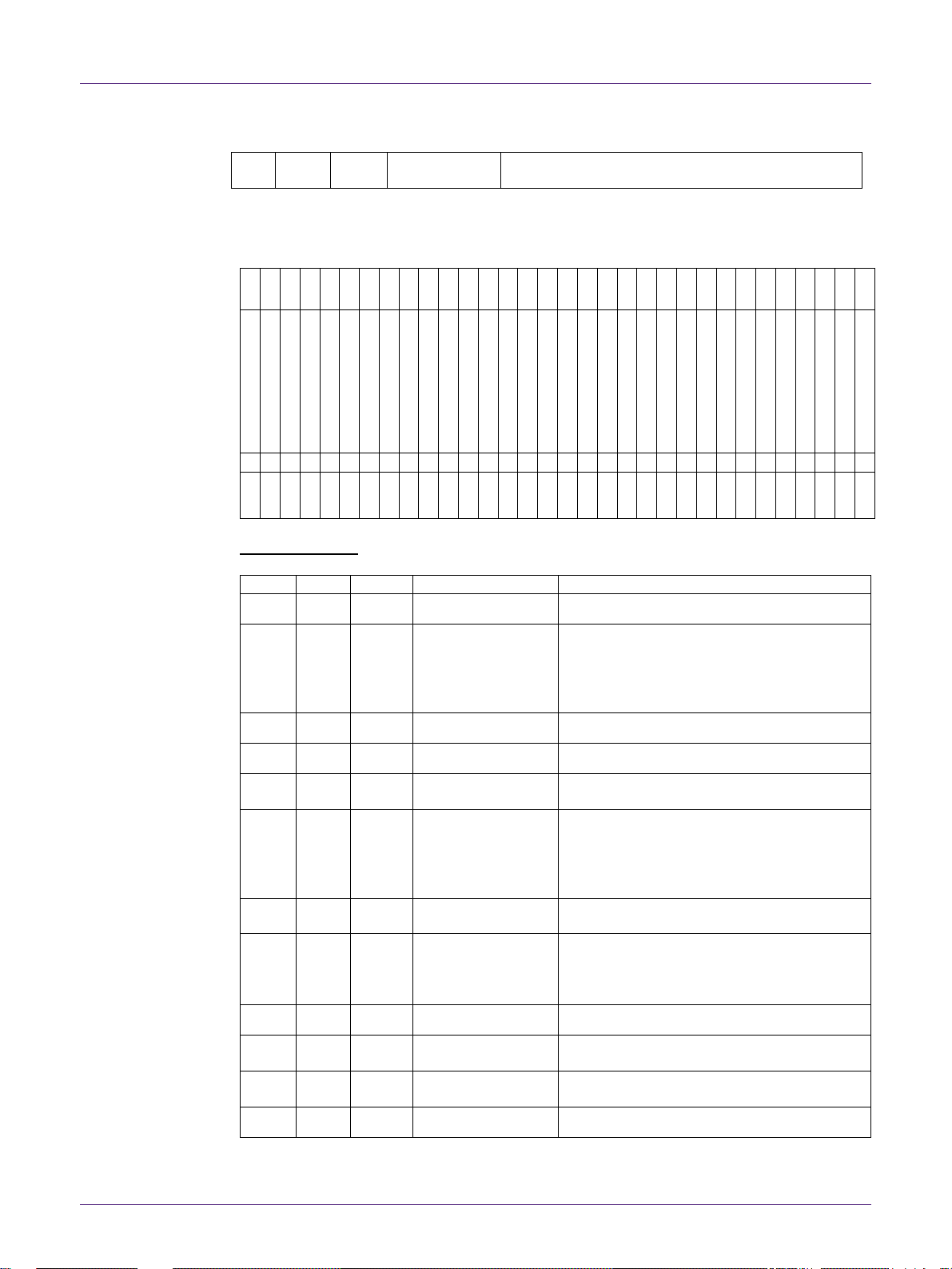

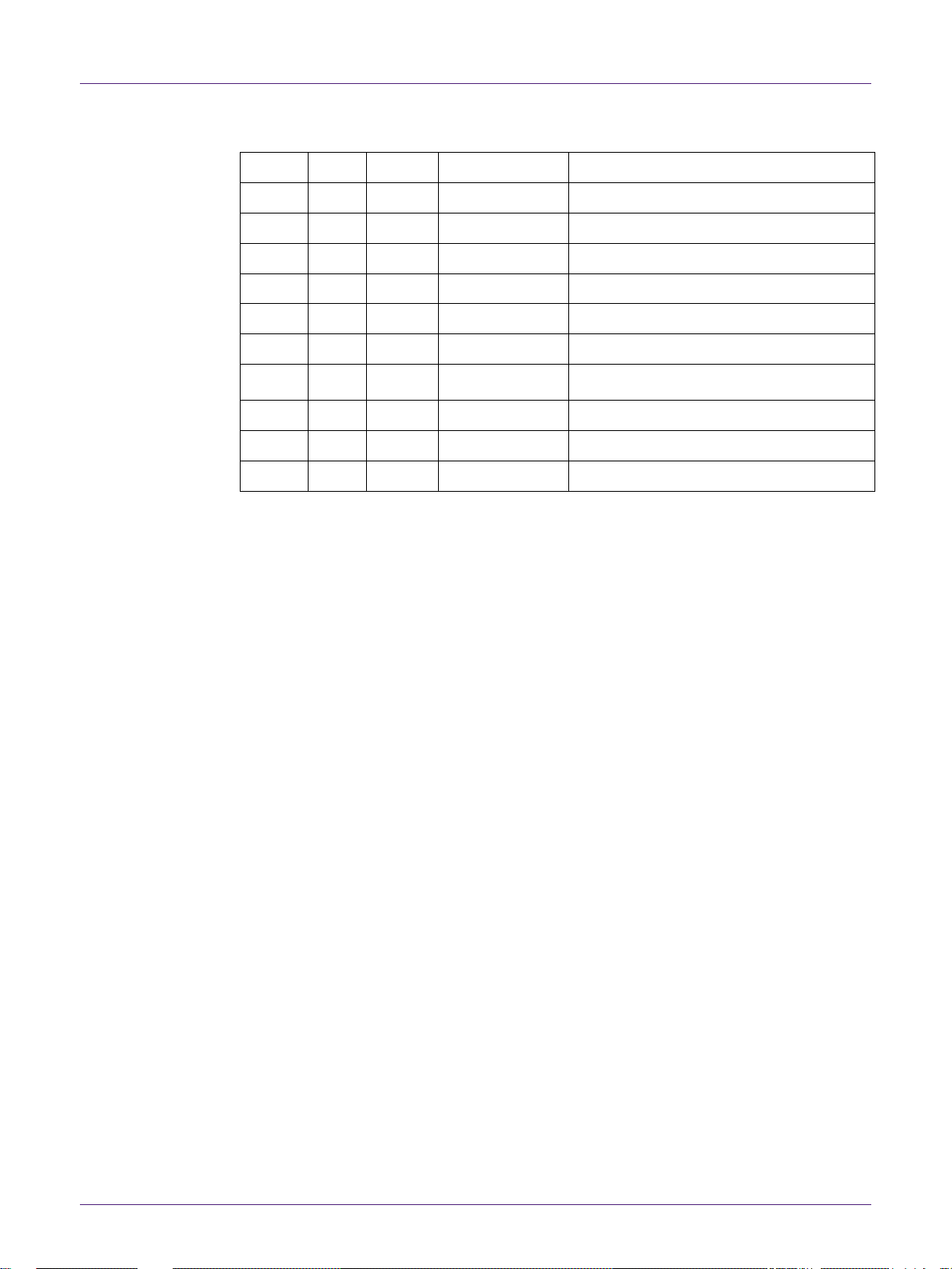

Table 3 CRSS (CLK_RST_SOFT_SET)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

GATING_TIMER3 GATING_TIMER2 GATING_TIMER1 GATING_TIMER0

GATING_UART1 GATING_UART0

GATING_SPI1 GATING_SPI0

GATING_32K_CLK

GATING_SPI_AHB

GATING_GPIO

GATING_ADC

GATING_DMA

GATING_BLE_AHB

GATING_PWM

REBOOT_SYS

LOCKUP_RST

BLE_RST

DP_RST

DPREG_RST

RTC_RST

I2C_RST

GPIO_RST

WDOG_RST

TIMER3_RST TIMER2_RST TIMER1_RST TIMER0_RST

USART1_RST USART0_RST

DMA_RST

CPU_RST

0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

RW1

Bit

Type

Reset

Symbol

Description

31

RW1 0 GATING_TIMER3

Write 1 to disable timer 3 clock, 0 no effect.

30

RW1 0 GATING_TIMER2

Write 1 to disable timer 2 clock, 0 no effect.

29

RW1 0 GATING_TIMER1

Write 1 to disable timer 1 clock, 0 no effect.

28

RW1 1 GATING_TIMER0

Write 1 to disable timer 0 clock, 0 no effect.

27

RW1 1 GATING_UART1

Write 1 to disable UART 1 clock, 0 no effect.

26

RW1 1 GATING_UART0

Write 1 to disable UART 0 clock, 0 no effect.

25

RW1 1 GATING_SPI1

Write 1 to disable SPI 1 clock, 0 no effect.

24

RW1 1 GATING_SPI0

Write 1 to disable SPI 0 clock, 0 no effect.

23

RW1 1 GATING_32K_CLK

Write 1 to disable 32KHz clock, 0 no effect.

22

RW1 1 GATING_SPI_AHB

Write 1 to disable FLASH control clock, 0 no effect.

21

RW1 1 GATING_GPIO

Write 1 to disable GPIO clock, 0 no effect.

20

RW1 1 GATING_ADC

Write 1 to disable ADC clock, 0 no effect.

19

RW1 1 GATING_DMA

Write 1 to disable DMA clock, 0 no effect.

18

RW1 1 GATING_BLE_AHB

Write 1 to disable BLE AHB clock, 0 no effect.

17

RW1 1 GATING_PWM

Write 1 to disable PWM clock, 0 no effect.

16

RW1 0 REBOOT_SYS

Write 1 to reboot entire system

15

RW1 0 LOCKUP_RST

Write 1 to enable LOCKUP reset control

14

RW1 1 BLE_RST

Write 1 to set BLE reset

13

RW1 1 DP_RST

Write 1 to set datapath reset

12

RW1 1 DPREG_RST

Write 1 to set datapath register reset

11

RW1 1 RTC_RST

Write 1 to set sleep timer reset

Page 9

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

9 of 128

10

RW1 1 I2C_RST

Write 1 to set I2C reset

9

RW1 1 GPIO_RST

Write 1 to set GPIO reset

8

RW1 1 WDOG_RST

Write 1 to set Watch Dog reset

7

RW1 1 TIMER3_RST

Write 1 to set timer 3 reset

6

RW1 1 TIMER2_RST

Write 1 to set timer 2 reset

5

RW1 1 TIMER1_RST

Write 1 to set timer 1 reset

4

RW1 1 TIMER0_RST

Write 1 to set timer 0 reset

3

RW1 1 USART1_RST

Write 1 to set USART1 (SPI 1 and UART 1) reset

2

RW1 1 USART0_RST

Write 1 to set USART0 (SPI 0 and UART 0) reset

1

RW1 1 DMA_RST

Write 1 to set DMA reset

0

RW1 1 CPU_RST

Write 1 to set CPU reset

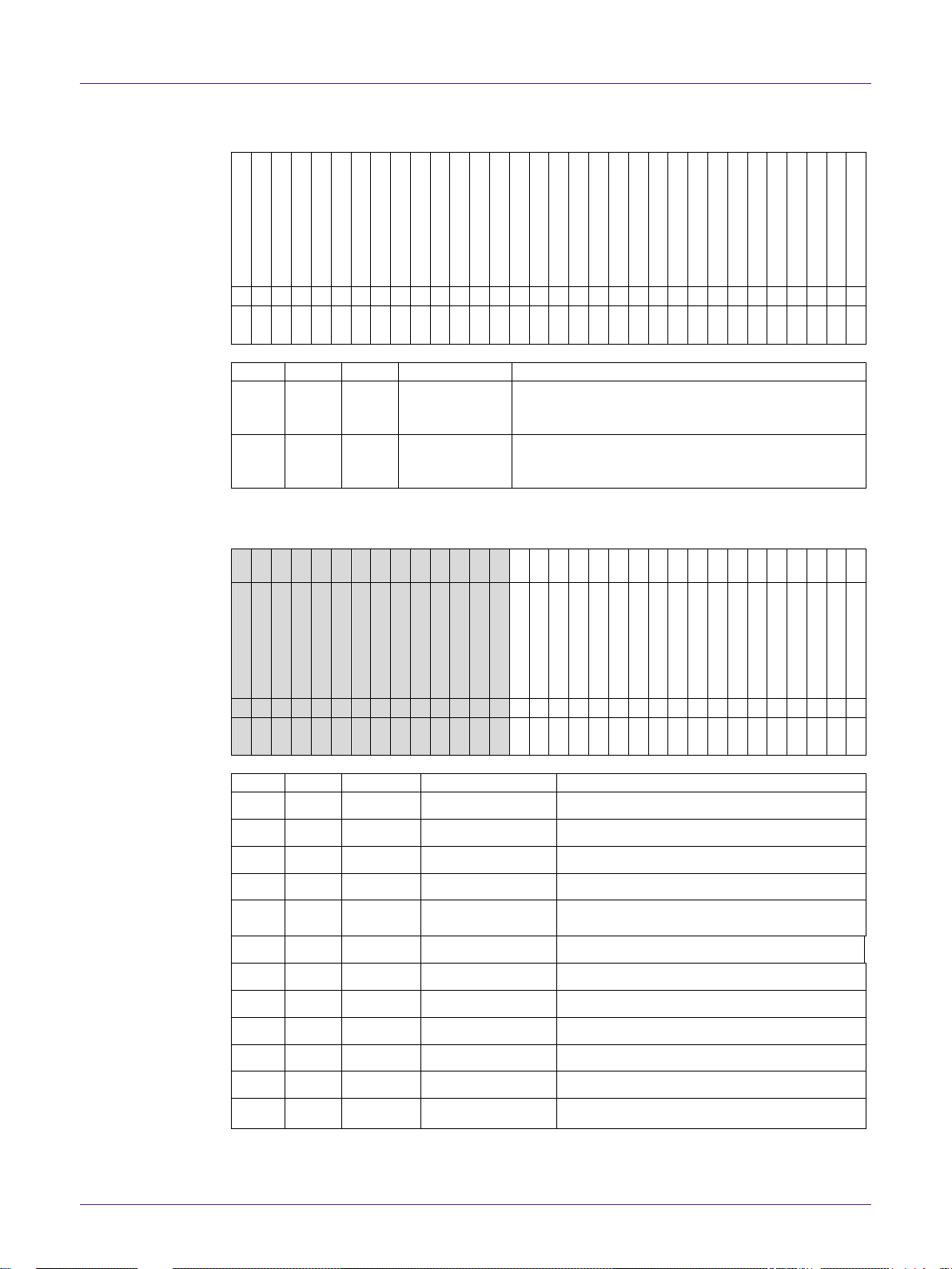

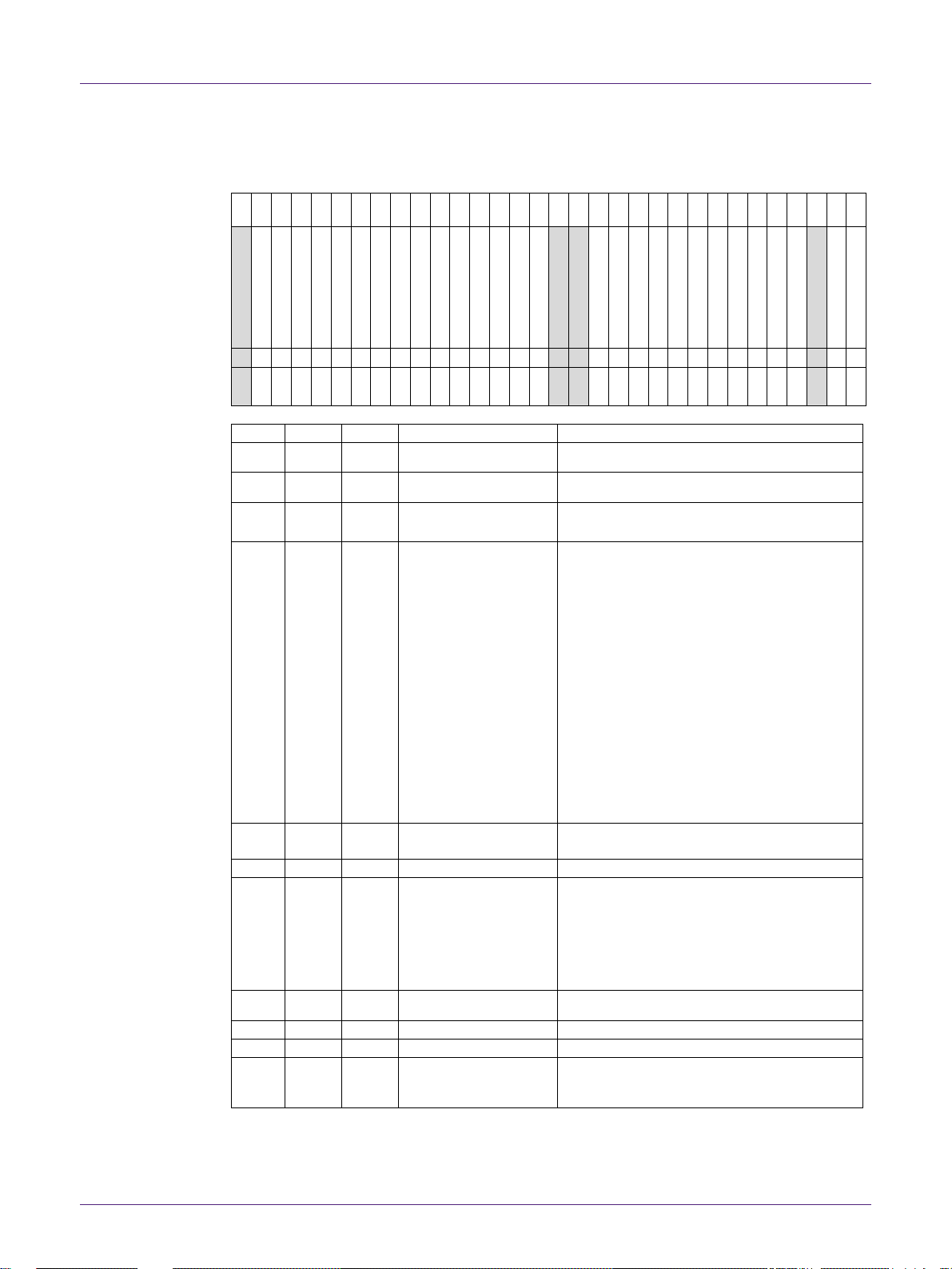

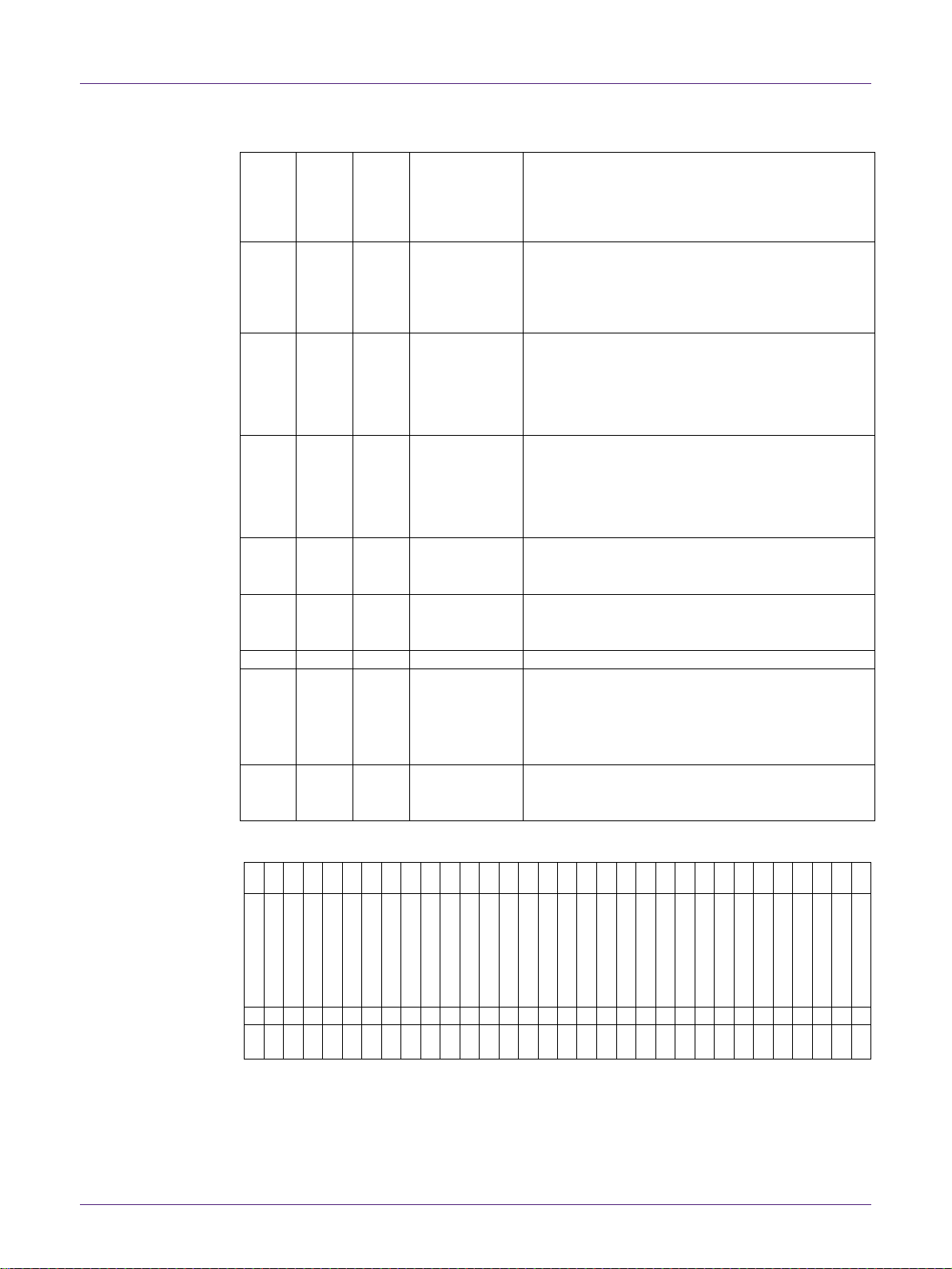

Table 4 CRSC (CLK_RST_SOFT_CLR)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

NGATING_TIMER3 NGATING_TIMER2 NGATING_TIMER1 NGATING_TIMER0

NGATING_UART1 NGATING_UART0

NGATING_SPI1 NGATING_SPI0

NGATING_32K_CLK

NGATING_SPI_AHB

NGATING_GPIO

NGATING_ADC

NGATING_DMA

NGATING_BLE_AHB

NGATING_PWM

RSVD

DIS_LOCKUP_RST

CLR_BLE_RST

CLR_DP_RST

CLR_DPREG_RST

CLR_SLPTIM_RST

CLR_I2C_RST

CLR_GPIO_RST

CLR_WDOG_RST

CLR_TIMER3_RST CLR_TIMER2_RST CLR_TIMER1_RST CLR_TIMER0_RST

CLR_USART1_RST CLR_USART0_RST

CLR_DMA_RST

CLR_CPU_RST

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x

x

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1 W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

W1

Bit

Type

Reset

Symbol

Description

31

W1 x NGATING_TIMER3

Write 1 to enable timer 3 clock

30

W1 x NGATING_TIMER2

Write 1 to enable timer 2 clock

29

W1 x NGATING_TIMER1

Write 1 to enable timer 1 clock

28

W1 x NGATING_TIMER0

Write 1 to enable timer 0 clock

27

W1 x NGATING_UART1

Write 1 to enable UART 1 clock

26

W1 x NGATING_UART0

Write 1 to enable UART 0 clock

25

W1 x NGATING_SPI1

Write 1 to enable SPI 1 clock

24

W1 x NGATING_SPI0

Write 1 to enable SPI 0 clock

23

W1 x NGATING_32K_CLK

Write 1 to enable 32KHz clock

22

W1 x NGATING_SPI_AHB

Write 1 to enable SPI AHB clock

21

W1 x NGATING_GPIO

Write 1 to enable GPIO clock

Page 10

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

10 of 128

20

W1 x NGATING_ADC

Write 1 to enable ADC clock

19

W1 x NGATING_DMA

Write 1 to enable DMA clock

18

W1 x NGATING_BLE_AHB

Write 1 to enable BLE AHB clock

17

W1 x NGATING_PWM

Write 1 to enable PWM clock

16 x

RSVD

Reserved

15

W1 x DIS_LOCKUP_RST

Write 1 to disable LOCKUP reset control

14

W1 x CLR_BLE_RST

Write 1 to clear BLE reset

13

W1 x CLR_DP_RST

Write 1 to clear datapath reset

12

W1 x CLR_DPREG_RST

Write 1 to clear datapath register reset

11

W1 x CLR_SLPTIM_RST

Write 1 to clear sleep timer reset

10

W1 x CLR_I2C_RST

Write 1 to clear I2C reset

9

W1 x CLR_GPIO_RST

Write 1 to clear GPIO reset

8

W1 x CLR_WDOG_RST

Write 1 to clear Watch Dog reset

7

W1 x CLR_TIMER3_RST

Write 1 to clear timer 3 reset

6

W1 x CLR_TIMER2_RST

Write 1 to clear timer 2 reset

5

W1 x CLR_TIMER1_RST

Write 1 to clear timer 1 reset

4

W1 x CLR_TIMER0_RST

Write 1 to clear timer 0 reset

3

W1 x CLR_USART1_RST

Write 1 to clear USART1 (SPI 1 and UART 1) reset

2

W1 x CLR_USART0_RST

Write 1 to clear USART0 (SPI 0 and UART 0) reset

1

W1 x CLR_DMA_RST

Write 1 to clear DMA reset

0

W1 x CLR _CPU_RST

Write 1 to clear CPU reset

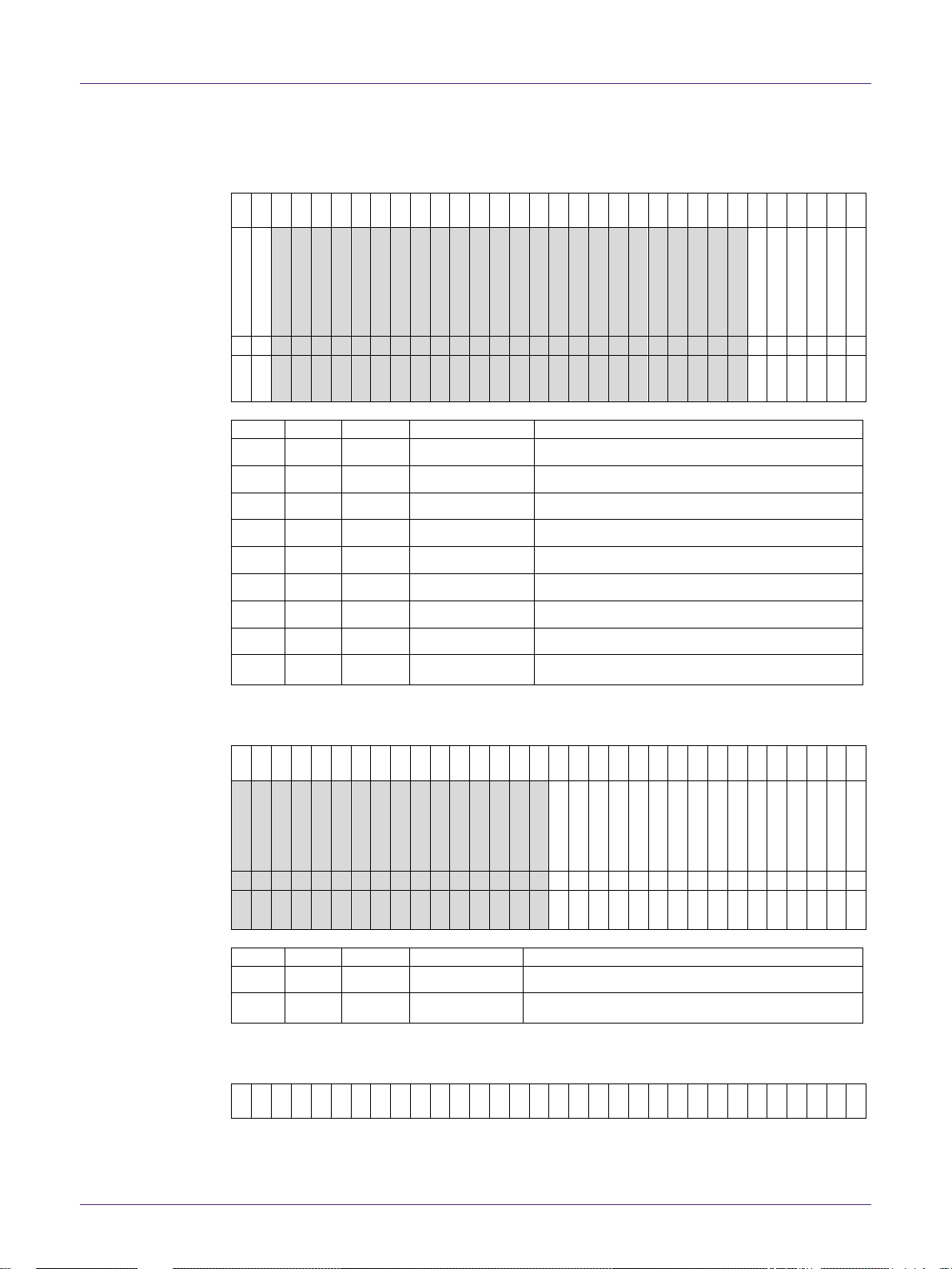

Table 5 CMDCR (CLK_MUX_DIV_CTRL)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

CLK_MUX[1] CLK_MUX[0]

SEL_CLK_32K

BLE_FRQ_SEL

BLE_DIV_BYPASS

BLE_DIVIDER

AHB_DIV_BYPASS

AHB_DIVIDER

USART1_DIV_BYPASS

USART1_DIVIDER

USART0_DIV_BYPASS

USART0_DIVIDER

RSVD

APB_DIV_BYPASS

APB_DIVIDER

TIMER_DIV_BYPASS

TIMER_DIVIDER

0 1 0 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 1 1 0 0

1

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW R RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

Page 11

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

11 of 128

31-

30

RW

01b

CLK_MUX[1-0]

Select system clock source.

00b = High frequency crystal 16MHz or 32MHz;

01b = 20MHz internal high frequency;

10b = 32MHz PLL output;

11b = 32KHz low speed clock;

29

RW 0 SEL_CLK_32K

1 = Select 32KHz clock from RCO

0 = Select 32KHz clock from XTAL32

28

RW 1 BLE_FRQ_SEL

Describe BLE clock frequency.

0 = 8 MHz;

1 = 16 MHz

27

RW 1 BLE_DIV_BYPASS

‘1’ is bypass BLE Divider; Only 16 or 8 MHz are supported;

26

RW 0 BLE_DIVIDER

If BLE_DIV_BYPASS is ‘0’,

BLE_CLK = AHB_CLK / (2*(BLE_DIVIDER +1));

Only 16 or 8 MHz are supported;

25

RW 1 AHB_DIV_BYPASS

‘1’ is bypass AHB Divider;

24-

16

RW 0 AHB_DIVIDER[8-0]

If AHB_DIV_BYPASS is ‘0’,

AHB_CLK = SYS_CLK/(2*(APB_DIVIDER+1));

15

RW 0 USART1_DIV_BYPASS

‘1’ is bypass USART1 Divider;

14-

12

RW

001b

USART1_DIVIDER[2-

0]

If USART1_DIV_BYPASS is ‘0’,

USART1_CLK = AHB_CLK/(2*(USART1_DIVIDER+1))

11

RW 1 USART0_DIV_BYPASS

‘1’ is bypass USART0 Divider;

10-8 RW 0 USART0_DIVIDER[2-

0]

If USART0_DIV_BYPASS is ‘0’,

USART0_CLK = AHB_CLK/(2*(USART1_DIVIDER+1))

7 R 0

RSVD

Reserved

6

RW 0 APB_DIV_BYPASS

‘1’ is bypass APB Divider;

5-4

RW

01b

APB_DIVIDER[1-0]

If APB_DIV_BYPASS is ‘0’,

APB_CLK = AHB_CLK/(2*(APB_DIVIDER+1))

3

RW 1 TIMER_DIV_BYPASS

‘1’ is bypass TIMER Divider;

2-0

RW

001b

TIMER_DIVIDER[2-0]

If TIMER_DIV_BYPASS is ‘0’,

TIMER_CLK = AHB_CLK / (2*(TIMER_DIVIDER + 1));

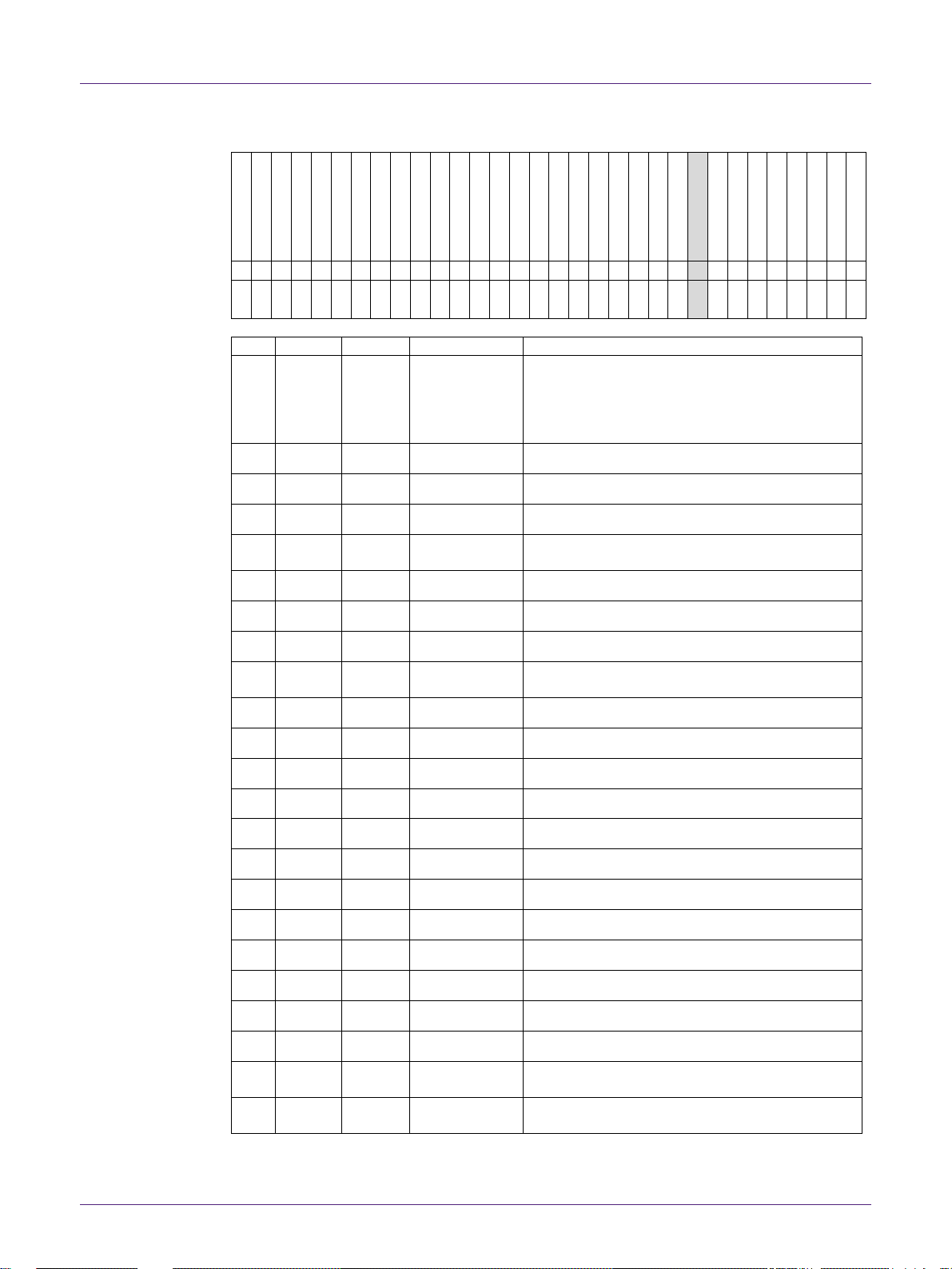

Table 6 STCR (SYS_TICK_CTRL)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

STCLEN

RSVD

RSVD

RSVD

RSVD

RSVD

STCALIB

1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 1 1

1

RW

R R R R R

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31

RW

1

STCLEN

‘1’ is enable STCLKEN, so that SCLK of CPU can be gated by

STCLKEN;

30-26

R

00000

RSVD

Reserved

Page 12

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

12 of 128

25-0

RW

10001

47h

STCALIB[2

5-0]

CPU STCALIB input

Table 7 PMCR0 (PIN_MUX_CTRL0)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

PIN_CTRL

[31]

PIN_CTRL[30] PIN_CTRL[29] PIN_CTRL[28] PIN_CTRL[27] PIN_CTRL[26] PIN_CTRL[25] PIN_CTRL[24] PIN_CTRL[23] PIN_CTRL[22] PIN_CTRL[21] PIN_CTRL[20] PIN_CTRL[19] PIN_CTRL[18] PIN_CTRL[17] PIN_CTRL[16] PIN_CTRL[15] PIN_CTRL[14] PIN_CTRL[13] PIN_CTRL[12] PIN_CTRL[11] PIN_CTRL[10]

PIN_CTRL[9] PIN_CTRL[8] PIN_CTRL[7] PIN_CTRL[6] PIN_CTRL[5] PIN_CTRL[4] PIN_CTRL[3] PIN_CTRL[2]

PIN_CTR[1]

PIN_CTRL[0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31-0

RW 0 PIN_CTRL[31-0]

Please see GPIO MUX Table;

Table 8 PMCR1 (PIN_MUX_CTRL1)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

FLASH_CTRL_PIN

TEST_ENABLE1 TEST_ENABLE0

PIN_CTRL[60] PIN_CTRL[59] PIN_CTRL[58] PIN_CTRL[57] PIN_CTRL[56] PIN_CTRL[55] PIN_CTRL[54] PIN_CTRL[53] PIN_CTRL[52] PIN_CTRL[51] PIN_CTRL[50] PIN_CTRL[49] PIN_CTRL[48] PIN_CTRL[47] PIN_CTRL[46] PIN_CTRL[45] PIN_CTRL[44] PIN_CTRL[43] PIN_CTRL[42] PIN_CTRL[41] PIN_CTRL[40] PIN_CTRL[39] PIN_CTRL[38] PIN_CTRL[37] PIN_CTRL[36] PIN_CTRL[35] PIN_CTRL[34] PIN_CTRL[33] PIN_CTRL[32]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31

RW

0

FLASH_CTRL_PIN

When External Flash is used,

0 = P1_0,P1_1,P1_2,P1_3 port is for SPI Flash;

1 = P1_0,P1_1,P1_2,P1_3port isn’t for SPI Flash;

30

RW

0

TEST_ENABLE1

Reserved. Must write 0.

29

RW

0

TEST_ENABLE0

Reserved. Must write 0.

28-0

RW

0

PIN_CTRL[60-32]

Please see GPIO MUX Table;

Table 9 PMCR2 (PIN_MUX_CTRL2)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

Page 13

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

13 of 128

TEST_CTRL[4] TEST_CTRL[3] TEST_CTRL[2] TEST_CTRL[1] TEST_CTRL[0]

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

CLKOUT1_PIN_SEL CLKOUT0_PIN_SEL

UART1_PIN_SEL

I2C_PIN_SEL

ADCT_PIN_SEL

RSVD

SPI0_PIN_SEL SPI1_PIN_SEL

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0

0

RW

RW

RW

RW

RW

R R R R R R R R R R R R R R R R R R R

RW

RW

RW

RW

RW R RW

RW

Bit

Type

Reset

Symbol

Description

31-27

RW

0

TEST_CTRL[4-0]

Reserved

26-8 R 0

RSVD

Reserved

7

RW

1

CLKOUT1_PIN_S

EL

0 = CLKOUT1 is HCLK;

1 = CLKOUT1 is CLK_32K

6

RW

0

CLKOUT0_PIN_S

EL

0 = CLKOUT0 is HCLK;

1 = CLKOUT0 is CLK_32K

5

RW

0

UART1_PIN_SEL

0 = UART1_cts is connected with P1_2;

UART1_rxd is connected with P1_0;

1 = UART1_cts is connected with P3_7;

UART1_rxd is connected with P2_0;

4

RW

0

I2C_PIN_SEL

0 = i2c_scl is connected with P2_4;

I2c_sda is connected with P2_3;

1 = i2c_scl is connected with P0_5;

I2c_sda is connected with P0_2;

3

RW

0

ADCT_PIN_SEL

0 = ADC Trigger is connected with P1_2;

1 = ADC Trigger is connected with P0_5;

2 R 0

RSVD

Reserved

1

RW

0

SPI0_PIN_SEL

0 = SPI 0 CLK is connected with P0_2;

SPI 0 CS0 is connected with P0_1;

SPI 0 Data out is connected with P0_0;

SPI 0 Data in is connected with P1_7;

1 = SPI 0 CLK is connected with P3_5;

SPI 0 CS0 is connected with P3_6;

SPI 0 Data out is connected with P3_4;

SPI 0 Data in is connected with P3_3;

0

RW

0

SPI1_PIN_SEL

0 = SPI 1 CLK is connected with P1_3;

SPI 1 CS0 is connected with P1_2;

SPI 1 Data out is connected with P1_1;

SPI 1 Data in is connected with P1_0;

1 = SPI 1 CLK is connected with P2_2;

SPI 1 CS0 is connected with P3_7;

SPI 1 Data out is connected with P2_1;

SPI 1 Data in is connected with P2_0;

Table 10 PDCR (PAD_DRV_CTRL)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

Page 14

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

14 of 128

RSVD

PAD_DRV_CTRL[30] PAD_DRV_CTRL[29] PAD_DRV_CTRL[28] PAD_DRV_CTRL[27] PAD_DRV_CTR

L[26]

PAD_DRV_CTRL[25] PAD_DRV_CTRL[24] PAD_DRV_CTRL[23] PAD_DRV_CTRL[22] PAD_DRV_CTRL[21] PAD_DRV_CTRL[20] PAD_DRV_CTRL[19] PAD_DRV_CTRL[18] PAD_DRV_CTRL[17] PAD_DRV_CTRL[16] PAD_DRV_CTRL[15] PAD_DRV_CTRL[14] PAD_DRV_CTRL[13] PAD_DRV_CTRL[12] PAD_DRV_CTRL

[11]

PAD_DRV_CTRL[10]

PAD_DRV_CTRL[9] PAD_DRV_CTRL[8] PAD_DRV_CTRL[7] PAD_DRV_CTRL[6] PAD_DRV_CTRL[5] PAD_DRV_CTRL[4] PAD_DRV_CTRL[3] PAD_DRV_CTRL[2] PAD_DRV_CTRL[1] PAD_DRV_CTRL[0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

R

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type Res

et

Symbol

Description

31 R 0

RSVD

Reserved

30-0

RW 0 PAD_DRV_CTRL[

30-0]

Every bit control one GPIO PAD driver ability;

0 = Low driver ,

1 = High driver.

Table 11 PPCR0 (PAD_PULL_CTRL0)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

PAD_PULL_CTRL[31] PAD_PULL_CTRL[30] PAD_PULL_CTRL[29] PAD_PULL_CTRL[28] PAD_PULL_CTRL[27] PAD_PULL_CTRL[26] PAD_PULL_CTRL[25] PAD_PULL_CTRL[24] PAD_PULL_CTRL[23] PAD_PULL_CTRL[22] PAD_PULL_CTRL[21] PAD_PULL_CTRL[20] PAD_PULL_CTRL[19] PAD_PULL_CTRL[18] PAD_PULL_CTRL[17] PAD_PULL_CTRL[16] PAD_PULL_CTRL[15] PAD_PULL_CTRL[14] PAD_PULL_CTRL[13] PAD_PULL_CTRL[12] PAD_PULL_CTRL[11] PAD_PULL_CTRL[10]

PAD_PULL_CTRL[9] PAD_PULL_CTRL[8] PAD_PULL_CTRL[7] PAD_PULL_CTRL[6] PAD_PULL_CTRL[5] PAD_PULL_CTRL[4] PAD_PULL_CTRL[3] PAD_PULL_CTRL[2] PAD_PULL_CTRL[1] PAD_PULL_CTRL[0]

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31-0

RW

AAAA

AAAA

h

PAD_PULL_CTRL[31-0]

Every two bit control one GPIO PAD Pull Up or

Pull Down;

00b = High-Z;

01b = Pull-down;

10b = Pull-up;

11b = Reserved

Table 12 PPCR1 (PAD_PULL_CTRL1)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

Page 15

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

15 of 128

RSVD

RSVD

PAD_PULL_CTRL[62] PAD_PULL_CTRL[61] PAD_PULL_CTRL[60] PAD_PULL_CTRL[59] PAD_PULL_CTRL[58] PAD_PULL_CTRL[57] PAD_PULL_CTRL[56] PAD_PULL_CTRL[55] PAD_PULL_CTRL[54] PAD_PULL_CTRL[53] PAD_PULL_CTRL[52] PAD_PULL_CTRL[51] PAD_PULL_CTRL[50] PAD_PULL_CTRL[49] PAD_PULL_CTRL[48] PAD_PULL_CTRL[47] PAD_PULL_CTRL[46] PAD_PULL_CTRL[45] PAD_PULL_CTRL[44] PAD_PULL_CTRL[43] PAD_PULL_CTRL[42] PAD_PULL_CTRL[41] PAD_PULL_CTRL[40] PAD_PULL_CTRL[39] PAD_PULL_CTRL[37] PAD_PULL_CTRL[36] PAD_PULL_CTRL[35] PAD_PULL_CTRL[34] PAD_PULL_CTRL[33] PAD_PULL_CTRL[32]

0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0

R

R

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31-30 R 0

RSVD

Reserved

29-0

RW

2AAAAA

AAh

PAD_PULL_CTRL[62-32]

Every two bit control one GPIO PAD Pull Up or

Pull Down;

00b = High-Z;

01b = Pull-down;

10b = Pull-up;

11b = Reserved

Table 13 RCS (RST_CAUSE_SRC)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

RST_CAUSE_CLR

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RST_CAUSE[7] RST_CAUSE[6] RST_CAUSE[5] RST_CAUSE[4] RST_CAUSE[3] RST_CAUSE[2] RST_CAUSE[1] RST_CAUSE[0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 x x x x x x x

x

W1

R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R

Bit

Type

Reset

Symbol

Description

31

W1 0 RST_CAUSE_CLR

Write ‘1’ clear RESET_CAUSE bits;

30-8 R 0

RSVD

Reserved

7-0 R x

RST_CAUSE[7-0]

xxxxxxx1b = Power-on Reset;

xxxxxx1xb = Brown-Down Reset;

xxxxx1xxb = External pin Reset;

xxxx1xxxb = Watch Dog Reset;

xxx1xxxxb = Lock Up Reset;

xx1xxxxxb = Reboot Reset;

x1000000b = CPU system Reset requirement;

10000000b = CPU software Reset;

Table 14 IOWCR (IO_WAKEUP_CTRL)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

Page 16

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

16 of 128

IO_VALUE[15] IO_VALUE[14] IO_VALUE[13] IO_VALUE[12] IO_VALUE[11] IO_VALUE[10]

IO_VALUE[9] IO_VALUE[8] IO_VALUE[7] IO_VALUE[6] IO_VALUE[5] IO_VALUE[4] IO_VALUE[3] IO_VALUE[2] IO_VALUE[1] IO_VALUE[0]

IO_WAKEUP_EN[15] IO_WAKEUP_EN[14] IO_WAKEUP_EN[13] IO_WAKEUP_EN[12] IO_WAKEUP_EN[11] IO_WAKEUP_EN[10]

IO_WAKEUP_EN[9] IO_WAKEUP_EN[8] IO_WAKEUP_EN[7] IO_WAKEUP_EN[6] IO_WAKEUP_EN[5] IO_WAKEUP_EN[4] IO_WAKEUP_EN[3] IO_WAKEUP_EN[2] IO_WAKEUP_EN[1] IO_WAKEUP_EN[0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31-16

RW

0

IO_VALUE[15-0]

Control GPIO 0 ~ 15 Interrupt cause;

0 = When GPIO x is 1, generate interrupt;

1 = When GPIO x is 0, generate interrupt;

15-0

RW

0

IO_WAKEUP_E

N[15-0]

Control GPIO 0 ~ 15 as Wakeup source;

0 = Disable GPIO x as Wakeup source;

1 = Enable GPIO x as Wakeup source;

Table 15 BLESR (BLE_STATUS)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

CLK_RDY

CLK_XTAL32_RDY

REF_PLL_RDY

BG_RDY

BUCK_RDY

TX_EN

RX_EN

OSC_EN

CLK_STATUS

RADIO_EN

FREQ_WORD[7] FREQ_WORD[6] FREQ_WORD[5] FREQ_WORD[4] FREQ_WORD[3] FREQ_WORD[2] FREQ_WORD[1] FREQ_WORD[0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R

R

Bit

Type

Reset

Symbol

Description

31-18 R 0

RSVD

Reserved

17 R 0

CLK_RDY

16MHz/32MHz XTAL is ready

16 R 0

CLK_XTAL32_RDY

32KHz XTAL is ready

15 R 0

REF_PLL_RDY

REF PLL is ready

14 R 1

FLSH_LOCATION

1 = Internal Flash

0 = External Flash

13 R 0

BUCK_RDY

BUCK power is ready

12 R 0

TX_EN

QN902X is in transmit state;

11 R 0

RX_EN

QN902X is in receive state;

10 R 0

OSC_EN

BLE IP osc_en output;

9 R 0

CLK_STATUS

BLE IP clk_status output;

8 R 0

RADIO_EN

BLE IP radio_en output;

7-0 R 0

FREQ_WORD[7-0]

BLE Frequency Word;

Page 17

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

17 of 128

Table 16 SMR (SYS_MODE_REG)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

BOOT_MODE

EN_SW_MAP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RAM_BIST_FAIL

RAM_BIST_END

ROM_BIST_FAIL

ROM_BIST_END

BIST_START

TEST_MOD

1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

RWH

RW

R R R R R R R R R R R R R R R R R R R R R R R R R R R

R

RW

RW

Bit

Type

Reset

Symbol

Description

31

RWH

1

BOOT_MODE

Must write ‘1’

30

RW

0

EN_SW_MAP

1 = Enable SW ReMap;

29-6 R 0

RSVD

Reserved

5 R 0

RAM_BIST_FAIL

Reserved

4 R 0

RAM_BIST_END

Reserved

3 R 0

ROM_BIST_FAIL

Reserved

2 R 0

ROM_BIST_END

Reserved

1

RW

0

BIST_START

Reserved. Must write ‘0’

0

RW

0

TEST_MOD

Reserved. Must write ‘0’

Table 17 CHIP_ID

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

CHIP_ID[15] CHIP_ID[14] CHIP_ID[13] CHIP_ID[12] CHIP_ID[11] CHIP_ID[10]

CHIP_ID[9] CHIP_ID[8] CHIP_ID[7] CHIP_ID[6] CHIP_ID[5] CHIP_ID[4] CHIP_ID[3] CHIP_ID[2]

CHIP_ID[1] CHIP_ID[0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0

0

R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R R

R

Bit

Type

Reset

Symbol

Description

31-16 R 0

RSVD

Reserved

15-0 R 2901h

CHIP_ID[15-0]

QN902X CHIP ID

Table 18 PGCR0 (POWER_GATING_CTRL0)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

Page 18

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

18 of 128

SEL_PD

PD_OSC

PD_BG

PD_V2I

PD_BUCK

PD_VREG_A

PD_VREG_D

PD_XTAL

PD_XTAL32

DIV_RST_SYNC

PD_LO_VCO

PD_LO_PLL

PD_PA

PD_LNA

PD_LNA_PKDET

PD_MIXER

PD_PPF_PKDET

PD_PPF

PD_RX_PKDET

PD_RX_ADC

PD_SAR_ADC

PD_RCO

BOND_EN

RSVD

PD_MEM7 PD_MEM6 PD_MEM5 PD_MEM4 PD_MEM3 PD_MEM2 PD_MEM1

PL_VREG_D

1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW R RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31

RW

1

SEL_PD

BLE radio sub-block (LO_VCO, …)power control

selection

0 = Controlled by individual register bit, DIS_xxx

1 = Automatically controlled by BLE baseband

hardware

30

RW

1

PD_OSC

Reserved. Must write ‘1’

29

RW

1

PD_BG

Reserved. Must write ‘1’

28

RW

1

PD_V2I

Reserved. Must write ‘1’

27

RW

1

PD_BUCK

While DC-DC enabled, write ‘0’;

While DC-DC disabled, write ‘1’;

26

RW

1

PD_VREG_A

Reserved. Must write ‘1’

25

RW

1

PD_VREG_D

Reserved. Must write ‘1’

24

RW

1

PD_XTAL

Reserved. Must write ‘1’

23

RW

0

PD_XTAL32

1 = Switch off 32KHz XTAL power in sleep mode

0 = Switch on 32KHz XTAL power in sleep mode

22

RW

1

DIV_RST_SYNC

Reserved. Must write ‘1’

21

RW

1

PD_LO_VCO

Reserved. Must write ‘1’

20

RW

1

PD_LO_PLL

Reserved. Must write ‘1’

19

RW

1

PD_PA

Reserved. Must write ‘1’

18

RW

1

PD_LNA

Reserved. Must write ‘1’

17

RW

1

PD_LNA_PKDET

Reserved. Must write ‘1’

16

RW

1

PD_MIXER

Reserved. Must write ‘1’

15

RW

1

PD_PPF_PKDET

Reserved. Must write ‘1’

14

RW

1

PD_PPF

Reserved. Must write ‘1’

13

RW

1

PD_RX_PKDET

Reserved. Must write ‘1’

12

RW

1

PD_RX_ADC

Reserved. Must write ‘1’

11

RW

1

PD_SAR_ADC

Reserved. Must write ‘1’

10

RW

0

PD_RCO

1 = Switch off 32KHz RC power in sleep mode

0 = Switch on 32KHz RC power in sleep mode

9

RW

1

BOND_EN

1 = Enable bond option;

0 = Disable bond option;

Page 19

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

19 of 128

Must write 1 for QN9020 and QN9021; can keep 0 for

QN9022.

8 R 0

RSVD

Reserved

7

RW

0

PD_MEM7

1 = Switch off memory 7 power in sleep mode

0 = Switch on memory 7 power in sleep mode

6

RW

0

PD_MEM6

1 = Switch off memory 6 power in sleep mode

0 = Switch on memory 6 power in sleep mode

5

RW

0

PD_MEM5

1 = Switch off memory 5 power in sleep mode

0 = Switch on memory 5 power in sleep mode

4

RW

0

PD_MEM4

1 = Switch off memory 4 power in sleep mode

0 = Switch on memory 4 power in sleep mode

3

RW

0

PD_MEM3

1 = Switch off memory 3 power in sleep mode

0 = Switch on memory 3 power in sleep mode

2

RW

0

PD_MEM2

1 = Switch off memory 2 power in sleep mode

0 = Switch on memory 2 power in sleep mode

1

RW

0

PD_MEM1

1 = Switch off memory 1 power in sleep mode

0 = Switch on memory 1 power in sleep mode

0

RW

0

PL_VREG_D

Low power mode, write ‘0’. Otherwise, write ‘1’

Table 19 PGCR1 (POWER_GATING_CTRL1)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

VDD_RCO_SET

DIS_OSC

DIS_BG

DIS_V2I

DIS_BUCK

DIS_VREG_A

DIS_VREG_D

DIS_XTAL

DIS_XTAL32

DIS_REF_PLL DIS_LO_VCO

DIS_LO_PLL

DIS_PA

DIS_LNA

DIS_LNA_PKDET

DIS_MIXER

DIS_PPF_PKDET

DIS_PPF

DIS_RX_PKDET

DIS_RX_ADC

DIS_SAR_ADC

DIS_RCO

RSVD

RSVD

DIS_MEM7 DIS_MEM6 DIS_MEM5 DIS_MEM4 DIS_MEM3 DIS_MEM2 DIS_MEM1

DIS_SAR_BUF

1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0

0

RWW RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

R

R

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31

RW

1

VDD_RCO_SET

1 = Set RCO VDD high

0 = Set RCO VDD low (~200mV difference)

30

RW

0

DIS_OSC

1 = Switch off 40MHz oscillator power

0 = Switch on 40MHz oscillator power

29

RW

0

DIS_BG

1 = Switch off bandgap power

0 = Switch on bandgap power

28

RW

0

DIS_V2I

1 = Switch off IVREF power

0 = Switch on IVREF power

27

RW

0

DIS_BUCK

1 = Switch off buck converter power

0 = Switch on buck converter power

26

RW

0

DIS_VREG_A

1 = Switch off VREG of analog power

0 = Switch on VREG of analog power

25

RW

0

DIS_VREG_D

1 = Switch off VREG of digital power

0 = Switch on VREG of digital power

24

RW

0

DIS_XTAL

1 = Switch off 16/32MHz XTAL power

0 = Switch on 16/32MHz XTAL power

23

RW

0

DIS_XTAL32

1 = Switch off 32KHz XTAL power

0 = Switch on 32KHz XTAL power

Page 20

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

20 of 128

22

RW

1

DIS_REF_PLL

1 = Switch off REF PLL power

0 = Switch on REF PLL power

21

RW

1

DIS_LO_VCO

LO VCO power control, only effective when SEL_PD=0

1 = Switch off VCO of LO PLL power

0 = Switch on VCO of LO PLL power

20

RW

1

DIS_LO_PLL

LO VCO power control, only effective when SEL_PD=0

1 = Switch off LO PLL power

0 = Switch on LO PLL power

19

RW

1

DIS_PA

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Tx PA power

0 = Switch on Tx PA power

18

RW

1

DIS_LNA

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Rx LNA power

0 = Switch on Rx LNA power

17

RW

1

DIS_LNA_PKDET

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Rx LNA peak detector power

0 = Switch on Rx LNA peak detector power

16

RW

1

DIS_MIXER

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Rx MIXER power

0 = Switch on Rx MIXER power

15

RW

1

DIS_PPF_PKDET

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Rx PPF peak detector power

0 = Switch on Rx PPF peak detector power

14

RW

1

DIS_PPF

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Rx PPF power

0 = Switch on Rx PPF power

13

RW

1

DIS_RX_PKDET

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Rx peak detector 3 power

0 = Switch on Rx peak detector 3 power

12

RW

1

DIS_RX_ADC

LO VCO power control, only effective when SEL_PD=0

1 = Switch off Rx ADC power

0 = Switch on Rx ADC power

11

RW

1

DIS_SAR_ADC

1 = Switch off SAR ADC power

0 = Switch on SAR ADC power

10

RW

1

DIS_RCO

1 = Switch off 32KHz RC power

0 = Switch on 32KHz RC power

9 R 0

RSVD

Reserved

8 R 0

RSVD

Reserved

7

RW

0

DIS_MEM7

1 = Switch off memory 7 power

0 = Switch on memory 7 power

6

RW

0

DIS_MEM6

1 = Switch off memory 6 power

0 = Switch on memory 6 power

5

RW

0

DIS_MEM5

1 = Switch off memory 5 power

0 = Switch on memory 5 power

4

RW

0

DIS_MEM4

1 = Switch off memory 4 power

0 = Switch on memory 4 power

3

RW

0

DIS_MEM3

1 = Switch off memory 3 power

0 = Switch on memory 3 power

2

RW

0

DIS_MEM2

1 = Switch off memory 2 power

0 = Switch on memory 2 power

1

RW

0

DIS_MEM1

1 = Switch off memory 1 power

0 = Switch on memory 1 power

Page 21

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

21 of 128

0

RW

0

DIS_SAR_BUF

1 = Switch off SAR buffer

0 = Switch on SAR buffer

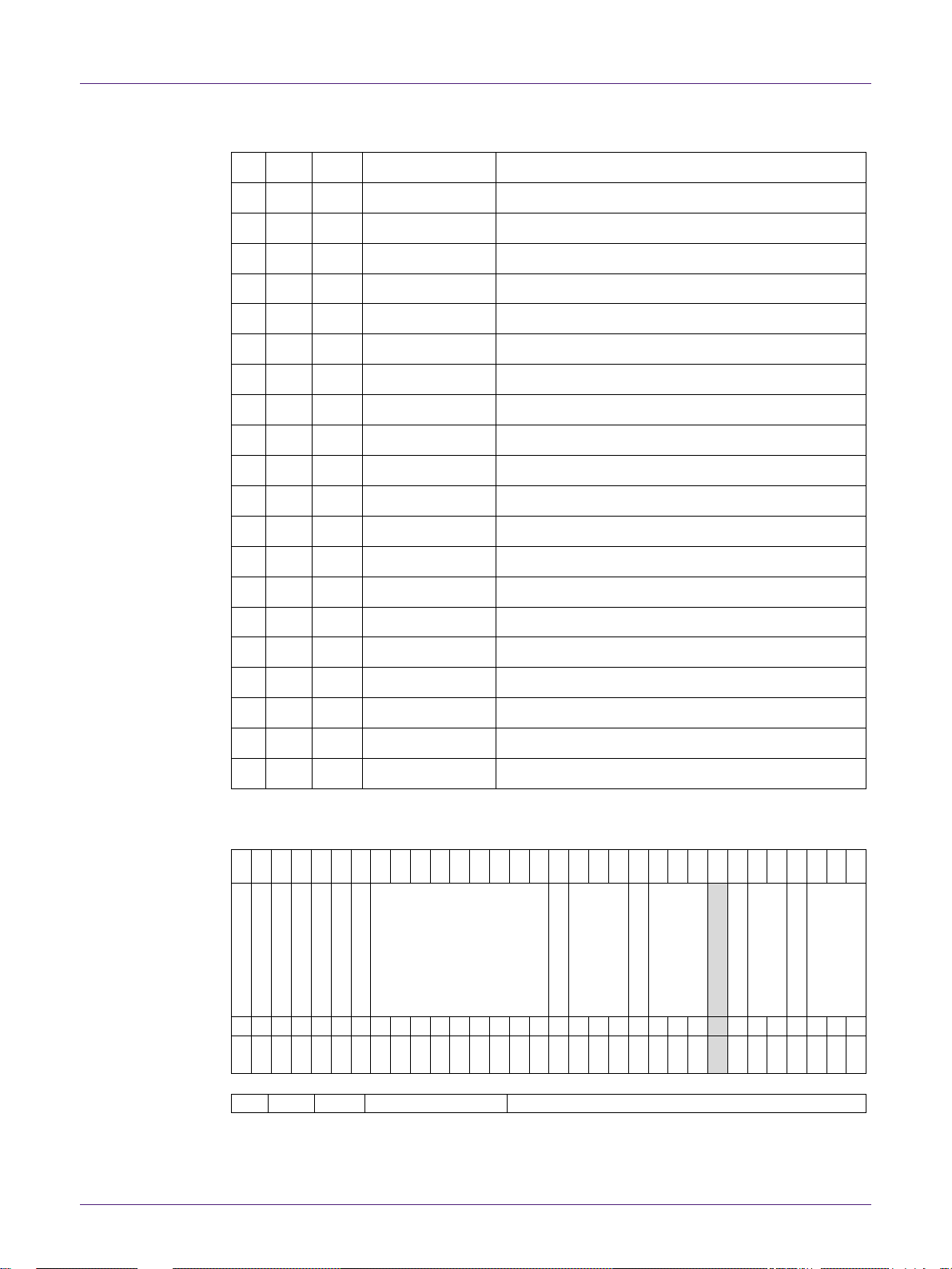

Table 20 PGCR2 (POWER_GATING_CTRL2)

Description of Word

Bit

Type

Reset

Name

Description

31-18 R 0h

RSVE

17-16

RW

01b

VREG12_A_BAK[1-0]

1.2V regulator for analog output voltage selection

11 = 1.3V

10 = 1.2V

01 = 1.1V

00 = 1.0V

15-9 R 0

RSVE

Reserved

8

RW 1 OSC_WAKEUP_EN

1 is Enable OSC_EN as wakeup source

7

RW 0 RTCI_PIN_SEL

0 = RTC Capture is connected with P0_0;

1 = RTC Capture is connected with P0_4;

6

RW 0 PD_STATE

Enable or disable wakeup source selection. Write

‘1’ before entering sleep mode. Write ‘0’ after

wakeup.

0 = Normal;

1 = Sleep;

5

RW 0 BD_AMP_EN

1 is Enable comparator of brown-out detector. It

should be set earlier than EN_BD 2us or more.

4

RW 0 DVDD12_PMU_SET

Write ‘1’ before entering sleep mode. Write ‘0’

after wakeup.

0 = High VDD_PMU in sleep mode

1 = Low VDD_PMU in sleep mode

3

RW 0 RX_EN_SEL

Reserved, must write ‘1’;

2

RW 1 FLASH_VCC_EN

1 = Open Flash Power;

0 = Close Flash Power;

1

RW 1 PMUENABLE

1 = Enable CPU power down operation mode;

0 = Disable CPU power down operation mode;

0

RW 1 DBGPMUENABLE

Reserved

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

VREG12_A_BAK[1] VREG12_A_BAK[0] RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

RSVE

OSC_WAKUP_EN RTCI_PIN_SEL PD_STATE BD_AMP_EN DVDD12_PMU_SET RX_EN_SEL FLASH_VCC_EN PMUENABLE DBGPMUENALBE

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 1 1

1

R R R R R R R R R R R R R

R

RW

RW

R R R R R R R

RW

RW

RW

RW

RW

RW

RW

RW

RW

Page 22

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

22 of 128

Table 21 GCR (GAIN_CTRL)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

TX_PWR_SEL

PA_GAIN_BOOST

BM_PA[1] BM_PA[0]

PA_GAIN[3] PA_GAIN[2] PA_GAIN[1] PA_GAIN[0]

LNA_GAIN1[1] LNA_GAIN1[0] LNA_GAIN2[1] LNA_GAIN2[0]

PPF_GAIN[3] PPF_GAIN[2] PPF_GAIN[1] PPF_GAIN[0]

RSVD

RSVD

LNA_GAIN_WEN

PPF_GAIN_WEN

VT_PKDET1_HG[2] VT_PKDET1_HG

[1]

VT_PKDET1_HG[0]

VT_PKDET1_MG[2] VT_PKDET1_MG[1] VT_PKDET1_MG[0]

VT_PKDET1_LG[2] VT_PKDET1_LG[1] VT_PKDET1_LG[0]

RSVD

VT_PKDET2 VT_PKDET3

0 0 1 0 1 1 0 1 0 0 0 0 1 0 0 0 0 0 0 0 1 0 1 1 0 1 1 0 1 0 0

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

R

R

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW R RW

RW

Bit

Type

Reset

Symbol

Description

31

RW 0 TX_PWR_SEL

Reserved. Write ‘0’

30

RW 0 PA_GAIN_BOOST

Reserved. Write ‘0’

29-28

RW

10b

BM_PA[1-0]

Reserved. Write ‘10b’

27-24

RW

1101b

PA_GAIN[3-0]

Together with PA_GAIN[4],PA_GAIN[0-4] means:

11111---------- 4dBm

01111---------- 3dBm

11110---------- 2dBm

01110---------- 1dBm

01101---------- 0dBm

01100---------- -2dBm

01010---------- -4dBm

01001---------- -6dBm

01000---------- -8dBm

00110---------- -10dBm

00101---------- -12dBm

00100---------- -14dBm

00010---------- -16dBm

00001---------- -18dBm

00000---------- -20dBm

23-22

RW 0 LNA_GAIN1[1-0]

Reserved. Write ‘00’

21-20

RW 0 LNA_GAIN2[1-0]

Reserved. Write ‘00’

19-16

RW

1000b

PPF_GAIN[3-0]

Reserved. Write ‘1000b’

15-14

R 0 RSVD

Reserved

13

RW 0 LNA_GAIN_WEN

Reserved. Write ‘0’

12

RW 0 PPF_GAIN_WEN

Reserved. Write ‘0’

11-9

RW

101b

VT_PKDET1_HG[2-0]

Reserved. Write ‘101b’

Page 23

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

23 of 128

8-6

RW

101b

VT_PKDET1_MG[2-0]

Reserved. Write ‘101b’

5-3

RW

101b

VT_PKDET1_LG[2-0]

Reserved. Write ‘101b’

2 R 0

RSVD

Reserved

1

RW 0 VT_PKDET2

Reserved. Write ‘0’

0

RW 0 VT_PKDET3

Reserved. Write ‘0’

Table 22 IVREF_X32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

BGSEL[3]

BGSEL[2] BGSEL[1] BGSEL[0]

VREG15[1] VREG15[0]

VREG12_A[1] VREG12_A[0]

TR_SWITCH

BM_PKDET3[1] BM_PKDET3[0]

VREG12_D[1] VREG12_D[0]

DVDD12_SW_EN

BUCK_BYPASS

BUCK_DPD

BUCK_ERR_ISEL[1] BUCK_ERR_ISEL[0]

BUCK_VBG[1]

BUCK_VBG[0]

X32SMT_EN

X32BP_RES

BM_X32BUF[1] BM_X32BUF[0]

X32INJ[1] X32INJ[0]

X32ICTRL[5] X32ICTRL[4] X32ICTRL[3] X32ICTRL[2] X32ICTRL[1] X32ICTRL[0]

1 0 0 0 1 0 0 1 0 0 1 1 0 0 0 0 0 1 1 0 0 0 0 1 0 0 1 0 0 0 0

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31-28

RW

1000b

BGSEL[3-0]

Bandgap voltage selection to compensate PVT

variations

8 steps with 5mV each upward. VBG=1225+5*BGSEL

27-26

RW

10b

VREG15[1-0]

1.5V regulator for analog output voltage selection

11b = 1.6V

10b = 1.6V

01b = 1.5V

00b = 1.4V

25-24

RW

01b

VREG12_A[1-0]

1.2V regulator for analog output voltage selection

11b =1.3V

10b = 1.2V

01b = 1.1V

00b =1.0V

23 R 0

TR_SWITCH

0 = Always use VREG12_A,BUCK_TMOS and

BUCK_BM;

1 = RX use VREG12_A, BUCK_TMOS and BUCK_BM,

TX use

VREG12_A_BAK,BUCK_TMOS_BAK,BUCK_BM_BAK;

Page 24

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

24 of 128

22-21

RW

01b

BM_PKDET3[1-0]

PKDET3 bias current setting

11 = 125%

10 = 100%

01 = 75%

00 = 50%

20-19

RW

10b

VREG12_D[1-0]

1.2V regulator for digital (dvdd12_core) output

voltage selection

11b = 1.3V

10b = 1.2V

01b = 1.1V

00b = 1.0V

18

RW 0 DVDD12_SW_EN

1 = Enable switch on between dvdd12_core and

dvdd12_pmu

17

RW 0 BUCK_BYPASS

Bypass buck converter

16

RW 0 BUCK_DPD

DC-DC power down without waiting current crossing

zero.

15-14

RW 1 BUCK_ERR_ISEL[10]

DC-DC error amplifier current adjustment.

00b = 15uA,

01b = 20uA,

10b = 25uA,

11b = 30uA.

13-12

RW 0 BUCK_VBG[1-0]

DC-DC Bandgap output voltage adjustment.

11

RW 0 X32SMT_EN

Reserved. Write ‘0’

10

RW 0 X32BP_RES

Bypass source degeneration resistor in the core of

32.768KHz XTAL.

9-8

RW

10b

BM_X32BUF[1-0]

Bias current control of 32.768KHz buffer

00b = 100nA

01b = 200nA

10b = 500nA

11b = 600nA

7-6

RW

01

X32INJ[1-0]

Select 32.768KHz XTAL clock source

00b = Use crystal oscillator between XTAL1/XTAL2

01b = Digital clock injection to XTAL1

10b = Single-end sine wave injection to XTAL1

11b = Differential since wave injection to XTAL1/

XTAL2

5-0

RW

10000

0b

X32ICTRL[5-0]

32.768KHz crystal bias current control

IB = 25nA*X32ICTRL

Table 23 XTAL_BUCK

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

NC

XINJ[1]

XINJ[0]

XICTRL[5] XICTRL[4] XICTRL[3] XICTRL[2] XICTRL[1] XICTRL[0]

XCSEL[5] XCSEL[4] XCSEL[3] XCSEL[2] XCSEL[1] XCSEL[0]

XSMT_EN

BUCK_VTHL[1] BUCK_VTHL[0]

BUCK_VTHH[1] BUCK_VTHH[0]

BUCK_TMOS[2] BUCK_TMOS[1] BUCK_TMOS[0]

BUCK_FC

BUCK_AGAIN BUCK_ADRES

BUCK_BM[1]

BUCK_BM[0]

TST_CPREF[3] TST_CPREF[2] TST_CPREF[1] TST_CPREF[0]

0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 1 1 1 0 1 0 0 1 0 1 0 0 1 0

1

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Page 25

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

25 of 128

Bit

Type

Reset

Symbol

Description

31

RW 0 NC

No Connected;

30-29

RW 0 XINJ[1-0]

Select high frequency XTAL clock source

00b = Use crystal oscillator between XTAL1/XTAL2

01b = Digital clock injection to XTAL1

10b = Single-end sine wave injection to XTAL1

11b = Differential sine wave injection to XTAL1/ XTAL2

28-23

RW

10000

0b

XICTRL[5-0]

High frequency crystal bias current control

For 16MHz XTAL: IB=80uA*XICTRL/64

For 32MHz XTAL: IB=160uA*XICTRL/64

22-17

RW

10000

0b

XCSEL[5-0]

Crystal oscillator cap loading selection. The loading cap

on each side is 10+XCSEL*0.32pF. It ranges from 10pF

to 30pF, while the default is 20pF.

16

RW 0 XSMT_EN

Reserved. Write ‘0’

15-14

RW

01b

BUCK_VTHL[1-0]

Reserved. Write ‘01b’

13-12

RW 1 BUCK_VTHH[1-0]

Reserved. Write ‘11b’

11-9

RW

010b

BUCK_TMOS[2-0]

Reserved. Write ‘010b’

8

RW 0 BUCK_FC

Reserved. Write ‘0’

7

RW 1 BUCK_AGAIN

Reserved. Write ‘1’

6

RW 0 BUCK_ADRES

Reserved. Write ‘0’

5-4

RW

10b

BUCK_BM[1-0]

Reserved. Write ‘10b’

3-0

RW

0101b

TST_CPREF[3-0]

Reserved. Write ‘0101b’

Table 24 LO1

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

XDIV

LO_TEST

_INT

LO_TST_CP[3] LO_TST_CP[2] LO_TST_CP[1] LO_TST_CP[0]

LO_ICPH

LO_BM_FIL[1] LO_BM_FIL[0]

LO_BM_DAC[1] LO_BM_DAC[0]

LO_BM_CML_C[1] LO_BM_CML_C[0]

LO_BM_CML_D[1] LO_BM_CML_D[0]

LO_BM_BVCO[1] LO_BM_BVCO[0]

LO_VCO_AMP[2] LO_VCO_AMP[1] LO_VCO_AMP[0]

PMUX_EN

PA_PHASE[1] PA_PHASE[0]

DAC_TEST_EN

DAC_TEST[7] DAC_TEST[6] DAC_TEST[5] DAC_TEST[4] DAC_TEST[3] DAC_TEST[2] DAC_TEST[1] DAC_TEST[0]

0 0 0 1 0 1 0 0 1 0 1 0 1 0 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0

0

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31

RW 0 XDIV XTAL frequency selection

0 = 16MHz

1 = 32MHz

30

RW 0 LO_TEST_INT

Reserved. Write ‘0’

29-26

RW

0101b

LO_TST_CP[3-0]

Reserved. Write ‘0101b’

Page 26

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

26 of 128

25

RW 0 LO_ICPH

Reserved. Write ‘0’

24-23

RW

01b

LO_BM_FIL[1-0]

Reserved. Write ‘01b’

22-21

RW

01b

LO_BM_DAC[10]

Reserved. Write ‘01b’

20-19

RW

01b

LO_BM_CML_C[

1-0]

Reserved. Write ‘01b’

18-17

RW

01b

LO_BM_CML_D

[1-0]

Reserved. Write ‘01b’

16-15

RW

01b

LO_BM_BVCO[1

-0]

Reserved. Write ‘01b’

14-12

RW

100b

LO_VCO_AMP[2

-0]

Reserved. Write ‘100b’

11

RW 0 PMUX_EN

Reserved. Write ‘0’

10-9

RW 0 PA_PHASE[1-0]

Reserved. Write ‘0’

8

RW 0 DAC_TEST_EN

Reserved. Write ‘0’

7-0

RW 0 DAC_TEST[7-0]

Reserved. Write ‘0’

Table 25 ADCCR

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

RSVD

SPEED_UP_TIME[7] SPEED_UP_TIME[6] SPEED_UP_TIME[5] SPEED_UP_TIME[4] SPEED_UP_TIME[3] SPEED_UP_TIME[2] SPEED_UP_TIME[1] SPEED_UP_TIME[0]

RSVD

CK_DAC_DLY

BYPASS_TESTBUF

SEL_TEST_EN

TESTREG[7] TESTREG[6] TESTREG[5] TESTREG[4] TESTREG[3] TESTREG[2] TESTREG[1] TESTREG[0]

RSVD

ADC_DIG_RST

ADC_CLK_SEL

ADC_DIV_BYPASS

ADC_DIV[3] ADC_DIV[2] ADC_DIV[1] ADC_DIV[0]

1 0 1 0 1 1 1 0 1 1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 1

1

W W W

W

RW

RW

RW

RW

RW

RW

RW

RW R RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW R RW

RW

RW

RW

RW

RW

RW

Bit

Type

Reset

Symbol

Description

31-28

R 0 RSVD

Reserved

27-20

RW

11101111b

SPEED_UP_TIM

E[7-0]

Reserved, write ‘11101111b’

19 R 0

RSVD

Reserved

18

RW 0 CK_DAC_DLY

Reserved

17

RW 1 BYPASS_TESTBU

F

Reserved

16

RW 0 SEL_TEST_EN

Reserved

15-8

RW 0 TESTREG[7-0]

Reserved

7 R 0

RSVD

Reserved

6

RW 1 ADC_DIG_RST

0 = Reset SAR ADC digital Interface;

5

RW 0 ADC_CLK_SEL

Select ADC source Clock

0 = 16MHz, 1: 32KHz

4

RW 0 ADC_DIV_BYPA

SS

‘1’ is bypass ADC Divider;

3-0

RW

0111b

ADC_DIV[3-0]

If ADC_DIV_BYPASS is ‘0’,

Page 27

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

27 of 128

ADC_CLK = ADC_SOURCE_CLK / (2<<ADC_DIV);

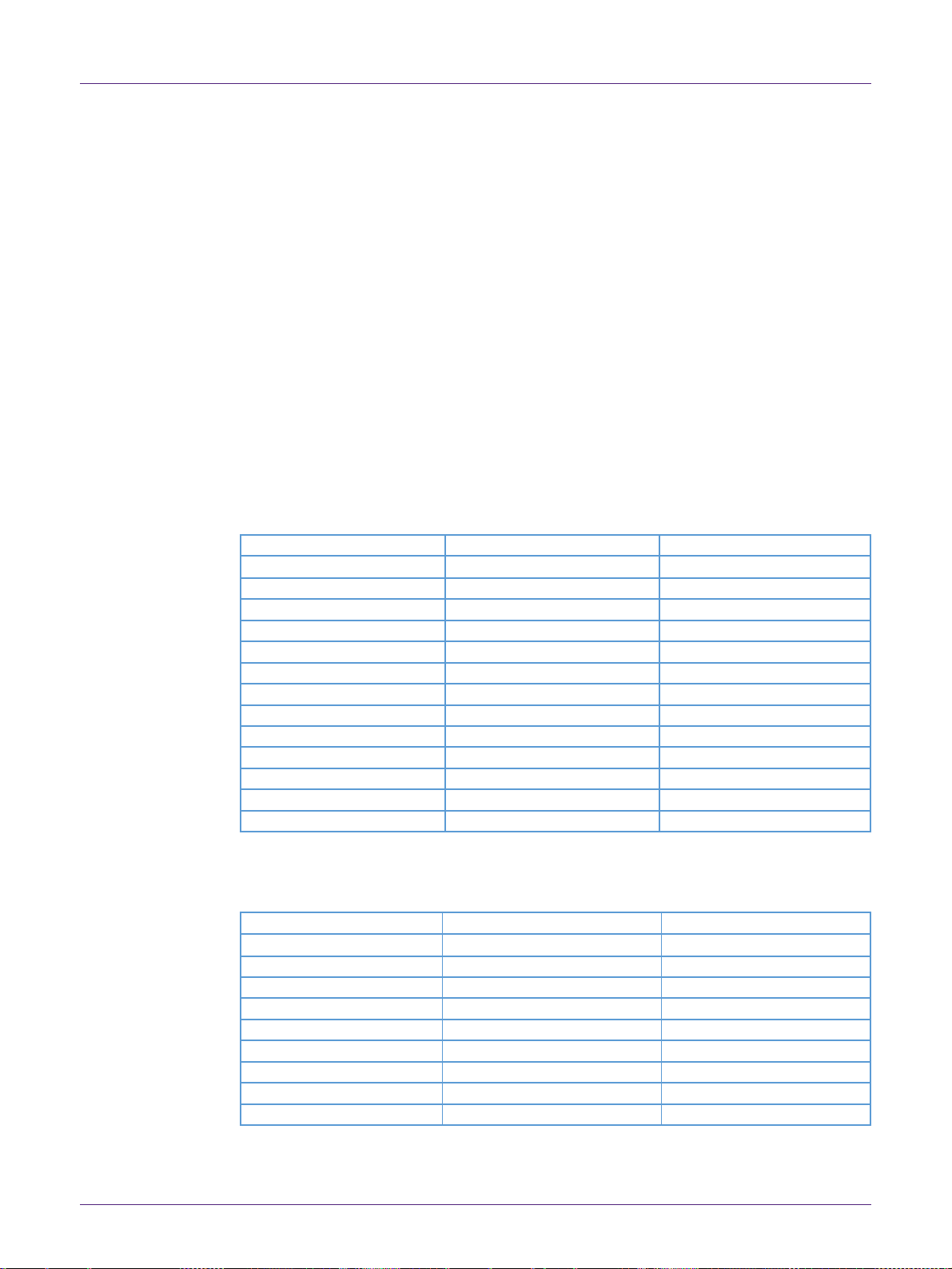

ANALOG_CTRL

Description of Word

Bit

Type

Reset

Name

Description

31-28

RW

0000b

ACMP0[3-0]

Comparator 0 reference voltage selection

0000b = Select external reference voltage

0001b = Select internal reference voltage (1/16

VDD)

0010b = Select internal reference voltage (2/16

VDD)

0011b = Select internal reference voltage (3/16

VDD)

0100b = Select internal reference voltage (4/16

VDD)

0101b = Select internal reference voltage (5/16

VDD)

0110b = Select internal reference voltage (6/16

VDD)

0111b = Select internal reference voltage (7/16

VDD)

1000b = Select internal reference voltage (8/16

VDD)

1001b = Select internal reference voltage (9/16

VDD)

1010b = Select internal reference voltage (10/16

VDD)

1011b = Select internal reference voltage (11/16

VDD)

1100b = Select internal reference voltage (12/16

VDD)

1101b = Select internal reference voltage (13/16

VDD)

1110b = Select internal reference voltage (14/16

VDD)

1111b = Select internal reference voltage (15/16

VDD)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9 8 7 6 5 4 3 2 1

0

ACMP0[3] ACMP0[2] ACMP0[1] ACMP0[0] ACMP1[3] ACMP1[2] ACMP1[1] ACMP1[0] BD[1]

BD[0]

EN_ACMP0 EN_ACMP1 EN_BT

EN_BD

EN_TS

ACMP1_VALUE ACMP0_VALUE ACMP1_HYST ACMP2_HYST AIN3_EN AIN2_EN AIN1_EN AIN0_EN BUCK_PMDR BUCK_NMDR PA_GAIN[4] XSP_CSEL SLEEP_TRIG

NC[3-0]

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1

1

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

Page 28

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

28 of 128

27-24

RW

0000b

ACMP1[3-0]

Comparator 1 reference voltage selection

0000b = Select external reference voltage

0001b = Select internal reference voltage (1/16

VDD)

0010b = Select internal reference voltage (2/16

VDD)

0011b = Select internal reference voltage (3/16

VDD)

0100b = Select internal reference voltage (4/16

VDD)

0101b = Select internal reference voltage (5/16

VDD)

0110b = Select internal reference voltage (6/16

VDD)

0111b = Select internal reference voltage (7/16

VDD)

1000b = Select internal reference voltage (8/16

VDD)

1001b = Select internal reference voltage (9/16

VDD)

1010b = Select internal reference voltage (10/16

VDD)

1011b = Select internal reference voltage (11/16

VDD)

1100b = Select internal reference voltage (12/16

VDD)

1101b = Select internal reference voltage (13/16

VDD)

1110b = Select internal reference voltage (14/16

VDD)

1111b = Select internal reference voltage (15/16

VDD)

23-22

RW

00b

BD[1-0]

Browned out detector threshold voltage selection

00b = 1.76V

01b = 1.7V

10b = 1.65V

11b = 1.6V

21

RW

0

EN_ACMP0

1 is Enable comparator 0

20

RW

0

EN_ACMP1

1 is Enable comparator 1

19

RW

0

EN_BT

1 is Enable battery monitor

18

RW

0

EN_BD

1 is Enable browned out detector

17

RW

0

EN_TS

Reserved, Write ‘0’

16

RW 0 ACMP1_VALUE

0 = When ACMP1 is 1, generate interrupt;

1 = When ACMP1 is 0, generate interrupt;

15

RW 0 ACMP0_VALUE

0 = When ACMP0 is 1, generate interrupt;

1 = When ACMP0 is 0, generate interrupt;

14

RW 0 ACMP0_HYST

1 is Enable hysteresis of analog comparator 0

13

RW 0 ACMP1_HYSR

1 is Enable hysteresis of analog comparator 1

12-9

RW 0 AINx_EN

1 is Enable P0_7/6 and P3_1/0 as Analog input

ONLY.

Page 29

NXP Semiconductors

QN902x

User Manual of QN902x

UM10996

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

User Manual

Rev 1.3 — 05 November 2018

29 of 128

8

RW 0 BUCK_PMDR

REVD

7

RW 0 BUCK_NMDR

REVD

6

RW 0 PA_GAIN[4]

Together with PA_GAIN[0-3], PA_GAIN[0-4]

means:

11111---------- 4dBm

01111---------- 3dBm

11110---------- 2dBm

01110---------- 1dBm

01101---------- 0dBm

01100---------- -2dBm

01010---------- -4dBm

01001---------- -6dBm

01000---------- -8dBm

00110---------- -10dBm

00101---------- -12dBm

00100---------- -14dBm

00010---------- -16dBm

00001---------- -18dBm

00000---------- -20dBm

5

RW 0 XSP_CSEL

Write ‘1’.

4

RW 0 SLEEP_TRIG

When it is 1, sleep counter registers of BLE can be

reloaded during BLE deep sleep state.

3-0

RW