PX1041A

PCI Express stand-alone X4 PHY

Rev. 01 — 21 June 2007 Objective data sheet

1. General description

The PX1041A is a high-performance, low-power, four-lane PCI Express electrical

PHYsical layer (PHY) that handles the low level PCI Express protocol and signaling. The

PX1041A PCI Express PHY is compliant to the

Rev. 1.0a

Recovery (CDR), dataserialization and de-serialization, 8b/10b encoding, analog buffers,

elastic buffer and receiver detection, and provides superior performance to the Media

Access Control (MAC) layer devices.

The PX1041A is a 2.5 Gbit/s PCI Express PHY with 4 × 8-bit data PXPIPE interface. Its

PXPIPE interface is a superset of the PHY Interface for the PCI Express (PIPE)

specification, enhanced and adapted for off-chip applications with the introduction of a

source synchronous clock for transmit and receive data. The 4 × 8-bit data interface

operates at 250 MHz with SSTL Class I signaling at 2.5 V or 1.8 V. The SSTL signaling is

compatible with the I/O interfaces available in FPGA products.

, and

Rev. 1.1

PCI Express Base Specification,

. The PX1041A includes features such as Clock and Data

2. Features

2.1 PCI Express interface

The PX1041A PCI Express PHY supports advanced power management functions. The

PX1041AI is for the industrial temperature range (−40 °C to +85 °C).

n Compliant to

n Four PCI Express 2.5 Gbit/s lane

n Data and clock recovery from serial stream

n Serializer and De-serializer (SerDes)

n Receiver detection

n 8b/10b coding and decoding, elastic buffer and word alignment

n Supports direct disparity control for use in transmitting compliance pattern

n Supports lane polarity inversion

n Low jitter and Bit Error Rate (BER)

n Supports PCI Express-side parallel loopback

n Supports PXPIPE-side parallel loopback

n Supports receiver lane-to-lane deskew (optional)

n Supports lane reversal (optional)

PCI Express Base Specification 1.0a and 1.1

2.2 PHY/MAC interface

n Based on Intel PHY Interface for PCI Express architecture v2.0 (PIPE)

n Adapted for off-chip with additional synchronous clock signals (PXPIPE)

NXP Semiconductors

n PIPE mode selectable

n 4 × 8-bit parallel data interface for transmit and receive at 250 MHz

n SSTL Class I signaling at 2.5 V or 1.8 V, without select pin

2.3 JTAG interface

n JTAG (IEEE 1149.1) boundary scan interface

n Built-In Self Test (BIST) controller tests SerDes and I/O blocks at speed

n 3.3 V CMOS signaling

2.4 Power management

n Dissipates < 1 W in L0 normal mode

n Support power management of L0, L0s, L1, and L2

2.5 Clock

n 100 MHz external reference clock with ±300 ppm tolerance

n Supports spread spectrum clock to reduce EMI

n On-chip reference clock termination

PX1041A

PCI Express stand-alone X4 PHY

2.6 Miscellaneous

n LFBGA208 lead free package

n Operating ambient temperature

u PX1041A for commercial range: 0 °C to +70 °C

u PX1041AI for industrial range: −40 °C to +85 °C

n ESD protection voltage for Human Body Model (HBM): 2000 V

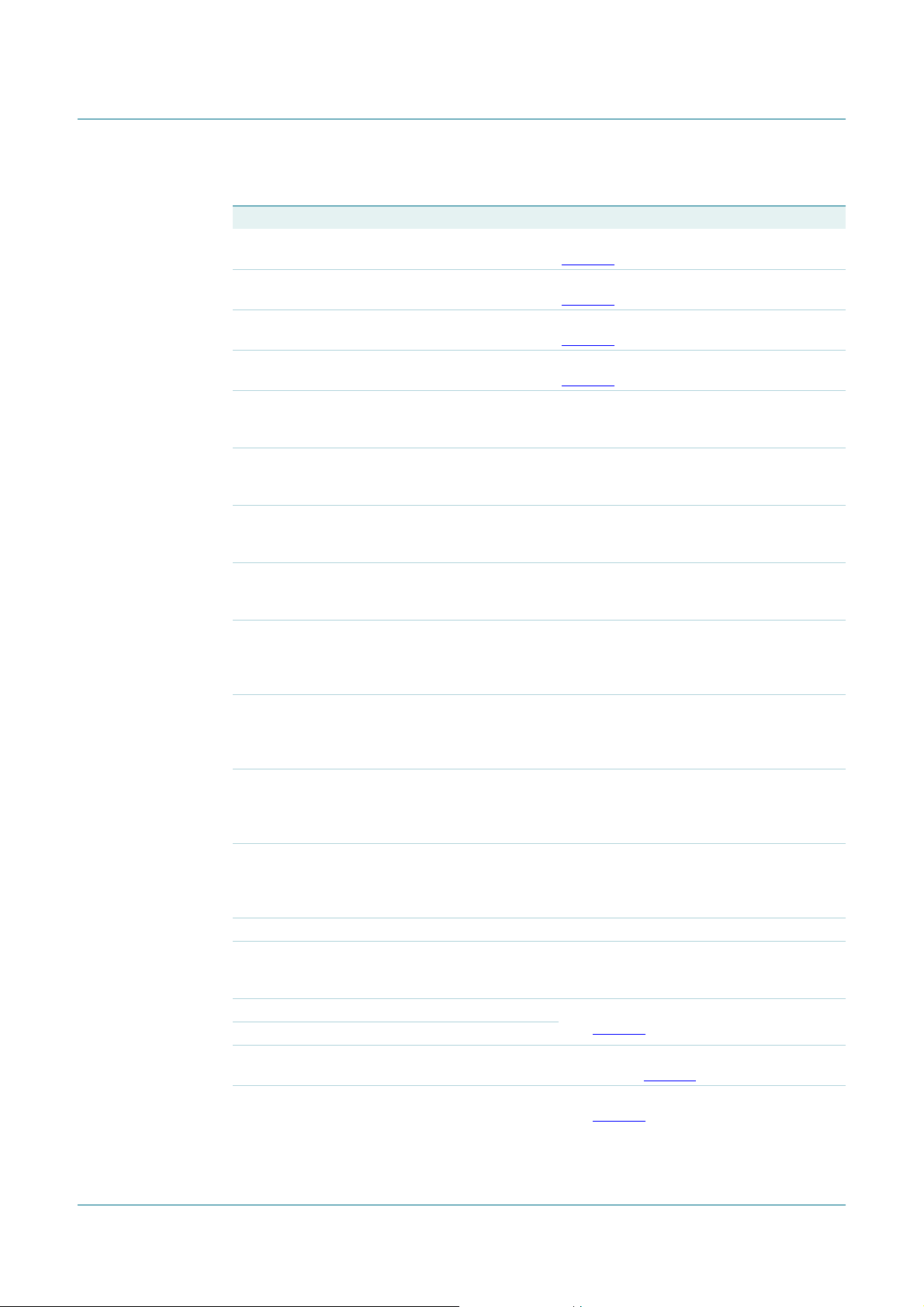

3. Quick reference data

Table 1. Quick reference data

Symbol Parameter Conditions Min Typ Max Unit

V

DDD1

V

DDD2

V

DDD3

V

DD

V

DDA1

V

DDA2

f

clk(ref)

T

amb

digital supply voltage 1 for JTAG I/O 3.0 3.3 3.6 V

digital supply voltage 2 for SSTL_18 I/O

digital supply voltage 3 for core 1.15 1.2 1.25 V

supply voltage for high-speed

analog supply voltage 1 for serializer 1.15 1.2 1.25 V

analog supply voltage 2 for serializer 3.0 3.3 3.6 V

reference clock frequency 99.97 100 100.03 MHz

ambient temperature operating

[1]

1.7 1.8 1.9 V

[1]

for SSTL_2 I/O

serial I/O and PVT

commercial 0 - +70 °C

industrial −40 - +85 °C

2.3 2.5 2.7 V

1.15 1.2 1.25 V

[1] No select pin needed.

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 2 of 36

NXP Semiconductors

4. Ordering information

Table 2. Ordering information

Type number Solder process Package

Name Description Version

PX1041A-EL1/G Pb-free (SnAgCu

solder ball compound)

PX1041AI-EL1/G Pb-free (SnAgCu

solder ball compound)

LFBGA208 plastic low profile fine-pitch ball grid array package;

LFBGA208 plastic low profile fine-pitch ball grid array package;

5. Marking

Table 3. Lead-free package marking

Line Marking Description

A PX1041A-EL1/G

PX1041AI-EL1/G

B xxxxxxx diffusion lot number

C 2PGyyww manufacturing code:

PX1041A

PCI Express stand-alone X4 PHY

SOT631-4

208 balls; body 15 × 15 × 1mm

SOT631-4

208 balls; body 15 × 15 × 1mm

full basic type number

[1]

2 = diffusion site

P = assembly site

G = lead-free

yy = year code

ww = week code

[1] Industrial temperature range.

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 3 of 36

NXP Semiconductors

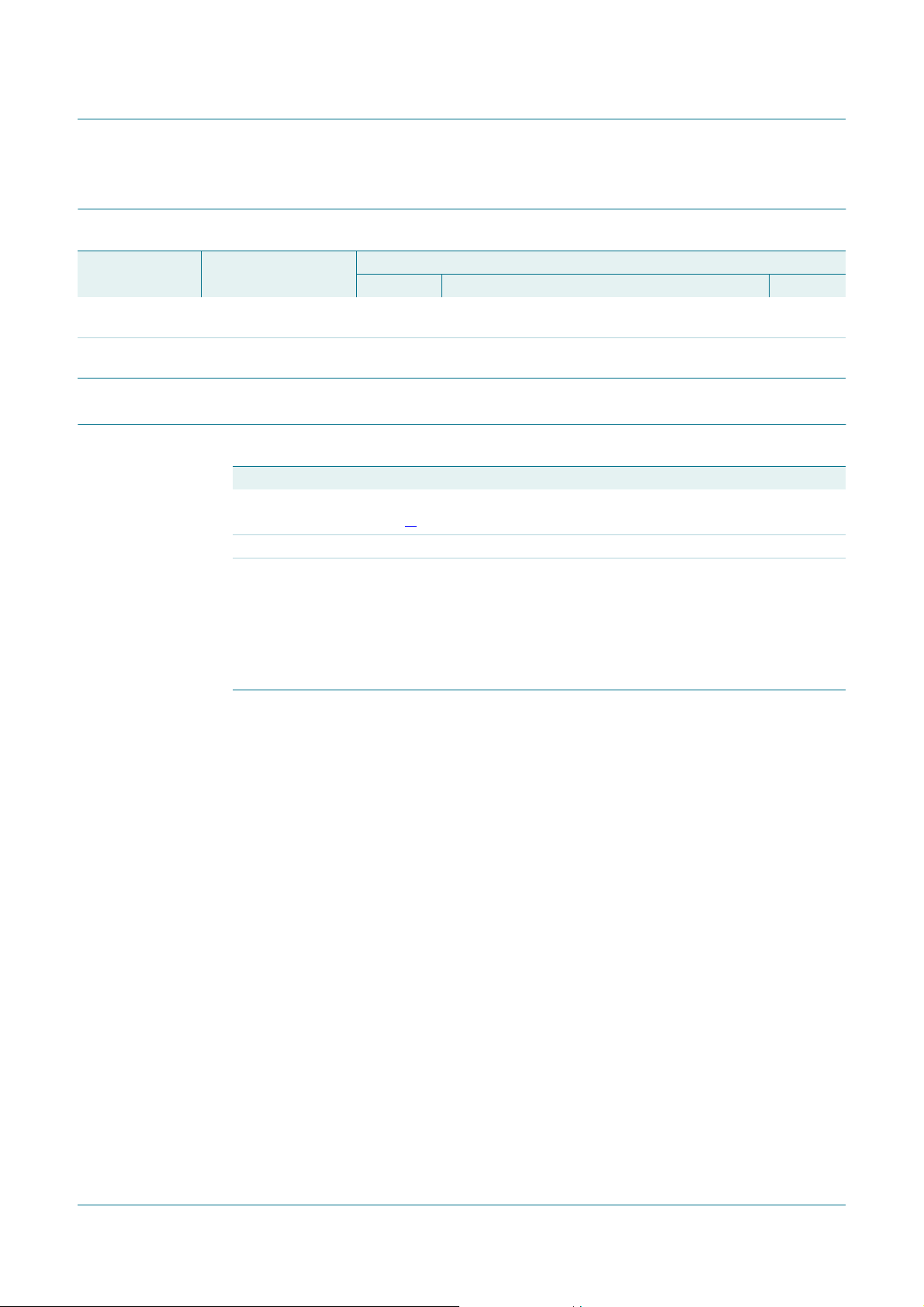

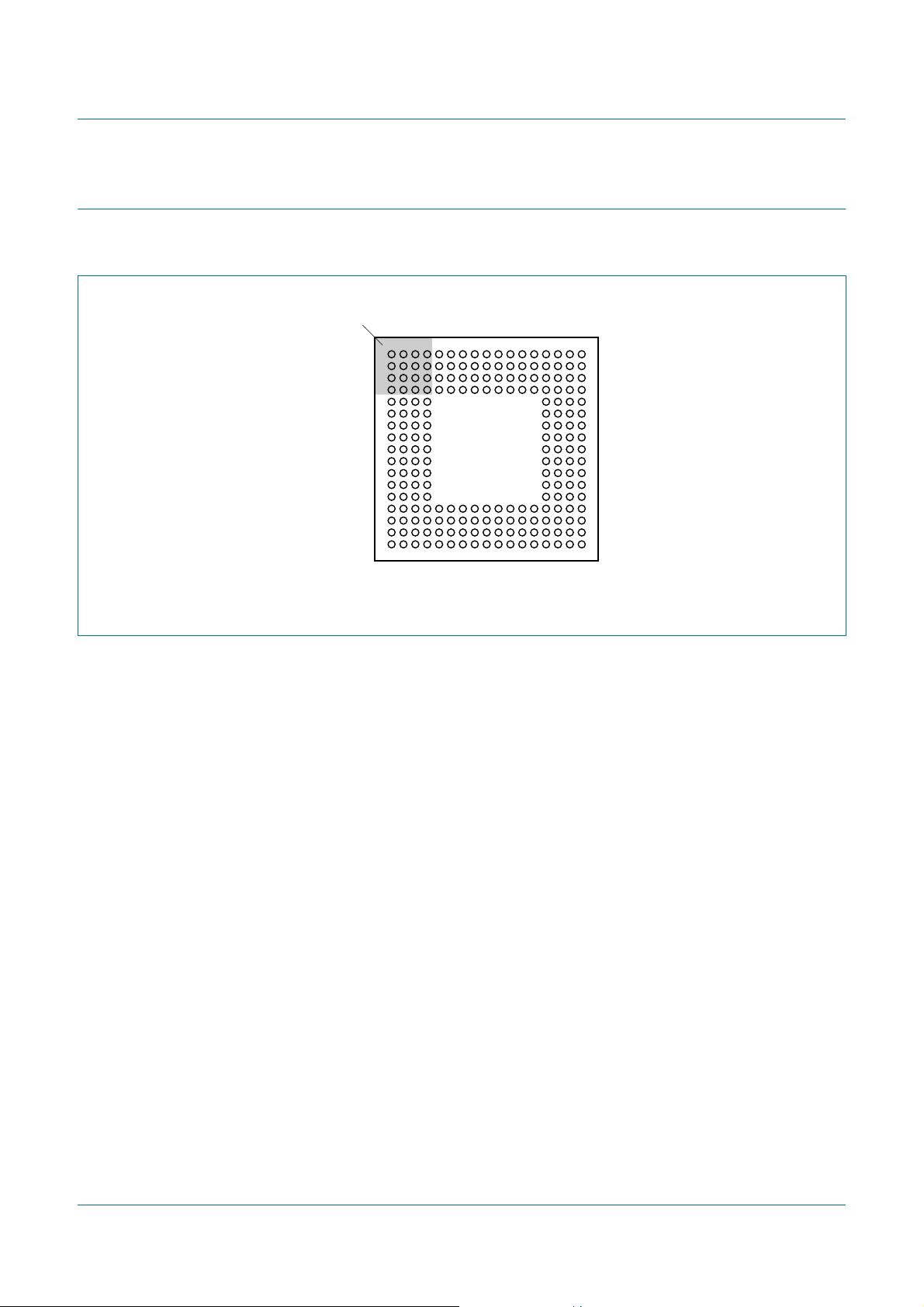

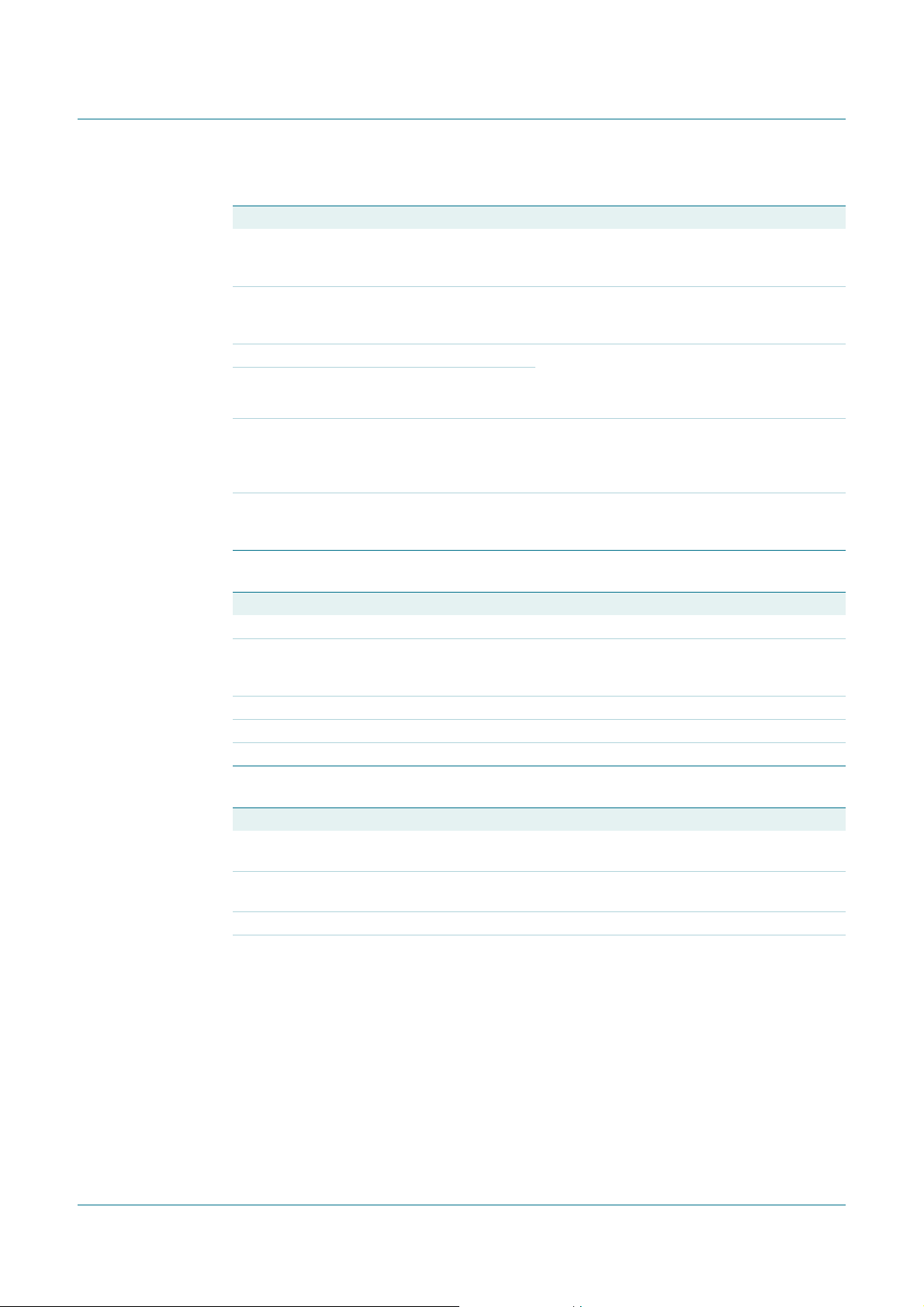

6. Block diagram

PX1041A

PCI Express stand-alone X4 PHY

TXCLK

Ln_TxData0

Ln_TxData1

ENCODE

PARALLEL

]

7:0

[

L0_TXDATA

8b/10b

TO

SERIAL

250 MHz

clock

]

7:0

[

L0_RXDATA

REGISTER

8

10b/8b

DECODE

ELASTIC

BUFFER

10

SERIAL

TO

PARALLEL

DATA

RECOVERY

CIRCUIT

PCI Express MAC

RESET_N

PCI Express PHY

LANE 0

K28.5

DETECTION

CLOCK RECOVERY

CIRCUIT PLL

RXCLK

L1_TXDATA[7:0]

LANE 1

L1_RXDATA[7:0]

L2_TXDATA[7:0]

LANE 2

L2_RXDATA[7:0]

L3_TXDATA[7:0]

LANE 3

L3_RXDATA[7:0]

TX I/O

L0_TX_P

L0_TX_N

L0_RX_P

Fig 1. Block diagram of PX1041A

RX I/O

bit stream at 2.5 Gbit/s

GENERATOR

REFCLK I/O

L0_RX_N

CLK

REFCLK_P

REFCLK_N

L1_TX_P

L1_TX_N

L1_RX_P

L1_RX_N

L2_TX_P

L2_TX_N

L2_RX_P

L2_RX_N

L3_TX_P

L3_TX_N

L3_RX_P

002aac432

L3_RX_N

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 4 of 36

NXP Semiconductors

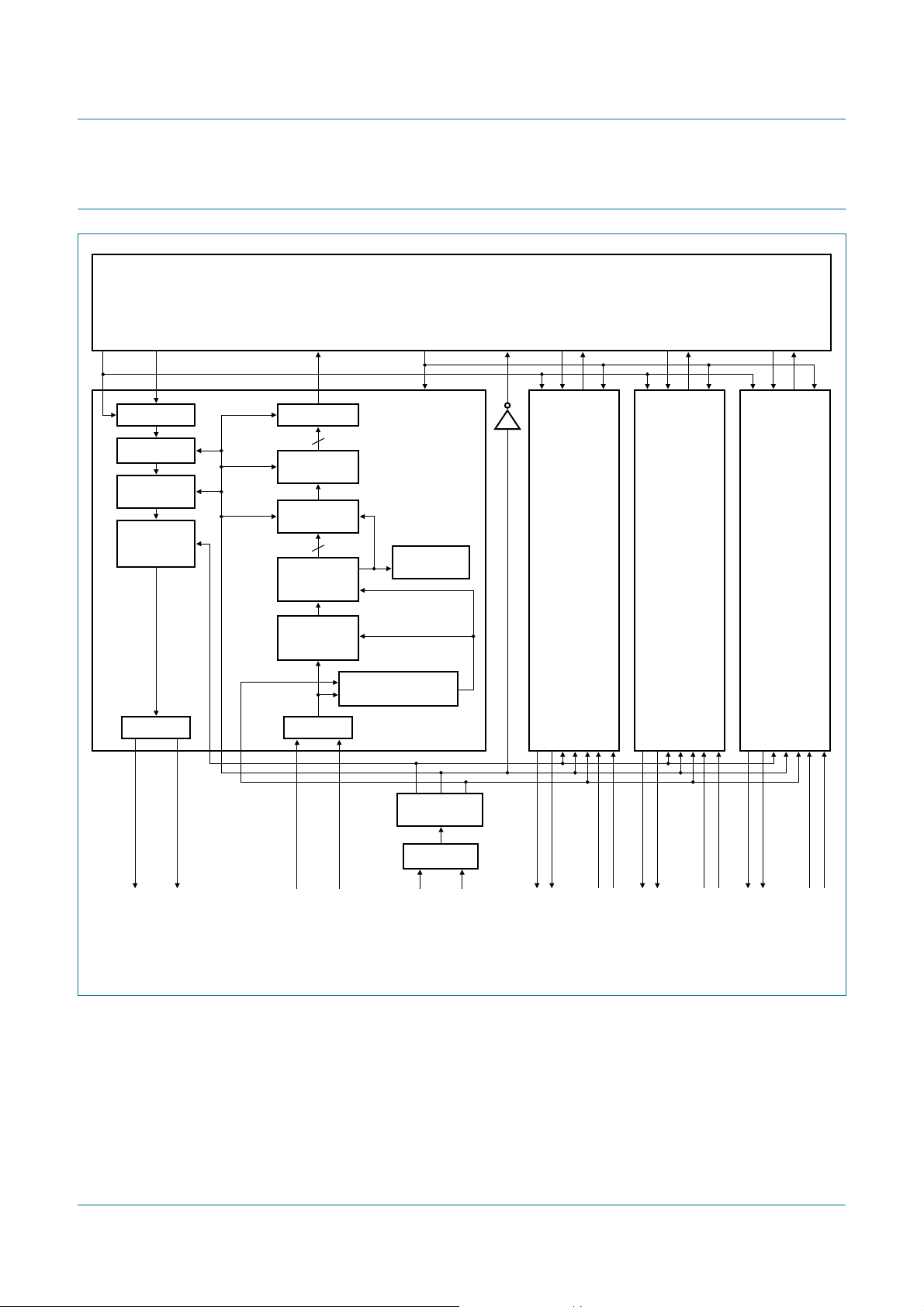

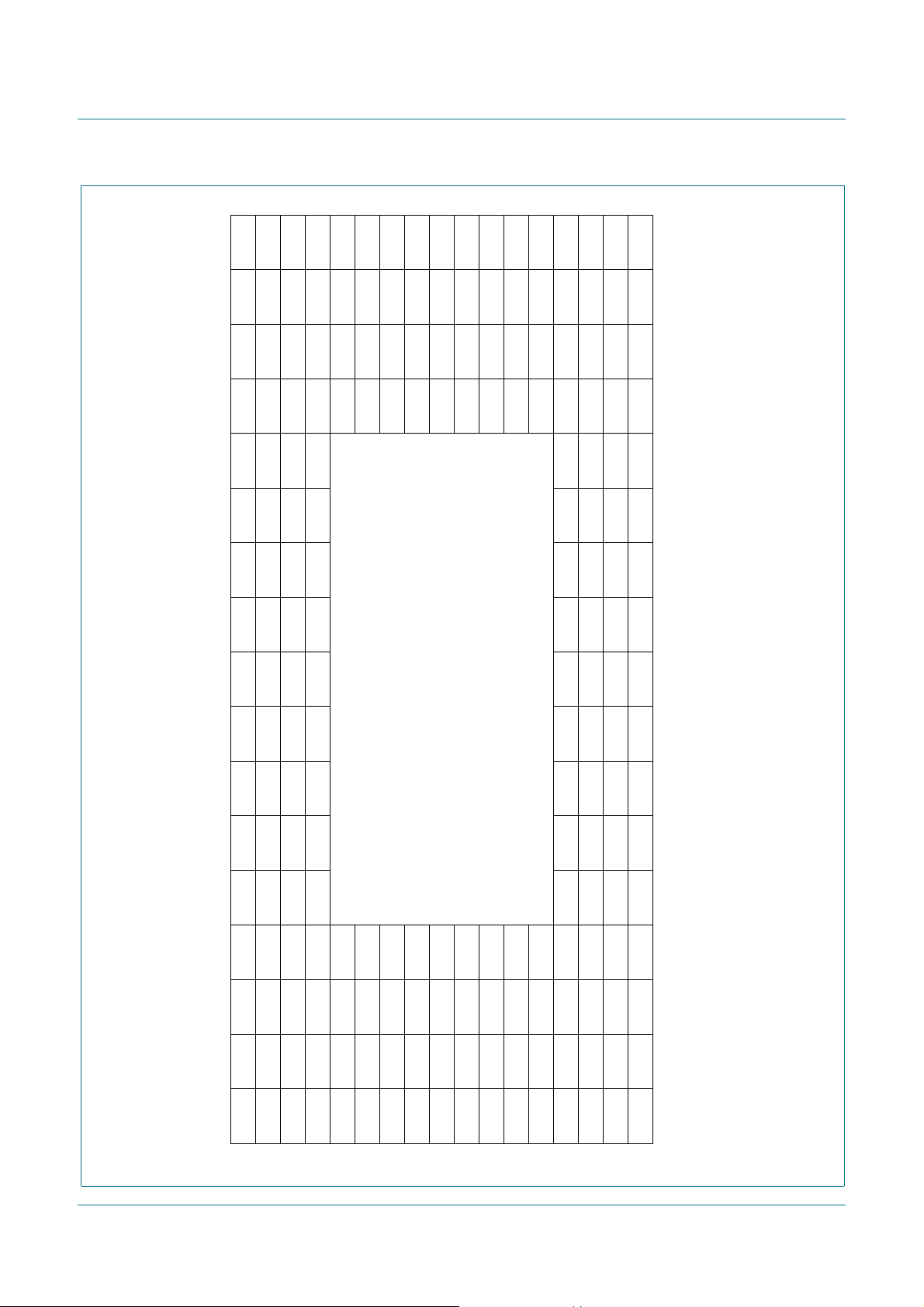

7. Pinning information

7.1 Pinning

ball A1

index area

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

246810121314

1357911

PX1041A-EL1/G

PX1041AI-EL1/G

Transparent top view

16

15 17

002aac433

PX1041A

PCI Express stand-alone X4 PHY

Fig 2. Pin configuration for LFBGA208

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 5 of 36

NXP Semiconductors

L1_

RXDATA6

L1_

PX1041A

PCI Express stand-alone X4 PHY

L1_

L1_

L1_

L1_

L1_

L1_

L1_

L1_

L1_

L2_

L2_

L2_

L2_

L2_

L2_

TXDATA7

TXDATA6

TXDATA4

TXDATA2

RXDATA5

RXDATA4

RXDATA3

RXDATA2

RXDATA0

TXDATA0

RXDATA7

RXDATA6

RXDATA5

RXDATA3

002aac434

RXDATA1

RXDATA0

SS

L1_

RXDATA7

DESKEW_

V

START

L1_

RXDATAK

VALID

DESKEW_

PWRDWN1

SS

V

RESET_N RXCLK TXCLK

L0_

L0_

10 11 12 13 14 15 16 17

L0_

L0_

L0_

PIPELOOPB PWRDWN0

L0_

L0_

TXDATA2

TXDATA1

TXDATA0

L0_

L0_

L0_

L0_

TXIDLE

TXDATA3

SS

L0_

V

TXDATAK

L0_

TXDATA6

TXCOMP

L0_

RXPOL

RXDATA1

TXDATA4

TXDATA5

TXDATA7

RXDATA0

SS

L1_

V

RXIDLE

RXDET_

PHYSTATUS

SS

V

LANE

SEL

PIPEMODE

EN

ENCODING

DDD2

V

DDD2

V

SS

V

DDD2

V

L1_

RXDATA1

L1_

LOOPB

RXSTATUS2

L1_

RXVALID

REVERSAL

L1_

SS

V

RXSTATUS1

DDD2

V

L1_

L1_

DDD2

V

TXDATA5

RXSTATUS0

L1_

L1_

DDD2

V

TXDATA3

L1_

RXPOL

SS

V

TXDATAK

DDD2

V

L1_

TXDATA1

L1_

TXIDLE

L1_

TXCOMP

L2_

L2_

L2_

RXDATAK

L2_

RXIDLE

L2_

RXVALID

SS

V

RXSTATUS2

RXPOL

L2_

RXDATA4

L2_

RXSTATUS1

SS

V

L2_

TXCOMP

DDD2

V

DDD2

V

DDD2

V

SS

V

DDD3

V

L2_

L2_

L2_

L2_

L2_

L3_

L3_

L3_

L3_

RXDATA2

L2_

RXSTATUS0

L2_

TXDATA4

TXIDLE

L2_

TXDATAK

L3_

RXIDLE

RXDATAK

L3_

RXSTATUS2

L3_

RXSTATUS1

SS

L2_

V

TXDATA7

L2_

TXDATA6

TXDATA5

VREFS

TXDATA3

SS

L2_

V

TXDATA2

L2_

TXDATA1

TXDATA0

L3_

RXDATA6

RXDATA7

SS

L3_

V

RXDATA5

L3_

RXDATA3

RXDATA4

L3_

RXDATA2

RXDATA1

SS

L0_

V

RXDATA2

L0_

L0_

RXDATA4

L0_

L0_

RXDATA5

SS

L0_

RXDATA7

23456789

TMS TDI

TRST_N TCK V

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx

xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

1

REFCLK_P

REFCLK_N

B

A

DDD2

L0_

V

RXVALID

SS

L0_

V

RXDATA3

RXSTATUS0

L0_

L0_

RXDATA6

L0_

RXSTATUS1

RXDATAK

TDO

DDD1

V

SS

V

C

RXSTATUS2

L0_

RXIDLE

PVT

SS

V

L0_RX_P

D

DDA2

V

SS

V

L0_TX_P V

SS

V

V

SS

V

L0_RX_N

F

E

DD

SS

DD

L0_TX_N V

SS

V

L1_RX_P

G

DD

V

SS

V

L1_TX_P V

SS

V

V

SS

V

L1_RX_N

J

H

DDA1

SS

DDA1

L1_TX_N V

SS

V

L2_RX_P

K

DDA1

V

SS

V

L2_TX_P V

SS

V

V

SS

V

L2_RX_N

L

M

DDA1

SS

L3_

DDA1

L3_

L2_TX_N V

SS

V

L3_RX_P

N

DDD3

V

SS

V

SS

V

SS

V

L3_RX_N

P

L3_

RXSTATUS0

L3_

RXVALID

L3_

RXPOL

TXDATAK

L3_

TXIDLE

TXCOMP

L3_

TXDATA0

SS

V

SS

V

R

SS

V

L3_

TXDATA6

L3_

TXDATA4

SS

V

L3_

TXDATA1

SS

V

L3_TX_P

T

L3_

RXDATA0

L3_

TXDATA7

L3_

TXDATA5

L3_

TXDATA3

L3_

TXDATA2

SS

V

L3_TX_N

U

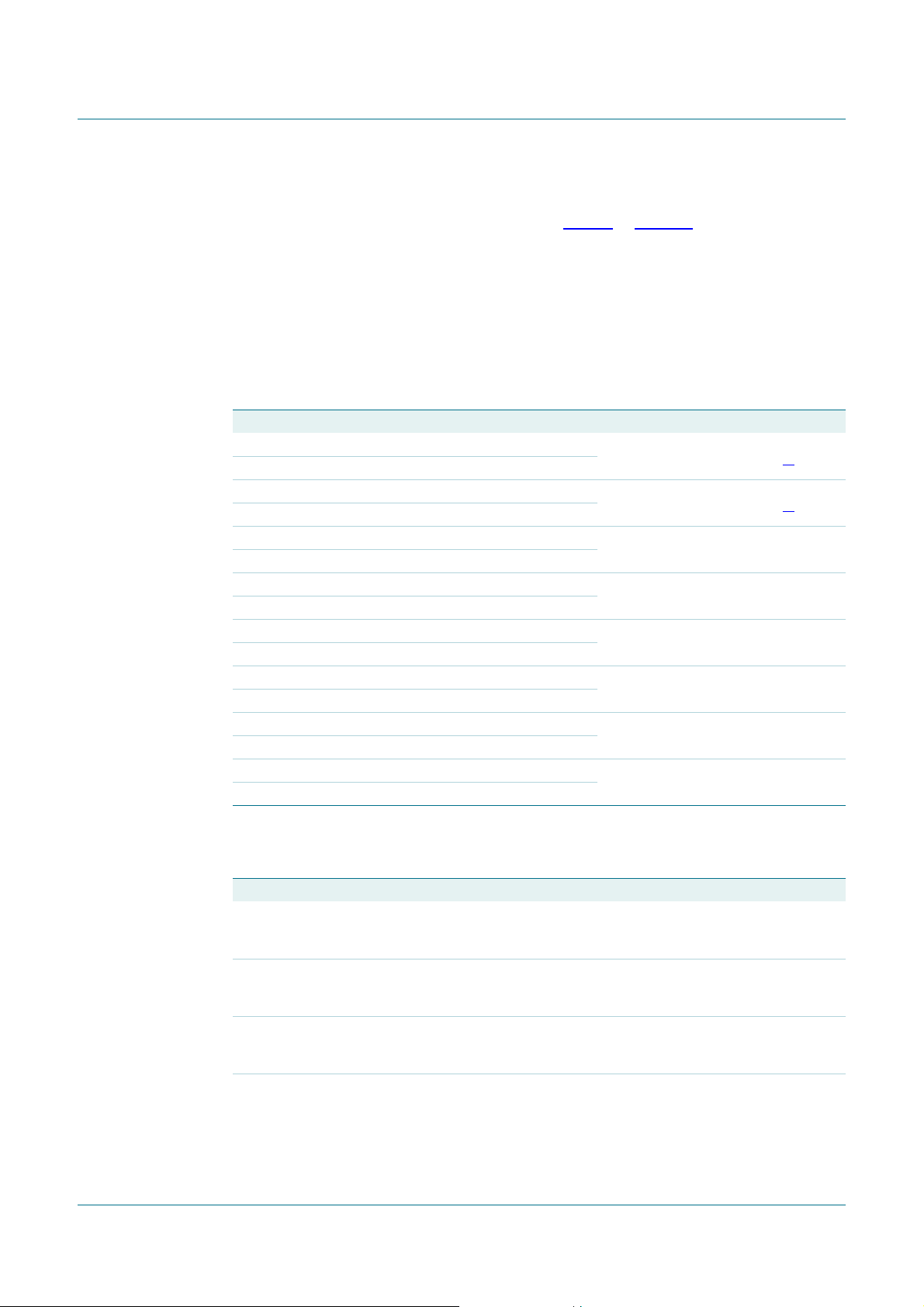

Transparent top view.

Fig 3. Ball mapping

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 6 of 36

NXP Semiconductors

7.2 Pin description

The PHY input and output pins are described in Table 4 to Table 11. Note that input and

output is defined from the perspective of the PHY. Thus a signal on a pin described as an

output is driven by the PHY and a signal on a pin described as an input is received by the

PHY. A basic description of each pin is provided.

Signals named Lx_*, designate the per-lane signal where x = (0 to 3). For example,

Lx_RX_P expands to the following signals L0_RX_P, L1_RX_P, L2_RX_P and L3_RX_P.

All SSTL signaling is 2.5 V or 1.8 V selectable.

Table 4. PCI Express serial data lines

Symbol Pin Type Signaling Description

L0_RX_P D1 input PCIe I/O lane 0 differential input receive pair

L0_RX_N E1 input PCIe I/O

L0_TX_P F3 output PCIe I/O lane 0 differential output transmit pair

L0_TX_N G3 output PCIe I/O

L1_RX_P G1 input PCIe I/O lane 1 differential input receive pair

L1_RX_N H1 input PCIe I/O

L1_TX_P J3 output PCIe I/O lane 1 differential output transmit pair

L1_TX_N K3 output PCIe I/O

L2_RX_P K1 input PCIe I/O lane 2 differential input receive pair

L2_RX_N L1 input PCIe I/O

L2_TX_P M3 output PCIe I/O lane 2 differential output transmit pair

L2_TX_N N3 output PCIe I/O

L3_RX_P N1 input PCIe I/O lane 3 differential input receive pair

L3_RX_N P1 input PCIe I/O

L3_TX_P T1 output PCIe I/O lane 3 differential output transmit pair

L3_TX_N U1 output PCIe I/O

PX1041A

PCI Express stand-alone X4 PHY

with 50 Ω on-chip termination

with 50 Ω on-chip termination

with 50 Ω on-chip termination

with 50 Ω on-chip termination

with 50 Ω on-chip termination

with 50 Ω on-chip termination

with 50 Ω on-chip termination

with 50 Ω on-chip termination

[1]

[1]

[1] As PCIe specification defined.

Table 5. PXPIPE interface transmit data signals

Symbol Pin Type Signaling Description

L0_TXDATA[7:0] A9, B9, A10,

A11, B11,

A12, B12, C12

L0_TXDATAK C10 input SSTL selection input for the symbols of

L1_TXDATA[7:0] G17, H17,

H16, J17, J16,

K17, L16, L17

L1_TXDATAK K15 input SSTL selection input for the symbols of

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 7 of 36

input SSTL 8-bit transmit data input from the MAC

to the PHY lane 0

transmit data at lane 0;

LOW = data byte; HIGH = control byte

input SSTL 8-bit transmit data input from the MAC

to the PHY lane 1

transmit data at lane 1;

LOW = data byte; HIGH = control byte

NXP Semiconductors

PX1041A

PCI Express stand-alone X4 PHY

Table 5. PXPIPE interface transmit data signals

Symbol Pin Type Signaling Description

L2_TXDATA[7:0] U16, T15,

U15, R14,

T14, U13,

T12, U12

L2_TXDATAK R12 input SSTL selection input for the symbols of

L3_TXDATA[7:0] U6, T6, U5,

T5, U4, U3,

T3, R3

L3_TXDATAK R5 input SSTL selection input for the symbols of

Table 6. PXPIPE interface receive data signals

Symbol Pin Type Signaling Description

L0_RXDATA[7:0] A4, B5, A5,

A6, B6, A7,

B8, A8

L0_RXDATAK C4 output SSTL selection output for the symbols of

L1_RXDATA[7:0] A16, A17,

B17, C17,

D17, E17,

F16, F17

L1_RXDATAK C16 output SSTL selection output for the symbols of

L2_RXDATA[7:0] M17, N17,

P17, P16,

R17, R16,

T17, U17

L2_RXDATAK M16 output SSTL selection output for the symbols of

L3_RXDATA[7:0] U11, T11,

U10, U9, T9,

T8, U8, U7

L3_RXDATAK R10 output SSTL selection output for the symbols of

input SSTL 8-bit transmit data input from the MAC

input SSTL 8-bit transmit data input from the MAC

output SSTL 8-bit receive data output from the PHY

output SSTL 8-bit receive data output from the PHY

output SSTL 8-bit receive data output from the PHY

output SSTL 8-bit receive data output from the PHY

…continued

to the PHY lane 2

transmit data at lane 2;

LOW = data byte; HIGH = control byte

to the PHY lane 3

transmit data at lane 3;

LOW = data byte; HIGH = control byte

lane 0 to the MAC

receive data at lane 0;

LOW = data byte; HIGH = control byte

lane 1 to the MAC

receive data at lane 1;

LOW = data byte; HIGH = control byte

lane 2 to the MAC

receive data at lane 2;

LOW = data byte; HIGH = control byte

lane 3 to the MAC

receive data at lane 3;

LOW = data byte; HIGH = control byte

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 8 of 36

NXP Semiconductors

Table 7. PXPIPE interface command signals

Symbol Pin Type Signaling Description

L0_TXIDLE C11 input SSTL forces lane 0 TX output to electrical idle (see

L1_TXIDLE L15 input SSTL forces lane 1 TX output to electrical idle (see

L2_TXIDLE R13 input SSTL forces lane 2 TX output to electrical idle (see

L3_TXIDLE R4 input SSTL forces lane 3 TX output to electrical idle (see

L0_TXCOMP C9 input SSTL used when transmitting the compliance

L1_TXCOMP L14 input SSTL used when transmitting the compliance

L2_TXCOMP P13 input SSTL used when transmitting the compliance

L3_TXCOMP P4 input SSTL used when transmitting the compliance

L0_RXPOL C8 input SSTL signals the PHY to perform a polarity

L1_RXPOL J15 input SSTL signals the PHY to perform a polarity

L2_RXPOL N14 input SSTL signals the PHY to perform a polarity

L3_RXPOL P5 input SSTL signals the PHY to perform a polarity

RESET_N A13 input SSTL PHY reset input; active LOW

RXDET_ LOOPB E15 input SSTL instructs the PHY to begin a receiver

PWRDWN0 C14 input SSTL transceiverpower-upandpower-down inputs

PWRDWN1 B14 input SSTL

DESKEW_ START B15 input SSTL signals the PHY to start a lane to lane

LANEREVERS E14 input SSTL signals the PHY to perform lane reversal

PX1041A

PCI Express stand-alone X4 PHY

Table 13)

Table 13)

Table 13)

Table 13)

pattern at lane 0; HIGH-levelsetstherunning

disparity to negative

pattern at lane 1; HIGH-levelsetstherunning

disparity to negative

pattern at lane 2; HIGH-levelsetstherunning

disparity to negative

pattern at lane 3; HIGH-levelsetstherunning

disparity to negative

inversion on the receive data at lane 0;

LOW = PHY does no polarity inversion;

HIGH = PHY does polarity inversion

inversion on the receive data at lane 1;

LOW = PHY does no polarity inversion;

HIGH = PHY does polarity inversion

inversion on the receive data at lane 2;

LOW = PHY does no polarity inversion;

HIGH = PHY does polarity inversion

inversion on the receive data at lane 3;

LOW = PHY does no polarity inversion;

HIGH = PHY does polarity inversion

detection operation or to begin loopback;

LOW = reset state

(see

Table 12); 0x2 = reset state

deskew (see

Table 15), LOW = reset state

(see

Table 15); LOW = reset state

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 9 of 36

NXP Semiconductors

PX1041A

PCI Express stand-alone X4 PHY

Table 7. PXPIPE interface command signals

Symbol Pin Type Signaling Description

PIPELOOPB C13 input SSTL signals the PHY to do loopback at PXPIPE

PIPESEL D13 input SSTL signals the PHY to switch from PXPIPE to

ENCODEN D12 input SSTL enable the internal encoder to replace

Table 8. PXPIPE interface status signals

Symbol Pin Type Signaling Description

L0_RXVALID C7 output SSTL indicates symbol lock and valid data on

L1_RXVALID F14 output SSTL indicates symbol lock and valid data on

L2_RXVALID M14 output SSTL indicates symbol lock and valid data on

L3_RXVALID R6 output SSTL indicates symbol lock and valid data on

L0_RXIDLE D4 output SSTL indicates receiver detection of an electrical

L1_RXIDLE D16 output SSTL indicates receiver detection of an electrical

L2_RXIDLE M15 output SSTL indicates receiver detection of an electrical

L3_RXIDLE R11 output SSTL indicates receiver detection of an electrical

L0_RXSTATUS0 C6 output SSTL encodes receiver status and error codes for

L0_RXSTATUS1 C5 output SSTL

L0_RXSTATUS2 D5 output SSTL

L1_RXSTATUS0 H15 output SSTL encodes receiver status and error codes for

L1_RXSTATUS1 G15 output SSTL

L1_RXSTATUS2 F15 output SSTL

L2_RXSTATUS0 R15 output SSTL encodes receiver status and error codes for

L2_RXSTATUS1 P15 output SSTL

L2_RXSTATUS2 N15 output SSTL

L3_RXSTATUS0 R7 output SSTL encodes receiver status and error codes for

L3_RXSTATUS1 R8 output SSTL

L3_RXSTATUS2 R9 output SSTL

DESKEW_VALID C15 output SSTL indicates the lane deskew is completed and

PHYSTATUS D15 output SSTL used to communicate completion of several

…continued

side (see

PIPE interface, LOW = reset state

side-band signals to perform selected

functions (see Table 15)

RX_DATA and RX_DATAK at lane 0

RX_DATA and RX_DATAK at lane 1

RX_DATA and RX_DATAK at lane 2

RX_DATA and RX_DATAK at lane 3

idle at lane 0; this is an asynchronous signal

idle at lane 1; this is an asynchronous signal

idle at lane 2; this is an asynchronous signal

idle at lane 3; this is an asynchronous signal

the received data stream and receiver

detection at lane 0 (see

the received data stream and receiver

detection at lane 1 (see Table 14)

the received data stream and receiver

detection at lane 2 (see Table 14)

the received data stream and receiver

detection at lane 3 (see Table 14)

passed (see

PHY functions including power management

state transitions and receiver detection

Table 15), LOW = reset state

Table 14)

Table 15)

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 10 of 36

NXP Semiconductors

Table 9. Clock and reference signals

Symbol Pin Type Signaling Description

TXCLK A15 input SSTL source synchronous 250 MHz transmit clock

RXCLK A14 output SSTL source synchronous 250 MHz clock output for

REFCLK_P A1 input PCIe I/O 100 MHz reference clock input. This is the

REFCLK_N B1 input PCIe I/O

PVT D3 - analog I/O input or output to create a compensation signal

VREFS U14 input reference voltage input for SSTL signaling.

PX1041A

PCI Express stand-alone X4 PHY

input from MAC. All input data and signals to the

PHY are synchronized to this clock.

received data and status signals bound for the

MAC.

spread spectrum source clock for PCI Express.

Differential pair input with 50 Ω on-chip

termination.

internally that will adjust the I/O pads

characteristics as PVT drifts. Connect to V

through a 49.9 Ω resistor.

Connect to 900 mV for SSTL_18, to 1.25 V for

SSTL_2.

DD

Table 10. 3.3 V JTAG signals

Symbol Pin Type Signaling Description

TMS A2 input 3.3 V CMOS test mode select input

TRST_N B2 input 3.3 V CMOS test reset input for the JTAG interface;

active LOW. pull-down required for normal

operation

TCK B3 input 3.3 V CMOS test clock input for the JTAG interface

TDI A3 input 3.3 V CMOS test data input

TDO C3 output 3.3 V CMOS test data output

Table 11. PCI Express PHY power supplies

Symbol Pin Type Signaling Description

V

DDA1

J4, K4, L4, M4, N4 power 1.2 V analog power supply for

serializer and de-serializer

V

DDA2

E4 power 3.3 V analog power supply for

serializer and de-serializer

V

V

DDD1

DDD2

C2 power 3.3 V power supply for JTAG I/O

D7, D8, D10, D11, G14,

H14, J14, K14, P10,

power 2.5 V or 1.8 V power supply for SSTL

I/O

P11, P12

PX1041A_1 © NXP B.V. 2007. All rights reserved.

Objective data sheet Rev. 01 — 21 June 2007 11 of 36

Loading...

Loading...