PN533

Near Field Communication (NFC) controller

Rev. 3.3 — 16 July 2012

158233

1. General description

The PN533 is a highly integrated transceiver module for contactle ss communication at

13.56 MHz based on the 80C51 microcontroller core. A dedicated ROM code is

implemented to handle different RF protocols.

1.1 RF protocols

The PN533 supports four main operating modes:

• ISO/IEC 14443A Reader/Writer (including MIFARE product family)

• ISO/IEC 14443B Reader/Writer

• FeliCa Reader/Writer

• ISO/IEC 18092, ECMA 340 Peer-to-Peer

Product short data sheet

PUBLIC

The PN533 hardware implements a demodulator and decoder for signals from

ISO/IEC 14443A compatible cards and transponders. The PN533 hardware handles the

complete ISO/IEC 14443A framing and error detection and upper layers of this protocol

(i.e. ISO/IEC 14443-4) are implemented in firmware.

The PN533 supports all MIFARE products (e.g. MIFARE crypto method). It supports

contactless communication using higher transfer speeds up to 848 kbit/s in both

directions.

The PN533 hardware supports layers 2 and 3 of the ISO/IEC 14443B Reader/Writer

communication scheme, except anticollision. Anticollision is implemented in firmware as

well as upper layers (i.e. ISO/IEC 14443-4).

The PN533 can demodulate and decode FeliCa coded signals. The PN533 handles the

FeliCa framing and error detection. It supports contactless communication using FeliCa

Higher transfer speeds up to 424 kbit/s in both directions.

Compliant to ECMA 340 and ISO/IEC 18092 NFCIP-1 Passive and Active co mmunication

modes, the PN5331B3HN/C270 offers the possibility to communicate to another NFCIP-1

compliant device, at transfer speeds up to 424 kbit/s. The PN533 handles the complete

NFCIP-1 framing and error detection.

1.2 Interfaces

The PN533 supports USB 2.0 full speed interface (bus powered or host powered mode).

PN533 also has a master I

2

C interface enabling the drive of following peripherals:

• An external EEPROM

• A TDA8029 smart card reader

NXP Semiconductors

1.3 Standards compliancy

PN533 offers commands in order for application s to be compliant in reader mode with

“Paypass-ISO/IEC 14443 Implementation v1.1”.

PN533 supports RF protocols ISO/IEC 14443A and B such as compliancy with Smar t eID

standard can be achieved at application level.

A dedicated command is implemented in PN533 firmware to support NFC secure

applications in accordance with “NFC sec Security layer for NFC” specification in order to

enable USB wireless or BT enabler applications in a host baseband.

2. Features and benefits

80C51 microcontroller core with 45056 bytes ROM and 1224 bytes RAM

Highly integrated demodulator and decoder

Buffered output drivers to connect an antenna with minimum number of external

components

Integrated RF level detector

Integrated data mode detector

Supports ISO/IEC 14443A Reader/Writer mode up to 848 kbit/s

Supports ISO/IEC 14443B Reader/Writer mode up to 848 kbit/s

Su pp or ts MIFARE encryption in Reader/Writer mode and high er tran sf er spee d

communication at 212 kbit/s, 424 kbit/s and 848kbit/s

Supports contactless communication according to the FeliCa protocol at 212 kbit/s and

424 kbit/s

Typical operating distance in Reader/Writer mode for communication to

ISO/IEC 14443A/MIFARE, ISO/IEC 14443B or FeliCa cards up to 50 mm depending

on antenna size and tuning

Su pp or t NF CIP- 1 mo d e up to 424 kbit /s

Typical operating distance in NFCIP-1 mode up to 5 0 mm dep ending on ante nna size ,

tuning and power supply

Su pp or te d USB 2. 0 full sp ee d int er fa ce

Restricted I

card reader

Lo w- po we r m od es

Hard-Power-Down mode

Soft-Power-Down mode

27.12 MHz Crystal oscillator

On-Chip PLL to generate internally 96 MHz for the USB interface

Power modes

USB bus power mode

2.5 V to 3.6 V power supply operating range in non-USB bus power mode

Dedicated IO ports for external device control

PN533

Near Field Communication (NFC) controlle r

2

C master interface to control an external I2C EEPROM or TDA8029 smart

PN533_SDS All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product short data sheet

PUBLIC

Rev. 3.3 — 16 July 2012

158233 2 of 9

NXP Semiconductors

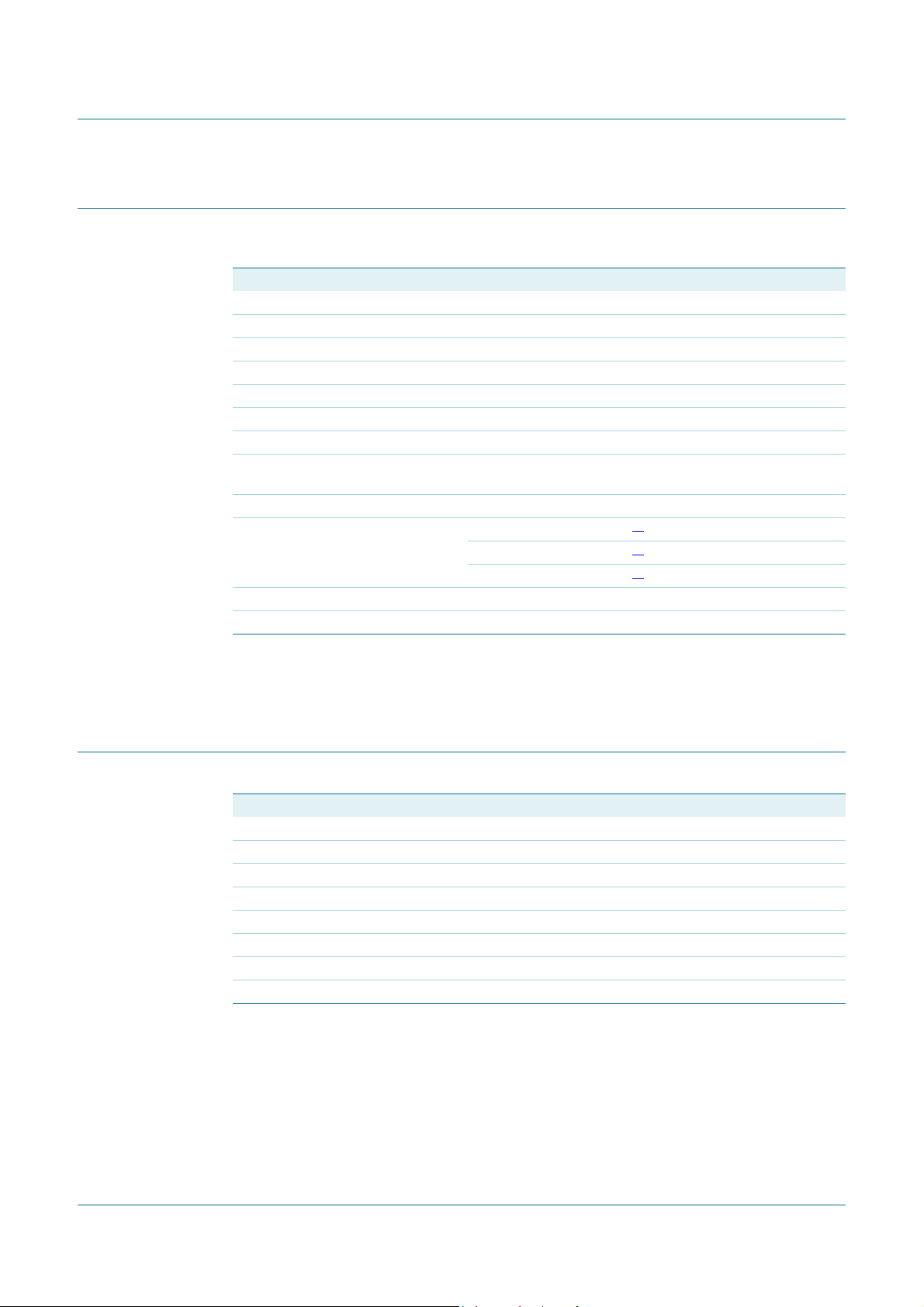

3. Quick reference data

PN533

Near Field Communication (NFC) controlle r

Table 1. Quick reference data

Symbol Parameter Conditions Min Typ Max Unit

V

BUS

V

DDA

V

DDD

V

DD(TVDD)

V

DD(PVDD)

V

DD(SVDD)

bus supply voltage 4.02 5 5.25 V

2.5 3.3 3.6 V

[1]

2.5 3.3 3.6 V

[1]

2.5 3.3 3.6 V

[1]

2.5 3.3 3.6 V

analog supply voltage V

digital supply voltage

TVDD supply voltage

(non-USB mode);

V

BUS=VDDD; VSSD

DDA

V

DD(PVDD)

V

SS(PVSS)

= V

DDD

; V

= V

= V

= V

SSA

SS(TVSS)

=0V

DD(TVDD)

SSD

= 0 V

=

=

PVDD supply voltage 1.6 - 3.6 V

SVDD supply voltage V

SSA

V

SS(TVSS)

= V

SSD

= V

SS(PVSS)

= 0 V ; reserved for

=

V

0.1 - V

DDD

DDD

V

future use

I

BUS

bus supply current maximum load current (USB

mode); measured on V

BUS

maximum inrush current

150 mA

100 mA

limitation; at power-up

(curlimoff =0)

I

pd

power-down current V

DDA

= V

DDD

= V

DD(TVDD)

hard power-down; RF

= V

DD(PVDD)

= 3 V; not powered from USB

10 A

level detector off

soft power-down; RF level

30 A

detector on

I

CCSL

I

DDD

I

DD(SVDD)

I

DDA

I

DD(TVDD)

P

tot

T

amb

suspended low-power

device supply current

RF level detector on,

(without resistor on DP/DM)

digital supply current RF level detector on,

switch off

= 3 V - - 30 mA

SVDD supply current V

V

DD(SVDD)

DDS

analog supply current RF level detector on - 6 - mA

TVDD supply current d uring RF transmission;

total power dissipation T

V

DD(TVDD)

amb

=3 V

= 30 Cto+85C--0.55W

ambient temperature 30 - +85 C

[1]

--250A

[1]

-15-mA

-60100mA

[1] V

DDD

, V

DDA

and V

DD(TVDD)

must always be at the same supply voltage.

4. Ordering information

[1][2]

Licenses”

Name Description Version

HVQFN40 plastic thermal enhanced very thin quad flat package; no

leads; 40 terminals; body 6 x 6 x 0.85 mm

Rev. 3.3 — 16 July 2012

158233 3 of 9

SOT618-1

Table 2. Ordering information

Type number Package

PN5331B3HN/C270

[1] 70 refers to the ROM code version described in User Manual.

[2] Refer to Section 9.4 “

PN533_SDS All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product short data sheet

PUBLIC

NXP Semiconductors

001aai112

SUPPLY

SUPER

VISOR

27 MHz OSC

AND

FRAC N

PLL

SVDD

SWITCH

NFC

ANALOG

FRONT END

AND

CLUART

80C51 CPU

44 k ROM

1.2 k BYTES RAM

USB

DEVICE

I

2

C

MASTER

MATX

RSTPD

PVDD

SVDD

VBUS

P30 P31 P32

GPIOs

P33 P35

RSTOUT DVDD IRQ GND

VGND

XTAL1

XTAL2

NSS

MOSI

I0

I1

SDA

SCL

Delatt

48 MHz

SIGIN

SIGOUT

P34

TVDD

AVDD

RX

VMID

TX1

TGND

TX2

REGULATOR

3.3 V

PCR

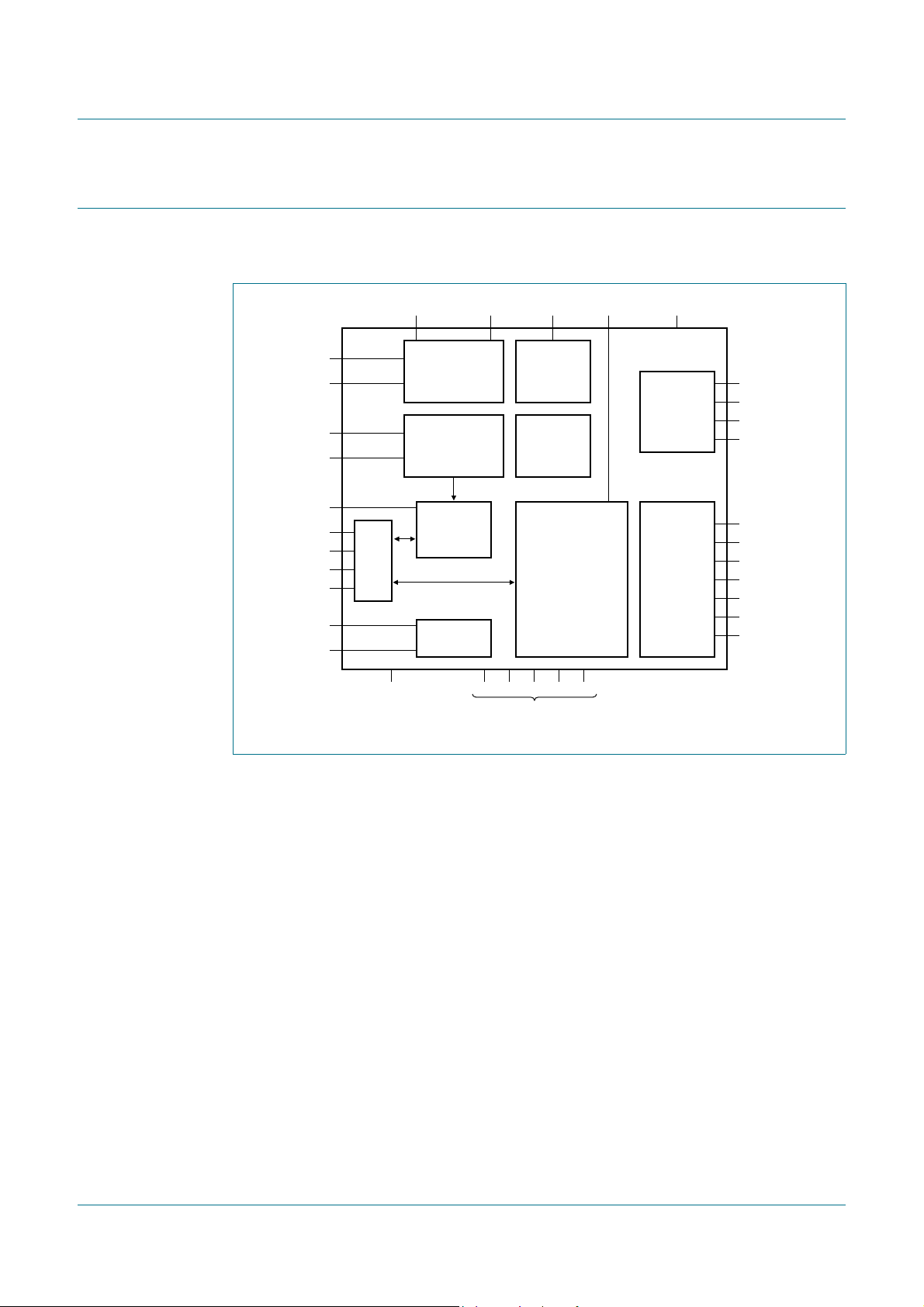

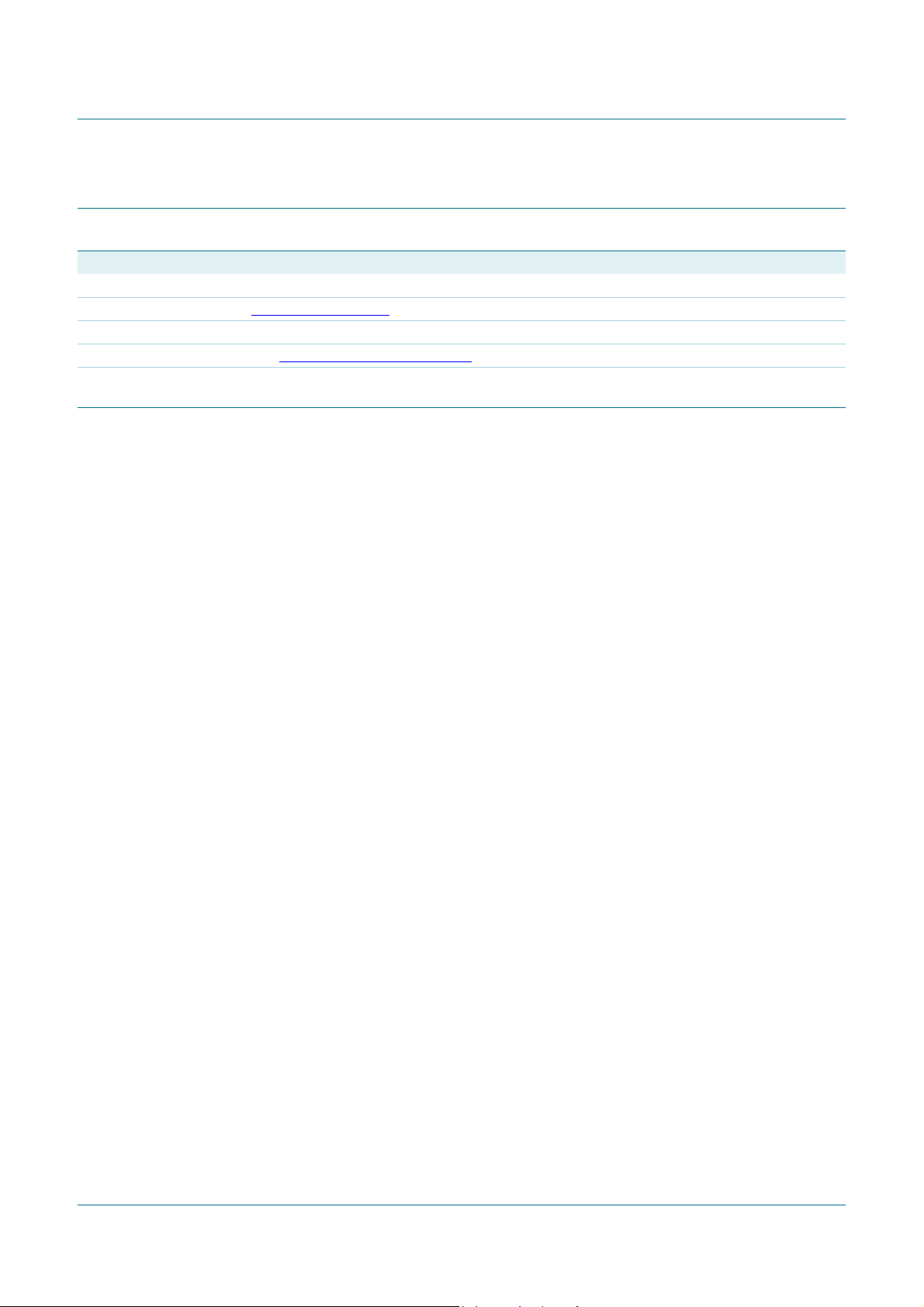

5. Block diagram

The following block diagram describes hardware blocks controlled by PN533 firmware or

which can be accessible for data transaction by a host baseband.

PN533

Near Field Communication (NFC) controlle r

Fig 1. Block diagram

PN533_SDS All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product short data sheet

PUBLIC

Rev. 3.3 — 16 July 2012

158233 4 of 9

NXP Semiconductors

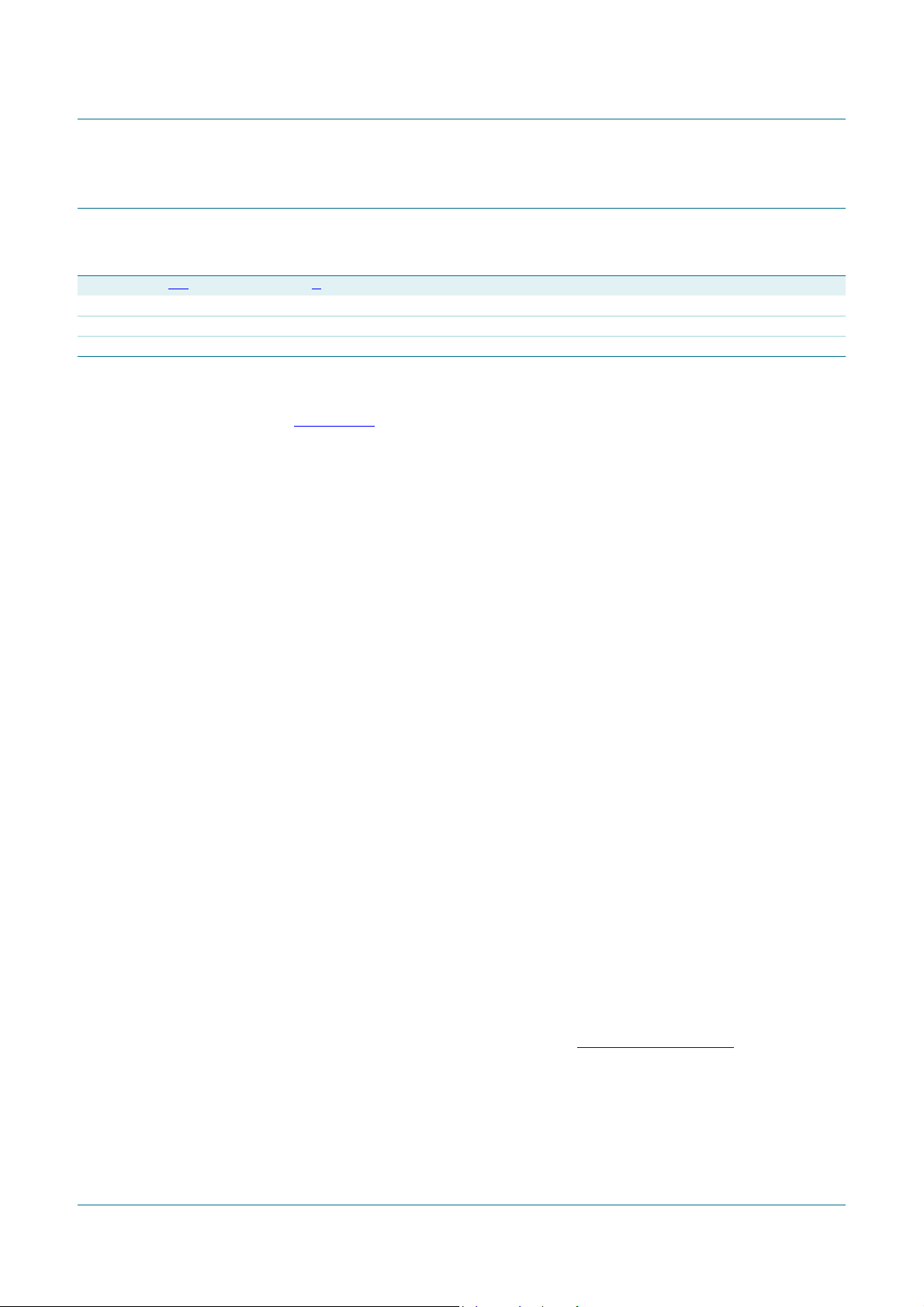

6. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter Conditions Min Max Unit

V

DDA

V

DDD

V

DD(TVDD)

V

DD(PVDD)

V

DD(SVDD)

V

BUS

P

tot

I

DD(SVDD)

V

i

V

ESD

T

stg

T

j

[1] 1500 , 100 pF; EIA/JESD22-A114-A

[2] 0.75 mH, 200 pF; EIA/JESD22-A115-A

[3] Field induced model; EIA/JESC22-C101-C

PN533

Near Field Communication (NFC) controlle r

analog supply voltage 0.5 +4 V

digital supply voltage 0.5 +4 V

TVDD supply voltage 0.5 +4 V

PVDD supply voltage 0.5 +4 V

SVDD supply voltage 0.5 +4 V

bus supply voltage 0.5 +5.5 V

total power dissipation - 500 mW

SVDD supply current maximum current in

switch

V

DDS

input voltage TX1, TX2, RX pins 0.5 +4 V

electrostatic discharge

voltage

HBM

MM

CDM

storage temperature 55 +150 C

junction temperature 40 +125 C

-30mA

[1]

[2]

-200V

[3]

- 1kV

2.0 kV

7. Abbreviations

Table 4. Abbreviations

Acronym Description

CDM Charge Device Model

CRC Cyclic Redundancy Check

EEPROM Electrically Erasable Programmable Read-Only Memory

HBM Human Body Model

HPD Hard Power Down

MM Machine Model

NFC Near Field Communication

SPD Soft Power-Down Mode

PN533_SDS All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product short data sheet

PUBLIC

Rev. 3.3 — 16 July 2012

158233 5 of 9

NXP Semiconductors

PN533

Near Field Communication (NFC) controlle r

8. Revision history

Table 5. Revision history

Document ID Release date Data sheet status Change notice Supersedes

PN533_SDS v.3.3 20120716 Product short data sheet - PN533_SDS v.3.2

Modifications: Section 9.4 “

PN533_SDS v.3.2 20120202 Product short data sheet - PN5331B3HN_ SDS_N_1

Modifications:

PN5331B3HN_SDS_N_1 20081231 Product short data sheet

• Section 1 “General description”: updated

Licenses”: updated

--

PUBLIC

PN533_SDS All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product short data sheet

PUBLIC

Rev. 3.3 — 16 July 2012

158233 6 of 9

NXP Semiconductors

PN533

Near Field Communication (NFC) controlle r

9. Legal information

9.1 Data sheet status

Document status

Objective [short] data sheet Development This document contains data from the objective specification for product development.

Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.

Product [short] data sheet Production This document contains the product specificatio n.

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term ‘short data sheet’ is explained in section “Definitions”.

[3] The product status of device(s) described in this docu ment may have change d since this d ocument was p ublished and may dif fe r in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

[1][2]

Product status

[3]

Definition

9.2 Definitions

Draft — The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences of

use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended

for quick reference only and should not be relied upon to co nt ain det ailed and

full information. For detailed and full information see the relevant full data

sheet, which is available on request via the local NXP Semiconductors sales

office. In case of any inconsistency or conflict with the short data sheet, the

full data sheet shall prevail.

Product specification — The information and data provided in a Product

data sheet shall define the specification of the product as agreed between

NXP Semiconductors and its customer, unless NXP Semiconductors and

customer have explicitly agreed otherwise in writing. In no event however,

shall an agreement be valid in which the NXP Semiconductors product is

deemed to offer functions and qualities beyond those described in the

Product data sheet.

9.3 Disclaimers

Limited warranty and liability — Information in this document is believed to

be accurate and reliable. However, NXP Semiconductors does not give any

representations or warranties, expressed or implied, as to the accuracy or

completeness of such information and shall have no liability for the

consequences of use of such information. NXP Semiconductors takes no

responsibility for the content in this document if provided by an information

source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental,

punitive, special or consequential damages (including - without limitation - lost

profits, lost savings, business interruption, costs related to the removal or

replacement of any products or rework charges) whether or not such

damages are based on tort (including negligence), warranty, breach of

contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason

whatsoever, NXP Semi conductors’ aggregat e and cumulative liabil ity towards

customer for the products described herein shall be limited in accordance

with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

PN533_SDS All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product short data sheet

PUBLIC

Rev. 3.3 — 16 July 2012

Suitability for use — NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in life support, life-critical or

safety-critical systems or equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors and its suppliers accept no liability for

inclusion and/or use of NXP Semiconductors products in such equipment or

applications and therefore such inclusion and/or use is at the cust omer’s own

risk.

Applications — Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Customers are responsible for the design and operation of their applications

and products using NXP Semiconductors products, and NXP Semiconductors

accepts no liability for any assistance with applications or customer product

design. It is customer’s sole responsibility to determine whether the NXP

Semiconductors product is suitable and fit for the customer’s applications and

products planned, as well as for the planned application and use of

customer’s third party customer(s). Customers should provide appropriate

design and operating safeguards to minimize the risks associated with their

applications and products.

NXP Semiconductors does not accept any liability related to any default ,

damage, costs or problem which is based on any weakness or default in the

customer’s applications or products, or the application or use by customer’s

third party customer(s). Customer is responsible for doing all necessary

testing for the customer’s applications and products using NXP

Semiconductors products in order to avoid a default of the applications and

the products or of the application or use by customer’s third part y

customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in

the Absolute Maximum Ratings System of IEC 60134) will cause permanent

damage to the device. Limiting values are stress ratings only and (proper)

operation of the device at these or any other conditions above those given in

the Recommended operating conditions section (if present) or the

Characteristics sections of this document is not warranted. Constant or

repeated exposure to limiting values will permanently and irreversibly affect

the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors

products are sold subject to the general terms and conditions of commercial

sale, as published at http://www.nxp.com/profile/terms

agreed in a valid written individual agreement. In case an individual

agreement is concluded only the terms and conditions of the respective

agreement shall apply. NXP Semiconductors hereby expressly objects to

applying the customer’s general terms and conditions with regard to the

purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or

construed as an offer to sell product s that is open for accept ance or the gr ant,

conveyance or implication of any license under any copyrights, patents or

other industrial or intellectual property rights.

, unless otherwise

158233 7 of 9

NXP Semiconductors

PN533

Near Field Communication (NFC) controlle r

Export control — This document as well as the item(s) described herein

may be subject to export control regulations. Export might require a prior

authorization from competent authorities.

Quick reference data — The Quick reference data is an extract of the

product data given in the Limiting values and Characteristics sections of this

document, and as such is not complete, exhaustive or legally binding.

Non-automotive qualified products — Unless this data sheet expressly

states that this specific NXP Semiconductors product is automotive qualified,

the product is not suitable for automotive use. It i s neit her qua lif ied nor tested

in accordance with automotive testing or application requirements. NXP

Semiconductors accepts no liability for inclusion and/or use of

non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in

automotive applications to automotive specifications and standards, custome r

(a) shall use the product without NXP Semiconductors’ warranty of the

product for such automotive applications, use and specifications, and (b)

whenever customer uses the product for automotive applications beyond

NXP Semiconductors’ specifications such use shall be solely at customer’s

own risk, and (c) customer fully indemnifies NXP Semiconductors for any

liability, damages or failed produ ct claims resulting from customer design and

use of the product for automotive applications beyond NXP Semiconductors’

standard warranty and NXP Semiconductors’ product specifications.

Translations — A non-E nglish (translated) version of a document is for

reference only. The Engl ish version shall prevail in case of any discrepancy

between the translated and English versions.

10. Contact information

9.4 Licenses

Purchase of NXP ICs with ISO/IEC 14443 type B functionality

This NXP Semiconductors IC is ISO/IEC 14443 T ype B

software enabled and is licensed under Innovatron’s

Contactless Card patents license for ISO/IEC 14443 B.

The license includes the right to use the IC in systems

and/or end-user equipment.

RATP/Innovatron

Technology

Purchase of NXP ICs with NFC technology

Purchase of an NXP Semiconductors IC that complies with one of the Near

Field Communication (NFC) standards ISO/IEC 18092 and ISO/IEC 21481

does not convey an implied license under any patent right infringed by

implementation of any of those standards.

9.5 Trademarks

Notice: All referenced brands, prod uct names, service names and trademarks

are the property of their respective owners.

MIFARE — is a trademark of NXP B.V.

2

I

C-bus — logo is a trademark of NXP B.V.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

PN533_SDS All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product short data sheet

PUBLIC

Rev. 3.3 — 16 July 2012

158233 8 of 9

NXP Semiconductors

11. Contents

1 General description. . . . . . . . . . . . . . . . . . . . . . 1

1.1 RF protocols . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.3 Standards compliancy. . . . . . . . . . . . . . . . . . . . 2

2 Features and benefits . . . . . . . . . . . . . . . . . . . . 2

3 Quick reference data . . . . . . . . . . . . . . . . . . . . . 3

4 Ordering information. . . . . . . . . . . . . . . . . . . . . 3

5 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 4

6 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 5

7 Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . . 5

8 Revision history. . . . . . . . . . . . . . . . . . . . . . . . . 6

9 Legal information. . . . . . . . . . . . . . . . . . . . . . . . 7

9.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . . 7

9.2 Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

9.3 Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

9.4 Licenses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

9.5 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

10 Contact information. . . . . . . . . . . . . . . . . . . . . . 8

11 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

PN533

Near Field Communication (NFC) controlle r

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section ‘Legal information’.

© NXP B.V. 2012. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 16 July 2012

158233

Loading...

Loading...