Page 1

AN13206

Modifying Debug Firmware on i.MX RT10xx Boards Featuring An

LPC4322-based Debug Probe

Rev. 0 — 04/2021

Contents

1 Introduction

Several NXP evaluation boards in the i.MX RT10xx series have a debug

circuit based on the LPC4322 MCU. Besides the default firmware, this circuit

can use an NXP-proprietary CMSIS-DAP based image that also supports

SWO features and this firmware is referred to as LPC-Link2. This image

also provides higher performance flash programming but does not include

drag-drop programming capability. The LPC4322 debug circuit also has an

option for an evaluation version of SEGGER’s popular J-Link probe. i.MX

RT10xx EVKs are factory programmed with an OpenSDA based CMSIS-DAP

implementation with drag-drop programming capability, but it is possible to run any of the three firmware options on these i.MX

RT10xx boards.

Table 1 describes the differences among the three firmware options.

Table 1. Comparison of firmware options

1 Introduction......................................1

2 Programming LINK2 CMSIS........... 2

3 Programming LPC-Link2 Segger J-

Link..................................................3

4 Switching back to OpenSDA DapLink

firmware (factory default firmware)

........................................................ 4

4.1 Getting the firmware images........4

5 Revision history...............................6

Application Note

OpenSDA Daplink

Power via USB (automatic target

regulator control)

SWD debug with MCUXpresso IDE √ √ √

SWO trace/profiling/ITM Ⅹ √ Ⅹ

Drag/drop programming √ Ⅹ Ⅹ

UART-USB (VCOM) √ √ √

Flash programming speed (relative to OpenSDA) 1X 3-4X 4X

Only the OpenSDA firmware version controls the regulator which power the target processor. When using the firmware other than

the default one, the power must be provided by other power sources. Such as a barrel-type power connector or USB1 connector.

For the power information, the hardware users guide can be a reference. The supply is at least 500 mA so that brownouts do not

occur in high current applications (such as graphics with backlit displays).

This application note describes how to the program the on-board debug probe board firmware with LINK2-CMSIS or J-Link

firmware and how to switch back to the OpenSDA firmware (factory default.)

The hardware used in this application note is MIMXRT1060-EVK (Rev.A1) but the same techniques can be used with any i.MX

RT10xx EVK with an LPC4322 debug probe. The utility used to update the firmware of LPC43xx/18xx devices is called LPCScrypt,

and this utility can be found at LPCScrypt v2.1.2.

√ Ⅹ Ⅹ

LPC-Link2

CMSIS-DAP

LPC-Link2

Segger J-link

Page 2

NXP Semiconductors

NOTE

When programming the J-link firmware with LPCScrypt, use an updated firmware image from SEGGER, as

updates to their firmware are required from time to time.

2 Programming LINK2 CMSIS

1. Download and install LPCScrypt.

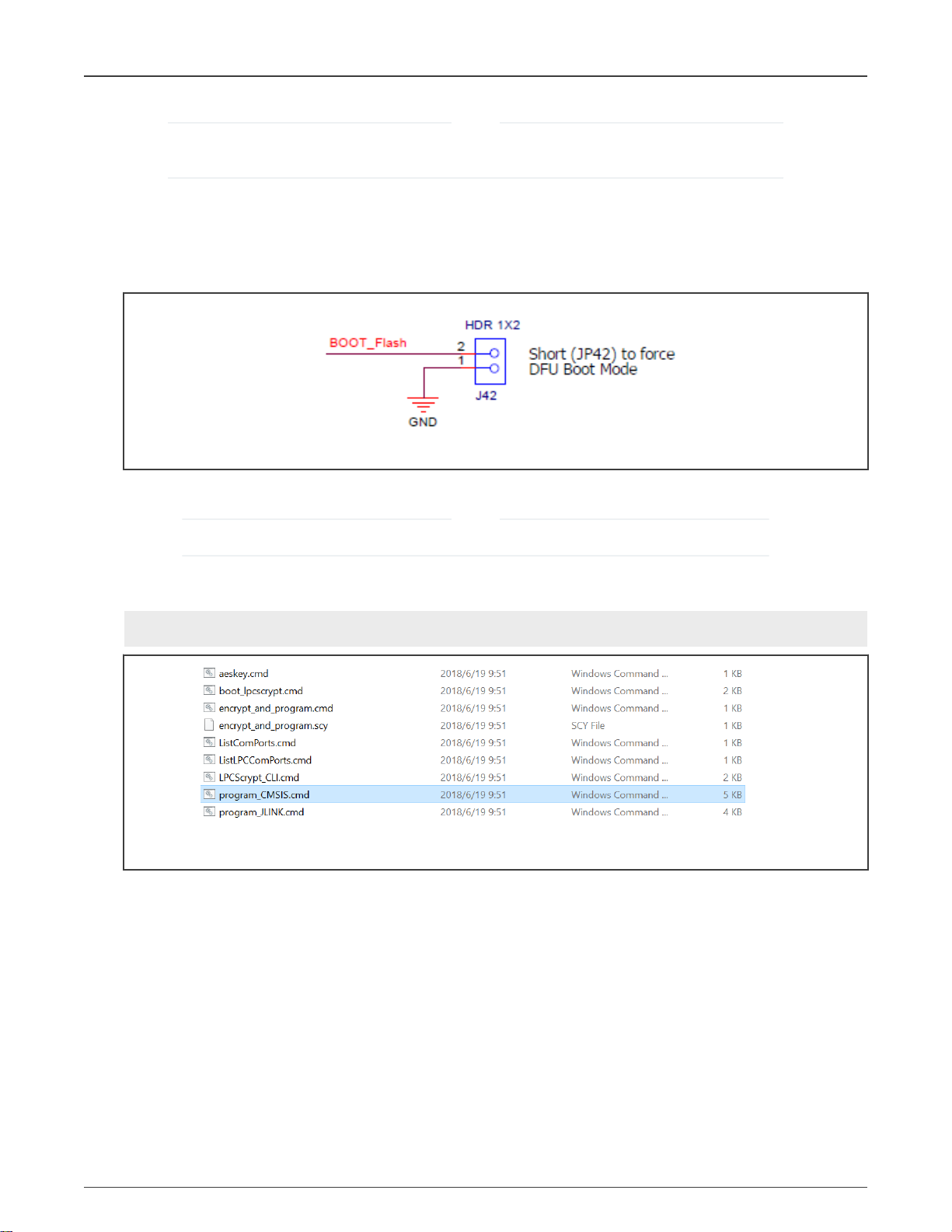

2. Install the LPC4322 DFU jumper, J42 on MIMXRT1060-EVK, to force DFU boot mode.

Figure 1. DFU jumper

3. Power on the board through the on-board debug probe USB connector, J41 on MIMXRT1060-EVK.

Programming LINK2 CMSIS

NOTE

Connect 3-4 of J1 to power the board from USB port and then connect LINK2 to LPC4322 debug port, J34.

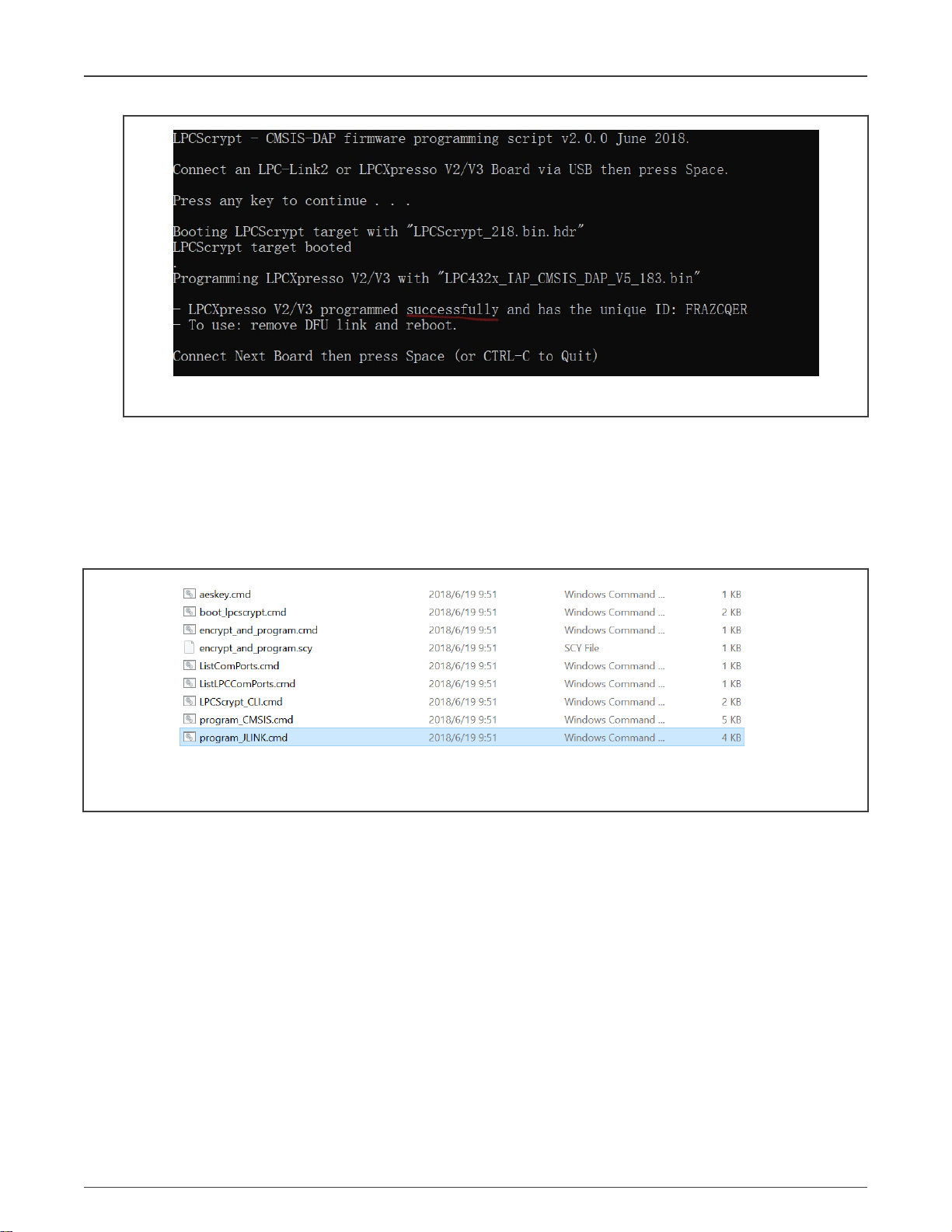

4. Go to the scripts subdirectory and run the program_CMSIS.cmd to run the script to program the debug probe for CMSIS. The

default path for .cmd files is:

C:\nxp\LPCScrypt_2.1.2_57\scripts

Figure 2. Select program_cmsis

5. Follow the on-screen instructions. Press any key to load the program and the script output shows that the firmware is

updated successfully.

Modifying Debug Firmware on i.MX RT10xx Boards Featuring An LPC4322-based Debug Probe, Rev. 0, 04/2021

Application Note 2 / 7

Page 3

NXP Semiconductors

Programming LPC-Link2 Segger J-Link

Figure 3. CMSIS firmware image programming output

6. As shown in Figure 3, there is a log showing the firmware has been programed successfully. Then, remove the jumper

of J42 to exit the DFU mode and re-power the board.

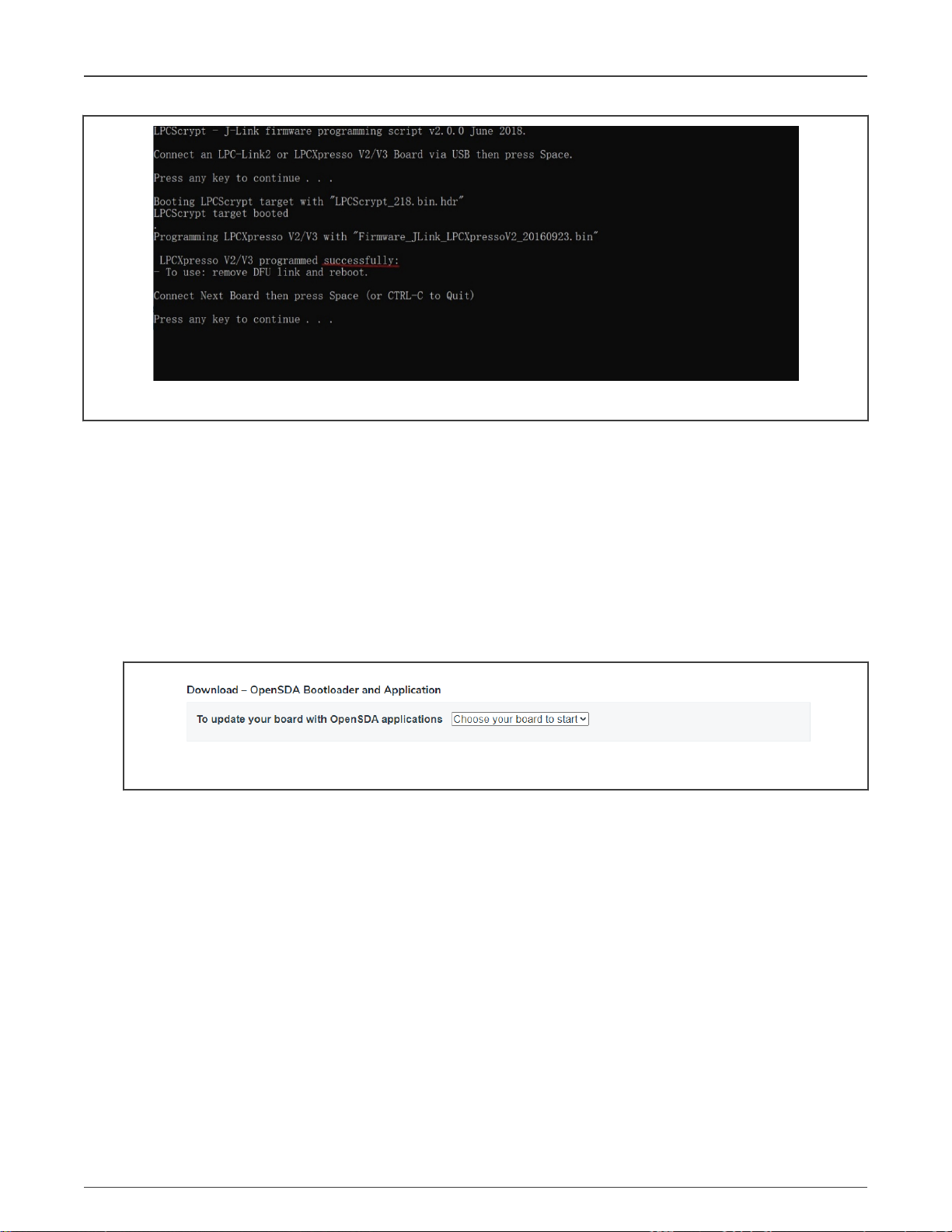

3 Programming LPC-Link2 Segger J-Link

The procedure of updating the mode into J-link is the same as LPC-Link2 CMSIS-DAP, except for running

the Program_JLINK.cmd.

Figure 4. Select program_JLINK

Figure 5 shows the output of a successful programming session.

Modifying Debug Firmware on i.MX RT10xx Boards Featuring An LPC4322-based Debug Probe, Rev. 0, 04/2021

Application Note 3 / 7

Page 4

NXP Semiconductors

Switching back to OpenSDA DapLink firmware (factory default firmware)

Figure 5. J-Link programming script output

4 Switching back to OpenSDA DapLink firmware (factory default firmware)

After updating to LINK2 CMSIS or J-Link mode, to switch back to default firmware, follow steps as below.

1. Install a bootloader needs to be installed using LPCScrypt before loading the actual OpenSDA image.

2. Use drag-drop programming.

4.1 Getting the firmware images

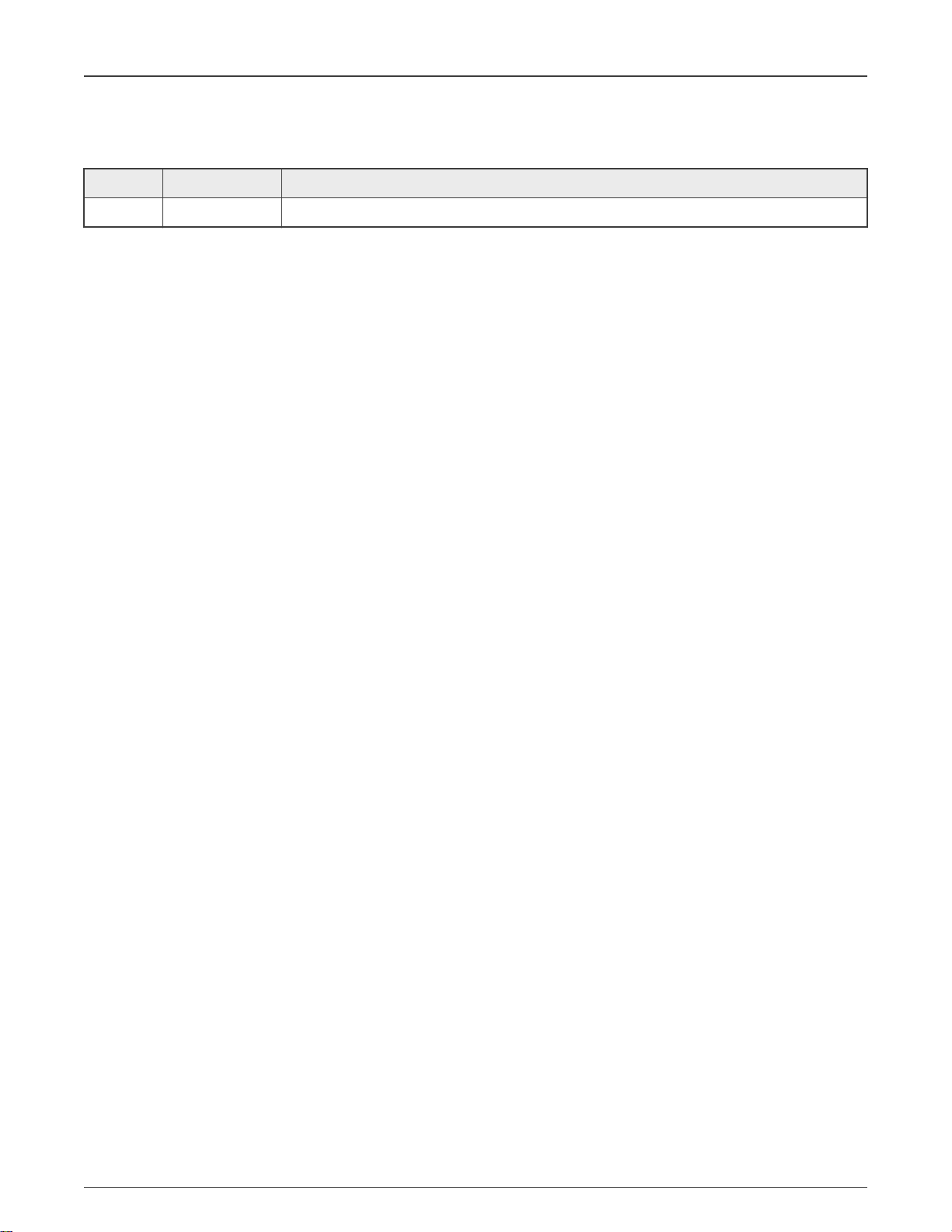

1. Download the bootloader and default firmware application from OpenSDA Serial and Debug Adapter.

2. Select the board from the pull-down menu, as shown in Figure 6.

Figure 6. Drop-down menu

3. After selecting the board, the screen changes to show available images for that board.

Modifying Debug Firmware on i.MX RT10xx Boards Featuring An LPC4322-based Debug Probe, Rev. 0, 04/2021

Application Note 4 / 7

Page 5

NXP Semiconductors

Switching back to OpenSDA DapLink firmware (factory default firmware)

Figure 7. Available images

4. Place the bootloader binary in a temporary directory without spaces in the path, e.g. c:\Temp\bootloader.

5. Enter the DFU mode with connector J42 and then power on the board.

6. Open a command window and go to the LPCScrypt installation directory. Go to the bin subdirectory and run the script

boot_lpcscrypt.cmd. Figure 8 shows the result.

Figure 8. Result

7. Enter the command:

lpcscrypt erase all

Errors may be reported but can be ignored.

8. Enter the command to program the bootloader into BankA (address 0x1a000000):

lpcscrypt program c:\Temp\bootloader\lpc4322_bl_crc_20180810.bin 0x1a000000

9. After a few seconds, the result in a message is as shown in Figure 9.

Figure 9. Result in message

10. Now remove J42, and power cycle the board. The board will now enumerate as a mass storage device

called MAINTENANCE.

11. To install the OpenSDA firmware, drag and drop the binary file onto the MAINTENANCE drive mentioned above. The

board (mass storage device) drive name will change to a board-specific name, e.g. RT1060-EVK.

Now the debug probe is ready to be used.

Modifying Debug Firmware on i.MX RT10xx Boards Featuring An LPC4322-based Debug Probe, Rev. 0, 04/2021

Application Note 5 / 7

Page 6

NXP Semiconductors

5 Revision history

Rev. Date Substantive changes

0 04/2021 Initial release

Revision history

Modifying Debug Firmware on i.MX RT10xx Boards Featuring An LPC4322-based Debug Probe, Rev. 0, 04/2021

Application Note 6 / 7

Page 7

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There

are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the

information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor

does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any

and all liability, including without limitation consequential or incidental damages. “Typical” parameters that may be provided

in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over

time. All operating parameters, including “typicals,” must be validated for each customer application by customer's technical

experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to

standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this

document, including without limitation specifications and product descriptions, at any time and without notice. This

document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities.

Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce

the effect of these vulnerabilities on customer’s applications and products. Customer’s responsibility also extends to other

open and/or proprietary technologies supported by NXP products for use in customer’s applications. NXP accepts no

liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately.

Customer shall select products with security features that best meet rules, regulations, and standards of the intended

application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all

legal, regulatory, and security related requirements concerning its products, regardless of any information or support that

may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com)

that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX,EMBRACE, GREENCHIP,

HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX,

MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG,

TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy

Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ

Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet,

Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, eIQ, and Immersive3D are

trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7,

Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle,

Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2,

ULINK-ME, ULINK-PLUS, ULINKpro, μVision, Versatile are trademarks or registered trademarks of Arm Limited (or its

subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights,

designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The

Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and

service marks licensed by Power.org.

©

NXP B.V. 2021. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 04/2021

Document identifier: AN13206

Loading...

Loading...