Page 1

DRAFT

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

UM10316

LPC29xx User manual

Rev. 01.01 — 14 July 2009 User manual

Document information

Info Content

Keywords LPC2917/01; LPC2919/01; LPC2927; LPC2929; LPC2921; LPC2923;

LPC2925; LPC2930; LPC2939 User Manual, ARM9, CAN, LIN, USB

Abstract This document extends the LPC29xx data sheets with additional details to

support both hardware and software development. It focuses on functional

description and typical application use.

F

T DRAFT DRAFT DRAFT DRA

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Page 2

DRAFT

NXP Semiconductors

Revision history

Rev Date Description

1.01 <tbd>

Modifications: • LIN chapter updated with description and register map of the UART mode.

• Corrected description of NMMEN bit (bit 0) in the RS485CTRL register: 0 = RS-485 mode disabled. 1 =

RS-485 mode enabled. Default value: 0.

• LPC2930/39 pin configuration table: pin 29 description corrected; P1[31] changed to P1[30].

• LPC2930/39 pin configuration table: USB_OVRCR1 function added to pin 31.

1 20090522 Initial LPC29xx user manual edition

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

LPC29xx User manual

D

RAFT

UM10316

F

T DRAFT DRAFT DRAFT DRA

DR

DRAFT

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 2 of 568

Page 3

UM10316

Chapter 1: LPC29xx Introductory information

Rev. 01.01 — 14 July 2009 User manual

1. Introduction

The LPC29xx combine an 125 MHz ARM968E-S CPU core, Full Speed USB 2.0 OTG

and device, CAN and LIN, up to 56 kB SRAM, up to 768 kB flash memory, external

memory interface, two or three 10-bit ADCs, and multiple serial and parallel interfaces in a

single chip targeted at consumer, industrial, medical, and communication. To optimize

system power consumption, the LPC29xx ha s a very flexible Clock Generation Unit

(CGU) that provides dynamic clock gating and scaling.

2. About this user manual

This document describes the following par ts: LPC2917/01, LPC2919/01, LPC2921,

LPC2923, LPC2925, LPC2927, LPC2929, LPC2930, a nd LPC29 39. Differences between

the various parts as they apply to each block or peripheral are listed at the beginning of

each chapter. For an overview of features see Table 1–2

DRAFT

.

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

F

T DRAFT DRAFT DRAFT DRA

DR

DRAFT

3. General features

Remark: See Table 1–2 for feature details for each LPC29xx part.

• ARM968E-S processor running at frequencies of up to 125 MHz maximum.

• Multi-layer AHB system bus at 125 MHz with four separate layers.

• On-chip memory:

– Two Tightly Coupled Memories (TCM), up to 32 kB Instruction (ITCM), up to 32 kB

– Two separate internal Static RAM (SRAM) instances; 32 kB SRAM and 16 kB

– 8 kB ETB SRAM.

– Up to 768 kB flash-program memory with 16 kB EEPROM.

• Dual-master , eight-channel GPDMA controller on the AHB multilayer matrix which can

be used with the SPI interfaces and the UARTs, as well as for memory-to-memory

transfers including the TCM memories.

• External Static Memory Controller (SMC) with eight memory banks; up to 32-bit data

bus; up to 24-bit address bus.

• Serial interfaces:

– USB 2.0 full-speed device/OTG controller with dedicated DMA controller and

– Two-channel CAN controller supporting Full-CAN and extensive message filtering

– Two LIN master controllers with full hardware support for LIN communication.

– Two 550 UARTs with 16-byte Tx and Rx FIFO depths, DMA support, and RS485

Data TCM (DTCM).

SRAM.

on-chip PHY for device and Host (LPC2930/39 only) functio ns.

support.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 3 of 568

Page 4

NXP Semiconductors

• Other peripherals:

• Up to 108 general-purpose I/O pins with programmable pull-up, pull-down, or bus

• Vectored Interrupt Controller (VIC) with 16 priority levels.

• Up to 24 level-sensitive external interrupt pins, including CAN and LIN wake-up

• Configurable clock-out pin for driving external system clocks.

• Processor wake-up from power-down via external interrupt pins; CAN or LIN activity.

• Flexible Reset Generator Unit (RGU) able to control resets of individual modules.

• Flexible Clock-Generation Unit (CGU) able to control clock frequency of individual

• Highly configurable system Power Management Unit (PMU):

• Standard ARM test and debug interface with real-time in-circuit emulator.

• Boundary-scan test supported.

• ETM/ETB debug functions with 8 kB of dedicated SRAM also accessible for

• Dual power supply:

DRAFT

Chapter 1: LPC29xx Introductory information

– Three full-duplex Q-SPIs with four slave-select lines; 16 bits wide; 8 locations

deep; Tx FIFO and Rx FIFO.

2

– Two I

– Up to three ADCs: Two 10-bit ADCs, 8-channels each, with 3.3 V measurement

– Multiple trigger-start option for all ADCs: timer, PWM, other ADC and external

– Four 32-bit timers each containing four capture-and-compare registers linked to

– Four six-channel PWMs (Pulse-Width Modulators) with capture and trap

– Two dedicated 32-bit timers to schedule and synchronize PWM and ADC.

– Quadrature encoder interface that can monitor one external quadrature encoder.

– 32-bit watchdog with timer change protection, running on safe clock.

keeper.

features.

modules:

– On-chip very low-power ring oscillator; fixed frequency of 0.4 MHz; always on to

– On-chip crystal oscillator with a recommended operating range from 10 MHz to

– On-chip PLL allows CPU operation up to a maximum CPU rate of 125 MHz.

– Generation of up to 11 base clocks.

– Seven fractional dividers.

clock control of individual modules.

allows minimization of system operating power consumption in any configuration.

application code and data storage.

C-bus interfaces.

range and one, 8-channel 10-bit ADC with 5.0 V measurement range provide a

total of up to 24 analog inputs, with conversion times as low as 2.44 μs per

channel. Each channel provides a compare function to minimize interrupts.

signal input.

I/Os.

functionality.

provide a Safe_Clock source for system monitoring.

25 MHz - max. PLL input 25 MHz.

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

UM10316

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRAFT

DRA

F

DR

AFT

DR

T DRAF

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 4 of 568

Page 5

NXP Semiconductors

– CPU operating voltage: 1.8 V ± 5%.

– I/O operating voltage: 2.7 V to 3.6 V; inputs tolerant up to 5.5 V.

• Available in 100-pin,144-pin, and 208-pin LQFP packages.

• −40 °C to 85 °C ambient operating temperature range.

4. Ordering information

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

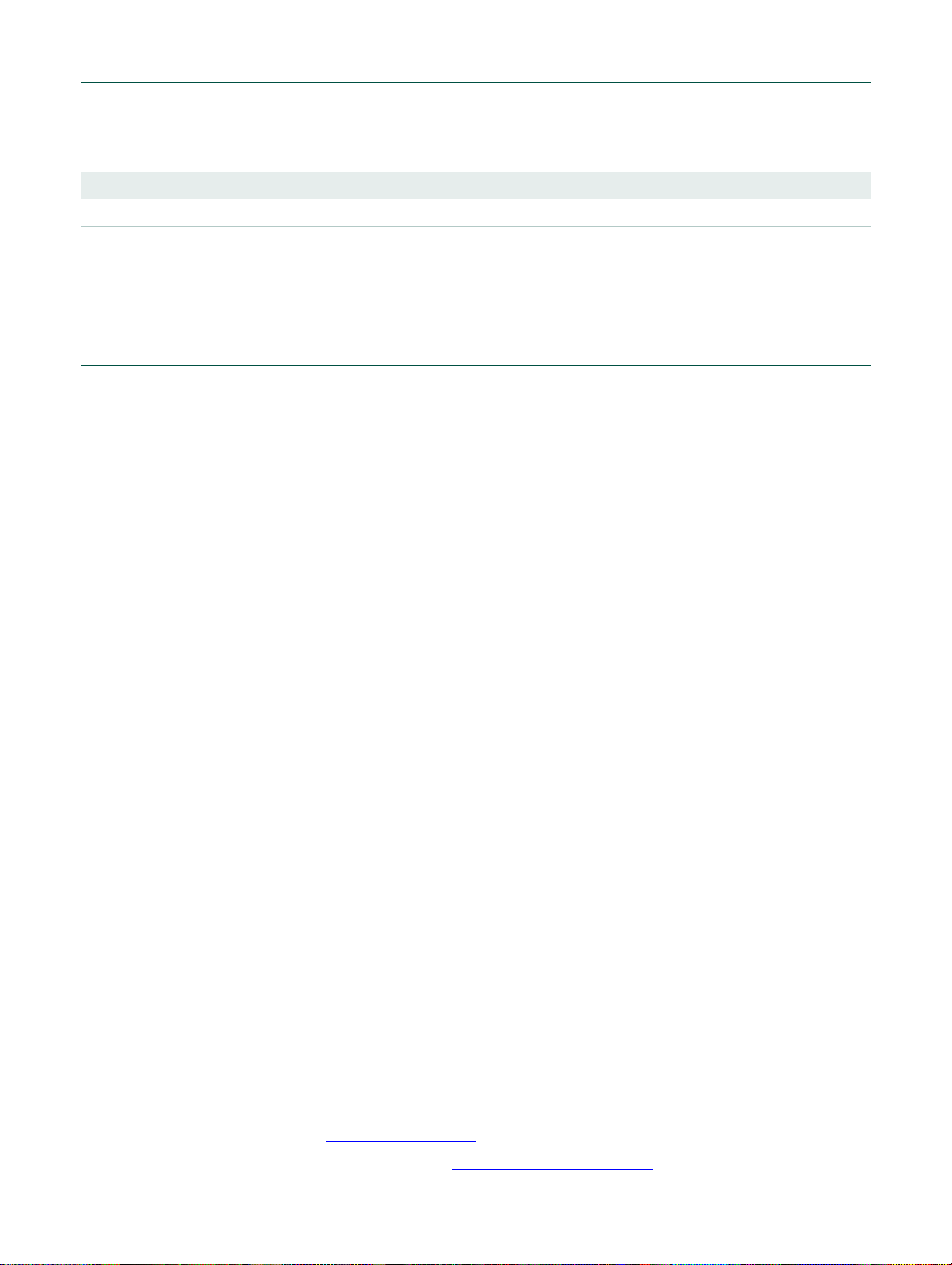

Table 1. Ordering information

Type number Package

LPC2917FBD144/01 LQFP144 plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm SOT486-1

LPC2919FBD144/01 LQFP144 plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm SOT486-1

LPC2921FBD100 LQFP100 plastic low profile quad flat package; 100 leads; body 14 x 14 x 1.4 mm SOT407-1

LPC2923FBD100 LQFP100 plastic low profile quad flat package; 100 leads; body 14 x 14 x 1.4 mm SOT407-1

LPC2925FBD100 LQFP100 plastic low profile quad flat package; 100 leads; body 14 x 14 x 1.4 mm SOT407-1

LPC2927FBD144 LQFP144 plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm SOT486-1

LPC2929FBD144 LQFP144 plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm SOT486-1

LPC2930FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 x 28 x 1.4 mm SOT459-1

LPC2939FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 x 28 x 1.4 mm SOT459-1

Name Description Version

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 5 of 568

Page 6

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 6 of 568

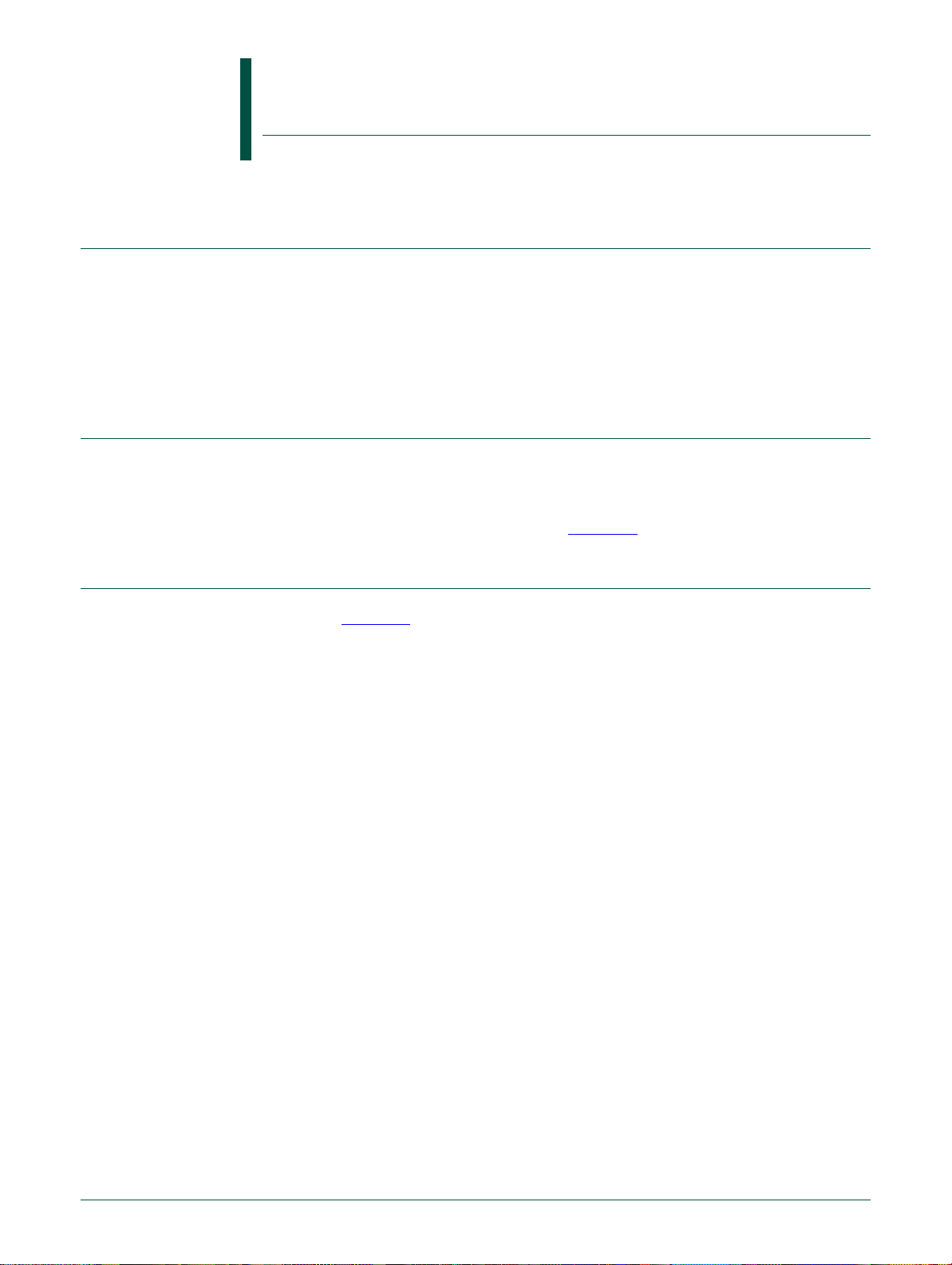

Table 2. LPC29xx part overview

Part

number

LPC2939 768 kB 56 kB 32/32 kB 2 2 208 2 3 2 Yes Yes Yes Yes Yes Yes Yes Yes Yes

LPC2930 - 56 kB 32/32 kB 2 2 208 2 3 2 Yes Yes Yes Yes Yes Yes Yes Yes Ye s

LPC2929 768 kB 56 kB 32/32 kB 2 2 144 2 3 2 Yes Yes Yes No Yes Yes Yes Yes Yes

LPC2927 512 kB 56 kB 32/32 kB 2 2 144 2 3 2 Yes Yes Yes No Yes Yes Yes Yes Yes

LPC2925 512 kB 40 kB 16/16 kB 2 2 100 2 3 2 No No Yes No No Yes Y es Yes Yes

LPC2923 256 kB 24 kB 16/16 kB 2 2 100 2 3 2 No No Yes No No Yes Y es Yes Yes

LPC2921 128 kB 24 kB 16/16 kB 2 2 100 2 3 2 No No Yes No No Yes Y es Yes Yes

LPC2919/01 768 kB 56 kB 16/16 kB 2 2 144 2 3 2 No Yes No No No Yes Yes Yes Yes

LPC2917/01 512 kB 56 kB 16/16 kB 2 2 144 2 3 2 No Yes No No No Yes Yes Yes Yes

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

4.1 Ordering options

Flash SRAM

(incl

ETB)

TCM

(I/D)

CAN LIN/

UART

Pins UART

RS485

SPI 3V3

ADC

5 V

ADC

SMC USB

device

USB

host

USB

ETM QEI I2C-bus Clkout

OTG

Remark: Note that parts LPC2927 and LPC2929 are not fully pin compatible with parts LPC2917/01 and LPC2919/01 or

LPC2917 and LPC2919. On the LPC2927/29 the MSCSS and timer blocks have a reduced pinout.

NXP Semiconductors

pin

4.2 Comparison with LPC2917/19 devices

Table 3. Feature comparison

Parts GPDMA UART

RS485

mode

LPC2917/19 no no no no 2 2 no 512/768 kB no 80 kB no no

LPC2917/19/01 yes yes yes yes 2 2 no 512/768 kB yes 88 kB 8 kB no

LPC2927/29 yes yes yes yes 2 2 yes 512/768 kB yes 120 kB 8 kB yes

I2C QEI CAN LIN USB

OTG/

device

Flash EEPROM SRAM

total

ETB

SRAM

5V

ADC

Chapter 1: LPC29xx Introductory information

DRAFT

D

RAFT DRA

D

RAFT DRAFT DRAFT DRAFT DRAFT D

UM10316

F

T DRAFT DRAFT DRAFT DRA

DRA

F

T DRAF

DR

D

RAFT

DRAFT

DR

AFT

DRAFT

DR

AFT

Page 7

D

RAFT

UM10316

NXP Semiconductors

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

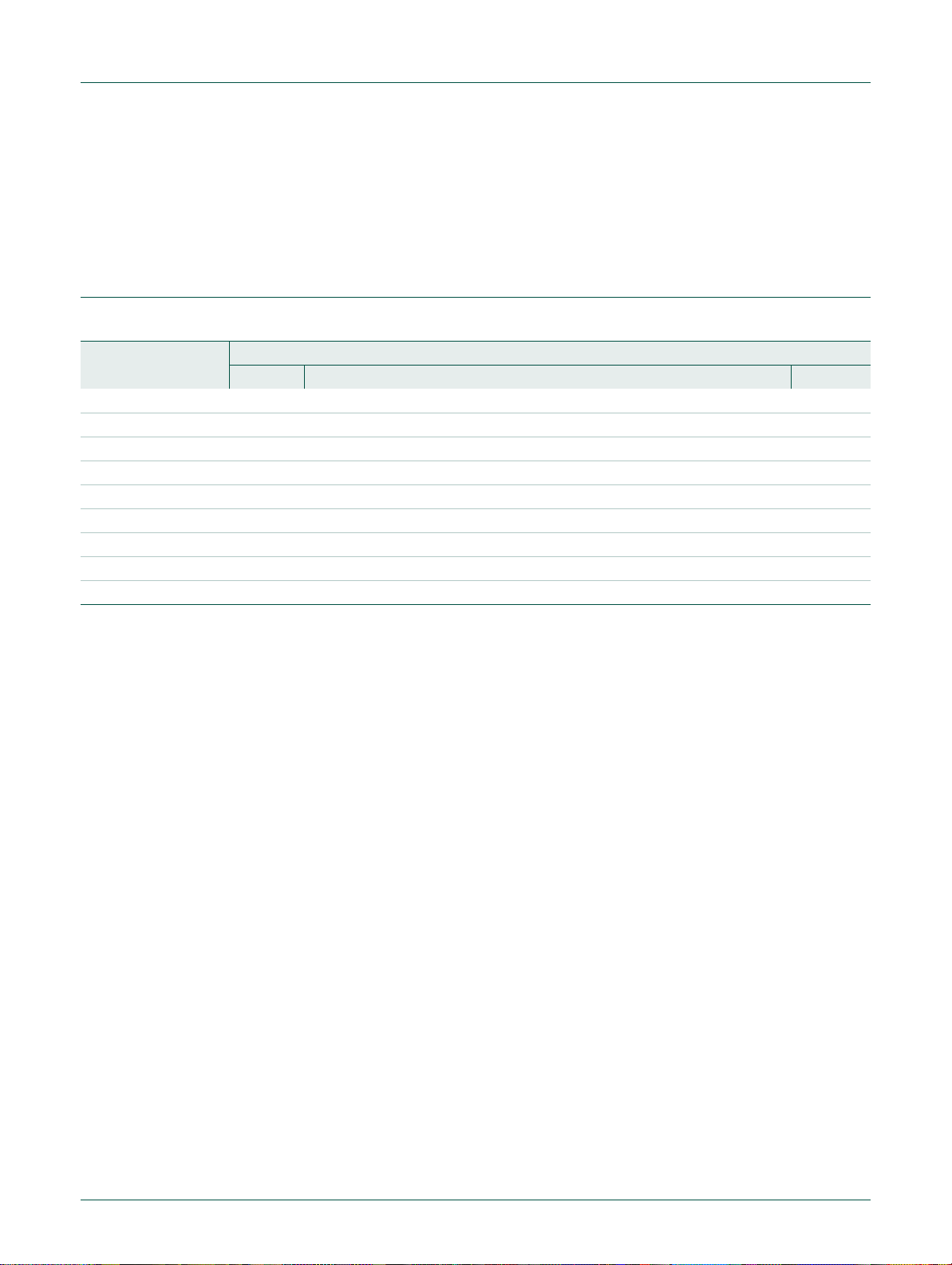

4.3 LPC29xx USB options

Table 4. LPC29x x USB options

Part On-chip controller Ports On-chip PHY

LPC2917/01 - - - - LPC2919/01 - - - - LPC2921 Full-speed - - 1 Device

LPC2923 Full-speed - - 1 Device

LPC2925 Full-speed - - 1 Device

LPC2927 Full-speed - Full-speed 1 Device

LPC2929 Full-speed - Full-speed 1 Device

LPC2930 Full-speed Full-speed Full-speed 2 Device, host

LPC2939 Full-speed Full-speed Full-speed 2 Device, host

Device Host OTG

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 7 of 568

Page 8

NXP Semiconductors

002aad959

ARM968E-S

DTCM

16 kB

ITCM

16 kB

TEST/DEBUG

INTERFACE

slave

slave

slave

slave

slave

slave

slave

slave

EXTERNAL STATIC

MEMORY CONTROLLER

GPDMA CONTROLLER

GPDMA REGISTERS

EMBEDDED FLASH

512/768 kB

16 kB

EEPROM

EMBEDDED SRAM 32 kB

SYSTEM CONTROL

TIMER0/1 MTMR

CAN0/1

GLOBAL

ACCEPTANCE

FILTER

LIN0/1

PWM0/1/2/3

3.3 V ADC1/2

EVENT ROUTER

EMBEDDED SRAM 16 kB

GENERAL PURPOSE I/O

PORTS 0/1/2/3

TIMER 0/1/2/3

SPI0/1/2

RS485 UART0/1

WDT

master

master

slave

AHB TO APB

BRIDGE

AHB TO DTL

BRIDGE

VECTORED

INTERRUPT

CONTROLLER

AHB TO DTL

BRIDGE

AHB TO APB

BRIDGE

QUADRATURE

ENCODER

CHIP FEATURE ID

AHB TO APB

BRIDGE

I2C0/1

AHB TO APB

BRIDGE

CLOCK

GENERATION

UNIT CGU0/1

POWER

MANAGEMENT

UNIT

RESET

GENERATION

UNIT

LPC2917/01

LPC2919/01

JTAG

interface

8 kB SRAM

slave

slave

1 × master

2 × slave

AHB

MULTI

LAYER

MATRIX

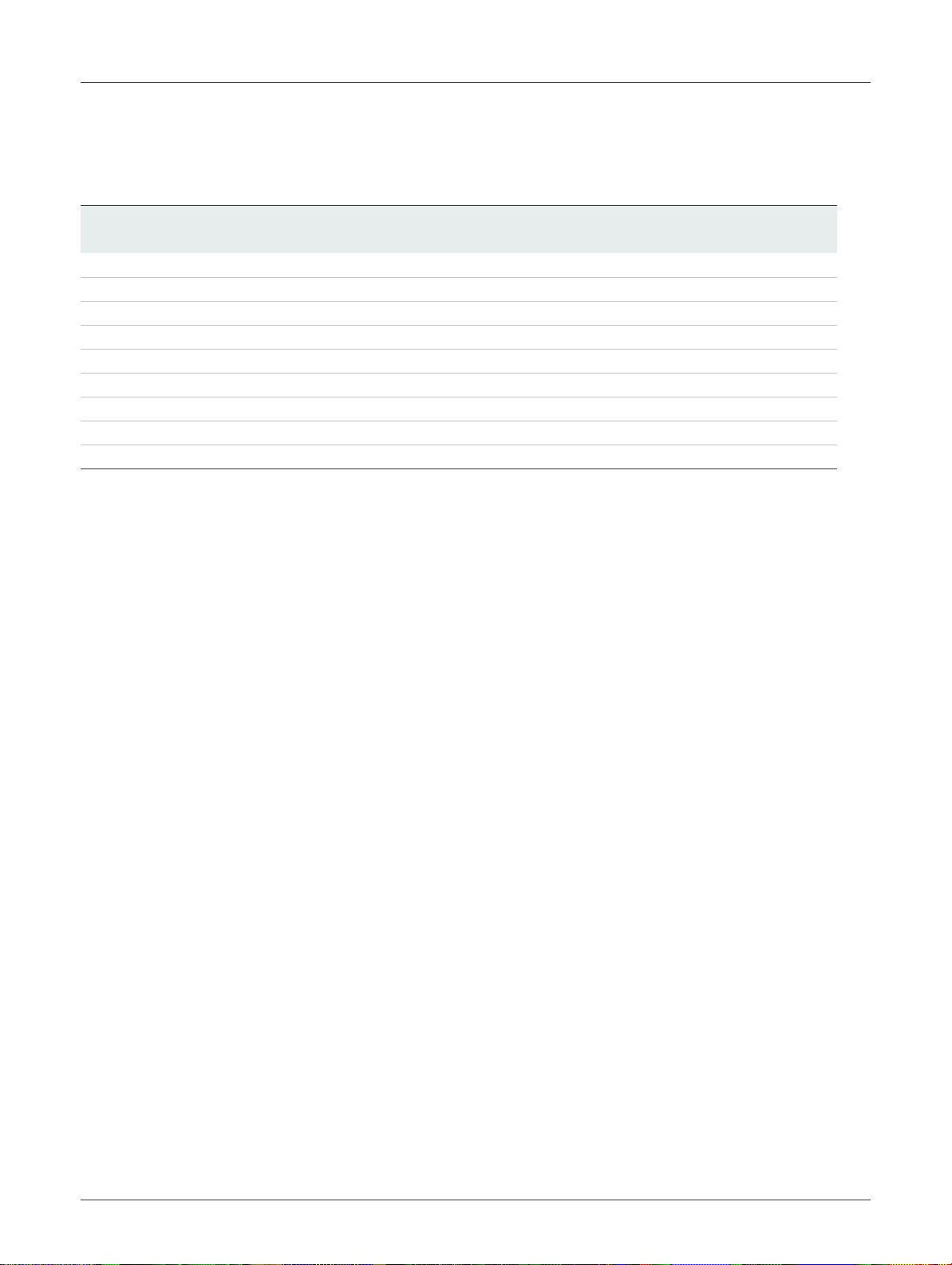

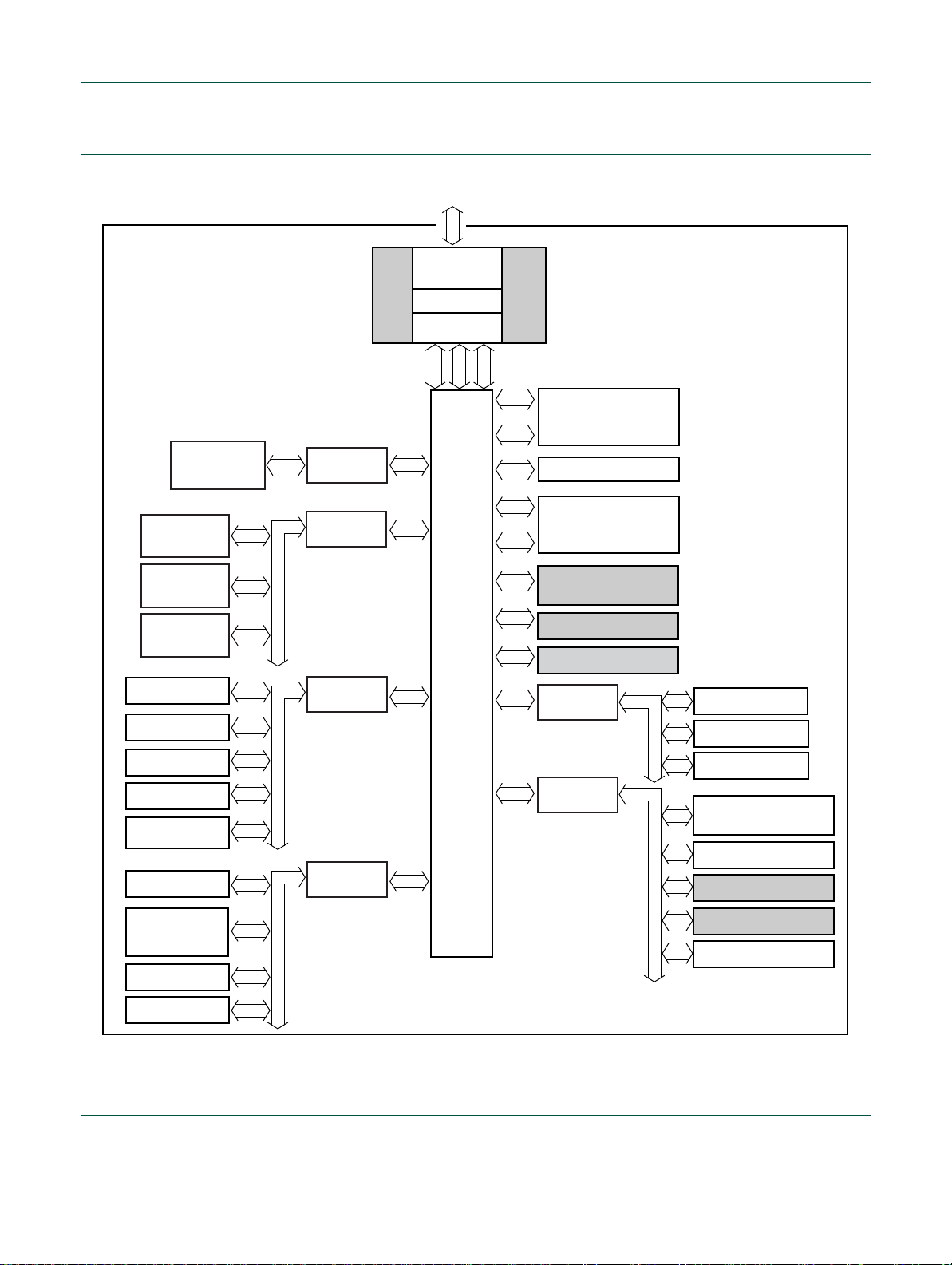

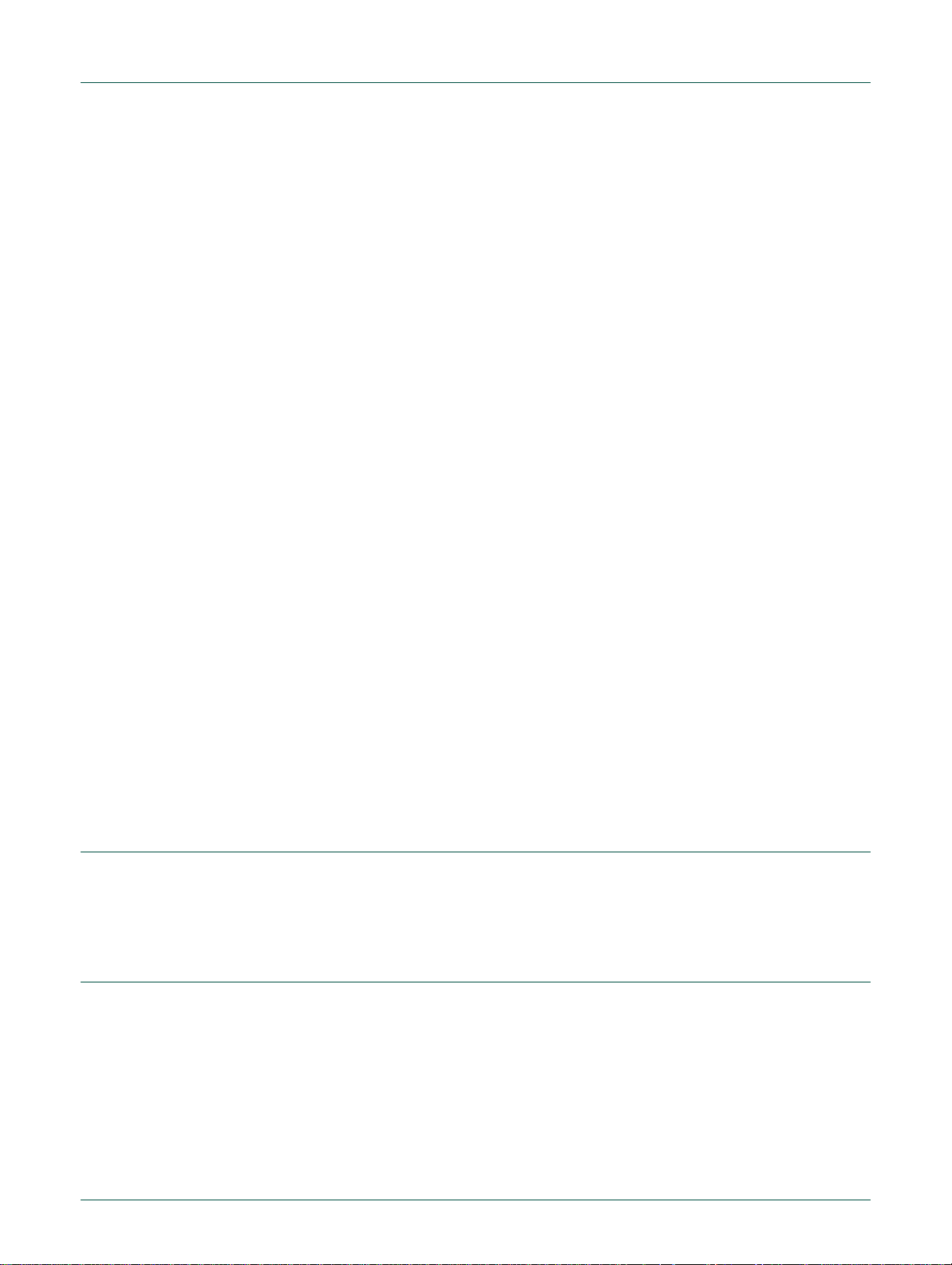

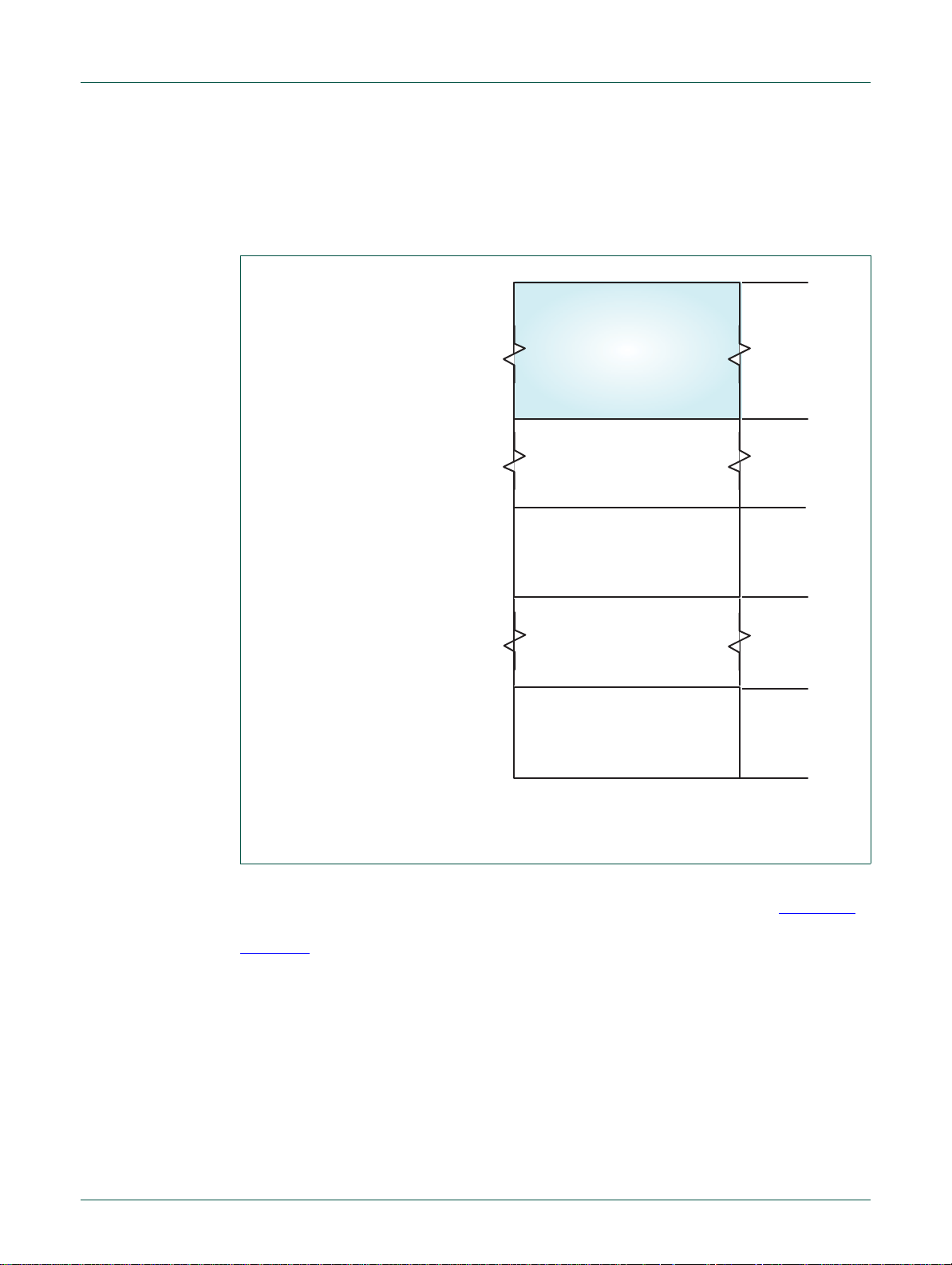

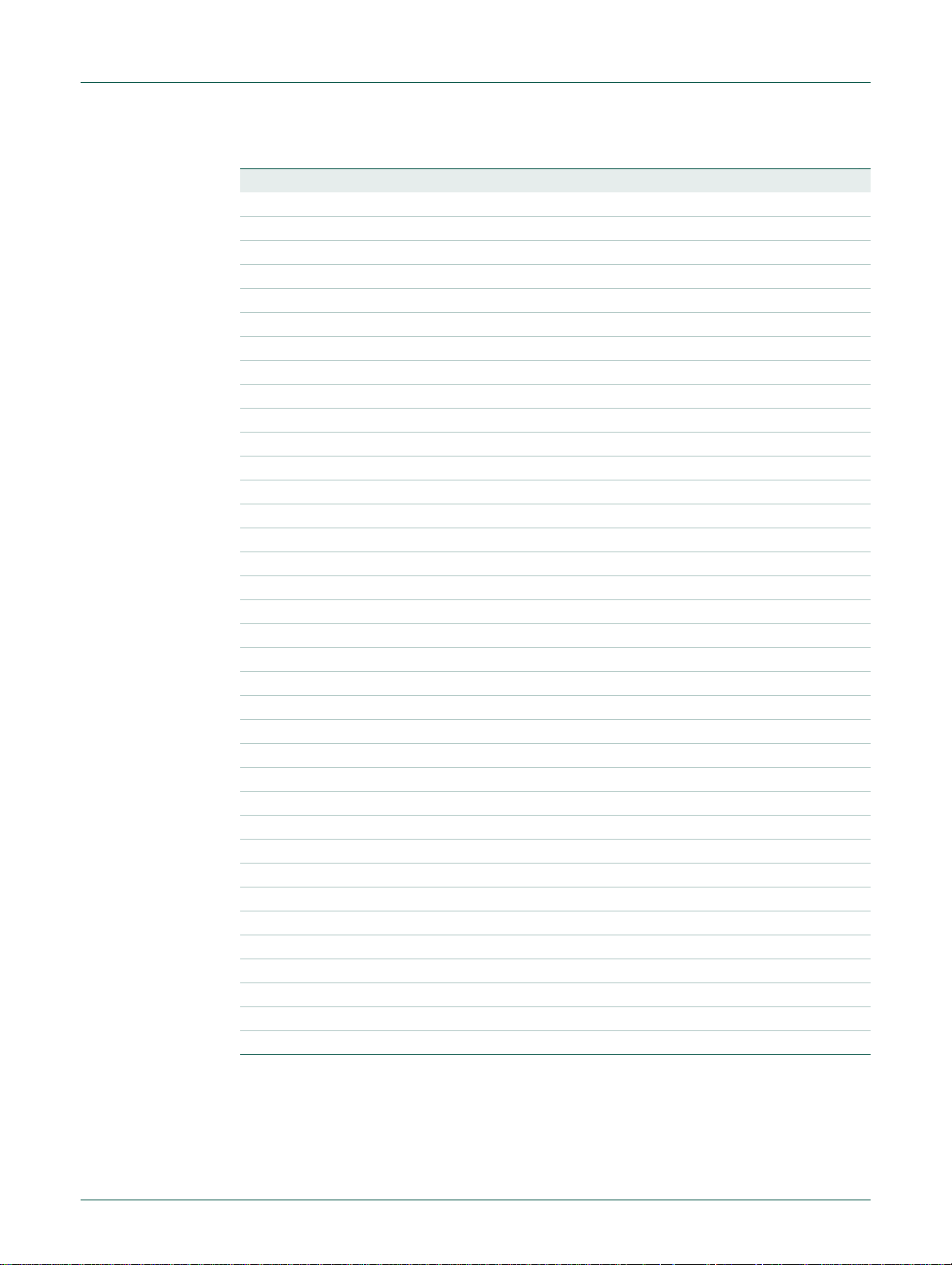

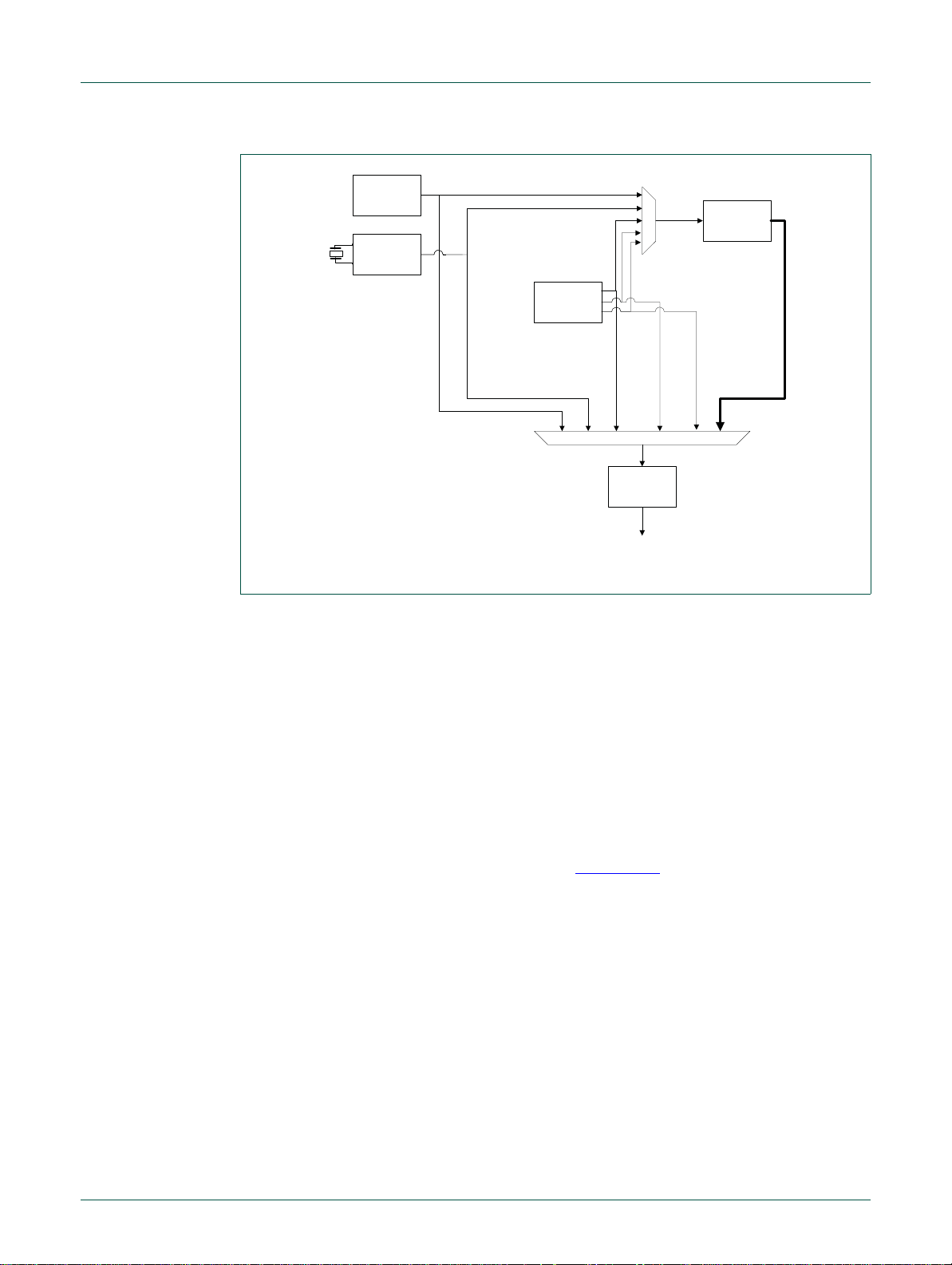

5. Block diagram

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Fig 1. LPC2917/19/01 block diagram

Grey-shaded blocks represent peripherals with connections to the GPDMA.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 8 of 568

Page 9

NXP Semiconductors

EMBEDDED FLASH

512/256/128 kB

002aae224

ARM968E-S

DTCM

16 kB

ITCM

16 kB

TEST/DEBUG

INTERFACE

slave

master

1 master

2 slaves

master

GPDMA CONTROLLER

GPDMA REGISTERS

16 kB

EEPROM

EMBEDDED SRAM 16 kB

(LPC2925 only)

SYSTEM CONTROL

TIMER0/1 MTMR

CAN0/1

GLOBAL

ACCEPTANCE

FILTER

PWM0/1/2/3

3.3 V ADC1/2

EVENT ROUTER

EMBEDDED SRAM 16 kB

GENERAL PURPOSE I/O

PORTS 0/1/5

TIMER 0/1/2/3

SPI0/1/2

RS-485 UART0/1

WDT

AHB TO APB

BRIDGE

AHB TO DTL

BRIDGE

VECTORED

INTERRUPT

CONTROLLER

master

slave

USB DEVICE

CONTROLLER

slave

slave

slave

slave

slave

slave

slave

slave

slave

AHB TO DTL

BRIDGE

AHB TO APB

BRIDGE

QUADRATURE

ENCODER

CHIP FEATURE ID

AHB TO APB

BRIDGE

I2C0/1

UART/LIN0/1

AHB TO APB

BRIDGE

AHB

MULTILAYER

MATRIX

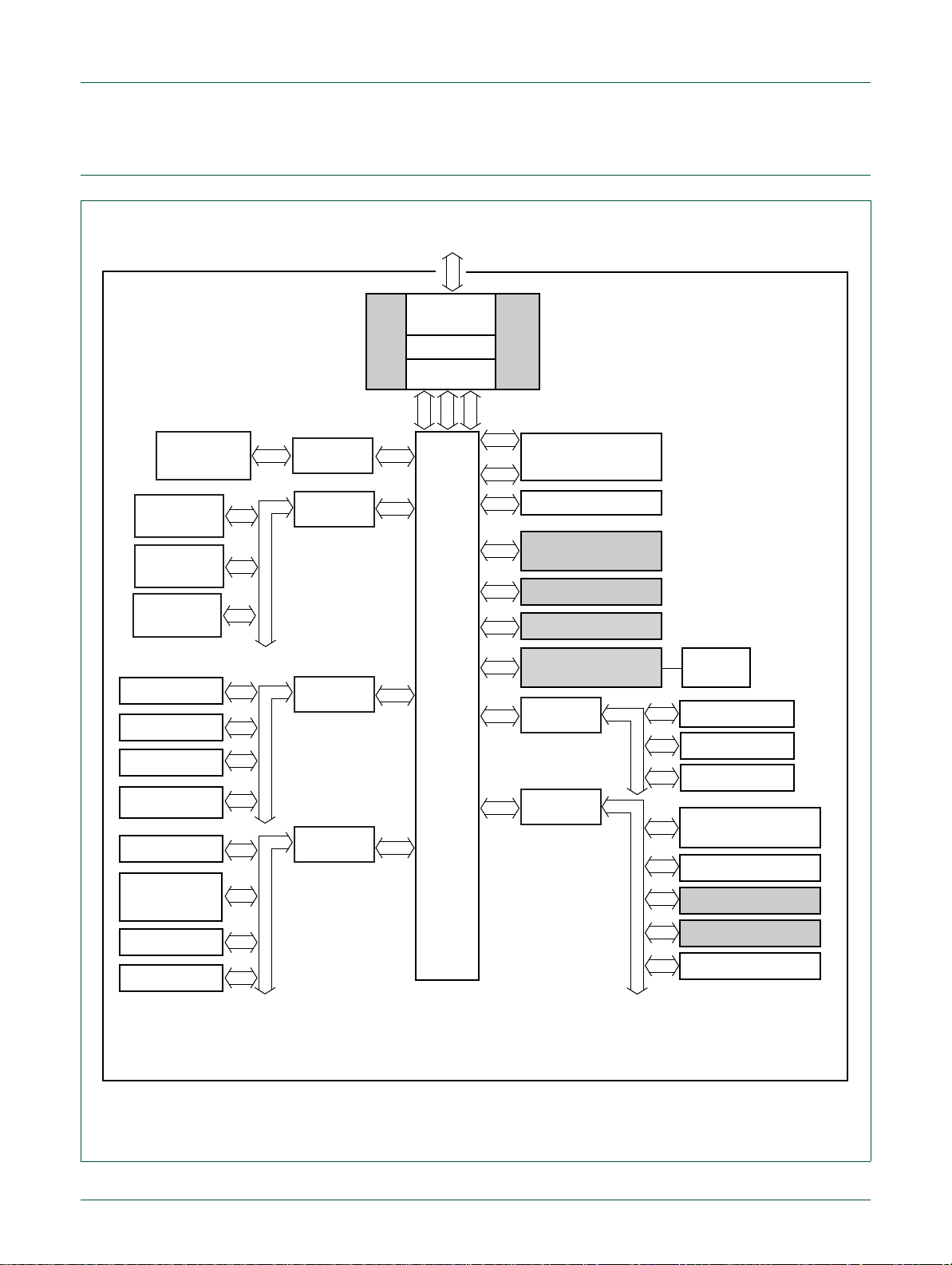

LPC2921/2923/2925

JTAG

interface

8 kB SRAM

general subsystem

power, clock, and

reset subsystem

MSC subsystem

networking subsystem

peripheral subsystem

CLOCK

GENERATION

UNIT

POWER

MANAGEMENT

UNIT

RESET

GENERATION

UNIT

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

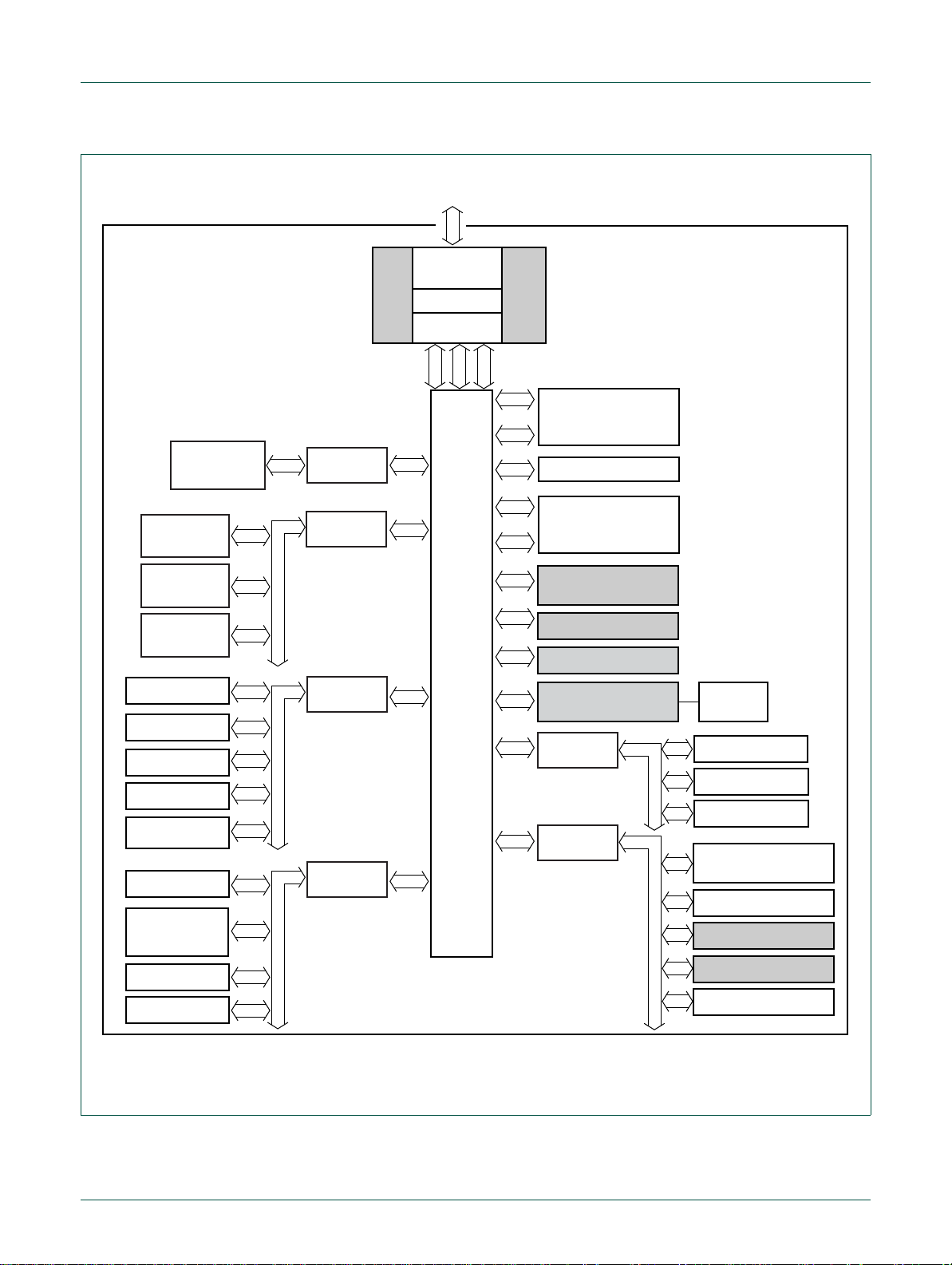

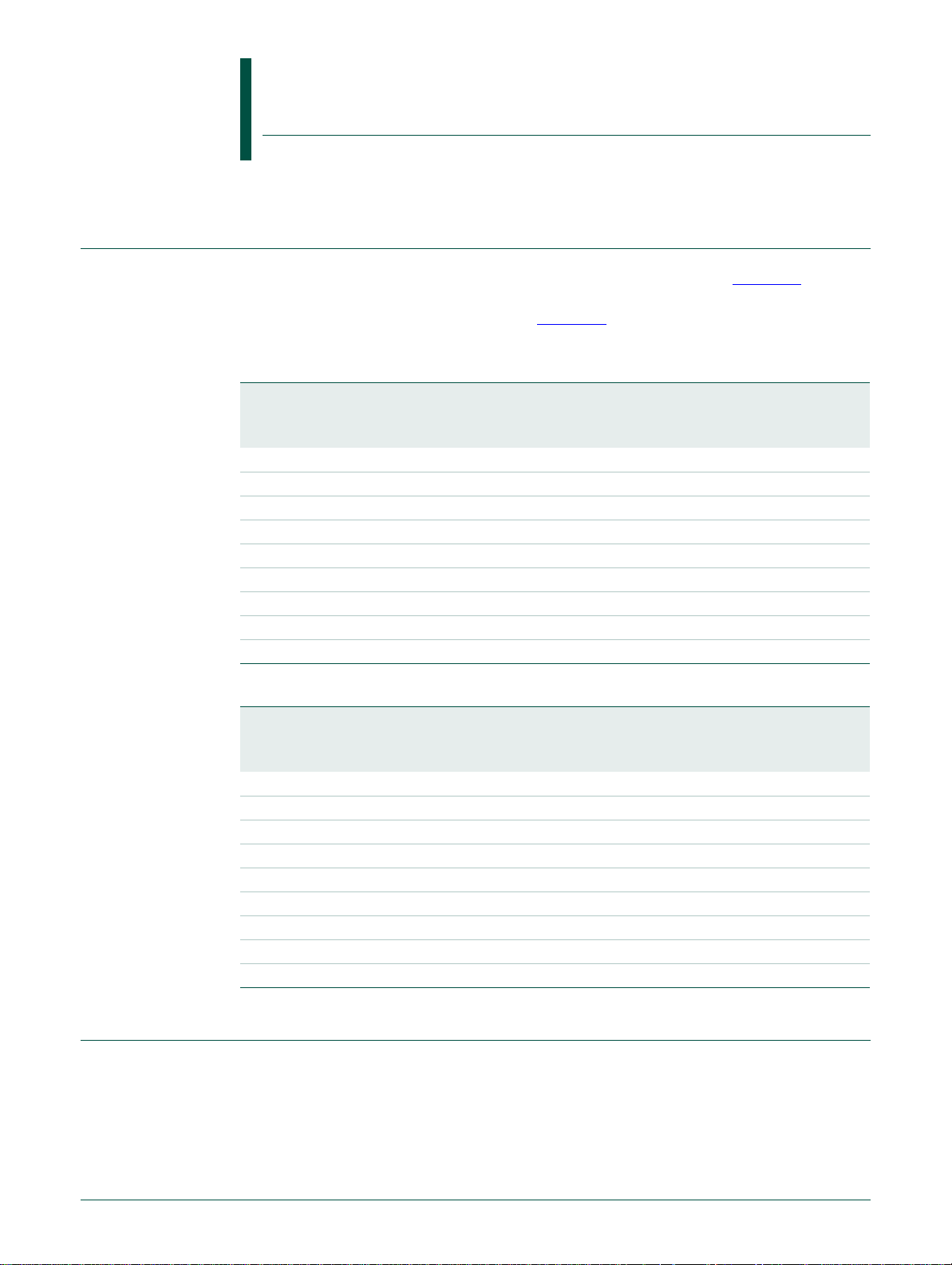

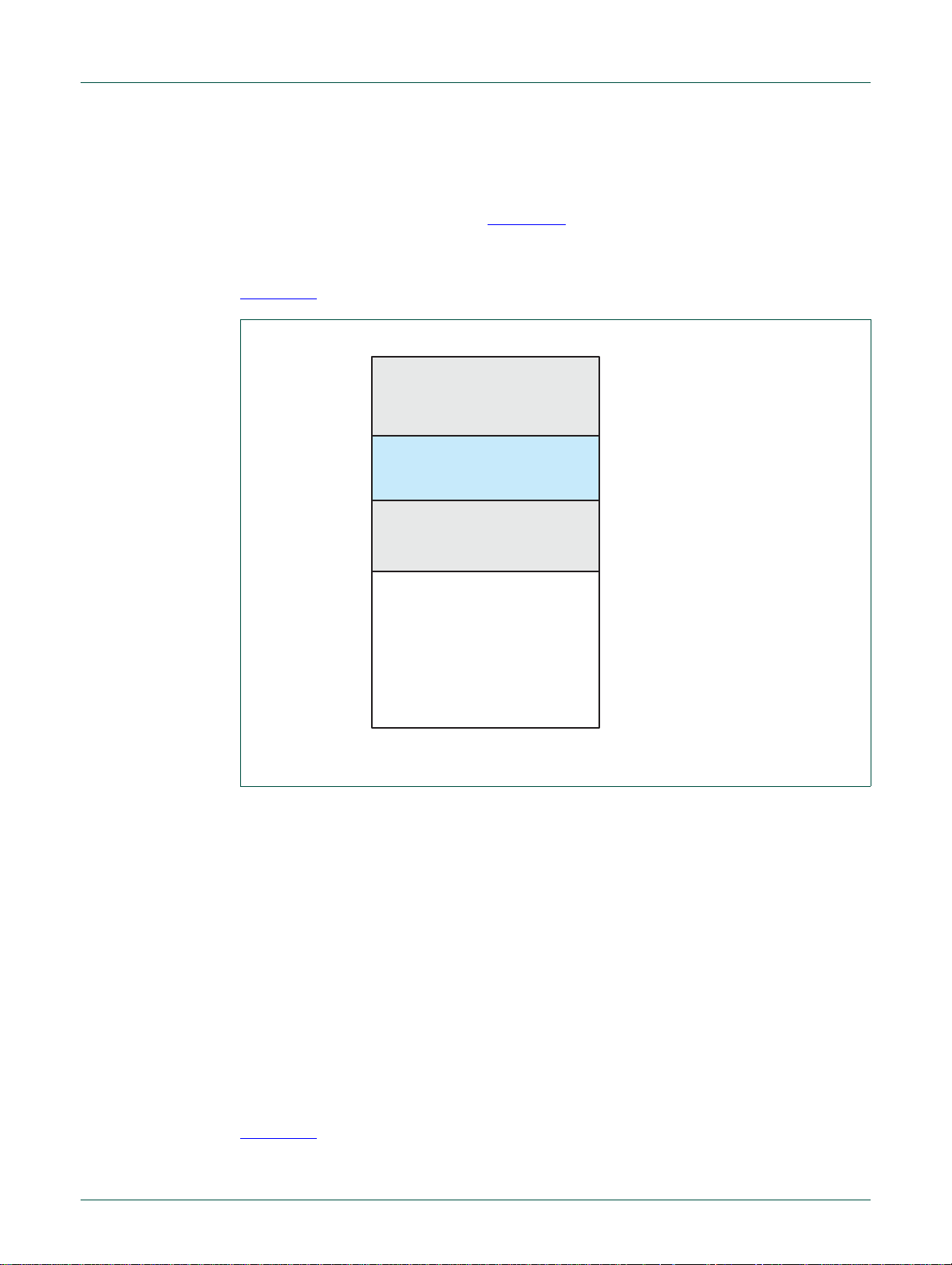

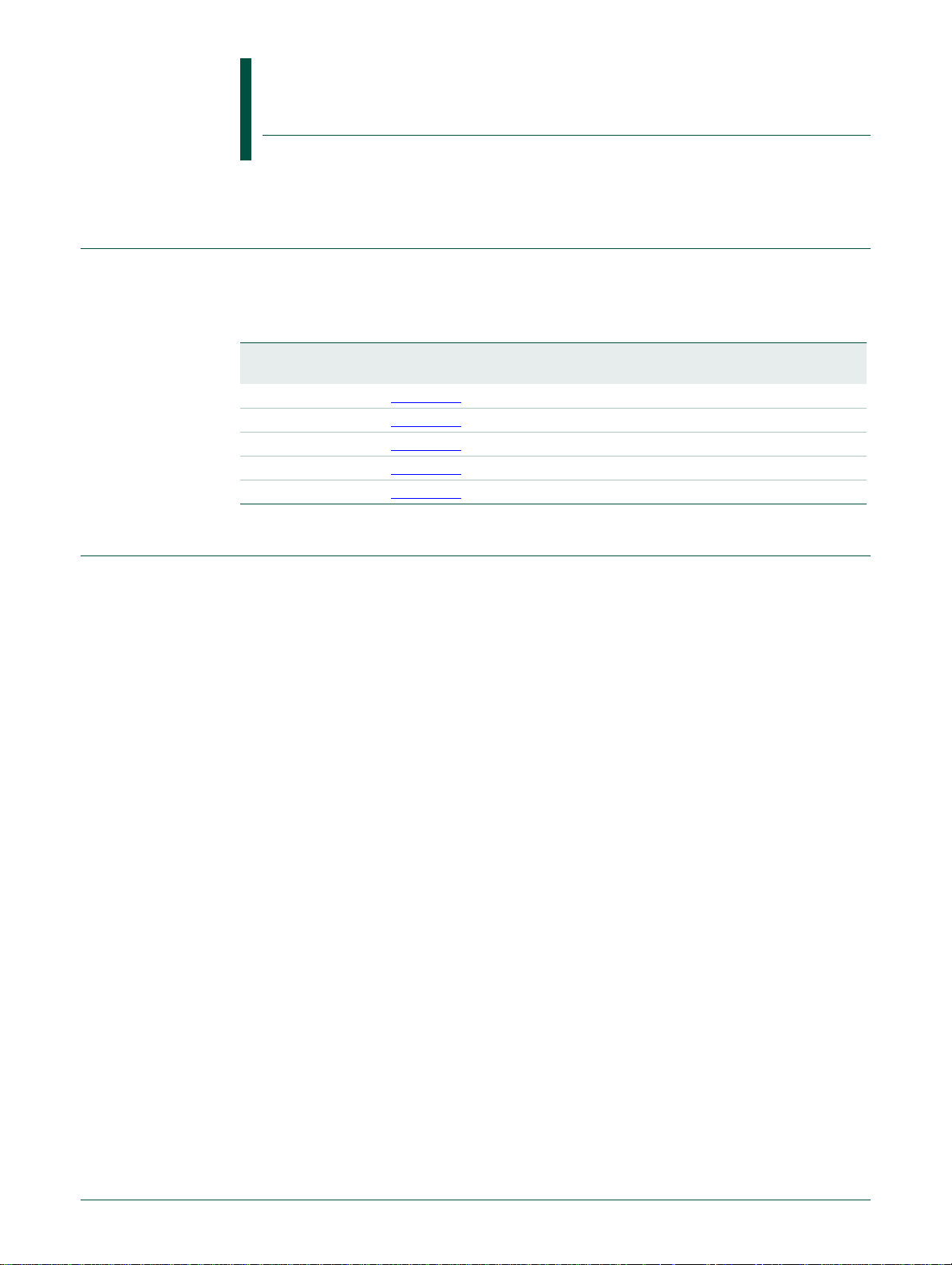

Fig 2. LPC2921/23/25 block diagram

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 9 of 568

Grey-shaded blocks represent peripherals with connections to the GPDMA.

Page 10

NXP Semiconductors

002aae143

ARM968E-S

DTCM

32 kB

ITCM

32 kB

TEST/DEBUG

INTERFACE

slave

master

1 master

2 slaves

master

EXTERNAL STATIC

MEMORY CONTROLLER

GPDMA CONTROLLER

GPDMA REGISTERS

EMBEDDED FLASH

512/768 kB

16 kB

EEPROM

EMBEDDED SRAM 32 kB

SYSTEM CONTROL

TIMER0/1 MTMR

CAN0/1

GLOBAL

ACCEPTANCE

FILTER

UART/LIN0/1

PWM0/1/2/3

3.3 V ADC1/2

EVENT ROUTER

EMBEDDED SRAM 16 kB

GENERAL PURPOSE I/O

PORTS 0/1/2/3/5

TIMER 0/1/2/3

SPI0/1/2

RS485 UART0/1

WDT

AHB TO APB

BRIDGE

AHB TO DTL

BRIDGE

VECTORED

INTERRUPT

CONTROLLER

master

slave

USB OTG/DEVICE

CONTROLLER

slave

slave

slave

slave

slave

slave

slave

slave

slave

slave

AHB TO DTL

BRIDGE

AHB TO APB

BRIDGE

5 V ADC0

QUADRATURE

ENCODER

CHIP FEATURE ID

AHB TO APB

BRIDGE

I2C0/1

AHB TO APB

BRIDGE

CLOCK

GENERATION

UNIT

POWER

MANAGEMENT

UNIT

RESET

GENERATION

UNIT

AHB

MULTILAYER

MATRIX

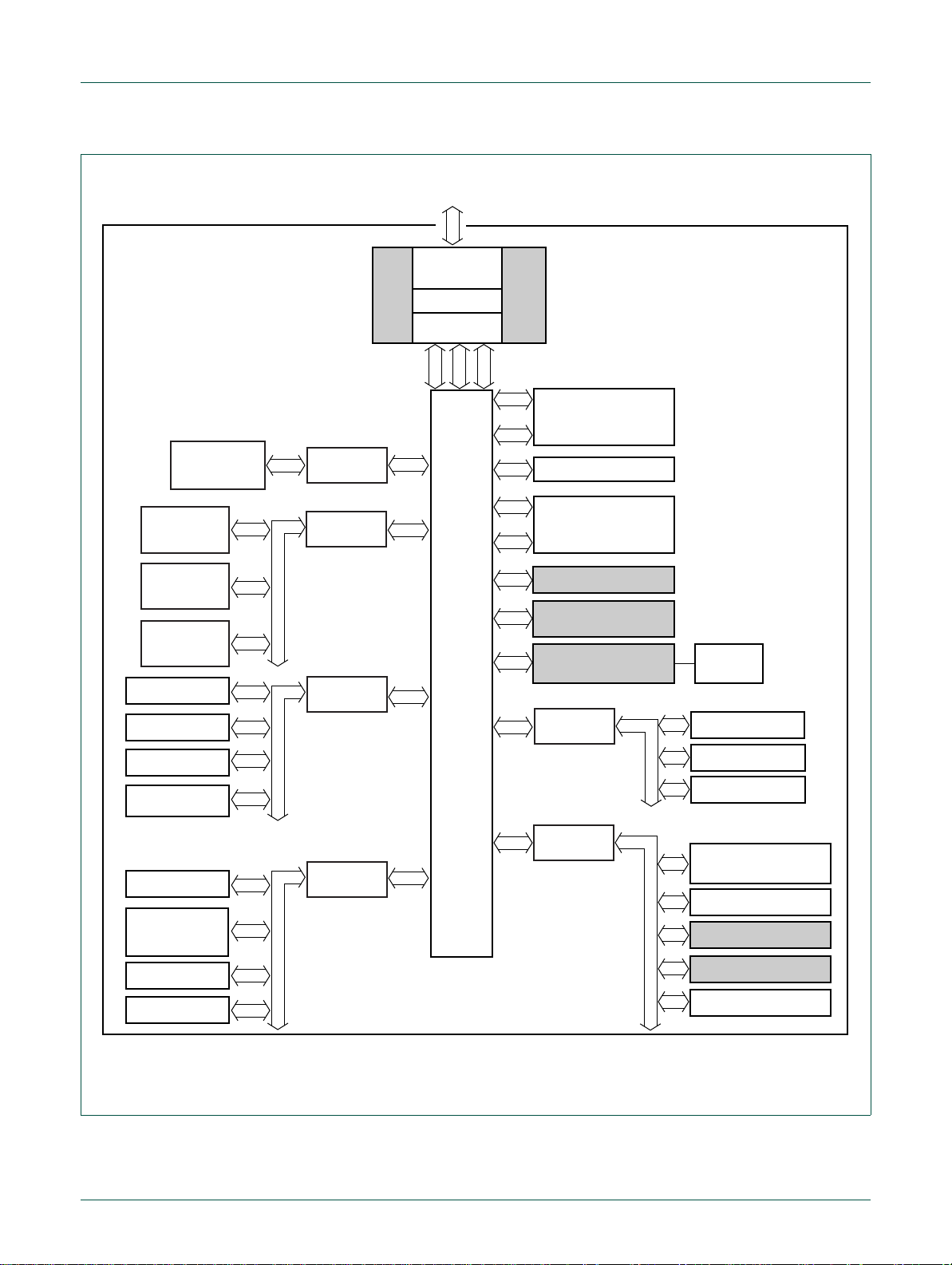

LPC2927/2929

JTAG

interface

8 kB SRAM

general subsystem

power. clock, and

reset subsystem

MSC subsystem

networking subsystem

peripheral subsystem

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

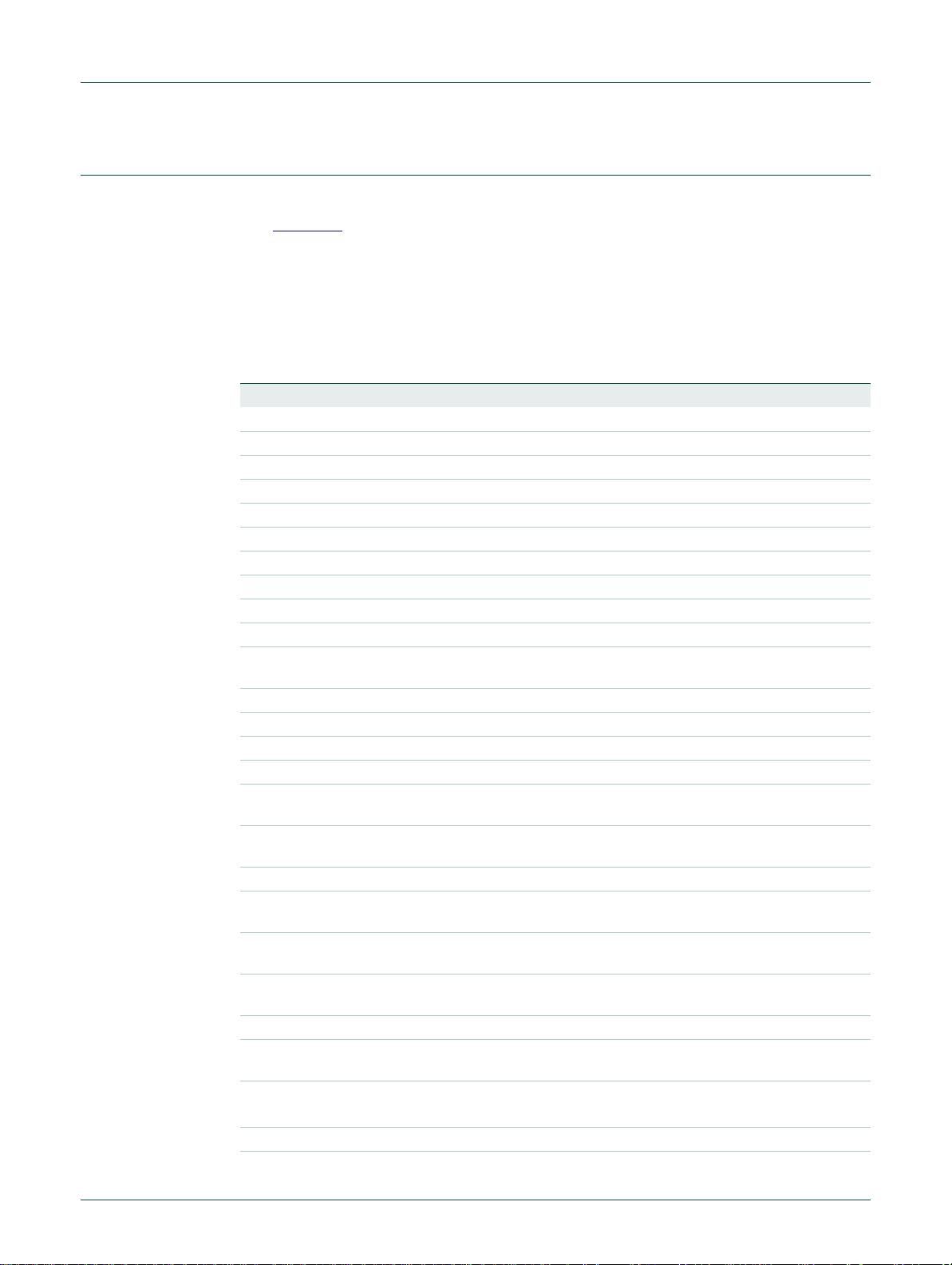

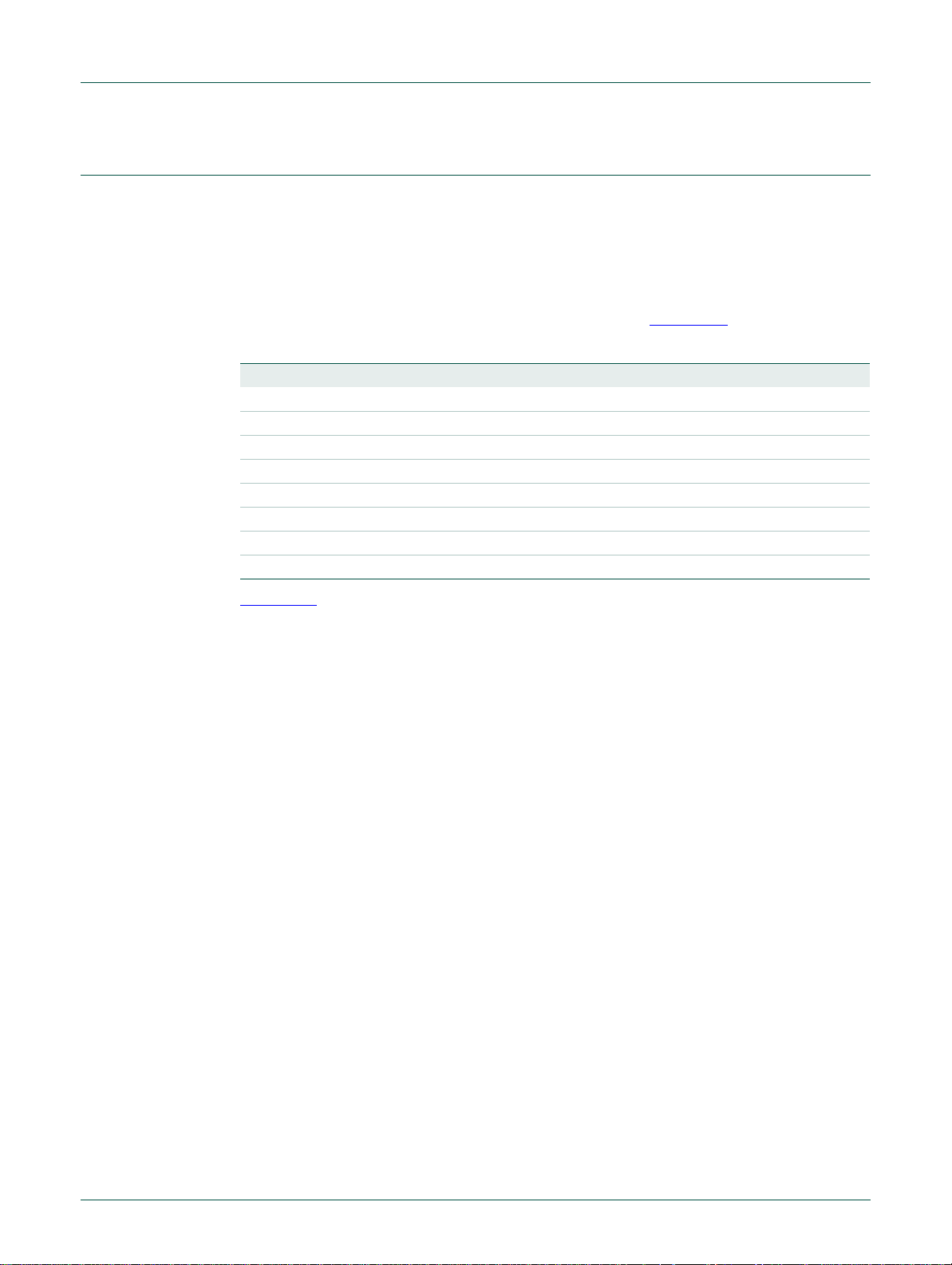

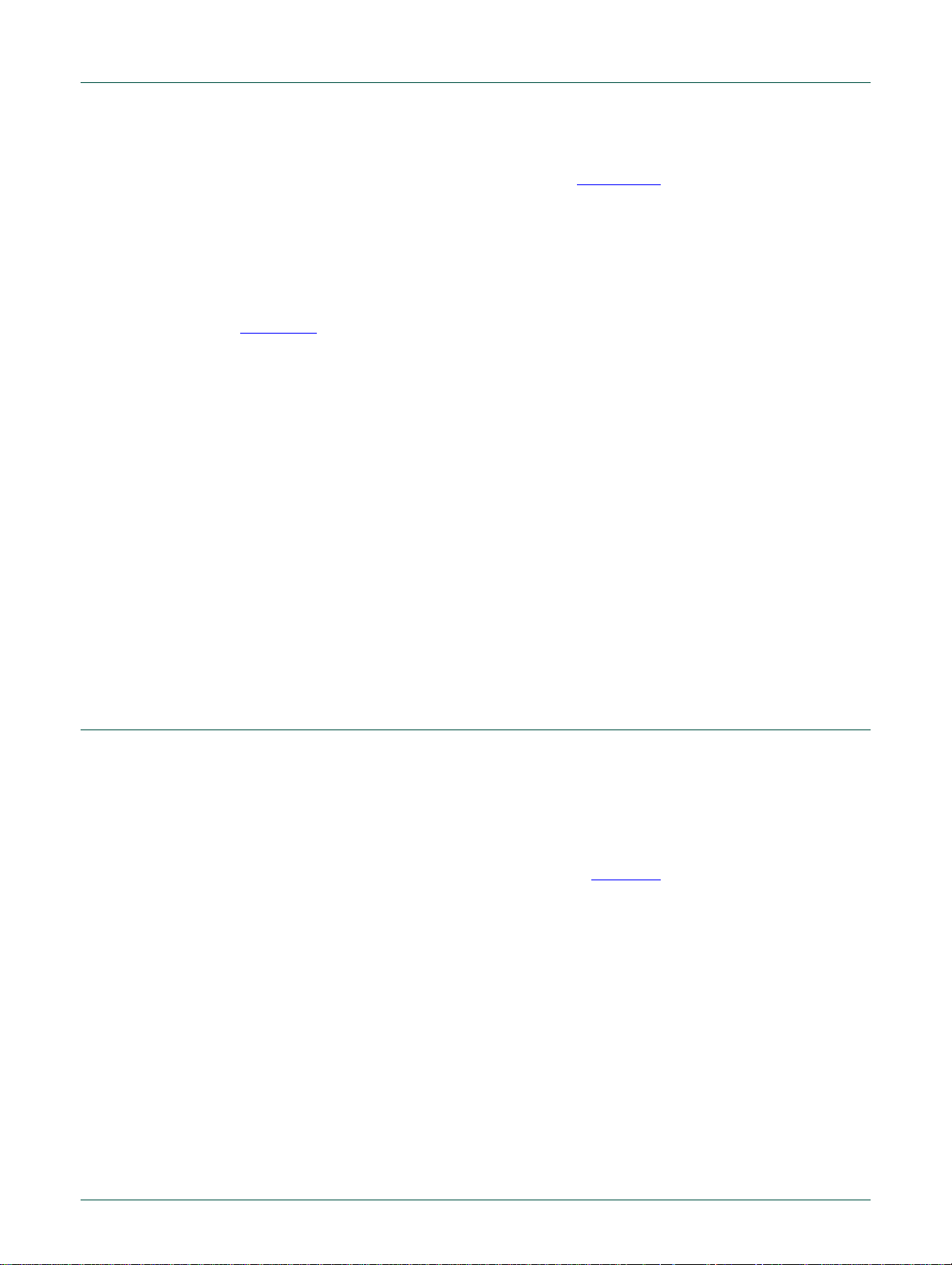

Fig 3. LPC2927/29 block diagram

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 10 of 568

Grey-shaded blocks represent peripherals with connections to the GPDMA.

Page 11

NXP Semiconductors

002aae257

ARM968E-S

DTCM

32 kB

ITCM

32 kB

TEST/DEBUG

INTERFACE

slave

master

1 master

2 slaves

master

EXTERNAL STATIC

MEMORY CONTROLLER

GPDMA CONTROLLER

GPDMA REGISTERS

EMBEDDED SRAM 32 kB

SYSTEM CONTROL

TIMER0/1 MTMR

CAN0/1

GLOBAL

ACCEPTANCE

FILTER

UART/LIN0/1

PWM0/1/2/3

3.3 V ADC1/2

EVENT ROUTER

EMBEDDED SRAM 16 kB

GENERAL PURPOSE I/O

PORTS 0/1/2/3/4/5

TIMER 0/1/2/3

SPI0/1/2

RS485 UART0/1

WDT

AHB TO APB

BRIDGE

AHB TO DTL

BRIDGE

VECTORED

INTERRUPT

CONTROLLER

master

slave

USB HOST/OTG/DEVICE

CONTROLLER

slave

slave

slave

slave

slave

slave

slave

slave

slave

AHB TO DTL

BRIDGE

AHB TO APB

BRIDGE

5 V ADC0

QUADRATURE

ENCODER

CHIP FEATURE ID

AHB TO APB

BRIDGE

I2C0/1

AHB TO APB

BRIDGE

CLOCK

GENERATION

UNIT

POWER

MANAGEMENT

UNIT

RESET

GENERATION

UNIT

AHB

MULTILAYER

MATRIX

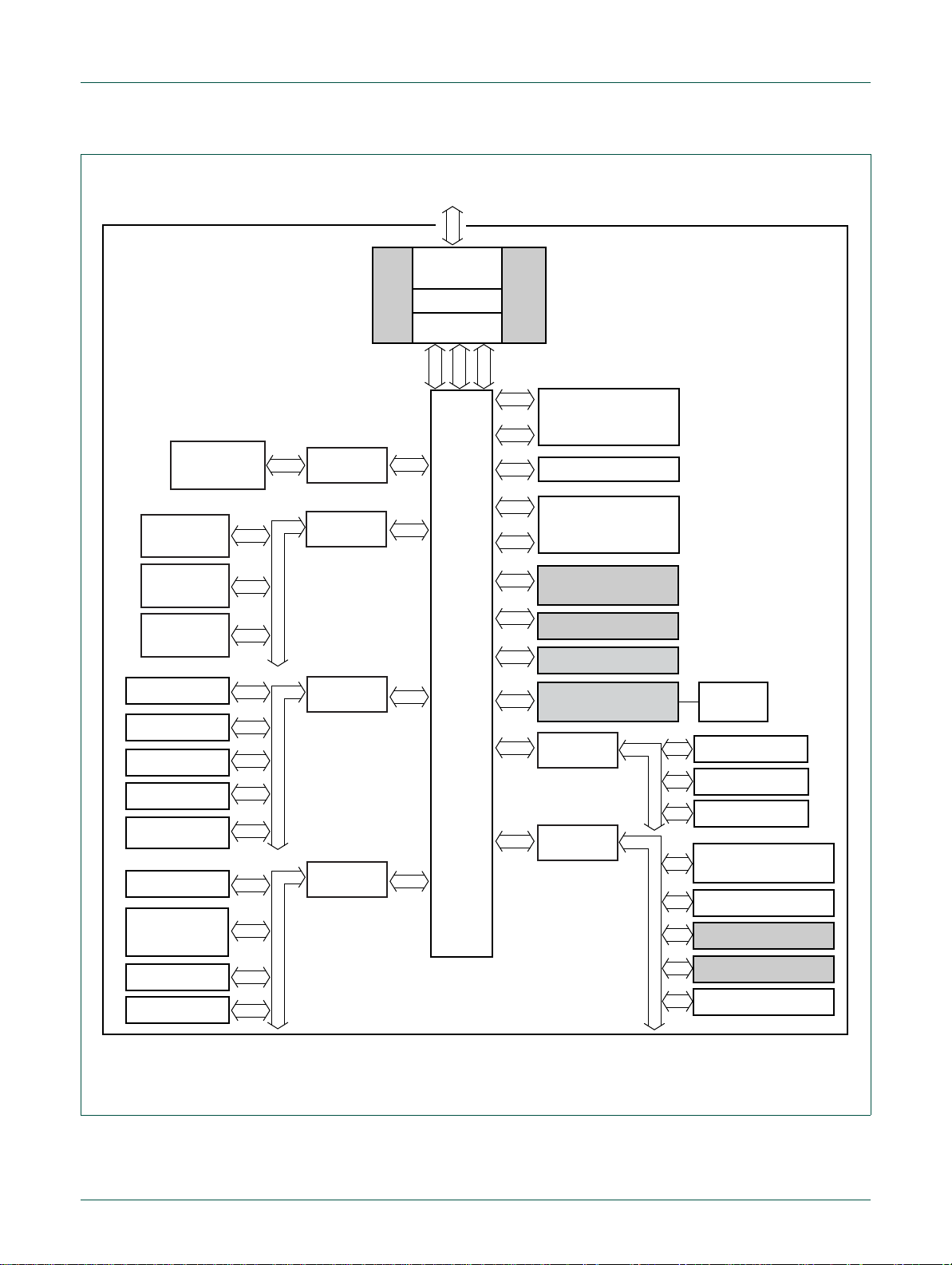

LPC2930

JTAG

interface

8 kB SRAM

general subsystem

power. clock, and

reset subsystem

MSC subsystem

networking subsystem

peripheral subsystem

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

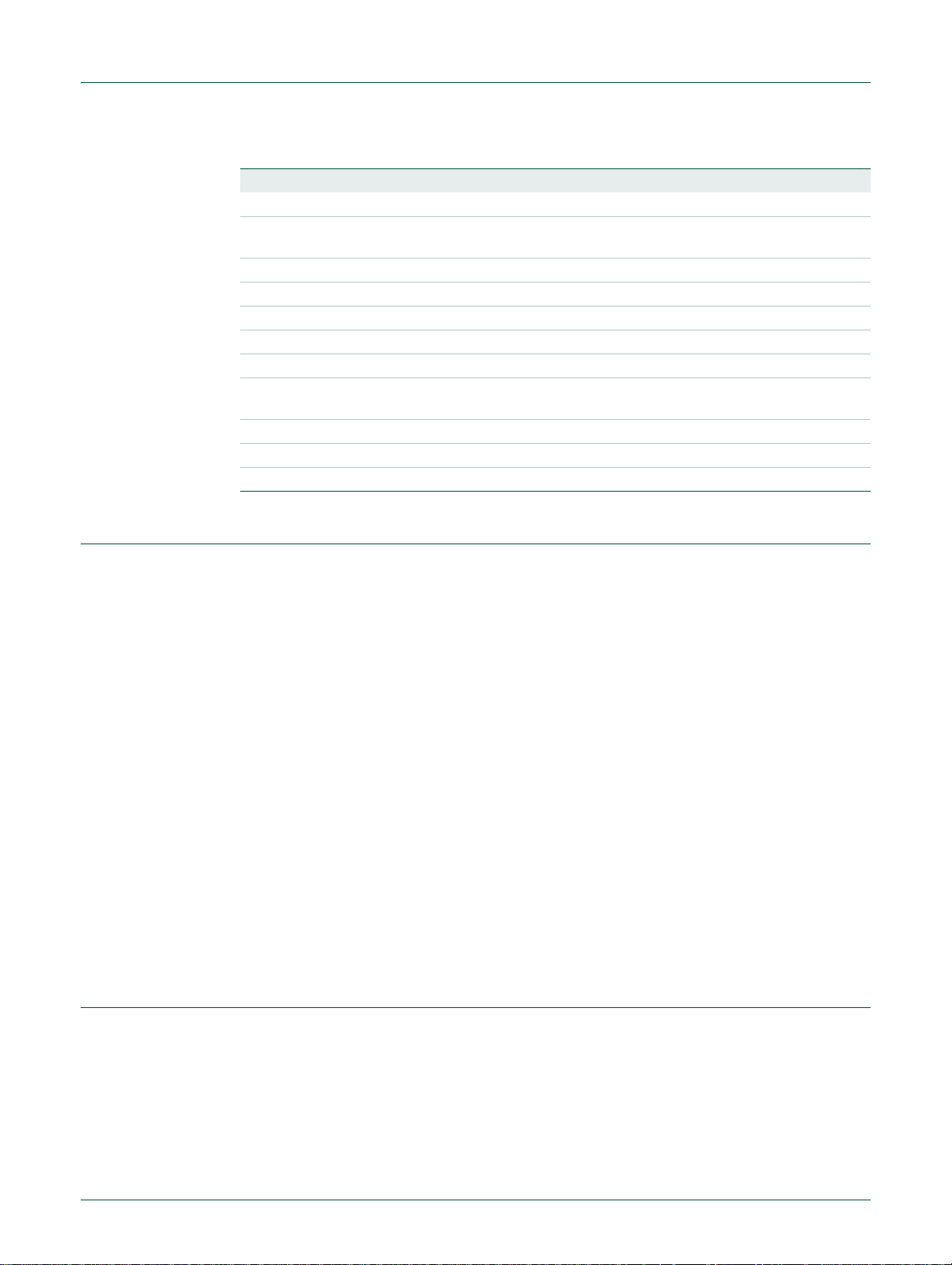

Grey-shaded blocks represent peripherals with connections to the GPDMA.

Fig 4. LPC2930 block diagram

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 11 of 568

Page 12

NXP Semiconductors

002aae254

ARM968E-S

DTCM

32 kB

ITCM

32 kB

TEST/DEBUG

INTERFACE

slave

master

1 master

2 slaves

master

EXTERNAL STATIC

MEMORY CONTROLLER

GPDMA CONTROLLER

GPDMA REGISTERS

EMBEDDED FLASH

768 kB

16 kB

EEPROM

EMBEDDED SRAM 32 kB

SYSTEM CONTROL

TIMER0/1 MTMR

CAN0/1

GLOBAL

ACCEPTANCE

FILTER

UART/LIN0/1

PWM0/1/2/3

3.3 V ADC1/2

EVENT ROUTER

EMBEDDED SRAM 16 kB

GENERAL PURPOSE I/O

PORTS 0/1/2/3/4/5

TIMER 0/1/2/3

SPI0/1/2

RS485 UART0/1

WDT

AHB TO APB

BRIDGE

AHB TO DTL

BRIDGE

VECTORED

INTERRUPT

CONTROLLER

master

slave

USB HOST/OTG/DEVICE

CONTROLLER

slave

slave

slave

slave

slave

slave

slave

slave

slave

slave

AHB TO DTL

BRIDGE

AHB TO APB

BRIDGE

5 V ADC0

QUADRATURE

ENCODER

CHIP FEATURE ID

AHB TO APB

BRIDGE

I2C0/1

AHB TO APB

BRIDGE

CLOCK

GENERATION

UNIT

POWER

MANAGEMENT

UNIT

RESET

GENERATION

UNIT

AHB

MULTILAYER

MATRIX

LPC2939

JTAG

interface

8 kB SRAM

general subsystem

power. clock, and

reset subsystem

MSC subsystem

networking subsystem

peripheral subsystem

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Fig 5. LPC2939 block diagram

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 12 of 568

Grey-shaded blocks represent peripherals with connections to the GPDMA.

Page 13

NXP Semiconductors

6. Functional blocks

This chapter gives an overview of the functional blocks, clock domains, and power modes.

See Table 1–2

The functional blocks are explained in detail in the following chapters. Several blocks are

gathered into subsystems and one or more of these blocks and/or subsystems are put into

a clock domain. Each of these clock domains can be configured individually for power

management (i.e. clock on or off and whether the clock respond s to sleep and wake-up

events).

Table 5. Functional blocks and clock domains

Short Description Comment

Clock domain AHB

ARM ARM9TDMI-S 32-bit RISC processor

SMC Static Memory Controller For external (static) memory banks

SRAM Internal Static Memory -

Clock domain Flash

Flash - Internal Flash Memory

FMC Flash Memory Controller Controller for the internal flash memory

Clock domain USB

USB USB OTG controller -

Clock domain DMA controller

GPDMA General Purpose DMA

Clock domain VIC

VIC Vectored Interrupt Controller Prioritized/vectored interrupt handling

Clock domain general subsystem

CFID Digital Chip ID Identifies the device and its possibilities

ER Event Router Routes wake-up events and external

SCU System Control Unit Configures memory map and I/O

Clock domain peripheral subsystem

GPIO General-Purpose

TMR Timer Provides match output and capture

UART Universal Asynchronous

WDT Watchdog Timer to guard (software) execution

SPI Serial Peripheral Interfac e Supports various industry-standard SPI

Clock domain modulation and sampling-control subsystem

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

DRAFT

Chapter 1: LPC29xx Introductory information

F

T DRAFT DRAFT DRAFT DRA

for availability of peripherals and blocks for specific LPC29xx parts.

controller

interrupts (to CGU/VIC)

functions

Directly controls I/O pins

Input/Output

inputs

Standard 550 serial port

Receiver/Transmitter

protocols

DR

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

ADC Analog-to-Digital Converter 10-bit Analog-to-Digital Converter

PWM Pulse-Width Modulator Synchronized Pulse-Width Modulator

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 13 of 568

Page 14

NXP Semiconductors

Table 5. Functional blocks and clock domains

Short Description Comment

TMR Timer Dedicated Sampling and Control Timer

QEI Quadrature encoder

Clock domain networking subsystem

CAN Gateway Includes acceptance filter

LIN Master controller LIN master controller

I2C I2C-bus

Clock domain power control subsystem

CGU0 Clock Generation Unit Controls clock sources and clock

CGU1 clock generation unit USB clocks and clock out

RGU reset generation unit PMU power management unit -

interface

DRAFT

Chapter 1: LPC29xx Introductory information

…continued

-

domains

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

UM10316

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

7. Architectural overview

The LPC29xx consists of:

• An ARM968E-S processor with real-time emulation support

• An AMBA multi-layer Advanced High-performance Bus (AHB) for interfacing to the

on-chip memory controllers

• Two DTL buses (an universal NXP interface) for interfacing to the interrupt controller

and the Power, Clock and Reset Control cluster (also called subsystem).

• Three ARM Peripheral Buses (APB - a compatible superset of ARM's AMBA

advanced peripheral bus) for connection to on-chip peripherals clustered in

subsystems.

• One ARM Peripheral Bus for event router and system control.

The LPC29xx configures the ARM968E-S processor in little-endian byte order. All

peripherals run at their own clock frequency to optimize the total system power

consumption. The AHB2APB bridge used in the subsystems contains a write-ahead buffer

one transaction deep. This implies that when the ARM968E-S issues a buff ered write

action to a register located on the APB side of the bridge, it continues even though the

actual write may not yet have taken place. Completion of a second write to the same

subsystem will not be executed until the first write is finished.

8. ARM968E-S processor

The ARM968E-S is a general purpose 32-bit RISC processor, which offers high

performance and very low power consumption. The ARM architecture is based on

Reduced Instruction Set Computer (RISC) principles, and the instruction set and related

decode mechanism are much simpler than those of microprogrammed Complex

Instruction Set Computers (CISC). This simplicity results in a high instruction throughput

and impressive real-time interrupt respon se fro m a sm all and co st- effective con tr olle r

core.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 14 of 568

Page 15

NXP Semiconductors

Amongst the most compelling features of the ARM968E-S are:

• Separate directly connected instruction and data Tightly Coupled Memory (TCM)

• Write buffers for the AHB and TCM buses

• Enhanced 16 × 32 multiplier capable of single-cycle MAC operations and 16-bit fixed-

Pipeline techniques are employed so that all pa rts of the p rocessing and memory systems

can operate continuously. The ARM968E-S is based on the ARMv5TE five-stage pipeline

architecture. Typica lly, in a three-stage pipeline architecture, while one instruction is being

executed its successor is being decoded and a third instruction is being fetched from

memory. In the five-stage pipeline additional stages are added for memory access and

write-back cycles.

The ARM968E-S processor also employs a unique architectural strategy known as

THUMB, which makes it ideally suited to high-volume applications with memory

restrictions or to applications where code density is an issue.

DRAFT

Chapter 1: LPC29xx Introductory information

interfaces

point DSP instructions to accelerate signal-processing algorithms and applications.

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

UM10316

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRAFT

DRA

F

DR

AFT

DR

T DRAF

The key idea behind THUMB is that of a super-reduced instruction set. Essentially, the

ARM968E-S processor has two instruction sets:

• Standard 32-bit ARMv5TE set

• 16-bit THUMB set

The THUMB set's 16-bit instruction length allows it to approach twice the density of

standard ARM code while retaining most of the ARM's performance advantage over a

traditional 16-bit controller using 16-bit registers. This is possible because THUMB code

operates on the same 32-bit register set as ARM code.

THUMB code can provide up to 65 % of the code size of ARM, and 160 % of the

performance of an equivalent ARM controller connected to a 16-bit memory system.

The ARM968E-S processor is described in detail in the ARM968E-S data sheet.

9. On-chip flash memory system

The LPC29xx includes up to 768 kB flash memory. This memory can be used for both

code and data storage. Flash memory can be programmed in- system via a serial port

(e.g., CAN).

10. On-chip static RAM

In addition to the two 16 kB or 32 kB TCMs, the LPC29xx includes two static RAM

memories: one of up to 32 kB and one of 16 kB. Both may be used for code and/or data

storage.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 15 of 568

Page 16

UM10316

Chapter 2: LPC29xx memory mapping

Rev. 01.01 — 14 July 2009 User manual

1. How to read this chapter

The memory configuration varies for the different LPC29xx parts (see Table 2–6). In

addition to the memory blocks, peripheral register blocks in memory region 7 are available

only if the peripheral is implemented. See Table 2–7

peripheral registers are available on all LPC29xx parts.

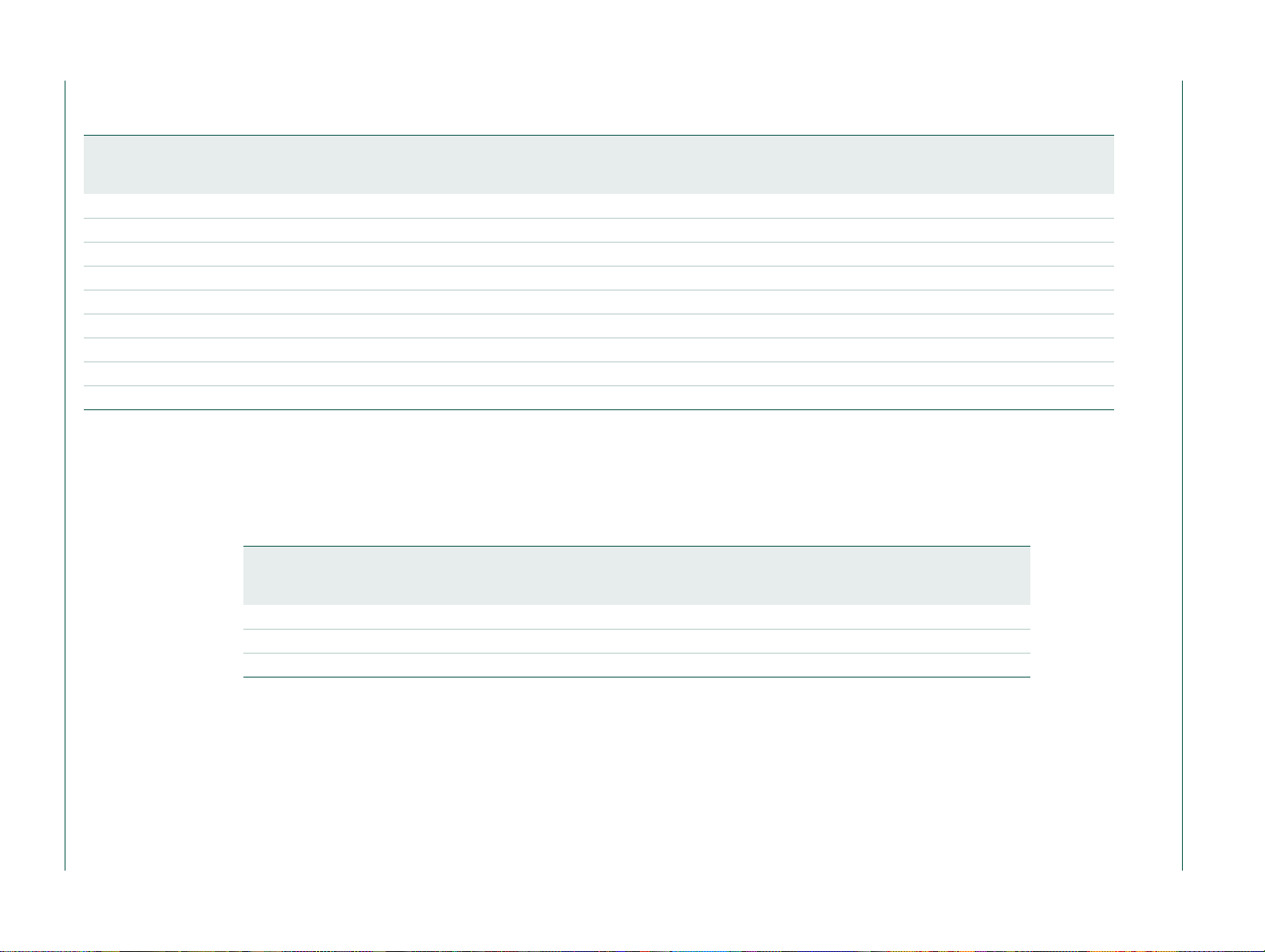

Table 6. LPC29xx memory configurations

Part number Flash SRAM TCM (I/D) SMC

LPC2917/01 512 kB 32 kB 16 kB yes 16/16 kB 8 banks, 16 MB each

LPC2919/01 768 kB 32 kB 16 kB yes 16/16 kB 8 banks, 16 MB each

LPC2921 128 kB 16 kB - yes 16/16 kB LPC2923 256 kB 16 kB - yes 16/16 kB LPC2925 512 kB 16 kB 16 kB yes 16/16 kB LPC2927 512 kB 32 kB 16 kB yes 32/32 kB 8 banks, 16 MB each

LPC2929 768 kB 32 kB 16 kB yes 32/32 kB 8 banks, 16 MB each

LPC2930 - 32 kB 16 kB yes 32/32 kB 8 banks, 16 MB each

LPC2939 768 kB 32 kB 16 kB yes 32/32 kB 8 banks, 16 MB each

SRAM @

0x8000 0000

SRAM @

0x8000 8000

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

DRAFT

F

T DRAFT DRAFT DRAFT DRA

for part specific registers. All other

ETB

(8 kB)

DR

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Table 7. LPC29xx configuration of peripheral registers

Part number peripheral

cluster #2

GPIO ADC0 ADC1 ADC2 USB

LPC291719/01 GPIO0/1/2/3 no yes yes no

LPC2919/01 GPIO0/1/2/3 no yes yes no

LPC2921 GPIO0/1/5 no yes yes yes

LPC2923 GPIO0/1/5 no yes yes yes

LPC2925 GPIO0/1/5 no yes yes yes

LPC2927 GPIO0/1/2/3/5 yes yes yes yes

LPC2929 GPIO0/1/2/3/5 yes yes yes yes

LPC2930 GPIO0/1/2/3/4/5 yes yes yes yes

LPC2939 GPIO0/1/2/3/4/5 yes yes yes yes

2. Memory-map view of the AHB

The LPC29xx uses an AHB multilayer bus with the CPU and the GPDMA as the bus

masters. The AHB slaves are connected to the AHB-lite multilayer bus.The ARM968E-S

CPU has access to all AHB slaves and hence to all address regions.

peripheral cluster #6 AHB

peripherals

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 16 of 568

Page 17

NXP Semiconductors

3. Memory-map regions

The ARM9 processor has a 4 GB of address space. The LPC29xx has divided this

memory space into eight regions of 512 MB each. Each region is used for a dedicated

purpose.

An exception to this is region 0; several of the other regions (or a part of it) can be

shadowed in the memory map at this region. This shadowing can be controlled by

software via the programmable re-mapping registers (see Table 6–64

Table 8. LPC29xx memory regions

Memory region # Address Description

0 0x0000 0000 TCM area and shadow area

1 0x2000 0000 embedded flash area

2 0x4000 0000 external static memory area

3 0x6000 0000 external static memory controller area

4 0x8000 0000 internal SRAM area

5 0xA000 0000 not used

6 0xC000 0000 not used

7 0xE000 0000 bus-peripherals area

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 2: LPC29xx memory mapping

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

).

DR

AFT

DRAFT

DR

F

T DRAF

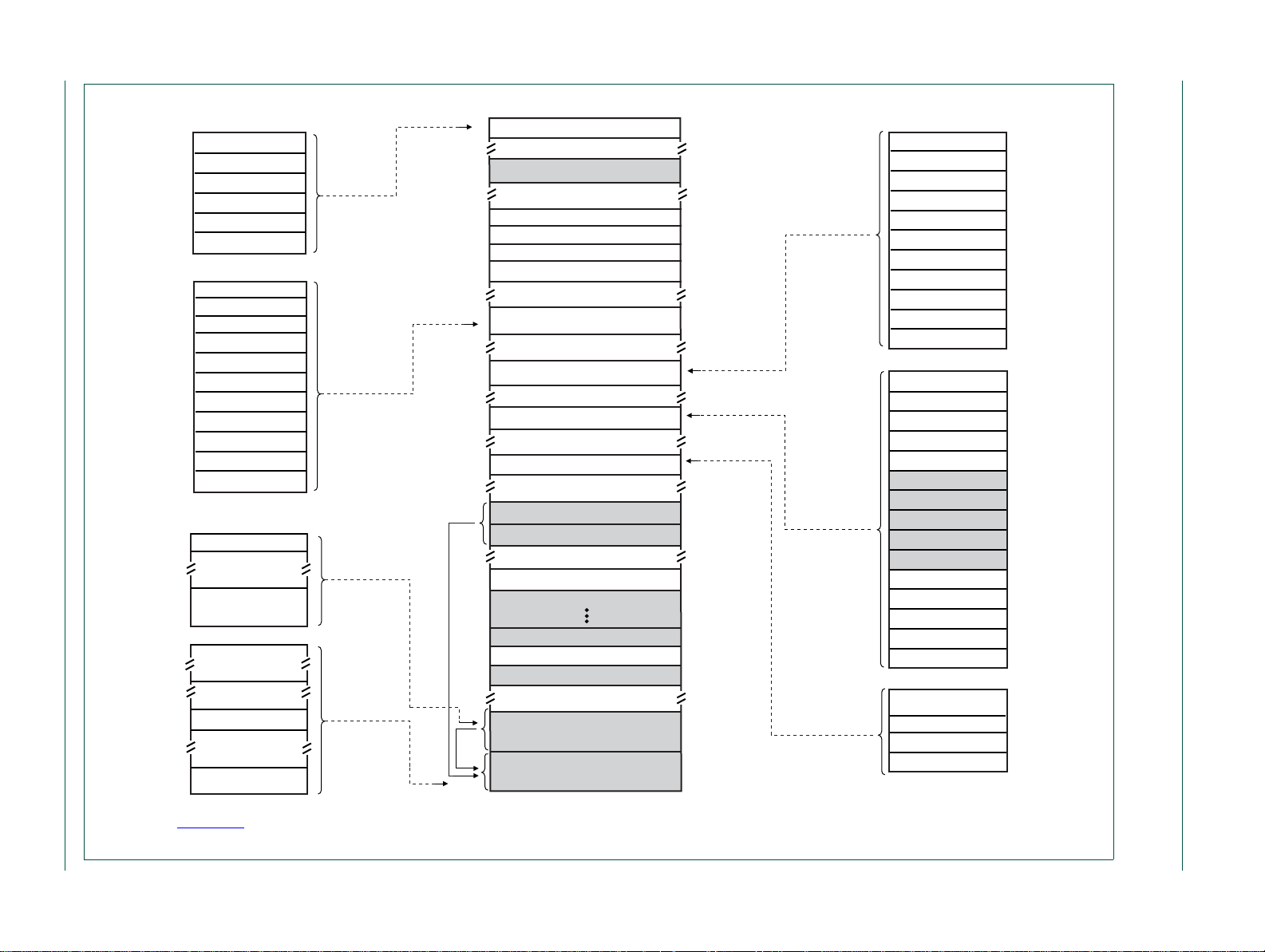

Figure 2–6 gives a graphical overview of the LPC29xx memory map.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 17 of 568

Page 18

User manual Rev. 01.01 — 14 July 2009 18 of 568

16 MB ext. static memory bank 0

(1)

16 MB ext. static memory bank 1

(1)

ext. static memory banks 7 to 2

(1)

reserved

DMA interface to TCM

PCR/VIC control

0x0000 0000

0 GB

1 GB

4 GB

2 GB

0x4000 0000

0x4100 0000

0x4300 0000

0x4200 0000

0x2000 0000

0x6000 0000

0x6000 4000

0x8000 0000

0x8000 8000

0x8000 C000

0xE000 0000

0xE002 0000

0xE004 0000

0xE006 0000

0xE008 0000

0xE00A 0000

0xE00C 0000

0xE00E 0000

0xE010 0000

0xE014 0000

0xE018 3000

0xF000 0000

0xF080 0000

0xFFFF 8000

0xFFFF FFFF

reserved

reserved

reserved

reserved

reserved

reserved

reserved

peripheral subsystem #0

peripheral subsystem #2

peripheral subsystem #4

peripheral subsystem #6

0xE018 2000

0xE018 0000

32 kB AHB SRAM

(1)

16 kB AHB SRAM

(1)

reserved

USB controller

(1)

DMA controller

8 kB ETB SRAM

ETB control

reserved

ITCM/DTCM

on-chip flash

(1)

0x2020 4000

0x0000 0000

0x0040 0000

0x0000 8000

0x0040 8000

0x0080 0000

0x2000 0000

32 kB

(1)

ITCM

32 kB

(1)

DTCM

reserved

reserved

no physical memory

peripherals #6

MSCSS

subsystem

ITCM/DTCM

memory

EMI/SMC

(1)

peripherals #2

peripheral

subsystem

0xE004 1000

0xE004 2000

0xE004 3000

0xE004 4000

0xE004 6000

0xE004 8000

0xE004 A000

0xE004 B000

0xE004 D000

0xE005 0000

0xE006 0000

0xE004 C000

0xE004 9000

0xE004 7000

0xE004 5000

0xE004 0000

SPI0

WDT

TIMER0

TIMER1

TIMER2

TIMER3

UART0

UART1

SPI1

SPI2

GPIO0

GPIO1

GPIO2

(1)

GPIO3 to GPIO5

(1)

peripherals #0

general

subsystem

0xE000 1000

0xE000 2000

0xE000 2000

0xE002 0000

0xE000 0000

CFID

SCU

event router

peripherals #4

networking

subsystem

0xE008 1000

0xE008 0000

CAN0

CAN1

0xE008 2000

0xE008 3000

0xE008 4000

0xE008 7000

0xE008 9000

0xE008 B000

0xE00A 0000

0xE008 A000

0xE008 8000

0xE008 6000

I2C0

I2C1

reserved

CAN ID LUT

CAN common regs

LIN0

LIN1

CAN AF regs

0xE00C 0000

0xE00C 1000

0xE00C 2000

0xE00C 3000

0xE00C 4000

0xE00C 5000

0xE00C 6000

0xE00C 7000

0xE00C 8000

0xE00C 9000

0xE00C A000

0xE00E 0000

ADC0 (5V)

(1)

ADC1

ADC2

PWM0

PWM1

PWM3

quadrature encoder

PWM2

MSCSS timer0

MSCSS timer1

PCR/VIC

subsystem

0xFFFF 8000

0xFFFF 9000

0xFFFF A000

0xFFFF B000

0xFFFF C000

0xFFFF F000

0xFFFF FFFF

PMU

CGU1

reserved

reserved

reserved

reserved

reserved

VIC

CGU0

RGU

512 MB shadow area

remappable to

shadow area

LPC29xx

768 kB

(1)

on-chip

flash

flash controller

0x2000 0000

reserved

0x200C 0000

0x2020 0000

0x2020 4000

flash

memory

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

UM10316_1 © NXP B.V. 2009. All rights reserved.

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

NXP Semiconductors

Fig 6. LPC29xx system memory map: graphical overview

(1) See Section 2–1 for part-specific implementation. Gray-shaded memory regions are accessible by the GPDMA controller.

Chapter 2: LPC29xx memory mapping

DRAFT

D

RAFT DRA

D

RAFT DRAFT DRAFT DRAFT DRAFT D

UM10316

F

T DRAFT DRAFT DRAFT DRA

DRA

F

T DRAF

DR

D

RAFT

DRAFT

DR

AFT

DRAFT

DR

AFT

Page 19

NXP Semiconductors

Region #0:TCM area

0x0000_0000 - 0x1FFF_FFFF

(Offset Address

0x0000 0000

0x1FFF FFFF

0x0000 4000/0

0x0040 0000

I-TCM region aliasses

I-TCM (16/32 kByte)

0x0080 0000

D-TCM region aliasses

D-TCM (16 kByte)

region #0 no physical memory

0x0040 4000/0

3.1 Region 0: TCM/shadow area

The ARM968E-S processor has its exception vectors located at address logic 0. Since

flash is the only non-volatile memory available in the LPC29xx, the exception vectors in

the flash must be located at address logic 0 at reset (AHB_RST).

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 2: LPC29xx memory mapping

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 19 of 568

Fig 7. Region 0 memory map

After booting a choice must be made for region 0. When enable d, the Tightly Coupled

Memories (TCMs) occupy fixed address locations in region 0 as indicated in Figure 2–6

Information on how to enable the TCMs can be found in the ARM documentation, see

Ref. 31–2

To enable memory re-mapping, the LPC29xx AHB system memory map provides a

shadow area (region 0) starting at address log ic 0 . This is a vir tual memo ry re gio n, i.e. no

actual memory is present at the shadow area addresses. A selectable region of the AHB

.

.

system memory map is, apart from its own specific region, also accessible via this shadow

area region.

Page 20

NXP Semiconductors

+ 0x00000000

+ 0x1FFFFFFF

+ 0x00200000

FLASH IF1

Configuration Area (4 Kbyte)

+ 0x00200FFF

Embedded FLASH

memory area

512 Kbyte -

768 Kbyte

+ 0x0007FFFF - 0x000BFFF

After reset, the region 1 embedded flash area is always available at the shadow area.

After booting, any other region of the AHB system memory map (e.g. internal SRAM) can

be re-mapped to region 0 by means of the shadow memory mapping register. For more

details about the shadow area see Table 6–64

3.2 Region 1: embedded flash area

Figure 2–8 gives a graphical overview of the embedded flash memory map.

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

DR

DRAFT

Chapter 2: LPC29xx memory mapping

F

T DRAFT DRAFT DRAFT DRA

.

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Fig 8. Region 1 embedded flash memory

Region 1 is reserved for the embedded flash. A data area of 2 Mbyte (to be prepared for a

larger flash-memory instance) and a configuration area of 4 kB are reserved for each

embedded flash instance. Although the LPC29xx contains only one embedded flash

instance, the memory aperture per instance is defined at 4 Mbyte.

3.3 Region 2: external static memory area

Region 2 is reserved for the external static memory. The LPC29xx provides I/O pins for

eight bank-select signals and 24 address lines. This implies that eight memory banks of

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 20 of 568

16 Mbytes each can be addressed externally.

3.4 Region 3: external static memory controller area

The external Static-Memory Controller configuration area is located at region 3

3.5 Region 4: internal SRAM area

Figure 2–6 gives a graphical overview of the internal SRAM memory map.

Page 21

NXP Semiconductors

Region 4 is reserved for internal SRAM. The LPC29xx has two internal SRAM instances.

Instance #0 is 32 kB, instance #1 is 16 kB. See Section 7–1

3.6 Regions 5 and 6

Regions 5 and 6 are not used.

3.7 Region 7: bus-peripherals area

Figure 2–6 gives a graphical overview of the bus-peripherals area memory map.

Region 7 is reserved for all stand-alone memory-mapped bus peripherals.

The lower part of region 7 is again divided into APB clusters, also referred to as

subsystems in this User Manual. A APB cluster is typically used as the address space for

a set of APB peripherals connected to a single AHB2APB bridge, the slave on the AHB

system bus. The clusters are aligned on 256 kB boundaries. In the LPC29xx four APB

clusters are in use: General SubSystem (GeSS), Peripheral SubSystem (PeSS) ,

Networking SubSystem (IVNSS), and the Modulation and Sampling SubSystem

(MSCSS). The APB peripherals are aligned on 4 kB boundaries inside the APB clusters.

D

RAFT

UM10316

F

T DRAFT DRAFT DRAFT DRA

D

RAFT DRA

.

D

RAFT DRAFT DRAFT DRAFT DRAFT D

DRAFT

Chapter 2: LPC29xx memory mapping

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

The upper part of region 7 is used as the memory area where memory-mapped register

interfaces of stand-alone AHB peripherals and a DTL cluster reside. Each of these is a

slave on the AHB system bus. In the LPC29xx two such slaves are present: the Power,

Clock and Reset subsystem (PCRSS) and the Vectored Interrupt Controller (VIC). The

PCRSS is a DTL cluster in which the CGU, PMU and RGU are connected to the AHB

system bus via an AHB2DTL adapter. The VIC is a DTL target connected to the AHB

system bus via its own AHB2DTL adapter.

4. Memory-map operating concepts

The basic concept in the LPC29xx is that each memory area has a ‘natural’ location in the

memory map. This is the address range for which code residing in that area is written.

Each memory space remains permanently fixed in the same location, elim inating the need

to have portions of the code designed to run in different address ranges.

Because of the location of the exception-handler vectors on the ARM9 processor (at

addresses 0000 0000h through 0000 001Ch: see Table 2–9

embedded flash is mapped at address 0000 0000h to allow initial code to be executed

and to perform the required initialization, which starts executing at 0000 0000h.

The LPC29xx generates the appropriate bus-cycle abort exception if an access is

attempted for an address that is in a reserved or unused address region or unassigned

peripheral spaces. For these areas both attempted data accesses and instruction fetches

generate an exception. Note that write-access addresses should be word-aligned in ARM

code or half-word aligned in Thumb code. Byte-aligned writes are performed as word or

half-word aligned writes without error signalling.

) By default, after reset, the

Within the address space of an existing peripheral a dat a-abort exception is not gen erated

in response to an access to an undefined address. Address decoding within each

peripheral is limited to that needed to distinguish defined registers within the peripheral

itself. Details of address aliasing within a peripheral sp ace are not defined in the LPC29xx

documentation and are not a supported feature.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 21 of 568

Page 22

NXP Semiconductors

Note that the ARM stores the pre-fetch abort flag along with the associated instruction

(which will be meaningless) in the pipeline and processes the abort only if an attempt is

made to execute the instruction fetched from the illegal address. This prevents the

accidental aborts that could be caused by pre-fetches occurring when code is executed

very near to a memory boundary.

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 2: LPC29xx memory mapping

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Table 2–10

Table 9. Interrupt vectors address table

Address Exception

0x0000 0000 Reset

0x0000 0004 Undefined instruction

0x0000 0008 Software interrupt

0x0000 000C Pre-fetch abort (instruction-fetch memory fault)

0x0000 0010 Data abort (data-access memory fault)

0x0000 0014 reserved

0x0000 0018 IRQ

0x0000 001C FIQ

Table 10. Peripherals base-address overview

Base address Base name AHB peripherals

Memory region 0 to region 6

0x0000 0000 TCM memory

0x2000 0000 Embedded flash memory

0x2020 0000 FMC RegBase Embedded-flash controller

0x4000 0000 External static memory

0x6000 0000 SMC RegBase External Static-Memory Controller

0x8000 0000 Internal SRAM memory

APB Cluster 0: general subsystem

0xE000 0000 CFID RegBase Chip/feature ID register

0xE000 1000 SCU RegBase System Control Unit

0xE000 2000 ER RegBase Event Router

APB Cluster 2: peripheral subsystem

0xE004 0000 WDT RegBase Watchdog Timer

0xE004 1000 TMR RegBase Timer 0

0xE004 2000 TMR RegBase Timer 1

0xE004 3000 TMR RegBase Timer 2

0xE004 4000 TMR RegBase Timer 3

0xE004 5000 UART RegBase UART 0

0xE004 6000 UART RegBase UART 1

0xE004 7000 SPI RegBase SPI 0

0xE004 8000 SPI RegBase SPI 1

0xE004 9000 SPI RegBase SPI 2

gives the base address overview of all peripherals:

configuration registers

configuration registers

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 22 of 568

Page 23

NXP Semiconductors

Table 10. Peripherals base-address overview

Base address Base name AHB peripherals

0xE004 A000 GPIO RegBase General-Purpose I/O 0

0xE004 B000 GPIO RegBase General-Purpose I/O 1

0xE004 C000 GPIO RegBase General-Purpose I/O 2

0xE004 D000 GPIO RegBase General-Purpose I/O 3

0xE004 E000 GPIO RegBase General-Purpose I/O 4

0xE004 F000 GPIO RegBase General-Purpose I/O 5

APB Cluster 4: networking subsystem

0xE008 0000 CANC RegBase CAN controller 0

0xE008 1000 CANC RegBase CAN controller 1

0xE008 2000 I2C RegBase I

0xE008 3000 I2C Regbase I

0xE008 6000 CANAFM RegBase CAN ID look-up table memory

0xE008 7000 CANAFR RegBase CAN acceptance filter registers

0xE008 8000 CANCS RegBase CAN central status registers

0xE008 9000 LIN RegBase LIN master controller 0

0xE008 A000 LIN RegBase LIN master controller 1

APB Cluster 6: modulation and sampling-control subsystem

0xE00C 0000 MTMR RegBase MSCSS timer 0

0xE00C 1000 MTMR RegBase MSCSS timer 1

0xE00C 2000 ADC RegBase ADC 0

0xE00C 3000 ADC RegBase ADC 1

0xE00C 4000 ADC RegBase ADC 2

0xE00C 5000 PWM RegBase PWM 0

0xE00C 6000 PWM RegBase PWM 1

0xE00C 7000 PWM RegBase PWM 2

0xE00C 8000 PWM RegBase PWM 3

0xE00C 9000 QEI RegBase Quadrature encoder interface

AHB peripherals: DMA controller, USB controller

E010 0000 USB RegBase USB controller registers

E014 0000 DMA RegBase GPDMA controller registers

Power, Clock and Reset control cluster

FFFF 8000 CGU RegBase Clock Generation Unit

FFFF 9000 RGU RegBase Reset Generation Unit

FFFF A000 PMU RegBase Power Management Unit

Vector interrupt controller

FFFF F000 VIC RegBase Vectored Interrupt Controller

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

DRAFT

Chapter 2: LPC29xx memory mapping

F

T DRAFT DRAFT DRAFT DRA

…continued

2

C0-bus interface

2

C1-bus interface

DR

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 23 of 568

Page 24

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

Rev. 01.01 — 14 July 2009 User manual

1. How to read this chapter

This chapter describes the base clock generation for all LPC29xx parts. CGU0 is identical

for all parts. CGU1 is configuration dependent.

T able 11. LPC29xx base clock options

Part CGU0 base

clocks

LPC2917/19/01 see Table 3–12

LPC2921/23/25 see Table 3–12

LPC2927/29 see Table 3–12

LPC2939 see Table 3–12

LPC2930 see Table 3–12

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT

RAFT DRA

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

CGU1 base clocks

BASE_OUT_CLK

BASE_OUT_CLK, BASE_USB_CLK

BASE_OUT_CLK, BASE_USB_CLK, BASE_USB_I2C_CLK

BASE_OUT_CLK, BASE_USB_CLK, BASE_USB_I2C_CLK

BASE_OUT_CLK, BASE_USB_CLK, BASE_USB_I2C_CLK

DR

AFT

DRAFT

DR

F

T DRAF

2. Introduction

The CGU0 is part of the Power Control, Clock, and Reset control (PCR) block and

provides the clocks for all subsystems. A second, dedicated CGU1 provides the clocks for

the USB block and a clock output. The CGU1 has two clock inputs to its PLL which are

internally connected to two base clocks in the CGU0.

Both CGUs are functionally identical and have their own PLL and fractional divider

registers.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 24 of 568

Page 25

NXP Semiconductors

TIMER0/1 MTMR

PWM0/1/2/3

ADC0/1/2

QEI

modulation and sampling

control subsystem

BASE_MSCSS_CLK

branch

clocks

branch

clocks

BASE_ADC_CLK

BASE_ICLK0_CLK

BASE_ICLK1_CLK

CAN0/1

GLOBAL

ACCEPTANCE

FILTER

LIN0/1

I2C0/1

networking subsystem

BASE_IVNSS_CLK

branch

clocks

RESET/CLOCK

GENERATION &

POWER

MANAGEMENT

power control subsystem

BASE_PCR_CLK

branch

clock

GPIO0 to 5

TIMER 0/1/2/3

SPI0/1/2

UART0/1

WDT

BASE_SYS_CLK

CPU

AHB MULTILAYER MATRIX

VIC

GPDMA

USB REGISTERS

FLASH/SRAM/SMC

general subsytem

peripheral subsystem

AHB TO APB BRIDGES

SYSTEM CONTROL

EVENT ROUTER

CFID

branch

clocks

BASE_SAFE_CLK

BASE_UART_CLK

BASE_SPI_CLK

BASE_TMR_CLK

CGU0

CGU1

BASE_USB_CLK

BASE_USB_I2C_CLK

BASE_OUT_CLK

USB

CLOCK

OUT

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

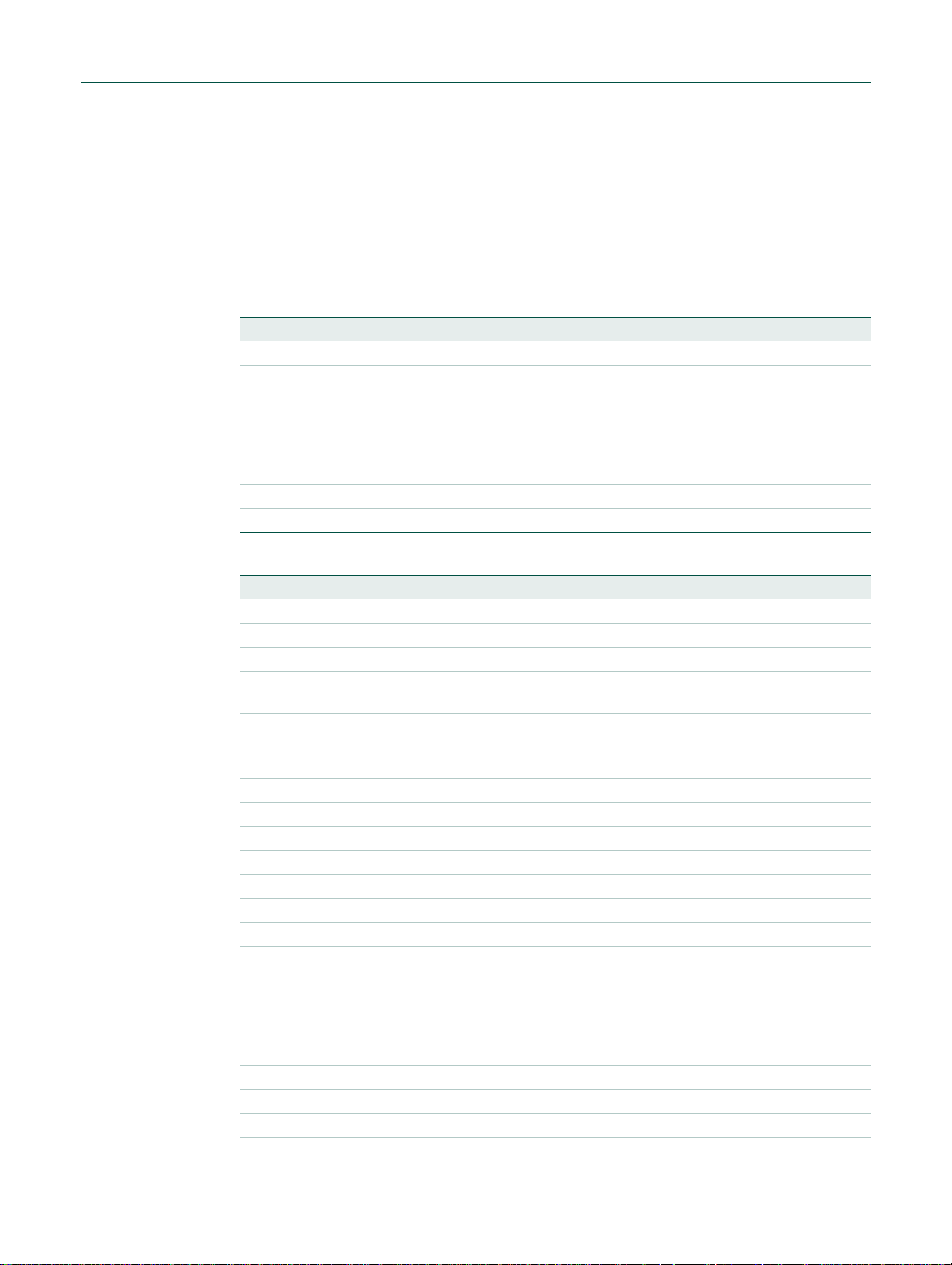

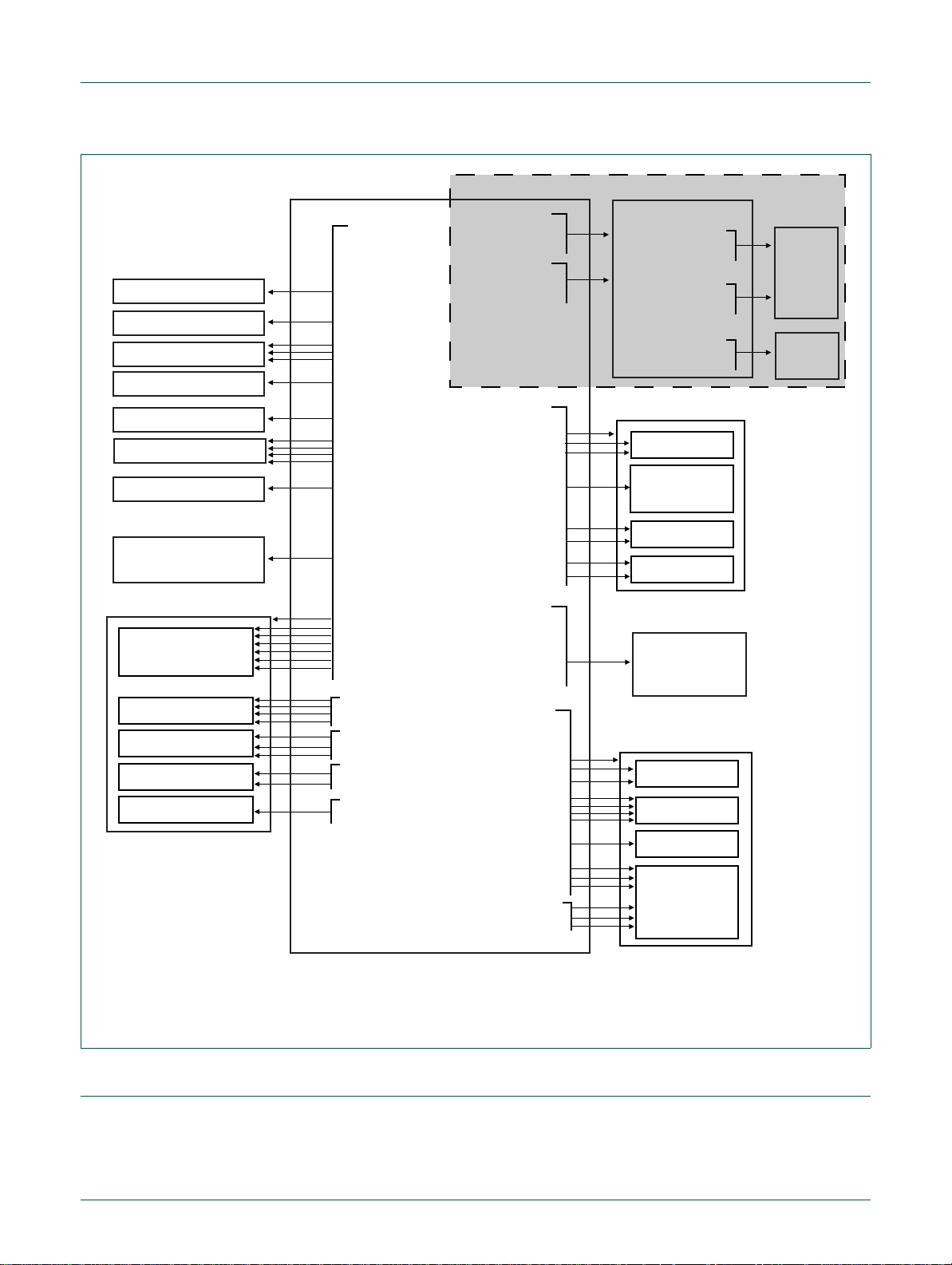

Fig 9. LPC29xx clock generation

3. CGU0 functional description

The implementation of GPIO, ADC, and memory subsystem branch clocks varies for different LPC29xx parts.

The CGU0 uses a set of building blocks to generate the clock for the output branches. The

building blocks are as follows:

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 25 of 568

Page 26

NXP Semiconductors

• OSC1M (LP_OSC) – 1 MHz crystal oscillator

• XO50M – up to 25 MHz oscillator

• PL160M – PLL

• FDIV0..6 – 7 Frequency Dividers

• Output control

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

The following clock output branches are generated (Table 3–12

Table 12. CGU0 base clocks

Number Name Frequency

0 BASE_SAFE_CLK 0.4 base safe clock (always on) for WDT

1 BASE_SYS_CLK 125 base system clock; ARM and AHB clock

2 BASE_PCR_CLK 0.4

3 BASE_IVNSS_CLK 125 base IVNSS subsystem clock for

4 BASE_MSCSS_CLK 125 base MSCSS subsystem clock for

5 BASE_ICLK0_CLK 125 base internal clock 0, for CGU1

6 BASE_UART_CLK 125 base UART clock

7 BASE_SPI_CLK 50 base SPI clock

8 BASE_TMR_CLK 125 base timers clock

9 BASE_ADC_CLK 4.5 base ADCs clock

10 test clock; reserved - this is an internal clock used for testing

1 1 BASE_ICLK1_CLK 125 base internal clock 1, for CGU1

(MHz)

[2]

[1]

Description

base PCR subsystem clock; for power

control subsystem

networking subsystem (CAN, LIN, and

I2C)

modulation and sampling control

subsystem.

only. This clock is running at start-up and

should be disabled in the PMU (see

Table 5–51

configuration registers).

):

for the test shell clock

[1] Maximum frequency that guarantees stable operation of the LPC29xx.

[2] Fixed to low-power oscillator.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 26 of 568

Page 27

NXP Semiconductors

400 kHz LP_OSC

PLL

FDIV0

EXTERNAL

OSCLLLATOR

FDIV1

FDIV6

OUT 0

OUT 1

OUT 11

clkout

clkout120

clkout240

CLOCK GENERATION UNIT (CGU0)

FREQUENCY MONITOR

CLOCK DETECTION

AHB TO DTL BRIDGE

BASE_SYS_CLK

BASE_ICLK1_CLK

(to CGU1)

OUT 3

BASE_IVNSS_CLK

OUT 2

BASE_PCR_CLK

BASE_SAFE_CLK

FDIV_CONF6

PLL_CONTROL

FDIV_CONF1

FDIV_CONF0

SYS_CLK_

CONF

SAFE_CLK_CONF

PCR_CLK_CONF

LP_OSC

EXT OSC

PLL clkout

PLL clkout120

PLL clkout240

FDIV0

FDIV6

LP_OSC

EXT OSC

PLL clkout

PLL clkout120

PLL clkout240

FDIV0

FDIV6

IVNSS_CLK_CONF

ICLK1_CLK_CONF

FREQ_MON

RDET

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

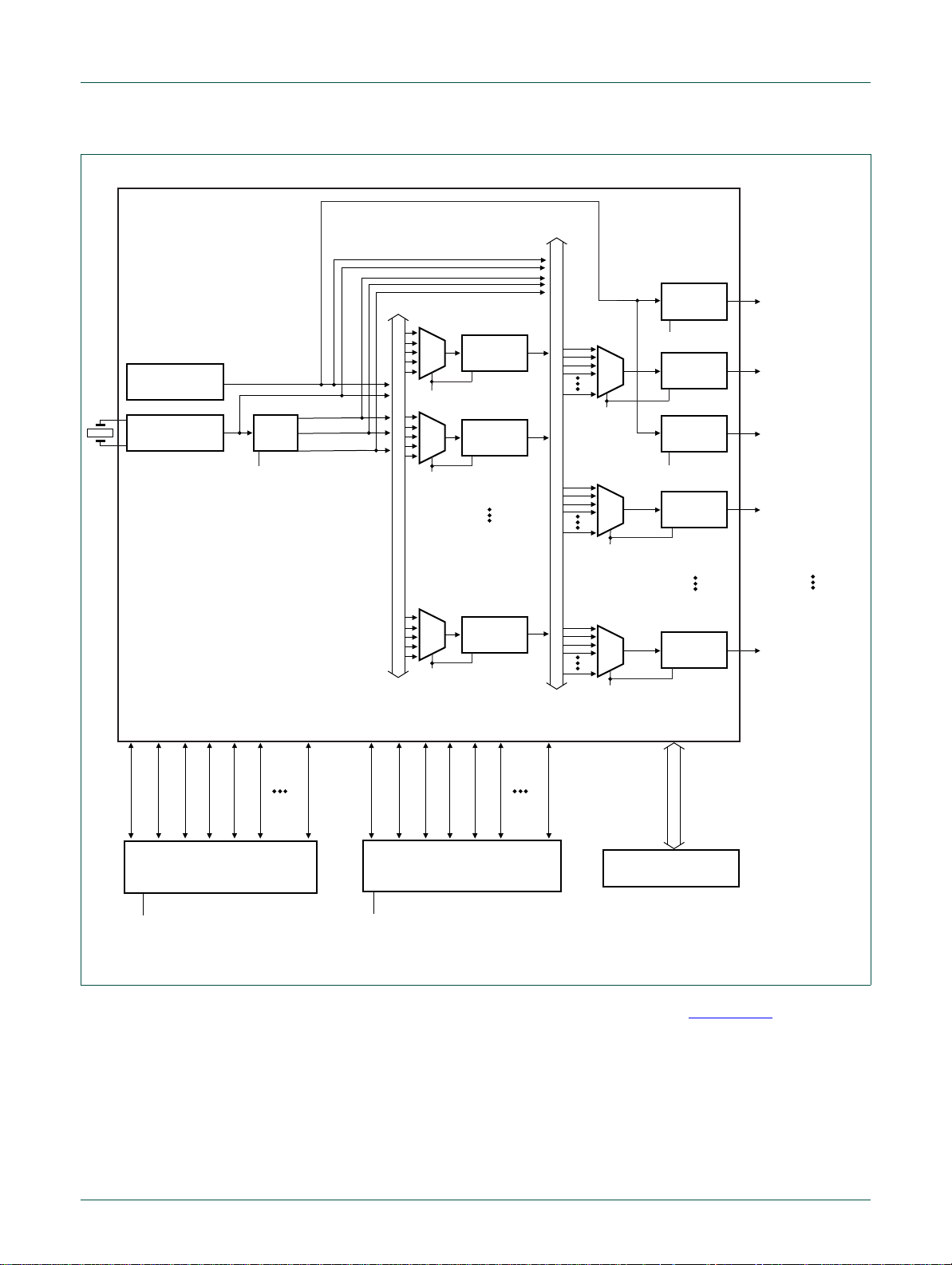

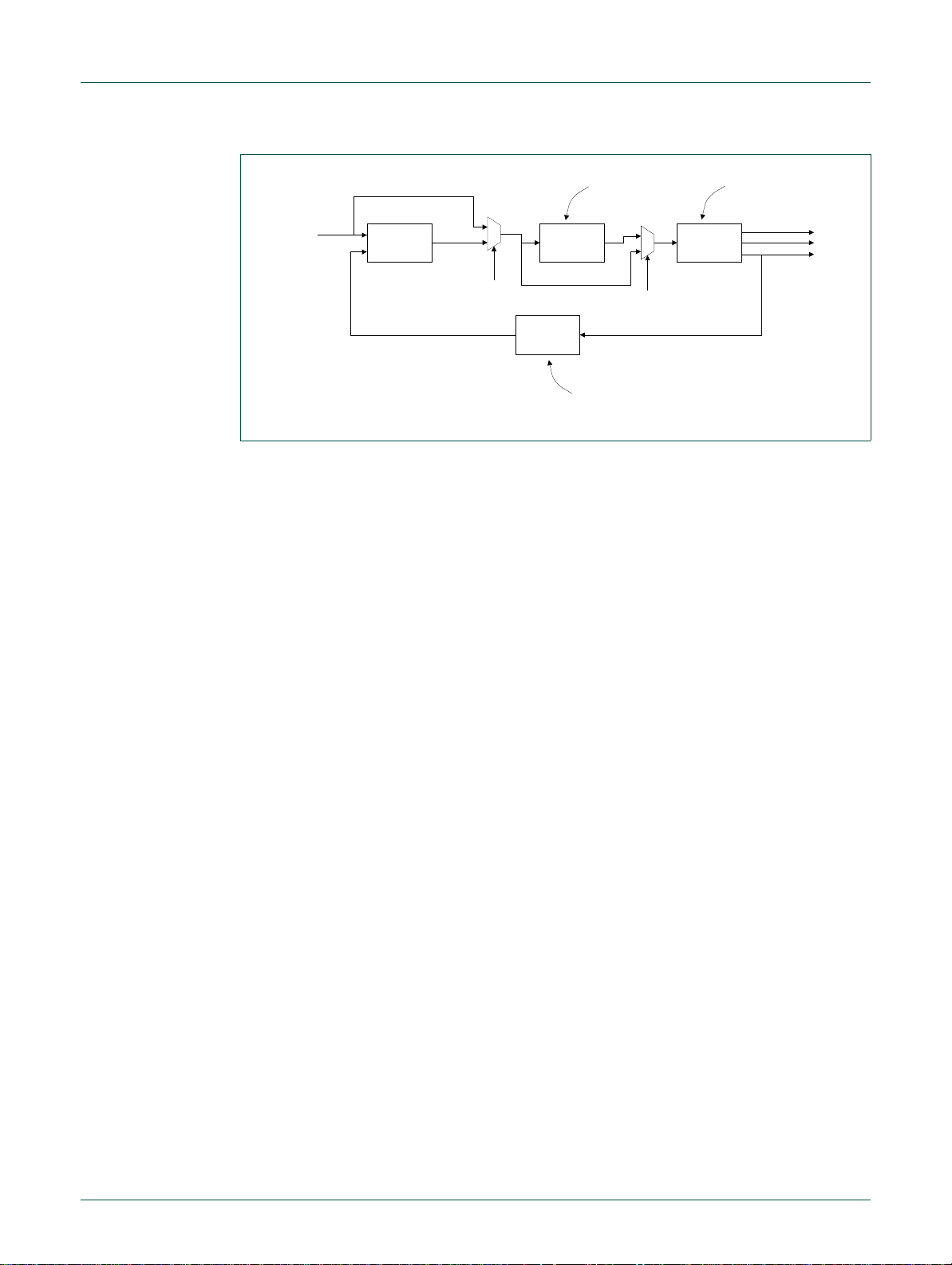

Fig 10. Schematic representation of the CGU0

The structure of the clock path of each clock output is shown in Figure 3–11.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 27 of 568

Page 28

NXP Semiconductors

OSC1M

XO50M

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

FDIV0..6

PLL160M

clkout /

clkout120 /

clkout240

Output

Control

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Clock

outputs

Fig 11. Structure of the clock generation scheme

3.1 Controlling the XO50M oscillator (external oscillator)

The XO50M oscillator can be disabled using the ENABLE field in the oscillator control

register. Even when enabled, this can be bypassed using the BYPASS field in the same

register. In this case the input of the OSC1M crystal is fed directly to the output.

The XO50M oscillator has an HF pin which selects the operating mode. For operation at

higher frequencies (15-25 MHz), the XO50M oscillator HF must be enabled. For

frequencies below that the pin must be disabl ed. Setting of the pin is contr olled b y th e HF

in the oscillator control register.

3.2 Controlling the PL160M PLL

The structure of the PLL clock path is shown in Figure 3–12.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 28 of 568

Page 29

NXP Semiconductors

P23CCO

/ MDIV

clkout120 /

clkout240

/ 2PDIV

MSEL

PSEL

P23EN

Input clock

Bypass

Direct

clkout

Fig 12. PLI60MPLL control mechanisms

The PLL reference input clock is provided by the external oscillator (XO50M). The PLLs

accept an input clock frequency in the range of 10 MHz to 25 MHz only. The input

frequency can be directly routed to the post-divider using the BYPASS control. The

post-divider can be bypassed using the DIRECT control.

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

The post-divider is controlled by settings of the field PSEL in the output control register.

PSEL is a 2-bit value that selects a division between 1 and 8 in powers of 2.

The feedback divider is controlled by settings of the MSEL field in the output control

register. The MSEL is a 5 -bit value corresponding to the feedback d ivider minus 1. Thus, if

MSEL is programmed to 0 the feedback divider is 1.

In normal mode the post-divider is enabled and the following relations are verified:

F

clkout

= MDIV × F

clkin

= F

/ 2×PDIV

cco

Values of the dividers are chosen with the following process:

1. Specify the input clock frequency F

2. Calculate M to obtain the desired output frequency F

3. Find a value for P so that F

cco

clkin

= 2×P / F

clkout

with M = F

clkout

clkout

/ F

clkin

4. Verify that all frequencies and divider values conform to the limits

In direct mode, the following relations are verified:

F

clkout

= M × F

clkin

= F

cco

Unless the PLL is configured in bypass mode it must be locked before using it as a clock

source. The PLL lock indication is read from the PLL status register.

Once the output clock is generated it is possible to use a three-phase ou tput control which

generates three clock signals separated in phase by 120°. This setting is controlled by

field P23EN.

Settings to power down the PLL, controlled by field PD in the PLL control registe r, and

safe switch setting controlled by the AUTOBLOK field are not shown in the illustration.

Note that safe switching of the clock is not enabled at reset.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 29 of 568

Page 30

NXP Semiconductors

3.3 Controlling the frequency dividers

The seven frequency dividers are controlled by the FDIV0..6 registers.

The frequency divider divides the incoming clock by (L/D), where L and D are both 12-bit

values, and attempts to produce a 50% duty-cycle. Each high or low phase is stretch ed to

last approximately D/(L*2) input-clock cycles. When D/(L*2) is an integer the duty cycle is

exactly 50%, otherwise it is an approximation.

The minimum division ratio is /2, so L should always be less than or equal to D/2. If not, or

if L is equal to 0, the input clock is passed directly to the output without being divided.

3.4 Controlling the clock output

Once a source is selected for one of the clock branches the output clock can be further

sub-divided using an output divider controlled by field IDIV in the clock-output

configuration register.

Each clock-branch output can be individually controlled to power it down and perform safe

switching between clock domains. These settings are controlled by the PD and

AUTOBLOK fields respectively.

DRAFT

Chapter 3: LPC29xx Clock Generation Unit (CGU)

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

UM10316

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

The clock output can trigger disabling of the clock branch on a specific polarity of the

output. This is controlled via field RTX of the output-configuration register.

3.5 Reading the control settings

Each of the control registers is associated with a status register. These registers can be

used to read the configured controls of each of the CGU building blocks.

3.6 Frequency monitor

The CGU includes a frequency-monitor mechanism which measures the clock pulses of

one of the possible clock sources against the reference clock. The reference clock is the

PCR block clock CLK_PCR.

When a frequency-monitor measurement begins two counters are started. The first starts

from the specified number of reference-clock cycles (set in field RCNT) and counts down

to 0: the second counts cycles of the monitored frequency starting from 0. The

measurement is triggered by enabling it in field MEAS and stops either when the

reference clock counter reaches 0 or the measured clock counter (in field FCNT)

saturates.

The rate of the measured clock can be calculated using the formula:

Fmeas = Fcore × FCNTfinal / (RCNTinitial - RCNTfinal)

When the measurement is finished either FCNTfinal is equal to the saturated value of the

counter (FCNT is a 14-bit value) or RCNTfinal is zero.

Measurement accuracy is influenced by the ratio between the clocks. For greater

accuracy the frequency to measure should be closer to the reference clock.

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 30 of 568

Page 31

NXP Semiconductors

Configure XO50MOSC

in normal mode with

HF pin enabled

Configure PLL to use

XO50MOSC as input

and generate 80MHz

(Fin = 10 MHz

and Fcco = 160 MHz)

with 3-phase output

enabled

Wait for PLL to lock

Configure FR clock

to 40 MHz

Configure FDIV5 to use

120° PLL output and

generate ~3.6866 MHz

Configure UART_CLK

to use FDIV5 and

divide by 2

3.7 Clock detection

All of the clock sources have a clock detector, the status of which can be read in a CGU

register. This register indicates which sources have been detected.

If this is enabled, the absence of any clock source can trigger a hardware interrupt.

3.8 Bus disable

This safety feature is provided to avoid accidental changing of the clock settings. If it is

enabled, access to all registers except the RBUS register (so that it can be disabled) is

disabled and the clock settings cannot be mod ifie d.

3.9 Clock-path programming

The following flowchart shows the sequence for programing a complete clock path:

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Fig 13. Programming the clock path

4. CGU1 functional description

The CGU1 block is functionally identical to the CGU0 block and generates two clocks for

the USB interface and a dedicated output clock. The CGU1 block uses its own PLL and

fractional dividers. The PLLs used in CGU0 and CGU1 are identical.

The clock input to the CGU1 PLL is provided by one of two base clocks generated in the

CGU0: BASE_ICLK0_CLK or BASE_INT1CLK. The base clock not used for the PLL can

be configured to drive the output clock directly.

The CGU1 provides the following three base clocks (Table 3–13

Table 13. CGU1 base clocks

Base clock Parts of the device clocked by this branch clock

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 31 of 568

BASE_OUT_CLK clock out pin

BASE_USB_CLK USB clock

BASE_USB_I2C_CLK USB OTG I2C clock

):

Page 32

NXP Semiconductors

PLL

FDIV0

OUT 0

OUT 2

clkout

clkout120

clkout240

CLOCK GENERATION UNIT

(CGU1)

AHB TO DTL BRIDGE

BASE_USB_CLK

BASE_OUT_CLK

OUT 1

BASE_USB_I2C_CLK

BASE_ICLK1_CLK

BASE_ICLK0_CLK

FDIV_CONF0

PLL_CONTROL

USB_CLK_CONF

USB_I2C_CLK_CONF

OUT_CLK_CONF

FREQUENCY MONITOR

CLOCK DETECTION

BASE_ICLK0_CLK

BASE_ICLK1_CLK

BASE_ICLK0_CLK

BASE_ICLK1_CLK

PLL clkout

PLL clkout120

PLL clkout240

FDIV0

PLL clkout

PLL clkout120

PLL clkout240

FDIV0

FREQ_MON

RDET

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

5. Register overview

Table 14. Register overview: CGU0 (CGU0 base address: 0xFFFF 8000)

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 32 of 568

Fig 14. Block diagram of the CGU1

Name Access Address

Remark: Any clock-frequency adjustment has a direc t impact on the timing of on- bo ar d

peripherals such as the UARTs, SPI, Watchdog, timers, CAN controller, LIN master

controller, ADCs, and flash memory interface.

Description Reset value Reference

offset

- R 0x000 Reserved 0x7100 0011 -

- R 0x004 Reserved 0x0000 0000 -

- R 0x008 Reserved 0x0C00 0000 -

- R 0x00C Reserved - FREQ_MON R/W 0x014 Frequency monitor register 0x0000 0000 see Table 3–16

RDET R 0x018 Clock detection register 0x0000 0FE3 see Table 3–17

Page 33

D

RAFT

UM10316

NXP Semiconductors

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

Table 14. Register overview: CGU0 (CGU0 base address: 0xFFFF 8000) …continued

Name Access Address

offset

XTAL_OSC_STATUS R 0x01C Crystal-oscillator status register 0x0000 0001 see Table 3–18

XTAL_OSC_CONTROL R/W 0x020 Crystal-oscillator control register 0x0000 0005 see Table 3–19

PLL_STATUS R 0x024 PLL status register 0x0005 1103 see Table 3–20

PLL_CONTROL R/W 0x028 PLL control register 0x0005 1103 see Table 3–21

FDIV_STATUS_0 R 0x02C FDIV 0 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_0 R/W 0x030 FDIV 0 frequency-divider control register 0x0000 1001 see Table 3–23

FDIV_STATUS_1 R 0x034 FDIV 1 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_1 R/W 0x038 FDIV 1 frequency-divider control register 0x0000 1001 see Table 3–23

FDIV_STATUS_2 R 0x03C FDIV 2 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_2 R/W 0x040 FDIV 2 frequency-divider control register 0x0000 1001 see Table 3–23

FDIV_STATUS_3 R 0x044 FDIV 3 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_3 R/W 0x048 FDIV 3 frequency-divider control register 0x0000 1001 see Table 3–23

FDIV_STATUS_4 R 0x04C FDIV 4 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_4 R/W 0x050 FDIV 4 frequency-divider control register 0x0000 1001 see Table 3–23

FDIV_STATUS_5 R 0x054 FDIV 5 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_5 R/W 0x058 FDIV 5 frequency-divider control register 0x0000 1001 see Table 3–23

FDIV_STATUS_6 R 0x05C FDIV 6 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_6 R/W 0x060 FDIV 6 frequency-divider control register 0x0000 1001 see Table 3–23

SAFE_CLK_STATUS R 0x064 Output-clock status register for

SAFE_CLK_CONF R/W 0x068 Output-clock configuration register for

SYS_CLK_STATUS R 0x06C Output-clock status register for

SYS_CLK_CONF R/W 0x070 Output-clock configuration register for

PCR_CLK_STATUS R 0x074 Output-clock status register for

PCR_CLK_CONF R/W 0x078 Output-clock configuration register for

IVNSS_CLK_STATUS R 0x07C Output-clock status register for

IVNSS_CLK_CONF R/W 0x080 Output-clock configuration register for

MSCSS_CLK_STATUS R 0x084 Output-clock status register for

MSCSS_CLK_CONF R/W 0x088 Output-clock configuration register for

ICLK0_CLK_CONF R/W 0x08C Output-clock configuration register for

ICLK1_CLK_STATUS R 0x090 Output-clock status register for

UART_CLK_STATUS R 0x094 Output-clock status register for

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 33 of 568

Description Reset value Reference

0x0000 0000 see Table 3–24

BASE_SAFE_CLK

0x0000 0000 see Table 3–25

BASE_SAFE_CLK

0x0000 0000 see Table 3–26

BASE_SYS_CLK

0x0000 0000 see Table 3–27

BASE_SYS_CLK

0x0000 0000 see Table 3–26

BASE_PCR_CLK

0x0000 0000 see Table 3–27

BASE_PCR_CLK

0x0000 0000 see Table 3–26

BASE_IVNSS_CLK

0x0000 0000 see Table 3–27

BASE_IVNSS_CLK

0x0000 0000 see Table 3–26

BASE_MSCSS_CLK

0x0000 0000 see Table 3–27

BASE_MSCSS_CLK

0x0000 0000 see Table 3–26

BASE_ICLK0_CLK

0x0000 0000 see Table 3–27

BASE_ICLK0_CLK

0x0000 0000 see Table 3–26

BASE_UART_CLK

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Page 34

DR

AFT

DRAFT

NXP Semiconductors

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

Table 14. Register overview: CGU0 (CGU0 base address: 0xFFFF 8000)

Name Access Address

offset

UART_CLK_CONF R/W 0x098 Output-clock configuration register for

SPI_CLK_STATUS R 0x09C Output-clock status register for

SPI_CLK_CONF R/W 0x0A0 Output-clock configuration register for

TMR_CLK_STATUS R 0x0A4 Output-clock status register for

TMR_CLK_CONF R/W 0x0A8 Output-clock configuration register for

ADC_CLK_STATUS R 0x0AC Output-clock status register for

ADC_CLK_CONF R/W 0x0B0 Output-clock configuration register for

- R 0x0B4 reserved 0x0000 0000 -

- R/W 0x0B8 reserved 0x0000 0000 ICLK1_CLK_STATUS R 0x0BC Output-clock status register for

ICLK1_CLK_CONF R/W 0x0C0 Output-clock configuration register for

INT_CLR_ENABLE W 0xFD8 Interrupt clear-enable register 0x0000 0000 see

INT_SET_ENABLE W 0xFDC Interrupt set-enable register 0x0000 0000 see

INT_STATUS R 0xFE0 Interrupt status register 0x0000 0FE3 see

INT_ENABLE R 0xFE4 interrupt enable register 0x0000 0000 see

INT_CLR_STATUS W 0xFE8 Interrupt clear-status register 0x0000 0000 see

INT_SET_STATUS W 0xFEC Interrupt set-status register 0x0000 0000 see

- R 0xFF0 Reserved - BUS_DISABLE R/W 0xFF4 Bus disable register 0x0000 0000 see Table 3–30

- R 0xFF8 Reserved - -

- R 0xFFC Reserved 0xA0A8 1000 -

Description Reset value Reference

BASE_UART_CLK

BASE_SPI_CLK

BASE_SPI_CLK

BASE_TMR_CLK

BASE_TMR_CLK

BASE_ADC_CLK

BASE_ADC_CLK

BASE_ICLK1_CLK

BASE_ICLK1_CLK

…continued

0x0000 0000 see Table 3–27

0x0000 0000 see Table 3–26

0x0000 0000 see Table 3–27

0x0000 0000 see Table 3–26

0x0000 0000 see Table 3–27

0x0000 0000 see Table 3–26

0x0000 0000 see Table 3–27

0x0000 0000 see Table 3–26

0x0000 0000 see Table 3–27

Table 10–91

Table 10–92

Table 10–93

Table 10–94

Table 10–95

Table 10–96

DRAFT

DRA

F

DR

AFT

DR

T DRAF

Table 15. Register overview: CGU1 (CGU1 base address: 0xFFFF B000)

Name Access Address

reserved R 0x000 Reserved 0x7100 0011 reserved R 0x004 Reserved 0x0000 0000 reserved R 0x008 Reserved 0x0C00 0000 reserved R 0x00C Reserved - FREQ_MON R/W 0x014 Frequency monitor register 0x0000 0000 see Table 3–16

UM10316_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 01.01 — 14 July 2009 34 of 568

Description Reset value Reference

offset

Page 35

DR

fselected

Qselected

Qref initial[]Qref final[]–()

------------------------------------------------------------------------- -

fref×=

AFT

DRAFT

NXP Semiconductors

DRAFT

D

D

RAFT DRAFT DRAFT DRAFT DRAFT D

RAFT DRA

D

RAFT

UM10316

Chapter 3: LPC29xx Clock Generation Unit (CGU)

F

T DRAFT DRAFT DRAFT DRA

Table 15. Register overview: CGU1 (CGU1 base address: 0xFFFF B000) …continue d

Name Access Address

offset

RDET R 0x018 Clock detection register 0x0000 0FE3 see Table 3–17

PLL_STATUS R 0x01C PLL status register 0x0005 1103 see Table 3–20

PLL_CONTROL R/W 0x020 PLL control register 0x0005 1103 see Table 3–21

FDIV_STATUS_0 R 0x024 FDIV 0 frequency-divider status register 0x0000 1001 see Table 3–22

FDIV_CONF_0 R/W 0x028 FDIV 0 frequency-divider control register 0x0000 1001 see Table 3–23

USB_CLK_STATUS R 0x02C Output-clock status register for