Page 1

DRAFT

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

Rev. 01.02. — 8 November 2007 User manual

Document information

Info Content

Keywords LPC2917/19, User Manual, ARM9, CAN, LIN, Gateway

Abstract This document extends the LPC2917/19 data sheet with additional details

to support both hardware and software development. It focuses on

functional description and typical application use.

F

T DRAFT DRAFT DRAFT DRA

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Page 2

DRAFT

NXP Semiconductors

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

Revision history

Rev Date Description

01.02 20071108

Modifications: Removed part LPC2915

01.01 20071003

Modifications: • starting address of static memory bank address corrected, see Table 27.

• Use of RBLE-bit in SMBCRn-register updated, see Table 34.

• Register base address table updated, see Table 3.

01 20070913 Initial version

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

DRAFT

F

T DRAFT DRAFT DRAFT DRA

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Contact information

For additional information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 2 of 263

Page 3

NXP Semiconductors

1. Introduction

1.1 About this document

This document extends the LPC2917/19 data sheet Ref. 1 with additional details to

support both hardware and software development. It focuses on functional description,

register details and typical application use. It does not contain a detailed description or

specification of the hardware already covered by the data sheet Ref. 1

1.2 Intended audience

This document is written for engineers evaluating and/or developing hardware or sof tware

for the LPC2917/19. Some basic knowledge of ARM processors, ARM architecture and

ARM9TDMI-S in particular is assumed Ref. 2

1.3 Guide to the document

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

.

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

F

T DRAFT DRAFT DRAFT DRA

.

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

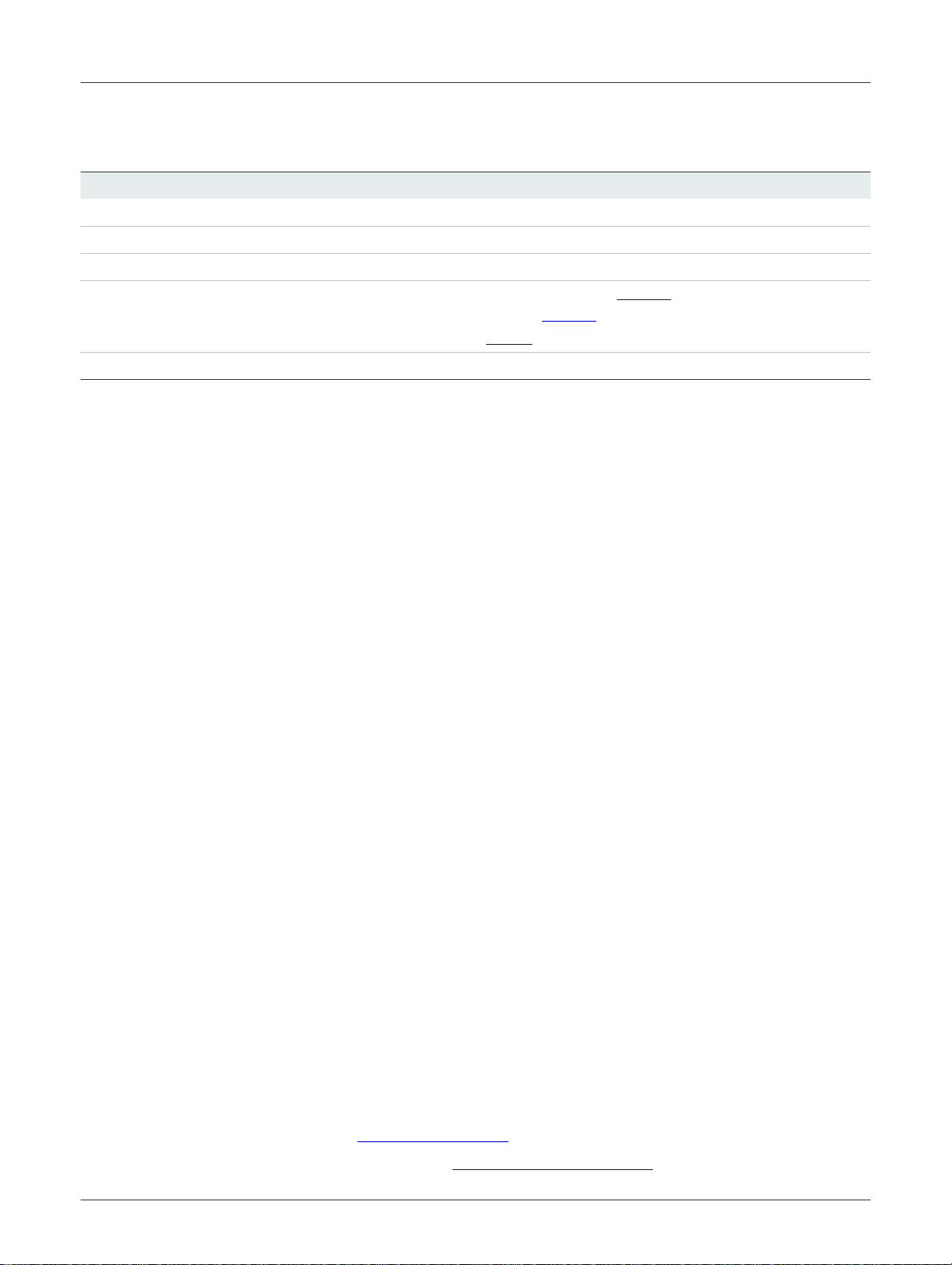

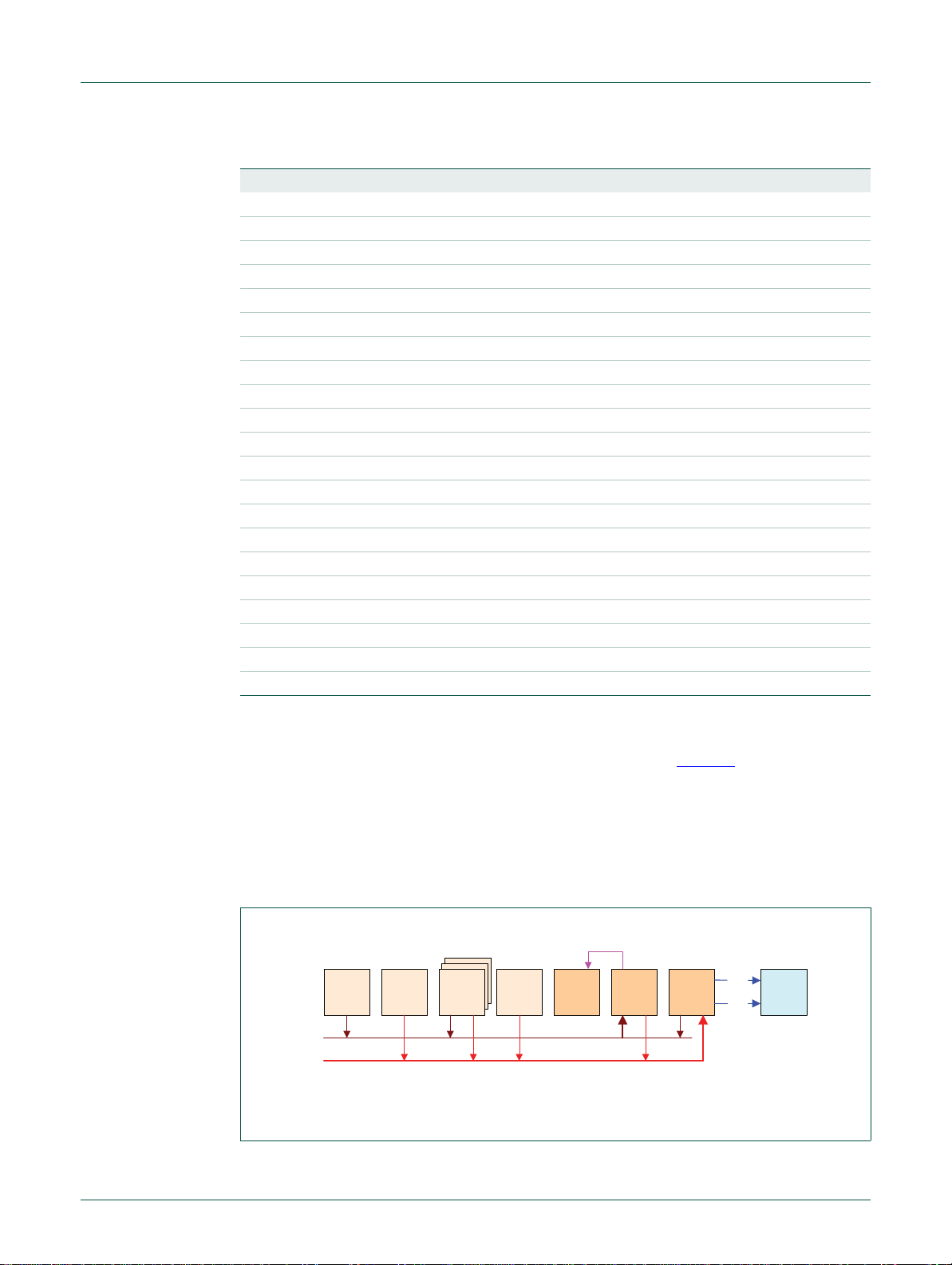

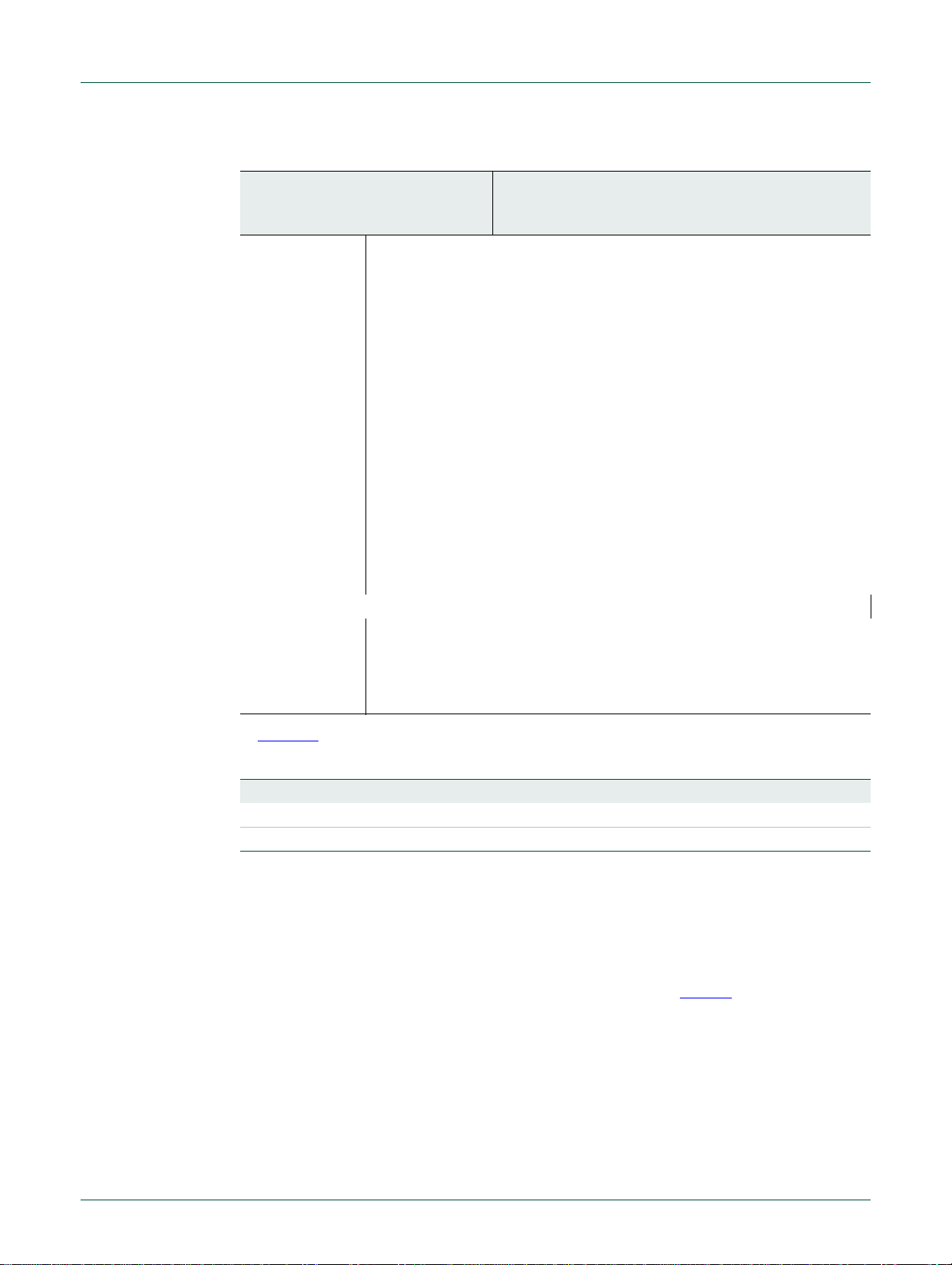

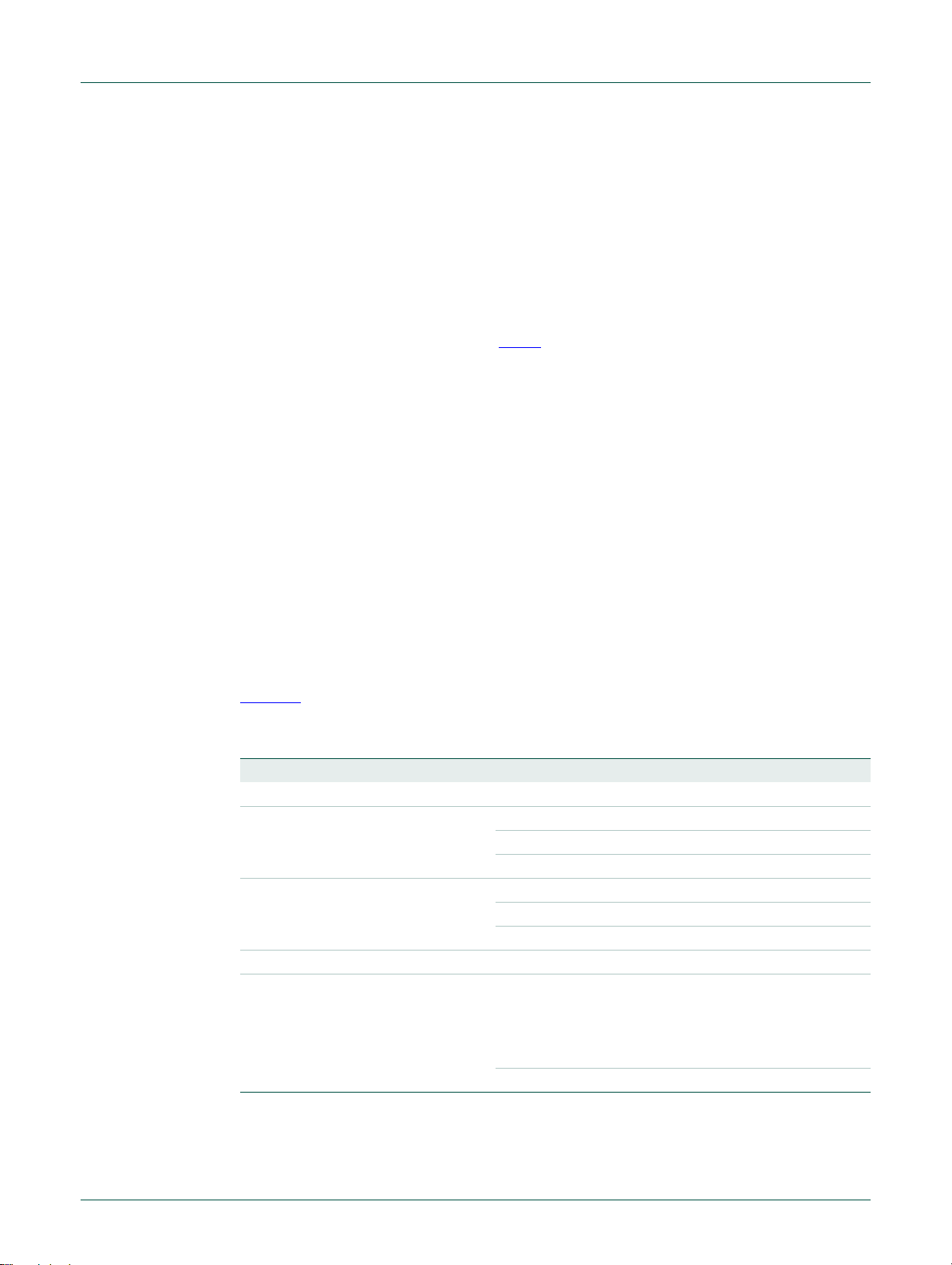

2. Overview

2.1 Functional blocks and clock domains

An overview of the functionality of the LPC2917/19 is given as well as a functional

description of the blocks and their typical usage. Register descriptions are given in the

appropriate sub-sections. The Datasheet Ref. 1

This chapter gives an overview of the functional blocks, clock domains, power modes an d

the interrupt and wake-up structure.

Figure 1 gives a simplified overview of the functional blocks. These blocks are explained

in detail in Section 3

gathered into subsystems and one or more of these blocks and/or subsystems are put into

a clock domain. Each of these clock domains can be configured individually for power

management (i.e. clock on or off and whether the clock responds to sleep and wake-up

events).

(with the exception of some trivial blocks). Several blocks are

should be used along with this document.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 3 of 263

Page 4

NXP Semiconductors

General Subsystem

Event Router (ER)

System Control Unit (SCU)

Chip Feature ID (CFID)

AHB2VPB

Bridge

s

IEEE 1149.1 JTAG TEST and

DEBUG INTERFACE

LPC2917/19

DTCM

16 Kb

ITCM

16 Kb

ARM968E-S

m

s

s

s

s

s

s

s

s

s

External Static Memory

Controller (SMC)

Embedded

SRAM Memory 32 Kb

SRAM Controller #0

Embedded

FLASH Memory

512 - 768 Kb

FLASH Memory Controller (FMC)

Embedded

SRAM Memory 16 Kb

SRAM Controller #1

GLOBAL ACCEPTANCE

FILTER

2 Kbyte Static RAM

LIN MASTER 0/1

CAN Controller

0, 1

Vectored Interrupt

Controller (VIC)

AHB2VPB

Bridge

AHB2DTL

Bridge

Modulation and Sampling

Control Subsystem

PWM 0, 1, 2, 3

ADC 1, 2

Timer 0, 1 (MTMR)

AHB2VPB

Bridge

Power Clock Reset

Control Subsystem

Power Management Unit (PMU)

Reset Generation Unit (RGU)

Clock Generation Unit (CGU)

AHB2DTL

Bridge

Peripheral Subsystem

General Purpose IO (GPIO)

0, 1, 2, 3

Timer (TMR)

0, 1, 2, 3

Watchdog Timer (WDT)

UART 0, 1

AHB2VPB

Bridge

TMR_CLK

SAFE_CLK

UART_CLK

SPI_CLK

PCR_CLK

IVNSS_CLK

ADC_CLK

MSCSS_CLK

SYS_CLK

SPI 0, 1, 2

s

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 4 of 263

Fig 1. LPC2917/19 clock distribution

Table 1 gives an overview of the clock domains and functional blocks, as used in Figure 1.

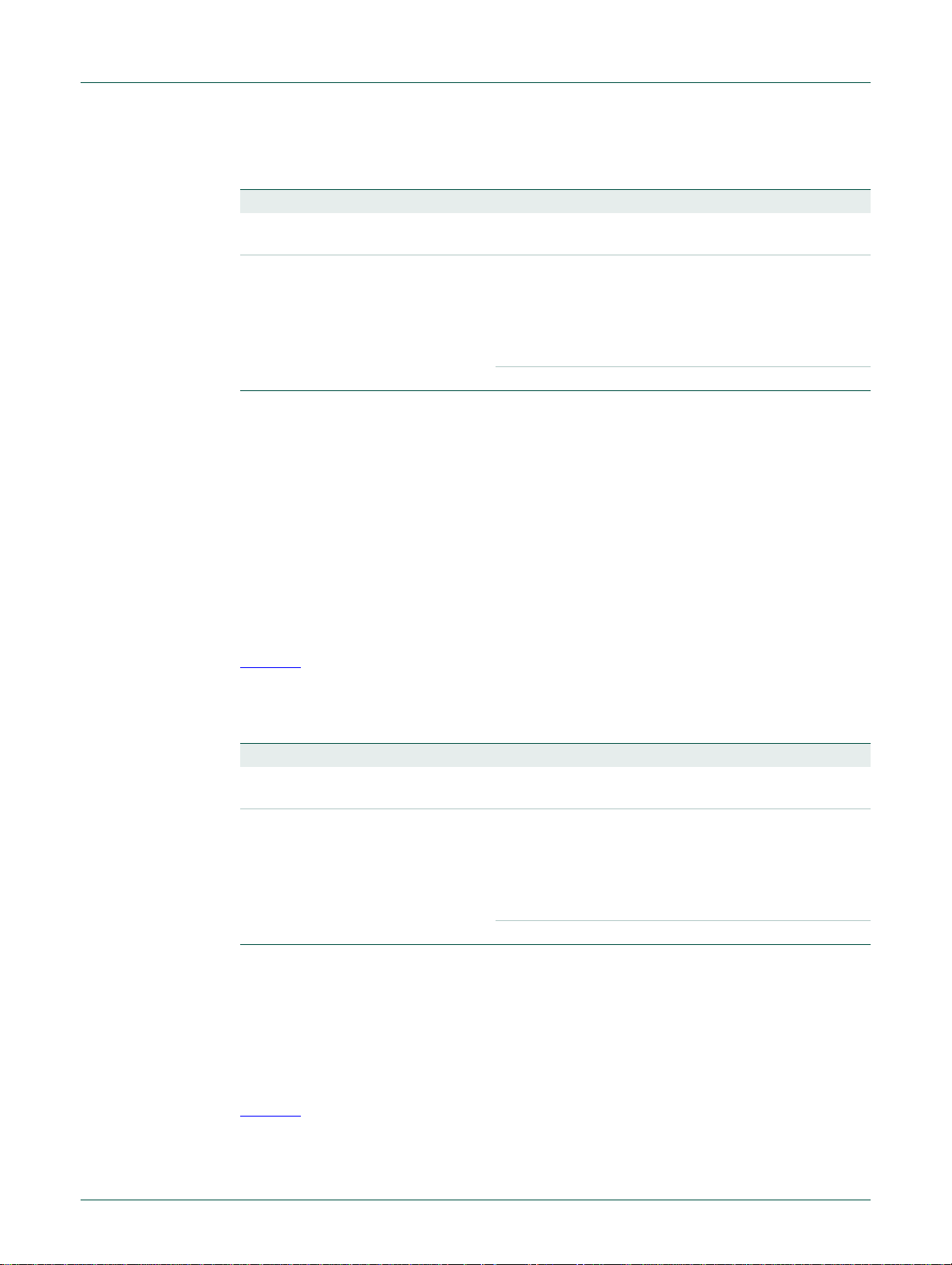

Table 1. Functional blocks and clock domains

Short Description Comment

Clock domain 0 - AHB

ARM ARM9TDMI-S 32-bit RISC processor

SMC Static Memory Controller For external (static) memory banks

SRAM Internal Static Memory Clock domain 1 – Flash

Flash - Internal Flash Memory

FMC Flash Memory Controller Controller for the internal flash memory

Clock domain 2 – General and Peripheral subsystems

General subsystem

CFID Digital In-vehicle Chip ID Identifies the device and its possibilities

Page 5

NXP Semiconductors

Table 1. Functional blocks and clock domains

Short Description Comment

CGU Clock Generation Unit Controls clock sources and clock

ER Event Router Routes wake-up events and external

RTC Real-Time Clock RTC with own power domain (e.g. for

SCU System Control Unit Configures memory map and I/O

SPI Serial Peripheral Interface Supports various industry-standard SPI

WD Watchdog Timer to guard (software) execution

Peripheral subsystem

GPIO General-Purpose

TMR Timer Provides match output and capture

UART Universal Asynchronous

VIC Vectored Interrupt Controller Prioritized/vectored interrupt handling

Modulation and sampling-control subsystem

ADC Analog-to-Digital Converter 10-bit Analog-to-Digital Converter

PWM Pulse-Width Modulator Synchronized Pulse-Width Modulator

TMR Timer Dedicated Sampling and Control Timer

Clock domain 3 – In-Vehicle Networking subsystem

Remark: There is also a fifth clock domain. This is used by the converter of the ADCs to determine

the conversion rate.

CAN Gateway Includes acceptance filter

LIN Master controller LIN master controller

- - Clock for the converter part of the ADC

DRAFT

Preliminary UM

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

LPC2917/19 - ARM9 microcontroller with CAN and LIN

F

T DRAFT DRAFT DRAFT DRA

…continued

domains

interrupts (to CGU/VIC)

battery)

functions

protocols

Directly controls I/O pins

Input/Output

inputs

Standard 550 serial port

Receiver/Transmitter

determining the conversion rate.

RAFT

DRAFT

DR

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 5 of 263

Page 6

NXP Semiconductors

Power Mode

“Normal”

Power Mode

“Idle”

Power Mode := “Idle”

(CGU.CPM register)

wake-up event

(from Event Router to CGU )

Reset

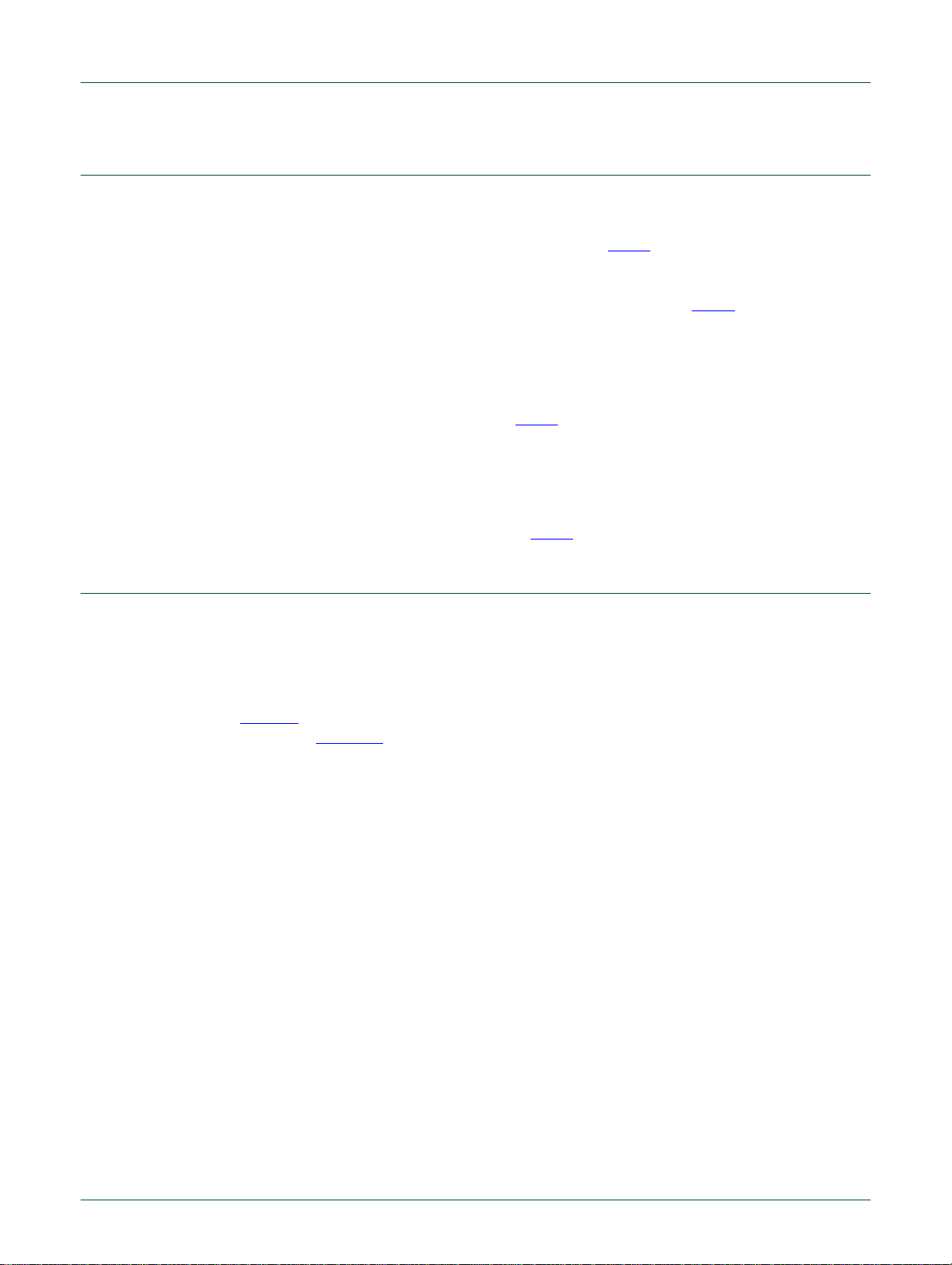

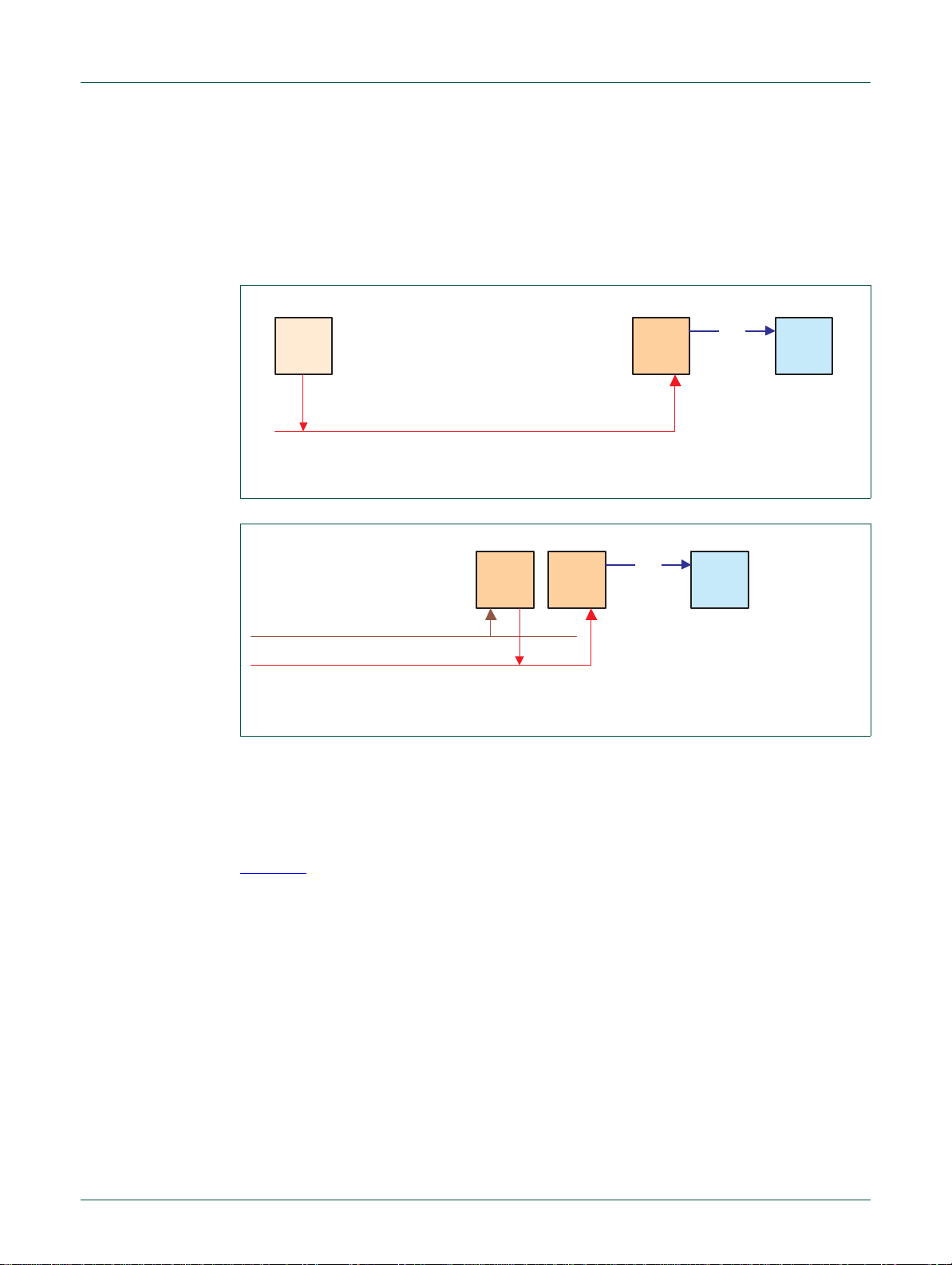

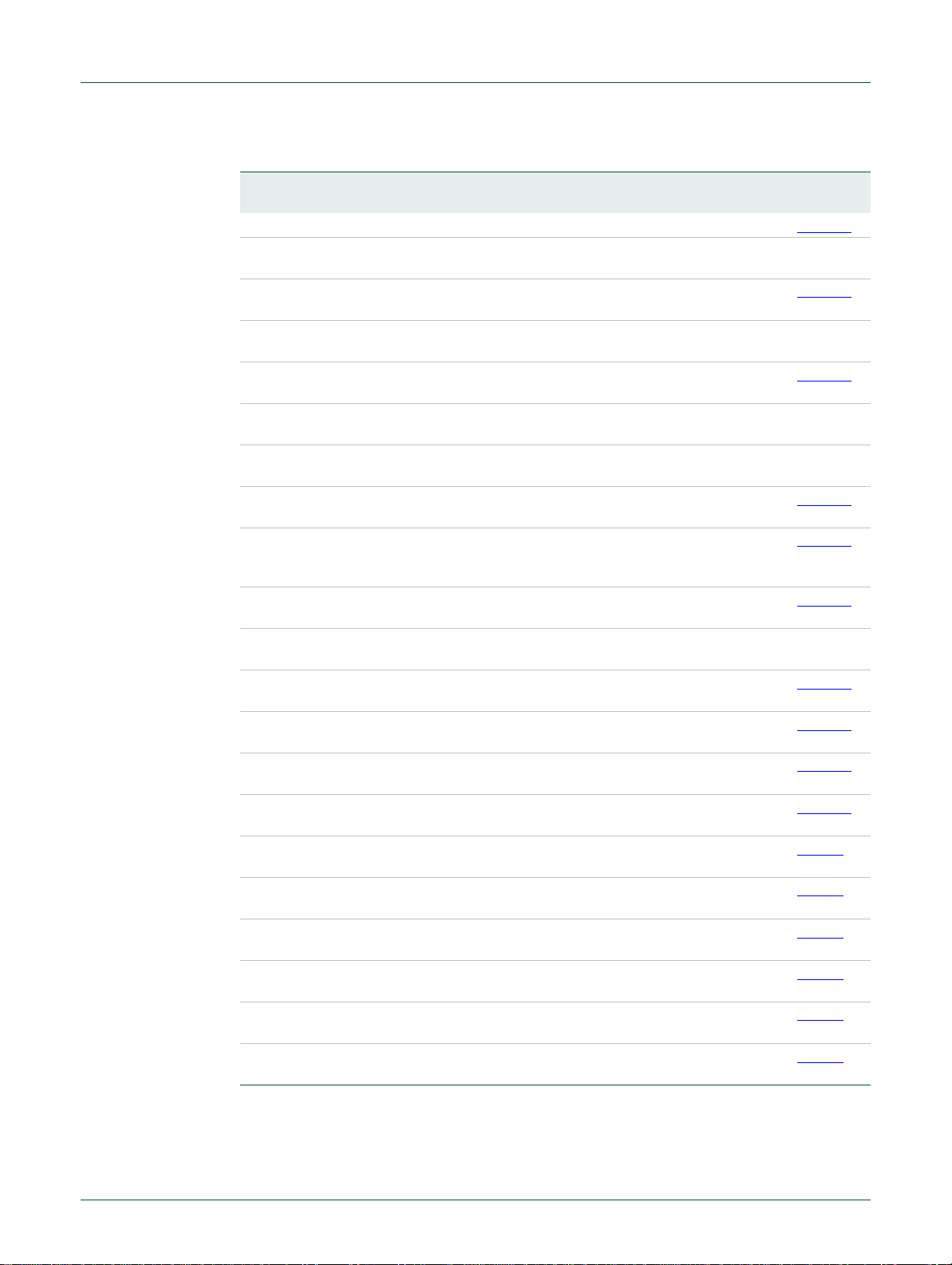

2.2 Power modes

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

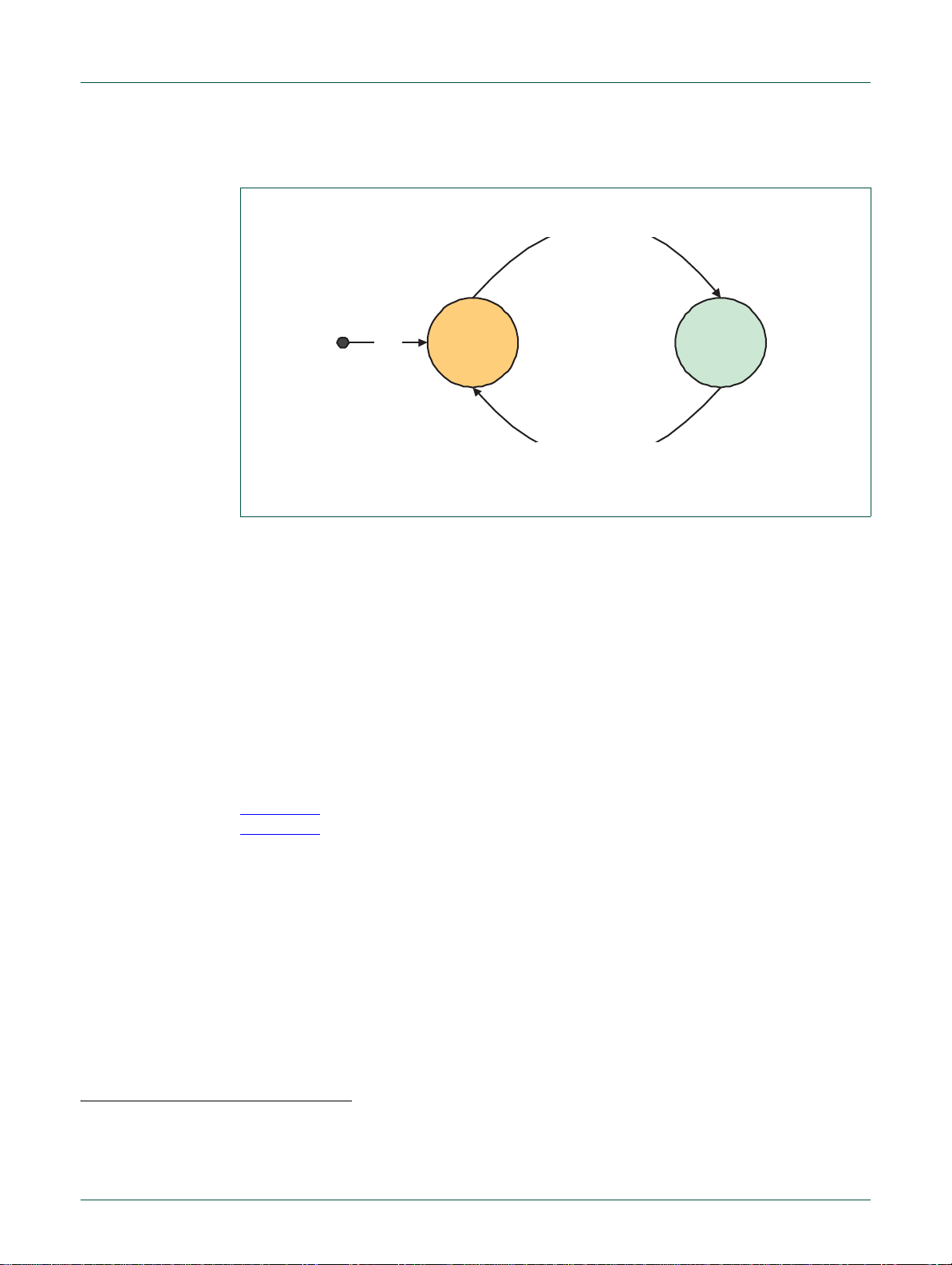

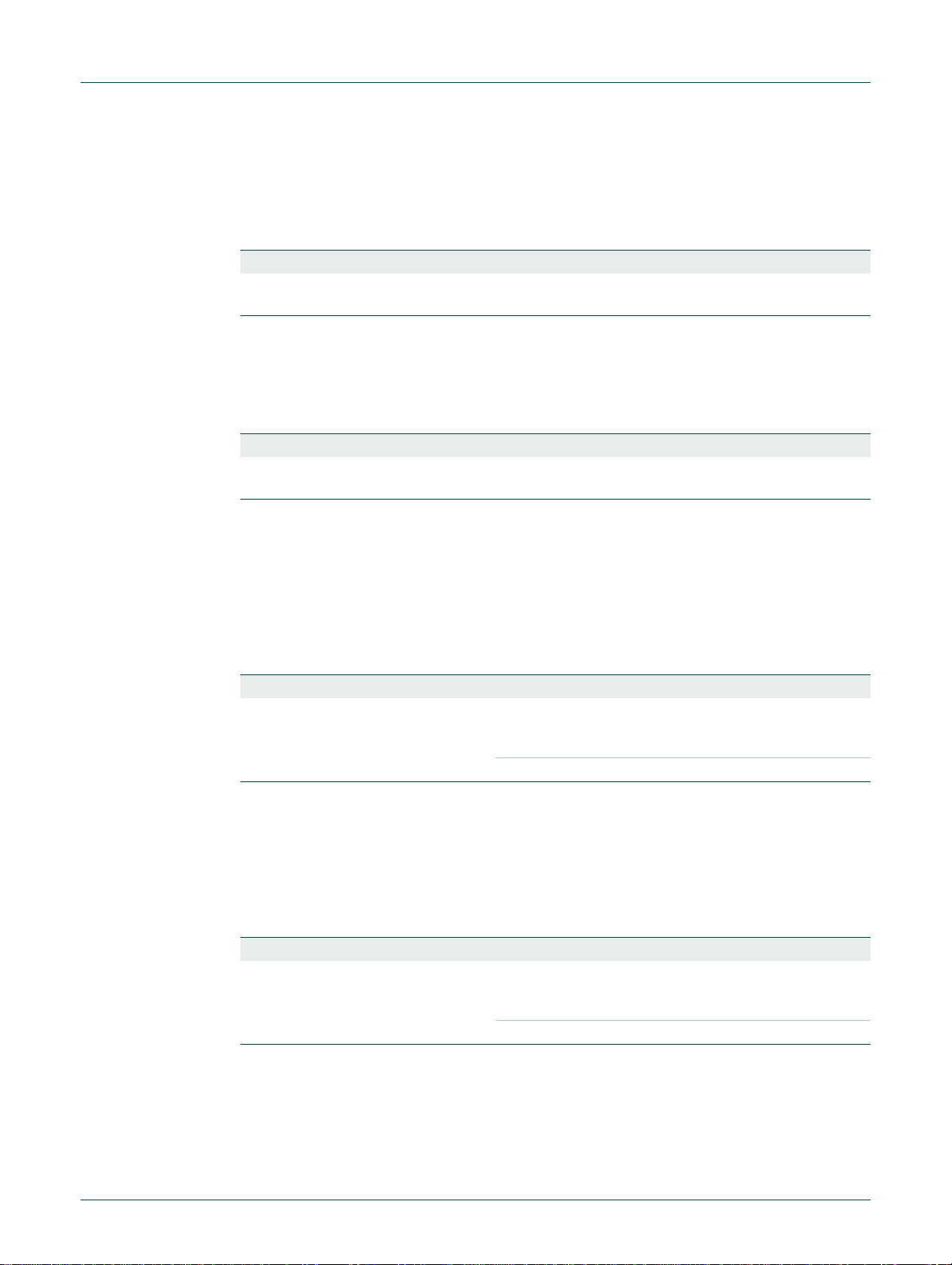

Fig 2. Power modes

The device operates in normal-power mode after reset. In this mode the device is fully

functional, i.e. all clock domains are available

1

. The system can be put into idle-power

mode either partially or fully. In this mode selected clock domains are switched off, and

this might also suspend execution of the software. The clock domains are enabled again

upon a wake-up event. This wake-up event is provided by the Event Router.

The clock domains that can be switched off during idle-power mode depend on the

selected wake-up events. For an external interrupt (e.g. EXTINT0) no active clock is

required, i.e. all clock domains can be switched off. However, for wake-up on a timer

interrupt the clock domain of the timer should stay enabled during low-power mode. In

general, each subsystem that might cause a wake-up upon an interrupt must be excluded

from the low power mode, i.e. the clock domain of the subsystem should stay enabled.

Setting the power mode and configuring the clock domains is handled by the CGU, see

Section 3.3

Section 3.6

. Configuration of wake-up events is handled by the Event Router, see

.

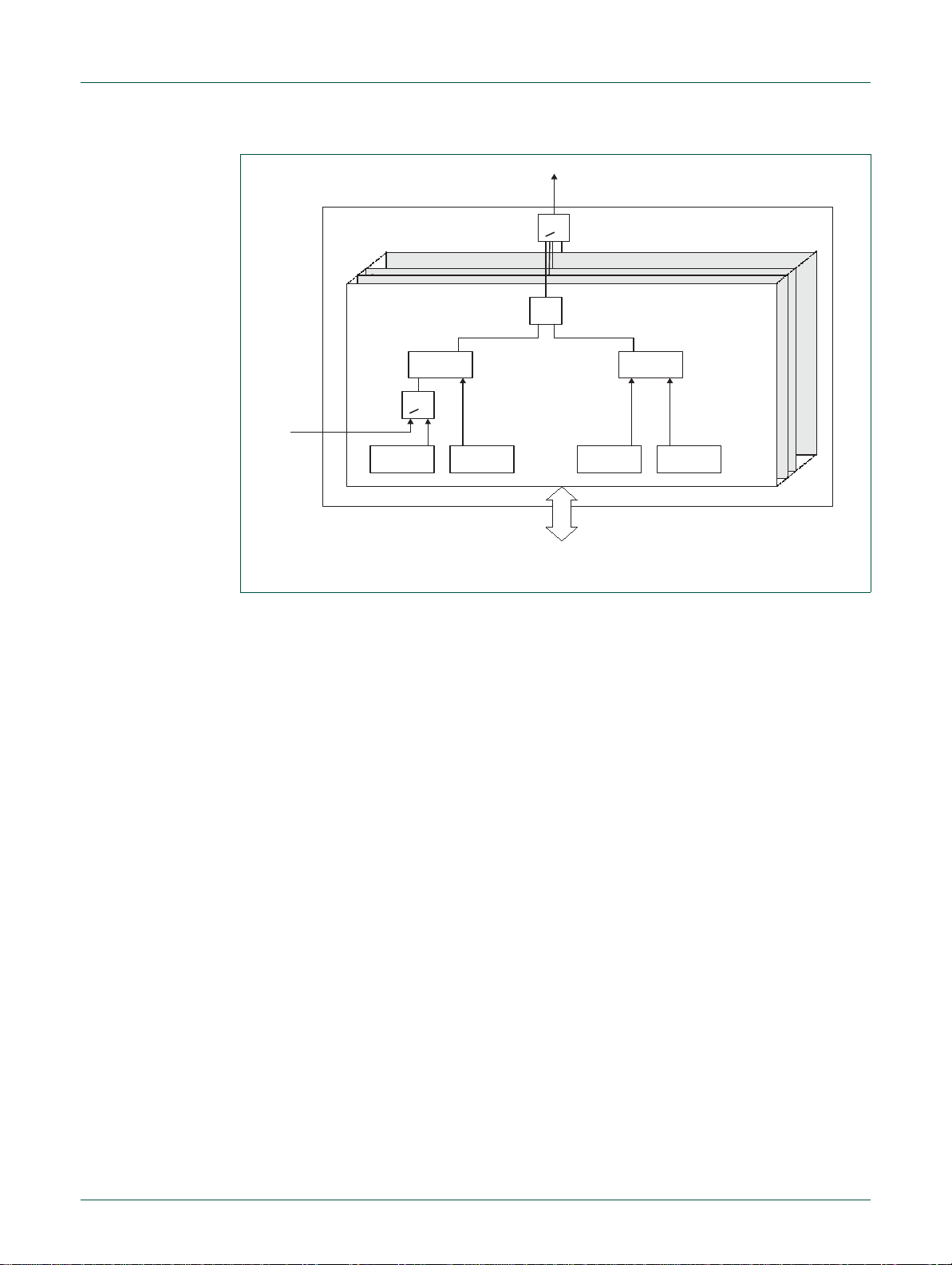

2.3 Memory map

2.3.1 Memory-map view of different AHB master layers

The LPC2917/19 has a multi-layer AHB bus structure with three layers. The different bus

masters in the LPC2917/19 (CPU, FRSS_A and FRSS_B) each have their own AHB-lite

system bus (layer). AHB slaves are hooked up to these AHB-lite busses. Not all slaves

are connected to all layers, so the individual AHB bus masters in the LPC2917/19 each

have their own view of the system memory map.

2

The ARM968E-S CPU has access to all AHB slaves and hence to all address regions.

1. Although all clock domains are available, not all the domains are enabled. E.g. the ADC clock domain is switched off by default

after reset.

2. The CAN and LIN controllers can issue a wake-up event via activity on the CAN or LIN bus. This feature does not require an active

clock for their subsystem; but the first message can be lost.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 6 of 263

Page 7

NXP Semiconductors

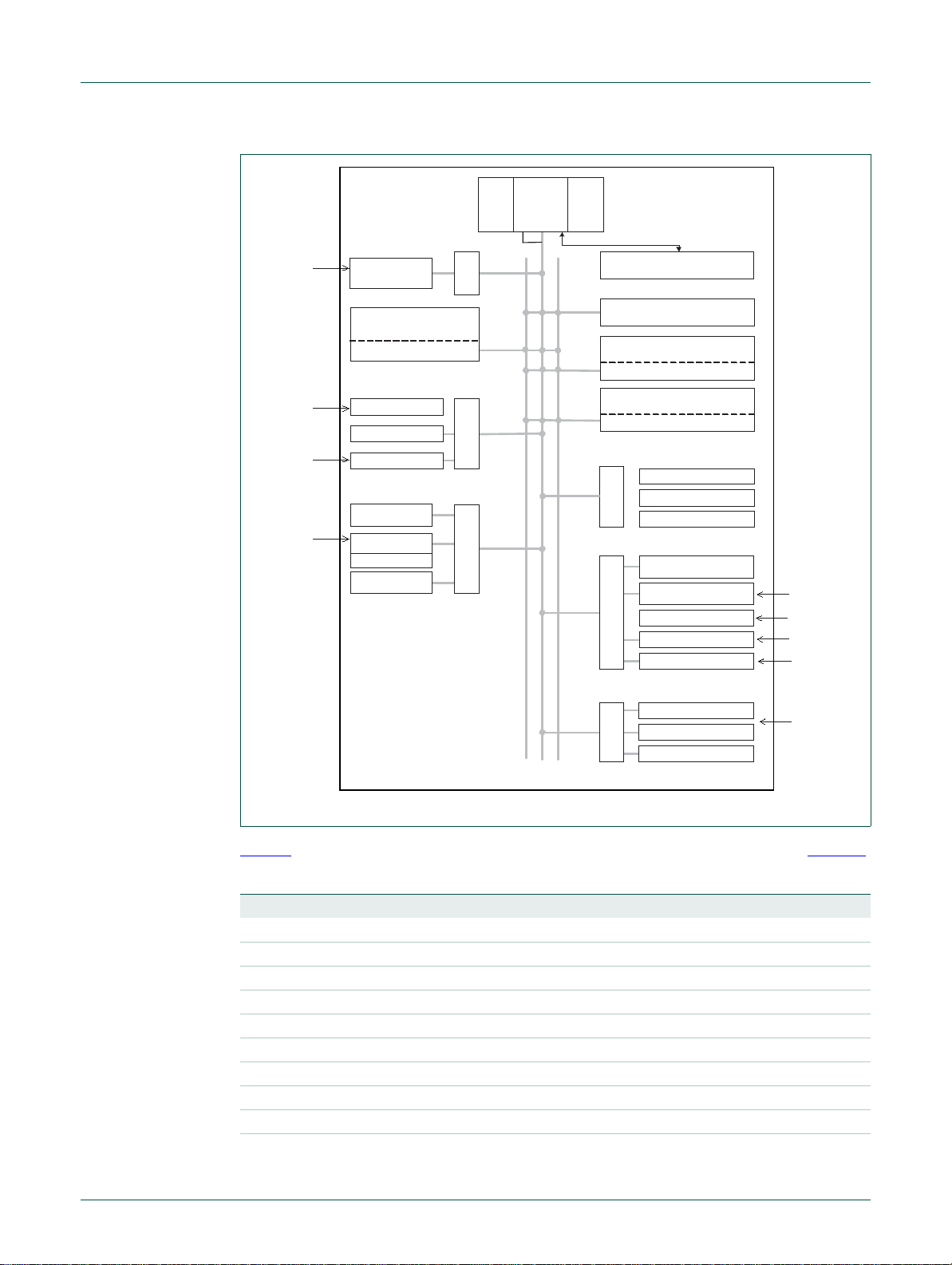

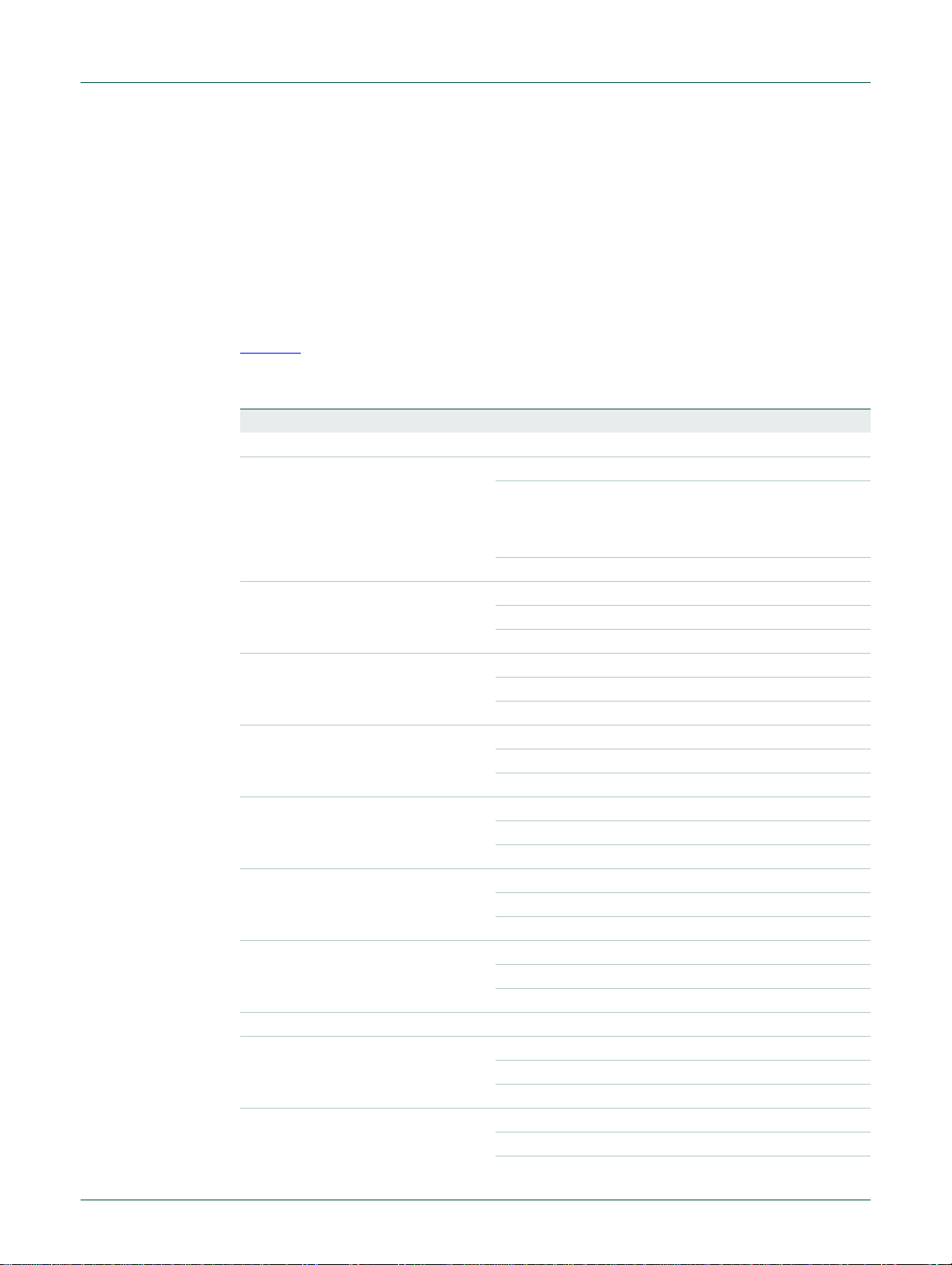

2.3.2 Memory-map regions

The ARM9 processor has a 4 GB of address space. The LPC2917/19 has divided this

memory space into eight regions of 512 MB each. Each region is used for a dedicated

purpose.

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

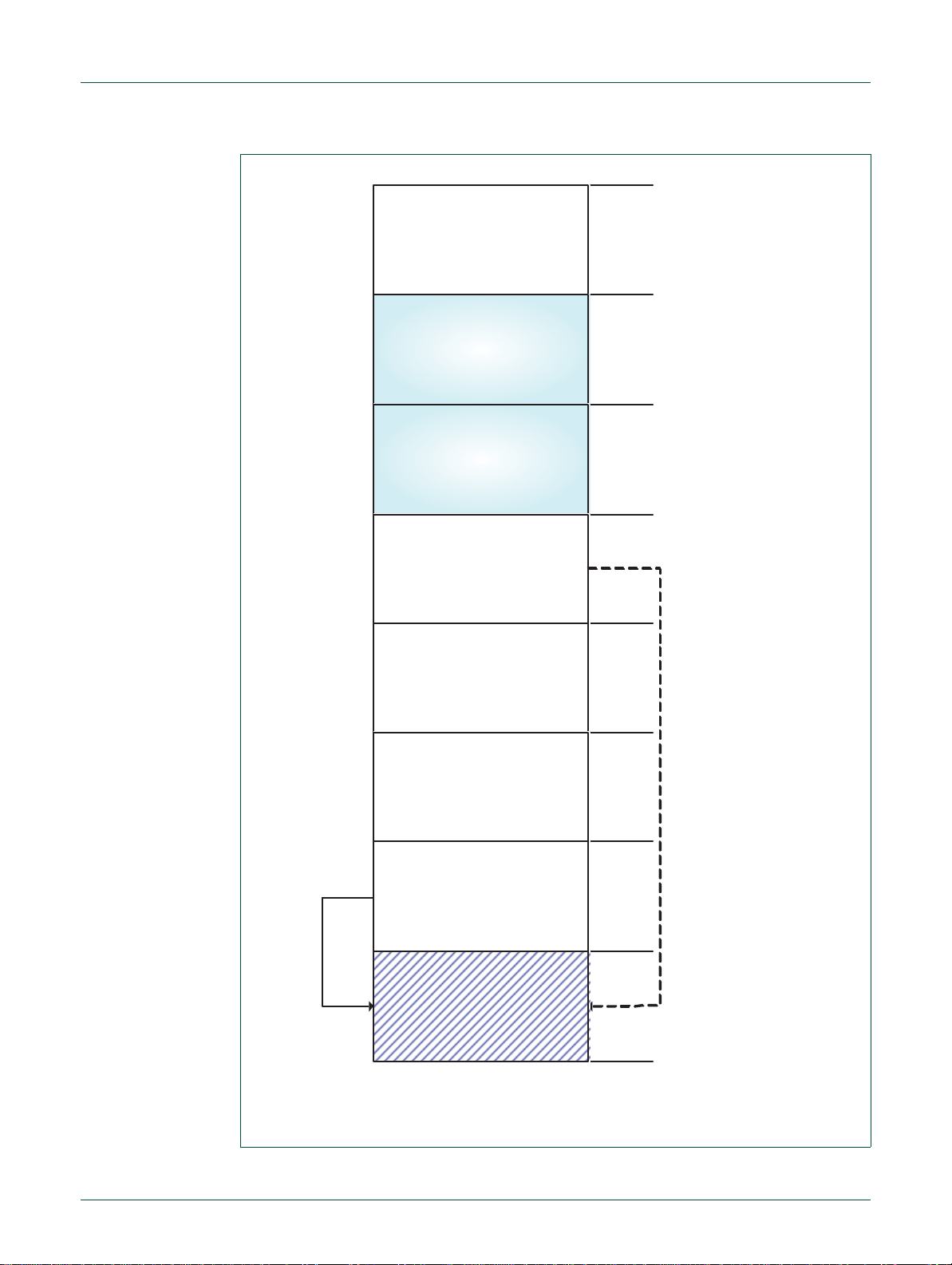

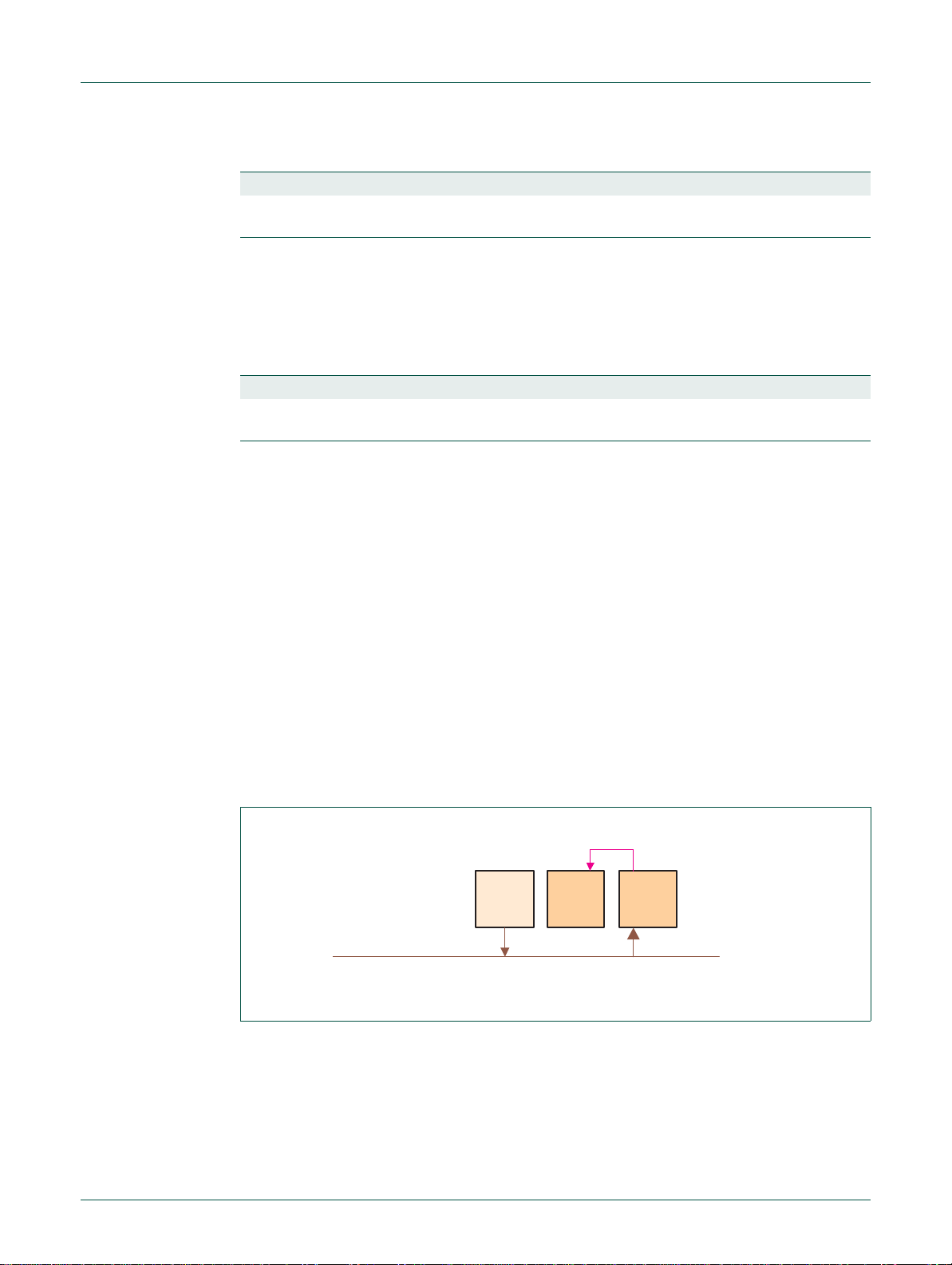

Figure 3

gives a graphical overview of the LPC2917/19 memory map.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 7 of 263

Page 8

NXP Semiconductors

DRAFT

Preliminary UM

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

LPC2917/19 - ARM9 microcontroller with CAN and LIN

F

T DRAFT DRAFT DRAFT DRA

0xFFFF_FFFF

Region #7 (512 Mbyte)

Bus Peripherals

0xE000_0000

Region #6 (512 Mbyte)

(reserved for future extensions)

0xC000_0000

Region #5 (512 Mbyte)

(reserved for future extensions)

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Embedded

flash

remapped

during

start-up

Region #4 (512 Mbyte)

embedded SRAM

Region #3 (512 Mbyte)

Static Memory Controller / External Bus Interface

(Configuration Area)

Region #2 (512 Mbyte)

Static Memory Controller / External Bus Interface

(Data Transfer Area)

Region #1 (512 Mbyte)

embedded FLASH

Region #0 (512 Mbyte)

Reserved for TCM

0xA000_0000

0x8000_0000

0x6000_0000

0x4000_0000

0x2000_0000

Programmable selection of remap

area via register in SCU

(example: embedded SRAM)

0x0000_0000

System Memory Map

(Memory Regions)

Fig 3. AHB system memory map: graphical overview

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 8 of 263

Page 9

NXP Semiconductors

Region #0: TCM area

0x0000_0000 - 0x1FFF_FFFF

(Offset Address)

0x0000_0000

0x1FFF_FFFF

0x0000_4000

0x0040_0000

I-TCM region aliasses

I-TCM (16 kByte)

0x0080_0000

D-TCM region aliasses

D-TCM (16 kByte)

region #0 no physical memory

0x0040_4000

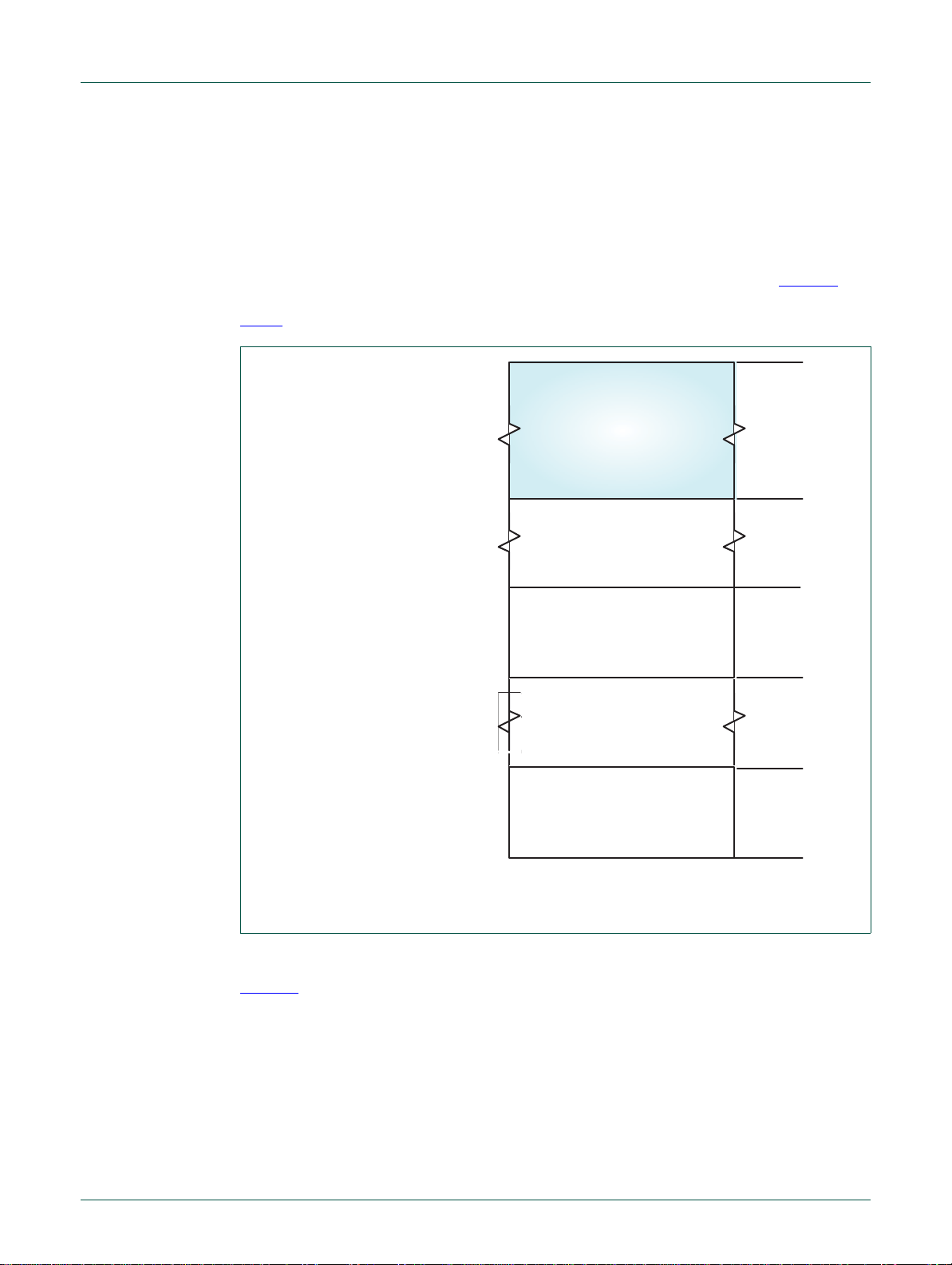

2.3.2.1 Region 0: TCM area

The ARM968E-S processor has its exception vectors located at address logic 0. Since

flash is the only non-volatile memory available in the LPC2917/19, the exception vectors

in the flash must be located at address logic 0 at reset (AHB_RST).

After booting a choice must be made for region 0. When enabled the Tightly Coupled

Memories (TCMs) occupy fixed address locations in region 0 as indicated in Figure 4

Information on how to enable the TCMs can be found in the ARM documentation, see

Ref. 2

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

DRAFT

F

T DRAFT DRAFT DRAFT DRA

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

.

.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 9 of 263

Fig 4. Region 0: TCM memory

2.3.2.2 Region 1: embedded flash area

Figure 5

gives a graphical overview of the embedded flash memory map.

Page 10

NXP Semiconductors

0x00000000

0x1FFFFFFF

0x00200000

FLASH IF1

Configuration Area (4 Kbyte)

0x00200FFF

Embedded FLASH

memory area

512 Kbyte -

768 Kbyte

0x0007FFFF - 0x000BFFFF

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

Fig 5. Region 1 embedded flash memory

Region 1 is reserved for the embedded flash. A data area of 2 Mbyte (to be prepared for a

larger flash-memory instance) and a configuration area of 4 kB are reserved for each

embedded flash instance. Although the LPC2917/19 contains only one embedded flash

instance, the memory aperture per instance is defined at 4 Mbyte.

2.3.2.3 Region 2: external static memory area

Region 2 is reserved for the external static memory. The LPC2917/19 provides I/O pi ns for

eight bank-select signals and 24 address lines. This implies that eight memory banks of

16 Mbytes each can be addressed externally.

2.3.2.4 Region 3: external static memory controller area

The external Static-Memory Controller configuration area is located at region 3

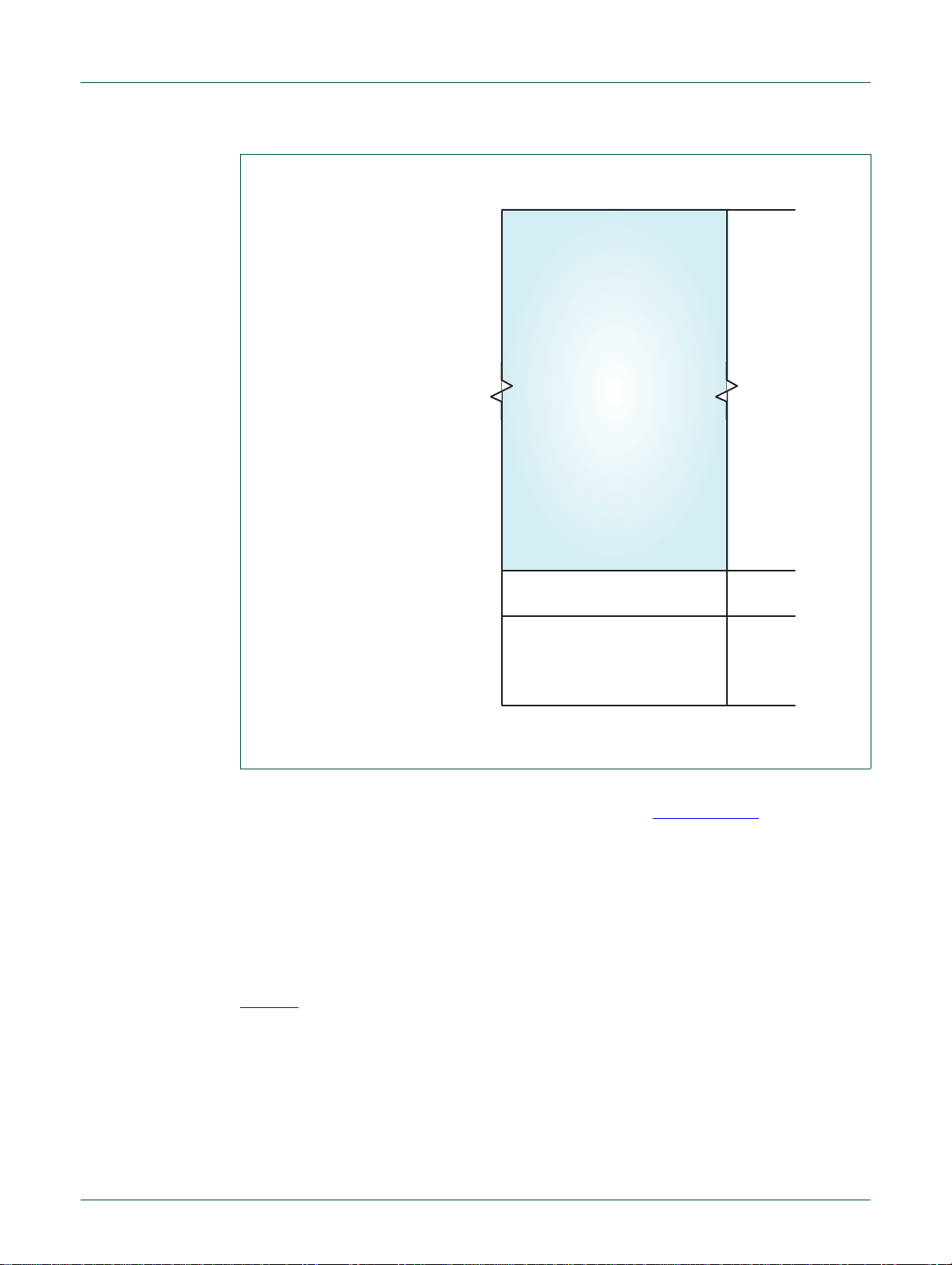

2.3.2.5 Region 4: internal SRAM area

Figure 6

gives a graphical overview of the internal SRAM memory map.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 10 of 263

Page 11

NXP Semiconductors

Region #4: embedded SRAM

0x8000_0000 - 0x9FFF_FFFF

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

embedded Memory (Controller) #2..#N

Data Transfer Area

(reserved for future extensions)

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

0x1FFF_FFFF

DR

AFT

DRAFT

DR

F

T DRAF

Fig 6. Region 4 internal SRAM memory

Region 4 is reserved for internal SRAM. The LPC2917/19 has two internal SRAM

instances. Instance #0 is 32 kB, instance #1 is 16 kB. See Section 3.5.2.3

2.3.2.6 Region 5

Not used.

2.3.2.7 Region 6

Not used.

2.3.2.8 Region 7: bus-peripherals area

Figure 7

gives a graphical overview of the bus-peripherals area memory map.

embedded Memory (Controller) #1

Data Transfer Area (16kByte)

embedded Memory (Controller) #0

Data Transfer Area (32kByte)

0x0000_c000

0x000_8000

0x0000_0000

(Offset Address)

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 11 of 263

Page 12

NXP Semiconductors

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

Interrupt Controller (4 kByte)

VIC

Not Used

Power, Clock & Reset Area (12 kByte)

Reserved for future FRSS extensions

PCR

Reserved

MMIO Area

(reserved for future extensions)

0x1FFF_FFFF

0x1FFF_F000

0x1FFF_B000

0x1FFF_8000

0x1FFF_7000

0x1FFF_6000

Region #7: Bus Peripherals

0xE000_0000 - 0xFFFF_FFFF

Peripheral Cluster #7..#N

(reserved for future extensions)

Peripheral Cluster #6 (128 kByte)

MSCSS

Peripheral Cluster #5 (128 kByte)

(reserved for future extensions)

Peripheral Cluster #4 (128 kByte)

IVNSS

Peripheral Cluster #3 (128 kByte)

(reserved for future extensions)

Peripheral Cluster #2 (128 kByte)

PeSS

Peripheral Cluster #1 (128 kByte)

(reserved for future extensions)

Peripheral Cluster #0 (128 kByte)

GeSS

0x1000_0000

0x000E_0000

0x000C_0000

0x000A_0000

0x0008_0000

0x0006_0000

0x0004_0000

0x0002_0000

0x0000_0000

(Offset Address)

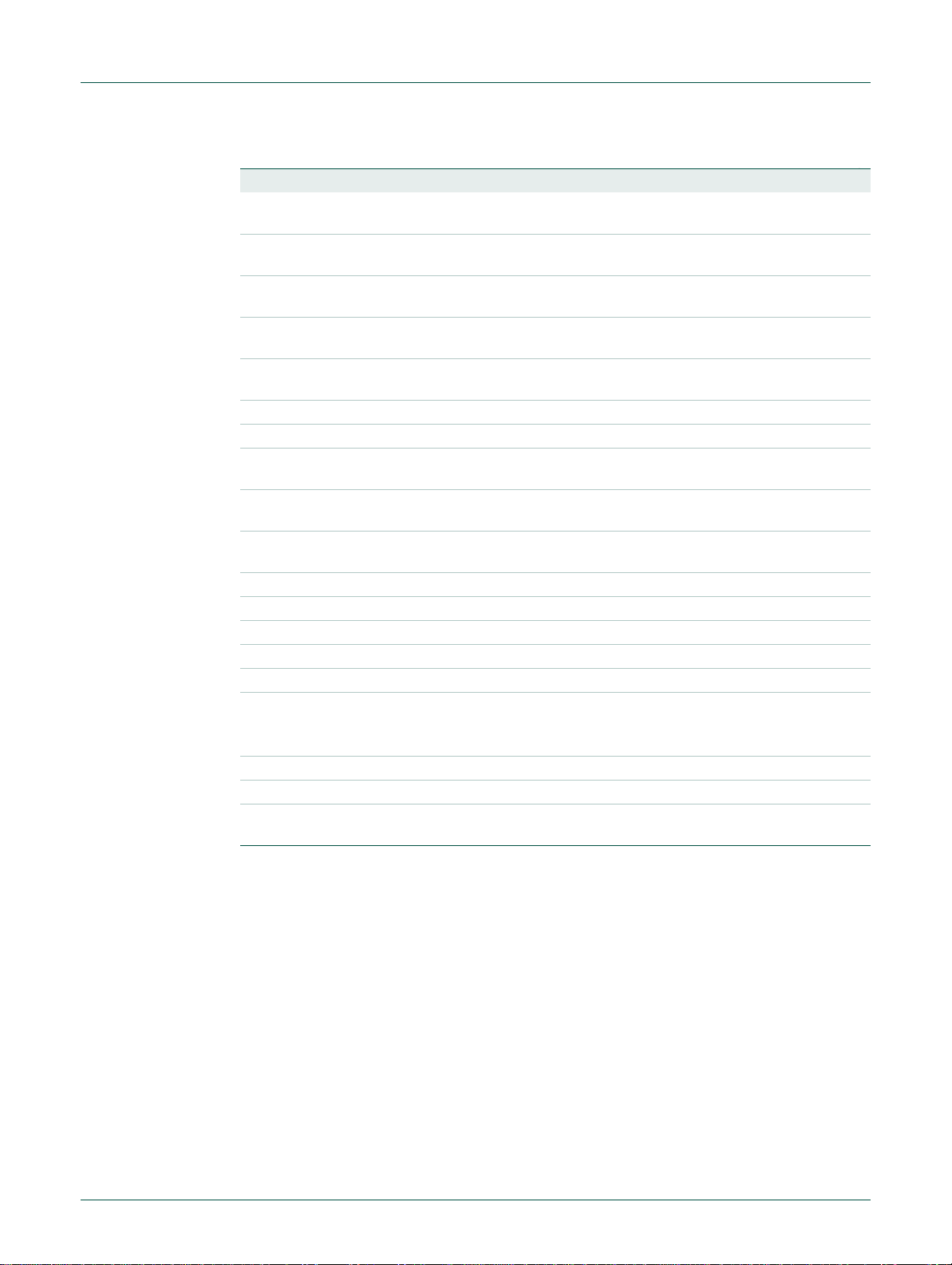

Fig 7. Region 7 bus-peripherals area memory

Region 7 is reserved for all stand-alone memory-mapped bus peripherals.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 12 of 263

Page 13

NXP Semiconductors

The lower part of region 7 is again divided into VPB clusters, also referred to as

subsystems in this User Manual. A VPB cluster is typically used as the address space for

a set of VPB peripherals connected to a single AHB2VPB bridge, the slave on the AHB

system bus. The clusters are aligned on 256 kB boundaries. In the LPC2917/19 four VPB

clusters are in use: General SubSystem (GeSS), Peripheral SubSystem (PeSS), InVehicle Networking SubSystem (IVNSS) and the Modulation and Sampling SubSystem

(MSCSS). The VPB peripherals are aligned on 4 kB boundaries inside the VPB clusters.

The upper part of region 7 is used as the memory area where memory-mapped register

interfaces of stand-alone AHB peripherals and a DTL cluster reside. Each of these is a

slave on the AHB system bus. In the LPC2917/19 two such slaves are present: the Power,

Clock and Reset subsystem (PCRSS) and the Vectored Interrupt Controller (VIC). The

PCRSS is a DTL cluster in which the CGU, PMU and RGU are connected to the AHB

system bus via an AHB2DTL adapter. The VIC is a DTL target connected to the AHB

system bus via its own AHB2DTL adapter.

2.3.3 Memory-map operating concepts

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

The basic concept in the LPC2917/19 is that each memory area has a ‘natural’ location in

the memory map. This is the address range for which code residing in that area is written.

Each memory space remains permanently fixed in the same location, eliminatin g the need

to have portions of the code designed to run in different address ran ges.

Because of the location of the exception-handler vectors on the ARM9 processor (at

addresses 0000 0000h through 0000 001Ch: see Table 2

embedded flash is mapped at address 0000 0000h to allow initial code to be executed

and to perform the required initialization, which starts executing at 0000 0000h.

The LPC2917/19 generates the appropriate bus-cycle abort exception if an access is

attempted for an address that is in a reserved or unused address region or unassigned

peripheral spaces. For these areas bo th attempted data accesses and instruction fetches

generate an exception. Note that write-access addresses should be word-aligned in ARM

code or half-word aligned in Thumb code. Byte-aligned writes are performed as word or

half-word aligned writes without error signalling.

Within the address space of an existing peripheral a dat a-abort exception is not gener ated

in response to an access to an undefined address. Address decoding within each

peripheral is limited to that needed to distinguish defined registers within the peripheral

itself. Details of address aliasing within a peripheral space are not defined in the

LPC2917/19 documentation and are not a supported feature.

Note that the ARM stores the pre-fetch abort flag along with the associated instruction

(which will be meaningless) in the pipeline and processes the abort only if an attempt is

made to execute the instruction fetched from the illegal address. This prevents the

accidental aborts that could be caused by pre-fetches occurring when code is executed

very near to a memory boundary.

) By default, after reset, the

Table 3

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 13 of 263

gives the base-address overview of all peripherals:

Page 14

NXP Semiconductors

Table 2. Interrupt vectors address table

Address Exception

0000 0000h Reset

0000 0004h Undefined instruction

0000 0008h Software interrupt

0000 000Ch Pre-fetch abort (instruction-fetch memory fault)

0000 0010h Data abort (data-access memory fault)

0000 0014h reserved

0000 0018h IRQ

0000 001Ch FIQ

Table 3. Peripherals base-address overview

Base address Base name AHB peripherals

Memory region 0 to region 6

0000 0000h TCM memory

2000 0000h Embedded flash memory

2020 0000h FMC RegBase Embedded-flash controller

4000 0000h External static memory

6000 0000h SMC RegBase External Static-Memory Controller

8000 0000h Internal SRAM memory

VPB Cluster 0: general subsystem

E000 0000h CFID RegBase Chip/feature ID register

E000 1000h SCU RegBase System Control Unit

E000 2000h ER RegBase Event Router

VPB Cluster 2: peripheral subsystem

E004 0000h WDT RegBase Watchdog Timer

E004 1000h TMR RegBase Timer 0

E004 2000h TMR RegBase Timer 1

E004 3000h TMR RegBase Timer 2

E004 4000h TMR RegBase Timer 3

E004 5000h UART RegBase 16C550 UART 0

E004 6000h UART RegBase 16C550 UART 1

E004 7000h SPI RegBase SPI 0

E004 8000h SPI RegBase SPI 1

E004 9000h SPI RegBase SPI 2

E004 A000h GPIO RegBase General-Purpose I/O 0

E004 B000h GPIO RegBase General-Purpose I/O 1

E004 C000h GPIO RegBase General-Purpose I/O 2

E004 D000h GPIO RegBase General-Purpose I/O 3

VPB Cluster 4:

E008 0000h CANC RegBase CAN controller 0

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

configuration registers

configuration registers

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 14 of 263

Page 15

NXP Semiconductors

Table 3. Peripherals base-address overview

Base address Base name AHB peripherals

E008 1000h CANC RegBase CAN controller 1

E008 6000h CANAFM RegBase CAN ID look-up table memory

E008 7000h CANAFR RegBase CAN acceptance filter registers

E008 8000h CANCS RegBase CAN central status registers

E008 9000h LIN RegBase LIN master controller 0

E008 A000h LIN RegBase LIN master controller 1

VPB Cluster 6: modulation and sampling-control subsystem

E00C 0000h MTMR RegBase MSCSS timer 0

E00C 1000h MTMR RegBase MSCSS timer 1

E00C 3000h ADC RegBase ADC 1

E00C 4000h ADC RegBase ADC 2

E00C 5000h PWM RegBase PWM 0

E00C 6000h PWM RegBase PWM 1

E00C 7000h PWM RegBase PWM 2

E00C 8000h PWM RegBase PWM 3

Power, Clock and Reset control cluster

FFFF 8000h CGU RegBase Clock Generation Unit

FFFF 9000h RGU RegBase Reset Generation Unit

FFFF A000h PMU RegBase Power Management Unit

Vector interrupt controller

FFFF F000h VIC RegBase Vectored Interrupt Controller

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

…continued

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

2.4 Interrupt and wake-up structure

An overview of the interrupt and wake-up structure is given in Figure 8. The main

functions are:

• Events and interrupt requests causing an interrupt (IRQ or FIQ) on the ARM

processor.

• Events and interrupt requests causing a wake-up. During low-power mode selected

clock domains are switched off, and they are turned on by this wake-up.

wake-up

R

I

Ext.

Int.

UART

...

...

...

RTC

Interrupt Requests

CGU VIC ARM

Events

Event

Router

Fig 8. Interrupt and wake-up structure

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 15 of 263

Q

FIQ

Page 16

NXP Semiconductors

VIC ARM

IRQ

UART

Interrupt Requests

Event

Router

VIC ARM

IRQ

Interrupt Requests

Events

In this case the VIC (Vectored Interru pt Controller) is configured to send an interr upt (IRQ

or FIQ) towards the ARM processor. Examples are interrupts to indicate the reception of

data via a serial interface, or timer interrupts. The Event Router serves as a multiplexer for

internal and external events (e.g. RTC tick and external interrupt lines) and indicates the

occurrence of such an event towards the VIC (Event-Router interrupt). The Event Router

is also able to latch the occurrence of these events (level or edge-triggered).

Fig 9. Interrupt (UART) causing an IRQ

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

Fig 10. Event causing an IRQ

2.4.1 Interrupt device architecture

In the LPC2917/19 a general approach is taken to generate inter rupt requests towards the

CPU. A vectored Interrupt Controller (VIC) receives and collects the interrupt requests as

generated by the several modules in the device.

Figure 11

the parameters provided by the user software.

shows the logic used to gate the event signal originating from the function with

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 16 of 263

Page 17

NXP Semiconductors

31

2

1

0

STATUS

&

SET

STATUS

CLEAR

STATUS

ENABLE

SET

ENABLE

CLEAR

ENABLE

>1

>1

Event

Interrupt

Request

Control

Interface

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

Fig 11. I nterrupt device architecture

A set of software-accessible variables is provided for each interrupt source to control and

observe interrupt request generation. In general, a pair of read-only registers is used for

each event that leads to an interrupt request:

• STATUS captures the event. The variable is typically set by a hardware event and

cleared by the software ISR, but for test purposes it can also be set by software

• ENABLE enables the assertion of an interrupt-request output signal for the captured

event

In conjunction with the STATUS/ENABLE variables, commands are provided to set and

clear the variable state through a software write-action to write-only registers. These

commands are SET_STATUS, CLR_STATUS, SET_ENABLE and CLR_ENABLE.

The event signal is logically OR-ed with its associated SET_STATUS register bit, so both

events writing to the SET_STATUS register sets the STATUS register.

Typically, the result of multiple STATUS/ENABLE pairs is logically OR-ed per functional

group, forming an interrupt request signal towards the Vectored Interrupt Controller.

2.4.2 Interrupt registers

A list is provided for each function in the detailed block-description part of this document,

containing the interrupt sources for that function. A table is also provide d to indicate the bit

positions per interrupt source. These positions are identical for all the six registers

INT_STATUS, INT_ENABLE, INT_SET_STATUS, INT_CLEAR_STATUS,

INT_SET_ENABLE and INT_CLEAR_ENABLE.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 17 of 263

Up to 32 interrupt bits are available for each register .

Page 18

NXP Semiconductors

2.4.2.1 Interrupt clear-enable register

Write ‘1’ actions to this register set one or more ENABLE variables in the INT_ENABLE

register. INT_SET_ENABLE is write-only. Writing a 0 has no effect.

Table 4. INT_CLR_ENABLE register bit description

Bit Variable Name Access Value Description

i CLR_ENABLE[i] W 1 Clears the ENABLE[i] variable in corresponding

2.4.2.2 Interrupt set-enable register

Write ‘1’ actions to this register set one or more ENABLE variables in the INT_ENABLE

register. INT_SET_ENABLE is write-only. Writing a 0 has no effect.

Table 5. INT_SET_ENABLE register bit description

Bit Variable Name Access Value Description

i SET_ENABLE[i] W 1 Sets the ENABLE[i] variable in corresponding

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

INT_ENABLE register (set to 0)

INT_ENABLE register to 1

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

2.4.2.3 Interrupt status register

The interrupt status register reflects the status of the corresponding interrupt event that

leads to an interrupt request. INT_STATUS is a read-only register. Its content is either

changed by a hardware event (from logic 0 to 1 in the case of an event), or by software

writing a 1 to the INT_CLR_STATUS or INT_SET_STATUS register.

T able 6. INT_STATUS register bit description

* = reset value

Bit Variable Name Access Value Description

i STATUS[i] R 1 Event captured; request for interrupt service on

2.4.2.4 Interrupt enable register

This register enables or disables generation of inte rrupt requests on associated interruptrequest output signals. INT_ENABLE is a read-only register. Its content is changed by

software writing to the INT_CLR_ENABLE or INT_SET_ENABLE registers.

Table 7. INT_ENABLE register bit description

* = reset value

Bit Variable Name Access Value Description

i ENABLE[i] R 1 Enables interrupt request generation. The

the corresponding interrupt request signal if

ENABLE[i] = 1 interrupt for end of scan

0*

corresponding interrupt request output signal is

asserted when STATUS[i] =1

0*

2.4.2.5 Interrupt clear-status register

Write ‘1’ actions to this register clear one or more status variables in the INT_STATUS

register. Writing a ‘0’ has no effect.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 18 of 263

Page 19

NXP Semiconductors

T able 8. INT_CLR_STATUS register bit description

Bit Variable Name Access Value Description

i CLR_STATUS[i] W 1 Clears STATUS[i] variable in INT_STATUS

2.4.2.6 Interrupt set-status register

Write ‘1’ actions to this register set one or more STATUS variables in the INT_STATUS

register. This registe r is write-only and is intended for debug purposes. W riting a ‘0’ has no

effect.

Table 9. INT_SET_STATUS register bit description

Bit Variable Name Access Value Description

i SET_STATUS[i] W 1 Sets STATUS[i] variable in INT_STATUS

2.4.3 Wake-up

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

register (set to 0)

register to 1

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

In low-power mode, selected idle clock domains are switched off. The wake-up signal

towards the CGU enables the clock of these domains. A typical application is to configu re

all clock domains to switch off. Since the clock of the ARM processor is also switched off,

execution of software is suspended and resumed on wake-up.

In this case the Event Router is configured to send a wake-up signal towards the CGU

(Clock Generation Unit). Examples are events to indicate the reception of dat a (e.g. on the

CAN receiver) or external interrupts.

The VIC can be used (IRQ wake-up event or FIQ wake-up event of the Event Router) to

generate a wake-up event on an interrupt occurrence. This is only possible if the clock

domain of the interrupt source is excluded from low-power mode. The VIC does not need

a clock to generate these wake-up events.

Examples of use are to configure a timer to wake up the system af ter a defined time, or to

wake up on receiving data via the UART.

wake-up

CGUUART

Event

Router

Events

Fig 12. Interrupt (UART) causing a wake-up

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 19 of 263

Page 20

NXP Semiconductors

Event

Router

CGU VICUART

wake-up

Interrupt Requests

Events

ARM FMC

Flash

JTAG

interface

(Flash Mode)

JTAG

interface

(ARM mode)

Fig 13. Event (RTC) causing a wake-up

3. Block description

This chapter describes each block and how it is used in a typical application. It is assumed

that the provided drivers Ref. 7

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

are used.

DR

AFT

DRAFT

DR

F

T DRAF

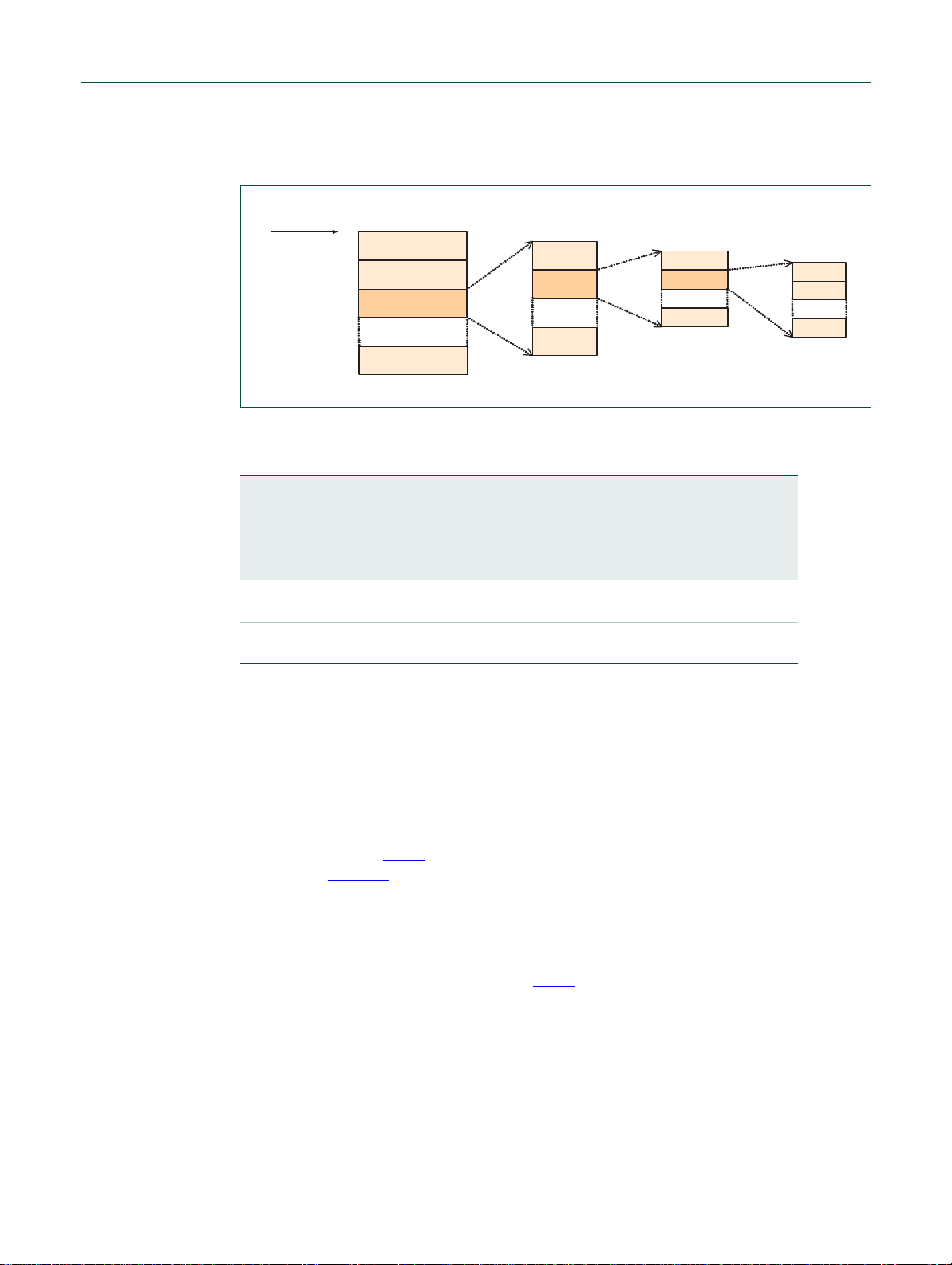

3.1 Flash Memory Controller (FMC)

3.1.1 Flash Memory Controller functional description

Fig 14. Schema t ic representation of the FMC

The flash memory consists of the embedded flash memory (flash) and a contro ller (the

FMC) to control access to it. The controller can be accessed in two ways: either by

register access in software, running on the ARM core, or directly via the JTAG interface

Figure 14

In the following sections access to the Flash Memory Controller via software is described.

Access via the JTAG interface is described in Section 6

.

.

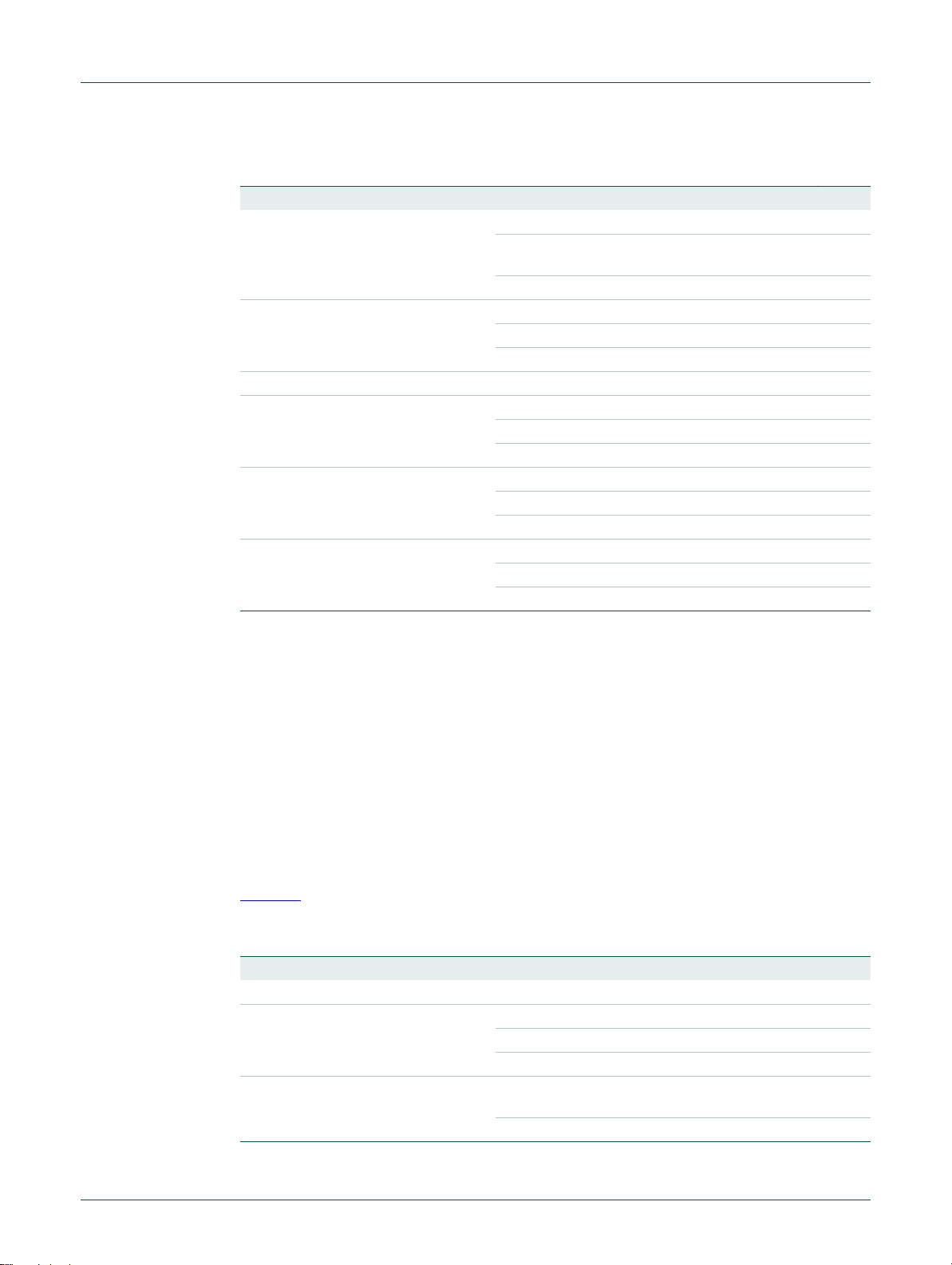

3.1.2 Flash memory layout

The flash memory is arranged into sectors, pages and flash-words Figure 15. For writing

(erase/burn) the following issues are relevant:

• Protection against erase/burn is arranged per sector.

• Erasing is done per sector.

• Burning - the actual write into flash memory - is done per page.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 20 of 263

Page 21

NXP Semiconductors

Base Address of

Flash Memory

Sector 0

Sector 2

Sector 1

Sector s

Page 1

Page 0

Page p

FlashWord 0

FlashWord 1

FlashWord

Byte 0

Byte 1

Byte 15

• The smallest part that can be written at once is a flash-word (16 bytes).

Fig 15. Flash memory layout

Table 10 lists the various parameters of the flash memory.

Table 10. Flash memory layout

Type number Flash size Sector Page

LPC2919 768k 8/11 8192/6553616/128 512 bytes 32 16 byte

DRAFT

Preliminary UM

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

DRAFT

LPC2917/19 - ARM9 microcontroller with CAN and LIN

F

T DRAFT DRAFT DRAFT DRA

Flash-word

#

small

large

Size

small

large

(per sector)

#

Size # Size

small

large

(per page)

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

LPC2917 512k 8/7 8192/6553616/128 512 byte 32 16 byte

3.1.3 Flash memory reading

During a read (e.g. read-only data or program execu tio n ) no spec ial ac tion s ar e re qu ire d .

The address space of flash memory can simply be accessed like normal ROM with word,

half-word or byte access. It is possible however to modify or optimize the read settings of

the flash memory.

For optimal read performance the flash memory cont ains two intern al 128- bit buf f ers. The

configuration of these buffers and the number of wait-states for unbuffered reads can be

set in the FMC, see Ref. 1

register see Table 18

. For a detailed description of the flash bridge wait-states

.

3.1.4 Flash memory writing

Writing can be split into two parts, erasing and burning. Both operations are

asynchronous; i.e. after initiating the operation it takes some time to complete. Erasing is

a relatively time-consuming process, see Ref. 1

flash memory results in wait-states. To serve interrupts or perform other actions this

critical code must be present outside the flash memory (e.g. internal RAM). Th e code that

initiates the erase/burn operation mus t al so be present outside the flash memory.

Normally the sectors are protected against write actions. Before a write is started the

corresponding sector(s) must be unprotected, after which protection can be enabled

again. Protection is automatically enabled on a reset. During a write (erase/burn)

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 21 of 263

operation the internal clock of the flash must be enabled. After comp letion the clock can

be disabled again.

. During this process any access to the

Page 22

NXP Semiconductors

In the following sections the typical write (erase and burn) sequences are listed.

3.1.4.1 Erase sequence (for one or more sectors)

• Unprotect sector(s) to be erased.

• Mark sector(s) to be erased.

• Initiate the erase process.

• Wait until erasing is finished see Section 2.4.1.

• Protect sector(s) (optional).

Remark: During the erase process the internal clock of the flash module must be enabled.

3.1.4.2 Burn sequence (for one or more pages)

Burning data into the flash memory is a two-stage process. First the data for a page is

written into data latches, and afterwards the contents of these data latc he s (sin g le page)

are burned into memory. If only a part of a page has to be burned the contents of the data

latches must be preset with logical 1s to avoid changing the remainder of the page.

Presetting these latches is done via the FMC (see Section 3.1.7

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

).

D

RAFT

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

• Unprotect the sectors containing the pa ges to be burned.

• For each page:

– Preset the data latches of the flash module (only required if a part of a page has to

be programmed; otherwise optional).

– Write data for the page into the data latches (ordin ary 32-bit word writes to the

address space of the flash memory).

Remark: Data must be written from flash-word boun daries onwards and must be a

multiple of a flash-word.

– Initiate the burn process.

– Wait until burning is finished, see Section 2.4.1

.

• Protect sectors (optional).

Remark: During the burn process the internal clock of the flash module must be enabled.

Remark: Only erased flash-word locations can be written to.

Remark: A complete page should be burned at one time. Before burning it again the

corresponding sector should be erase d.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 22 of 263

Page 23

NXP Semiconductors

Unprotect sectors

Enable flash clock

for each page to

be programmed

Write data to page

Start burning page

Wait for burning

to finish

Disable flash clock

Fig 16. Flash-memory burn sequence

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

3.1.5 Flash signature generation

The flash module contains a built-in signature generator. This generator can produce a

128-bit signature (MISR) from a range of the fl ash memory. A typical usage is to verify the

flashed contents against a calculated signature (e.g. during programming).

Remark: The address range for generating a signature must be aligned on flash-word

boundaries.

Remark: Like erasing a sector or burning a page, the generation of a signature is also an

asynchronous action; i.e. after starting generation the module begins calculating the

signature, and during this process any access to the flash results in wait-states (see

Section 3.1.2

). To serve interrupts or perform other actions this critical code must be

present outside flash memory (e.g. internal RAM). The code that initiates the signature

generation must also be present outside flash memory.

3.1.6 Flash interrupts

Burn, erase and signature generation (MISR) are asynchronous operations; i.e. after

initiating them it takes some time before they complete. During this period access to the

flash memory results in wait-states.

Completion of these operations is checked vi a the interrupt status register (INT_STATUS).

This can be done either by polling the corresponding interrupt status or by enabling the

generation of an interrupt via the interrupt enable register (INT_SET_ENABLE).

The following interrupt sources are available (see Ref. 1

):

• END_OF_BURN; indicates the completion of burning a page.

• END_OF_ERASE; indicates the completion of erasing one or more sectors.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 23 of 263

• END_OF_MISR; indicates the completion of signature generation.

Generation of an interrupt can be enabled (INT_SET_ENABLE register) or disabled

(INT_CLR_ENABLE register) for each of these interrupt sources. The interrupt status is

always available even if the corresponding interrupt is disabled. INT_STATUS indicates

the raw, unmasked interrupt status.

Page 24

NXP Semiconductors

Remark: The interrupt status of an operation should be cleared via the

INT_CLR_STATUS register before starting the operation, o therwise the status might

indicate completion of a previous operation.

Remark: Access to flash memory is blocked during asynchronous operations and results

in wait-states. Any interrupt service routine that needs to be serviced during this period

must be stored entirely outside the flash memory (e.g. in internal RAM).

Remark: To detect the completion of an operation (e.g. erase or burn) it is also possible to

poll the interrupt status register. This register indicates the raw interrupt status, i.e. the

status is independent of whether an interrupt is enabled or not. In this case the interrupts

of the Flash Memory Controller must be disabled (default value after reset).

Polling is the easiest way to detect completion of an operation. This method is also used

in the previous examples.

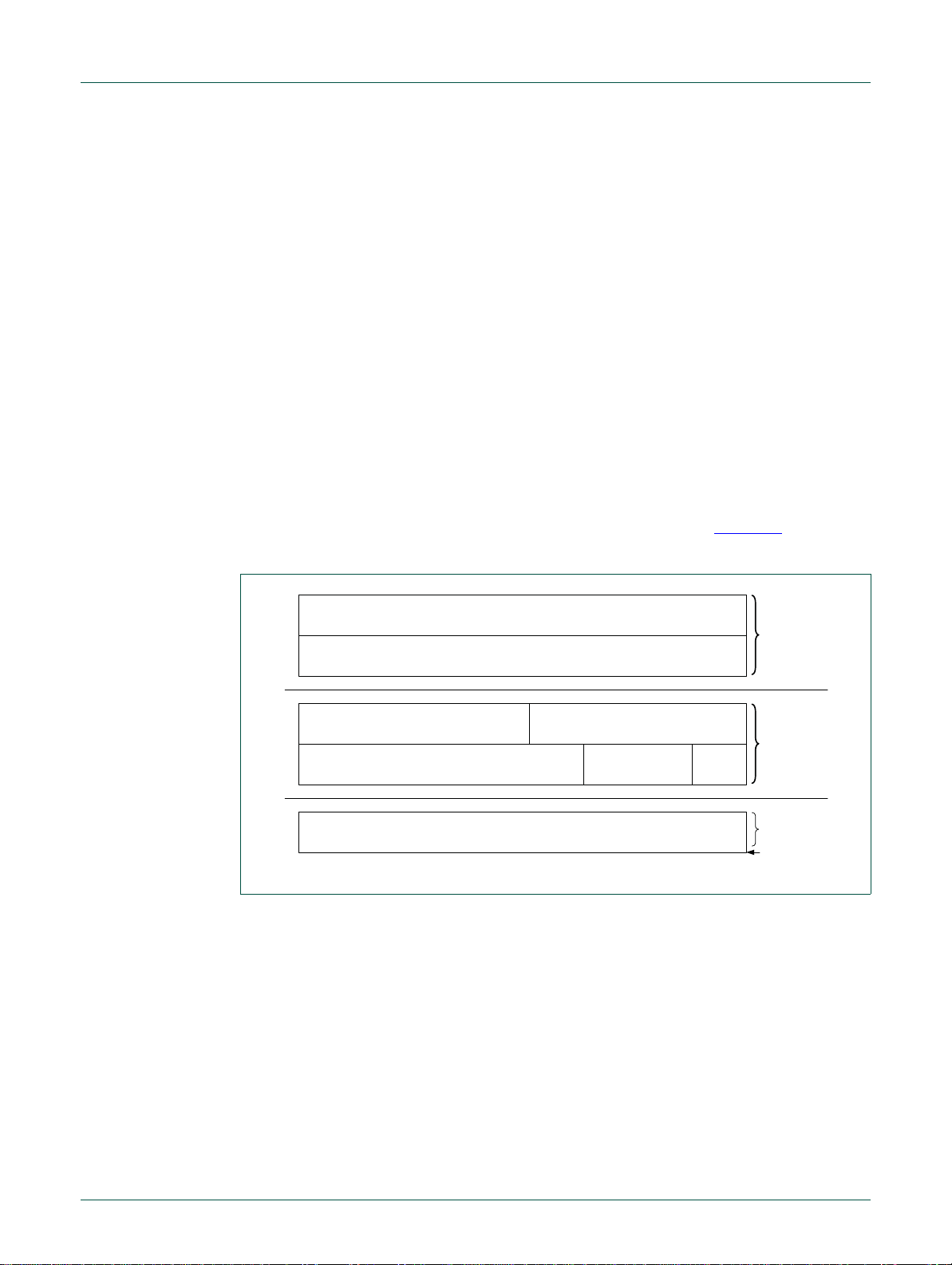

3.1.7 Flash memory index-sector features

The flash memory has a special index sector. This is normally invisible from the address

space. By setting the FS_ISS bit in the FCTR register the index sector becomes visible at

the flash base address and replaces all regular sectors. The layout Figure 17

procedure are similar to those for regular sectors.

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

and burn

DR

AFT

DRAFT

DR

F

T DRAF

JTAG

access

PAGES 6 - 7

PAGES 4 - 5

PAGES 0 - 3

Base address of

Flash Memory

Customer info

Customer info

Fig 17. Index sector layout

Sect or Se cur ity

Sect or Se cur ity

Reser ved

Reser ved

Reser ved

protection

By writing to specific locations in this sector the following features can be enabled:

• JTAG access protection

• Storage of customer information

• Sector security

Remark: It is not possible to erase the index sector. As a result the sector is write-only

and enabled features cannot be disabled again.

In the following sections these features and the procedures to en able th em are describ ed

in detail.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 24 of 263

Page 25

NXP Semiconductors

Remark: As the index sector shares the address space of the regular sectors it is not

possible to access it via code in flash. Accessing is only possible via code outside flash

memory (e.g. internal RAM).

Remark: Take care when writing locations in the index sector. The sector cannot be

erased, and using unspecified values or locations might result in a corrupted or

malfunctioning device which cannot be recovered.

3.1.7.1 JTAG access protection

JTAG access protection is a feature to block ac ce ss to the de vice thr ou g h the J TAG

interface. When this feature is enabled it is no longer possible to use the JTAG interface

(e.g. via a debugger) and read out memory or debug code.

The following flash word in the index sector controls JTAG access protection :

Table 11. JTAG access protection values

Flash-word

address

2000 0800h 4 All bits 1 Protection disabled (default)

LPC2917/19 - ARM9 microcontroller with CAN and LIN

FSS_ISS bit setIndex

sector page #

DRAFT

Preliminary UM

Flash-word value Description

All bits 0 Protection enabled

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

Remark: After enabling this feature is not activated until next reset.

Remark: When enabled it is not possible to disable this feature.

3.1.7.2 Index-sector customer info

The index sector can also be used to program customer-specific information. Page 5 (32

flash words) and the last 31 flash-words of page 4 (the first flash-word is used for JTAG

access protection) can be programme d at the cu sto m er’s discretion. The range available

for this purpose is shown in Table 12

Table 12. Customer-specific information

Index Sector Page #

(FS_ISS bit set)

4 0x2000 0830 0x2000 09FF

5 0x2000 0A40 0x2000 0BFF

3.1.7.3 Flash memory sector security

Sector security is a feature for setting sectors to Read-Only. It is possible to enable this

feature for each individual sector. Once it has been enabled it is no longer possible to

write (erase/burn) to the sector. This feature can be used, for example, to prevent a boot

sector from being replaced.

For every sector in flash memory there is a corresponding flash-word in the index sector

that defines whether it is secured or not. Table 13

flash-words and sectors in flash memory:

:

Customer Info

Address Range

shows the link between index sector

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 25 of 263

Page 26

NXP Semiconductors

Table 13. Index sector flash-words

Flash Memory

Address Range

0x2000 0000 0x2000 1FFF 6 11 0x2000 0CB0

0x2000 2000 0x2000 3FFF 6 12 0x2000 0CC0

0x2000 4000 0x2000 5FFF 6 13 0x2000 0CD0

0x2000 6000 0x2000 7FFF 6 14 0x2000 0CE0

0x2000 8000 0x2000 9FFF 6 15 0x2000 0CF0

0x2000 A000 0x2000 BFFF 7 16 0x2000 0E00

0x2000 C000 0x2000 DFFF 7 17 0x2000 0E10

0x2000 E000 0x2000 FFFF 7 18 0x2000 0E20

0x2001 0000 0x2001 FFFF 6 0 0x2000 0C00

0x2002 0000 0x2002 FFFF 6 1 0x2000 0C10

0x2003 0000 0x2003 FFFF 6 2 0x2000 0C20

0x2004 0000 0x2004 FFFF 6 3 0x2000 0C30

0x2005 0000 0x2005 FFFF 6 4 0x2000 0C40

0x2006 0000 0x2006 FFFF 6 5 0x2000 0C50

0x2007 0000 0x2007 FFFF 6 6 0x2000 0C60

Only for LPC2919

0x2008 0000 0x2008 FFFF 6 7 0x2000 0C70

0x2009 0000 0x2009 FFFF 6 8 0x2000 0C80

0x200A 0000 0x200A FFFF 6 9 0x2000 0C9 0

0x200B 0000 0x200B FFFF 6 10 0x2000 0CA0

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

Index Sector

Page #

Flash Memory

Sector #

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

Flash-Word

Address

(FS_ISS bit set)

DR

AFT

DRAFT

DR

F

T DRAF

In Table 14 decoding of the flash-word is listed:

Table 14. Sector security values

Flash-word value Description

All bits ‘1’ Corresponding sector is Read/Write (default)

All bits ‘0’ Corresponding sector is Read-Only

Remark: After enabling this feature is not activated until the next reset.

Remark: When enabled, it is not possible to disable this feature.

3.1.8 FMC register overview

The Flash Memory Controller registers have an offset to the base address FMC RegBase

which can be found in the peripherals base-address map, see Table 3

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 26 of 263

.

Page 27

NXP Semiconductors

Table 15. Flash Memory Controller re gister overview

Address

offset

000h R/W 0005h FCTR Flash control register see Table 16

004h reserved Reserved register; do

008h R/W 0000h FPTR Flash program-time

00Ch R - reserved Reserved register; do

010h R/W C004h FBWST Flash bridge wait-state

014h R - reserved Reserved register; do

018h R - reserved Reserved register; do

01Ch R/W 000h FCRA Flash clock divider

020h R/W 0 0000h FMSSTART Flash Built-In Self Test

024h R/W 0 0000h FMSSTOP Flash BIST stop-address

028h R - reserved Reserved register; do

02Ch R - FMSW0 Flash 128-bit signature

030h R - FMSW1 Flash 128-bit signature

034h R - FMSW2 Flash 128-bit signature

038h R - FMSW3 Flash 128-bit signature

FD8h W - INT_CLR_ENABLE Flash interrupt clear-

FDCh W - INT_SET_ENABLE Flash interrupt set-

FE0h R 0h INT_STATUS Flash interrupt status

FE4h R 0h INT_ENABLE Flash interrupt enable

FE8h W - INT_CLR_STATUS Flash interrupt

FECh W - INT_SET_ST ATUS Flash interrupt set-status

Access Reset

Value

DRAFT

Preliminary UM

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

DRAFT

LPC2917/19 - ARM9 microcontroller with CAN and LIN

F

T DRAFT DRAFT DRAFT DRA

Name Description Reference

-

not modify

see Table 17

register

-

not modify

see Table 18

register

-

not modify

-

not modify

see Table 19

register

see Table 20

(BIST) start-address

register

see Table 21

register

-

not modify

see Table 22

Word 0 register

see Table 23

Word 1 register

see Table 24

Word 2 register

see Table 25

Word 3 register

see Table 4

enable register

see Table 5

enable register

see Table 6

register

see Table 7

register

see Table 8

clear-status register

see Table 9

register

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

3.1.9 Flash memory control register

The flash memory control register (FCTR) is us ed to select read mode s and to control the

programming of flash memory.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 27 of 263

Page 28

NXP Semiconductors

Flash memory has data latches to store the data that is to be programmed into it, so that

the data-latch contents can be read instead of reading the flash memory contents.

Data-latch reading is always done without buffering, with the programmed number of

wait-states (WSTs) on every beat of the burst. Data-latch reading can be done both

synchronously and asynchronously, and is selected with the FS_RLD bit.

Index-sector reading is always done without buffering, with the programmed number of

WSTs on every beat of the burst. Index-sector reading can be done both synchronously

and asynchronously and is selected with the FS_ISS bit.

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

Table 16

Table 16. FCTR register bit description

* = reset value

Bit Symbol Access Value Description

31 to 16 reserved R - Reserved; do not modify. Read as logic 0

15 FS_LOADREQ R/W Data load request.

14 FS_CACHECLR R/W Buffer-line clear.

13 FS_CACHEBYP R/W Buffering bypass.

12 FS_PROGREQ R/W Programming request.

11 FS_RLS R/W Select sector latches for reading.

10 FS_PDL R/W Preset data latches.

9 FS_PD R/W Power-down.

8 reserved R - Reserved; do not modify. Read as logic 0

7 FS_WPB R/W Program and erase protection.

6 FS_ISS R/W Index-sector selection.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 28 of 263

shows the bit assignment of the FCTR register.

1 The flash memory is written if FS_WRE has

been set; the data load is automatically

triggered after the last word was written to the

load register.

0* Automatically cleared; always read as logic 0.

1 All bits of the data-transfer register are set.

0* Reset value.

1 Reading from flash memory is without buffering.

0* Read-buffering is active.

1 Flash memory programming is requested.

0* Reset value.

1 The sector latches are read.

0* The flash memory array is read.

1 All bits in the data latches are set.

0* Reset value.

1 The flash memory is in power-down.

0* Reset value.

1 Program and erase enabled.

0* Program and erase disabled.

1 The index sector will be read.

0* The flash memory array will be read.

Page 29

NXP Semiconductors

t

er

t

er tsec()

512 t

clk sys()

×

-------------------------------- -

=

t

er

t

wr pg()

512 t

clk sys()

×

-------------------------------- -

=

Table 16. FCTR register bit description

* = reset value

Bit Symbol Access Value Description

5 FS_RLD R/W Read data latches.

4 FS_DCR R/W DC-read mode.

3 reserved R - Reserved; do not modify. Read as logic 0

2 FS_WEB R/W Program and erase enable.

1 FS_WRE R/W Program and erase selection.

0 FS_CS R/W Flash memory chip-select.

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

…continued

1 The data latches are read for verification of data

that is loaded to be programmed.

0* The flash memory array is read.

1 Asynchronous reading selected.

0* Synchronous reading selected.

1* Program and erase disabled.

0 Program and erase enabled.

1 Program and data-load selected.

0* Erase selected.

1* The flash memory is ac ti ve .

0 The flash memory is in standby.

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

3.1.10 Flash memory program-time register

The flash memory program-time register (FPTR) controls the timer for burning and

erasing the flash memory. It also allows reading of the remaining burn or erase time.

Erase time to be programmed can be calculated from the following formula:

Burn time to be programmed can be calculated from the following formula:

Table 17

Table 17. FPTR register bit description

* = reset value

Bit Symbol Access Value Description

31 to 16 reserved R - Reserved; do not modify. Read as logic 0

15 EN_T R/W Program-timer enable.

14 to 0 TR[14:0] R/W Program timer; the (remaining) burn and erase

shows the bit assignment of the FPTR register.

1 Flash memory program timer enabled.

0* Flash memory program timer disabled.

0000h* Reset value.

time is 512 × TR clock cycles.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 29 of 263

Page 30

NXP Semiconductors

WST

t

acc clk()

t

t

tclk sys()

------------------

> 1–

WST

t

acc addr()

t

tclk sys()

--------------------- -

> 1–

3.1.11 Flash bridge wait-states register

The flash bridge wait-states register (FBWST) controls the number of wait-states inserted

for flash-read transfers. This register also controls the seco nd buffer line for asynchronous

reading.

To eliminate the delay associated with synchronizing flash-read data, a predefined

number of wait-states must be programmed. These depend on flash-memory response

time and system clock period. The minimum wait-states value can be calculated with the

following formulas where t

t

acc(addr)

Synchronous reading:

Asynchronous reading:

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

= clock access time, t

acc(clk)

= address access time (see Ref. 1 for further details):

clk(sys)

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

F

T DRAFT DRAFT DRAFT DRA

= system clock period and

DRAFT

DRA

F

DR

AFT

DR

T DRAF

Remark: If the programmed number of wait-states is more than three, flash-data reading

cannot be performed at full speed (i.e. with zero wait-states at the AHB bus) if speculative

reading is active.

Table 18

Table 18. FBWST register bit description

* = reset value

Bit Symbol Access Value Description

31 to 16 reserved R - Reserved; do not modify. Read as logic 0

15 CACHE2EN R/W Dual buffering enable.

14 SPECALWAYS R/W Speculative reading.

13 to 8 reserved R - Reserved; do not modify. Read as logic 0

7 to 0 WST[7:0] R/W Number of wait-states. Contains the number of

shows the bit assignment of the FBWST register.

1* Second buffer line is enabled.

0 Second buffer line is disabled.

1* S peculative reading is always performed.

0 Single speculative reading is performed.

wait-states to be inserted for flash memory

reading. The minimum calculated value must

be programmed for proper flash memory readoperation.

04h* Reset value.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 30 of 263

Page 31

NXP Semiconductors

t

BIST

t

fl BIST()

3+ t

clk sys()

×()FMSSTOP FMSSTART– 1+()×=

3.1.12 Flash-memory clock divider register

The flash-memory clock divider register (FCRA) controls the clock divider for the flashmemory program-and-erase clock CRA. This clock should be programmed to 66 kHz

during burning or erasing.

The CRA clock frequency fed to flash memory is the system clock frequency divided by

3 × (FCRA + 1). The programmed value must result in a CRA clock frequency of

66 kHz ± 20 %.

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

Table 19

Table 19. FCRA register bit description

* = reset value

Bit Symbol Access Value Description

31 to 12 reserved R - Reserved; do not modify. Read as logic 0

11 to 0 FCRA[11:0] R/W Clock divider setting.

shows the bit assignment of the FCRA register.

000h* No CRA clock is fed to the flash memory.

3.1.13 Flash-memory BIST control registers

The flash-memory Built-In Self Test (BIST) control registers control the embedded BIST

signature generation. This is implemented via the BIST start- address register FMSSTART

and the stop-address register FMSSTOP.

A signature can be generated for any part of the flash memory contents. The address

range to be used for generation is defined by writing the start address to the BIST startaddress register and the stop address to the BIST stop-address register. The BIST start

and stop addresses must be flash memory word-aligne d and can be derived from th e AHB

byte addresses through division by 16. Signature generation is star ted by setting the BIST

start-bit in the BIST stop-address register. Setting the BIST star t-bit is typically combined

with defining the signature stop address.

Flash access is blocked during the BIST signature calculation. The duration of the flash

BIST time is

Table 20

and Table 21 show the bit assignment of the FMSSTART and FMSSTOP

registers respectively.

Table 20. FMSSTART register bit description

* = reset value

Bit Symbol Access Value Description

31 to 17 reserved R - Reserved; do not modify. Read as logic 0,

write as logic 0.

16 to 0 FMSSTART[16:0] R/W 0 0000h* BIST start address (corresponds to AHB byte

address [20:4]).

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 31 of 263

Page 32

NXP Semiconductors

Table 21. FMSSTOP register bit description

* = reset value

Bit Symbol Access Value Description

31 to 18 reserved R - Reserved; do not modify. Read as logic 0,

17 MISR_START R/W BIST start.

16 to 0 FMSSTOP[16:0] R/W BIST stop address divided by 16 (corresponds

3.1.14 Flash-memory BIST signature registers

The flash-memory BIST signature registers return signatures as produced by the

embedded signature generator. There is a 128-bit signature reflected by the four registers

FMSW0, FMSW1, FMSW2 and FMSW3.

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

write as logic 0.

1 BIST signature generation is initiated.

0* Reset value.

to AHB byte address [20:4]).

0 0000h* Reset value.

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

The signature generated by the flash memory is used to verify the flash memory conten ts.

The generated signature can be compared with an expected signature and thus makes

unnecessary the more time- and code-consuming procedure of reading back the entire

contents.

Table 22

to Table 25 show bit assignment of the FMSW0 and FMSW1, FMSW2, FMSW3

registers respectively.

Table 22. FMSW0 register bit description

Bit Symbol Access Value Description

31 to 0 FMSW0[31:0] R - Flash BIST 128-bit signature (bits 31 to 0).

Table 23. FMSW1 register bit description

Bit Symbol Access Value Description

31 to 0 FMSW1[63:32] R - Flash BIST 128-bit signature (bits 63 to 32).

Table 24. FMSW2 register bit description

Bit Symbol Access Value Description

31 to 0 FMSW2[95:64] R - Flash BIST 128-bit signature (bits 95 to 64).

Table 25. FMSW3 register bit description

Bit Symbol Access Value Description

31 to 0 FMSW3[127:96] R - Flash BIST 128-bit signature (bits 127 to 96).

3.1.15 Flash interrupts

Burn, erase and signature generation (MISR) are asynchronous operations; i.e. after

initiating them it takes some time before they complete. During this period access to the

flash memory results in wait-states.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 32 of 263

Page 33

NXP Semiconductors

Completion of these operations is checked vi a the interrupt status register (INT_STATUS).

This can be done either by polling the corresponding interrupt status or by enabling the

generation of an interrupt via the interrupt enable register (INT_SET_ENABLE).

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

The following interrupt sources are available (see Ref. 1

):

• END_OF_BURN; indicates the completion of burning a page.

• END_OF_ERASE; indicates the completion of erasing one or more sectors.

• END_OF_MISR; indicate s the completion of a signature generation (MISR).

For each of these interrupt sources generation of an interrupt can be enabled

(INT_SET_ENABLE register) or disabled (INT _C LR_ E NA BLE re gis te r) . Th e interr u pt

status is always available even if the corresponding interrupt is disabled. INT_STATUS

indicates the raw, unmasked interrupt status.

Remark: The interrupt status of an operation should be cleared via the

INT_CLR_STATUS register before starting the operation, o therwise the status might

indicate completion of a previous operation.

Remark: Access to flash memory is blocked during asynchronous operations and results

in wait-states. Any interrupt service routine that needs to be serviced during this period

must be stored entirely outside flash memory (e.g. in internal RAM).

Remark: To detect completion of an operation (e.g. erase or burn) it is also possible to

poll the interrupt status register. This register indicates the raw interrupt status; i.e. the

status is independent of whether an interrupt is enabled or not. In this case the interrupts

of the Flash Memory Controller must be disabled (default value after reset).

Polling is the easiest way to detect completion of an operation. This method is also used

in the previous examples.

3.1.15.1 FMC interrupt bit description

Table 26

gives the interrupts for the FMC. The first column gives the bit numb er in the

interrupt registers. For a general explanation of the interrupt concept and a description of

the registers see Section 2.4

Table 26. FMC interrupt sources

Register

bit

31 to 3 unused Unused

2 END_OF_MISR BIST signature generati on has finished

1 END_OF_BURN Page burning has finished

0 END_OF_ERASE Erasing of one or more sectors has finished

Interrupt source Description

.

3.2 Static Memory Controller (SMC)

3.2.1 SMC functional description

External memory can be connected to the device. The Static Memory Controller (SMC)

controls timing and configuration of this external memory.

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 33 of 263

Page 34

NXP Semiconductors

ARM

Data (8/16/32 bit)

Address (lowest part)

SMC

External

Memory

Bank n

External

Memory

Bank 1

External

Memory

Bank 0

CS1

CS0

CS

n

Bank Select

Fig 18. Schemat ic representation of the SMC

The SMC provides an interface between a system bus and external (off-chip) memory

devices. It provides support for up to eight independently configurable memory banks

simultaneously . Each memory bank is capable of supporting SRAM , ROM, Flash EPROM,

Burst ROM memory or external I/O devices (memory-mapped).

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F

T DRAFT DRAFT DRAFT DRA

DR

AFT

DRAFT

DR

F

T DRAF

Each memory bank may be 8, 16, or 32 bits wide.

Table 27. Static-memory bank address range

Bank Address Range

0 0x4000 0000 0x43FF FFFF

1 0x4400 0000 0x47FF FFFF

2 0x4800 0000 0x4BFF FFFF

3 0x4C00 0000 0x4FFF FFFF

4 0x5000 0000 0x53FF FFFF

5 0x5400 0000 0x57FF FFFF

6 0x5800 0000 0x5BFF FFFF

7 0x5C00 0000 0x5FFF FFFF

Memory banks can be set to write-protect state. In this case the memory controller blocks

write access for the specified bank. When an illegal write occurs the WRITEPROTERR bit

in the SMBSR register is set.

3.2.2 External memory interface

The external memory interface depends on the bank width: 32, 16 or 8 bits selected via

MW bits in the corresponding SMBCR register. Choice of memory chips requires an

adequate set-up of the RBLE bit in the same register. RBLE = 0 for 8-bit based external

memories, while memory chips capable of accepting 16- or 32-bit wide data will work with

RBLE = 1. If a memory bank is configured to be 32 bits wide, address lines A0 and A1 can

be used as non-address lines. Memory banks configured to 16 bits wide do not require

A0, while 8-bit wide memory banks require address lines down to A0.

Configuring A1 and/or A0 line(s) to provide address or non-add ress function is

accomplished by setting up the SCU. Symbol A[x] refers to the highest-o rder add ress li ne

of the memory chip used in the external-memory interface. CS refers to the eight bankselect lines, and BLS refers to the four byte-lane select lines. WE_N is the write output

enable and OE_N is the output enable. Address pins on the device are shared with other

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 34 of 263

functions. When connecting external memories, check that the I/O pin is programmed to

the correct function. Control of these settings is handled by the SCU (see Section 3.4

).

Page 35

NXP Semiconductors

CS0 .. CS

n

OE_N

CECE

OEOE

WEWE

IO[15:0]IO[15:0]

A[x:0]A[x:0]

D[31:16] D[15:0]

BLS0

BLS1

A[x+2:2]

BLS2

BLS3

LB

UBUB

LB

WE_N

Figure 19 shows configuration of a 32-bit wide memory bank using 8-bit devices.

Figure 20

Figure 22

Figure 23

Figure 24

DRAFT

Preliminary UM

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

LPC2917/19 - ARM9 microcontroller with CAN and LIN

F

and Figure 21 show a 32-bit wide memory using 16- and 32-bit devices.

shows configuration of a 16-bit wide memory bank using 8-bit devices.

shows configuration of a 16-bit wide memory bank using 16-bit devices.

shows an 8-bit wide memory bank. This memory width requires 8-bit devices.

CS0 .. CS n

OE_N

CE CECECE

BLS3 BLS0BLS1BLS2

D[31:24] D[23:16] D[15:8] D[7:0]

A[x+2:2]

WE WEWEWE

IO[7:0] IO[7:0]IO[7:0]IO[7:0]

OEOE OEOE

D

RAFT

DR

DRAFT

T DRAFT DRAFT DRAFT DRA

A[x:0]A[x:0]A[x:0]A[x:0]

AFT

DRA

DR

AFT

DRAFT

DR

F

T DRAF

32-bit bank using 8-bit devices

Fig 19. External memory interface: 32-bit banks with 8-bit devices

32-bit bank using 16-bit devices

Fig 20. External memory interface: 32-bit banks with 16-bit devices

UMxxxxx © NXP B.V. 2007. All rights reserved.

User manual Rev. 01.02. — 8 November 2007 35 of 263

Page 36

NXP Semiconductors

CS0 .. CS

n

OE_N

CE

OE

WE

IO[31:0]

A[x:0]

D[31:0]

BLS2

BLS3

A[x+2:2]

B2

B3

BLS0

BLS1

B0

B1

WE_N

CS0 .. CS

n

OE_N

CECE

OEOE

WEWE

IO[7:0]IO[7:0]

A[x:0]A[x:0]

D[15:8] D[7:0]

BLS0BLS1

A[x+1:1]

LB

DRAFT

Preliminary UM

LPC2917/19 - ARM9 microcontroller with CAN and LIN

D

RAFT DRAFT DRAFT DRAFT DRAFT D

D

RAFT DRA

D

RAFT

DR

AFT

DRAFT

DRA

F