Page 1

UM10114

LPC21xx and LPC22xx User manual

Rev. 03 — 2 April 2008 User manual

Document information

Info Content

Keywords LPC2109/00, LPC2109/01, LPC2119, LPC2119/01, LPC2129,

LPC2129/01, LPC2114, LPC2114/01, LPC2124, LPC2124/01, LPC2194,

LPC2194/01, LPC2210, LPC2220, LPC2210/01, LPC2212, LPC2212/01,

LPC2214, LPC2214/01, LPC2290, LPC2290/01, LPC2292, LPC2292/01,

LPC2294, LPC2294/01, ARM, ARM7, 32-bit, Microcontroller

Abstract User manual for LPC2109/19/29/14/24/94 and

LPC2210/20/12/14/90/92/94 including /01 parts

Page 2

NXP Semiconductors

UM10114

LPC21xx and LPC22xx

Revision history

Rev Date Description

3.0 20080402

• Flash chapter updated with correct boot process flowchart.

• The Reinvoke ISP command has been removed from the ISP command description

because it is not implemented in the LPC21xx/LPC22xx.

• Description of CRP levels has been corrected, and CRP description for different

bootloader code versions has been added.

• Numbering of CAN controllers in the global CAN filter look-up table has been corrected

for /01 devices.

• Part ID’s have been updated for LPC2210/20 parts.

2.0 20080104 Integrated related parts into this manual and made numerous editorial and content updates

throughout the document:

• The format of this data sheet has been redesigned to comply with the new identity

guidelines of NXP Semiconductors.

• Legal texts have been adapted to the new company name where appropriate.

• Parts LPC2109, LPC2119, LPC2129, LPC2114, LPC2124, LPC2194, LPC2212,

LPC2214, LPC2290, LPC2292, LPC2294 and /01 parts added.

• PWM mode description updated.

• Fractional baud rate generator updated.

• CTCR register updated.

• ADC pin description updated.

• SPI clock conditions updated.

• JTAG pin description updated.

• Startup sequence diagram added.

• SPI master mode: SPI SSEL line conditioning for LPC2210/20 added in SPI pin

description table.

1.0 20051012 Moved the UM document into the new structured FrameMaker template. Many changes

were made to the format throughout the document. Here are the most important:

• UART0 and UART1 description updated (fractional baudrate generator and hardware

handshake features added - auto-CTS/RTS)

• ADC chapter updated with the dedicated result registers

• GPIO chapter updated with the descri ption of the Fast IOs

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 2 of 386

Page 3

1. Introduction

UM10114

Chapter 1: Introductory information

Rev. 03 — 2 April 2008 User manual

The LPC21xx and LPC22xx are based on a 16/32 bit ARM7TDMI-STM CPU with real-time

emulation and embedded trace support, together with 64/128/256 kilobytes (kB) of

embedded high speed flash memory. A 128-bit wide internal memory interface and a

unique accelerator architecture enable 32-bit code execution at maximum clock rate. For

critical code size applications, the alternative 16-bit Thumb Mode reduces code by more

than 30% with minimal performance penalty.

With their compact 64 and 144 pin packages, low power consumption, various 32-bit

timers, up to 12 external interrupt pins, and four channel 10-bit ADC and 46 GPIOs (64 pin

packages), or 8-channel 10-bit ADC and 112 GPIOs (144 pin package), these

microcontrollers are particularly targeted for industrial control, medical systems, access

control, and point-of-sale. With a wide range of serial communications interfaces, they are

also very well suited for communication gateways, protocol converters, and embedded soft

modems as well as many other general-purpose applications.

2. How to read this manual

The LPC21xx and LPC22xx user manual covers the following parts and versions:

• LPC2109, LPC2119, LPC2129, /00 and /01 versions

• LPC2114, LPC2124, /00 and /01 versions

• LPC2194 and LPC2194/01

• LPC2210, LPC2210/01, and LPC22 2 0

• LPC2212, LPC2214, /00 and /01 versions

• LPC2290 and LPC2290/01

• LPC2292, LPC2294, /00 and /01 versions

All parts exist in legacy versions and enhanced versions. Enhanced parts are equipped

with enhanced GPIO, SSP, ADC, UART, and timer peripherals. They are also backward

compatible to the “legacy” parts containing legacy versions of the same peripherals.

Therefore, enhanced parts contain all features of legacy parts as well. See Table 1–16

an overview.

To denote different versions the following suffixes are used (see Section 1–4 “

options”); no suffix, /00, /01, and /G. All /01 versions and the LPC2220 (no suffix) contai n

enhanced features.

for

Ordering

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 3 of 386

Page 4

NXP Semiconductors

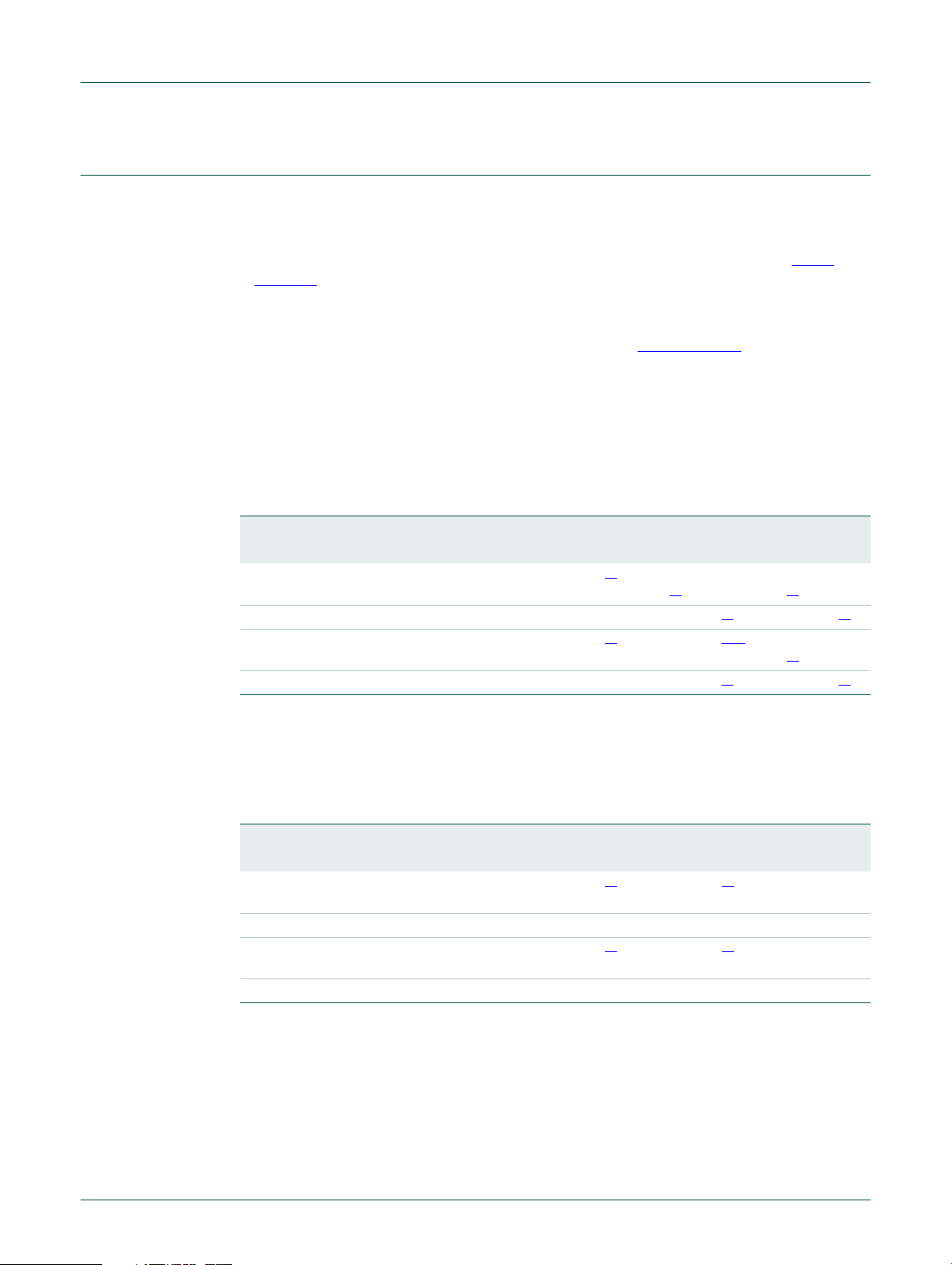

T able 1. LPC21xx and LPC22xx legacy/enhanced parts overview

Legacy parts Enhanced parts

LPC2109/00

LPC2119, LPC2119/00

LPC2129, LPC2129/00

LPC2114, LPC2114/00

LPC2124, LPC2124/00

LPC2194, LPC2194/00 LPC2194/01

LPC2210 LPC2210/01

LPC2212, LPC2212/00

LPC2214, LPC2214/00

LPC2290 LPC2290/01

LPC2292, LPC2292/00

LPC2294, LPC2294/00

This user manual describes enhanced feat ur es together with legacy features for all

LPC21xx and LPC22xx parts. Part specific and legacy/enhanced specific pinning,

registers, and configurations are listed in a table at the beginn ing of each chap ter (see for

example Table 6–52 “

determine which parts of the user manual apply.

UM10114

Chapter 1: Introductory information

LPC2109/01

LPC2119/01

LPC2129/01

LPC2114/01

LPC2124/01

LPC2220, LPC2220/G

LPC2212/01

LPC2214/01

LPC2292/01

LPC2294/01

LPC21xx/22xx part-specific register bits” ). Use this table to

3. Features

3.1 Legacy features common to all LPC21xx and LPC22xx parts

• 16-bit/32-bit ARM7TDMI-S microcontroller in a 64 or 144 pin package.

• 8/16/64 kB of on-chip static RAM and 64/128/256 kB of on-chip flash program

memory (except for flashless LPC2210/20/90). 128-bit wide interface/accelerator

enables high-speed 60 MHz operation.

• Diversified Code Read Protection (CRP) enables different security levels to be

implemented.

In-System/In-Application Programming (ISP/IAP) via on-chip boot loader software.

Single flash sector or full chip erase in 100 ms and programming of 256 bytes in 1 ms.

• External 8, 16, or 32-bit bus (144 pin package).

• EmbeddedICE RT and Embedded Trace offer real-time debugging with the on-chip

RealMonitor software and high speed tracing of instruction execution.

• Up to four interconnected CAN interfaces with advanced acceptance filters.

• 10-bit A/D converter providing four/eigh t analo g inp u ts with conversion time s as low

as 2.44 ms per channel and dedicated result registers to minimize interrupt overhead.

• Two 32-bit timers/external event counters with four capture and four compare

channels each, PWM unit (6 outputs), Real Time Clock (RTC), and watchdog.

• Multiple serial interfaces including two UARTs (16C550), a fast I

and two SPI interfaces.

2

C-bus (400 kbit/s),

• Vectored interrupt controller with configurable priorities and vector addresses.

• Up to forty-eight 5 V tolerant fast general purpose I/O pins.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 4 of 386

Page 5

NXP Semiconductors

• Up to 12 edge or level sensitive external interrupt pins available.

• 60 MHz maximum CPU clock available from programmable on-chip PLL with a

• For flashless LPC2210/20/90 only: 60 MHz (LPC2210/90), 72 MHz (LPC2290/01), or

• On-chip integrated oscillator operates with an external crystal in the range from

• Two power saving modes, Idle mode and Power-down mode.

• Peripheral clock scaling and individual enable/disable of peripheral functions for

• Processor wake-up from Power-down mode via external interrupt or CAN controllers.

• Dual power supply:

UM10114

Chapter 1: Introductory information

possible input frequency of 10 MHz to 25 MHz and a settling time of 100 ms.

75 MHz (LPC2210/01 and LPC2220) maximum CPU clock available from

programmable on-chip Phase-Locked Loop (PLL) with settling time of 100 μs.

1 MHz to 25 MHz and with an external oscillator up to 50 MHz.

additional power optimization.

– CPU operating voltage range of 1.65 V to 1.95 V (1.8 V ± 8.3 %).

– I/O power supply range of 3.0 V to 3.6 V (3.3 V ± 10 %) with 5 V tolerant I/O pads.

3.2 Enhanced features

• Fast GPIO ports enable port pin toggling up to 3.5 times faster than the original

device. They also allow for a port pin to be read at any time regardless of its function.

• Dedicated result registers for ADC reduce interrupt overhead. The ADC p ads are 5 V

tolerant when configured for digital I/O function(s).

• UART0/1 include fractional baud rate generator, auto-bauding capabilities, and

handshake flow-control fully implemented in hardware.

• Buffered SSP serial controller supporting SPI, 4-wire SSI, and Microwire formats.

• SPI programmable data length and master mode enhancement.

• General purpose timers can operate as ex ternal event counters.

4. Ordering options

4.1 LPC2109/21 19/2129

Table 2. LPC2109 /2119/2129 Ordering information

Type number Package

LPC2109FBD64/00 LQFP64 plastic low profile quad flat package; 64 leads;

LPC2109FBD64/01 LQFP64 plastic low profile quad flat package; 64 leads;

LPC2119FBD64 LQFP64 plastic low profile quad flat package; 64 leads;

LPC2119FBD64/00 LQFP64 plastic low profile quad flat package; 64 leads;

LPC2119FBD64/01 LQFP64 plastic low profile quad flat package; 64 leads;

Name Description Version

SOT314-2

body 10 × 10 × 1.4 mm

SOT314-2

body 10 × 10 × 1.4 mm

SOT314-2

body 10 × 10 × 1.4 mm

SOT314-2

body 10 × 10 × 1.4 mm

SOT314-2

body 10 × 10 × 1.4 mm

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 5 of 386

Page 6

NXP Semiconductors

UM10114

Chapter 1: Introductory information

Table 2. LPC2109 /2119/2129 Ordering information

…continued

Type number Package

Name Description Version

LPC2129FBD64 LQFP64 plastic low profile quad flat package; 64 leads;

SOT314-2

body 10 × 10 × 1.4 mm

LPC2129FBD64/00 LQFP64 plastic low profile quad flat package; 64 leads;

SOT314-2

body 10 × 10 × 1.4 mm

LPC2129FBD64/01 LQFP64 plastic low profile quad flat package; 64 leads;

SOT314-2

body 10 × 10 × 1.4 mm

Table 3. LPC2109/2119/2129 Ordering options

Type number Flash

memory

RAM CAN Fast GPIO/

SSP/

Temperature range

Enhanced

UART , ADC,

Timer

LPC2109FBD64/00 64 kB 8 kB 1 channel no −40 °C to +85 °C

LPC2109FBD64/01 64 kB 8 kB 1 channel yes −40 °C to +85 °C

LPC2119FBD64 128 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2119FBD64/00 128 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2119FBD64/01 128 kB 16 kB 2 channels yes −40 °C to +85 °C

LPC2129FBD64 256 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2129FBD64/00 256 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2129FBD64/01 256 kB 16 kB 2 channels yes −40 °C to +85 °C

4.2 LPC2114/2124

Table 4. LPC 2114/2124 Ordering information

Type number Package

Name Description Version

LPC2114FBD64 LQFP64 plastic low profile quad flat package; 64 leads;

body 10 × 10 × 1.4 mm

LPC2114FBD64/00 LQFP64 plastic low profile quad flat package; 64 leads;

body 10 × 10 × 1.4 mm

LPC2114FBD64/01 LQFP64 plastic low profile quad flat package; 64 leads;

body 10 × 10 × 1.4 mm

LPC2124FBD64 LQFP64 plastic low profile quad flat package; 64 leads;

body 10 × 10 × 1.4 mm

LPC2124FBD64/00 LQFP64 plastic low profile quad flat package; 64 leads;

body 10 × 10 × 1.4 mm

LPC2124FBD64/01 LQFP64 plastic low profile quad flat package; 64 leads;

body 10 × 10 × 1.4 mm

SOT314-2

SOT314-2

SOT314-2

SOT314-2

SOT314-2

SOT314-2

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 6 of 386

Page 7

NXP Semiconductors

Table 5. LPC2114/2124 Ordering options

Type number Flash

LPC2114FBD64 128 kB 16 kB no −40 °C to +85 °C

LPC2114FBD64/00 128 kB 16 kB no −40 °C to +85 °C

LPC2114FBD64/01 128 kB 16 kB yes −40 °C to +85 °C

LPC2124FBD64 256 kB 16 kB no −40 °C to +85 °C

LPC2124FBD64/00 256 kB 16 kB no −40 °C to +85 °C

LPC2124FBD64/01 256 kB 16 kB yes −40 °C to +85 °C

4.3 LPC2194

Table 6. LPC2194 Ordering information

Type number Package

LPC2194HBD64 LQFP64 plastic low profile quad flat package; 64 leads;

LPC2194HBD64/00 LQFP64 plastic low profile quad flat package; 64 leads;

LPC2194HBD64/01 LQFP64 plastic low profile quad flat package; 64 leads;

UM10114

Chapter 1: Introductory information

RAM Fast GPIO/SSP/

memory

Enhanced

UART, ADC,

Timer

Name Description Version

body 10 × 10 × 1.4 mm

body 10 × 10 × 1.4 mm

body 10 × 10 × 1.4 mm

Temperature range

SOT314-2

SOT314-2

SOT314-2

Table 7. LPC2194 Ordering options

Type number Flash

memory

RAM CAN Fast GPIO/

SSP/

Temperature range

Enhanced

UART, ADC,

Timer

LPC2194HBD64 256 kB 16 kB 4 channels no −40 °C to +125 °C

LPC2194HBD64/00 256 k B 16 kB 4 channels no −40 °C to +125 °C

LPC2194HBD64/01 256 k B 16 kB 4 channels yes −40 °C to +125 °C

4.4 LPC2210/2220

Table 8. LPC2210 /2220 Ordering information

Type number Package

Name Description Version

LPC2210FBD144 LQFP144 plastic low profile quad flat package; 144

leads; body 20 × 20 × 1.4 mm

LPC2210FBD144/01 LQFP144 plastic low profile quad flat package; 144

leads; body 20 × 20 × 1.4 mm

SOT486-1

SOT486-1

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 7 of 386

Page 8

NXP Semiconductors

UM10114

Chapter 1: Introductory information

Table 8. LPC2210 /2220 Ordering information

…continued

Type number Package

Name Description Version

LPC2220FBD144 LQFP144 plastic low profile quad flat package; 144

leads; body 20 × 20 × 1.4 mm

LPC2220FET144 TFBGA144 plastic thin fine-pitch ball grid array package;

144 balls; body 12 × 12 × 0.8 mm

LPC2220FET144/G TFBGA144 plastic thin fine-pitch ball grid array package;

144 balls; body 12 × 12 × 0.8 mm

Table 9. LPC2210/2220 Ordering options

Type number RAM Fast GPIO/

T e m perature range

SSP/

Enhanced

UART, ADC,

Timer

LPC2210FBD144 16 kB no −40 °C to +85 °C

LPC2210FBD144/01 16 kB yes −40 °C to +85 °C

LPC2220FBD144 64 kB yes −40 °C to +85 °C

LPC2220FET144 64 kB yes −40 °C to +85 °C

LPC2220FET144/G 64 kB yes −40 °C to +85 °C

SOT486-1

SOT569-1

SOT569-1

4.5 LPC2212/2214

Table 10. LPC2212/2214 Ordering information

Type number Package

Name Description Version

LPC2212FBD144 LQFP144 plastic low profile quad flat package; 144 leads;

body 20 × 20 × 1.4 mm

LPC2212FBD144/00 LQFP144 plastic low profile quad flat package; 144 leads;

body 20 × 20 × 1.4 mm

LPC2212FBD144/01 LQFP144 plastic low profile quad flat package; 144 leads;

body 20 × 20 × 1.4 mm

LPC2214FBD144 LQFP144 plastic low profile quad flat package; 144 leads;

body 20 × 20 × 1.4 mm

LPC2214FBD144/00 LQFP144 plastic low profile quad flat package; 144 leads;

body 20 × 20 × 1.4 mm

LPC2214FBD144/01 LQFP144 plastic low profile quad flat package; 144 leads;

body 20 × 20 × 1.4 mm

SOT486-1

SOT486-1

SOT486-1

SOT486-1

SOT486-1

SOT486-1

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 8 of 386

Page 9

NXP Semiconductors

Table 11. LPC2212/2214 Ordering options

Type number Flash memory RAM Fast GPIO/

LPC2212FBD144 128 kB 16 kB no −40 °C to +85 °C

LPC2212FBD144/00 128 kB 16 kB no −40 °C to +85 °C

LPC2212FBD144/01 128 kB 16 kB yes −40 °C to +85 °C

LPC2214FBD144 256 kB 16 kB no −40 °C to +85 °C

LPC2214FBD144/00 256 kB 16 kB no −40 °C to +85 °C

LPC2214FBD144/01 256 kB 16 kB yes −40 °C to +85 °C

4.6 LPC2290

Table 12. LPC2290 Ordering information

Type number Package

LPC2290FBD144 LQFP144 plastic low profile quad flat package;

LPC2290FBD144/01 LQFP144 plastic low profile quad flat package;

UM10114

Chapter 1: Introductory information

Temperature range

SSP/

Enhanced

UART, ADC,

Timer

Name Description Version

SOT486-1

144 leads; body 20 × 20 × 1.4 mm

SOT486-1

144 leads; body 20 × 20 × 1.4 mm

Table 13. LPC2290 Ordering options

Type number RAM CAN Enhancements T emperature range

LPC2290FBD144 16 kB 2 channels None −40 °C to +85 °C

LPC2290FBD144/01 64 kB 2 channels Higher CPU clock, more

−40 °C to +85 °C

on-chip SRAM, Fast I/Os,

improved UARTs, added SSP,

upgraded ADC

4.7 LPC2292/2294

Table 14. LPC2292/2294 Ordering information

Type number Package

Name Description Version

LPC2292FBD144 LQFP144 plastic low profile quad flat package;

144 leads; body 20 × 20 × 1.4 mm

LPC2292FBD144/00 LQFP144 plastic low profile quad flat package;

144 leads; body 20 × 20 × 1.4 mm

LPC2292FBD144/01 LQFP144 plastic low profile quad flat package;

144 leads; body 20 × 20 × 1.4 mm

LPC2292FET144/00 TFBGA144 plastic thin fine-pitch ball grid array package;

144 balls; body 12 × 12 × 0.8 mm

LPC2292FET144/01 TFBGA144 plastic thin fine-pitch ball grid array package;

144 balls; body 12 × 12 × 0.8 mm

LPC2292FET144/G TFBGA144 plastic thin fine-pitch ball grid array package;

144 balls; body 12 × 12 × 0.8 mm

SOT486-1

SOT486-1

SOT486-1

SOT569-1

SOT569-1

SOT569-1

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 9 of 386

Page 10

NXP Semiconductors

UM10114

Chapter 1: Introductory information

Table 14. LPC2292/2294 Ordering information

Type number Package

Name Description Version

LPC2294HBD144 LQFP144 plastic low profile quad flat package;

144 leads; body 20 × 20 × 1.4 mm

LPC2294HBD144/00 LQFP144 plastic low profile quad flat package;

144 leads; body 20 × 20 × 1.4 mm

LPC2294HBD144/01 LQFP144 plastic low profile quad fla t package;

144 leads; body 20 × 20 × 1.4 mm

Table 15. LPC2292/2294 Ordering options

Type number Flash

memory

LPC2292FBD144 256 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2292FBD144/00 256 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2292FBD144/01 256 kB 16 kB 2 channels yes −40 °C to +85 °C

LPC2292FET144/00 256 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2292FET144/01 256 kB 16 kB 2 channels yes −40 °C to +85 °C

LPC2292FET144/G 256 kB 16 kB 2 channels no −40 °C to +85 °C

LPC2294HBD144 256 kB 16 kB 4 channels no −40 °C to +125 °C

LPC2294HBD144/00 256 kB 16 kB 4 channels no −40 °C to +125 °C

LPC2294HBD144/01 256 kB 16 kB 4 channels yes −40 °C to +125 °C

RAM CAN Fast GPIO/

…continued

SOT486-1

SOT486-1

SOT486-1

Temperature range

SSP/

Enhanced

UART, ADC,

Timer

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 10 of 386

Page 11

NXP Semiconductors

system

clock

SCL

P0[30:27], P[25:0]

P2[31:0]

P1[31:16], P1[1:0]

P3[31:0]

SDA

CS3 to CS0

A23 to A0

BLS3 to BLS0

OE, WE

D31 to D0

TRST

(1)

TMS

(1)

TCK

(1)

TDI

(1)

TDO

(1)

XTAL2

XTAL1

SCK1

MOSI1

MISO1

EINT3 to EINT0

4 × CAP0

4 × CAP1

4 × MAT1

4 × MAT0

n × AIN

PWM6 to PWM1

SSEL1

n × TD

n × RD

TXD0, TXD1

RXD0, RXD1

DSR1, CTS1,

DCD1, RI1

AMBA AHB

(Advanced High-performance Bus)

AHB BRIDGE

EMULATION

TRACE MODULE

TEST/DEBUG

INTERFACE

AHB

DECODER

AHB TO APB

BRIDGE

APB

DIVIDER

VECTORED

INTERRUPT

CONTROLLER

SYSTEM

FUNCTIONS

PLL

SPI1/SSP

SERIAL INTERFACE

I

2

C-BUS SERIAL

INTERFACE

UART0/UART1

CAN

WATCHDOG

TIMER

EXTERNAL

INTERRUPTS

GENERAL

PURPOSE I/O

PWM0

CAPTURE/

COMPARE

TIMER 0/TIMER 1

A/D CONVERTER

ARM7TDMI-S

LPC21xx

LPC22xx

INTERNAL

SRAM

CONTROLLER

8/16 kB

SRAM

ARM7 local bus

APB (advanced

peripheral bus)

SCK0

MOSI0

MISO0

SSEL0

SPI0

SERIAL INTERFACE

REAL-TIME CLOCK

SYSTEM CONTROL

INTERNAL

FLASH

CONTROLLER

64/128/256 kB

FLASH

RST

EXTERNAL MEMORY

CONTROLLER

P0, P1

HIGH-SPEED

GPI/O

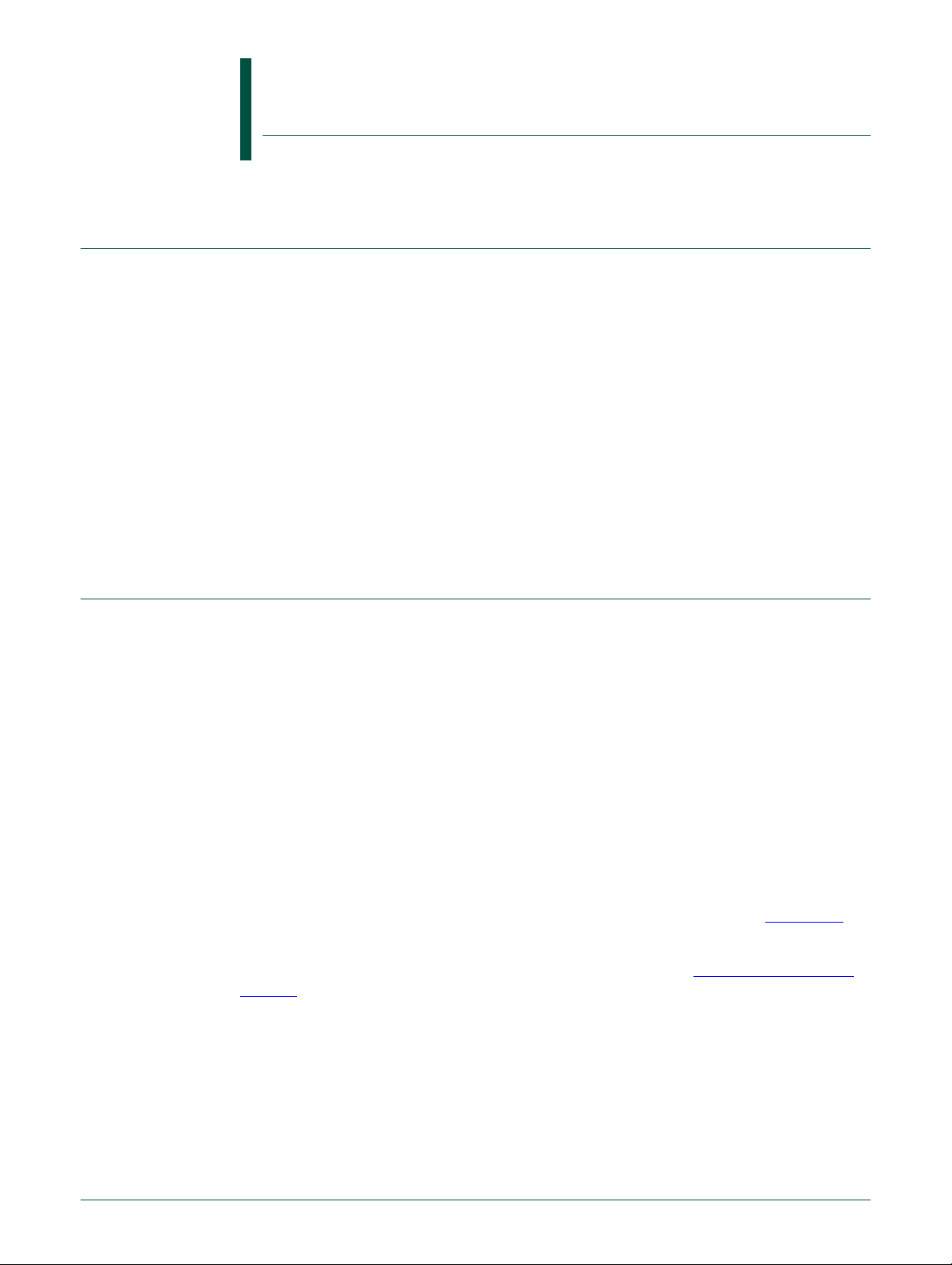

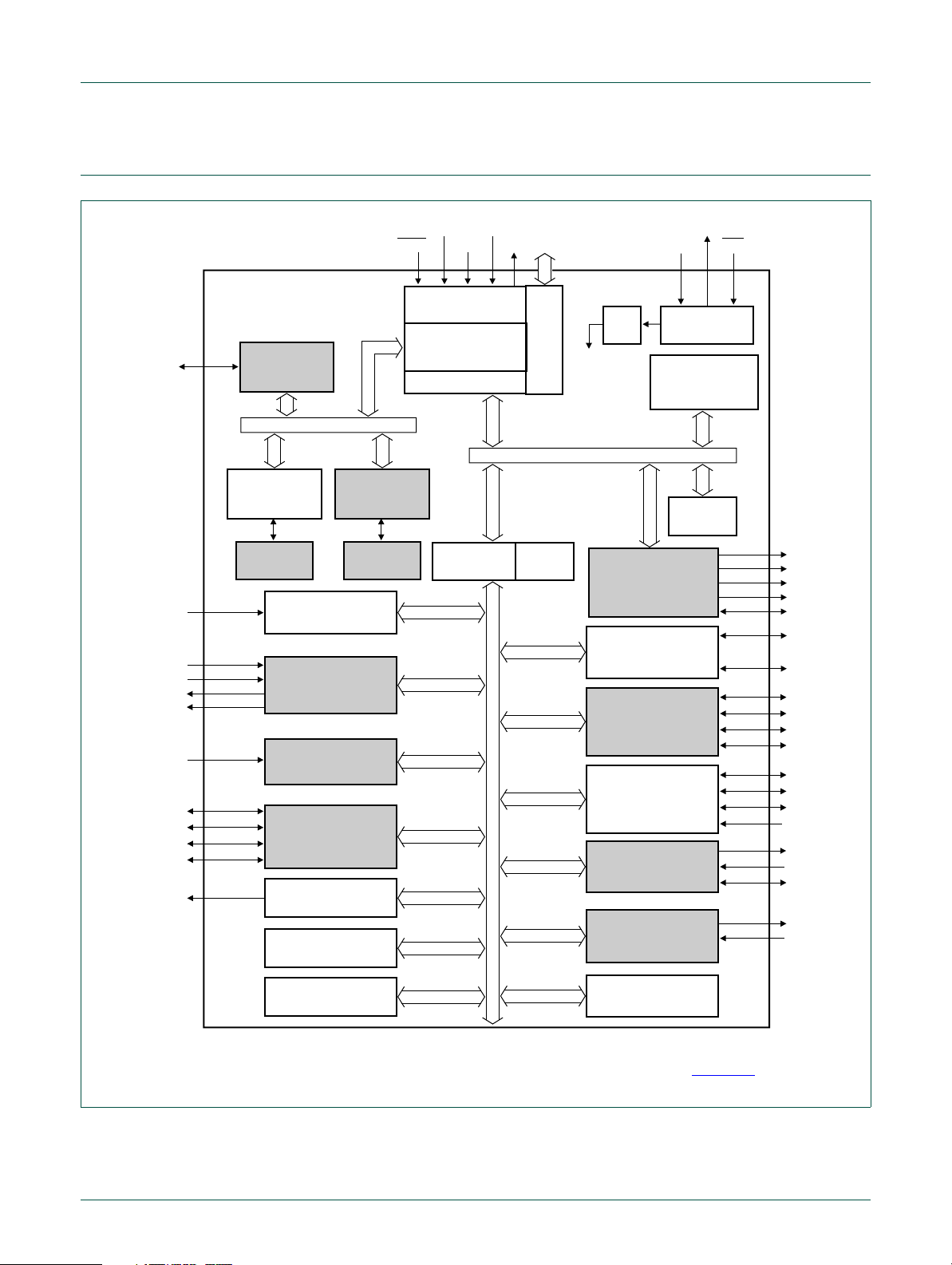

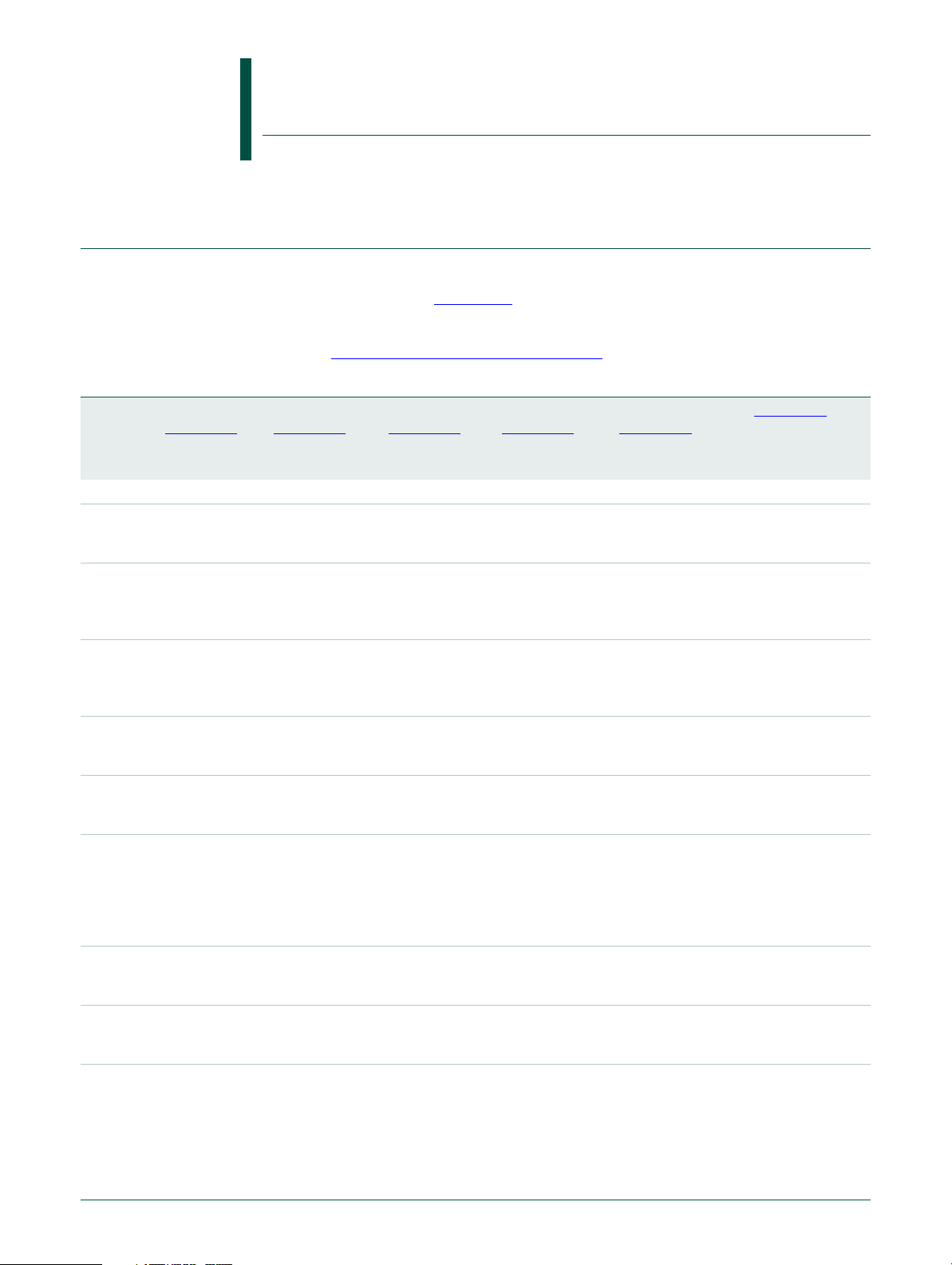

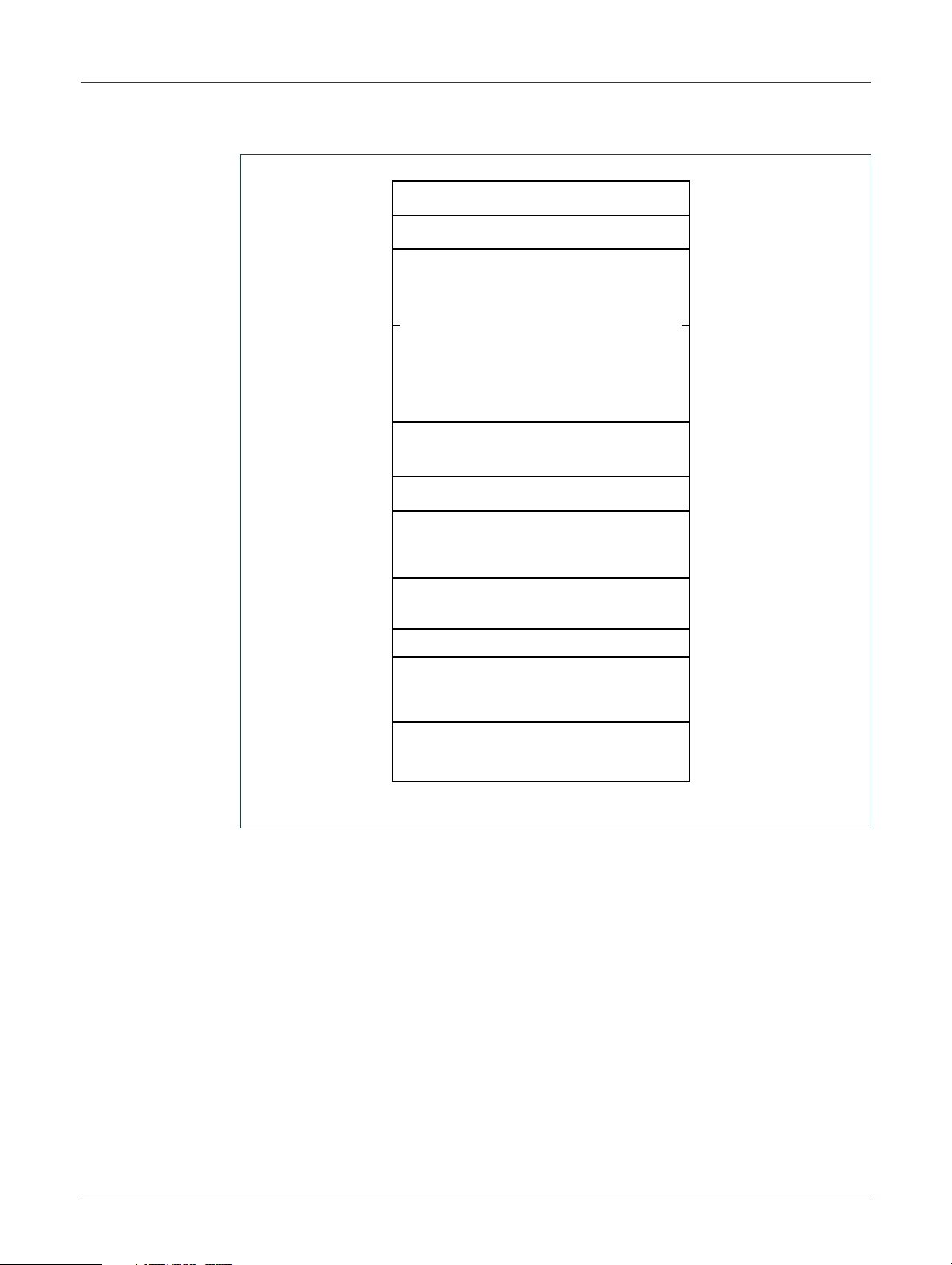

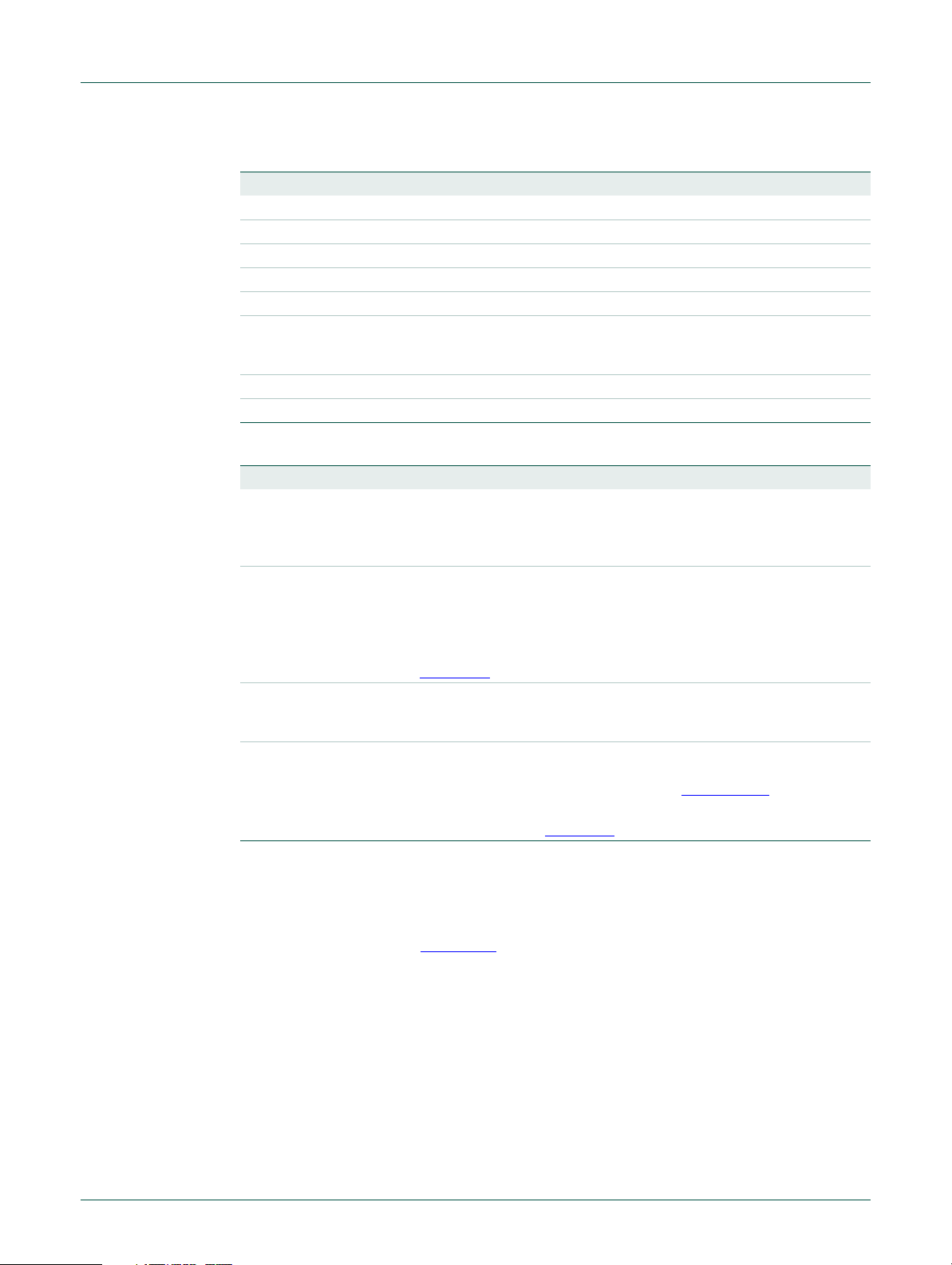

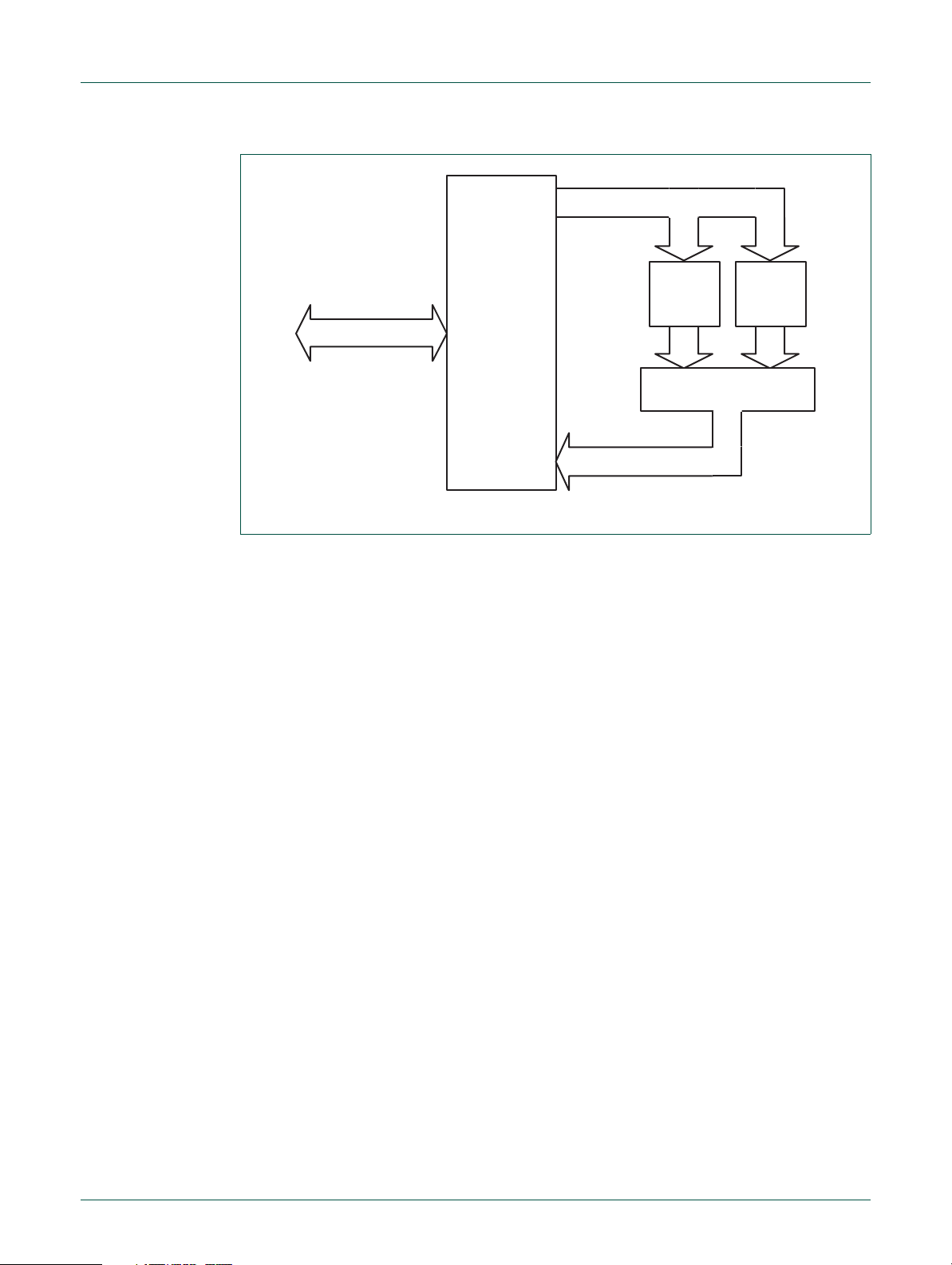

5. Block diagram

UM10114

Chapter 1: Introductory information

Grey-shaded blocks indicate configuration or pinout dependent on part and version number, see Table 1–16.

Fig 1. LPC21xx and LPC22xx block diagram

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 11 of 386

Page 12

NXP Semiconductors

UM10114

Chapter 1: Introductory information

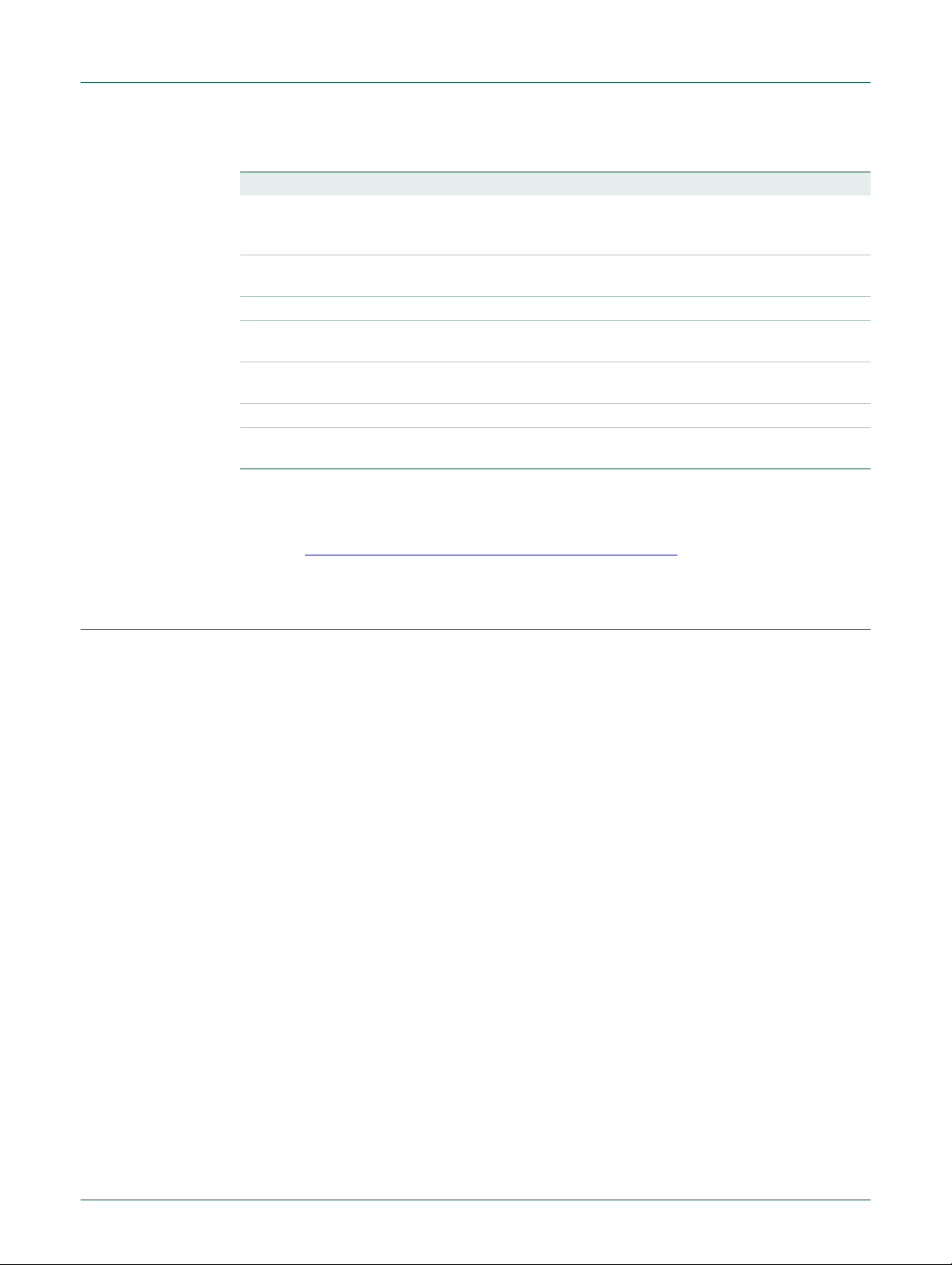

Table 16. LPC21xx/22xx part-specific configuration

Part EMC SRAM Flash Legacy

No-suffix and /00 parts

LPC2109 - 8 kB 64 kB P0/1 - - 1 4/- - LPC2119 - 16 kB 128 kB P0/1 - - 2 4 /- - LPC2129 - 16 kB 256 kB P0/1 - - 2 4 /- - LPC2114 - 16 kB 128 kB P0/1 - - - 4/- - LPC2124 - 16 kB 256 kB P0/1 - - - 4/- - LPC2194 - 16 kB 256 kB P0/1 - - 4 4 /- - LPC2210 yes 16 kB - P0/1/2/3 - - - 4/- - LPC2220 yes 64 kB - P0/1/2/3 P0/1 yes - 8/yes yes yes

LPC2212 yes 16 kB 128 kB P0/1/2/3 - - - 8/- - LPC2214 yes 16 kB 256 kB P0/1/2/3 - - - 8/- - LPC2290 yes 16 kB - P0/1/2/3 - - 2 8/- - LPC2292 yes 16 kB 256 kB P0/1/2/3 - - 2 8/- - LPC2294 yes 16 kB 256 kB P0/1/2/3 - - 4 8/- - -

/01 parts

LPC2109 - 8 kB 64 kB P0/1 P0/1 yes 1 4/yes yes yes

LPC2119 - 16 kB 128 kB P0/1 P0/1 yes 2 4/yes yes yes

LPC2129 - 16 kB 256 kB P0/1 P0/1 yes 2 4/yes yes yes

LPC2114 - 16 kB 128 kB P0/1 P0/1 yes - 4/yes yes yes

LPC2124 - 16 kB 256 kB P0/1 P0/1 yes - 4/yes yes yes

LPC2194 - 16 kB 256 kB P0/1 P0/1 yes 4 4/yes yes yes

LPC2210 yes 16 kB - P0/1/2/3 P0/1 yes - 8/yes yes yes

LPC2212 yes 16 kB 128 kB P0/1/2/3 P0/1 yes - 8/yes yes yes

LPC2214 yes 16 kB 256 kB P0/1/2/3 P0/1 yes - 8/yes yes yes

LPC2290 yes 64 kB - P0/1/2/3 P0/1 yes 2 8/yes yes yes

LPC2292 yes 16 kB 256 kB P0/1/2/3 P0/1 yes 2 8/yes ye s yes

LPC2294 yes 16 kB 256 kB P0/1/2/3 P0/1 yes 4 8/yes ye s yes

GPIO

Fast

GPIO

SSP CAN ADC Enhanced

UART

channels channels/

enhanced

ADC

Enhanced

timers

6. Architectural overview

The LPC21xx/LPC22xx consist of an ARM7TDMI-S CPU with emulation support, the

ARM7 Local Bus for interface to on-chip memory controllers, the AMBA Advanced

High-performance Bus (AHB) for interface to the interrupt controller, and the ARM

Peripheral Bus (APB, a compatible superset of ARM’s AMBA Advanced Peripheral Bus)

for connection to on-chip peripheral functions. The LPC21xx/LPC22xx configures the

ARM7TDMI-S processor in little-endian byte order.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 12 of 386

Page 13

NXP Semiconductors

AHB peripherals are allocated a 2 megabyte range of addresses at the very top of the

4 gigabyte ARM memory space. Each AHB periph eral is allocated a 16 kB address space

within the AHB address space. LPC21xx/LPC22xx peripheral functions (other than the

interrupt controller) are connected to the APB bus. The AHB to APB bridge interfaces the

APB bus to the AHB bus. APB peripherals are also allocated a 2 megabyte range of

addresses, beginning at the 3.5 gigabyte address point. Each APB peripheral is allocated

a 16 kB address space within the APB address space.

The connection of on-chip peripherals to device pins is controlled by a Pin Connect Block

(see Section 8–6

requirements for the use of peripheral functions and pins.

). This must be configured by software to fit specific application

7. ARM7TDMI-S processor

The ARM7TDMI-S is a general purpose 32-bit microprocessor, which offers high

performance and very low power consumption. The ARM architecture is based on

Reduced Instruction Set Computer (RISC) principles, and the instruction set and related

decode mechanism are much simpler than those of microprogrammed Complex

Instruction Set Computers. This simplicity results in a high instruction throughput and

impressive real-time interrupt response from a small and cost-effective processor core.

UM10114

Chapter 1: Introductory information

Pipeline techniques are employed so that all part s of the pro cessing and memory systems

can operate continuously. Typically, while one instruction is being executed, its successor

is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI-S processor also employs a unique architectural strategy known as

THUMB, which makes it ideally suited to high-volume applications with memory

restrictions, or applications where code density is an issue.

The key idea behind THUMB is that of a super-reduced instruction set. Essentially, the

ARM7TDMI-S processor has two instruction sets:

• The standard 32-bit ARM instruction set.

• A 16-bit THUMB instruction set.

The THUMB set’s 16-bit instruction length allows it to approach twice the density of

standard ARM code while retaining most of the ARM’s performance advantage over a

traditional 16-bit processor using 16-bit registers. This is possible because THUMB code

operates on the same 32-bit register set as ARM code.

THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the

performance of an equivalent ARM processor connected to a 16-bit memory system.

The ARM7TDMI-S processor is described in detail in the ARM7TDMI-S data sh eet that

can be found on official ARM website.

8. On-chip flash memory system

The LPC21xx/LPC22xx incorporate a 64 kB to 256 kB flash memory. This memory may

be used for both code and data storage. Programming of the flash memory may be

accomplished in several ways:

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 13 of 386

Page 14

NXP Semiconductors

• using the serial built-in JTAG interface

• using In System Programming (ISP) and UART

• using In Application Programming (IAP) capabilities

The application program, using the IAP functions, may also erase and/or program the

flash while the application is running, allowing a great degree of flexibility for dat a sto rage

field firmware upgrades, etc. The entire flash memory is available for user code because

the boot loader resides in a separate memory location.

The LPC21xx/LPC22xx flash memory provides minimum of 100,000 erase/write cycles

and 20 years of data-retention.

9. On-chip Static RAM (SRAM)

On-chip Static RAM (SRAM) may be used for code and/or data storage. The on-chip

SRAM may be accessed as 8-bits, 16-bits, and 32-bits.

The LPC21xx/LPC22xx SRAM is designed to be accessed as a byte-addressed memory.

Word and halfword accesses to the memory ignore the alignment of the address and

access the naturally-aligned value that is addressed (so a memory access ignores

address bits 0 and 1 for word accesses, and ignores bit 0 for halfword accesses).

Therefore valid reads and writes require data accessed as halfwords to originate from

addresses with address line 0 being 0 (addresses ending with 0, 2, 4, 6, 8, A, C, and E in

hexadecimal notation) and data accessed as words to originate from addresses with

address lines 0 and 1 being 0 (addresses ending with 0, 4, 8, and C in hexadecimal

notation).

UM10114

Chapter 1: Introductory information

The SRAM controller incorporates a write-back buffer in order to prevent CPU stalls

during back-to-back writes. The write-back buffer always holds the last data sent by

software to the SRAM. This data is only written to the SRAM when another write is

requested by software (the data is only written to the SRAM when software does another

write). If a chip reset occurs, actual SRAM contents will not reflect the most recent write

request (i.e. after a "warm" chip reset, the SRAM does not reflect the last wr ite operation).

Any software that checks SRAM contents after reset must take this into account. Two

identical writes to a location guarantee that the data will be present after a Reset.

Alternatively, a dummy write operation before entering idle or power-down mode will

similarly guarantee that the last data written will be present in SRAM after a subsequent

Reset.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 14 of 386

Page 15

UM10114

Chapter 2: LPC21xx/22xx Memory map

Rev. 03 — 2 April 2008 User manual

1. How to read this chapter

Remark: The LPC21xx and LPC22xx contain different memory configurations and

APB/AHB peripherals. See Table 2–17

For an overview of how LPC21xx and LPC22xx parts and versions are described in this

manual, see Section 1–2 “

Table 17. LPC21xx and LPC22xx memory and peripheral configuration

Part EMC

Figure 2–2

addresses size/ addresses size/

No suffix and /01 parts

LPC2109 - 8 kB/

LPC2119 - 16 kB/

LPC2129 - 16 kB/

LPC2114 - 16 kB/

LPC2124 - 16 kB/

LPC2194 - 16 kB/

LPC2210 0x8000 0000 -

0x83FF FFFF

LPC2220 0x8000 0000 -

0x83FF FFFF

LPC2212 0x8000 0000 -

0x83FF FFFF

SRAM

Figure 2–2

0x4000 0000 0x4000 1FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

16 kB/

0x4000 0000 0x4000 2FFF

64 kB/

0x4001 0000 0x4000 FFFF

16 kB/

0x4000 0000 0x4000 2FFF

How to read this manual”.

Flash

Figure 2–2

addresses

64 kB/

0x0000 0000 0x0000 FFFF

128 kB/

0x0000 0000 0x0001 FFFF

256 kB/

0x0000 0000 0x0003 FFFF

128 kB/

0x0000 0000 0x0001 FFFF

256 kB/

0x0000 0000 0x0003 FFFF

256 kB/

0x0000 0000 0x0003 FFFF

-- --

- 0x3FFF C000 -

128 kB/

0x0000 0000 0x0001 FFFF

for part-specific memory and peripherals.

Fast GPIO

Figure 2–2

addresses APB base addresses

- - 0xE003 8000 -

- - 0xE003 8000 -

- - 0xE003 8000 -

---

---

- - 0xE003 8000 -

0x3FFF FFFF

---

SSP

Table 2–18

0xE005 C000 -

CAN Table 2–18

0xE004 0000

CAN1: 0xE004 4000

0xE004 0000

CAN1:0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

CAN3: 0xE004 C000

CAN4: 0xE005 0000

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 15 of 386

Page 16

NXP Semiconductors

Table 17. LPC21xx and LPC22xx memory and peripheral configuration

Part EMC

Figure 2–2

addresses size/ addresses size/

LPC2214 0x8000 0000 -

0x83FF FFFF

LPC2290 0x8000 0000 -

0x83FF FFFF

LPC2292 0x8000 0000 -

0x83FF FFFF

LPC2294 0x8000 0000 -

0x83FF FFFF

/01 parts

LPC2109 - 8 kB/

LPC2119 - 16 kB/

LPC2129 - 16 kB/

LPC2114 - 16 kB/

LPC2124 - 16 kB/

LPC2194 - 16 kB/

LPC2210 0x8000 0000 -

0x83FF FFFF

LPC2212 0x8000 0000 -

0x83FF FFFF

SRAM

Figure 2–2

16 kB/

0x4000 0000 0x4000 2FFF

16 kB/

0x4000 0000 0x4000 2FFF

16 kB/

0x4000 0000 0x4000 2FFF

16 kB/

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 1FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

0x4000 0000 0x4000 2FFF

16 kB/

0x4000 0000 0x4000 2FFF

16 kB/

0x4000 0000 0x4000 2FFF

Flash

Figure 2–2

addresses

256 kB/

0x0000 0000 0x0003 FFFF

- - - 0xE003 8000 -

256 kB/

0x0000 0000 0x0003 FFFF

256 kB/

0x0000 0000 0x0003 FFFF

64 kB/

0x0000 0000 0x0000 FFFF

128 kB/

0x0000 0000 0x0001 FFFF

256 kB/

0x0000 0000 0x003 FFFF

128 kB/

0x0000 0000 0x0001 FFFF

256 kB/

0x0000 0000 0x003 FFFF

256 kB/

0x0000 0000 0x0003 FFFF

- 0x3FFF C000 -

128 kB/

0x0000 0000 0x0001 FFFF

Fast GPIO

Figure 2–2

addresses APB base addresses

---

- - 0xE003 8000 -

- - 0xE003 8000 -

0x3FFF C000 0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

UM10114

Chapter 2: LPC21xx/22xx Memory map

SSP

Table 2–18

0xE005 C000 0xE003 8000 -

0xE005 C000 0xE003 8000 -

0xE005 C000 0xE003 8000 -

0xE005 C000 -

0xE005 C000 -

0xE005 C000 0xE003 8000 -

0xE005 C000 -

0xE005 C000 -

CAN Table 2–18

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

CAN3: 0xE004 C000

CAN4: 0xE005 0000

0xE004 0000

CAN1: 0xE004 4000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

CAN3: 0xE004 C000

CAN4: 0xE005 0000

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 16 of 386

Page 17

NXP Semiconductors

Table 17. LPC21xx and LPC22xx memory and peripheral configuration

Part EMC

Figure 2–2

addresses size/ addresses size/

LPC2214 0x8000 0000 -

0x83FF FFFF

LPC2290 0x8000 0000 -

0x83FF FFFF

LPC2292 0x8000 0000 -

0x83FF FFFF

LPC2294 0x8000 0000 -

0x83FF FFFF

SRAM

Figure 2–2

16 kB/

0x4000 0000 0x4000 2FFF

64 kB/

0x4001 0000 0x4000 FFFF

16 kB/

0x4000 0000 0x4000 2FFF

16 kB/

0x4000 0000 0x4000 2FFF

Flash

Figure 2–2

addresses

256 kB/

0x0000 0000 0x0003 FFFF

- 0x3FFF C000 -

256 kB/

0x0000 0000 0x0003 FFFF

256 kB/

0x0000 0000 0x0003 FFFF

Fast GPIO

Figure 2–2

addresses APB base addresses

0x3FFF C000 0x3FFF FFFF

0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

0x3FFF C000 0x3FFF FFFF

UM10114

Chapter 2: LPC21xx/22xx Memory map

SSP

Table 2–18

0xE005 C000 -

0xE005 C000 0xE003 8000 -

0xE005 C000 0xE003 8000 -

0xE005 C000 0xE003 8000 -

CAN Table 2–18

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

0xE004 0000

CAN1: 0xE004 4000

CAN2: 0xE004 8000

CAN3: 0xE004 C000

CAN4: 0xE005 0000

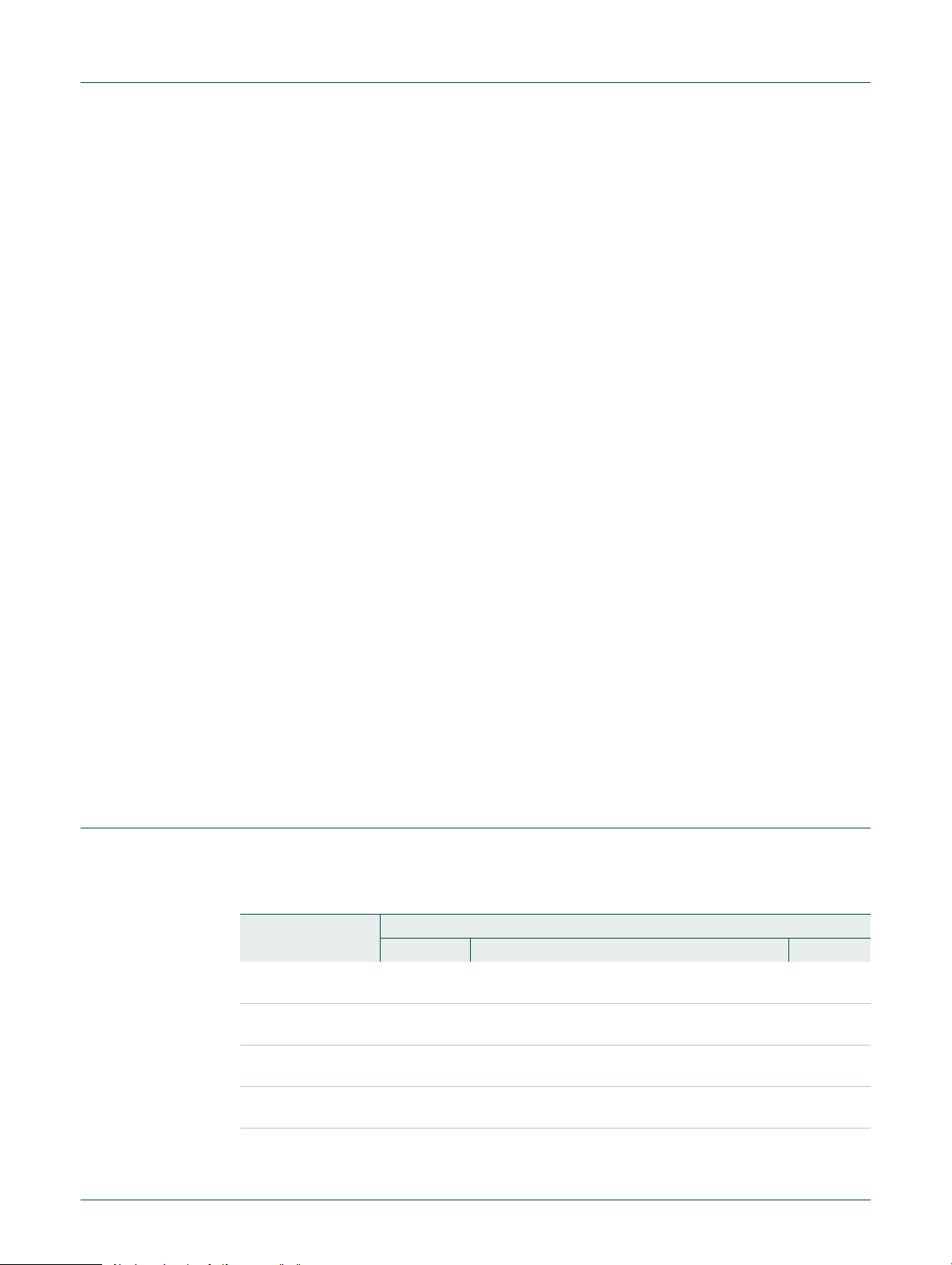

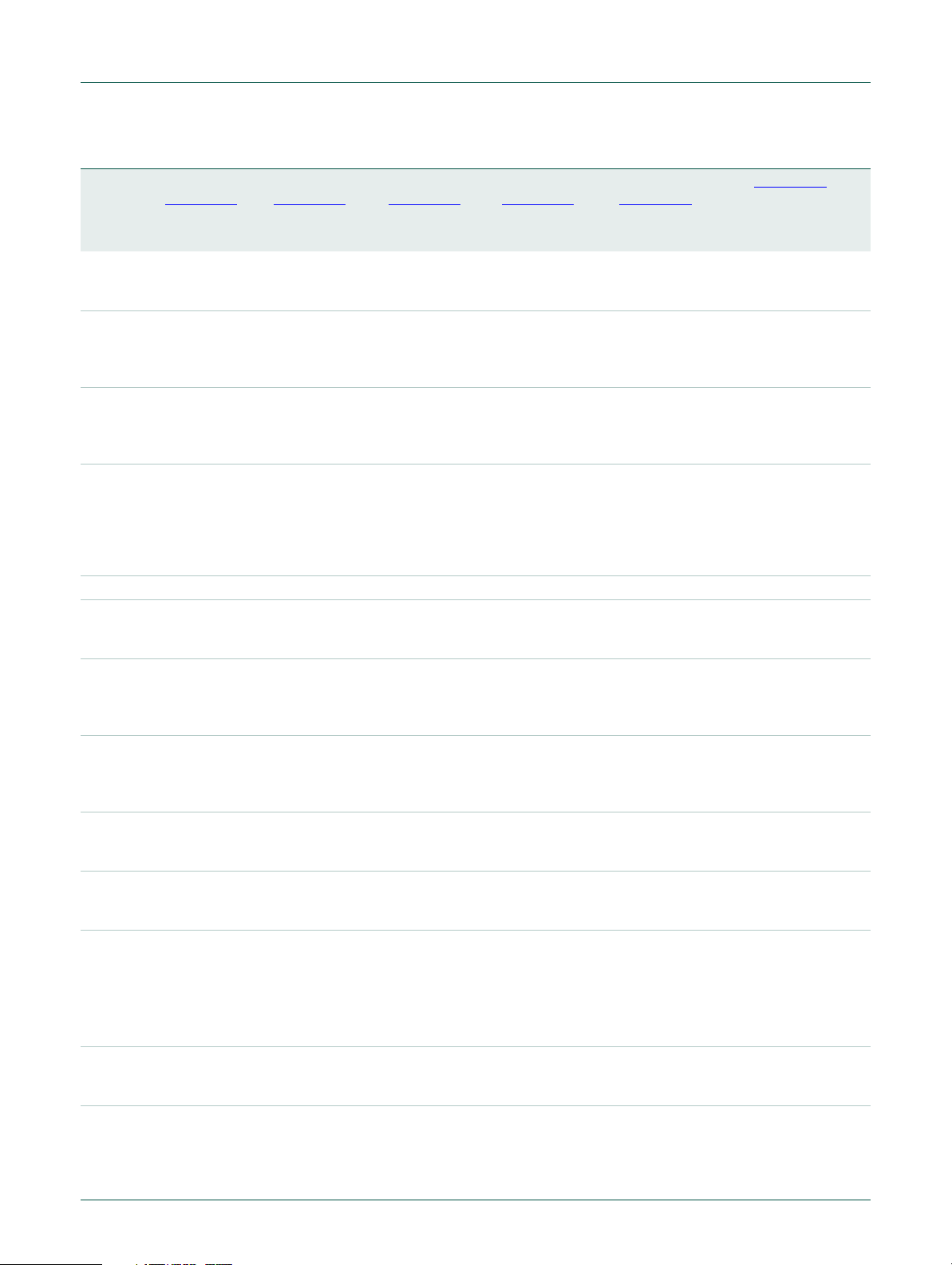

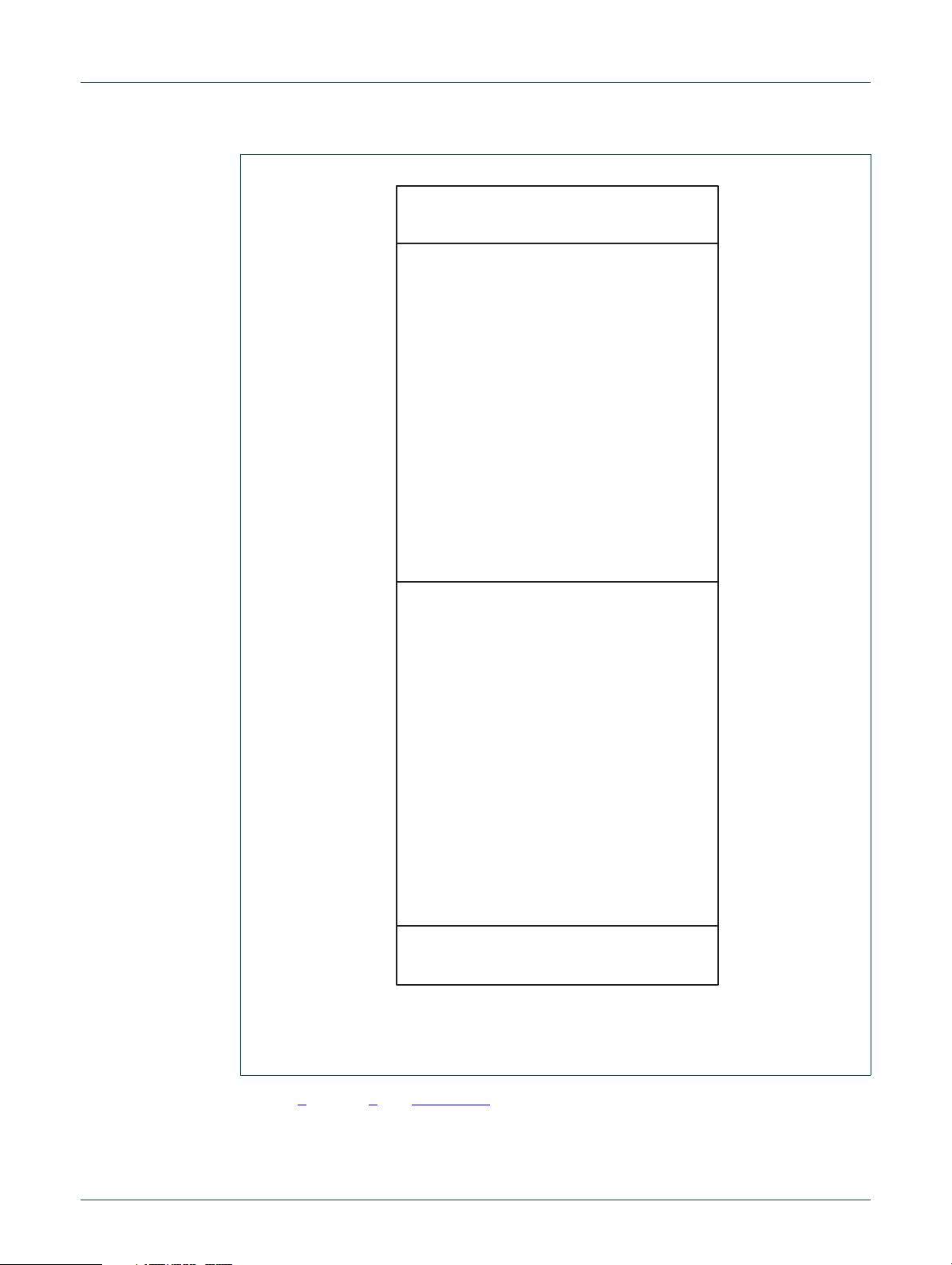

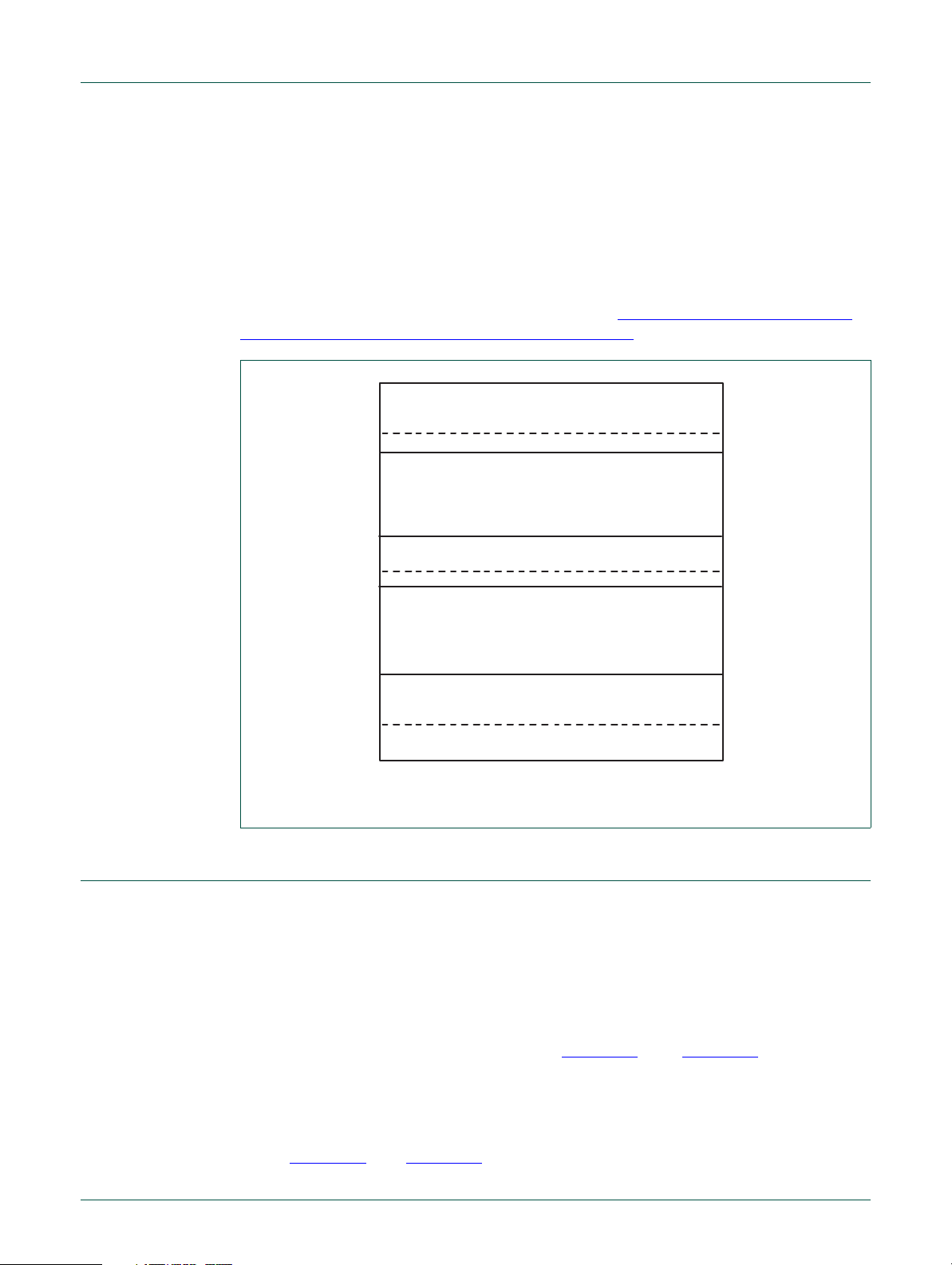

2. Memory maps

The LPC21xx and LPC22xx incorporate several distinct memory regions, shown in the

following figures. Figure 2–2

user program viewpoint following reset. The interrupt vector area supports address

remapping, which is described later in this section.

shows the overall map of the entire address space from the

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 17 of 386

Page 18

NXP Semiconductors

AHB PERIPHERALS

APB PERIPHERALS

RESERVED ADDRESS SPACE

EXTERNAL MEMORY BANKS 0 TO 4

BOOT BLOCK (RE-MAPPED FROM

ON-CHIP FLASH MEMORY)

RESERVED ADDRESS SPACE

UP TO 64 kB ON-CHIP STATIC RAM

FAST GPIO REGISTERS

RESERVED ADDRESS SPACE

UP TO 256 kB ON-CHIP FLASH MEMORY

0xFFFF FFFF

0xF000 0000

0xEFFF FFFF

0xE000 0000

0xC000 0000

0xDFFF FFFF

0x8000 0000

0x7FFF FFFF

0x8400 0000

0x83FF FFFF

0x7FFF E000

0x7FFF DFFF

0x4001 0000

0x4000 FFFF

0x4000 0000

0x3FFF FFFF

0x3FFF C000

0x0004 0000

0x0003 FFFF

4.0 GB

3.75 GB

3.5 GB

3.0 GB

2.0 GB

1.0 GB

0.0 GB

0x0000 0000

UM10114

Chapter 2: LPC21xx/22xx Memory map

Fig 2. LPC21xx and LPC22xx system memory map

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 18 of 386

Page 19

NXP Semiconductors

RESERVED

RESERVED

0xF000 0000

0xEFFF FFFF

APB PERIPHERALS

0xE020 0000

0xE01F FFFF

0xE000 0000

AHB PERIPHERALS

0xFFFF FFFF

0xFFE0 0000

0xFFDF FFFF

3.75 GB

3.5 GB

3.5 GB + 2 MB

4.0 GB - 2 MB

4.0 GB

UM10114

Chapter 2: LPC21xx/22xx Memory map

AHB section is 128 x 16 kB blocks (totaling 2 MB).

APB section is 128 x 16 kB blocks (totaling 2MB).

Fig 3. Peripheral memory map

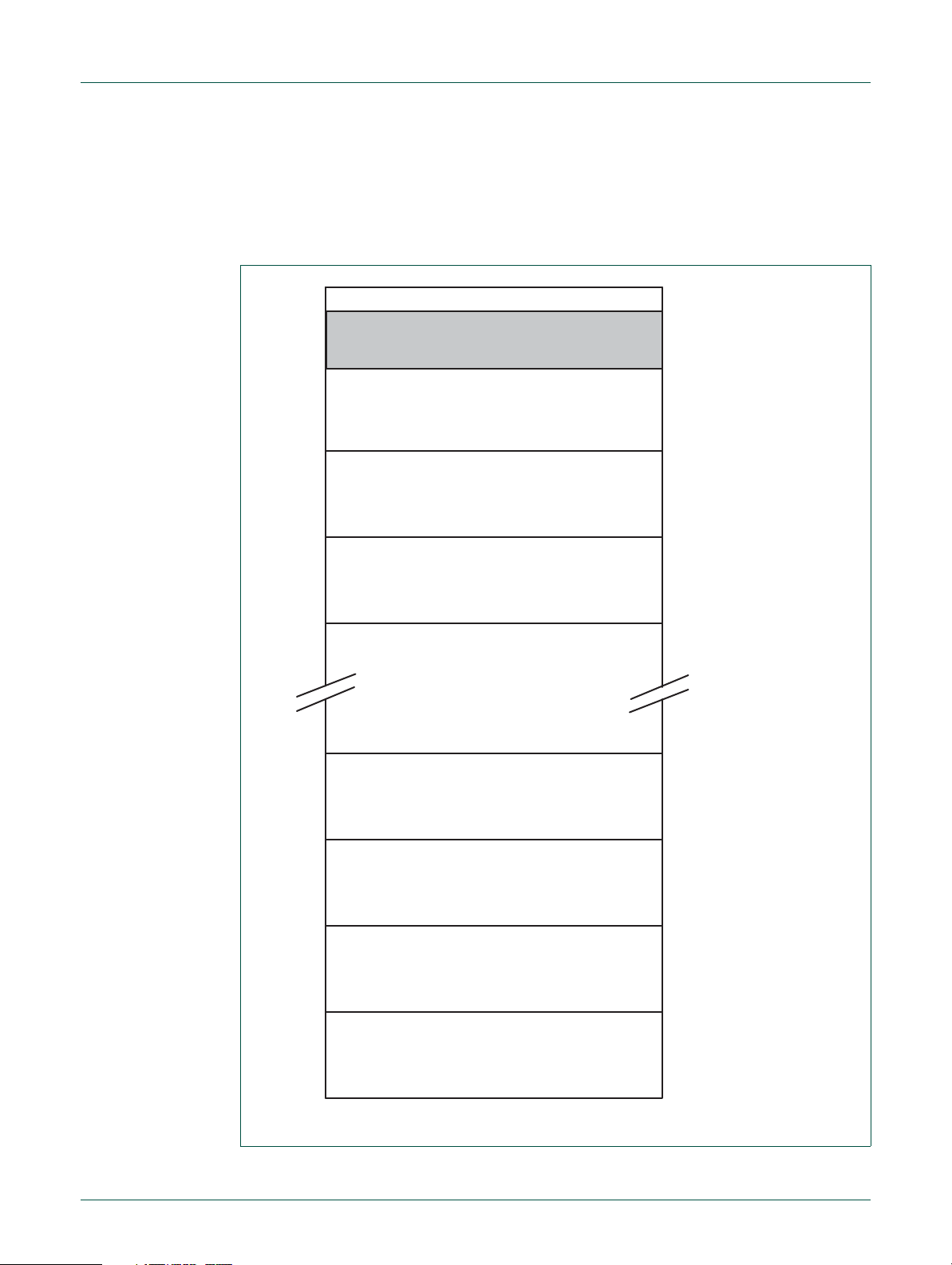

Figures 3 through 4 and Table 2–18 show different views of the peripheral address space.

Both the AHB and APB peripheral areas are 2 megabyte sp aces which are divided up into

128 peripherals. Each peripheral space is 16 kilobytes in size. This allows simplifying the

address decoding for each peripheral. All peripheral register addresses are word aligned

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 19 of 386

Page 20

NXP Semiconductors

VECTORED INTERRUPT CONTROLLER

(AHB PERIPHERAL #0)

0xFFFF F000 (4G - 4K)

0xFFFF C000

0xFFFF 8000

(AHB PERIPHERAL #125)

(AHB PERIPHERAL #124)

(AHB PERIPHERAL #3)

(AHB PERIPHERAL #2)

(AHB PERIPHERAL #1)

(AHB PERIPHERAL #126)

0xFFFF 4000

0xFFFF 0000

0xFFE1 0000

0xFFE0 C000

0xFFE0 8000

0xFFE0 4000

0xFFE0 0000

NOT USED

NOT USED

NOT USED

EXTERNAL MEMORY CONTROLLER

NOT USED

NOT USED

(to 32-bit boundaries) regardless of their size. This eliminates the need for byte lane

mapping hardware that would be required to allow byte (8-bit) or half-wor d (16-bit)

accesses to occur at smaller boundaries. An implication of this is that word and half-word

registers must be accessed all at once. For example, it is not possible to read or write the

upper byte of a word register separately.

UM10114

Chapter 2: LPC21xx/22xx Memory map

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 20 of 386

Fig 4. AHB peripheral map

Page 21

NXP Semiconductors

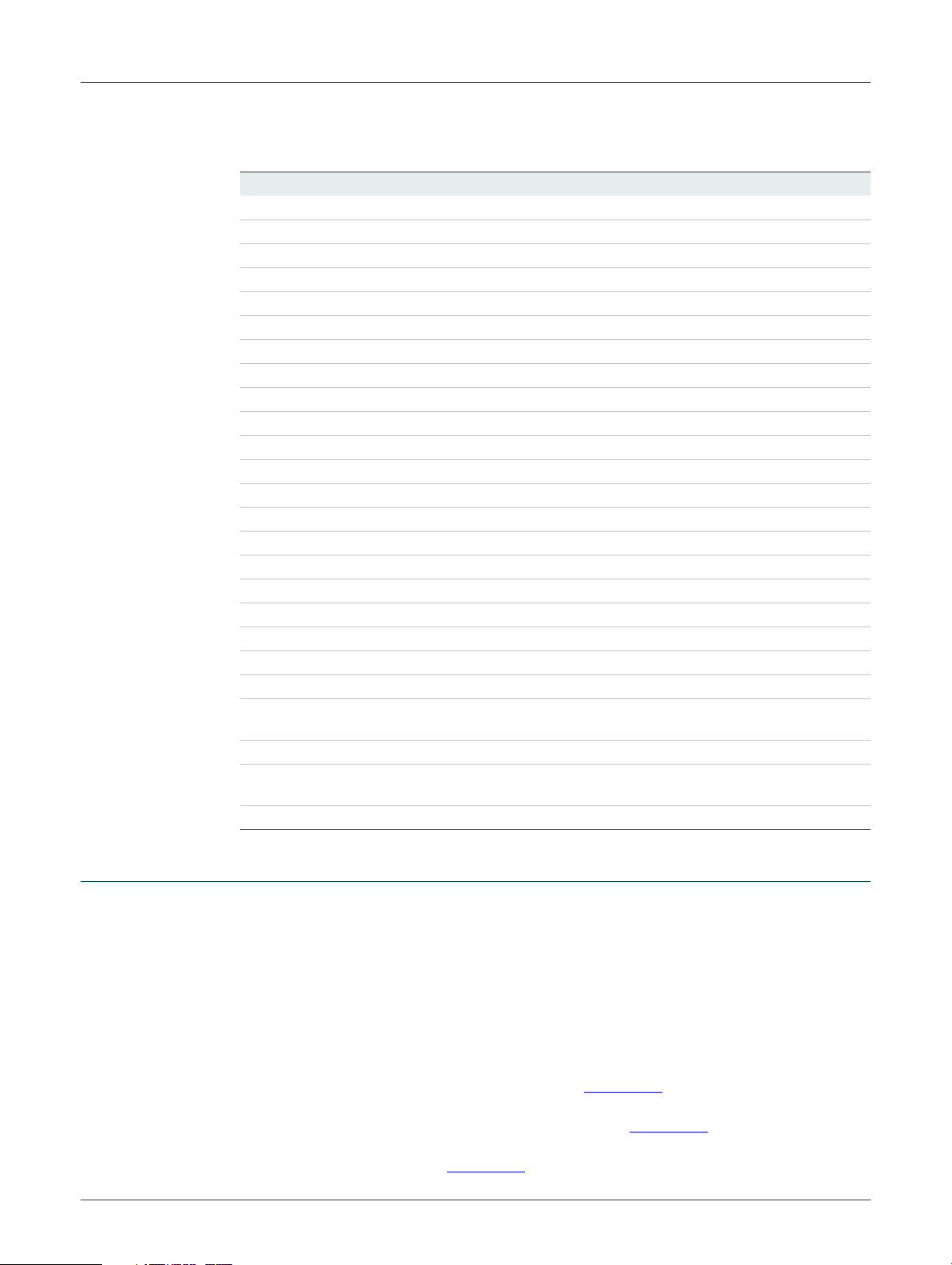

Table 18. APB peripheries and base addr esses

APB peripheral Base address Peripheral name

0 0xE000 0000 Watchdog timer

1 0xE000 4000 Timer 0

2 0xE000 8000 Timer 1

3 0xE000 C000 UART0

4 0xE001 0000 UART1

5 0xE001 4000 PWM

6 0xE001 8000 Not used

7 0xE001 C000 I

8 0xE002 0000 SPI0

9 0xE002 4000 RTC

10 0xE002 8000 GPIO

11 0xE002 C000 Pin connect block

12 0xE003 0000 SPI1

13 0xE003 4000 10 bit ADC

14 0xE003 8000 CAN Acceptance Filter RAM

15 0xE003 C000 CAN Acceptance Filter Registers

16 0xE004 0000 CAN Common Registers

17 0xE004 4000 CAN Controller 1

18 0xE004 8000 CAN Controller 2

19 0xE004 C000 CAN Controller 3

20 0xE005 0000 CAN Controller 4

21 - 22 0xE005 4000

23 0xE005 C000 SSP

24 - 126 0xE006 0000 -

127 0xE01F C000 System Control Block

0xE005 8000

0xE01F 8000

2

C

Not used

Not used

UM10114

Chapter 2: LPC21xx/22xx Memory map

3. LPC21xx and LPC22xx memory re-mapping and boot block

3.1 Memory map concepts and operating modes

The basic concept on the LPC21xx and LPC22xx is that each memory area has a

"natural" location in the memory map. This is the address range for which code r esiding in

that area is written. The bulk of each memory space remains permanently fixed in the

same location, eliminating the need to have portions of the code designed to run in

different address ranges.

Because of the location of the interrupt vectors on the ARM7 processor (at addresses

0x0000 0000 through 0x0000 001C, as shown in Table 2–19

Boot Block and SRAM spaces need to be re-mapped in order to allow alternative uses of

interrupts in the different operating modes described in Table 2–20

interrupts is accomplished via the Memory Mapping Control features. To select a specific

memory mapping mode, see Table 6–62

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 21 of 386

.

below), a small portion of the

. Re-mapping of the

Page 22

NXP Semiconductors

Table 19. ARM exception vector locations

Address Exception

0x0000 0000 Reset

0x0000 0004 Undefined Instruction

0x0000 0008 Software Interrupt

0x0000 000C Prefetch Abort (instruction fetch memory fault)

0x0000 0010 Data Abort (data access memory fault)

0x0000 0014 Reserved

0x0000 0018 IRQ

0x0000 001C FIQ

Table 20. LPC21xx and LPC22xx memory mapping modes

Mode Activation Usage

Boot

Loader

mode

User

Flash

mode

User RAM

mode

User

External

mode

Hardware

activation by

any Reset

Software

activation by

Boot code

Software

activation by

User program

Activated by

BOOT1:0

pins

UM10114

Chapter 2: LPC21xx/22xx Memory map

Note: Identified as reserved in ARM documentation.

The boot loader always executes after any reset. The boot block

interrupt vectors are mapped to the bottom of memory to allow

handling exceptions and using interrupts during the boot loading

process.

Activated by boot loader when a valid user program signature is

recognized in memory and boot loader operation is not forced.

Interrupt vectors are not re-mapped and are found in the bottom of the

flash memory.

Remark: This mode is not available in flashless parts (see

Table 2–17

Activated by a user program as desired. Interrupt vectors are

re-mapped to the bottom of the Static RAM.

Activated by the boot loader when one or both BOOT pins are LOW at

the end of RESET LOW. Interrupt vectors are re-mapped from the

bottom of the external memory map (see Section 8–6.5

Remark: This mode is available for parts with external memory

controller only (see Table 2–17

).

).

).

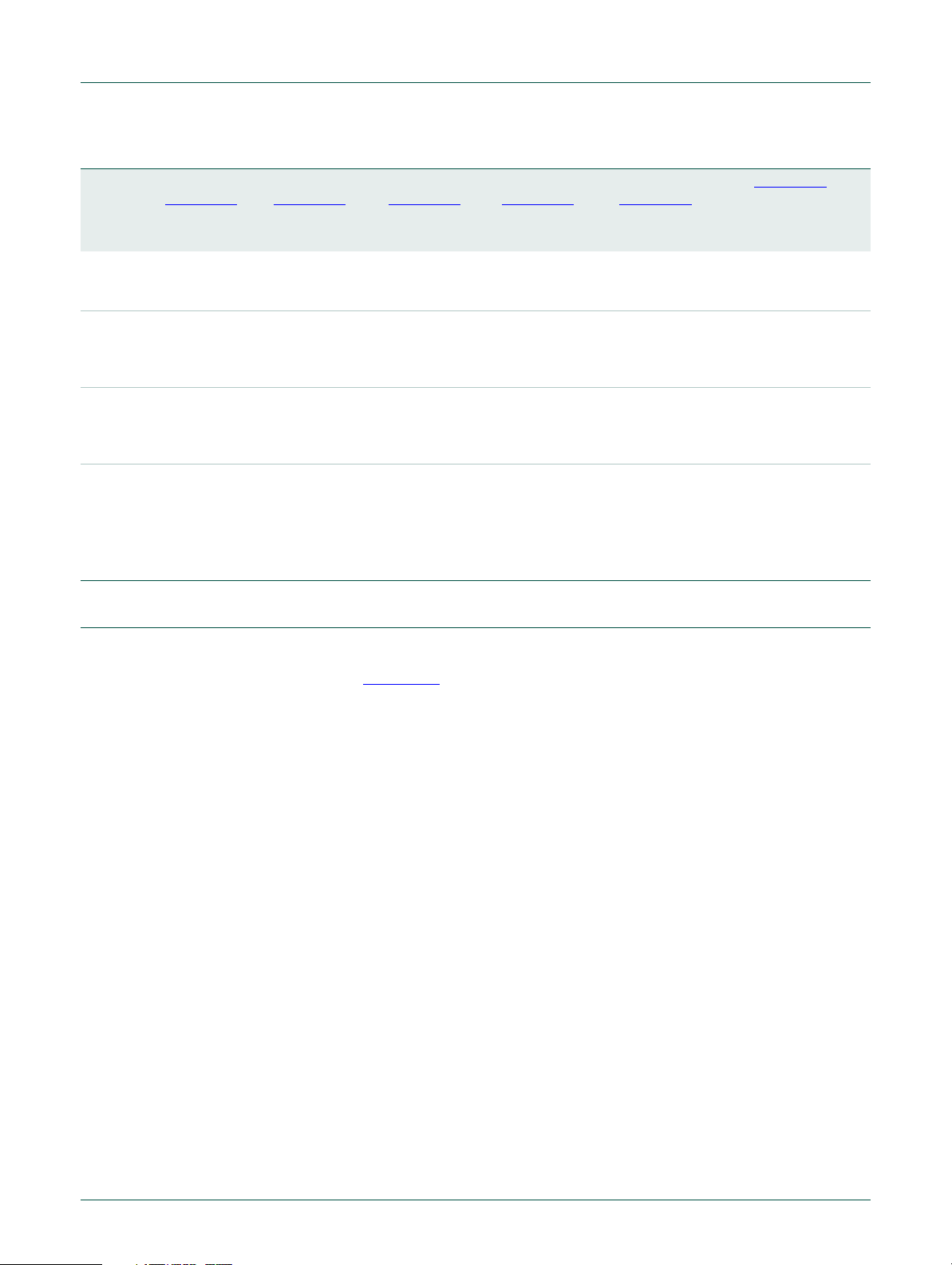

3.2 Memory re-mapping

In order to allow for compatibility with future derivatives, the entire boot block is mapped to

the top of the on-chip memory space. Memory spaces other tha n th e int er ru pt vecto r s

remain in fixed locations. Figure 2–5

defined above.

The portion of memory that is re-mapped to allow interrupt processing in different modes

includes the interrupt vector area (32 bytes) and an additional 32 bytes, for a total of

64 bytes. The re-mapped code locations overlay addresses 0x0000 0000 through

0x0000 003F. The vector contained in the SRAM, external memory, and boot block must

contain branches to the actual interrupt handlers or to other instructions that accomplish

the branch to the interrupt handlers.

There are two reasons this configuration was chosen:

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 22 of 386

shows the on-chip memory mapping in the modes

Page 23

NXP Semiconductors

8 kB BOOT BLOCK

ON-CHIP FLASH MEMORY

0.0 GB

ACTIVE INTERRUPT VECTORS

FROM BOOT BLOCK

0x7FFF FFFF

2.0 GB - 8 kB

2.0 GB

(BOOT BLOCK INTERRUPT VECTORS)

0x0000 0000

0x7FFF E000

(SRAM INTERRUPT VECTORS)

ON-CHIP SRAM

RESERVED ADDRESS SPACE

1.0 GB

0x4000 0000

RESERVED ADDRESS SPACE

0x4003 FFFF

0x4000 4000

1. Minimize the need for the SRAM and Boot Block vectors to deal with arbitrary

2. To provide space to store constants for jumping beyond the range of single word

Re-mapped memory areas, including the boot block and interrupt vectors, continue to

appear in their original location in addition to the re-mapped address.

UM10114

Chapter 2: LPC21xx/22xx Memory map

boundaries in the middle of code space.

branch instructions.

Details on re-mapping and examples can be found in Section 6–8.1 “

control register (MEMMAP - 0xE01F C040)” on page 68.

Memory Mapping

Fig 5. Map of lower memory is showing re-mapped and re-mappable areas for a part

with on-chip flash memory

4. Prefetch Abort and Data Abort Exceptions

The LPC21xx and LPC22xx generate the appropriate bus cycle abort exception if an

access is attempted for an address that is in a reserved or unassigned address region.

The regions are:

• Areas of the memory map that are not implemented for a specific ARM derivative. Fo r

the LPC21xx and LPC22xx, those areas are:

– Address space between the on-chip non-volatile memory and On-Chip SRAM,

labelled "Reserved Address Space" in Figure 2–2

address range from 0x0002 0000 to 0x3FFF FFFF for the 128 kB flash device and

0x0004 0000 to 0x3FFF FFFF for the 256 kB flash device.

– Address space between on-chip SRAM and the boot block. This is the address

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 23 of 386

range from 0x4000 4000 to 0x7FFF DFFF, labelled "Reserved Address Space" in

Figure 2–2

, and Figure 2–5.

, and Figure 2–5. This is an

Page 24

NXP Semiconductors

• Unassigned AHB peripheral spaces. See Figure 2–4.

• Unassigned APB peripheral spaces. See Table 2–18.

For these areas, both attempted data acce ss and in struction fetch genera te an exception.

In addition, a Prefetch Abort exception is generated for any instruction fetch that maps to

an AHB or APB peripheral address.

Within the address space of an existing APB peripheral, a data abort exception is not

generated in response to an access to an undefined address. Address decoding within

each peripheral is limited to that needed to distinguish defined registers within the

peripheral itself. For example, an access to address 0xE000 D000 (an undefined address

within the UART0 space) may result in an access to the register defined at address

0xE000 C000. Details of such address aliasing within a peripheral space are not defined

in the LPC21xx and LPC22xx documentation and are not a su pp or te d fe at ur e.

UM10114

Chapter 2: LPC21xx/22xx Memory map

– Address space between the top of the boot block and the APB peripheral space,

except space used for external memory (LPC2292/2294 only). This is the address

range from 0x8000 0000 to 0xDFFF FFFF, labelled "Reserved Address Space" in

Figure 2–2

– Reserved regions of the AHB and APB spaces. See Figure 2–3

, and Figure 2–5.

and Table 2–18.

Note: The ARM core stores the Prefetch Abort flag along with the associated instruction

(which will be meaningless) in the pipeline and processes the abort only if an attempt is

made to execute the instruction fetched from the illegal address. This prevents accidental

aborts that could be caused by prefetches that occur when code is executed very near a

memory boundary.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 24 of 386

Page 25

UM10114

Chapter 3: LPC21xx/22xx Memory Accelerator Module (MAM)

Rev. 03 — 2 April 2008 User manual

1. How to read this chapter

The MAM is identical for all parts with flash memory. It is available in the following parts:

• LPC2109, LPC2119, LPC2129, and /01 versions

• LPC2114, LPC2124, and /01 versions

• LPC2194 and LPC2194/01

• LPC2212, LPC2214, and /01 versions

• LPC2292, LPC2294, and /01 versions

For an overview of how LPC21xx and LPC22xx parts and versions are described in this

manual, see Section 1–2 “

How to read this manual”.

2. Introduction

3. Operation

The MAM block in the LPC21xx and LPC22xx maximizes the performance of the ARM

processor when it is running code in flash memory using a dual flash bank.

Simply put, the Memory Accelerator Module (MAM) attempts to have the next ARM

instruction that will be needed in its latches in time to prevent CPU fetch stalls. The

method used is to split the flash memory into two banks, each capable of independent

accesses. Each of the two flash banks has its own prefetch buffer a nd branch trail buffer.

The branch trail buffers for the two banks capture two 128-bit lines of flash data when an

instruction fetch is not satisfied by either the pref etc h bu ffer or branch trail bu ffer for its

bank, and for which a prefetch has not been initia te d. Each pr e fet ch buffer captu res one

128-bit line of instructions from its flash bank at the conclusion of a prefetch cycle initiated

speculatively by the MAM.

Each 128 bit value includes four 32-bit ARM instructions or eight 16-bit Thumb

instructions. During sequential code execution, typically one flash bank contains or is

fetching the current instruction and the entir e flash line that contains it. The other bank

contains or is prefetching the next sequential code line. After a code line delivers its last

instruction, the bank that contained it begins to fetch the next line in that bank.

Timing of flash read operations is programmable and is described in Section 3–9

.

Branches and other program flow changes cause a break in the sequential flow of

instruction fetches described above. When a backward branch occurs, there is a distinct

possibility that a loop is being executed. In this case the branch trail buffers may already

contain the target instruction. If so, execution continues without the need for a flash read

cycle. For a forward branch, there is also a chance that the new address is already

contained in one of the prefetch buffers. If it is, the branch is again taken with no delay.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 25 of 386

Page 26

NXP Semiconductors

When a branch outside the contents of the branch trail and prefetch buffers is taken, one

flash access cycle is needed to load the branch trail buffers. Subsequently, there will

typically be no further fetch delays until another such “Instruction Miss” occurs.

The flash memory controller detects data accesses to the flash memo ry and uses a

separate buffer to store the results in a manner similar to that used during code fetches.

This allows faster access to data if it is accessed sequentially. A single line buffer is

provided for data accesses, as opposed to the two buf fers per flash bank tha t are provided

for code accesses. There is no prefetch function for data accesses.

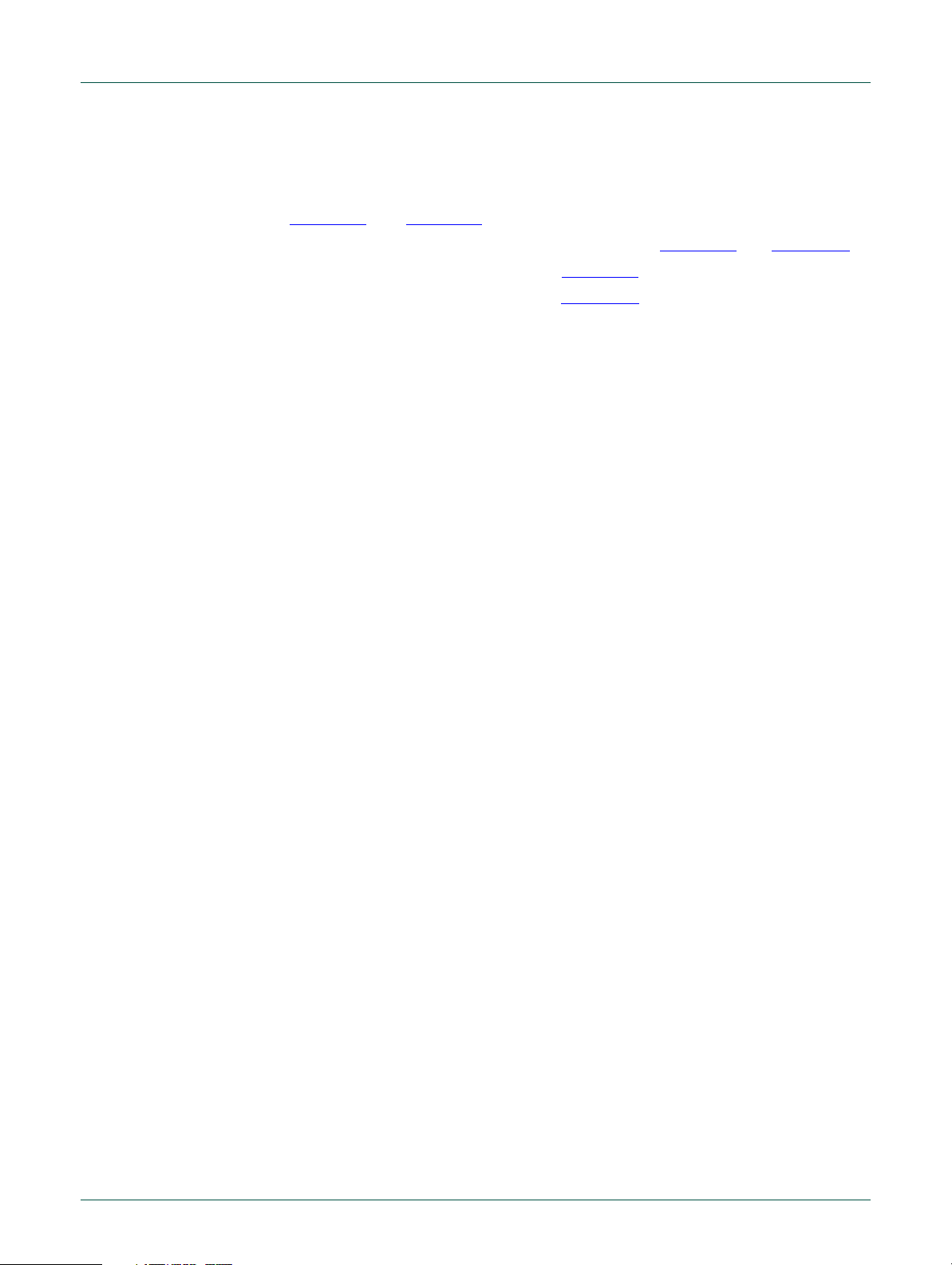

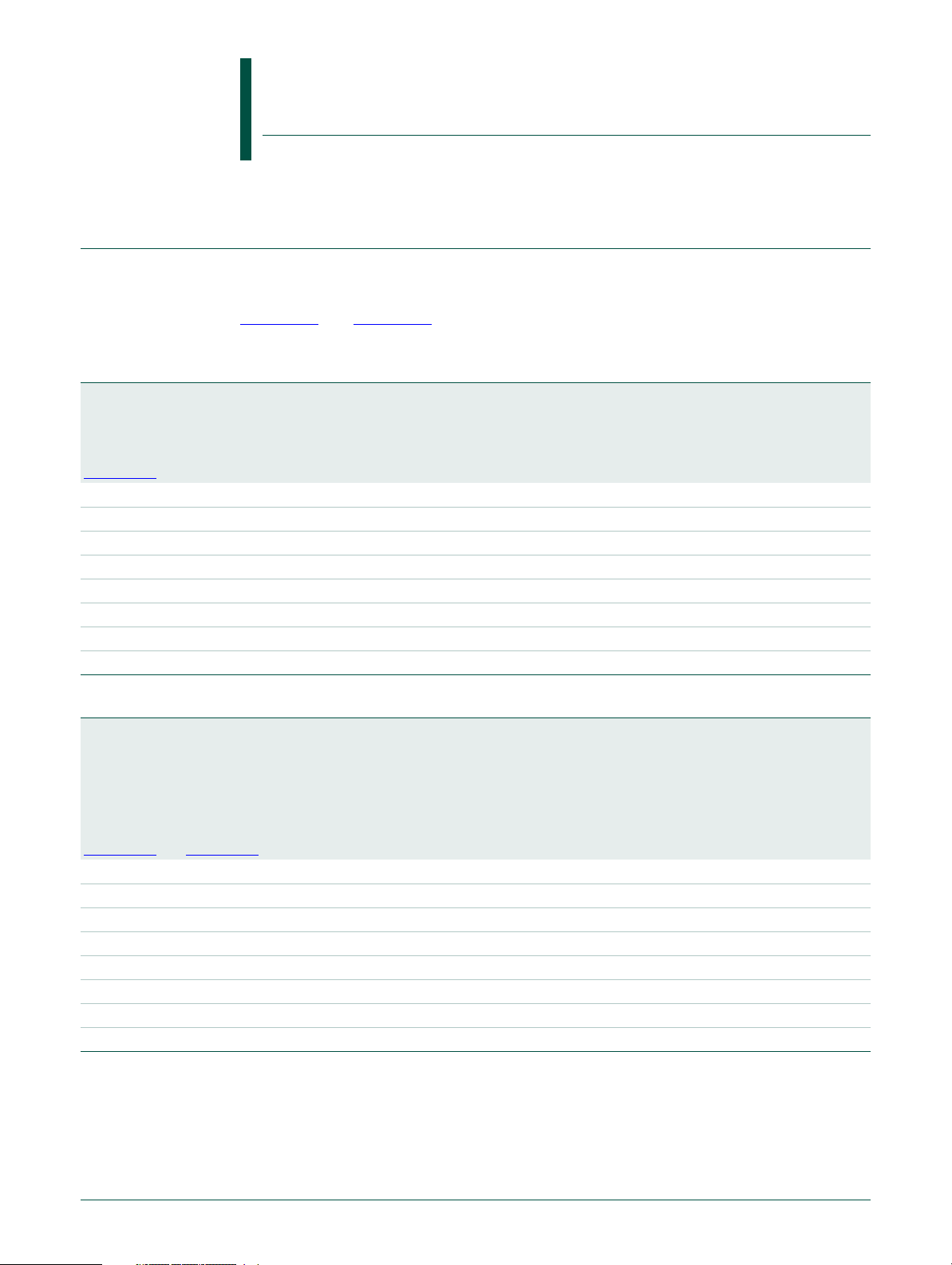

4. MAM blocks

The Memory Accelerator Module is divided into several functional blocks:

• A flash address latch for each bank: An incrementor function is associated with the

• Two flash memory banks

• Instruction latches, data latches, address comparison latches

• Control and wait logic

UM10114

Chapter 3: LPC21xx/22xx Memory Accelerator Module (MAM)

bank 0 flash address latch.

Figure 3–6

paths.

In the following descriptions, the term “fetch” applies to an explicit flash read request from

the ARM. “Pre-fetch” is used to denote a flash read of instructions beyond the current

processor fetch address.

shows a simplified block diagram of the Memory Accelerator Module dat a

4.1 Flash memory bank

There are two banks of flash memory in order to allow parallel access and eliminate

delays for sequential access.

Flash programming operations are not controlled by the MAM but are handled as a

separate function. A “boot block” sector contains flash programming algorithms that may

be called as part of the application program and a loader that may be run to allow serial

programming of the flash memory.

The flash memories are wired so that each sector exists in both banks and that a sector

erase operation acts on part of both banks simultaneously. In effect, the existence of two

banks is transparent to the programming functions.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 26 of 386

Page 27

NXP Semiconductors

ARM LOCAL BUS

BUS

INTERFACE

FLASH

MEMORY

BANK 0

FLASH

MEMORY

BANK 1

BANK SELECTION

MEMORY DATA

Fig 6. Simplified block diagram of the Memory Accelerator Module (MAM)

UM10114

Chapter 3: LPC21xx/22xx Memory Accelerator Module (MAM)

4.2 Instruction latches and data latches

Code and data accesses are treated separately by the Memory Accelerator Mod ule.There

are two sets of 128-bit instruction latches and 12-bit compar ison address latches

associated with each flash bank. One of the two sets, called the branch trail buffer, holds

the data and comparison address for that bank from the last instruction miss. The other

set, called the prefetch buffer, holds the data and comparison address from prefetches

undertaken speculatively by the MAM. Each instruction latch ho lds 4 words of code (4

ARM instructions, or 8 Thumb instructions).

Similarly, there is a 128-bit data latch and 13-bit data address latch, that are used during

data cycles. This single set of latches is shared by both flash bank s. Each data access

that is not in the data latch causes a flash fetch of 4 words of data, which are captured in

the data latch. This speeds up sequential data operations, but has little or no effect on

random accesses.

4.3 Flash programming Issues

Since the flash memory does not allow access during programming and erase operations,

it is necessary for the MAM to force the CPU to wait if a memory access to a flash address

is requested while the flash module is busy . Un der some conditions, this delay could result

in a Watchdog time-out. The user will need to be aware of this possibility and take step s to

insure that an unwanted Watchdog reset does not cause a system failure while

programming or erasing the flash memory.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 27 of 386

In order to preclude the possibility of stale data being read from the flash memory, the

LPC21xx and LPC22xx MAM holding latches are automatically invalidated at the

beginning of any flash programming or erase opera tion. Any subsequent read from a flash

address will cause a new fetch to be initiated after the flash operation has completed.

Page 28

NXP Semiconductors

5. MAM operating modes

Three modes of operation are defined for the MAM, trading off performance for ease of

predictability:

Mode 0: MAM off. All memory requests result in a flash read operation (see Table

note 3–2). There are no instruction prefetches.

Mode 1: MAM partially enabled. Sequential instruction accesses are fulfilled from the

holding latches if the data is present. Instruction prefetch is enabled. Non-sequential

instruction accesses initiate flash read operations (see Table note 3–2

all branches cause memory fetches. All data operations cause a flash read because

buffered data access timing is hard to predict and is very situation dependent.

Mode 2: MAM fully enabled. Any memory request (code or data) for a value that is

contained in one of the corresponding holding latches is fulfilled from the latch.

Instruction prefetch is enabled. Flash read operations are initiated for instruction

prefetch and code or data values not available in the corresponding holding latches.

T able 21. MAM responses to program accesses of various types

Program Memory Request Type MAM Mode

Sequential access, data in latches Initiate Fetch

Sequential access, data not in latches Initiate Fetch Initiate Fetch

Non-sequential access, data in latches Initiate Fetch

Non-sequential access, data not in latches Initiate Fetch Initiate Fetch

UM10114

Chapter 3: LPC21xx/22xx Memory Accelerator Module (MAM)

). This means that

0 1 2

[2]

Use Latched

Data

[2]

Initiate Fetch

[1]

Use Latched

Data

[1]

Initiate Fetch

[1][2]

Use Latched

Data

[1]

Initiate Fetch

[1]

[1]

[1]

[1]

[1] Instruction prefetch is enabled in modes 1 and 2.

[2] The MAM actually uses latched data if it is available, but mimics the timing of a flash read operation. This

saves power while resulting in the same execution timing. The MAM can truly be turned off by setting the

fetch timing value in MAMTIM to one clock.

Table 22. MAM responses to data accesses of various types

Data Memory Request T ype MAM Mode

0 1 2

Sequential access, data in latches Initiate Fetch

[1]

Initiate Fetch

[1]

Use Latched

Data

Sequential access, data not in latches Initiate Fetch Initiate Fetch Initiate Fetch

Non-sequential access, data in latches Initiate Fetch

[1]

Initiate Fetch

[1]

Use Latched

Data

Non-sequential access, data not in latches Initiate Fetch Initiate Fetch Initiate Fetch

[1] The MAM actually uses latched data if it is available, but mimics the timing of a flash read operation. This

saves power while resulting in the same execution timing. The MAM can truly be turned off by setting the

fetch timing value in MAMTIM to one clock.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 28 of 386

Page 29

NXP Semiconductors

6. MAM configuration

After reset the MAM defaults to the disabled state. Software can turn memory access

acceleration on or off at any time. This allows most of an application to be run at the

highest possible performance, while certain functions can be run at a somewhat slower

but more predictable rate if more precise timing is required.

7. Register description

All registers, regardless of size, are on word address boundaries. Details of the registers

appear in the description of each function.

T able 23. Summary of MAM registers

Name Description Access Reset

MAMCR Memory Accelerator Module Control Register.

Determines the MAM functional mode, that is, to

what extent the MAM performance enhancements

are enabled. See Table 3–24

MAMTIM Memory Accelerator Module Timing control.

Determines the number of clocks used for flash

memory fetches (1 to 7 processor clocks).

UM10114

Chapter 3: LPC21xx/22xx Memory Accelerator Module (MAM)

Address

[1]

value

R/W 0x0 0xE01F C000

.

R/W 0x07 0xE01F C004

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

8. MAM Control Register (MAMCR - 0xE01F C000)

Two configuration bits select the three MAM operating modes, as shown in Table 3–24.

Following Reset, MAM functions are disabled. Changing the MAM operating mode causes

the MAM to invalidate all of the holding latches, resulting in new reads of flash information

as required.

T able 24. MAM Control Register (MAMCR - address 0xE01F C000) bit description

Bit Symbol Value Description Reset

1:0 MAM_mode

_control

7:2 - - Reserved, user software should not write ones to reserved

00 MAM functions disabled 0

01 MAM functions partially enabled

10 MAM functions fully enabled

11 Reserved. Not to be used in the ap plication.

bits. The value read from a reserved bit is not defined.

9. MAM Timing register (MAMTIM - 0xE01F C004)

The MAM Timing register determines how many CCLK cycles are used to access the

flash memory . This allows tuning MAM timin g to match the processor operating frequency.

flash access times from 1 clock to 7 clocks are possible. Single clock flash accesses

would essentially remove the MAM from timing calculations. In this case the MAM mode

may be selected to optimize power usage.

value

NA

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 29 of 386

Page 30

NXP Semiconductors

T able 25. MAM Timing register (MAMTIM - address 0xE01F C004) bit description

Bit Symbol Value Description Reset

2:0 MAM_fetch_

7:3 - - Reserved, user software should not write ones to reserved

UM10114

Chapter 3: LPC21xx/22xx Memory Accelerator Module (MAM)

value

000 0 - Reserved. 07

cycle_timing

001 1 - MAM fetch cycles are 1 processor clock (CCLK) in

duration

010 2 - MAM fetch cycles are 2 CCLKs in duration

011 3 - MAM fetch cycles are 3 CCLKs in duration

100 4 - MAM fetch cycles are 4 CCLKs in duration

101 5 - MAM fetch cycles are 5 CCLKs in duration

110 6 - MAM fetch cycles are 6 CCLKs in duration

111 7 - MAM fetch cycles are 7 CCLKs in duration

Warning: These bits set the duration of MAM flash fetch operations

as listed here. Improper setting of this value may result in incorrect

operation of the device.

NA

bits. The value read from a reserved bit is not defined.

10. MAM usage notes

When changing MAM timing, the MAM must first be turned off by writing a zero to

MAMCR. A new value may then be written to MAMTIM. Finally, the MAM may be turned

on again by writing a value (1 or 2) corresponding to the desired operating mode to

MAMCR.

For system clock slower than 20 MHz, MAMTIM can be 001. For system clock between

20 MHz and 40 MHz, flash access time is suggested to be 2 CCLKs, while in systems with

system clock faster than 40 MHz, 3 CCLKs are proposed. For system clocks of 60 MHz

and above, 4CCLK’s are needed.

Table 26. Suggestions for MAM timing selection

system clock Number of MAM fetch cycles in MAMTIM

< 20 MHz 1 CCLK

20 MHz to 40 MHz 2 CCLK

40 MHz to 60 MHz 3 CCLK

> 60 MHz 4 CCLK

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 30 of 386

Page 31

UM10114

Chapter 4: LPC21xx/22xx External Memory Controller (EMC)

Rev. 03 — 2 April 2008 User manual

1. How to read this chapter

This chapter applies to all parts with external memory controller. The EMC is identical for

all these parts. It is available in the following parts (in all 144 pin packages):

• LPC2210, LPC2210/01, and LPC22 2 0

• LPC2212, LPC2214, and /01 versions

• LPC2290 and LPC2290/01

• LPC2292, LPC2294, and /01 versions

The LPC21xx parts do not have an EMC controller.

For an overview of how LPC21xx and LPC22xx parts and versions are described in this

manual, see Section 1–2 “

How to read this manual”.

2. Features

3. Description

• Support for various static memory-mapped devices including RAM, ROM, flash, burst

ROM, and some external I/O devices

• Asynchronous page mode read operation in non-clocked memory subsystems

• Asynchronous burst mode read access to burst mode ROM devices

• Independent configuration for up to four banks, each up to 16 MB

• Programmable bus turnaround (idle) cycles (1 to 16)

• Programmable read and write WAIT states (up to 32) for static RAM devices

• Programmable initial and subsequent burst read WAIT state, for burst ROM devices

• Programmable write protection

• Programmable burst mode operation

• Programmable read byte lane enable control

The external Static Memory Controller is an AMBA AHB slave module which provides an

interface between an AMBA AHB system bus and external (off-chip) memory devices. It

provides support for up to four independently configurable memory banks simult aneously.

Each memory bank is capable of supporting SRAM, ROM, Flash EPROM, Burst ROM

memory, or some external I/O devices .

Each memory bank may be 8, 16, or 32 bits wide.

Since the LPC22xx 144 pin packages pin out address lines A[23:0] only, the decoding

among the four banks uses address bits A[25:24]. The native lo catio n of th e four ban ks is

at the start of the External Memory area identified in Figure 2–2

for initial booting under control of the state of the BOOT[1:0] pins.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 31 of 386

, but Bank 0 can be used

Page 32

NXP Semiconductors

Table 27. Address ranges of the external memory banks

Bank Address range Configuration register

0 0x8000 0000 - 0x80FF FFFF BCFG0

1 0x8100 0000 - 0x81FF FFFF BCFG1

2 0x8200 0000 - 0x82FF FFFF BCFG2

3 0x8300 0000 - 0x83FF FFFF BCFG3

4. Pin description

Table 28. External Memory Controller pin description

Pin name Type Pin description

D[31:0] Input/Output External memory Data lines

A[23:0] Output External memory Address lines

OE Output Low-active Output Enable signal

BLS[3:0] Output Low-active Byte Lane Select signals

WE Output Low-active Write Enable signal

CS[3:0] Output Low-active Chip-Select signals

UM10114

Chapter 4: LPC21xx/22xx External Memory Controller (EMC)

5. Register description

The external memory controller contains 4 registers as shown in Table 4–29.

Table 29. External Memory Controller register map

Name Description Access Reset value,

BCFG0 Configuration register for memory bank 0 R/W 0x0000 FBEF 0xFFE0 0000

BCFG1 Configuration register for memory bank 1 R/W 0x2000 FBEF 0xFFE0 0004

BCFG2 Configuration register for memory bank 2 R/W 0x1000 FBEF 0xFFE0 0008

BCFG3 Configuration register for memory bank 3 R/W 0x0000 FBEF 0xFFE0 000C

Each register selects the following options for its memory bank:

• The number of idle clock cycles inserted between read and write accesses in this

bank, and between an access in another bank and an access in this bank, to avoid

bus contention between devices (1 to 17 clocks)

• The length of read accesses, except for subsequent reads from a burst ROM (3 to 35

clocks)

• The length of write accesses (3 to 19 clocks)

• Whether the bank is write-protected or not

• Whether the bank is 8, 16, or 32 bits wide

Address

see Table 4–30

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 32 of 386

Page 33

NXP Semiconductors

5.1 Bank Configuration Registers 0-3 (BCFG0-3 - 0xFFE0 0000 to 0xFFE0 000C)

Table 30. Bank Configuration Registers 0-3 (BCFG0-3 - 0xFFE0 0000 to 0xFFE0 000C)

BCFG0-3 Name Function Reset

3:0 IDCY This field controls the minimum number of “idle” CCLK cycles

4 - Reserved, user software should not write ones to reserved bits.

9:5 WST1 This field controls the length of read accesses (except for

10 RBLE This bit should be 0 for banks composed of byte-wide or

15:11 WST2 For SRAM banks, this field controls the length of write accesses,

23:16 - Reserved, user software should not write ones to reserved bits.

24 BUSERR The only known case in which this bit is set is if the EMC detects

25 WPERR This bit is set if software attempts to write to a bank that has the

26 WP A 1 in this bit write-protects the bank. 0

27 BM A 1 in this bit id entifies a burst-ROM bank. 0

29:28 MW Th is field controls the width of the data bus for this bank:

31:30 AT Always write 00 to this field. 00

Chapter 4: LPC21xx/22xx External Memory Controller (EMC)

address description

that the EMC maintains between read and write accesses in this

bank, and between an access in another bank and an access in

this bank, to avoid bus contention between devices. The number

of idle CCLK cycles between such accesses is the value in this

field plus 1.

The value read from a reserved bit is not defined.

subsequent reads from a burst ROM). The length of read

accesses, in CCLK cycles, is this field value plus 3.

non-byte-partitioned devices, so that the EMC drives the BLS3:0

lines High during read accesses. This bit should be 1 for banks

composed of 16-bit and 32-bit wide devices that include byte

select inputs, so that the EMC drives the BLS3:0 lines Low

during read accesses.

which consist of:

One CCLK cycle of address setup with CS, BLS, and WE high

This value plus 1, CCLK cycles with address valid and CS, BLS,

and WE low

AND

One CCLK cycle with address valid, CS low, BLS and WE high.

For burst ROM banks, this field controls the length of subsequent

accesses, which are (this value plus 1) CCLK cycles long.

The value read from a reserved bit is not defined.

an AMBA request for more than 32 bits of data. The

ARM7TDMI-S will not make such a request.

WP bit 1. Write a 1 to this bit to clear it.

00=8 bit, 01=16 bit, 10=32 bit, 11=reserved

UM10114

value

1111

NA

11111

0

11111

NA

0

0

See

Table 4–

31

The table below shows the state of BCFG0[29:28] after the Boot Loader has run. The

hardware reset state of these bits is 10.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 33 of 386

Page 34

NXP Semiconductors

T able 31. Default memory widths at reset

Bank BOOT[1:0] during Reset BCFG[29:28] Reset value Memory width

0LL 00 8bits

0LH 01 16bits

0HL 10 32bits

0HH 01 16bits

1XX 10 32bits

2XX 01 16bits

3XX 00 8bits

5.2 Read Byte Lane Control (RBLE)

The External Memory Controller (EMC) generates byte lane control signals BLS[3:0]

according to:

• External memory bank data bus wid th , de fined within each configuration register (see

• External memory bank type, being either byte (8 bits), halfword (16 bits) or word (32

UM10114

Chapter 4: LPC21xx/22xx External Memory Controller (EMC)

MW field in BCFG register)

bits) (see RBLE field in BCFG register)

Each memory bank can either be 8, 16 or 32 bits wide. The type of memory used to

configure a particular memory bank determines how the WE and BLS signals are

connected to provide byte, halfword and word access. For read accesses, it is necessary

to control the BLS signals by driving them either all HIGH, or all LOW.

This control is achieved by programming the Read Byte Lane Enable (RBLE) bit within

each configuration register. The following two sections explain why different connections

in respect of WE and BLS[3:0] are needed for different memory configurations.

5.2.1 Accesses to memory banks constructed from 8-bit or non byte-partitioned

memory devices

For memory banks constructed from 8-bit or non byte-partitioned memory devices, it is

important that the RBLE bit is cleared to zero within the respective memory bank

configuration register. This forces all BLS[3:0] lines HIGH during a read access to that

particular bank.

Figure 4–7

memory banks that are 8, 16 and 32 bits wide. In each of these configurations, the

BLS[3:0] signals are connected to write enable (WE) inputs of each 8-bit memory.

Note: The WE signal from the EMC is not used. For write transfers, the relevant BLS[3:0]

byte lane signals are asserted LOW and steer the data to the addressed bytes.

For read transfers, all of the BLS[3:0] lines are deasserted HIGH, which allows the

external bus to be defined for at least the width of the accessed memory.

(a), Figure 4–8 (a) and Figure 4–9 show 8-bit memory being used to configure

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 34 of 386

Page 35

NXP Semiconductors

5.2.2 Accesses to memory banks constructed from 16 or 32 bit memory devices

For memory banks constructed from 16 bit or 32-bit memory devices, it is important that

the RBLE bit is set to one within the respective memory bank configuraton register. This

asserts all BLS[3:0] lines LOW during a read access to that particular bank. For 16 and

32-bit wide memory devices, byte select signals exist and must be appropriately

controlled as shown in Figure 4–7

6. External memory interface

External memory interfacing depends on the bank width (32, 16 or 8 bit selected via MW

bits in corresponding BCFG register). Furthermore, the memory chip(s) require an

adequate setup of RBLE bit in BCFG register. Memory accessed with an 8-bit wide data

bus require RBLE = 0, while memory banks capable of accepting 16 or 32 bit wide data

require RBLE = 1.

If a memory bank is configured to be 32 bits wide, address lines A0 and A1 can be used

as non-address lines. If a memory bank is configured to 16 bits wide, A0 is not required.

However, 8 bit wide memory banks do require all address lines down to A0. Configuring

A1 and/or A0 line(s) to provide address or non-address function is accomplished using

bits 23 and 24 in Pin Function Select Register 2 (PINSEL2 register, see Table 8–88

UM10114

Chapter 4: LPC21xx/22xx External Memory Controller (EMC)

and Figure 4–8.

).

Symbol "a_b" in the following figures refers to the highest order address line in the data

bus. Symbol "a_m" refers to the highest order address line of the me mory chip used in the

external memory interface.

See Section 8–6.5 “

Boot control for LPC22xx part s ” for how to boot from external memor y.

UM10114_3 © NXP B.V. 2008. All rights reserved.

User manual Rev. 03 — 2 April 2008 35 of 386

Page 36

NXP Semiconductors

A[a_b:2]

BLS[1]

D[15:8]

CE

OE

WE

IO[7:0]

A[a_m:0]

BLS[0]

D[7:0]

CE

OE

WE

IO[7:0]

A[a_m:0]

OE

CS

BLS[3]

D[31:24]

CE

OE

WE

IO[7:0]

A[a_m:0]

BLS[2]

D[23:16]

CE

OE

WE

IO[7:0]

A[a_m:0]

OE

CS

WE

CE

OE

WE

UB

LB

IO[15:0]

A[a_m:0]

D[31:16]

BLS[2]

CE

OE

WE

UB

LB

IO[15:0]

A[a_m:0]

D[15:0]

BLS[0]

A[a_b:2]

BLS[3] BLS[1]

OE

CS

WE

CE

OE

WE

B3

B2

B1

B0

IO[31:0]

A[a_m:0]

D[31:0]

BLS[2]

A[a_b:2]

BLS[3]

BLS[0]

BLS[1]

Chapter 4: LPC21xx/22xx External Memory Controller (EMC)