A

B

C

D

E

F G H

PG110-A00

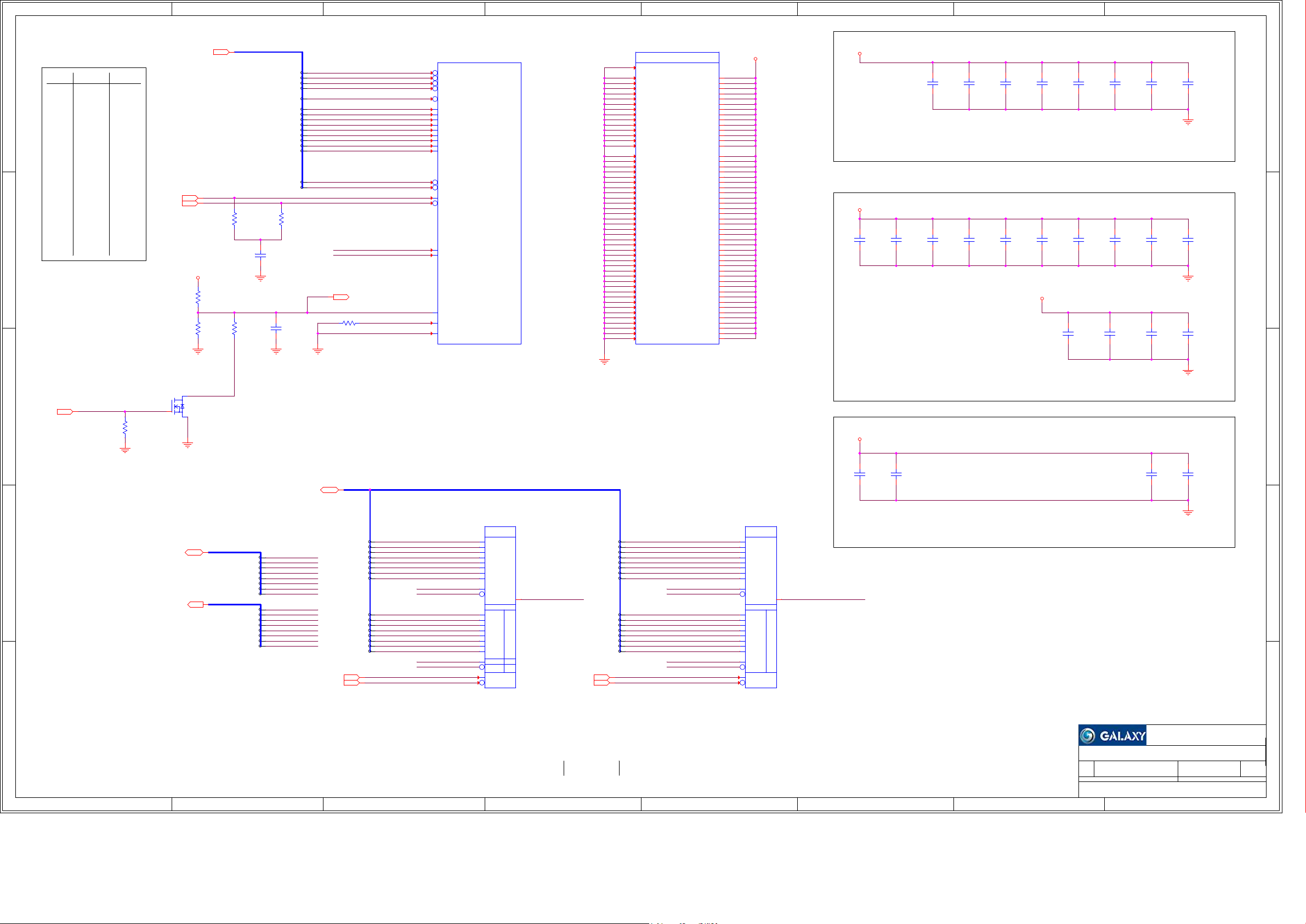

GP108 64Bit GDDR5 X32

1

HDMI/DP + DVI-D/DP

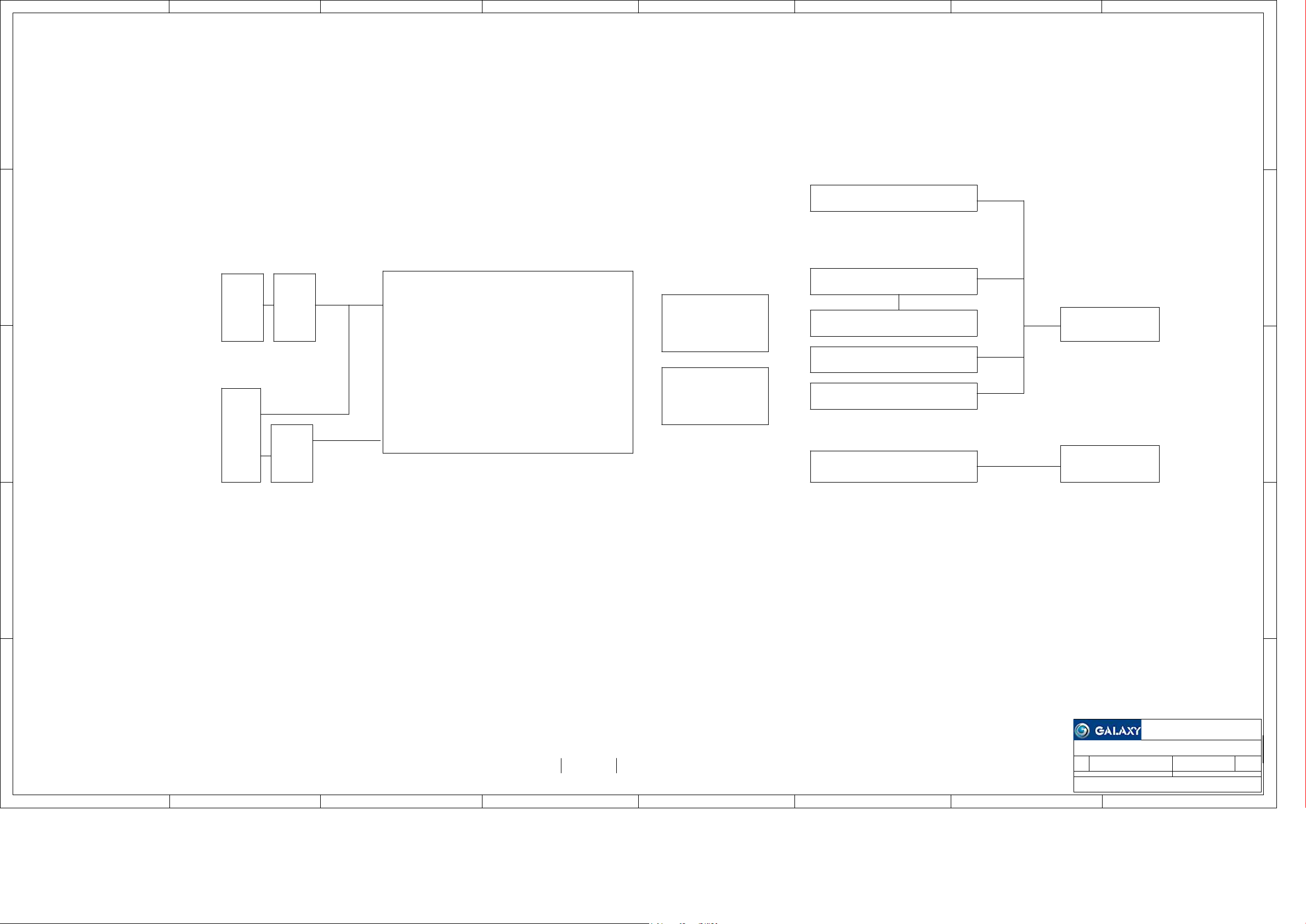

TABLE OF CONTENTS

1

Page

2

3

Description

Table of Contents

1

2

Block Diagram

3

PCI Express

4

GPU Frame Buffer

5

FBA bits 31..00

6

FBA bits 63..32

7

NVVVD Decoupling

8

FBVDDQ and 1V8 Decoupling

9

IFPAB DL-DVI

10

IFPA DP

IFPB DP/HDMI

11

12

JTAG,GPIO&XTAL

ROM & STRAPS

13

14

Power Sequence

15

POWER:1V8 & 5V

16

POWER: NV3V3, NV12V

17

POWER:PEX_VDD

18

POWER:FBVDDQ

19

POWER:NVVDD

20

POWER:NVVDD

21

Mechanical

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. N VIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO T HE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A

B

C

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

Table of Contents

4

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet

Date : Sheet

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

E

G

Galaxy Microsystems (HK) Ltd.

Table of Contents

Table of Contents

Table of Contents

Design By:

Design By:

P85C

P85C

P85C

Design By:

James Lee V10

James Lee V10

James Lee V10

1 21Wednesday, April 05, 2017

1 21Wednesday, April 05, 2017

1 21Wednesday, April 05, 2017

HFD

of

of

A

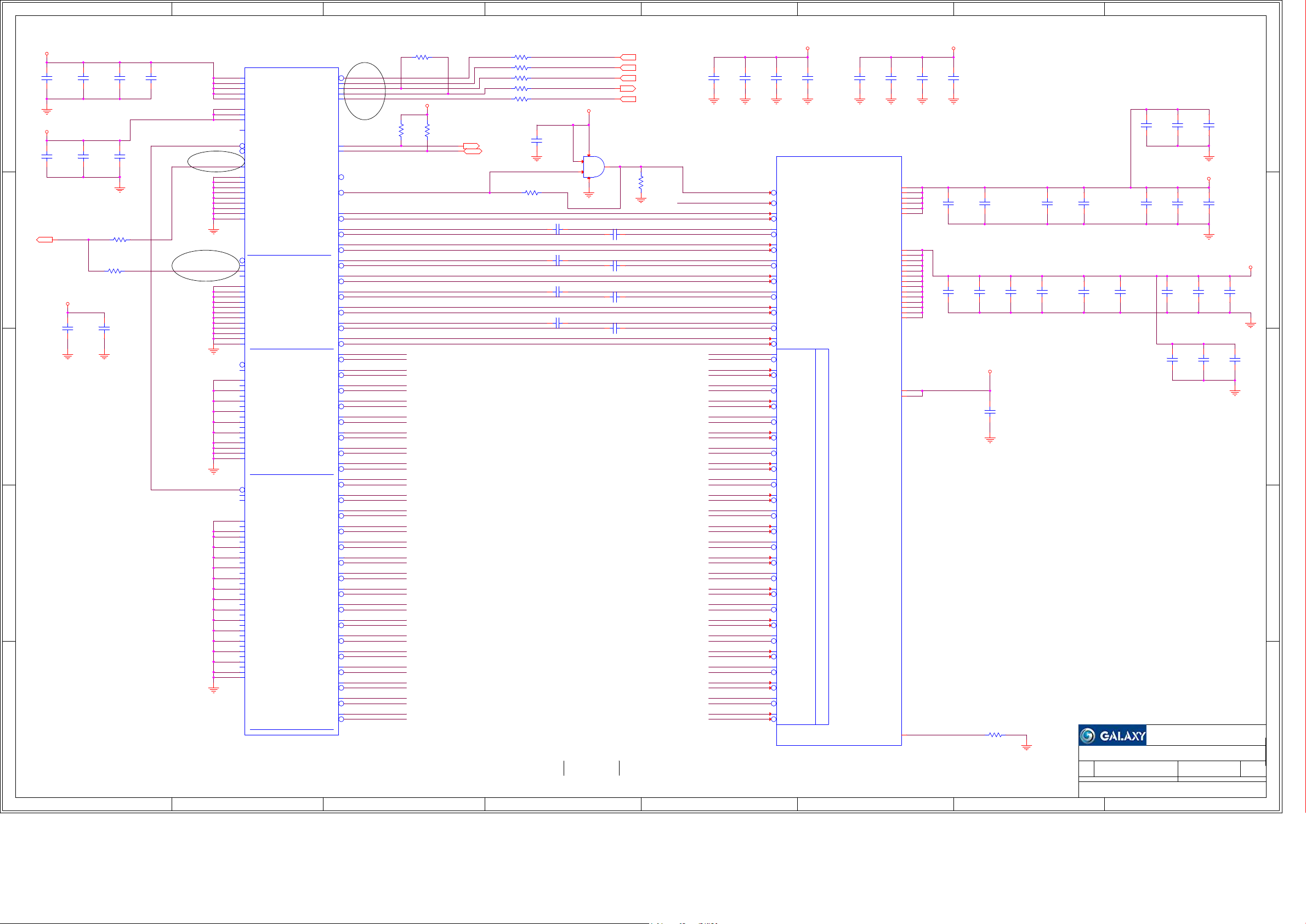

Block Diagram

B

C D

E

F G H

1

1

NVVDD PH1/2

2

2

FBVDDQ

DP

HDMI

LINK B

FBA LO

PEX_VDD

PEX_12V

1V8

GP108

3

FBA HI

FAN

3

DVI-I

LINK A

DP

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. N VIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO T HE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A

B

C

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

Block Diagram

DP POWER

E

FD

G

PEX_3V3

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Block Diagram

Block Diagram

Block Diagram

Design By:

Design By:

P85C

P85C

P85C

Design By:

James Lee V10

James Lee V10

James Lee V10

2 21Wednesday, April 05, 2017

2 21Wednesday, April 05, 2017

2 21Wednesday, April 05, 2017

H

4

5

A

B

C D

E

F G H

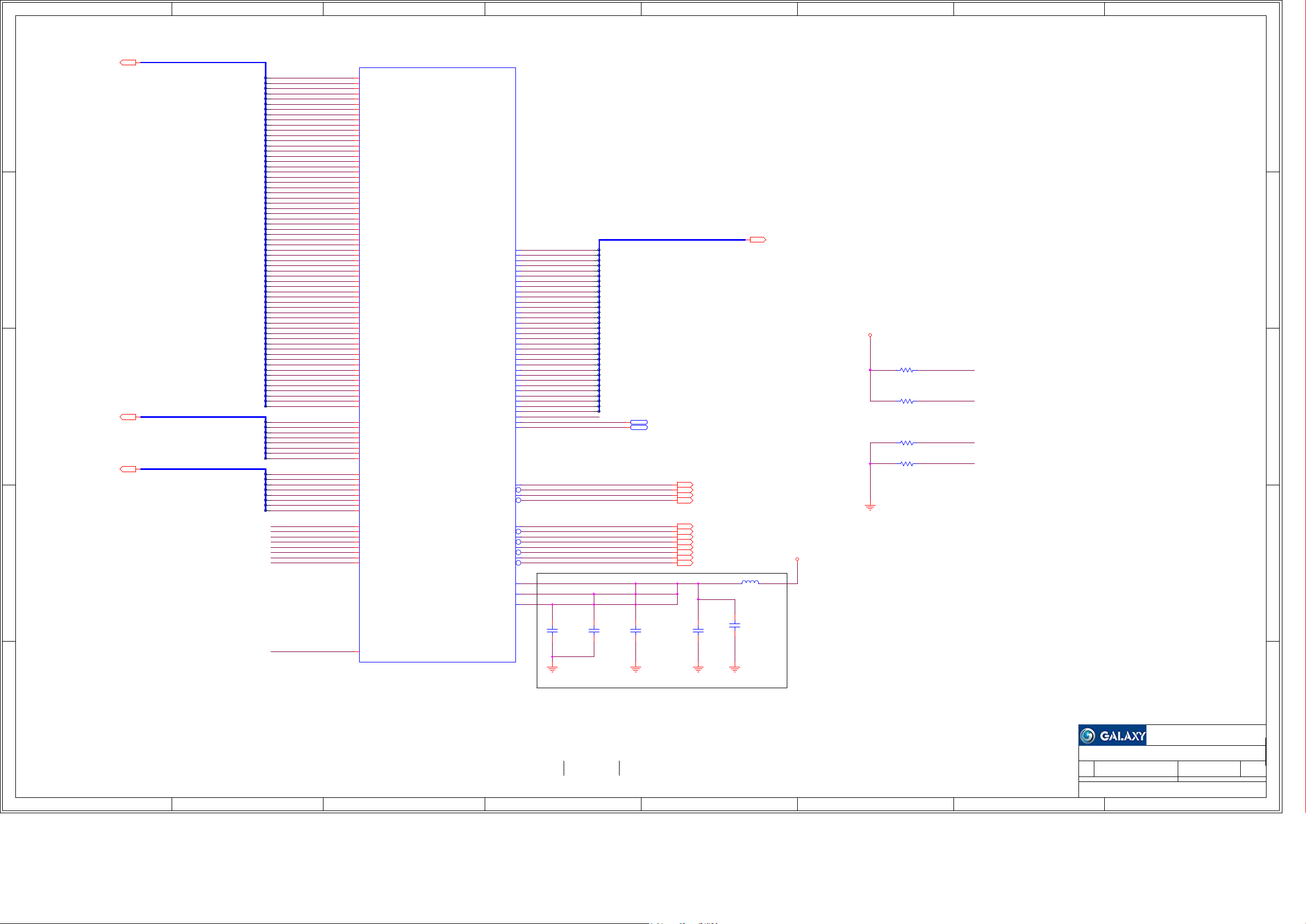

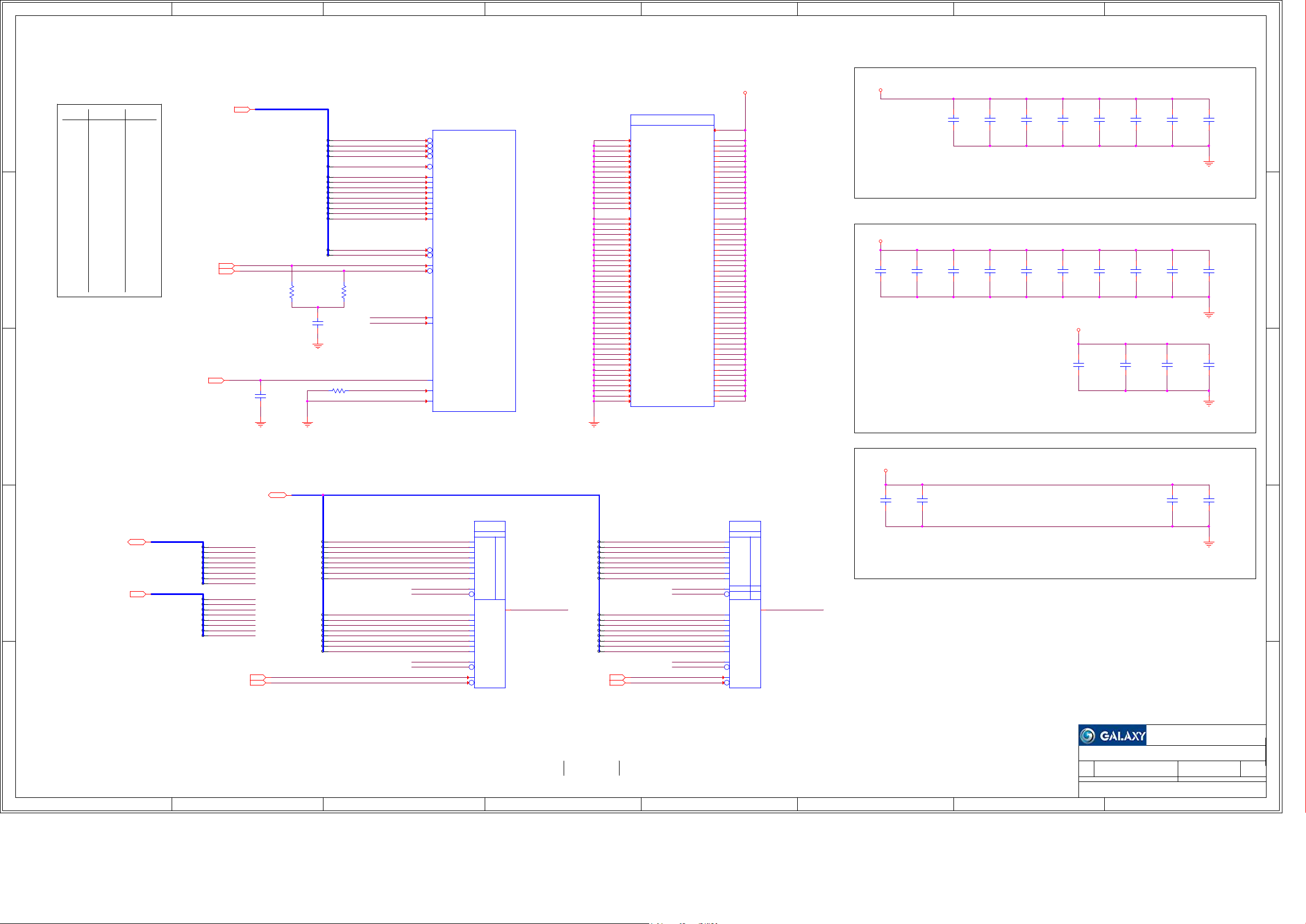

PCI Express

12V_PEX

PLACE DECOUPLING CAPS NEAR PCI-E CONN FINGERS

C91

10uF

16V

10%

X6S

0805

GND

3V3_PEX

OUT

NO STUFF

C678

10uF

16V

10%

X6S

0805

NO STUFF

POWER_BRAKE*

1

2

12V_PEX

GND

nv_cap

C94

1uF

16V

20%

X6S

0603W

COMMON

C93

10uF

16V

10%

X6S

0805

NO STUFF

C96

1uF

16V

10%

X7R

0603

COMMON

12

R97 0ohm

0402 NO STUFF

GND

R94

0402

0.05 ohm

C90

1uF

16V

20%

X6S

0603W

COMMON

GND

0.05 ohm

nv_cap

C695

1uF

16V

10%

X7R

0603

COMMON

C682

0.1uF

16V

10%

X7R

0402

COMMON

0ohm

NO STUFF

CO-LAY WITH 0805 CAP

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. N VIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO T HE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A

C83

0.1uF

16V

10%

X7R

0402

COMMON

5A

1A

PEX_PRSNT*

PEX_B12

GND

PEX_B30

GND

GND

GND

CN1

NONPHY-X16

CON_X16

@electro_mechanic.con_pci_express(sym_1):page3_i2

NO STUFF

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

END OF X1

B30

RSVD

A20

GND

B22

GND

A24

GND

B26

GND

A28

GND

B29

GND

A31

GND

B32

GND

END OF X4

A34

GND

B36

GND

A38

GND

B40

GND

A42

GND

B44

GND

A46

GND

B47

GND

B49

GND

A49

GND

END OF X8

B81

PRSNT2

A51

GND

B53

GND

A54

GND

B56

GND

A58

GND

B60

GND

A62

GND

B64

GND

A66

GND

B68

GND

A70

GND

B72

GND

A74

GND

B76

GND

A78

GND

B80

GND

A82

GND

END OF X16

B

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

R136

0ohm

0402

COMMON

0.05 ohm

PEX_TRST*

B9

PEX_TCLK

A5

PEX_TDI

A6

PEX_TDO

A7

PEX_TMS

A8

PEX_SMCLK

B5

PEX_SMDAT

B6

PEX_RST* PEX_RST_BUF*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

SNN_PEX_TXX4

A35

SNN_PEX_TXX4*

A36

SNN_PEX_RXX4

B33

SNN_PEX_RXX4*

B34

SNN_PEX_TXX5

A39

SNN_PEX_TXX5*

A40

SNN_PEX_RXX5

B37

SNN_PEX_RXX5*

B38

SNN_PEX_TXX6

A43

SNN_PEX_TXX6*

A44

SNN_PEX_RXX6

B41

SNN_PEX_RXX6*

B42

SNN_PEX_TXX7

A47

SNN_PEX_TXX7*

A48

SNN_PEX_RXX7

B45

SNN_PEX_RXX7*

B46

SNN_PEX_TXX8

A52

SNN_PEX_TXX8*

A53

SNN_PEX_RXX8

B50

SNN_PEX_RXX8*

B51

SNN_PEX_TXX9

A56

SNN_PEX_TXX9*

A57

SNN_PEX_RXX9

B54

SNN_PEX_RXX9*

B55

SNN_PEX_TXX10

A60

SNN_PEX_TXX10*

A61

SNN_PEX_RXX10

B58

SNN_PEX_RXX10*

B59

SNN_PEX_TXX11

A64

SNN_PEX_TXX11*

A65

SNN_PEX_RXX11

B62

SNN_PEX_RXX11*

B63

SNN_PEX_TXX12

A68

SNN_PEX_TXX12*

A69

SNN_PEX_RXX12

B66

SNN_PEX_RXX12*

B67

SNN_PEX_TXX13

A72

SNN_PEX_TXX13*

A73

SNN_PEX_RXX13

B70

SNN_PEX_RXX13*

B71

SNN_PEX_TXX14

A76

SNN_PEX_TXX14*

A77

SNN_PEX_RXX14

B74

SNN_PEX_RXX14*

B75

SNN_PEX_TXX15

A80

SNN_PEX_TXX15*

A81

SNN_PEX_RXX15

B78

SNN_PEX_RXX15*

B79

3V3_PEX

R88

R89

100k

100k

5 %

5 %

0402

0402

NO STUFF

DIFFPAIR

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

NO STUFF

OUT

BI

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

12

R133

R134

R132

R135

R131

0ohm

0402

NO STUFF

0.05 ohm

0ohm

NO STUFF

0402

0.05 ohm

0ohm

NO STUFF

0402

0.05 ohm

0ohm

12

NO STUFF

0402

0.05 ohm

0ohm

0402

NO STUFF

0.05 ohm

C677

0.1uF

16V

10%

X7R

12

0402

COMMON

GND

R1144

0ohm

0402

NO STUFF

0.05 ohm

C676 0.22uF

0402

COMMON

C674 0.22uF

0402 16V

COMMON

C672 0.22uF

0402

COMMON

C663

0402

COMMON

C

JTAG_TRST*

JTAG_TCLK

JTAG_TDI

JTAG_TDO

JTAG_TMS

16V

16V

0.22uF

16V

ASSEMBLY

PAGE DETAIL

1V8

5

1

2

3

GND

IN

IN

IN

OUT

IN

U502

@logic.u_and_2in(sym_1):page3_i54

4

SC70-5

COMMON

GND

C675

0.22uF

0402

16V

COMMON

C673

0.22uF

0402 16V

COMMON

C671

0.22uF

0402

16V

COMMON

C662 0.22uF

0402 16V

COMMON

<ASSEMBLY_DESCRIPTION>

PCI Express

R541

100k

5 %

0402

COMMON

12

12

12

12

SNN_GPU_PEX_CLKREQ*

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

12V_PEX

0.400

C84

C86

1uF

16V

10%

X7R

0603

COMMON

C693

1uF

16V

10%

X7R

0603

COMMON

1uF

16V

10%

X7R

0603

COMMON

GND GND GND GND

G1A

@digital.u_gpu_gb2c_64(sym_1):page3_i108

BGA595

COMMON

1/14 PCI_EXPRESS

AC7

PEX_RST

AC6

AE8

AD8

AC9

AB9

AG6

AG7

AB10

AC10

AE7

AD11

AC11

AE9

AC12

AB12

AG9

AG10

AB13

AC13

AF10

AE10

AD14

AC14

AE12

AF12

AC15

AB15

AG12

AG13

AB16

AC16

AF13

AE13

AD17

AC17

AE15

AF15

AC18

AB18

AG15

AG16

AB19

AC19

AF16

AE16

AD20

AC20

AE18

AF18

AC21

AB21

AG18

AG19

AD23

AE23

AF19

AE19

AF24

AE24

AE21

AF21

AG24

AG25

AG21

AG22

PEX_CLKREQ

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

AF7

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

AF9

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

SNN_PEX_TX4

SNN_PEX_TX4*

SNN_PEX_RX4

SNN_PEX_RX4*

SNN_PEX_TX5

SNN_PEX_TX5*

SNN_PEX_RX5

SNN_PEX_RX5*

SNN_PEX_TX6

SNN_PEX_TX6*

SNN_PEX_RX6

SNN_PEX_RX6*

SNN_PEX_TX7

SNN_PEX_TX7*

SNN_PEX_RX7

SNN_PEX_RX7*

SNN_PEX_TX8

SNN_PEX_TX8*

SNN_PEX_RX8

SNN_PEX_RX8*

SNN_PEX_TX9

SNN_PEX_TX9*

SNN_PEX_RX9

SNN_PEX_RX9*

SNN_PEX_TX10

SNN_PEX_TX10*

SNN_PEX_RX10

SNN_PEX_RX10*

SNN_PEX_TX11

SNN_PEX_TX11*

SNN_PEX_RX11

SNN_PEX_RX11*

SNN_PEX_TX12

SNN_PEX_TX12*

SNN_PEX_RX12

SNN_PEX_RX12*

SNN_PEX_TX13

SNN_PEX_TX13*

SNN_PEX_RX13

SNN_PEX_RX13*

SNN_PEX_TX14

SNN_PEX_TX14*

SNN_PEX_RX14

SNN_PEX_RX14*

SNN_PEX_TX15

SNN_PEX_TX15*

SNN_PEX_RX15

SNN_PEX_RX15*

E

NETNET NV_NETCLASS NV_NETCLASS

C694

1uF

16V

10%

X7R

0603

COMMON

3V3_PEX

0.400

C684

C681

C679

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

GND GND GND GND

AA22

PEX_DVDD

AB23

PEX_DVDD

AC24

PEX_DVDD

AD25

PEX_DVDD

AE26

PEX_DVDD

AE27

PEX_DVDD

AA10

PEX_HVDD

AA12

PEX_HVDD

AA13

PEX_HVDD

AA16

PEX_HVDD

AA18

PEX_HVDD

AA19

PEX_HVDD

AA20

PEX_HVDD

AA21

PEX_HVDD

AB22

PEX_HVDD

AC23

PEX_HVDD

AD24

PEX_HVDD

AE25

PEX_HVDD

AF26

PEX_HVDD

AF27

PEX_HVDD

PEX_PLL_HVDD

PEX_PLL_HVDD

AA8

AA9

1uF

16V

10%

X7R

0603

NO STUFF

C683

1uF

16V

10%

X7R

0603

NO STUFF

C549

1uF

6.3V

10%

X6S

0402

COMMON

PLACE UNDER GPU

C581

1uF

6.3V

10%

X6S

0402

COMMON

PLACE UNDER GPU

35mA

PLACE UNDER GPU

C577

1uF

6.3V

10%

X6S

0402

COMMON

1V8

GND

C605

1uF

6.3V

10%

X6S

0402

COMMON

C600

0.1uF

16V

10%

X7R

0402

COMMON

135mA

C148

4.7uF

6.3V

20%

X6S

0603

COMMON

PLACE NEAR GPU MIDWAY BETWEEN GPU AND PS

C588

C583

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

C149

4.7uF

6.3V

20%

X6S

0603

COMMON

188mA

C565

4.7uF

6.3V

20%

X6S

0603

COMMON

PLACE NEAR GPU

CO-LAYOUT 0805 AND 0603

C612

4.7uF

6.3V

20%

X6S

0603

COMMON

C569

22uF

4V

20%

X6S

0603W

NO STUFF

C542

10uF

6.3V

10%

X6S

0805

COMMON

C609

10uF

6.3V

10%

X6S

0805

COMMON

MIDWAY BETWEEN GPU AND PS

CO-LAYOUT 0805 AND 0603

C610

22uF

4V

20%

X6S

0603W

NO STUFF

C567

22uF

4V

20%

X6S

0603W

NO STUFF

C568

10uF

6.3V

10%

X6S

0805

COMMON

GND

PEX_VDD

GND

C629

10uF

6.3V

10%

X6S

0805

COMMON

C543

22uF

4V

20%

X6S

0603W

NO STUFF

C570

22uF

6.3V

20%

X6S

0805

NO STUFF

C627

22uF

4V

20%

X6S

0603W

NO STUFF

1

2

1V8

C626

22uF

6.3V

20%

X6S

0805

COMMON

GND

C628

22uF

4V

20%

X6S

0603W

NO STUFF

GND

3

4

PEX LA NES 15 - 4 ARE DEFEATURED

5

PEX_TERMP

FD

PEX_TERMP

AF25

50OHM_NETCLASS1

R514

2.49k

0402

COMMON

1 %

GND

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

G

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

PCI Express

PCI Express

PCI Express

Design By:

Design By:

P85C

P85C

P85C

Design By:

James Lee V10

James Lee V10

James Lee V10

H

3 21Wednesday, April 05, 2017

3 21Wednesday, April 05, 2017

3 21Wednesday, April 05, 2017

A

B

C D

E

F G H

GPU Frame Buffer

G1B

@digital.u_gpu_gb2c_64(sym_2):page4_i151

AA24

AA23

AD27

AB25

AD26

AC25

AA27

AA26

W26

W27

W25

W24

AA25

W23

AB26

W22

AB27

E18

F18

E16

F17

D20

D21

F20

E21

E15

D15

F15

F13

C13

B13

E13

D13

B15

C16

A13

A15

B18

A18

A19

C19

B24

C23

A25

A24

A21

B21

C20

C21

R22

R24

T22

R23

N25

N26

N23

N24

V23

V22

T23

U22

Y24

Y22

Y25

R26

T25

N27

R27

V26

V27

D19

D14

C17

C22

P24

U25

E19

C15

B16

B22

R25

T26

F19

C14

A16

A22

P25

T27

D23

BGA595

COMMON

2/14 FBA

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM4

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

FB_VREF

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_CMD32

FBA_CMD34

FBA_CMD35

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK01

FBA_WCK01

FBA_WCK23

FBA_WCK23

FBA_WCK45

FBA_WCK45

FBA_WCK67

FBA_WCK67

FB_PLL_AVDD

FB_PLL_AVDD

FB_REFPLL_AVDD

C27

C26

E24

F24

D27

D26

F25

F26

F23

G22

G23

G24

F27

G25

G27

G26

M24

M23

K24

K23

M27

M26

M25

K26

K22

J23

J25

J24

K27

K25

J27

J26

B19

F22

J22

D24

D25

N22

M22

D18

C18

D17

D16

T24

U24

V24

V25

F16

P22

H22

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

SNN_FBA_CMD32

FBA_CMD34_DEBUG

FBA_CMD35_DEBUG

FOR DEBUG

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_WCK01

FBA_WCK01*

FBA_WCK23

FBA_WCK23*

FBA_WCK45

FBA_WCK45*

FBA_WCK67

FBA_WCK67*

FB_PLL_AVDD

C555

0.1uF

16V

10%

X7R

0402

COMMON

FBA_CMD[31..0]

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

TP501

TP502

FB_CLKFBA_CLK0

5

FBA_CLK0 FB_CLK

5

FBA_CLK1 FB_CLK

6

FBA_CLK1 FB_CLK

6

FBA_WCK01 FB_WCK

5

FBA_WCK01 FB_WCK

5

FBA_WCK23 FB_WCK

5

FBA_WCK23 FB_WCK

5

FBA_WCK45 FB_WCK

6

FBA_WCK45 FB_WCK

6

FBA_WCK67 FB_WCK

6

FBA_WCK67 FB_WCK

6

C554

0.1uF

16V

10%

X7R

0402

COMMON

C579

0.1uF

16V

10%

X7R

0402

COMMON

1

FB_CMD

5,6

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

104.5mA

C553

22uF

6.3V

20%

X6S

0805

COMMON

OUT

LB501 30ohm

BEAD_0603 COMMON

C552

22uF

4V

20%

X6S

0603W

NO STUFF

2

FBVDDQ

CKE*

R505

0402

R503 10k

0402 COMMON

R509 10k

0402

R510

0402

GND

1V8

FBA_CMD30

10k

COMMON

5 %

FBA_CMD14

5 %

RESET*

FBA_CMD13

COMMON

5 %

FBA_CMD29

10k

COMMON

5 %

3

4

FBA_D[63..0]

FBA_DBI[7..0]

FBA_EDC[7..0]

5,6

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FB_DBI

5,6

FB_EDC

5,6

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBA_D63

FBA_DBI0

FBA_DBI1

FBA_DBI2

FBA_DBI3

FBA_DBI4

FBA_DBI5

FBA_DBI6

FBA_DBI7

FBA_EDC0

FBA_EDC1

FBA_EDC2

FBA_EDC3

FBA_EDC4

FBA_EDC5

FBA_EDC6

FBA_EDC7

SNN_FBA_DQS_RN0

SNN_FBA_DQS_RN1

SNN_FBA_DQS_RN2

SNN_FBA_DQS_RN3

SNN_FBA_DQS_RN4

SNN_FBA_DQS_RN5

SNN_FBA_DQS_RN6

SNN_FBA_DQS_RN7

SNN_FB_VREF_D32

OUT

1

2

3

OUT

OUT

4

GND GND GND GND

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. N VIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO T HE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUTLIMITATION, THE WARRANTIES OF DESI GN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A

B

C

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

GPU Frame Buffer

CO-LAYOUT 0805 AND 0603

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

E

FD

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

GPU Frame Buffer

GPU Frame Buffer

GPU Frame Buffer

Design By:

Design By:

P85C

P85C

P85C

Design By:

James Lee V10

James Lee V10

James Lee V10

H

4 21Wednesday, April 05, 2017

4 21Wednesday, April 05, 2017

4 21Wednesday, April 05, 2017

of

A

B

C D

E

F G H

FBA bits 31..00

GDDR5_BGA170_MIRR

0.. 31

CMD

CS*

1

2

3

CMD0

CMD1

CMD2

CMD3

CMD4

CMD5

CMD6

CMD7

CMD8

CMD9

CMD10

CMD11

CMD12

CMD14

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

CMD31

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE*

A7_A8

A6_A11

ABI*

A12_RFU

A0_A10

A1_A9

RAS*

RST*CMD13

CKE*

CAS*

IN

GPIO10_FBVREF_SEL

32.. 63

CS*

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE*

A7_A8

A6_A11

ABI*

A12_RFU

A0_A10

A1_A9

RAS*

RST*

CKE*

CAS*

12

GND

R501

10k

5 %

0402

COMMON

1G1D1S

IN

IN

D

Q501

@discrete.q_fet_n_enh(sym_2):page5_i7

SOT323_1G1D1S

G

1

COMMON

S

GND

IN

FBVDDQ

R502

549ohm

1 %

0402

COMMON

R506

1.33k

1 %

0402

COMMON

GND

FBA_VREF_Q

3

0.300

2

30V

0.3A

1900mohm@10V / 1900mohm@4.5V / 1900mohm@2.5V

1.2A

0.2W

12V

FBA_CMD[15..0]

FBA_CLK0

4

FBA_CLK0*

4

R144

40.2ohm

1 %

0402

COMMON

FBA_CLK0_CM

GND

R504

931ohm

1 %

0402

COMMON

4

R143

40.2ohm

1 %

0402

COMMON

C153

10nF

25V

10%

X7R

0402

COMMON

6

C159

820pF

50V

10%

X7R

0402

COMMON

GND GND

12

15

5

0

8

10

11

2

1

3

4

7

6

9

13

14

0.300

FBA_CMD12

FBA_CMD15

FBA_CMD5

FBA_CMD0

FBA_CMD8

FBA_CMD10

FBA_CMD11

FBA_CMD2

FBA_CMD1

FBA_CMD3

FBA_CMD4

FBA_CMD7

FBA_CMD6

FBA_CMD9

FBA_CMD13

FBA_CMD14

OUT

0.140A

R507 121ohm

0402

BI

SNN_FBA_RFU_1

SNN_FBA_RFU_2

COMMON

1 %

FBA_VREFC

FBA_ZQ_1

FBA_D[31..0]

4

M1D

@memory.u_mem_sd_ddr5_x32(sym_5):page5_i94

BGA170

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

J13

ZQ

J10

SEN

GND

M1B

@memory.u_mem_sd_ddr5_x32(sym_6):page5_i98

BGA170

COMMON

Normal

J1

MF_VSS/SOE*

add 1k to VSS

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

FBVDDQ

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

B12

B14

B3

D1

D12

D14

D3

E10

E5

F1

F12

F14

F3

G13

G2

H12

H3

K12

K3

L13

L2

M1

M12

M14

M3

N10

N5

P1

P12

P14

P3

T1

T12

T14

T3

FBVDDQ

PLACE Directly Under DRAM

FBVDDQ

C520

1uF

6.3V

10%

X6S

0402

COMMON

C534

1uF

6.3V

10%

X6S

0402

COMMON

C517

1uF

6.3V

10%

X6S

0402

COMMON

C155

1uF

6.3V

10%

X6S

0402

COMMON

C530

1uF

6.3V

10%

X6S

0402

COMMON

C501

1uF

6.3V

10%

X6S

0402

COMMON

C523

1uF

6.3V

10%

X6S

0402

COMMON

C518

1uF

6.3V

10%

X6S

0402

COMMON

FBVDDQ

C515

1uF

6.3V

10%

X6S

0402

COMMON

C513

1uF

6.3V

10%

X6S

0402

COMMON

C502

10uF

4V

20%

X6S

0603

COMMON

C525

1uF

6.3V

10%

X6S

0402

COMMON

C511

1uF

6.3V

10%

X6S

0402

COMMON

C514

1uF

6.3V

10%

X6S

0402

COMMON

C531

1uF

6.3V

10%

X6S

0402

COMMON

C503

10uF

4V

20%

X6S

0603

COMMON

C539

1uF

6.3V

10%

X6S

0402

COMMON

C157

1uF

6.3V

10%

X6S

0402

COMMON

C504

10uF

4V

20%

X6S

0603

COMMON

GND

GND

C535

1uF

6.3V

10%

X6S

0402

COMMON

C156

1uF

6.3V

10%

X6S

0402

COMMON

C505

10uF

4V

20%

X6S

0603

COMMON

1

2

GND

PLACE CLOSE TO DRAM

3

FBVDDQ

C163

10uF

4V

20%

X6S

0603

COMMON

C160

10uF

4V

20%

X6S

0603

COMMON

C161

22uF

4V

20%

X6S

0603W

COMMON

C162

22uF

4V

20%

X6S

0603W

COMMON

M1A

@memory.u_mem_sd_ddr5_x32(sym_1):page5_i76

BGA170

COMMON

FBA_D0

0

FBA_D1

FB_DBI

FBA_DBI[7..0]

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. N VIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO T HE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUTLIMITATION, THE WARRANTIES OF DESI GN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

BI

OUT

FB_EDC

FBA_EDC[7..0]

A

4,6

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

4,6

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

B

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

8

9

10

11

12

13

14

15

IN

IN

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_EDC0

FBA_DBI0

FBA_EDC1

FBA_DBI1

FBA_WCK01

4

FBA_WCK01*

4

C

NORMA L

A4

DQ0

A2

DQ1

B4

DQ2

B2

DQ3

E4

DQ4

E2

DQ5

F4

DQ6

F2

DQ7

C2

EDC0

D2

DBI0

x32

A11

DQ8

A13

DQ9

B11

DQ10

B13

DQ11

E11

DQ12

E13

DQ13

F11

DQ14

F13

DQ15

C13

EDC1

D13

DBI1

D4

WCK01

D5

WCK01

SNN_FBA_VREFD_1 SNN_FBA_VREFD_2

A10

VREFD

x16

NC

NC

NC

NC

NC

NC

NC

NC

GND

NC

ASSEMBLY

PAGE DETAIL

IN

IN

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

24

25

26

27

28

29

30

31

<ASSEMBLY_DESCRIPTION>

FBA bits 31..00

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_WCK23

4

FBA_WCK23*

4

FBA_EDC2

FBA_DBI2

FBA_EDC3

FBA_DBI3

M1C

@memory.u_mem_sd_ddr5_x32(sym_3):page5_i97

BGA170

COMMON

NORMA L

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

x32

V4

DQ24

V2

DQ25

T4

DQ26

T2

DQ27

N4

DQ28

N2

DQ29

M4

DQ30

M2

DQ31

R2

EDC3

P2

DBI3

P4

WCK23

P5

WCK23

E

VREFD

GND

PLACE Around DRAM

4

V10

x16

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FD

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

FBA bits 31..00

FBA bits 31..00

FBA bits 31..00

Design By:

Design By:

P85C

P85C

P85C

Design By:

James Lee V10

James Lee V10

James Lee V10

H

5 21Wednesday, April 05, 2017

5 21Wednesday, April 05, 2017

5 21Wednesday, April 05, 2017

A

FBA bits 63..32

B

C D

E

F G H

FBVDDQ

PLACE Directly Under DRAM

FBVDDQ

C158

1uF

6.3V

10%

X6S

0402

COMMON

C533

1uF

6.3V

10%

X6S

0402

COMMON

PLACE CLOSE TO DRAM

C521

1uF

6.3V

10%

X6S

0402

COMMON

C526

1uF

6.3V

10%

X6S

0402

COMMON

C524

1uF

6.3V

10%

X6S

0402

COMMON

C154

1uF

6.3V

10%

X6S

0402

COMMON

C538

1uF

6.3V

10%

X6S

0402

COMMON

C537

1uF

6.3V

10%

X6S

0402

COMMON

C528

1uF

6.3V

10%

X6S

0402

COMMON

C519

1uF

6.3V

10%

X6S

0402

COMMON

FBVDDQ

C509

10uF

4V

20%

X6S

0603

COMMON

C536

1uF

6.3V

10%

X6S

0402

COMMON

C512

1uF

6.3V

10%

X6S

0402

COMMON

C507

10uF

4V

20%

X6S

0603

COMMON

C510

1uF

6.3V

10%

X6S

0402

COMMON

C540

1uF

6.3V

10%

X6S

0402

COMMON

C516

1uF

6.3V

10%

X6S

0402

COMMON

C532

1uF

6.3V

10%

X6S

0402

COMMON

C506

10uF

4V

20%

X6S

0603

COMMON

GND

GND

GND

C529

1uF

6.3V

10%

X6S

0402

COMMON

C522

1uF

6.3V

10%

X6S

0402

COMMON

C508

10uF

4V

20%

X6S

0603

COMMON

1

2

3

J1

C10

C5

D11

G1

G11

G14

G4

L1

L11

L14

L4

P11

R10

R5

B1

B12

B14

B3

D1

D12

D14

D3

E10

E5

F1

F12

F14

F3

G13

G2

H12

H3

K12

K3

L13

L2

M1

M12

M14

M3

N10

N5

P1

P12

P14

P3

T1

T12

T14

T3

FBVDDQ

1

2

3

GDDR5_BGA170_MIRR

0.. 31

CMD

CS*

CMD0

A3_BA3

CMD1

A2_BA0

CMD2

A4_BA2

CMD3

A5_BA1

CMD4

WE*

CMD5

A7_A8

CMD6

A6_A11

CMD7

ABI*

CMD8

A12_RFU

CMD9

A0_A10

CMD10

A1_A9

CMD11

RAS*

CMD12

RST*

CMD13

CKE*

CMD14

CAS*

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

CMD31

32.. 63

CS*

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE*

A7_A8

A6_A11

ABI*

A12_RFU

A0_A10

A1_A9

RAS*

RST*

CKE*

CAS*

M2B

FBA_CMD[31..16]

IN

FBA_CLK1

IN

FBA_CLK1*

IN

4

4

4

R512

40.2ohm

1 %

0402

COMMON

FBA_CLK1_CM

C541

10nF

25V

10%

X7R

0402

COMMON

M2D

@memory.u_mem_sd_ddr5_x32(sym_5):page6_i77

BGA170_MIRR

G12

K11

K10

H11

H10

COMMON

L3

RAS

G3

CAS

WE

L12

CS

J4

ABI

K4

A0_A10

K5

A1_A9

A2_BA0

A3_BA3

A4_BA2

A5_BA1

H5

A6_A11

H4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

FBA_CMD28

28

FBA_CMD31

31

FBA_CMD21

21

FBA_CMD16

16

FBA_CMD24

24

FBA_CMD26

26

FBA_CMD27

27

FBA_CMD18

18

FBA_CMD17

17

FBA_CMD19

19

FBA_CMD20

20

FBA_CMD23

23

FBA_CMD22

22

FBA_CMD25

25

FBA_CMD29

29

FBA_CMD30

30

R511

40.2ohm

1 %

0402

COMMON

SNN_FBA_RFU7

SNN_FBA_RFU8

GND

IN

5

C527

820pF

50V

10%

X7R

0402

COMMON

R508

121ohm

0402

COMMON

1 %

FBA_VREFC

FBA_ZQ_2_B

GND GND

J14

VREFC

J13

ZQ

J10

SEN

GND

@memory.u_mem_sd_ddr5_x32(sym_7):page6_i87

BGA170_MIRR

COMMON

Mirrored

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

SOE*/MF_VDD

add 1k to VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

FBA_D[63..32]

BI

FB_DBI

FBA_DBI[7..0]

BI

4

FB_EDC

FBA_EDC[7..0]

IN

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. N VIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO T HE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUTLIMITATION, THE WARRANTIES OF DESI GN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A

4,5

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

4,5

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

FBA_WCK45

IN

FBA_WCK45*

IN

B

4

M2A

@memory.u_mem_sd_ddr5_x32(sym_2):page6_i66

BGA170_MIRR

COMMON

MIRRORED

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

4

4

FBA_EDC4

FBA_DBI4

FBA_EDC5

FBA_DBI5

V11

V13

T11

T13

N11

N13

M11

M13

R13

P13

V4

V2

T4

T2

N4

N2

M4

M2

R2

P2

P4

P5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

EDC0

DBI0

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

EDC1

DBI1

WCK01

WCK01

x16x32

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

SNN_FBA_VREFD_3 SNN_FBA_VREFD_4

V10

VREFD

C

ASSEMBLY

PAGE DETAIL

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

IN

IN

<ASSEMBLY_DESCRIPTION>

FBA bits 63..32

FBA_WCK67

FBA_WCK67*

4

4

FBA_EDC6

FBA_DBI6

FBA_EDC7

FBA_DBI7

M2C

@memory.u_mem_sd_ddr5_x32(sym_4):page6_i88

BGA170_MIRR

COMMON

MIRRORED

x32 x16

A11

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

EDC2

DBI2

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

EDC3

DBI3

WCK23

WCK23

VREFD

NC

NC

NC

NC

NC

NC

NC

NC

GND

NC

A13

B11

B13

E11

E13

F11

F13

C13

D13

A4

A2

B4

B2

E4

E2

F4

F2

C2

D2

D4

D5

E

FBVDDQ

C167

10uF

4V

20%

X6S

0603

COMMON

C164

10uF

4V

20%

X6S

0603

COMMON

C165

22uF

4V

20%

X6S

0603W

COMMON

C166

22uF

4V

20%

X6S

0603W

COMMON

GND

PLACE Around DRAM

4

A10

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FD

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

FBA bits 31..00

FBA bits 31..00

FBA bits 31..00

Design By:

Design By:

P85C

P85C

P85C

Design By:

James Lee V10

James Lee V10

James Lee V10

H

6 21Wednesday, April 05, 2017

6 21Wednesday, April 05, 2017

6 21Wednesday, April 05, 2017

A

B

C D

E

F G H

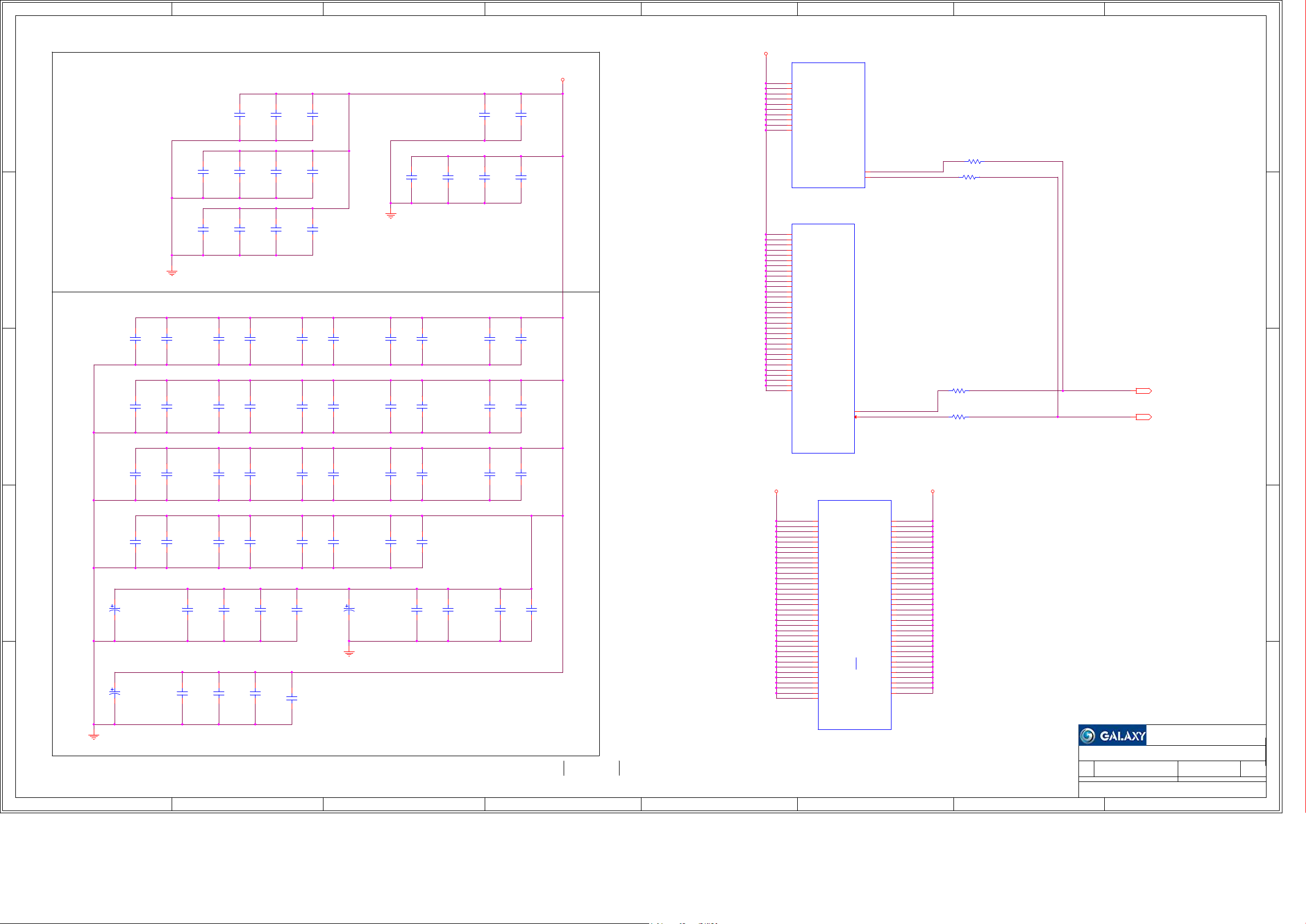

NVVVD Decoupling

G1D

NVVDD

@digital.u_gpu_gb2c_64(sym_7):page7_i55

BGA595

COMMON

NVVDD

1

PLACE UNDER GPU

C576

10uF

6.3V

20%

X6S

0603

COMMON

C580

10uF

6.3V

20%

X6S

0603

2

GND

COMMON

PLACE NEAR GPU

C634

C635

22uF

22uF

10V

4V

10%

20%

X7R

X6S

0805

0603W

COMMON

NO STUFF

C647

C648

10uF

3

16V

10%

X6S

0805

NO STUFF

22uF

4V

20%

X6S

0603W

NO STUFF

C584

1uF

6.3V

10%

X6S

0402

COMMON

C587

10uF

6.3V

20%

X6S

0603

COMMON

C592

10uF

6.3V

20%

X6S

0603

COMMON

CO-Layout 0603 and 0805

C638

22uF

10V

10%

X7R

0805

COMMON

C653

10uF

16V

10%

X6S

0805

NO STUFF

C639

22uF

4V

20%

X6S

0603W

NO STUFF

C652

22uF

4V

20%

X6S

0603W

NO STUFF

C575

1uF

6.3V

10%

X6S

0402

COMMON

C604

10uF

6.3V

20%

X6S

0603

COMMON

C597

10uF

6.3V

20%

X6S

0603

COMMON

C636

22uF

10V

10%

X7R

0805

COMMON

C139

10uF

16V

10%

X6S

0805

NO STUFF

C586

1uF

6.3V

10%

X6S

0402

COMMON

C582

10uF

6.3V

20%

X6S

0603

COMMON

C602

10uF

6.3V

20%

X6S

0603

COMMON

C637

22uF

4V

20%

X6S

0603W

NO STUFF

C120

22uF

4V

20%

X6S

0603W

NO STUFF

C615

10uF

6.3V

20%

X6S

0603

COMMON

GND

C649

22uF

10V

10%

X7R

0805

NO STUFF

C146

10uF

16V

10%

X6S

0805

NO STUFF

C650

22uF

4V

20%

X6S

0603W

NO STUFF

C145

22uF

4V

20%

X6S

0603W

NO STUFF

C608

10uF

6.3V

20%

X6S

0603

COMMON

C566

1uF

6.3V

10%

X6S

0402

COMMON

C598

10uF

6.3V

20%

X6S

0603

COMMON

C655

10uF

16V

10%

X6S

0805

NO STUFF

C138

10uF

16V

10%

X6S

0805

NO STUFF

C585

1uF

6.3V

10%

X6S

0402

COMMON

C578

10uF

6.3V

20%

X6S

0603

COMMON

C654

22uF

4V

20%

X6S

0603W

NO STUFF

C137

22uF

4V

20%

X6S

0603W

NO STUFF

7/14 VDDS

L11

VDDS

L17

VDDS

M14

VDDS

P10

VDDS

P12

VDDS

P16

VDDS

P18

VDDS

T14

VDDS

U11

VDDS

U17

VDDS

GM108

RSVD

RSVD

G1C

@digital.u_gpu_gb2c_64(sym_11):page7_i54

BGA595

COMMON

11/14 NVVDD

K10

VDD

K12

VDD

K14

VDD

K16

VDD

K18

VDD

L13

VDD

L15

VDD

M10

VDD

M12

VDD

M16

VDD

M18

VDD

N11

VDD

N13

VDD

N15

VDD

N17

VDD

P14

VDD

R11

VDD

R13

VDD

R15

VDD

R17

VDD

T10

VDD

T12

VDD

T16

VDD

T18

VDD

U13

VDD

U15

VDD

V10

VDD

V12

VDD

V14

VDD

V16

VDD

V18

VDD

VDDS_SENSE

GNDS_SENSE

VDD_SENSE

GND_SENSE

F4

F3

GPU_NVVDD_VSENSE_L

F2

GPU_NVVDD_GNDSNS_L

F1

GPU_NVDS_VSENSE

GPU_GND_S_GSENSE

R122

R117

1

GPU_NVVDD_VSENSE

nv_res

R524

0ohm

NO STUFF

0402

0.05 ohm

nv_res

R525

0ohm

GPU_NVVDD_GNDSNS

NO STUFF

0402

0.05 ohm

2

nv_res

0ohm

COMMON

0402

0.05 ohm

nv_res

0ohm

0402

COMMON

0.05 ohm

19

19

OUT

3

OUT

C144

C143

10uF

22uF

16V

4V

10%

20%

X6S

X6S

0805

0603W

NO STUFF

NO STUFF

C119

C140

22uF

22uF

6.3V

4V

20%

20%

X6S

X6S

0805

0603W

NO STUFF

4

C644

330uF

NO STUFF

20%

2V@105degC

AL-Polymer

3.5A@105degC,100KHz

0.006ohm

SMD_7343

NO STUFF

C642

22uF

4V

20%

X6S

0603W

NO STUFF

C136

10uF

16V

10%

X6S

0805

NO STUFF

C132

22uF

6.3V

20%

X6S

0805

NO STUFF

C643

22uF

6.3V

20%

X6S

0805

COMMON

C135

22uF

4V

20%

X6S

0603W

NO STUFF

C131

22uF

4V

20%

X6S

0603W

NO STUFF

C646

22uF

6.3V

20%

X6S

0805

COMMON

C645

22uF

4V

20%

X6S

0603W

NO STUFF

CO-Layout 0603, 0805 and PO SCAP

C630

330uF

NO STUFF

20%

2V@105degC

AL-Polymer

3.5A@105degC,100KHz

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. N VIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO T HE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

0.006ohm

SMD_7343

GND

A

C623

10uF

16V

10%

X6S

0805

COMMON

C622

22uF

4V

20%

X6S

0603W

NO STUFF

C631

22uF

6.3V

20%

X6S

0805

COMMON

C632

22uF

4V

20%

X6S

0603W

NO STUFF

B

C142

10uF

16V

10%

X6S

0805

NO STUFF

C641

22uF

6.3V

20%

X6S

0805

COMMON

C141

22uF

4V

20%

X6S

0603W

NO STUFF

C640

22uF

4V

20%

X6S

0603W

NO STUFF

GND

C658

330uF

NO STUFF

20%

2V@105degC

AL-Polymer

3.5A@105degC,100KHz

0.006ohm

SMD_7343

C133

10uF

16V

10%

X6S

0805

NO STUFF

C129

22uF

6.3V

20%

X6S

0805

NO STUFF

C134

22uF

4V

20%

X6S

0603W

NO STUFF

C130

22uF

4V

20%

X6S

0603W

NO STUFF

C656

22uF

6.3V

20%

X6S

0805

NO STUFF

C657

22uF

4V

20%

X6S

0603W

NO STUFF

C128

10uF

16V

10%

X6S

0805

NO STUFF

C661

22uF

6.3V

20%

X6S

0805

NO STUFF

C127

22uF

4V

20%

X6S

0603W

NO STUFF

C660

22uF

4V

20%

X6S

0603W

NO STUFF

C

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

NVVVD Decoupling

NVVDD NVVDD

E

G1E

@digital.u_gpu_gb2c_64(sym_6):page7_i56

BGA595

COMMON

6/14 XVDD

G1

XVDD

G2

XVDD

G3

XVDD

G4

XVDD

G5

XVDD

G6

XVDD

G7

XVDD

H3

XVDD

H4

XVDD

H6

XVDD

J1

XVDD

J2

XVDD

J3

XVDD

J4

XVDD

J5

XVDD

J6

XVDD

J7

XVDD

K1

XVDD

K2

XVDD

K3

XVDD

K4

XVDD

K5

XVDD

K6

XVDD

K7

XVDD

L3

XVDD

L4

XVDD

M1

M2

M3

M4

M5

M7

N1

N2

N3

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

GM1 08

RSVD

FD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

XVDD

N4

N5

N7

P3

P4

P6

R1

R2

R3

R4

R5

R6

R7

T1

T2

T3

T4

T5

T6

T7

U3

U4

U6

V1

V2

V3

V4

V5

V6

V7

W1

W2

W3

W4

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

G

Galaxy Microsystems (HK) Ltd.

NVVVD Decoupling

NVVVD Decoupling

NVVVD Decoupling

Design By:

Design By:

P85C

P85C

P85C

Design By:

James Lee V10

James Lee V10

James Lee V10

H

7 21Wednesday, April 05, 2017

7 21Wednesday, April 05, 2017

7 21Wednesday, April 05, 2017

4

5

Loading...

Loading...