NSC LM2636MX, LM2636MTCX, LM2636M Datasheet

LM2636

5-Bit Programmable Synchronous Buck Regulator

Controller

General Description

The LM2636 is a high speed controller designed specifically

for use in synchronous DC/DC buck converters for advance

d microprocessors. A 5-bit DAC accepts the VID code directly fromthe CPU and adjusts the output voltage from 1.3V

to 3.5V.It provides the power good, over-voltage protection,

and output enable features as required by Intel VRM specifications. Current limiting is achieved by monitoring the voltage drop across the r

DS_ON

of the high side MOSFET, which

eliminates an expensive current sense resistor.

The LM2636 employs a fixed-frequency voltage mode PWM

architecture. To provide a faster response to a large and fast

load transient, two ultra-fast comparators are built in to monitor the output voltage and override the primary control loop

when necessary. The PWM frequency is adjustable from 50

kHz to 1 MHz through an external resistor. The wide range of

PWM frequency gives the power supply designer the flexibility to make trade-offs between load transient response performance, MOSFET cost and the overall efficiency. The

adaptive non-overlapping MOSFET gate drivers help avoid

any potential shoot-through problem while maintaining high

efficiency.BiCMOS gate drivers with rail-to-rail swing ensure

that no spurious turn-on occur. When only 5V is available, a

bootstrap structure can be employed to accommodate an

NMOS high side switch. The precision reference trimmed to

2.5%over temperature is available externally for use by

other regulators. Dynamic positioning of load voltage, which

helps cut the number of output capacitors, can also be implemented easily.

Features

n 1.3V to 3.5V 5-bit programmable output voltage

n Synchronous rectification

n Power Good flag and output enable

n Over-voltage protection

n Initial Output Accuracy: 1.5%over temperature

n Current limit without external sense resistor

n Adaptive non-overlapping MOSFET gate drives

n Adjustable switching frequency: 50 kHz to 1 MHz

n Dynamic output voltage positioning

n 1.256V reference voltage available externally

n Plastic SO-20 package and TSSOP-20 package

Applications

n Motherboard power supply/VRM for Cyrix Gxm, Cyrix

Gxi, Cyrix MII, Pentium

™

II, Pentium Pro, 6x86 and K6

processors

n 5V to 1.3V–3.5V high current power supplies

Typical Application

Pentium™is a trademark of Intel Corporation.

DS100834-1

FIGURE 1. 5V to 1.3V–3.5V, 14A Power Supply

October 1999

LM2636 5-Bit Programmable Synchronous Buck Regulator Controller

© 1999 National Semiconductor Corporation DS100834 www.national.com

Connection Diagrams

Pin Descriptions

LSGATE (Pin 1): Gate drive for the low-side N-channel

MOSFET. This signal is interlocked with HSGATE (Pin 20) to

avoid a shoot-through problem.

BOOTV (Pin 2): Power supply for high-side N-channel

MOSFET gate drive. The voltage should be at least one gate

threshold above the converter input voltage to properly operate the high-side N-FET.

PGND (Pin 3): Ground for high current circuitry. It should be

connected to system ground.

SGND (Pin 4): Ground for signal level circuitry. It should be

connected to system ground.

V

CC

(Pin 5): Power supply for the controller.

SENSE (Pin 6): Converter output voltage sensing. It pro-

vides input for power good, fast dual comparator control

loop, and over-voltage protection circuitry. It is recommended that a 0.1 µF capacitor be connected between this

pin and ground to avoid potential noise problems.

IMAX (Pin 7): Current limit threshold setting. It sinks a fixed

180 µA current. By connecting a resistor between the high

side MOSFET drain and this pin, a fixed voltage drop can be

built across the resistor. This voltage drop is compared with

the V

DS

of the high-side N-MOSFET to determine if an over-

current condition has occurred.

IFB (Pin 8): High-side N-MOSFET source voltage sensing.

This pin is one V

DS

below drain voltage. When this voltage is

lower than that of IMAX pin during the time the high-side FET

is on, it means V

DS

is higher than the preset voltage across

the IMAX resistor, which can be interpreted as an overcurrent condition.

V

REF

(Pin 9): Bandgap reference voltage. This voltage is

mainly for use by other power supplies on the motherboard

which need a reference.

EA_OUT (Pin 10): Output of the error amplifier. The voltage

level on this pin is compared with an internally generated

ramp signal to determine the duty cycle. This pin is necessary for compensating the primary control loop.

FB (Pin 11): Inverting input of the error amplifier.A pin necessary for compensating the control loop.

FREQ_ADJ (Pin 12): Switching frequency adjustment.

Switching frequency can be adjusted by changing the

grounding resistance on this pin.

PWRGD (Pin 13): Power Good. There are two windows

around the DAC output voltage that are associated with

PWRGD pin, the

±

10%window and the±8%window. If

PWRGD is initially high (open drain state) and output voltage

travels out of

±

10%window, PWRGD goes to low (low impedance to ground). If PWRGD is initially low and output

voltage travels into the

±

8%window and has stayed within

the window for at least 10 ms, PWRGD goes to high. A

PWRGD high means the output voltage is at least within the

±

10%window whereas a PWRGD low indicates the output

voltage is definitely outside the

±

8%window.

VID4:0 (Pins 14, 15, 16, 17, 18): Voltage Identification

Code. The five pins accept an open-ground pattern 5-bit binary code from outside the chip (typically from the CPU) for

generating the desired output voltage. Each VID pin is internally pulled up to V

CC

via a 90 µA current source.

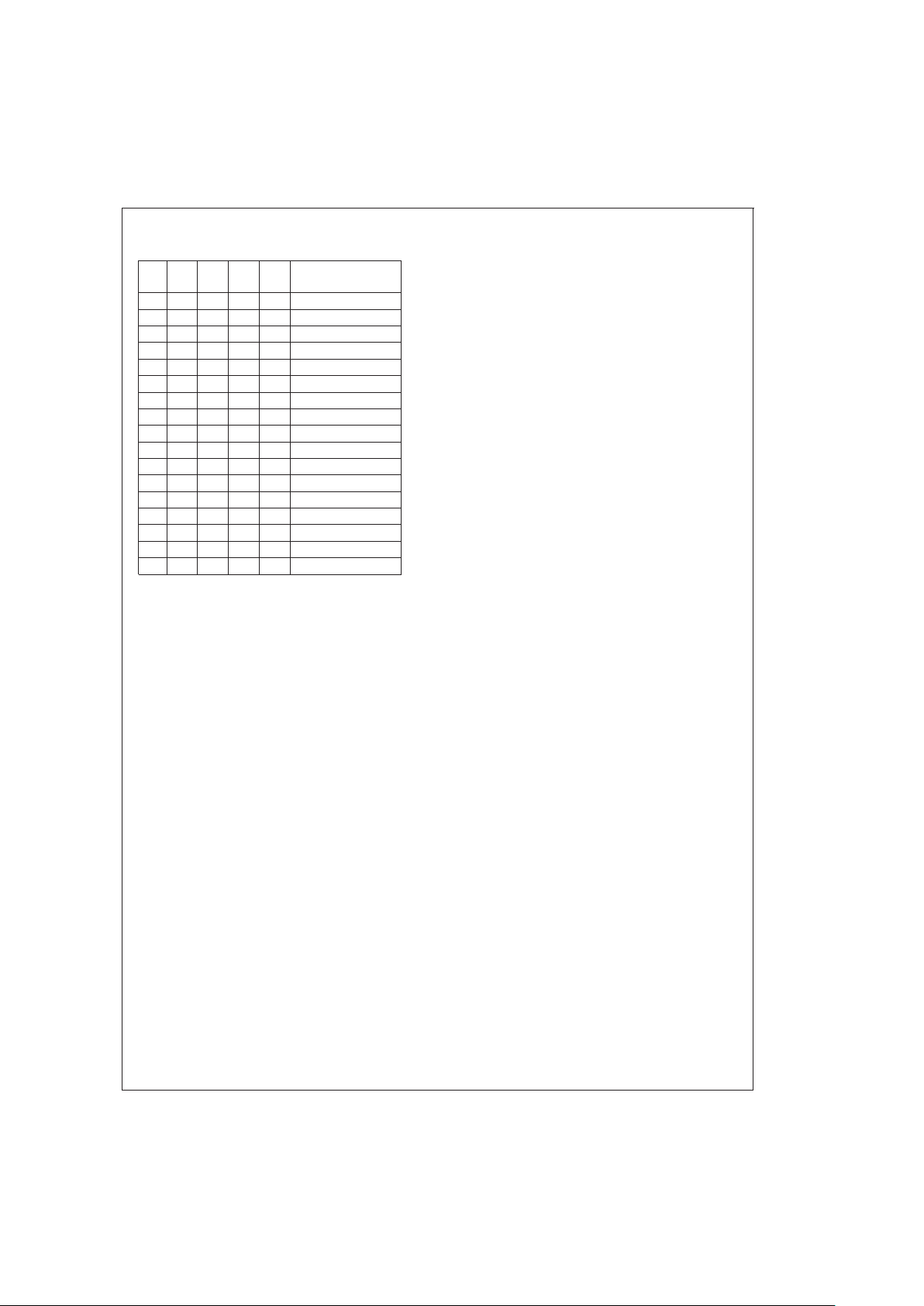

Table 1

shows the code table.

OUTEN (Pin 19): Output Enable. The output voltage is dis-

abled when this pin is pulled low. It is internally pulled up to

V

CC

via a 90 µA current source.

HSGATE (Pin 20): Gate drive for the high-side N-channel

MOSFET. This signal is interlocked with LSGATE (Pin 1) to

avoid a shoot-through problem.

TABLE 1. VID Code and DAC Output

V

ID4VID3VID2VID1VID0

Rated Output

Voltage (V)

01111 1.30

01110 1.35

01101 1.40

01100 1.45

01011 1.50

01010 1.55

01001 1.60

01000 1.65

00111 1.70

00110 1.75

00101 1.80

00100 1.85

00011 1.90

00010 1.95

00001 2.00

TOP VIEW

DS100834-3

Plastic SO-20

Order Number LM2636M

See NS Package Number M20B

TOP VIEW

DS100834-3

Plastic TSSOP-20

Order Number LM2636MTC

See NS Package Number MTC20

LM2636

www.national.com 2

Pin Descriptions (Continued)

TABLE 1. VID Code and DAC Output (Continued)

V

ID4VID3VID2VID1VID0

Rated Output

Voltage (V)

00000 2.05

11111 (shutdown)

11110 2.1

11101 2.2

11100 2.3

11011 2.4

11010 2.5

11001 2.6

11000 2.7

10111 2.8

10110 2.9

10101 3.0

10100 3.1

10011 3.2

10010 3.3

10001 3.4

10000 3.5

LM2636

www.national.com3

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

(All voltages are referenced to the PGND and SGND pins.)

V

CC

7V

BOOTV 18V

Junction Temperature 150˚C

DC Power Dissipation (Note 2) 1.42W

Storage Temperature −65˚C to +150˚C

Soldering Time, Temperature

Wave (4 seconds)

Infrared (10 seconds)

Vapor Phase (75 seconds)

260˚C

240˚C

219˚C

ESD Susceptibility (Note 3) 2 kV

Recommended Operating

Conditions

(Note 1)

Supply Voltage Range (V

CC

) 4.5V to 5.5V

Junction Temperature Range 0˚C to +125˚C

Electrical Characteristics

VCC= 5V unless otherwise indicated under the Conditions column. Typicals and limits appearing in plain type apply for TA=

T

J

= +25˚C. Limits appearing in boldface type apply over 0˚C to +70˚C.

Symbol Parameter Conditions Min Typ Max Units

V

BOOTV

FET Driver Supply

Voltage

18 V

V

DACOUT

5-Bit DAC Output

Voltage

VID4:0=01111 1.284 1.304 1.324

V

VID4:0=01101 1.385 1.406 1.427

VID4:0=01011 1.483 1.506 1.529

VID4:0=01001 1.585 1.609 1.633

VID4:0=00111 1.683 1.709 1.735

VID4:0=00101 1.784 1.811 1.838

VID4:0=00001 1.983 2.013 2.043

VID4:0=11101 2.173 2.206 2.239

VID4:0=11010 2.471 2.509 2.547

VID4:0=10111 2.768 2.81 2.852

∆V

OUT

DC Load Regulation I

OUT

=0 to 14A

Figure 2

−5

mV

DC Line Regulation V

IN

=4.75V to 5.25V

Figure 2

1

G

EA

Error Amplifier DC Gain 85 dB

SR

EA

Error Amplifier Slew

Rate

6 V/µs

BW

EA

Error Amplifier Unity

Gain Bandwidth

5 MHz

I

Q_V

CC

Operating VCCCurrent OUTEN=VCC=5V, VID=10111 1.5 2.5 4

mA

Shutdown V

CC

Current OUTEN Floating, VID0:4 Floating 1 1.5 3

I

Q_BOOTV

BOOTV Pin Quiescent

Current

BOOTV=12V, OUTEN=0, VID0:4

Floating

4µA

D

MAX

Maximum Duty Cycle 90

%

D

MIN

Minimum Duty Cycle 0

%

R

SENSE

SENSE Pin Resistance

to Ground

7 11.5 16 kΩ

R

DS_SRC

FET Driver

Drain-Source ON

Resistance when

Sourcing Current

BOOTV=5V

7 Ω

R

DS_SINK

FET Driver

Drain-Source ON

Resistance when

Sinking Current

(Independent of BOOTV Voltage)

1.7 Ω

f

OSC

Oscillator Frequency RFA=84kΩ 250 300 350

kHzR

FA

=22kΩ 1000

R

FA

= 10.5 kΩ 2000

I

MAX

IMAX Pin Sink Current V

IMAX

= 5V, V

IFB

= 6V, VCC=5V 130 180 230 µA

LM2636

www.national.com 4

Electrical Characteristics (Continued)

VCC= 5V unless otherwise indicated under the Conditions column. Typicals and limits appearing in plain type apply for TA=

TJ= +25˚C. Limits appearing in boldface type apply over 0˚C to +70˚C.

Symbol Parameter Conditions Min Typ Max Units

V

OUTEN_IH

OUTEN Pin Input Logic

Low to Logic High Trip

Point

OUTEN Voltage

↑

3.5 3.0 V

V

OUTEN_IL

OUTEN Pin Input Logic

High to Logic Low Trip

Point

OUTEN Voltage

↓

1.8 1.5 V

V

REF

Band Gap Reference I

VREF

=0mA 1.225 1.256 1.287 V

V

REF_LOAD

Reference Voltage at

Full Load

I

VREF

= 0.5 mA, Sourcing

1.223 1.254 1.285 V

V

REF_525

Reference Voltage at

High Line

I

VREF

= 0 mA, VCC= 5.25V

1.226 1.257 1.288 V

V

REF_475

Reference Voltage at

Low Line

I

VREF

= 0 mA, VCC= 4.75V

1.224 1.255 1.286 V

∆V

REF_LOAD

Reference Voltage

Load Regulation

I

VREF

= 0.5 mA, Sourcing

−2 mV

∆V

REF_LINE

Reference Voltage Line

Regulation

I

VREF

= 0 mA, VCCChanges from

5.25V to 4.75V

−0.5 mV

V

SAWL

Ramp Signal Valley

Voltage

1.25 V

V

SAWH

Ramp Signal Peak

Voltage

3.25 V

V

PWRBAD_GD

PWRGD Pin↓Trip

Points (see Pin

Description for Pin 13)

%

above DAC Output Voltage, when

Output Voltage

↑

10

%

%

below DAC Output Voltage, when

Output Voltage

↓

−10

V

PWRGD_BAD

PWRGD Pin↑Trip

Points (see Pin

Description for Pin 13)

%

above DAC Output Voltage, when

Output Voltage

↓

8

%

%

below DAC Output Voltage, when

Output Voltage

↑

−8

V

OVP

Over-voltage Protection

Trip Point

%

above DAC Output Voltage

15

%

t

PWRGD

Power Good Response

Time

V

SENSE

Rises from 0V to Rated

V

OUT

2 6 15 µs

t

PWRBAD

Power Not Good

Response Time

V

SENSE

Falls from Rated V

OUT

to 0V

2 6 15 µs

I

OUTEN

OUTEN Pin Internal

Pull-Up Current

60 90 130 µA

V

VID_IH

VID Pins Logic High

Trip Point

3.5 3.0 V

V

VID_IL

VID Pins Logic Low

Trip Point

1.8 1.3 V

I

VID

VID0:4 Internal Pull-Up

Current

60 90 130 µA

t

SS

Soft Start Duration

2048

clock

cycles

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur.Recommended Operating Conditions are conditions under which

the device operates correctly. Recommended Operating Conditions do not imply guaranteed performance limits.

Note 2: Maximum allowable DC power dissipation is a function of the maximum junction temperature, T

JMAX

, the junction-to-ambient thermal resistance, θJA, and

the ambient temperature, T

A

. The maximum allowable power dissipation at any ambient temperature is calculated using:

The junction-to-ambient thermal resistance, θJA, for LM2636 in the M20B package is 88˚C/W, and 120˚C/W for the MTC20 package.

LM2636

www.national.com5

Loading...

Loading...