NSC LM12L458CIV Datasheet

LM12L458

12-Bit + Sign Data Acquisition System with

Self-Calibration

LM12L458 12-Bit + Sign Data Acquisition System with Self-Calibration

July 1999

General Description

The LM12L458 is a highly integrated 3.3V Data Acquisition

System. It combines a fully-differential self-calibrating (correcting linearity and zero errors) 13-bit (12-bit + sign)

analog-to-digital converter (ADC) and sample-and-hold

(S/H) with extensive analog functions and digital functionality. Up to 32 consecutive conversions, using two’s complement format, can be stored in an internal 32-word (16-bit

wide) FIFO data buffer. An internal 8-word RAM can store

the conversion sequence for up to eight acquisitions through

the LM12L458’s eight-input multiplexer. The LM12L458 can

also operate with 8-bit + sign resolution and in a supervisory

“watchdog” mode that compares an input signal against two

programmable limits. Programmable acquisition times and

conversion rates are possible through the use of internal

clock-driven timers.

All registers, RAM, and FIFO are directly addressable

through the high speed microprocessor interface to either an

8-bit or 16-bit databus. The LM12L458 includes a direct

memory access (DMA) interface for high-speed conversion

data transfer.

Applications

n Data Logging

n Process Control

n Energy Management

n Medical Instrumentation

Key Specifications

=

(f

6 MHz)

CLK

n Resolution 12-bit + sign or 8-bit + sign

n 13-bit conversion time 7.3 µs

n 9-bit conversion time 3.5 µs

n 13-bit Through-put rate 106k samples/s (min)

n Comparison time (“watchdog” mode) 1.8 µs (max)

n ILE

n V

range GND to V

IN

n Power dissipation 15 mW (max)

n Stand-by mode 5 µW (typ)

n Single supply 3V to 5.5V

±

1 LSB (max)

Features

n Three operating modes: 12-bit + sign, 8-bit + sign, and

“watchdog”

n Single-ended or differential inputs

n Built-in Sample-and-Hold

n Instruction RAM and event sequencer

n 8-channel multiplexer

n 32-word conversion FIFO

n Programmable acquisition times and conversion rates

n Self-calibration and diagnostic mode

n 8- or 16-bit wide databus microprocessor or DSP

interface

n CMOS compatible I/O

+

A

TRI-STATE®is a registeredtrademark of National Semiconductor Corporation.

®

AT

is a registered trademark of International Business Machines Corporation.

© 1999 National Semiconductor Corporation DS011711 www.national.com

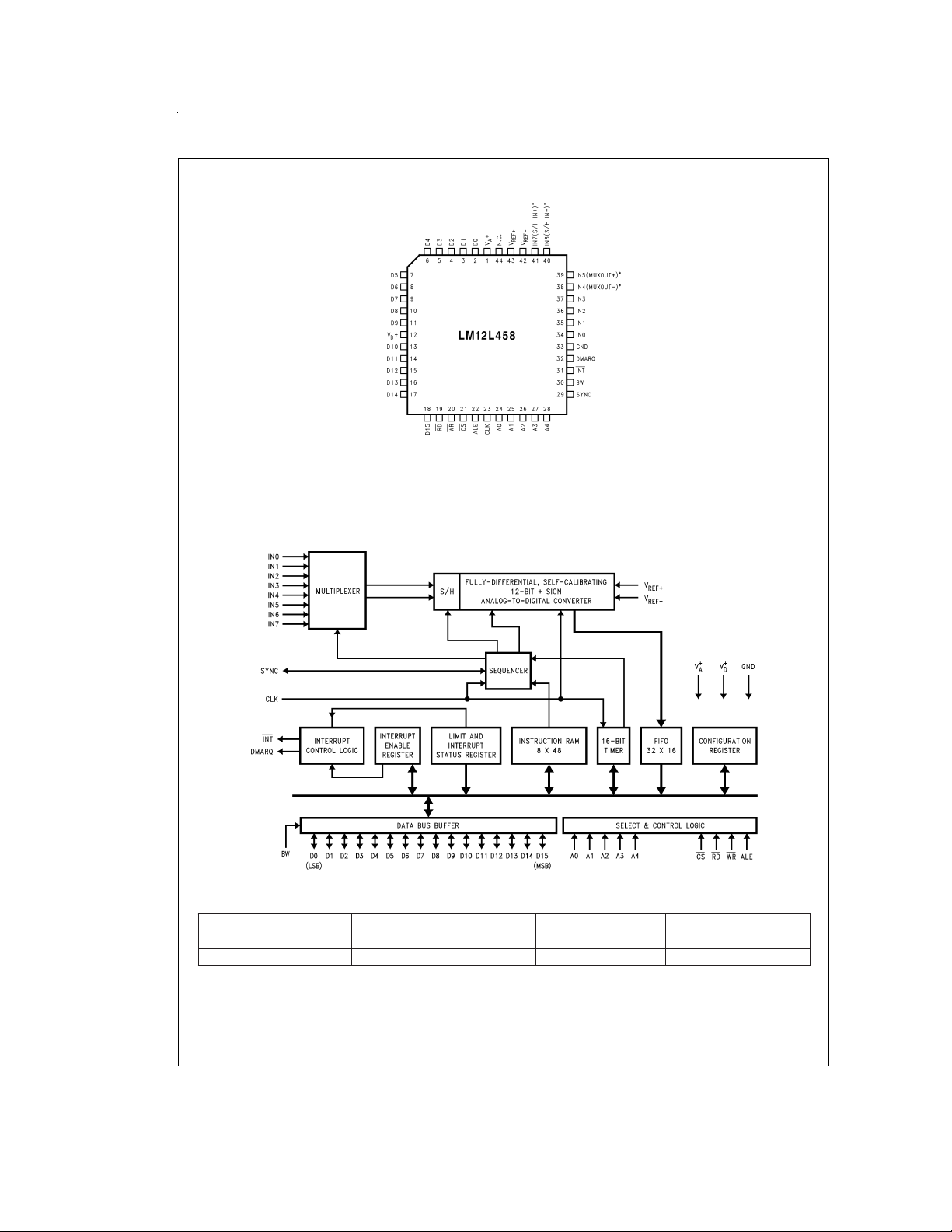

Connection Diagram

*

Pin names in ( ) apply to the LM12L454.

Order Number LM12L458CIV

See NS Package Number V44A

DS011711-1

Functional Diagram

LM12L458

Ordering Information

Guaranteed Guaranteed Order See NS

Clock Freq (min) Linearity Error (max) Part Number Package Number

6 MHz

±

1.0 LSB LM12L458CIV V44A

DS011711-3

www.national.com 2

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

Voltage at Input and Output Pins

except IN0–IN7 (LM12L458) −0.3V to V

Voltage at Analog Inputs

IN0–IN7 (LM12L458) GND − 5V to V

+−VD+| 300 mV

|V

A

Input Current at Any Pin (Note 3)

Package Input Current (Note 3)

Power Dissipation (T

V Package (Note 4) 875 mW

Storage Temperature −65˚C to +150˚C

Lead Temperature

V Package, Infrared, 15 sec. +300˚C

ESD Susceptibility (Note 5) 1.5 kV

+ and VD+) 6.0V

A

+

+ 0.3V

+

±

5mA

±

=

25˚C)

A

20 mA

+5V

See AN-450 “Surface Mounting Methods and Their Effect

on Product Reliability” for other methods of soldering

surface mount devices.

Operating Ratings (Notes 1, 2)

Temperature Range

≤ TA≤ T

(T

min

LM12L458CIV −40˚C ≤ T

Supply Voltage

+, VD+ 3.0V to 5.5V

V

A

+−VD+| ≤100 mV

|V

A

Input Range GND ≤ V

V

IN+

Input Range GND ≤ V

V

IN−

Input Voltage 1V ≤ V

V

REF+

Input Voltage 0V ≤ V

V

REF−

V

REF+−VREF−

Common Mode

V

REF

Range (Note 16) 0.1 V

max

)

≤ 85˚C

A

IN+

IN−

REF+

≤ V

REF−

REF+

1V ≤ V

REF

+

≤ V

A

REFCM

≤ 0.6 V

≤ VA+

≤ VA+

≤ VA+

−1V

≤ VA+

+

A

Converter Characteristics

The following specifications apply for VA+=VD+=3.3V, V

6.0 MHz, R

age, and minimum acquisition time unless otherwise specified. Boldface limits apply for T

limits T

=

25Ω, source impedance for V

S

=

=

T

25˚C. (Notes 6, 7, 8, 9)

A

J

REF+

and V

=

2.5V, V

REF+

≤ 25Ω, fully-differential input with fixed 1.25V common-mode volt-

REF−

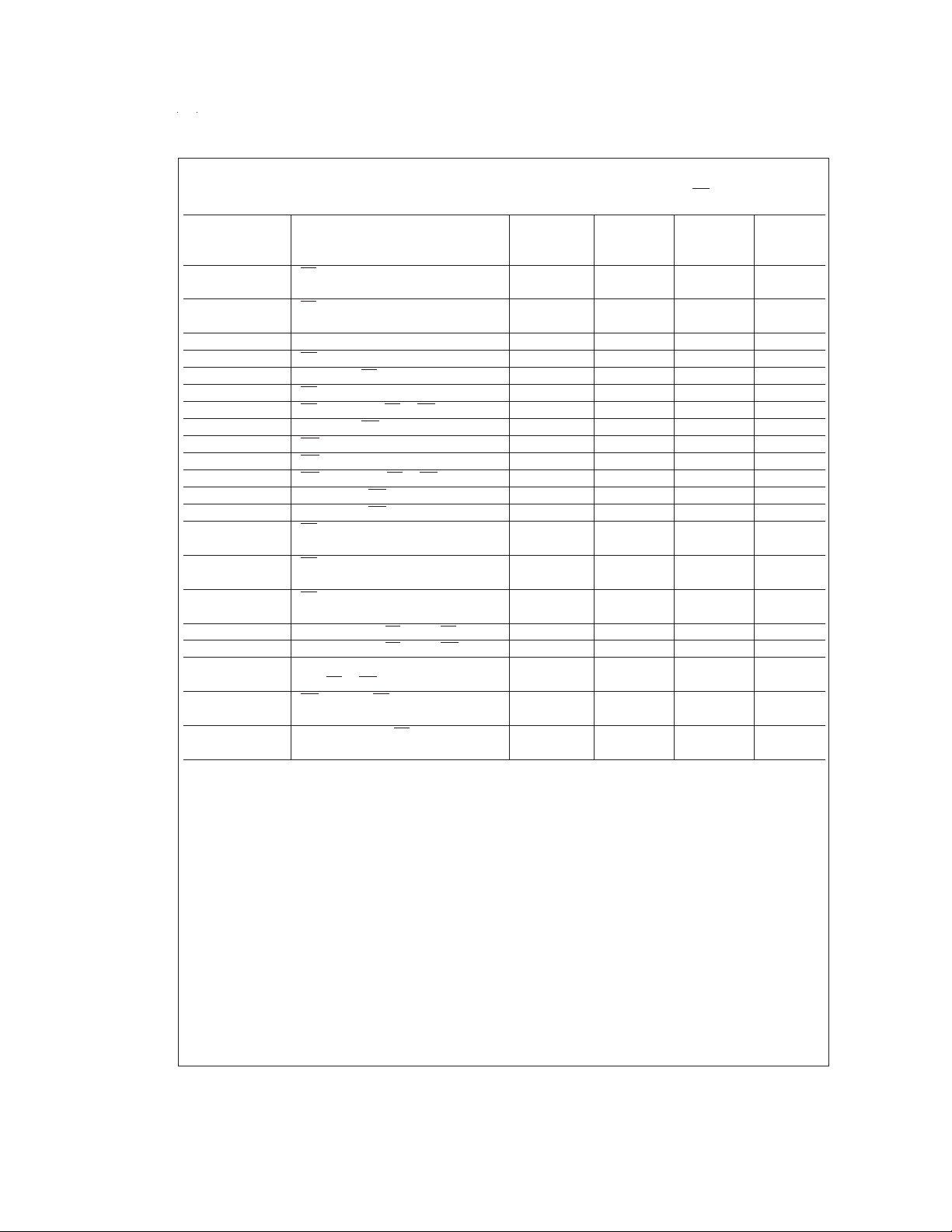

Symbol Parameter Conditions Typical Limits Unit

ILE Positive and Negative Integral

After Auto-Cal (Notes 12, 17)

Linearity Error

TUE Total Unadjusted Error After Auto-Cal (Note 12)

Resolution with No Missing Codes After Auto-Cal (Note 12) 13 Bits (max)

DNL Differential Non-Linearity After Auto-Cal

Zero Error After Auto-Cal (Notes 13, 17)

Positive Full-Scale Error After Auto-Cal (Notes 12, 17)

Negative Full-Scale Error After Auto-Cal (Notes 12, 17)

DC Common Mode Error (Note 14)

ILE 8-Bit + Sign and “Watchdog” Mode

(Note 12)

Positive and Negative Integral

Linearity Error

TUE 8-Bit + Sign and “Watchdog” Mode

After Auto-Zero

Total Unadjusted Error

8-Bit + Sign and “Watchdog” Mode

Resolution with No Missing Codes

DNL 8-Bit + Sign and “Watchdog” Mode

Differential Non-Linearity

8-Bit + Sign and “Watchdog” Mode

After Auto-Zero

Zero Error

8-Bit + Sign and “Watchdog” Positive

and Negative Full-Scale Error

8-Bit + Sign and “Watchdog” Mode DC

Common Mode Error

Multiplexer Channel-to-Channel

Matching

V

IN+

Non-Inverting Input Range GND V (min)

=

0V, 12-bit + sign conversion mode, f

REF−

=

=

T

A

J

(Note 10) (Note 11) (Limit)

±

1/2

±

1 LSB

±

1/4

±

1/2

±

1/2

±

2

±

1/2

±

1/8

±

0.05

to T

T

MIN

MAX

±

1

±

1 LSB (max)

±

1 LSB (max)

±

3 LSB (max)

±

3 LSB (max)

±

4 LSB (max)

±

1/2 LSB (max)

±

3/4

9

±

1

±

1/2

±

1/2

V

+ V (max)

A

; all other

=

CLK

LSB (max)

LSB (max)

Bits (max)

LSB (max)

LSB (max)

LSB (max)

LSB

LSB

www.national.com3

Converter Characteristics (Continued)

The following specifications apply for VA+=VD+=3.3V, V

6.0 MHz, R

age, and minimum acquisition time unless otherwise specified. Boldface limits apply for T

limits T

=

25Ω, source impedance for V

S

=

=

T

25˚C. (Notes 6, 7, 8, 9)

A

J

REF+

and V

=

2.5V, V

REF+

≤ 25Ω, fully-differential input with fixed 1.25V common-mode volt-

REF−

Symbol Parameter Conditions Typical Limits Unit

V

IN−

V

IN+−VIN−

Inverting Input Range GND V (min)

Differential Input Voltage Range −V

Common Mode Input Voltage Range GND V (min)

PSS Power Supply Zero Error V

Sensitivity Full-Scale Error V

+=VD+=3.3V±10

A

=

2.5V, V

REF+

(Note 15) Linearity Error

C

REF

C

IN

V

REF+/VREF−

Input Capacitance 85 pF

Selected Multiplexer Channel Input

Capacitance

=

0V, 12-bit + sign conversion mode, f

REF−

=

=

T

A

J

(Note 10) (Note 11) (Limit)

±

0.2

±

0.4

±

0.2 LSB

REF−

=

%

GND

75

to T

T

MIN

MAX

V

+ V (max)

A

+

A

V

+ V (max)

A

V

+ V (max)

A

±

1.75 LSB (max)

±

2 LSB (max)

; all other

CLK

V (min)

=

pF

Converter AC Characteristics

The following specifications apply for VA+=VD+=3.3V, V

MHz, R

and minimum acquisition time unless otherwise specified. Boldface limits apply for T

T

=

25Ω, source impedance for V

S

=

=

T

25˚C. (Notes 6, 7, 8, 9)

A

J

REF+

and V

REF−

=

2.5V, V

REF+

≤ 25Ω, fully-differential input with fixed 1.25V common-mode voltage,

Symbol Parameter Conditions Typical Limits Unit

Clock Duty Cycle 50

t

C

Conversion Time 13-Bit Resolution,

Sequencer State S5 (

Figure 15

9-Bit Resolution,

Sequencer State S5 (

t

A

Acquisition Time Sequencer State S7 (

Figure 15

Figure 15

Built-in minimum for 13-Bits

Built-in minimum for 9-Bits and

“Watchdog” mode

t

Z

t

CAL

Auto-Zero Time Sequencer State S2 (

Full Calibration Time Sequencer State S2 (

Figure 15

Figure 15

Throughput Rate

(Note 18) (min)

t

WD

t

PU

t

WU

“Watchdog” Mode Sequencer States S6, S4,

Comparison Time and S5 (

Figure 15

)

Power-Up Time 10 ms

Wake-Up Time 10 ms

=

0V, 12-bit + sign conversion mode, f

REF−

=

=

T

A

to T

T

J

MIN

MAX

(Note 10) (Note 11) (Limit)

40

60

44 (t

21 (t

9(t

2(t

CLK

CLK

CLK

CLK

CLK

CLK

)

)

)

)76(t

) 4944 (t

) 44 (t

) 21 (t

) 9(t

) 2(t

) 76 (t

) 4944 (t

)+50ns

CLK

)+50ns

CLK

)+50ns

CLK

)+50ns

CLK

)+50ns (max)

CLK

)+50ns (max)

CLK

107 106

11 (t

) 11 (t

CLK

)+50ns

CLK

=

CLK

; all other limits

%

%

(max)

(max)

(max)

(max)

(max)

(max)

kHz

6.0

%

(min)

www.national.com 4

DC Characteristics

The following specifications apply for VA+=VD+=3.3V, V

time unless otherwise specified. Boldface limits apply for T

7, 8)

REF+

=

2.5V, V

=

=

T

A

J

Symbol Parameter Conditions Typical Limits Unit

+V

I

D

I

+V

A

I

ST

+ Supply Current CS=“1” 0.4 1.0 mA (max)

D

+ Supply Current CS=“1” 2.25 3.5 mA (max)

A

Stand-By Supply Current Power-Down Mode Selected

(I

++IA+) Clock Stopped 1.5 4.5 µA (max)

D

Multiplexer ON-Channel

Leakage Current

V

+=3.6V

A

ON-Channel=3.6V

OFF-Channel=0V 0.1 0.3 µA (max)

ON-Channel=0V

OFF-Channel=3.6V 0.1 0.3 µA (max)

Multiplexer OFF-Channel

Leakage Current

V

+=3.6V

A

ON-Channel=3.6V

OFF-Channel=0V 0.1 0.3 µA (max)

ON-Channel=0V

OFF-Channel=3.6V 0.1 0.3 µA (max)

R

ON

Multiplexer ON-Resistance V

Multiplexer

Channel-to-Channel

matching

R

ON

=

3.3V 850 1500 Ω

IN

=

V

1.65V 1300 2000 Ω

IN

=

V

0V 830 1500 Ω

IN

=

3.3V

V

IN

=

V

1.65V

IN

=

V

0V

IN

=

REF−

to T

T

MIN

MAX

=

0V, f

6.0 MHz and minimum acquisition

CLK

; all other limits T

=

A

=

T

25˚C. (Notes 6,

J

(Note 10) (Note 11) (Limit)

6 MHz Clock 30 µA (max)

±

%

1.0

±

%

1.0

±

%

1.0

±

%

3.0

±

%

3.0

±

%

3.0

Ω

Ω

Ω

Digital Characteristics

The following specifications apply for VA+=VD+=3.3V, unless otherwise specified. Boldface limits apply for T

to T

T

MIN

; all other limits T

MAX

=

=

T

A

J

25˚C. (Notes 6, 7, 8)

Symbol Parameter Conditions Typical Limits Unit

(Note 10) (Note 11) (Limit)

V

IN(1)

V

IN(0)

Logical “1” Input Voltage VA+=VD+=3.6V 2.0 V (min)

Logical “0” Input Voltage VA+=VD+=3.0V 0.7 V (max)

ALE, Pin 22 0.6

I

IN(1)

Logical “1” Input Current V

=

3.3V 0.005 1.0 µA (max)

IN

2.0

I

IN(0)

Logical “0” Input Current V

=

0V −0.005 −1.0 µA (max)

IN

−2.0

C

V

V

I

OUT

IN

OUT(1)

OUT(0)

D0–D15 Input Capacitance 6 pF

Logical “1” Output Voltage VA+=VD+=3.0V

=

I

−360 µA 2.4 V (min)

OUT

=

I

−10 µA 2.85 V (min)

OUT

Logical “0” Output Voltage VA+=VD+=3.0V

=

I

1.6 mA 0.4 V (max)

OUT

=

I

10 µA 0.1

OUT

TRI-STATE®Output Leakage Current V

=

0V −0.01 −3.0 µA (max)

OUT

=

V

3.3V 0.01 3.0 µA (max)

OUT

=

T

A

www.national.com5

=

J

Digital Timing Characteristics

=

The following specifications apply for VA+=VD+=3.3V, t

unless otherwise specified. Boldface limits apply for T

=

t

3 ns, and C

r

f

=

=

T

A

T

J

MIN

Symbol Typical Limits Unit

(See

Figures 10,

11, 12

)

Parameter Conditions (Note 10) (Note 11) (Limit)

1, 3 CS or Address Valid to ALE Low

Set-Up Time

2, 4 CS or Address Valid to ALE Low

Hold Time

5 ALE Pulse Width 45 ns (min)

6 RD High to Next ALE High

7 ALE Low to RD Low

8 RD Pulse Width

9 RD High to Next RD or WR Low

10 ALE Low to WR Low

11 WR Pulse Width

12 WR High to Next ALE High

13 WR High to Next RD or WR Low

14 Data Valid to WR High Set-Up Time

15 Data Valid to WR High Hold Time

16 RD Low to Data Bus Out of TRI-STATE

17 RD High to TRI-STATE

R

L

18 RD Low to Data Valid (Access Time)

20 Address Valid or CS Low to RD Low

21 Address Valid or CS Low to WR Low

19 Address Invalid

from RD or WR High

22 INT High from RD Low 30 10 ns (min)

23 DMARQ Low from RD Low

Note 1: Absolute Maximum Ratings indicate limits beyond which damage tothe device may occur. OperatingRatings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: When the input voltage (V

The 20 mA maximum package input current rating allows the voltage at any four pins, with an input current of 5 mA, to simultaneously exceed the power supply voltages.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

to ambient thermal resistance), andT

ber given in the Absolute Maximum Ratings, whichever is lower. For this device, T

LM12L458 in the V package, when board mounted, is 47˚C/W.

Note 5: Human body model, 100 pF discharged through a 1.5 kΩ resistor.

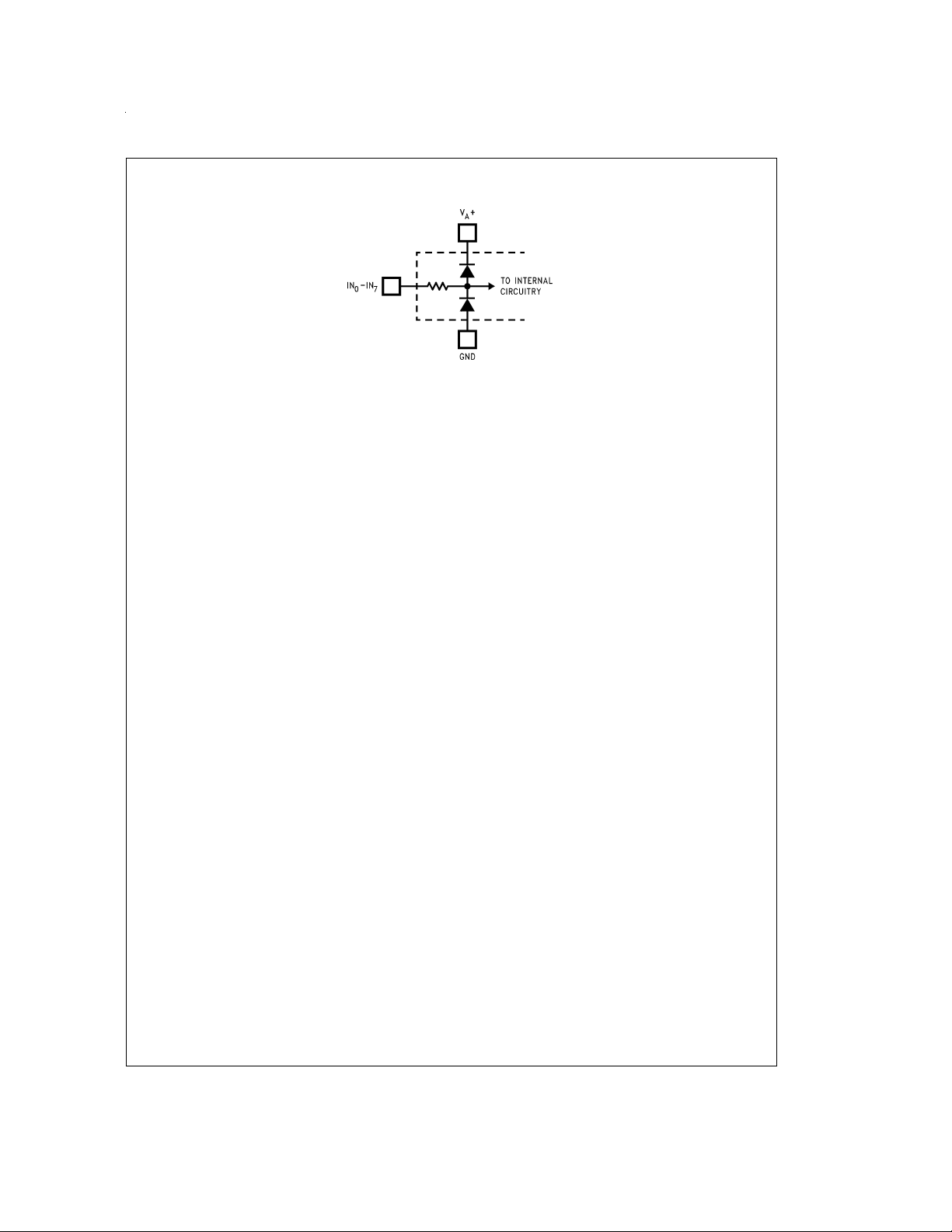

Note 6: Two on-chip diodes are tied to each analog input through a series resistor, as shown below.Input voltage magnitude up to 5V above V

will not damage the LM12L458. However, errors in the A/D conversion can occur if these diodes are forward biased by more than 100 mV.As an example, if V

, full-scale input voltage must be ≤3.1 VDCto ensure accurate conversions.

3.0 V

DC

) at any pin exceeds the power supply rails (V

IN

(ambient temperature). Themaximum allowable power dissipation at any temperature is PD

A

IN

<

GND or V

Jmax

=

100 pF on data I/O, INT and DMARQ lines

to T

MAX

L

; all other limits T

=

=

T

A

J

25˚C. (Notes 6, 7, 8)

40

20

ns (min)

ns (min)

35 ns (min)

20 ns (min)

100 ns (min)

100 ns (min)

20 ns (min)

60 ns (min)

75 ns (min)

140 ns (min)

40 ns (min)

30 ns (min)

30 10 ns (min)

70 ns (max)

=

1kΩ 30 10 ns (min)

110 ns (max)

30 10 ns (min)

95 ns (max)

20 ns (min)

20 ns (min)

10

ns (min)

60 ns (max)

30 10 ns (min)

60 ns (max)

>

(VA+orVD+)), the current at that pin should be limited to 5 mA.

IN

(maximum junction temperature), θJA(package junction

Jmax

=

150˚C, and the typical thermal resistance (θ

max

=

(T

Jmax−TA

JA

)/θJAor the num-

) of the LM12L454 and

+ or 5V below GND

A

A

+is

www.national.com 6

Digital Timing Characteristics (Continued)

DS011711-4

Note 7: VA+ and VD+ must be connected together to the same power supply voltage and bypassed with separate capacitors at each V+pin to assure conversion/

comparison accuracy.

Note 8: Accuracy is guaranteed when operating at f

Note 9: With the test condition for V

Note 10: Typicals are at T

Note 11: Limits are guaranteed to National’s AOQL (Average Output Quality Level).

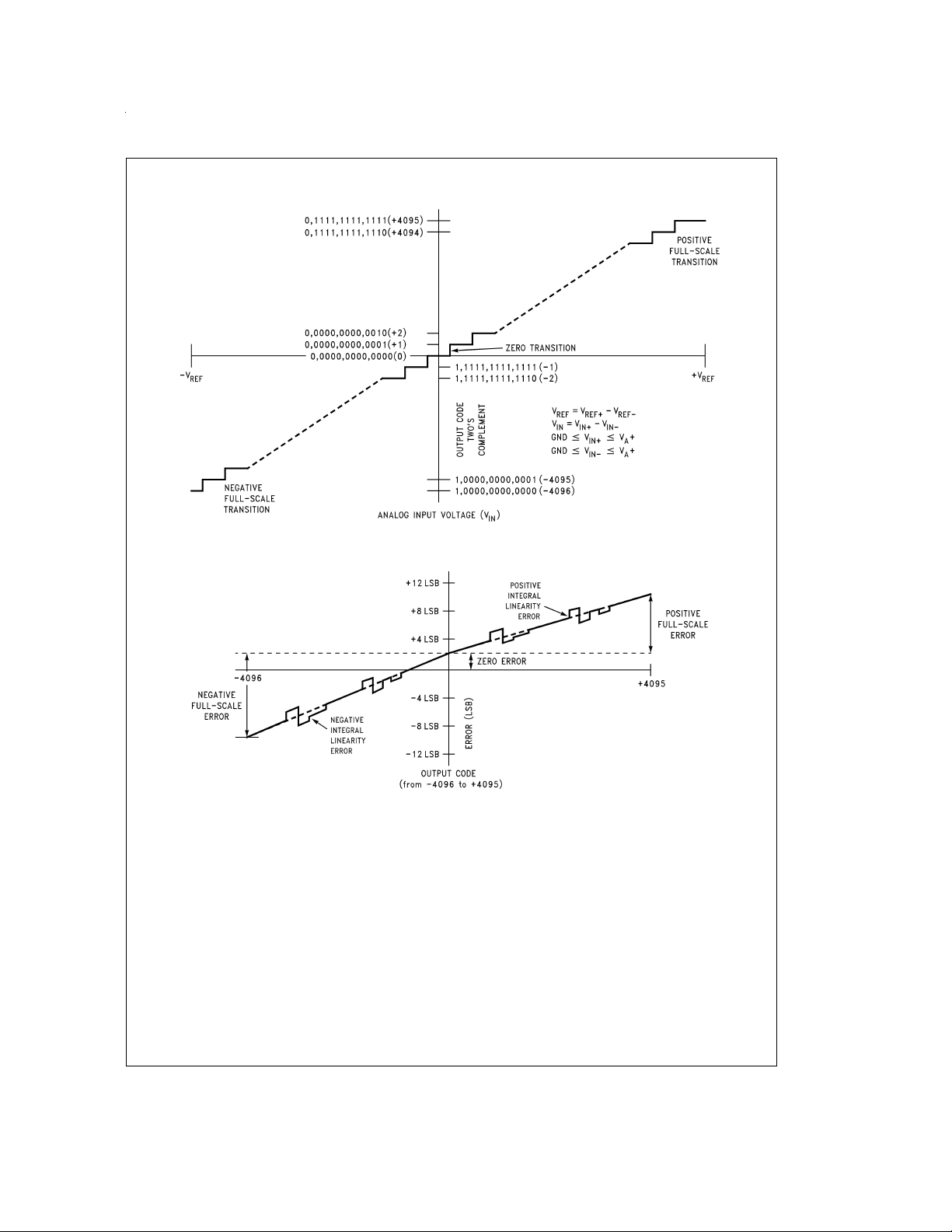

Note 12: Positive integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive

full-scale and zero. For negative integral linearity error the straight line passes through negative full-scale and zero. (See

Note 13: Zero error is a measure of the deviation from the mid-scale voltage (a code of zero), expressed in LSB. It is the worst-case value of the code transitions

between −1 to 0 and 0 to +1 (see

Note 14: The DC common-mode error is measured with both inputs shorted together and driven from 0V to 2.5V.The measured value is referred to the resulting

output value when the inputs are driven with a 1.25V signal.

=

A

=

V

REF

25˚C and represent most likely parametric norm.

Figure 8

).

Note 15: Power Supply Sensitivity is measured after Auto-Zero and/or Auto-Calibration cycle has been completed with V

Note 16: V

Note 17: The LM12L458’s self-calibration technique ensures linearity and offset errors as specified, but noise inherent in the self-calibration process will result in

a repeatability uncertainty of

Note 18: The Throughput Rate is for a single instruction repeated continuously. Sequencer states 0 (1 clock cycle), 1 (1 clock cycle), 7 (9 clock cycles) and 5 (44

clock cycles) are used (see

version. The Throughput Rate is f

(Reference Voltage Common Mode Range) is defined as (V

REFCM

±

0.10 LSB.

Figure 15

). One additional clock cycle is used to read the conversion result stored in the FIFO, for a total of 56 clock cycles per con-

(MHz)/N, where N is the number of clock cycles/conversion.

CLK

CLK

REF+−VREF−

=

6 MHz.

given as +2.5V, the 12-bit LSB is 305 µV and the 8-bit/“Watchdog” LSB is 4.88 mV.

Figures 6, 7

).

+ and VD+ at the specified extremes.

REF++VREF−

)/2.

A

www.national.com7

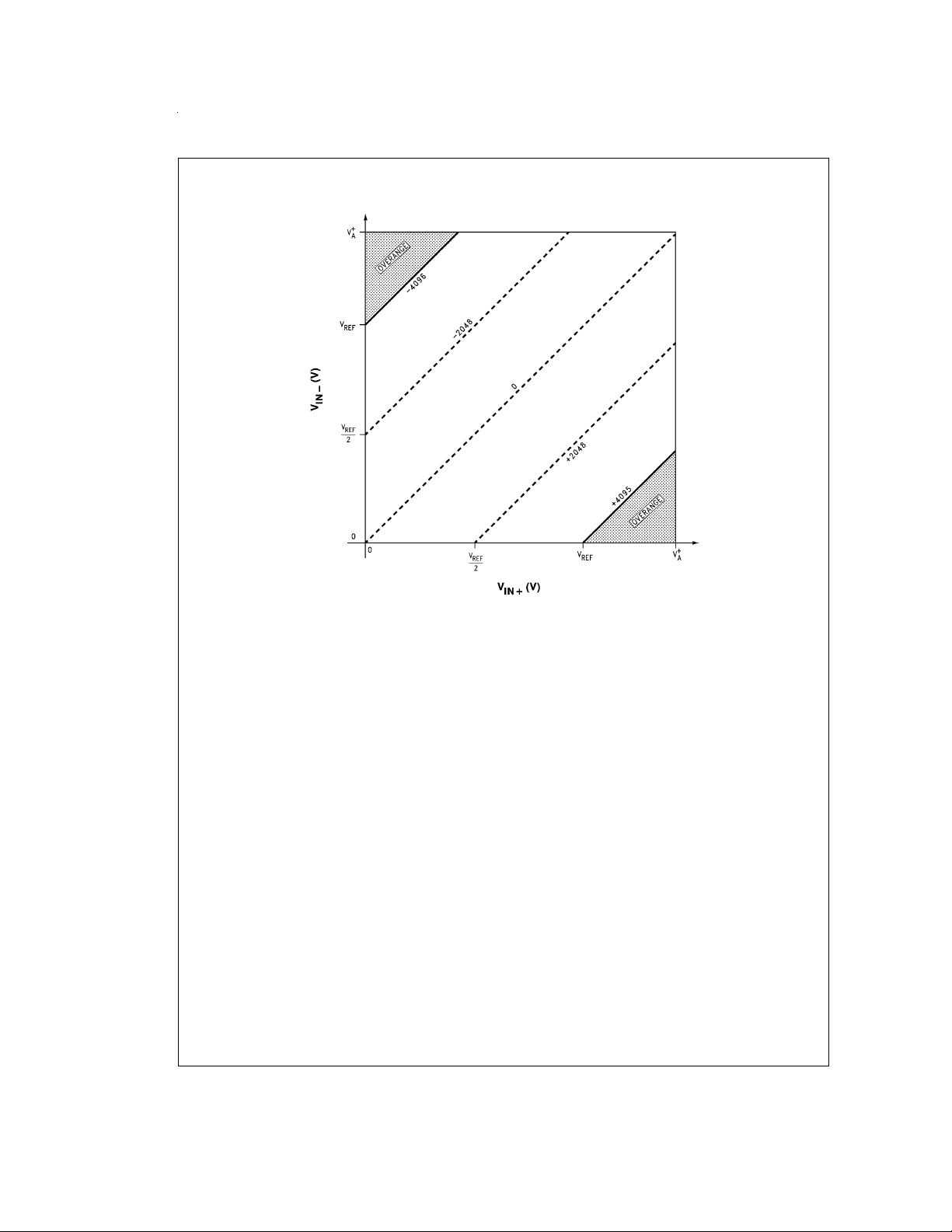

Digital Timing Characteristics (Continued)

V

REF

=

V

IN

GND ≤ V

GND ≤ V

=

V

REF+−VREF−

V

IN+−VIN−

≤ VA+

IN+

≤ VA+

IN−

DS011711-5

FIGURE 1. The General Case of Output Digital Code vs the Operating Input Voltage Range

www.national.com 8

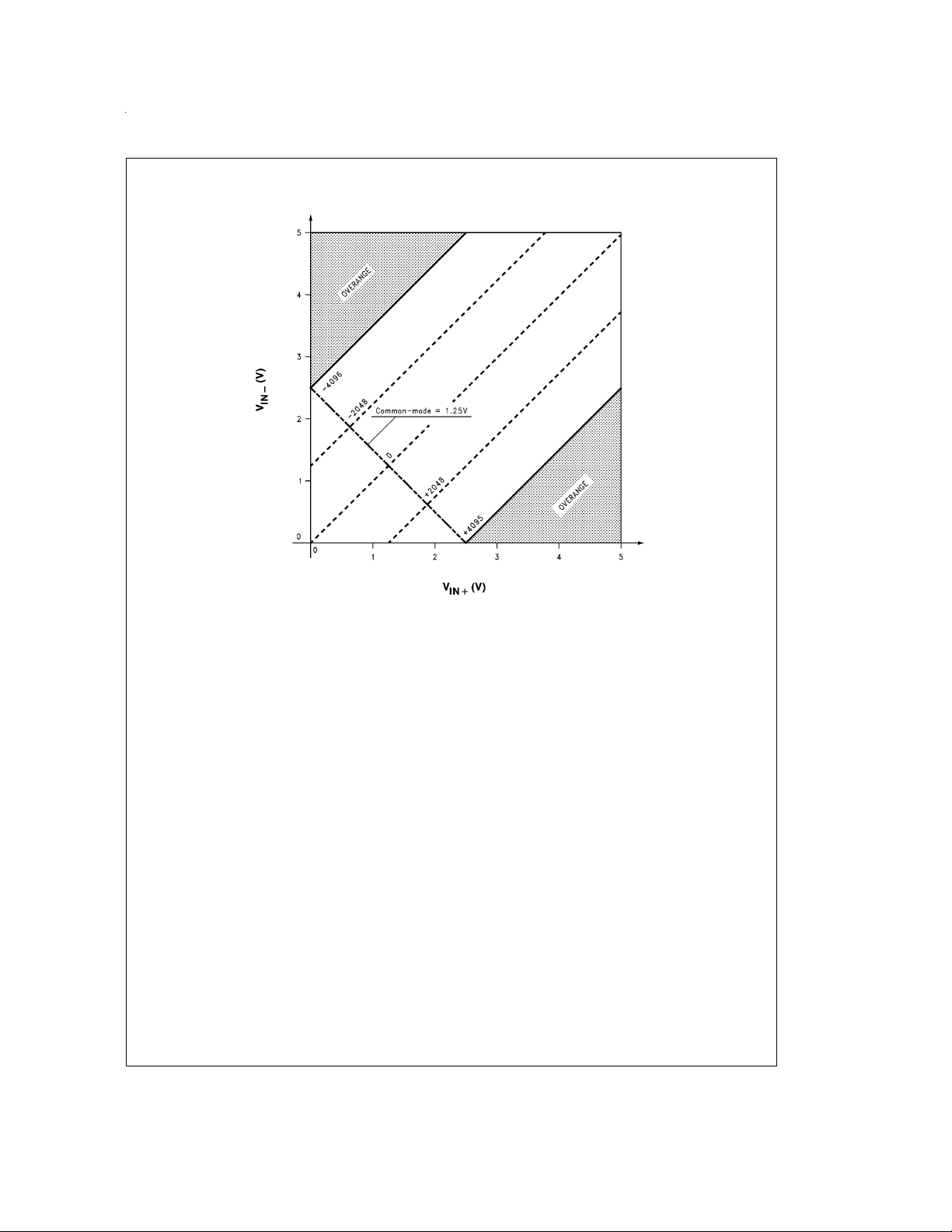

Digital Timing Characteristics (Continued)

=

V

IN+−VIN−

≤ VA+

IN+

≤ VA+

IN−

=

2.5V

V

REF+−VREF−

V

IN

GND ≤ V

GND ≤ V

FIGURE 2. Specific Case of Output Digital Code vs the Operating Input Voltage Range for V

DS011711-6

REF

=

2.5V

www.national.com9

Digital Timing Characteristics (Continued)

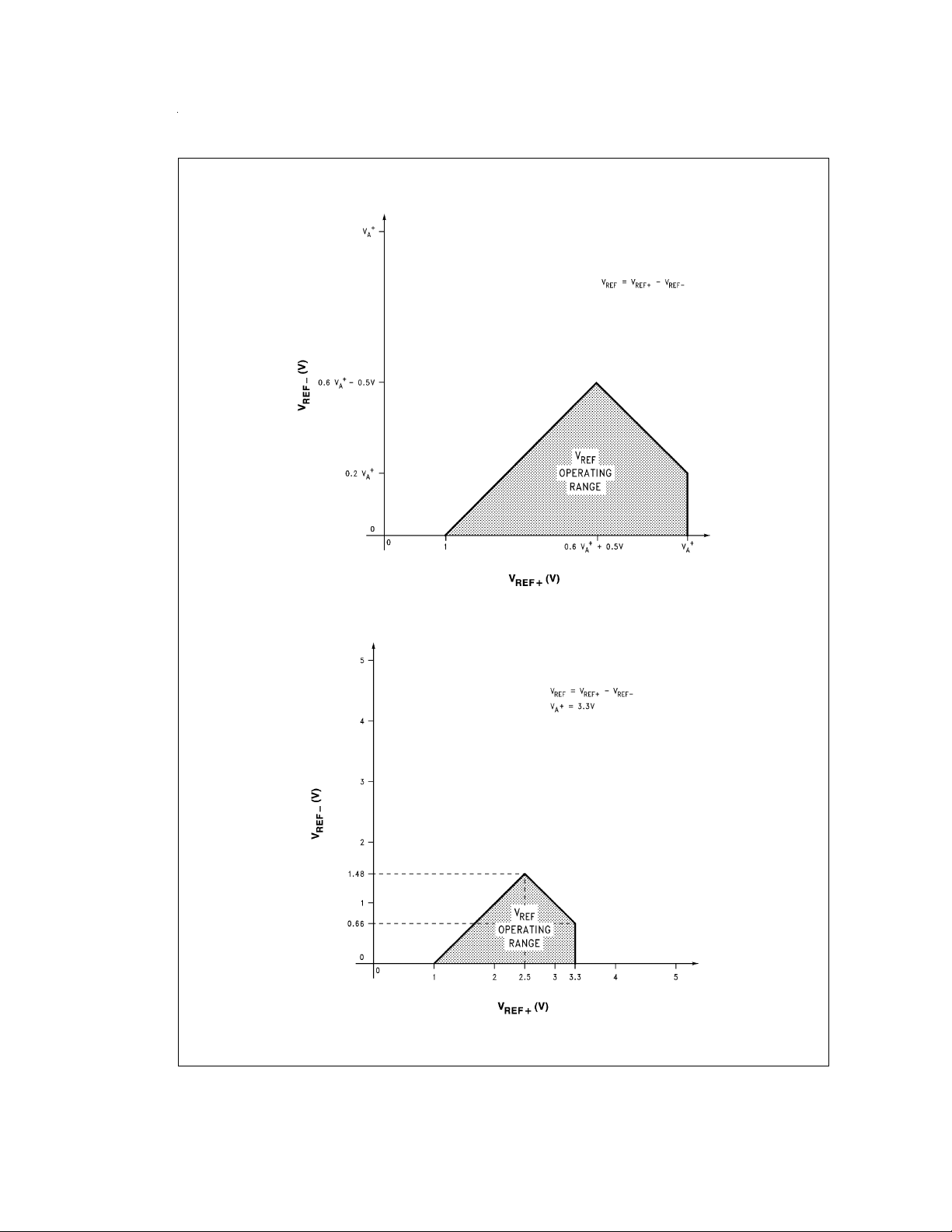

FIGURE 3. The General Case of the V

Operating Range

REF

DS011711-7

FIGURE 4. The Specific Case of the V

www.national.com 10

Operating Range for VA+=3.3V

REF

DS011711-8

Digital Timing Characteristics (Continued)

FIGURE 5. Transfer Characteristic

DS011711-9

DS011711-10

FIGURE 6. Simplified Error Curve vs Output Code without Auto-Calibration or Auto-Zero Cycles

www.national.com11

Loading...

Loading...