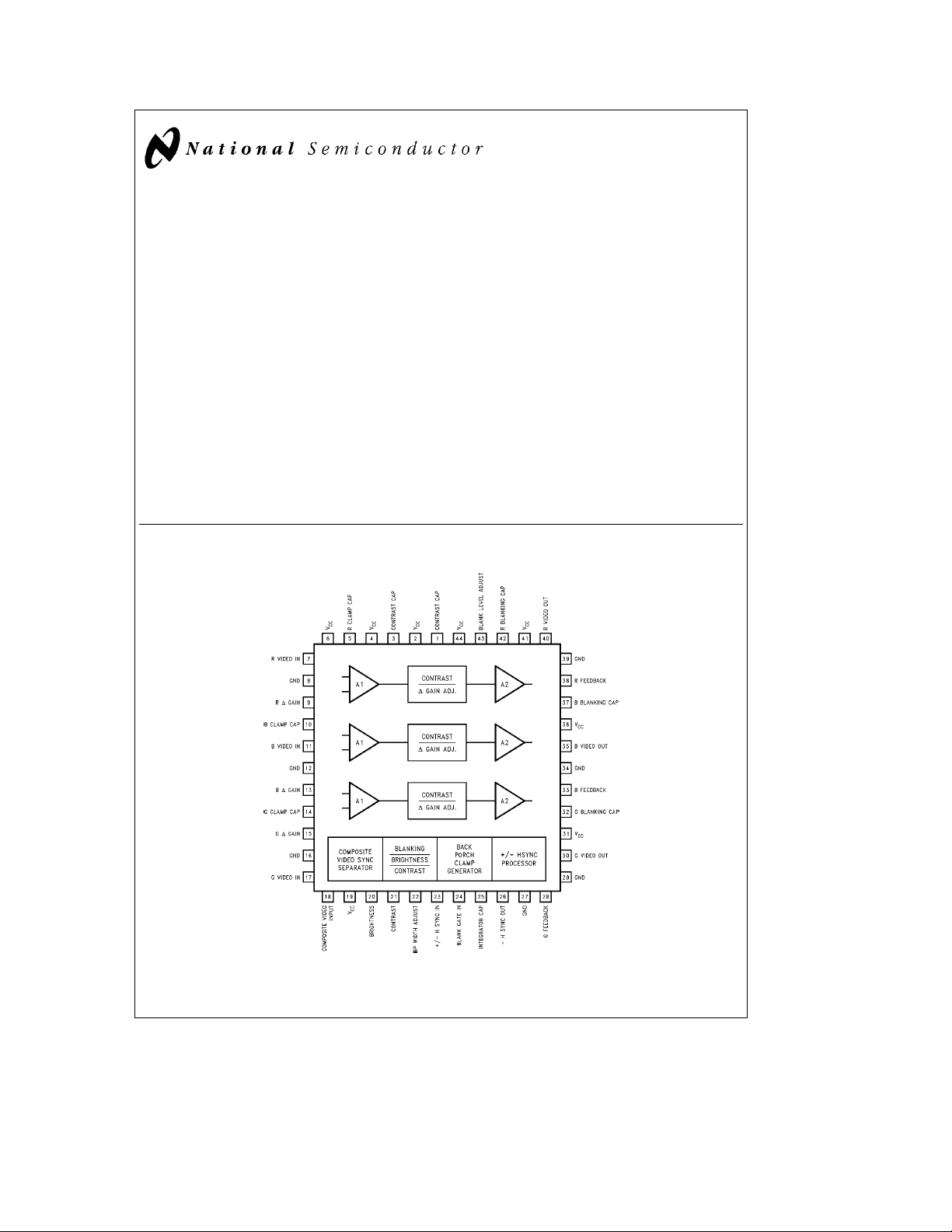

LM1204 150 MHz RGB Video Amplifier System

General Description

The LM1204 is a triple 150 MHz video amplifier system

designed specifically for high resolution RGB video display

applications. In addition to three matched video amplifiers,

the LM1204 contains a DC operated contrast control, a DC

operated drive control for each amplifier, and a dual clamping system for both brightness control and video blanking.

The LM1204 also contains a back porch clamp pulse generator which is activated by an externally supplied

g

H/HV

sync signal or by an external composite video signal. The

g

H/HV sync input will have priority over the composite vid-

eo input. A single

b

H/HV sync output is provided for the

automatically selected sync input signal. The back porch

clamp pulse width is user adjustable from 0.3 msto4ms.

The LM1204 video output stage will directly drive most

Hybrid or discrete CRT amplfier input stages without the

need for an external buffer transistor. The device has been

designed to operate from a 12V supply with all DC controls

operating over a 0V to 4V range providing for an easy interface to serial digital buss controlled monitors.

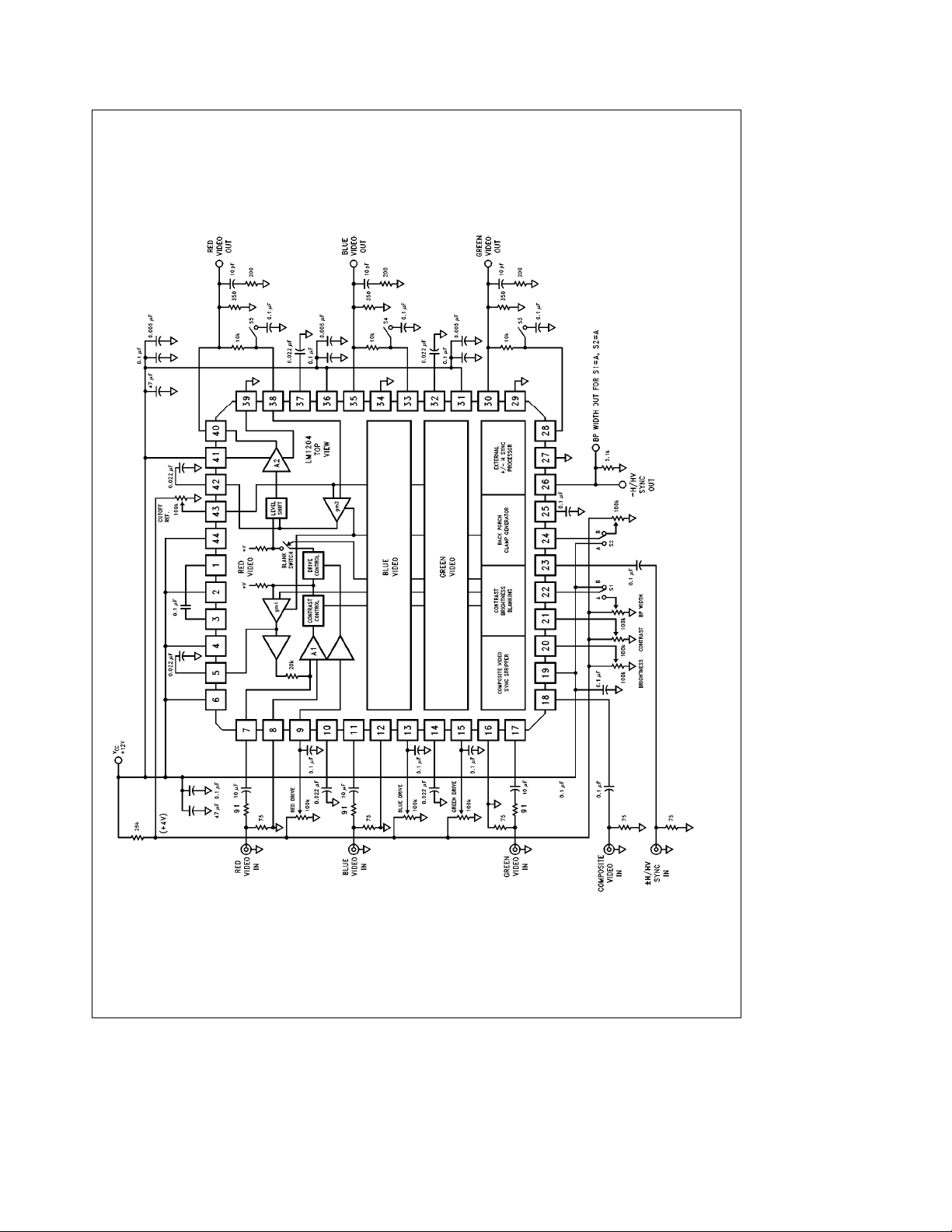

Block Diagram and Connection Diagram

Features

Y

Built-in video blanking function

Y

Built-in sync separator for composite video input

Y

Includes DC restoration of video signals

Y

Back porch clamp pulse width user adjustable

Y

DC control of brightness, contrast, blanking level, drive

and cutoff

Y

DC controls are 0V to 4V for easy interfacing to a

digitally controlled system

Key Specifications

Y

150 MHz large signal bandwidth (typ)

Y

2.3 ns rise/fall times (typ)

Y

0.1 dB contrast tracking (typ)

Y

g

3 dB drive (D gain) adjustments on R, G, B channels

(typ)

Applications

Y

High resolution CRT monitors

Y

Video AGC amplifier

Y

Wideband amplifier with gain and DC offset control

Top View

LM1204 150 MHz RGB Video Amplifier System

December 1994

Ordering Information

TL/H/11238– 1

Order Number LM1204V

See NS Package Number V44A

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

TL/H/11238

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage, V

Pins 2, 4, 6, 19, 31, 41, 44 (Note 3) 13.5V

Peak Video Output Source Current

(Any One Amplifier) Pins 30, 35 or 39 30 mA

Voltage at Any Input Pin, V

MaximumgH Sync Input Voltage 5.5 V

Power Dissipation, PD (Above 25§C

Derate Based on iJAand TJ) 2.4W

CC

IN

GNDsV

s

V

IN

CC

Thermal Resistance, i

Junction Temperature, T

JA

J

52§C/W

150§C

ESD Susceptibility (Note 4) 2.5 kV

Storage Temperature

b

65§Cto150§C

Lead Temperature

Vapor Phase (60 seconds) 215

Infrared (15 seconds) 220

PP

Operating Ratings (Note 2)

C

§

C

§

Temperature Range 0§Cto70§C

Supply Voltage, V

CC

10.8VsV

CC

s

13.2V

DC Electrical Characteristics (Video Amplifier Section)

The following specifications apply for VCC(pins 2, 4, 6, 19, 31, 36, 41 and 44)e12V and T

e

S1

B, S2eB, S3, 4, 5 closed, V9, 13, 15e2V, V20, 21, 22, 24, 43e0.5V unless otherwise specified; see test circuit,

Figure 1

.

Symbol Parameter Conditions

I

I

Blank

I

Blank

I

Clamp

I

Clamp

V

V

V

H

V

L

V

CM43

I

I

24h

I

24l

I

FB

I

BB

I

CB

24h

B

24l

Supply Current No Video or Sync Input

S

Signals, S1

e

A (Max)

Input Bias Current S1eA

(Pin 9, 13, 15, 20, 21 or 22) (Max)

Blank Gate Input High Current V24e4V

Blank Gate Input Low Current V24e0V

Feedback Input Current

(Pin 28, 33 or 38)

Blank Cap Charge Current V

a

Blank Cap Discharge Current V

b

32,37,42

32,37,42

e

0V 185 75 mA (Min)

e

5V

Blank Cap Bias Current (Pins 32, 37, 42) 20 nA

Clamp Cap Charge Current V

a

Blank Cap Discharge Current V

b

5,10,14

5,10,14

e

0V 185 75 mA (Min)

e

5V

Clamp Cap Bias Current (Pins 5, 10, 14) 20 nA

Blank Gate High Input Voltage Input Signal is Not Blanked 2 V (Min)

Blank Gate Low Input Voltage Input Signal is Blanked 0.8 V (Max)

Blank Comparator Offset Voltage Voltage between V43 and

Any One Video Output (Max)

Video Output High Voltage R

(Pins 30, 35, 40) V28, 33, 38

Video Output Low Voltage R

(Pins 30, 35, 40) V28, 33, 38

e

350X

L

L

e

350X

e

0V

e

4V

Common Mode Range of Blank 0.5 V(Min)

Comparator (Pins 43, 28, 33, 38)

e

25§C unless otherwise specified.

A

Typical Limit

(Note 5) (Note 6)

100 125

0.3 2

0.01 2

25

150 nA

b

185

b

185

b

75 mA (Min)

b

75 mA (Min)

250

8.7 7 V(Min)

0.1 0.5 V(Max)

4 V(Max)

Units

mA

mA

mA

(Max)

mA

(Max)

mV

2

DC Electrical Characteristics (Sync Separator/Processor Section)

The following specifications apply for VCC(Pins 2, 4, 6, 19, 31, 36, 41 and 44)e12V and T

specified. S1

Circuit

Symbol Parameter Conditions

b

HV

b

HV

V

23

Figure 1

OH

OL

e

B, S2eB, S3, 4, 5 closed, V9, 13, 15e2V, V20, 21, 22, 24, 43e0.5V, unless otherwise specified; see Test

.

Typical Limit

(Note 5) (Note 6)

b

H Sync Output Logic High (Pin 26) 4.2 2.4 V(Min)

b

H Sync Output Logic Low (Pin 26) 0.1 0.4 V(Max)

Quiescent DC Voltage atgH

Sync Input

3V

e

25§C, unless otherwise

A

Units

AC Electrical Characteristics (Video Amplifier Section)

The following specifications apply for VCC(Pins 2, 4, 6, 19, 31, 36, 41 and 44)e12V and T

specified. S1

Figure 1

Symbol Parameter Conditions

R

IN

A

Vmax

DA

Vtrack

DA

V2V

DA

V0.5V

DGain D Gain Range (Pins 9, 13, 15) V9, 13, 15e0V to 4V

DV

O

f

b

3dB

THD Video Amplifier Distortion V

t

R

t

F

V

ISO (1 MHz)

V

ISO (130 MHz)

e

B, S2eB, S3, 4, 5 closed, V9, 13, 15, 21, 24, 43e4V, V20e2V, unless otherwise specified; see Test Circuit

.

Video Amplifier Input Resistance 20 kX

Maximum Video Amplifier Gain f

e

12 kHz 10 5.5 V/V(Min)

IN

Amplifier Gain (Contrast)

Tracking (Note 7)

Attenuation at 2V Ref: A

Attenuation at 0.5V Ref: A

V21e2V 6 dB

V

max

V21e0.5V 28 20 dB(Min)

V

max

Max Brightness Tracking Error (Note 8) 100 mV

Video Amplifier Bandwidth (Note 9) V

e

3.5 V

OUT

OUT

PP

e

1VPP,fe12 kHz 0.3 %

Video Output Rise Time (Note 9) Square Wave Input

V

OUT

e

3.5 VPP,R

e

350X

L

Video Output Fall Time (Note 9) Square Wave Input

V

OUT

e

3.5 VPP,R

e

350X

L

Video Amplifier 1 MHz

Isolation (Notes 9, 10)

Video Amplifier 130 MHz

Isolation (Notes 9, 10)

e

25§C, unless otherwise

A

Typical Limit

(Note 5) (Note 6)

Units

0.1 dB

g

3dB

150 MHz

2.0 ns

2.3 ns

b

50 dB

b

10 dB

3

AC Electrical Characteristics (Sync Separator/Processor Section)

The following specifications apply for VCC(Pins 2, 4, 6, 19, 31, 36, 41 and 44)e12V and T

specified. S1

e

A, S2eB, S3, 4, 5 closed, V9, 13, 15, 20, 21, 43e2V, unless otherwise specified; see Test Circuit

e

25§C, unless otherwise

A

Figure 1

and Timing Diagram for input waveform.

Symbol Parameter Conditions

V

18(Min)

V

18(Max)

V

23

Composite Video Input Voltage S2eA, Inpute10% Duty

(Pin 18) Cycle, Test for Loss of BP (Min)

Composite Video Input Voltage Pulse at Pin 26

(Pin 18) (Max)

g

H Sync Input Voltage (Pin 23) Inpute10% Duty Cycle

Back Porch Clamp Pulse Width S2eA, Pin 26eBP Output

e

at V

1V (Max)

24

Back Porch Clamp Pulse Width

e

at V

4V (Max)

24

Typical Limit

(Note 5) (Note 6)

0.15

2

1.6

1 1.4

300 600

Units

V

V

V

(Min)

ms

ns

MaximumgH Sync Input Frequency 600 KHz

D

HI

D

LO

t

pdl1

t

pdh1

t

pd1

t

pdl2

t

pdh2

t

pd2

t

pdl2–tpdl1

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications

and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics

may degrade when the device is not operated under the listed test conditions.

Note 3: V

Note 4: Human body model, 100 pF discharged through a 1.5 kX resistor.

Note 5: Typical specifications are specified at

Note 6: Tested limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 7: DA

gain change between any two amplifiers with the contrast voltage, V21, at either 4V or 2V measured relative to an A

max, the three amplifier gains might be 17.4 dB, 16.9 dB and 16.4 dB and change to 7.3 dB, 6.9 dB and 6.5 dB respectively for V21e2V. This yields the measured

typical

Note 8: Brightness tracking error is measured with all three video channels set for equal gain. The measured value is limited by the resolution of the measurement

equipment.

Note 9: When measuring video amplifier bandwidth or pulse rise and fall times, a double sided full ground plane printed circuit board is recommended. Video

amplifier isolation tests also require this printed circuit board. The measured rise and fall times are effective rise and fall times, taking into account the rise and fall

times of the generator.

Note 10: Measure output levels of either undriven amplifier relative to the driven amplifier to determine channel isolation. Terminate the undriven amplifier inputs.

Max Duty Cycle of Active High Test for Loss of Sync

H Sync (Pin 23) at Pin 26

Max Duty Cycle of Active Low

H Sync (Pin 23)

g

H Sync Input tobH Sync Inpute10% Duty Cycle

Output Low Delay

g

H Sync Input tobH Sync Inpute10% Duty Cycle

Output High Delay

g

H Sync Input Trailing Edge to Inpute10% Duty Cycle,

Back Porch Clamp Output Delay S2

e

A

Composite Video Input tobH Inpute10% Duty Cycle

Sync Output Low Delay

Composite Video Input tobH Inpute10% Duty Cycle

Sync Output High Delay

Composite Video Input Trailing Inpute10% Duty Cycle

Edge to Back Porch Clamp Output Delay S2

e

A

Composite Video andgH Sync Input Inpute10% Duty Cycle

b

to

H Sync Output Delta Delay

supply pins 2, 4, 6, 19, 31, 36, 41 and 44 must be externally wired together to prevent internal damage during VCCpower on/off cycle.

CC

a

25§C and represent the most likely parametric norm.

tracking is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three attenuators. It is the difference in

V

g

0.1 dB channel tracking.

22 %

22 %

100 ns

65 ns

70 ns

106 ns

68 ns

78 ns

6ns

max condition V21e4V. For example, at A

V

PP

PP

PP

V

4

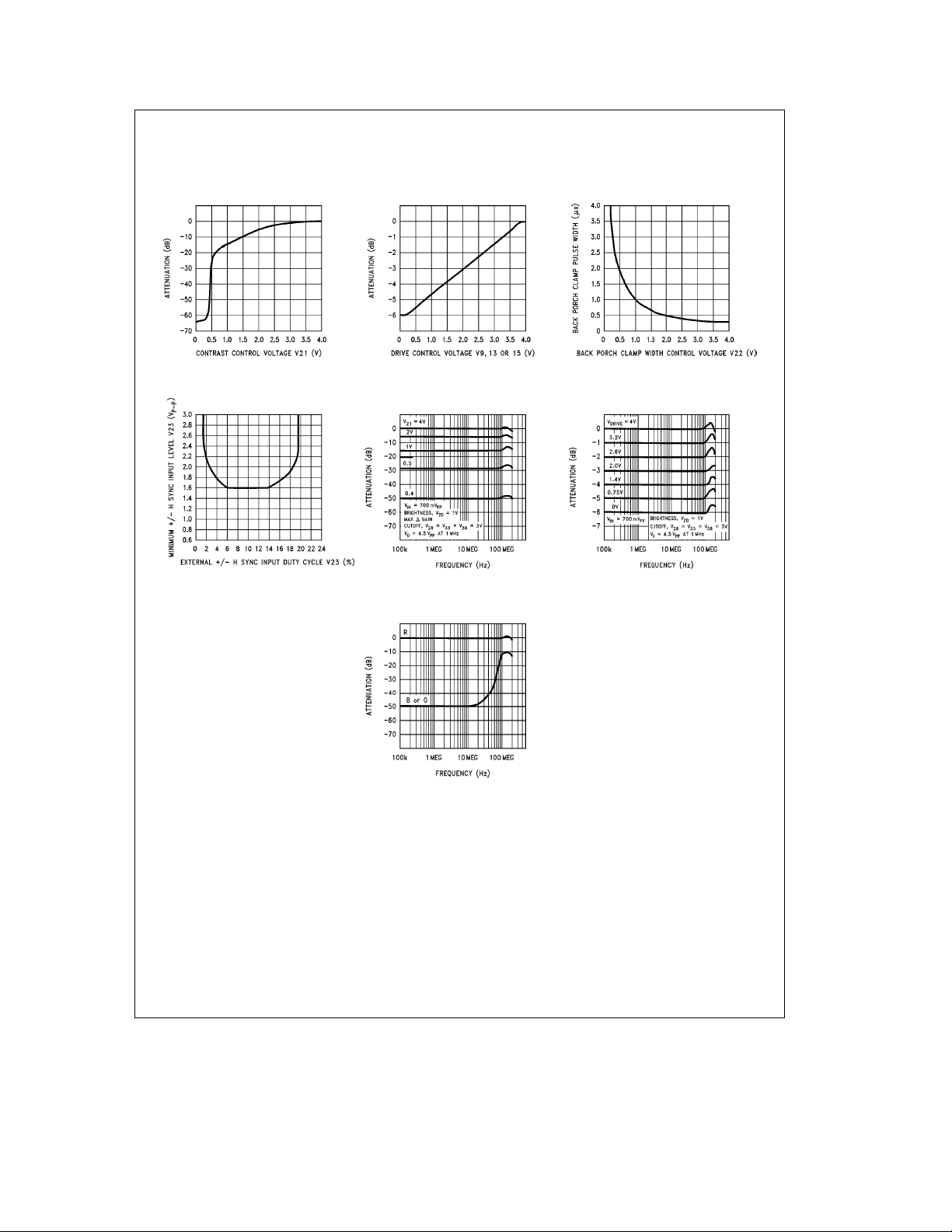

Typical Performance Characteristics V

CC

e

12V, T

e

25§C unless otherwise specified

A

Attenuation vs Contrast

Control Voltage (

Minimum External

Sync Input Level (V

vs Input Duty Cycle (%)

f

e

g

H

PP

12 kHz)

Attenuation vs Drive

Control Voltage (

f

e

12 kHz)

Back Porch Clamp Pulse

Width vs Pin 22 Voltage

)

Contrast vs Frequency Drive Control vs Frequency

Crosstalk vs Frequency

TL/H/11238– 2

5

TL/H/11238– 3

FIGURE 1. LM1204 Test Circuit

6

Loading...

Loading...