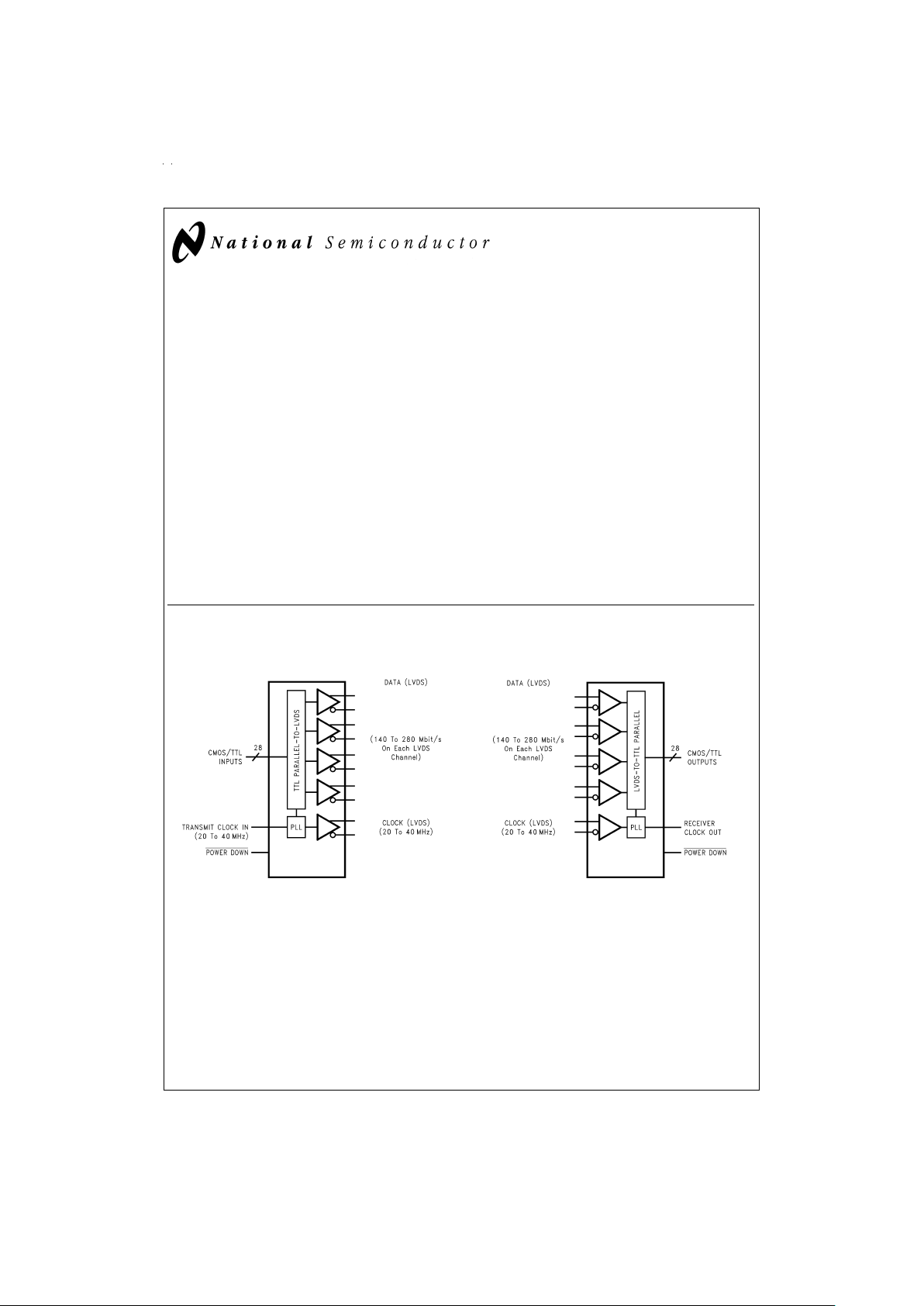

DS90CR281/DS90CR282

28-Bit Channel Link

General Description

The DS90CR281 transmitter converts 28 bits of CMOS/TTL

data intofour LVDS (Low Voltage Differential Signaling) data

streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle

of the transmit clock 28 bits of input data are sampled and

transmitted. The DS90CR282 receiver converts the LVDS

data streams back into 28 bits of CMOS/TTL data. At a transmit clock frequency of 40 MHz, 28 bits of TTL data are transmitted at a rate of 280 Mbps per LVDS data channel. Using

a 40 MHz clock, the data throughput is 1.12 Gbit/s

(140 Mbytes/s).

The multiplexing of the data lines provides a substantial

cable reduction. Long distance parallel single-ended buses

typically require a ground wire per active signal (and have

very limited noise rejection capability). Thus, for a 28-bit wide

data bus and one clock, up to 58 conductors are required.

With the Channel Link chipset as few as 11 conductors (4

data pairs, 1 clock pair and a minimum of one

ground) are needed. This provides a 80%reduction in required cable width, which provides a system cost savings,

reduces connector physical size and cost, and reduces

shielding requirements due to the cables’ smaller form factor.

The 28 CMOS/TTL inputs can support a variety of signal

combinations. For example, 7 4-bit nibbles or 3 9-bit (byte +

parity) and 1 control.

Features

n Narrow bus reduces cable size and cost

n

±

1V common mode range (ground shifting)

n 290 mV swing LVDS data transmission

n 1.12 Gbit/s data throughput

n Low swing differential current mode drivers reduce EMI

n Rising edge data strobe

n Power down mode

n Offered in low profile 56-lead TSSOP package

Block Diagrams

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

DS90CR281

DS012638-27

Order Number DS90CR281MTD

See NS Package Number MTD56

DS90CR282

DS012638-1

Order Number DS90CR282MTD

See NS Package Number MTD56

July 1997

DS90CR281/DS90CR282 28-Bit Channel Link

© 1998 National Semiconductor Corporation DS012638 www.national.com

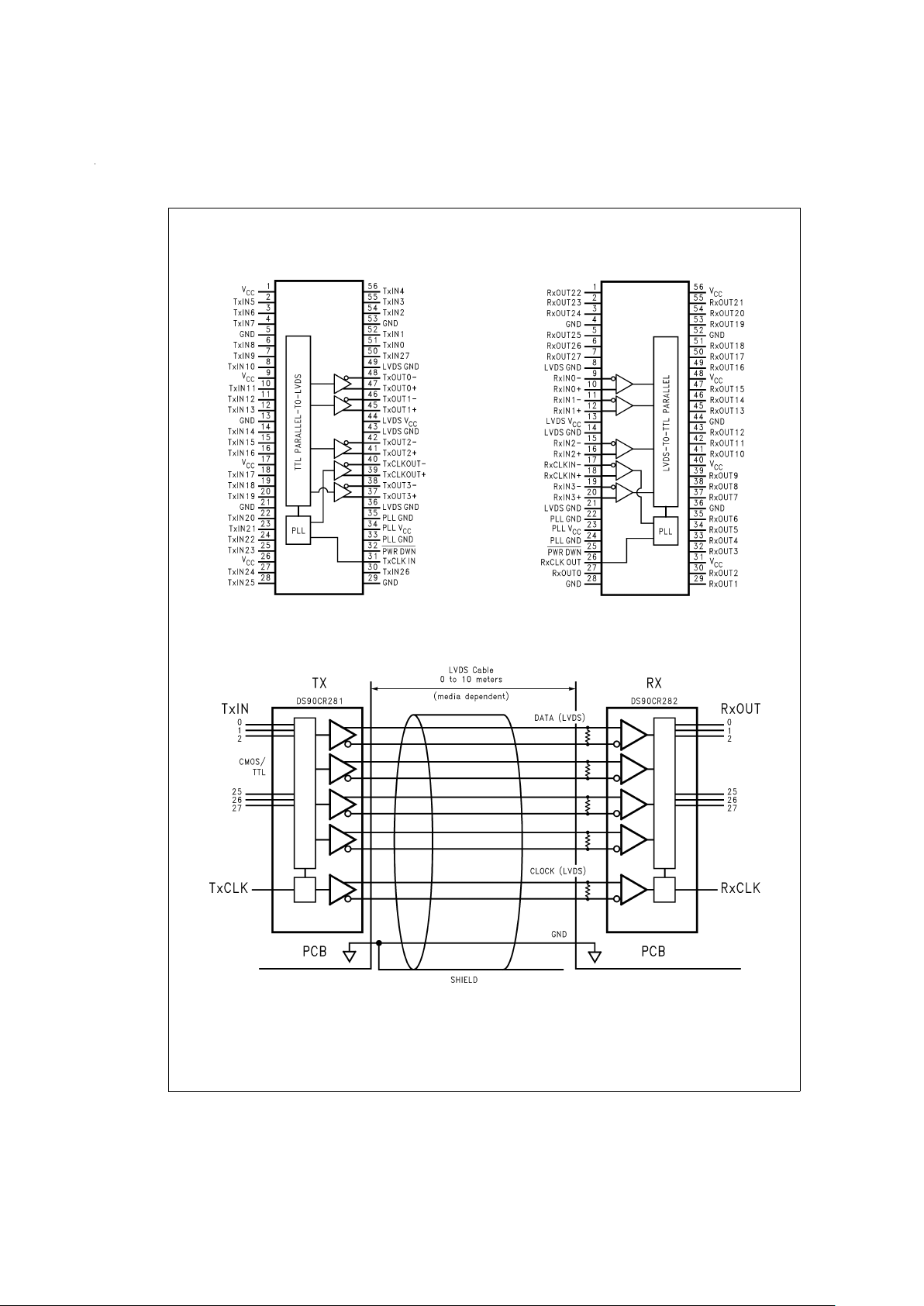

Connection Diagrams

Typical Application

DS90CR281

DS012638-2

DS90CR282

DS012638-3

DS012638-19

www.national.com 2

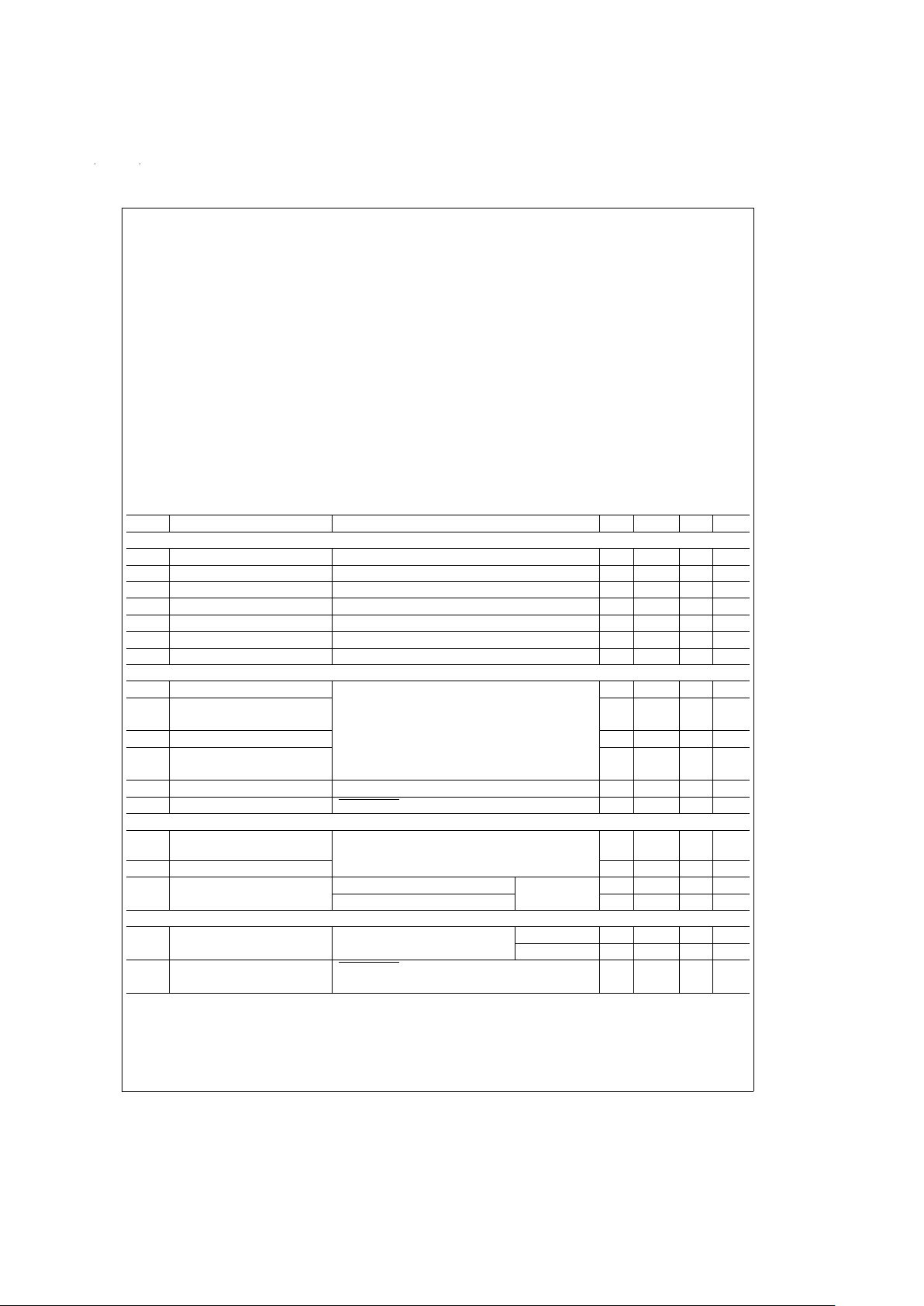

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CC

) −0.3V to +6V

CMOS/TTL Input Voltage −0.3V to (V

CC

+ 0.3V)

CMOS/TTL Ouput Voltage −0.3V to (V

CC

+ 0.3V)

LVDS Receiver Input Voltage −0.3V to (V

CC

+ 0.3V)

LVDS Driver Output Voltage −0.3V to (V

CC

+ 0.3V)

LVDS Output Short Circuit

Duration continuous

Junction Temperature +150˚C

Storage Temperature Range −65˚C to +150˚C

Lead Temperature

(Soldering, 4 sec.) +260˚C

Maximum Package Power Dissipation

@

+25˚C

MTD56(TSSOP) Package:

DS90CR281 1.63W

DS90CR282 1.61W

Package Derating:

DS90CR281 12.5 mW/˚C above +25˚C

DS90CR282 12.4 mW/˚C above +25˚C

This device does not meet 2000V ESD rating (Note 4).

Recommended Operating

Conditions

Min Max Units

Supply Voltage (V

CC

) 4.5 5.5 V

Operating Free Air Temperature (T

A

) −10 +70 ˚C

Receiver Input Range 0 2.4 V

Supply Noise Voltage (V

CC

) 100 mV

P-P

Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified

Symbol Parameter Conditions Min Typ Max Units

CMOS/TTL DC SPECIFICATIONS

V

IH

High Level Input Voltage 2.0 V

CC

V

V

IL

Low Level Input Voltage GND 0.8 V

V

OH

High Level Output Voltage I

OH

=

−0.4 mA 3.8 4.9 V

V

OL

Low Level Output Voltage I

OL

=

2 mA 0.1 0.3 V

V

CL

Input Clamp Voltage I

CL

=

−18 mA −0.79 −1.5 V

I

IN

Input Current V

IN

=

V

CC

, GND, 2.5V or 0.4V

±

5.1±10 µA

I

OS

Output Short Circuit Current V

OUT

=

0V −120 mA

LVDS DRIVER DC SPEClFlCATIONS

V

OD

Differential Output Voltage R

L

=

100Ω 250 290 450 mV

∆V

OD

Change in VODbetween 35 mV

Complementary Output States

V

CM

Common Mode Voltage 1.1 1.25 1.375 V

∆V

CM

Change in VCMbetween 35 mV

Complementary Output States

I

OS

Output Short Circuit Current V

OUT

=

OV, R

L

=

100Ω −2.9 −5 mA

I

OZ

Output TRI-STATE®Current Power Down=0V, V

OUT

=

0V or V

CC

±1±

10 µA

LVDS RECEIVER DC SPECIFlCATIONS

V

TH

Differential Input High

Threshold

V

CM

=

+1.2V +100 mV

V

TL

Differential Input Low Threshold −100 mV

I

IN

Input Current V

IN

=

+2.4V V

CC

=

5.5V

<

±1±

10 µA

V

IN

=

0V

<

±1±

10 µA

TRANSMITTER SUPPLY CURRENT

I

CCTW

Transmitter Supply Current, R

L

=

100Ω,C

L

=

5 pF, f=32.5 MHz 34 51 mA

Worst Case Worst Case Pattern (

Figures 1, 2

)f=37.5 MHz 36 53 mA

I

CCTZ

Transmitter Supply Current, Power Down=Low 125µA

Power Down

www.national.com3

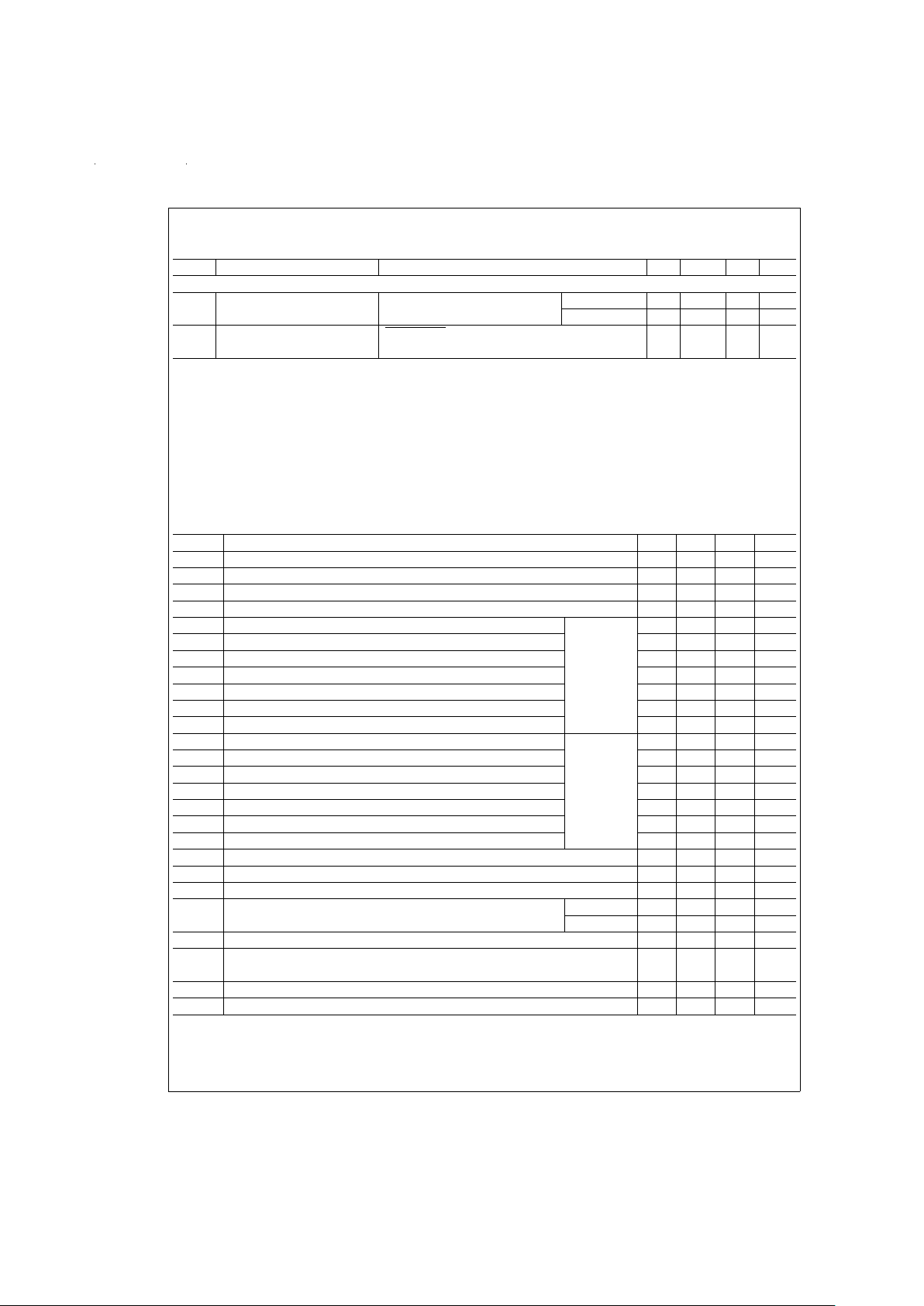

Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified

Symbol Parameter Conditions Min Typ Max Units

RECEIVER SUPPLY CURRENT

I

CCRW

Receiver Supply Current, C

L

=

8 pF, f=32.5 MHz 55 75 mA

Worst Case Worst Case Pattern (

Figures 1, 3

)f=37.5 MHz 60 80 mA

I

CCRZ

Receiver Supply Current, Power Down=Low 110µA

Power Down

Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device

should be operated at these limits. The tables of “Electrical Characteristics” specify conditions for device operation.

Note 2: Typical values are given for V

CC

=

5.0V and T

A

=

+25˚C.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except V

OD

and ∆VOD).

Note 4: ESD Rating: HBM (1.5 kΩ, 100 pF)

PLL V

CC

≥ 1000V

All other pins ≥ 2000V

EIAJ (0Ω, 200 pF) ≥ 150V

Transmitter Switching Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified

Symbol Parameter Min Typ Max Units

LLHT LVDS Low-to-High Transition Time (

Figure 2

) 0.75 1.5 ns

LHLT LVDS High-to-Low Transition Time (

Figure 2

) 0.75 1.5 ns

TCIT TxCLK IN Transition Time (

Figure 4

)8ns

TCCS TxOUT Channel-to-Channel Skew (Note 5) (

Figure 5

) 350 ps

TPPos0 Transmitter Output Pulse Position for Bit 0 (

Figure 16

)f

=

20 MHz −200 150 350 ps

TPPos1 Transmitter Output Pulse Position for Bit 1 6.3 7.2 7.5 ns

TPPos2 Transmitter Output Pulse Position for Bit 2 12.8 13.6 14.6 ns

TPPos3 Transmitter Output Pulse Position for Bit 3 20 20.8 21.5 ns

TPPos4 Transmitter Output Pulse Position for Bit 4 27.2 28 28.5 ns

TPPos5 Transmitter Output Pulse Position for Bit 5 34.5 35.2 35.6 ns

TPPos6 Transmitter Output Pulse Position for Bit 6 42.2 42.6 42.9 ns

TPPos0 Transmitter Output Pulse Position for Bit 0 (

Figure 16

)f

=

40 MHz −100 100 300 ps

TPPos1 Transmitter Output Pulse Position for Bit 1 2.9 3.3 3.9 ns

TPPos2 Transmitter Output Pulse Position for Bit 2 6.1 6.6 7.1 ns

TPPos3 Transmitter Output Pulse Position for Bit 3 9.7 10.2 10.7 ns

TPPos4 Transmitter Output Pulse Position for Bit 4 13 13.5 14.1 ns

TPPos5 Transmitter Output Pulse Position for Bit 5 17 17.4 17.8 ns

TPPos6 Transmitter Output Pulse Position for Bit 6 20.3 20.8 21.4 ns

TCIP TxCLK IN Period (

Figure 6

) 25 T 50 ns

TCIH TxCLK IN High Time (

Figure 6

) 0.35T 0.5T 0.65T ns

TCIL TxCLK IN Low Time (

Figure 6

) 0.35T 0.5T 0.65T ns

TSTC TxIN Setup to TxCLK IN (

Figure 6

) f = 20 MHz 14 ns

f=40MHz 8 ns

THTC TxIN Hold to TxCLK IN (

Figure 6

) 2.5 2 ns

TCCD TxCLK IN to TxCLK OUT Delay

@

25˚C, 5 9.7 ns

V

CC

=

5.0V (

Figure 8

)

TPLLS Transmitter Phase Lock Loop Set (

Figure 10

)10ms

TPDD Transmitter Powerdown Delay (

Figure 14

) 100 ns

Note 5: This limit based on bench characterization.

www.national.com 4

Receiver Switching Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified

Symbol Parameter Min Typ Max Units

CLHT CMOS/TTL Low-to-High Transition Time (

Figure 3

) 3.5 6.5 ns

CHLT CMOS/TTL High-to-Low Transition Time (

Figure 3

) 2.7 6.5 ns

RCOP RxCLK OUT Period (

Figure 7

) 25 T 50 ns

RSKM Receiver Skew Margin (Note 6)

V

CC

=

5V, T

A

=

25˚C (

Figure 17

)f

=

20 MHz 1.1 ns

f=40 MHz 700 ps

RCOH RxCLK OUT High Time (

Figure 7

)

f=20 MHz 19 ns

f=40 MHz 6 ns

RCOL RxCLK OUT Low Time (

Figure 7

)

f=20 MHz 21.5 ns

f=40 MHz 10.5 ns

RSRC RxOUT Setup to RxCLK OUT (

Figure 7

)

f=20 MHz 14 ns

f=40 MHz 4.5 ns

RHRC RxOUT Hold to RxCLK OUT (

Figure 7

)

f=20 MHz 16 ns

f=40 MHz 6.5 ns

RCCD RxCLK IN to RxCLK OUT Delay

@

25˚C, 7.6 11.9 ns

V

CC

=

5.0V (

Figure 9

)

RPLLS Receiver Phase Lock Loop Set (

Figure 11

)10ms

RPDD Receiver Powerdown Delay (

Figure 15

)1µs

Note 6: Receiver Skew Margin is defined as the valid data sampling region atthereceiverinputs.Thismargintakesintoaccount for transmitter output skew (TCCS)

and the setup and hold time (internal data sampling window), allowing LVDS cable skew dependent on the type/length and source clock (TxCLK IN) jitter.

RSKM ≥ cable skew (type, length) + source clock jitter (cycle to cycle).

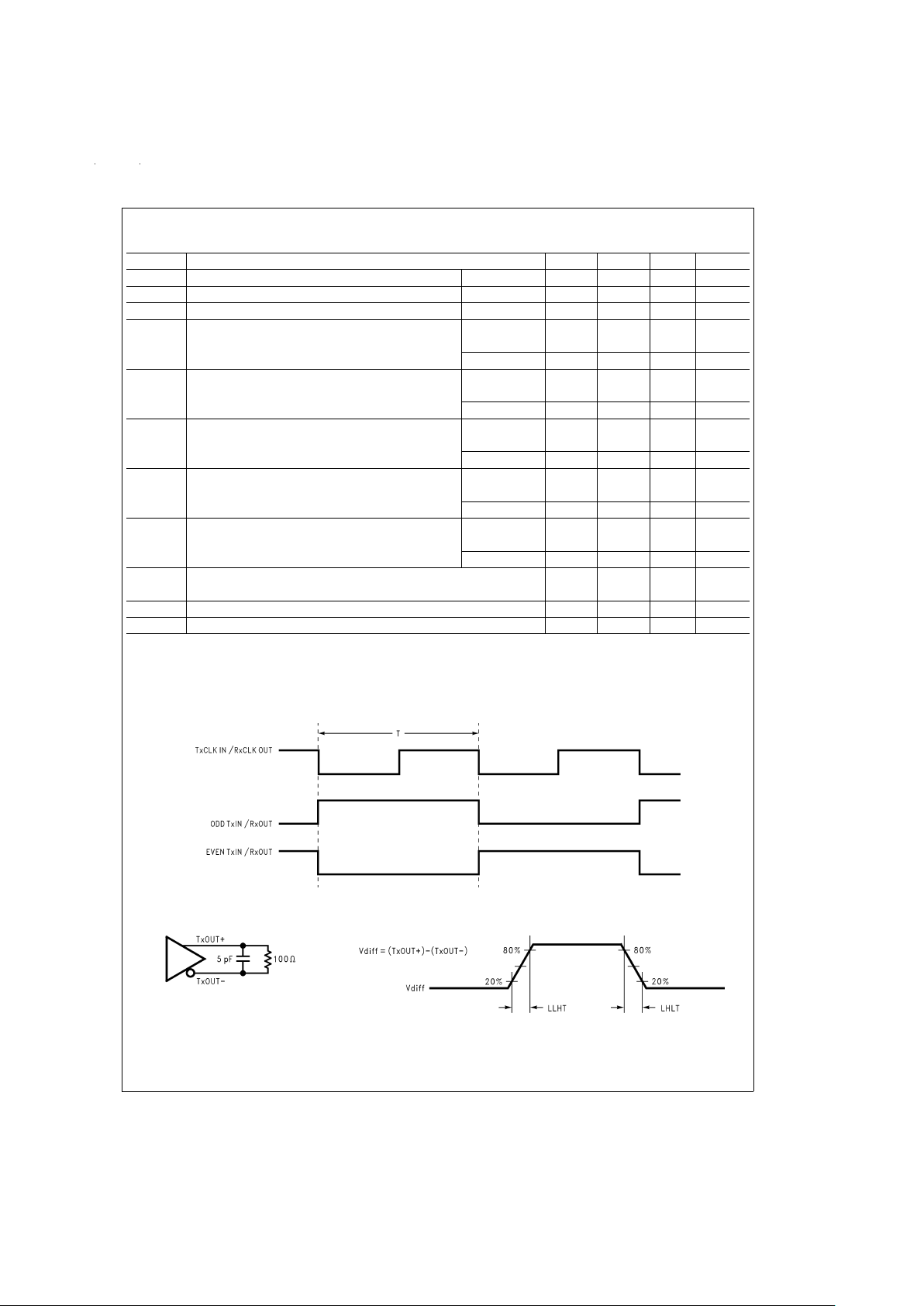

AC Timing Diagrams

DS012638-4

FIGURE 1. “WORST CASE” Test Pattern

DS012638-5

DS012638-6

FIGURE 2. DS90CR281 (Transmitter) LVDS Output Load and Transition Timing

www.national.com5

Loading...

Loading...