ADC10321

10-Bit, 20MSPS, 98mW A/D Converter with Internal

Sample and Hold

ADC10321 10-Bit, 20MSPS, 98mW A/D Converter with Internal Sample and Hold

January 2000

General Description

The ADC10321 is a low power, high performance CMOS

analog-to-digital converter that digitizes signals to 10 bits

resolution at sampling rates up to 25Msps while consuming

a typical 98mW from a single 5V supply. Reference force

and sense pins allow the user to connect an external reference buffer amplifierto ensure optimal accuracy. No missing

codes is guaranteed over the full operating temperature

range. The unique twostage architecture achieves 9.2 Effective Bits with a 10MHz input signal and a 20MHz clock frequency. Output formatting is straight binary coding.

To ease interfacing to 3V systems, the digital I/O power pins

of the ADC10321 can be tied to a 3V power source, making

the outputs 3V compatible. Whennot converting, power consumption can be reduced by pulling the PD (Power Down)

pin high, placing the converter into a low power standby

state, where it typically consumes less than 4mW. The

ADC10321’s speed, resolution and single supply operation

makes it well suited for a variety of applications in video, imaging, communications, multimedia and high speed data acquisition. Low power, single supply operation ideally suit the

ADC10321 for high speed portable applications, and its

speed and resolution are ideal for charge coupled device

(CCD) input systems.

The ADC10321 comes in a space saving 32-pin TQFP and

operates over the industrial (−40˚C ≤ T

ture range.

≤ +85˚C) tempera-

A

Features

n Internal Sample-and-Hold

n Single +5V Operation

n Low Power Standby Mode

n Guaranteed No Missing Codes

n Tri-State Outputs

n TTL/CMOS or 3V Logic Input/Output Compatible

Key Specifications

n Resolution 10 Bits

n Conversion Rate 20 Msps

n ENOB 10MHz Input 9.2 Bits (typ)

n DNL 0.35 LSB (typ)

n Conversion Latency 2 Clock Cycles

n PSRR 56dB

n Power Consumption 98mW (typ)

n Low Power Standby Mode

<

4mW (typ)

Applications

n Digital Video

n Communications

n Document Scanners

n Medical Imaging

n Electro-Optics

n Plain Paper Copiers

n CCD Imaging

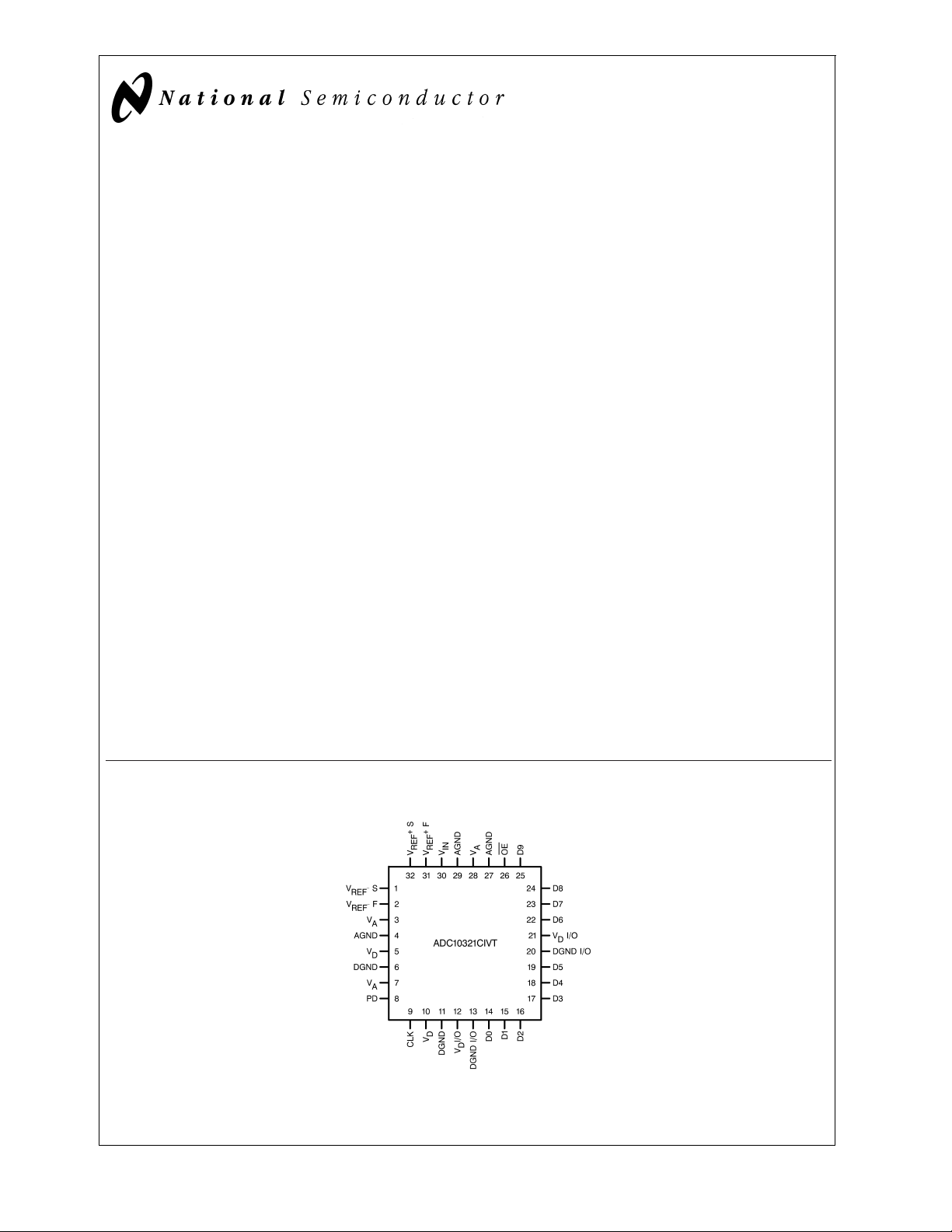

Connection Diagram

DS100897-1

© 2000 National Semiconductor Corporation DS100897 www.national.com

Ordering Information

ADC10321

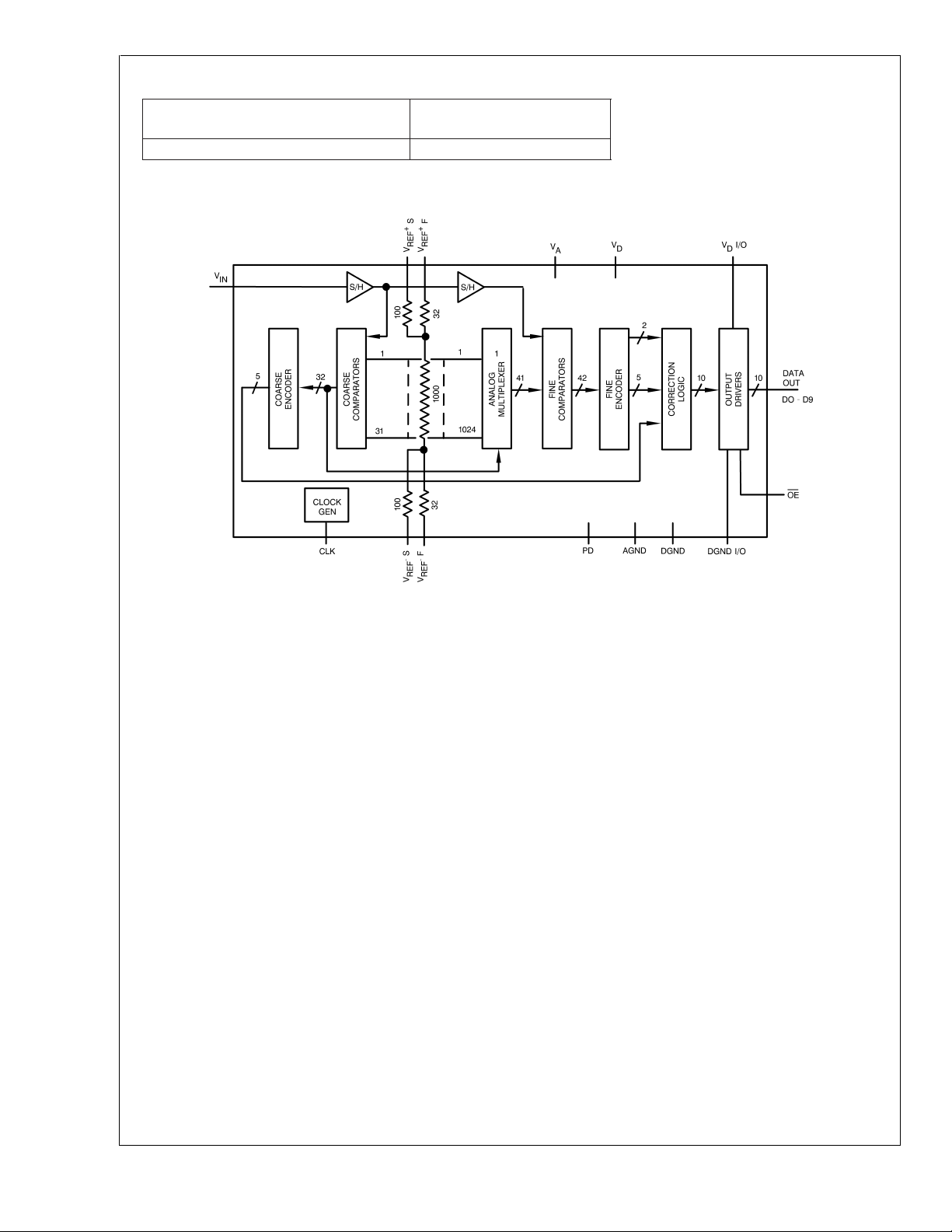

Block Diagram

Commercial

(−40˚C ≤ T

ADC10321CIVT TQFP

≤ +85˚C)

A

NS Package

DS100897-2

www.national.com 2

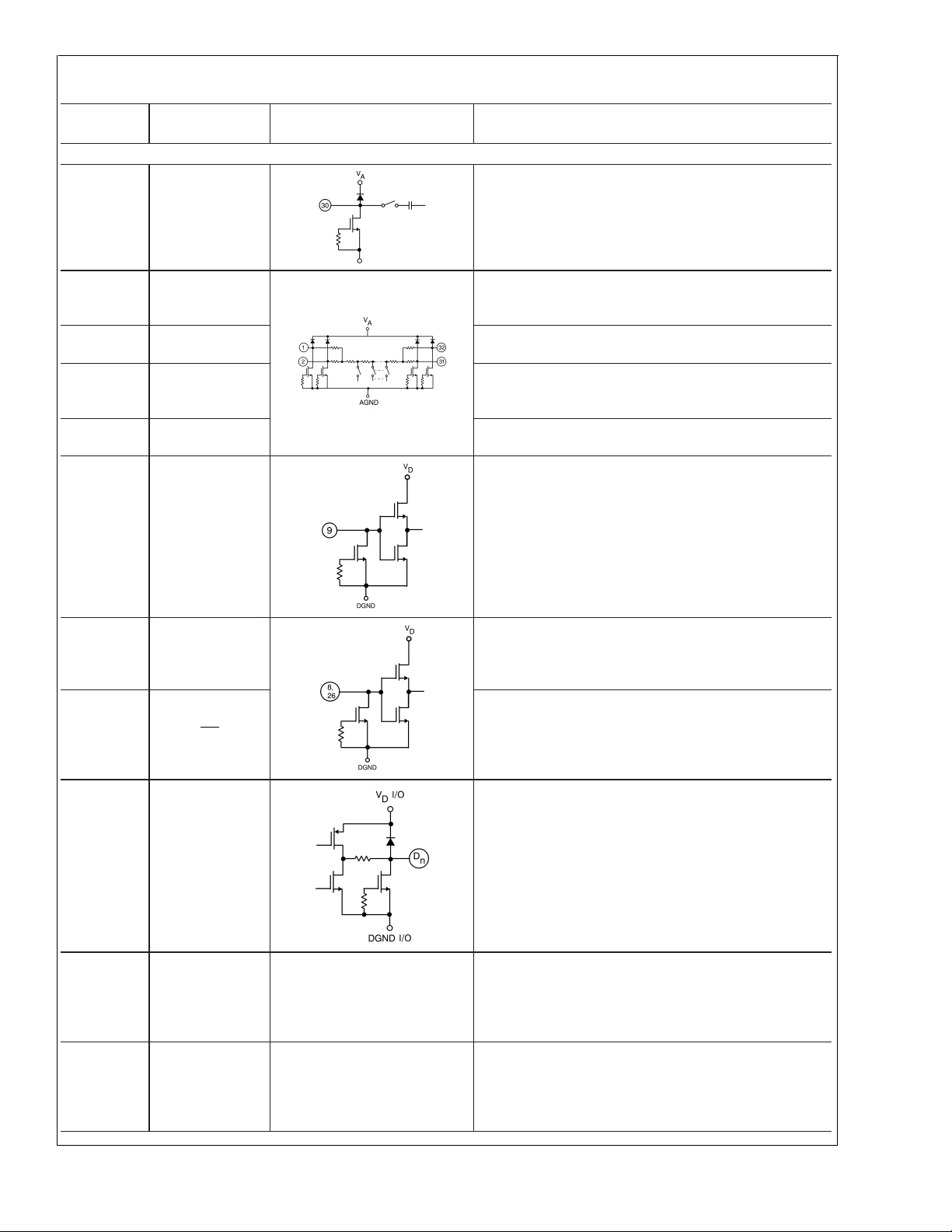

Pin Descriptions and Equivalent Circuits

ADC10321

Pin

Symbol Equivalent Circuit

No.

Analog I/O

30 V

31 V

32 V

2V

1V

IN

REF

REF

REF

REF−

+

+

−

9 CLK

Description

Analog Input signal to be converted. Conversion

range is V

REF

+

StoV

REF

−

S.

Analog input that goes to the high side of the

F

S

reference ladder of the ADC. This voltage should

+

force V

S to be in the range of 2.3V to 4.0V.

REF

Analog output used to sense the voltage at the top

of the ADC reference ladder.

Analog input that goes to the low side of the

F

S

reference ladder of the ADC. This voltage should

force V

S to be in the range of 1.3V to 3.0V.

REF−

Analog output used to sense the voltage at the

bottom of the ADC reference ladder.

Converter digital clock input. VINis sampled on the

falling edge of CLK input.

8PD

26 OE

14

thru

19

and

D0 -D9

22

thru

25

3, 7,

28

5, 10 V

V

A

D

Power Down input. When this pin is high, the

converter is in the Power Down mode and the data

output pins are in a high impedance state.

Output Enable pin. When this pin and the PD pin

are low, the output data pins are active. When this

pin or the PD pin is high, the output data pins are in

a high impedance state.

Digital Output pins providing the 10 bit conversion

results. D0 is the LSB, D9 is the MSB. Valid data is

present just after the falling edge of the CLK input.

Positive analog supply pins. These pins should be

connected to a clean, quiet voltage source of +5V.

and VDshould have a common supply and be

V

A

separately bypassed with 10µF to 50µF capacitors

in parallel with 0.1µF capacitors.

Positive digital supply pins. These pins should be

connected to a clean, quiet voltage source of +5V.

and VDshould have a common supply and be

V

A

separately bypassed with 10µF to 50µF capacitors

in parallel with 0.1µF capacitors.

www.national.com3

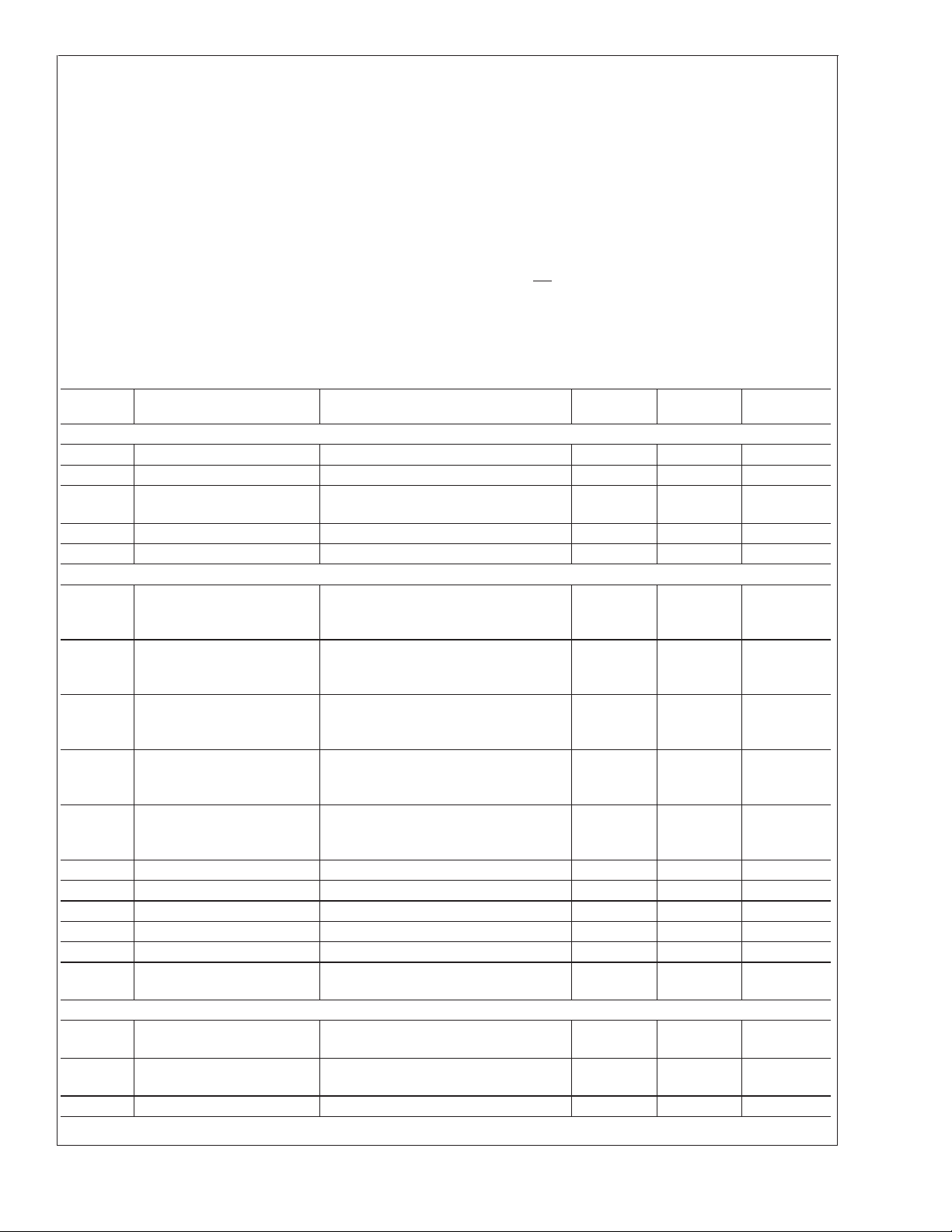

Pin Descriptions and Equivalent Circuits (Continued)

ADC10321

Pin

No.

Analog I/O

12, 21 V

4, 27,

29

6, 11 DGND

13, 20 DGND I/O The ground return of the digital output drivers.

Symbol Equivalent Circuit

I/O

D

AGND

Description

Positive supply pins for the digital output drivers.

These pins should be connected to a clean, quiet

voltage source of +3V to +5V and be separately

bypassed with 10µF capacitors.

The ground return for the analog supply. AGND and

DGND should be connected together close to the

ADC10321 package.

The ground return for the digital supply. AGND and

DGND should be connected together close to the

ADC10321 pacjage.

www.national.com 4

ADC10321

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

Soldering Temp., Infrared, 10 sec. (Note 6) 300˚C

Storage Temperature −65˚C to +150˚C

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Positive Supply Voltage (V=V

Voltage on Any I/O Pin −0.3V to (V

=

) 6.5V

V

A

D

or VD) +0.3V)

A

Input Current at Any Pin (Note 3)

Package Input Current (Note 3)

Package Dissipation at T

=

25˚C See (Note 4)

A

ESD Susceptibility (Note 5)

Human Body Model 1500V

±

25mA

±

50mA

Operating Ratings(Notes 1, 2)

Operating Temperature −40˚C ≤ T

V

Supply Voltage +4.5V to +5.5V

A,VD

V

I/O Supply Voltage +2.7V to 5.5V

D

V

Voltage Range 1.3V to (VA-1.0V)

IN

V

+ Voltage Range 2.3V to (VA-1.0V)

REF

V

− Voltage Range 1.3V to 3.0V

REF

PD, CLK, OE Voltage

−0.3V to + 5.5V

≤ +85˚C

A

Machine Model 200V

Converter Electrical Characteristics

The following specifications apply for V

=

C

20pF, f

L

CLK

=

20MHz, R

=

S

=

+5.0V

A

25Ω. Boldface limits apply for T

Symbol Parameter Conditions

Static Converter Characteristics

INL Integral Non-Linearity

DNL Differential-Non Linearity

Resolution with No Missing

Codes

Zero Scale Offset Error −6 mV(max)

Full-Scale Error −6 mV(max)

Dynamic Converter Characteristics

=

f

IN

ENOB Effective Number of Bits

S/(N+D)

Signal-to-Noise Plus

Distortion Ratio

SNR Signal-to-Noise Ratio

THD Total Harmonic Distortion

SFDR

Spurious Free Dynamic

Range

DG Differential Gain Error f

DP Differential Phase Error f

Overrange Output Code V

Underrange Output Code V

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

f

IN

=

IN

=

IN

>

IN

<

IN

BW Full Power Bandwidth 150 MHz

PSRR

Power Supply Rejection

Ratio

Change in Full Scale with 4.5V to

5.5V Supply Change

Reference and Analog Input Characteristics

V

IN

C

IN

I

IN

Analog Input Range

Analog VINInput

Capacitance

Input Leakage Current 10 µA

DC,VD

=

5.0V

DC,VD

A

=

I/O=5.0VDC,V

to T

T

MIN

: all other limits T

MAX

+=+3.5VDC,V

REF

Typical

(Note 8)

±

0.45

±

0.35

1.0MHz

4.43MHz

10MHz

1.0MHz

4.43MHz

10MHz

1.0MHz

4.43MHz

10MHz

1.0MHz

4.43MHz

10MHz

1.0MHz

4.43MHz

10MHz

4.43MHz, f

4.43MHz, f

V

+ 1023

REF

V

− 0

REF

=

17.72MHz 0.5

CLK

=

17.72MHz 0.5 deg(max)

CLK

9.5

9.5

9.2

59

59

57

60

60

58

−71

−70

−66

74

72

68

56 dB

5pF

−=+1.5VDC,

REF

=

25˚C(Note 7)

A

Limits

(Note 9)

±

1.0 LSB(max)

±

0.85 LSB(max)

10 Bits

9.0

56

58

−59

Bits(min)

dB(min)

dB(min)

dB(min)

60

%

1.3

4.0

V(min)

V(max)

Units

Bits

Bits

dB

dB

dB

dB

dB

dB

dB

dB

dB

(max)

www.national.com5

Loading...

Loading...