NSC 5962-8995001SFA, 5962-8995001SEA, 5962-8995001S2A, 5962-8995001MFA, 5962-8995001M2A Datasheet

...

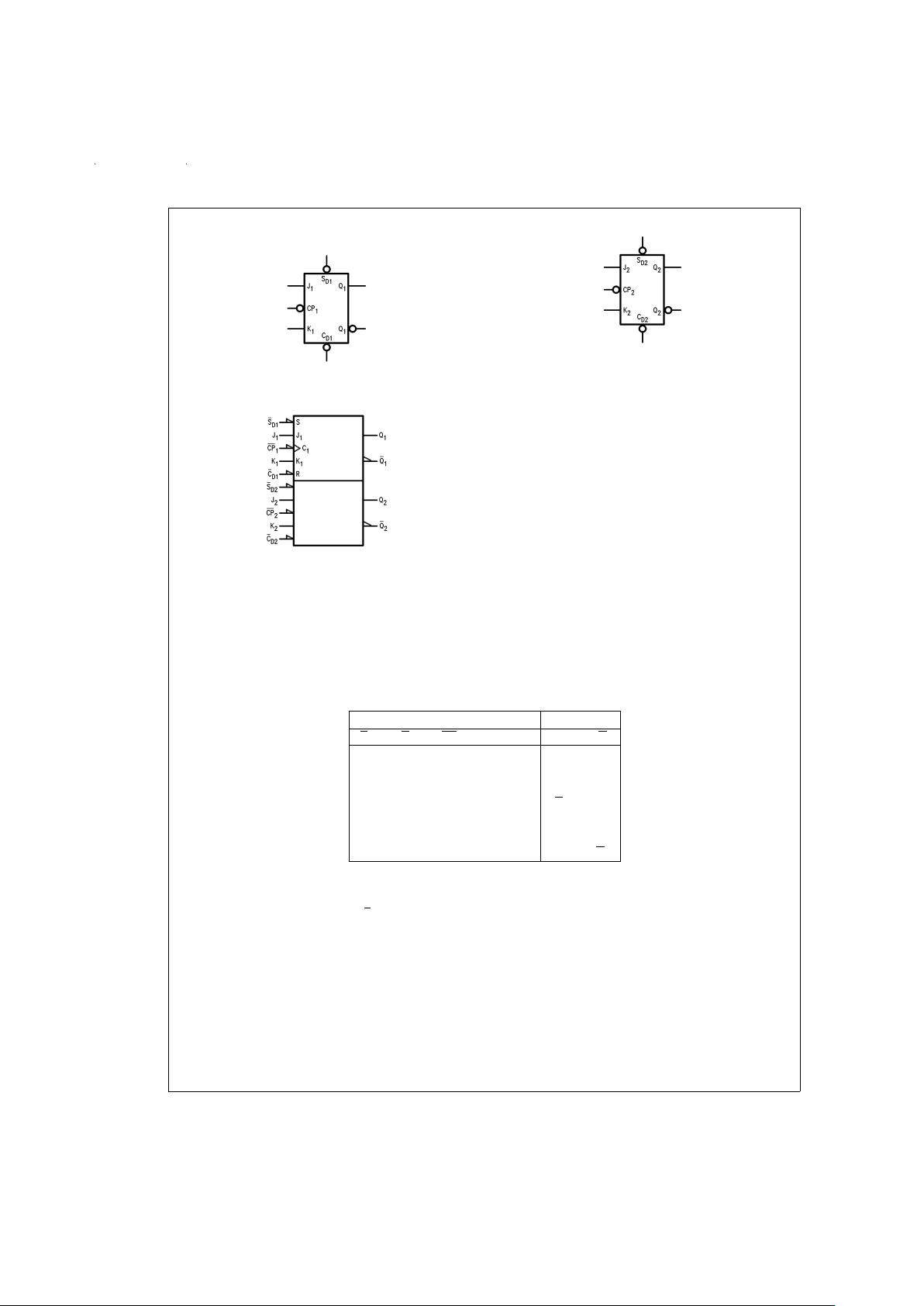

54ACT112

Dual JK Negative Edge-Triggered Flip-Flop

General Description

The ’ACT112 contains two independent, high-speed JK

flip-flops with Direct Set and Clear inputs. Synchronous state

changes are initiated by thefallingedgeoftheclock.Triggering occurs at a voltage level of the clock and is not directly

related to the transition time. The J and K inputs can change

when the clock is in either state without affecting the flip-flop,

provided that they are in the desired state during the recommended setup and hold times relative to the falling edge of

the clock. A LOW signal on S

D

or CDprevents clocking and

forces Q or Q HIGH, respectively. Simultaneous LOW signals on SDand CDforce both Q and Q HIGH.

Asynchronous Inputs:

LOW input to S

D

sets Q to HIGH level

LOW input to CDsets Q to LOW level

Clear and Set are independent of clock

Simultaneous LOW on C

D

and SDmakes both Q and Q

HIGH

Features

n ’ACT112 has TTL-compatible inputs

n Outputs source/sink 24 mA

n Standard Microcircuit Drawing (SMD) 5962-8995001

Connection Diagram Pin Descriptions

Pin Names Description

J

1,J2,K1,K2

Data Inputs

CP

1

,CP

2

Clock Pulse Inputs

(Active Falling Edge)

C

D1,CD2

Direct Clear Inputs (Active LOW)

S

D1,SD2

Direct Set Inputs (Active LOW)

Q

1,Q2,Q1,Q2

Outputs

FACT™is a trademark ofFairchild Semiconductor Corporation.

Pin Assigment for

DIP and Flatpack

DS100976-3

Pin Assigment

for LCC

DS100976-5

September 1998

54ACT112 Dual JK Negative Edge-Triggered Flip-Flop

© 1998 National Semiconductor Corporation DS100976 www.national.com

Logic Symbols

Truth Table

Inputs Outputs

S

D

C

D

CP JKQ Q

LHXXXHL

HLXXXLH

LLXXXHH

HHMhhQ

0

Q

0

HHMlhLH

HHMhlHL

HHMllQ

0

Q

0

H (h)=HIGH Voltage Level

L (l)=LOW Voltage Level

X=Immaterial

M=HIGH-to-LOW Clock Transition

Q

0(Q0

)=Before HIGH-to-LOW Transition of Clock

Lower case letters indicate the state of the referenced input or output one setup time prior to the HIGH-to-LOW clock

transition.

DS100976-1

IEEE/IEC

DS100976-4

DS100976-2

www.national.com 2

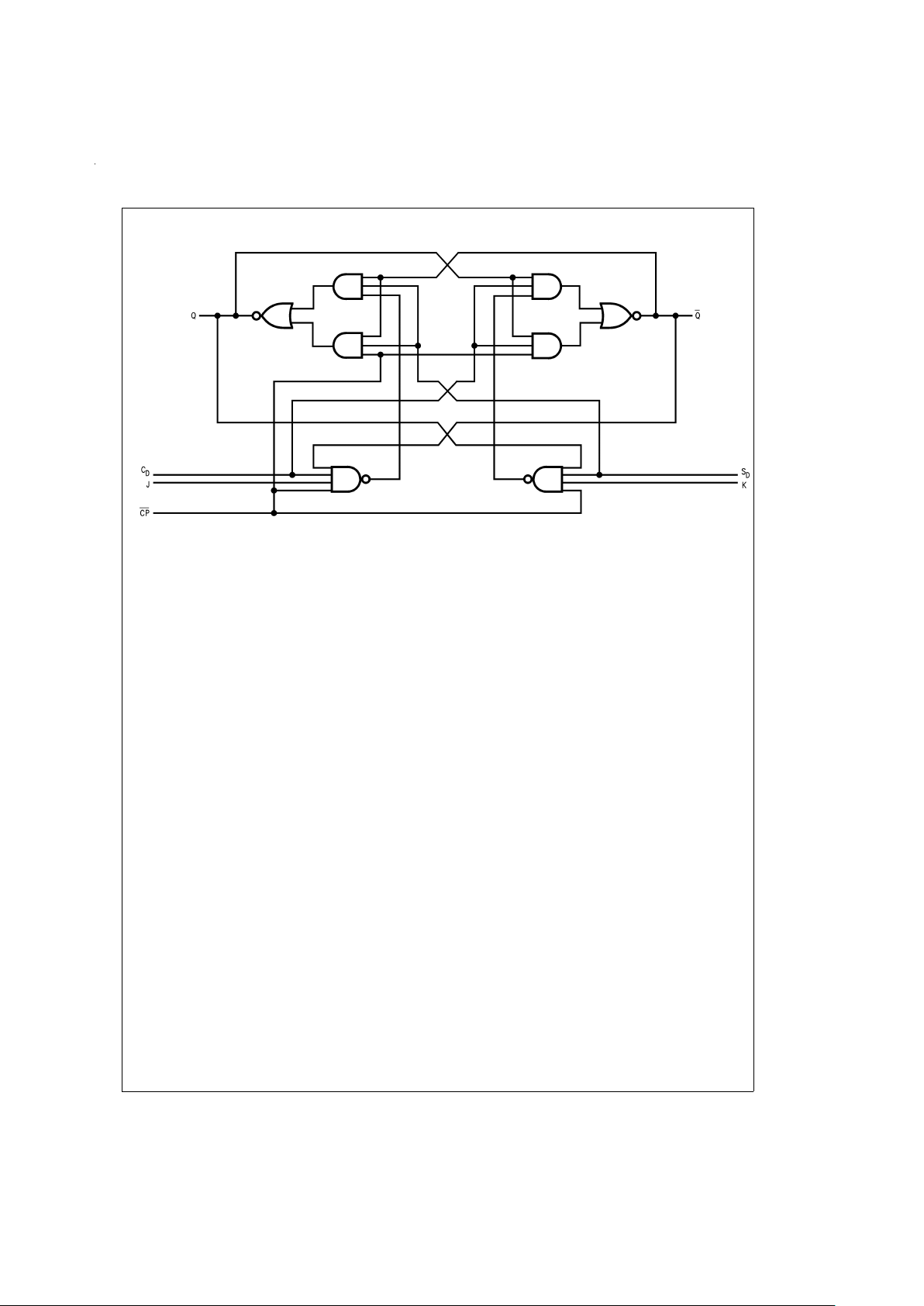

Logic Diagram (One Half Shown)

DS100976-6

www.national.com3

Loading...

Loading...