NSC 5962-8776101FA, 5962-87761012A, 5962-8776101EA, 54ACT253MDA Datasheet

54AC253•54ACT253

Dual 4-Input Multiplexer with TRI-STATE

®

Outputs

General Description

The ’AC/’ACT253 is a dual 4-input multiplexer with

TRI-STATE outputs. It can select two bits of data from four

sources using common select inputs. The outputs may be individually switched to a high impedance state with a HIGH

on the respective Output Enable (OE) inputs, allowing the

outputs to interface directly with bus oriented systems.

Features

n ICCand IOZreduced by 50

%

n Multifunction capability

n Noninverting TRI-STATE outputs

n Outputs source/sink 24 mA

n ’ACT253 has TTL-compatible inputs

n Standard Military Drawing (SMD)

—’AC253: 5962-87693

—’ACT253: 5962-87761

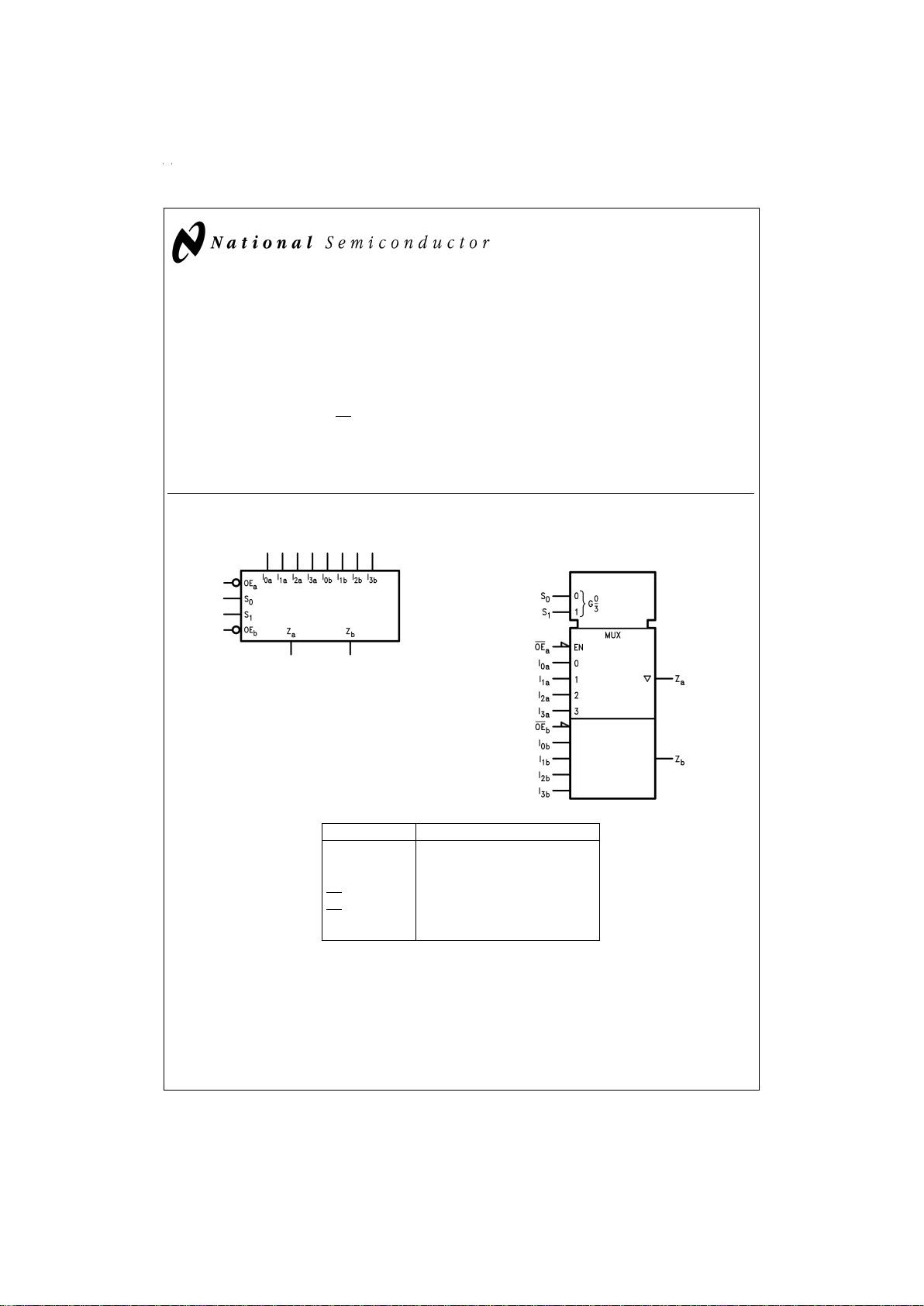

Logic Diagrams

Pin Names Description

I

0a–I3a

Side A Data Inputs

I

0b–I3b

Side B Data Inputs

S

0,S1

Common Select Inputs

OE

a

Side A Output Enable Input

OE

b

Side B Output Enable Input

Z

a,Zb

TRI-STATE Outputs

TRI-STATE®is a registered trademarkof National Semiconductor Corporation.

FACT

®

is a registered trademark of Fairchild Semiconductor Corporation.

DS100285-1

IEEE/IEC

DS100285-2

August 1998

54AC253

•

54ACT253 Dual 4-Input Multiplexer with TRI-STATE Outputs

© 1998 National Semiconductor Corporation DS100285 www.national.com

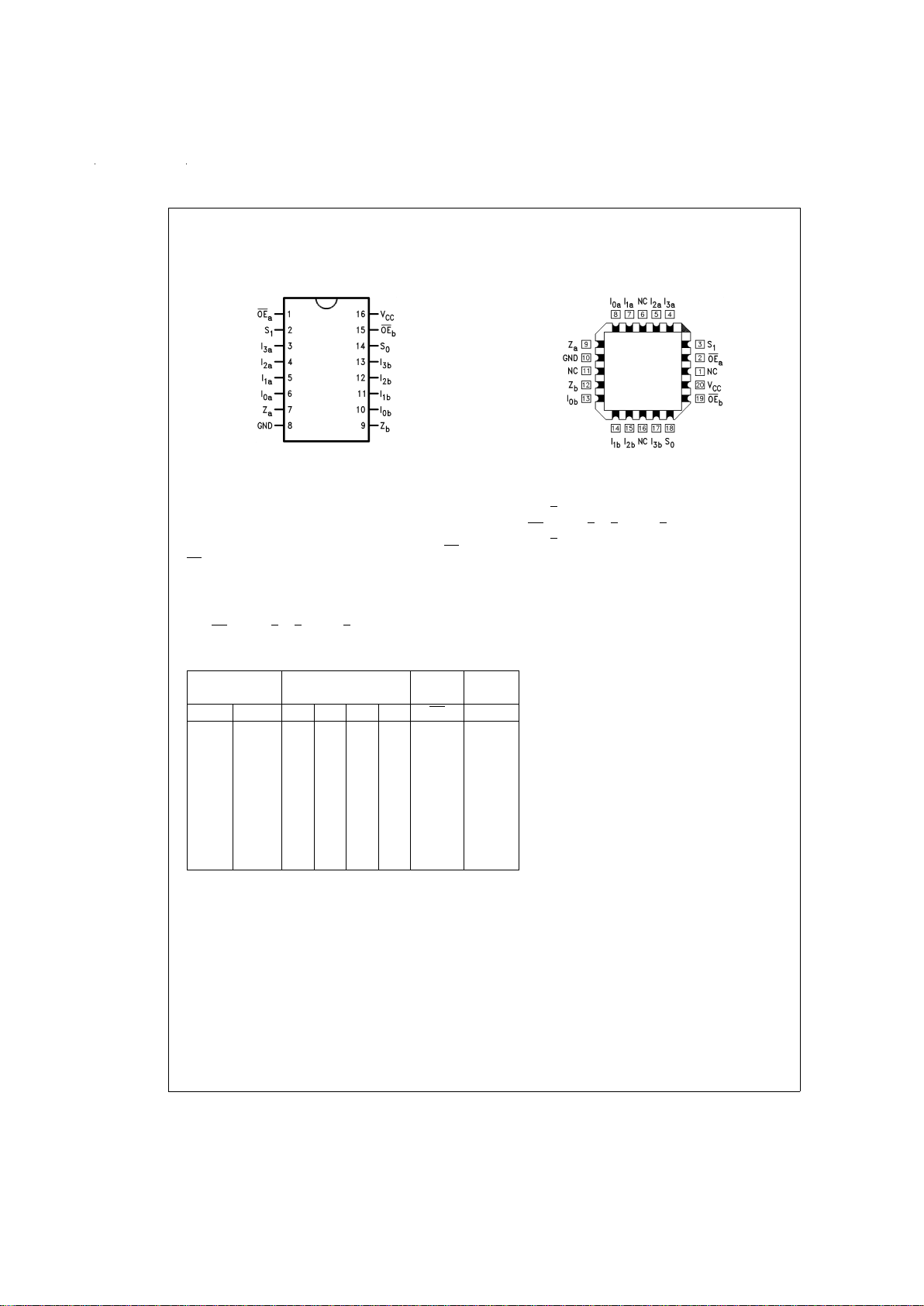

Connection Diagrams

Functional Description

The ’AC/’ACT253 contains two identical 4-input multiplexers

with TRI-STATE outputs. They select two bits from four

sources selected by common Select inputs (S

0,S1

). The

4-input multiplexers have individual Output Enable (OE

a

,

OEb) inputs which, when HIGH, force the outputs to a high

impedance (High Z) state. This device is the logic implementation of a 2-pole, 4-position switch, where the position of the

switch is determined by the logic levels supplied to the two

select inputs. The logic equations for the outputs are shown:

Z

a

=

OE

a

•

(I

0a

•

S

1

•

S0+I

1a

•

S

1

•

S0+

I

2a

•

S

1

•

S0+I

3a

•

S

1

•

S0)

Z

b

=

OE

b

•

(I

0b

•

S

1

•

S0+I

1b

•

S

1

•

S0+

I

2b

•

S

1

•

S0+I

3b

•

S

1

•

S0)

If the outputs of TRI-STATE devices are tied together, all but

one device must be in the high impedance state to avoid

high currents that would exceed the maximum ratings. Designers should ensure that Output Enable signals to

TRI-STATE devices whose outputs are tied together are designed so that there is no overlap.

Truth Table

Select Data Inputs Output Outputs

Inputs Enable

S

0

S

1

I0I1I2I

3

OE Z

X X XXXX H Z

L L LXXX L L

L L HXXX L H

H L XLXX L L

H L XHXX L H

L H XXLX L L

L H XXHX L H

H H XXXL L L

H H XXXH L H

Address Inputs S0and S1are common to both sections.

H=HIGH Voltage Level

L=LOW Voltage Level

X=Immaterial

Z=High Impedance

Pin Assignment

for DIP and Flatpak

DS100285-3

Pin Assignment

for LCC

DS100285-4

www.national.com 2

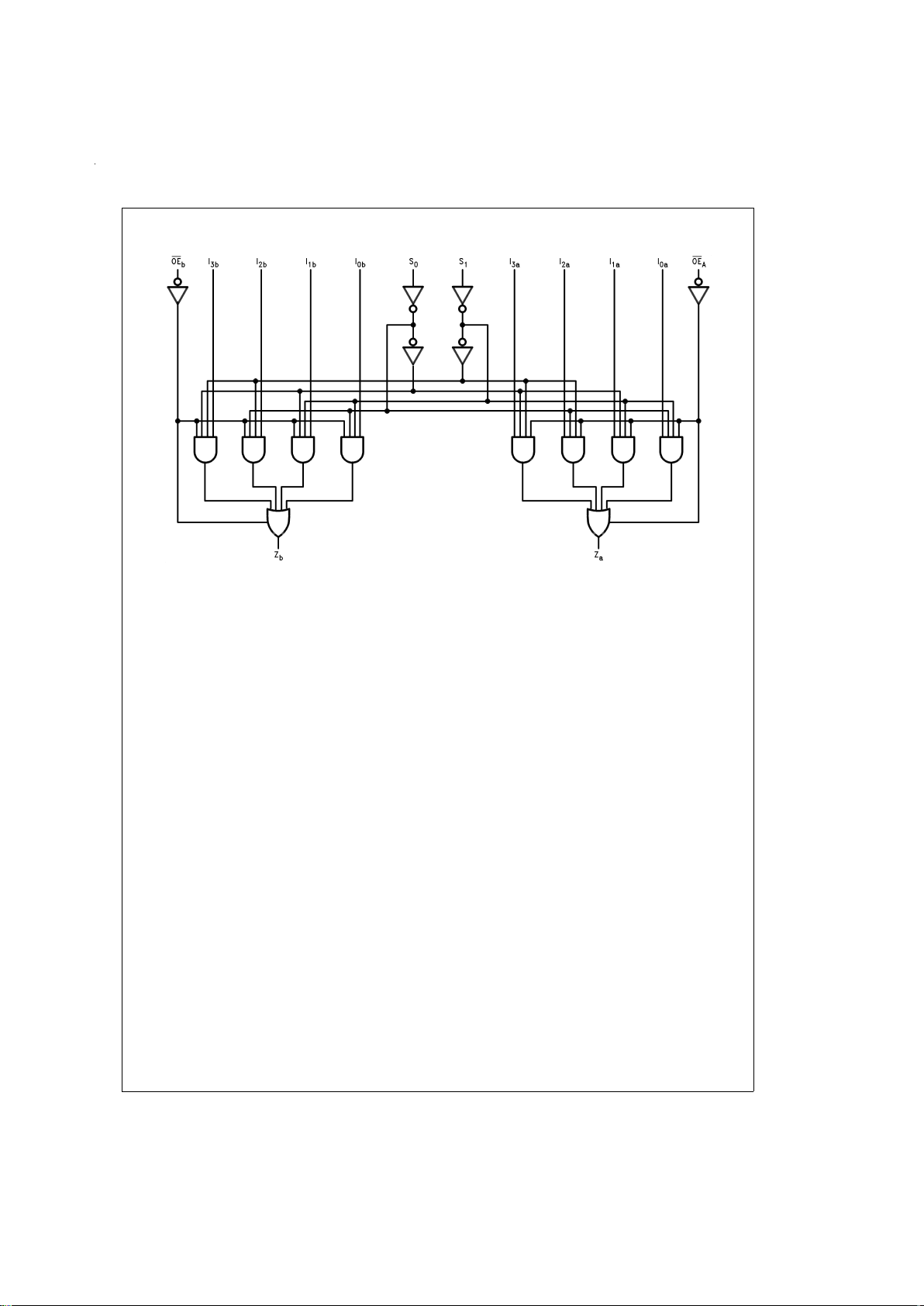

Logic Diagram

DS100285-5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.national.com3

Loading...

Loading...