Page 1

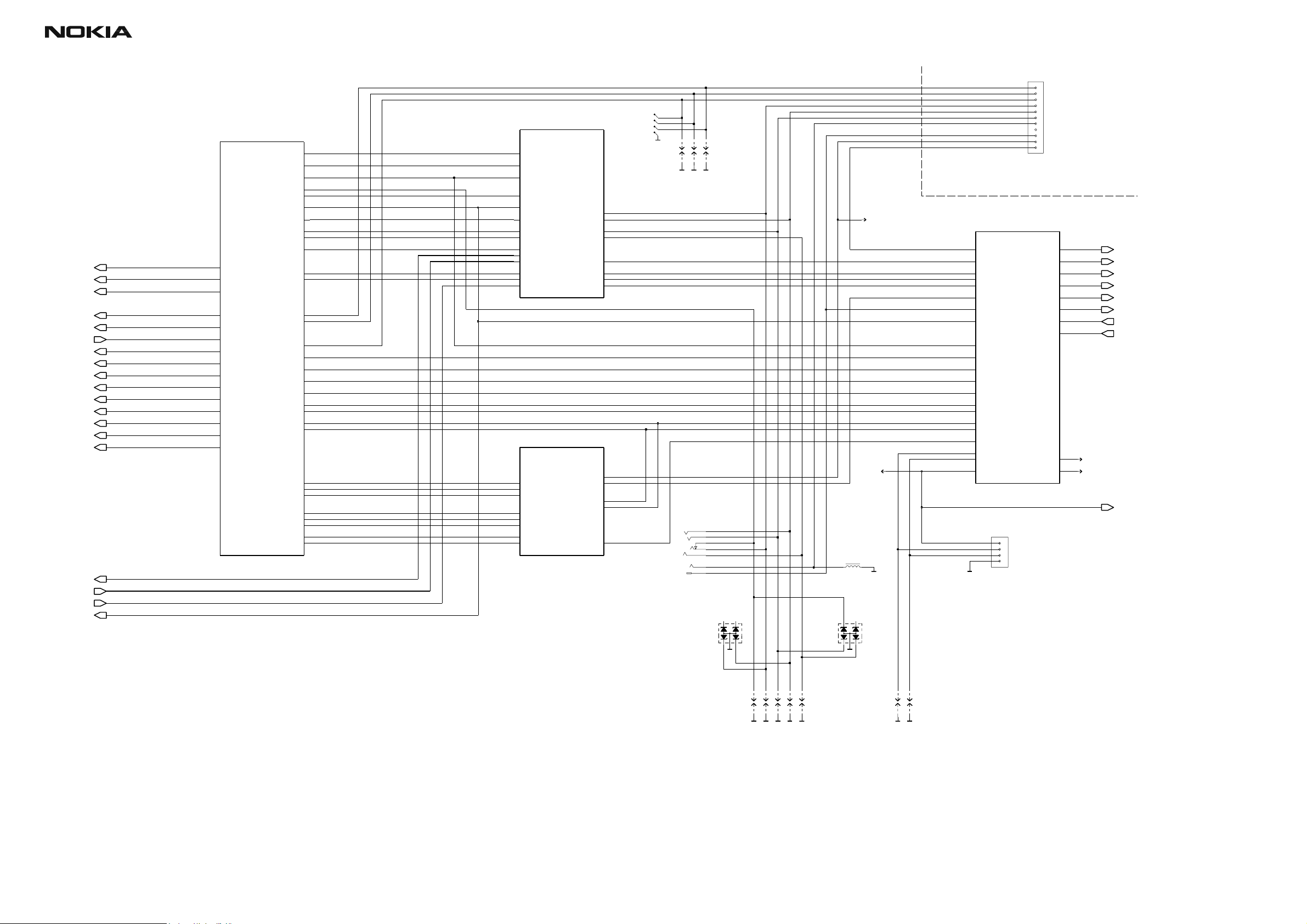

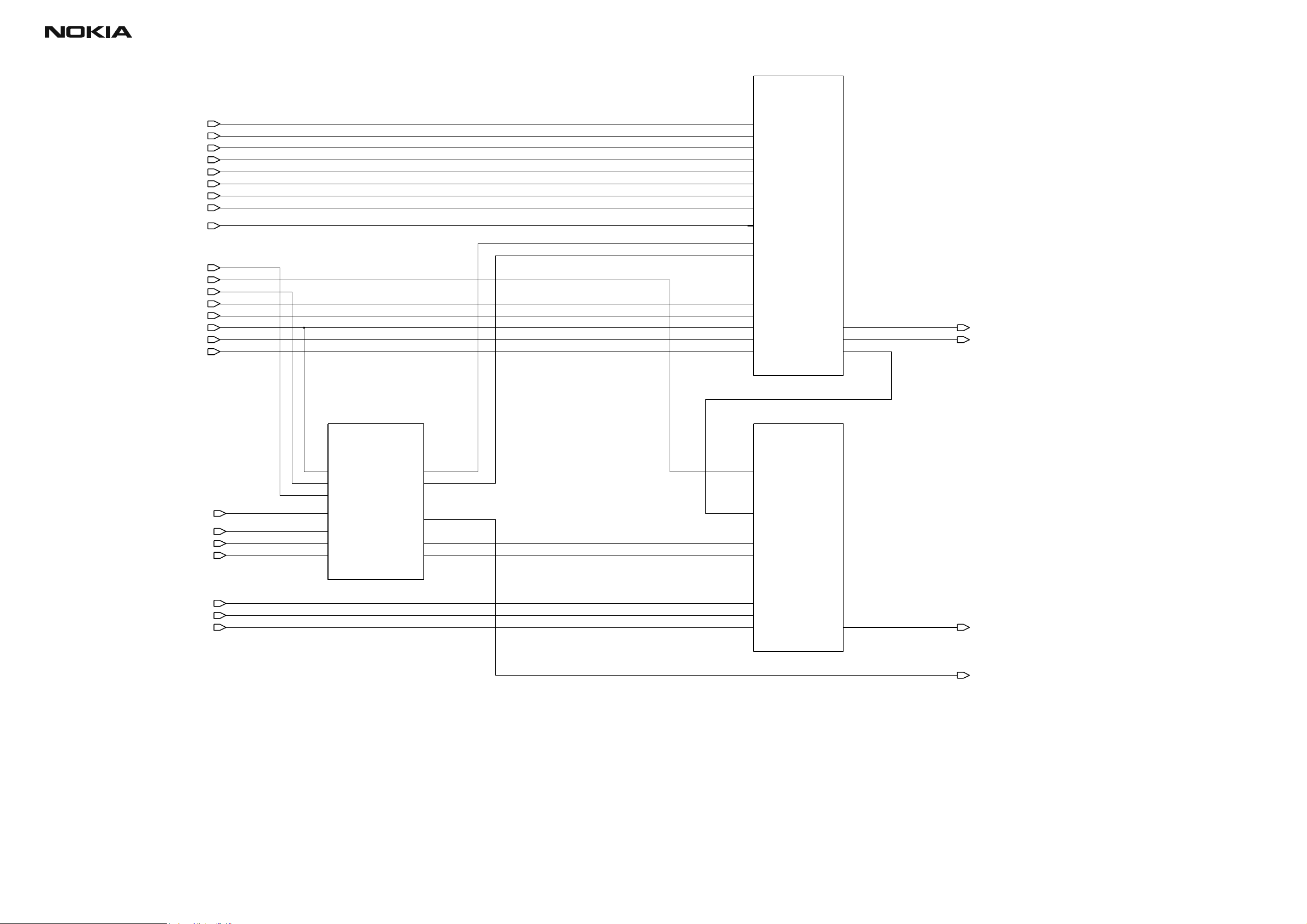

BB-RF Interface

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

BB RF_DCT3

VR1VR1

VR1

VR2

VR3

VR4

VR5

VR7 VR7

VR7

5V

BVOLT BVOLT

BVOLT

VR1

VR2VR2

VR2

VR3VR3

VR3

VR4VR4

VR4

VR5VR5

VR5

VR7

5V5V

5V

BVOLT

RXIQ(3:0)

TXIQ(3:0)

TIF_EN

RIF_EN

CAFE_TX_GATE

TX_LIM_ADJ

TX_IF_AGC

TX_RF_AGC

TX_LIM

RF_TX_GATE_P

RX_IF_AGC

RX_GS

FILT_SEL_P

FILT_SEL_N

AFC

SYN_CLK

SYN_LE1

SYN_DAT

CLK19M2RF

PA_TEMP

RXIQ(3:0)RXIQ(3:0)

TXIQ(3:0)TXIQ(3:0)

TIF_ENTIF_EN

RIF_ENRIF_EN

CAFE_TX_GATECAFE_TX_GATE

TX_LIM_ADJTX_LIM_ADJ

TX_IF_AGCTX_IF_AGC

TX_RF_AGCTX_RF_AGC

TX_LIMTX_LIM

RF_TX_GATE_PRF_TX_GATE_P

RX_GS RX_GS

FILT_SEL_P FILT_SEL_P

FILT_SEL_N FILT_SEL_N

RX_IF_AGCRX_IF_AGC

AFCAFC

SYN_CLKSYN_CLK

SYN_LE1SYN_LE1

SYN_DATSYN_DAT

CLK19M2RFCLK19M2RF

PA_TEMPPA_TEMP

RXIQ(3:0)

TXIQ(3:0)

TIF_EN

RIF_EN

CAFE_TX_GATE

TX_LIM_ADJ

TX_IF_AGC

TX_RF_AGC

TX_LIM

RF_TX_GATE_P

RX_IF_AGC

RX_GS

FILT_SEL_P

FILT_SEL_N

AFC

SYN_CLK

SYN_LE1

SYN_DAT

CLK19M2RF

PA_TEMP

Issue 1 05/02 Nokia Corporation Page A-1

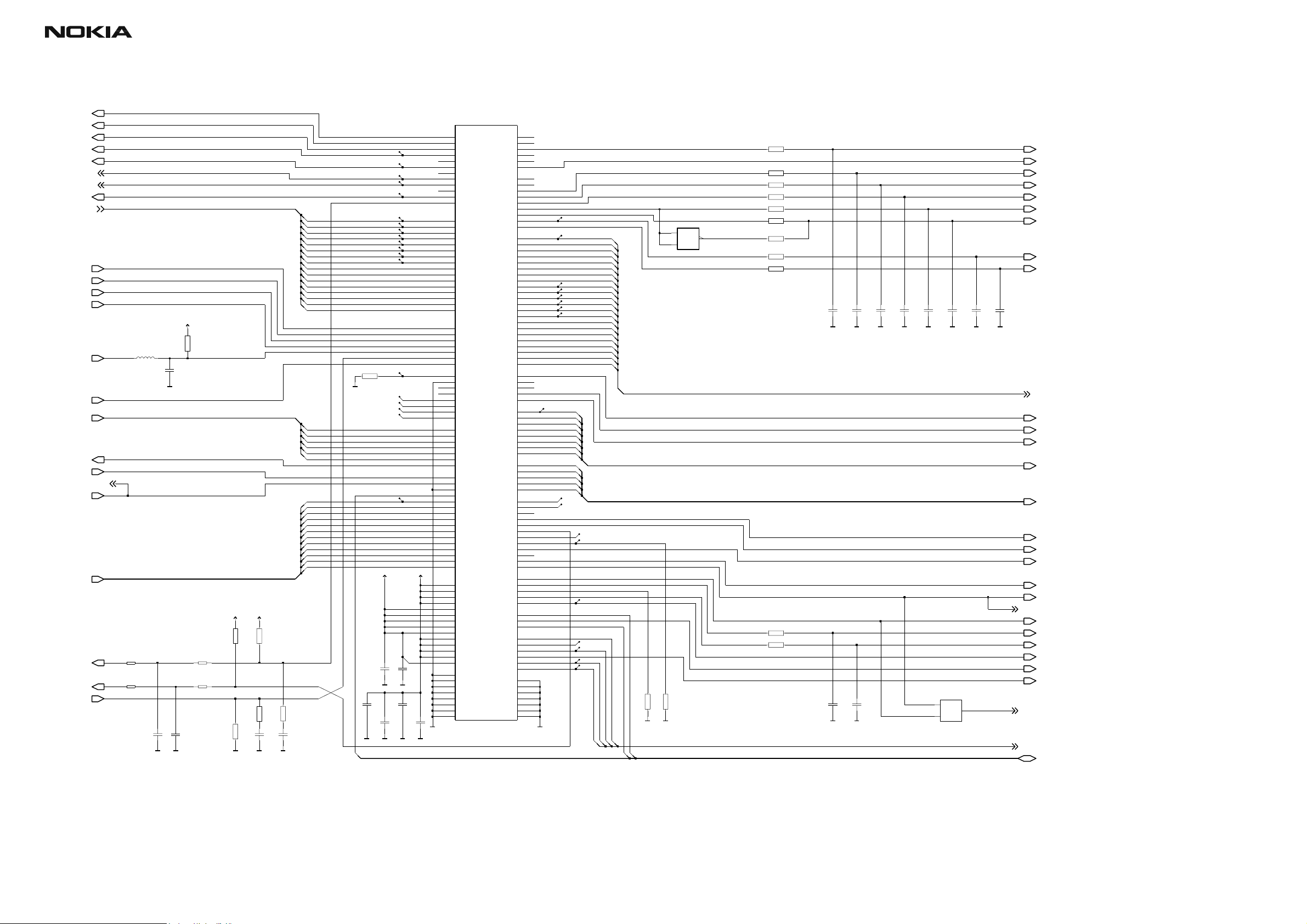

Page 2

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of Baseband

SYN_CLK

SYN_DAT

SYN_LE1

TX_RF_AGC

TX_IF_AGC

TX_LIM

TX_LIM_ADJ

RX_GS

RX_IF_AGC

FILT_SEL_P

FILT_SEL_N

RF_TX_GATE_P

AFC

TIF_EN

RIF_EN

TXIQ(3:0)

RXIQ(3:0)

CLK19M2RF

CAFE_TX_GATE

SYN_CLK

SYN_DAT

SYN_LE1

TX_RF_AGC

TX_IF_AGC

TX_LIM

TX_LIM_ADJ

RX_GS

RX_IF_AGC

FILT_SEL_P

FILT_SEL_N

RF_TX_GATE_P

TIF_EN

RIF_EN

AFC

SYN_CLK

SYN_DAT

SYN_LE1

TX_RF_AGC

TX_IF_AGC

TX_LIM

TX_LIM_ADJ

RX_GS

RX_IF_AGC

FILT_SEL_P

FILT_SEL_N

RF_TX_GATE_P

AFC

TIF_EN

RIF_EN

MAD4

HF_MUTE

RESETX

CLK_EN

EAD_HEADINT

HOOKINT

CAFE_TX_GATE

CAFESIO(2:0)

TXD(7:0)

RXD(11:0)

IQSEL

CLK19M2O

CLK9M83

FBUS_TX

FBUS_RX

MBUS

STOP_CH

SLEEPCLK

VLIM

PURX

CCONT_INT

CCONTCSX

UIF_CCONT_SCLK

UIF_CCONT_SDIO

LCD_CD

LCD_RESETX

LCD_CS

BACKLIGHT

BUZZER

VIBRA

COL(4:0)

ROW(5:0)

CLK_EN

EAD_HEADINT

FBUS_TX

FBUS_RX

MBUS

BUZZER

CAFE_TX_GATECAFE_TX_GATE

CAFESIO(2:0)CAFESIO(2:0)

CLK19M2RF

LCD_RESETXLCD_RESETX

HF_MUTEHF_MUTE

RESETXRESETX

CLK_EN

HOOKINTHOOKINT

TXD(7:0)TXD(7:0)

RXD(11:0)RXD(11:0)

TXIQ(3:0)

RXIQ(3:0)

CLK19M2OCLK19M2O

CLK9M83CLK9M83

LCD_CDLCD_CD

LCD_CSLCD_CS

BACKLIGHTBACKLIGHT

BUZZER

COL(4:0)COL(4:0)

ROW(5:0)ROW(5:0)

IQSELIQSEL

VIBRAVIBRA

CAFE

HF_MUTE

RESETX

CLK_EN

HOOKINT

CAFE_TX_GATE

CAFESIO(2:0)

TXD(7:0)

RXD(11:0)

IQSEL

TXIQ(3:0)

RXIQ(3:0)

CLK19M2O

CLK9M83

CLK19M2RF

LCD_CD

LCDRSTX

LCD_CS

BACKLIGHT

BUZZER

VIBRA

COL(4:0)

UI

VPP_FLASH

VPP_CCONT

UIF_CCONT_SDIO

UIF_CCONT_SCLK

PWRONXROW(5:0)

FBUS / MBUS CONNECTOR

MBUS

J55

FBUS_RX

J56

J57

FBUS_TX

J58

E061

E062

E060

XEAR

XEAR

SGND

SGND

XMICP

XMICP

XMICN

XMICN

EAD

EAD

VREF VREF

VREF

VR6 VR6

VR6

VR1_SW

VPP_FLASH

VPP_CCONT

UIF_CCONT_SDIO

UIF_CCONT_SCLK

X050

SGND

6

XMICP

PWRONX

7

EAD_HEADINT

9

XEAR

8

XMICN

5

L_GND

4

V_IN

2

VPP_FLASH

BVOLT

L050

33R/100MHz

SYSTEM CONNECTOR

V050

RSA6.1EN

V051

RSA6.1EN

WDDIS

WD_DIS

EAD

EAD

VREF

VR6

VR1_SWVR1_SW

CLK_EN

STOP_CHSTOP_CH

SLEEPCLKSLEEPCLK

PWRONX

BTEMP

V_IN

VLIMVLIM

PURXPURX

BVOLT

BSI

BVOLT

BTEMP

VR1_SW

VPP_CCONT

V_IN

CAFE_TX_GATE

CLK_EN

STOP_CH

SLEEPCLK

VLIM

PURX

CCONT_INT

CCONTCSX

UIF_CCONT_SCLK

UIF_CCONT_SDIO

PWRONX

BSI

BTEMP

BVOLT

BSI

VPP_CCONT

CAFE_TX_GATE

CCONT_INTCCONT_INT

CCONTCSXCCONTCSX

UIF_CCONT_SCLKUIF_CCONT_SCLK

UIF_CCONT_SDIOUIF_CCONT_SDIO

BATTERY CONNECTOR

X052

FBUS_TX

FBUS_RX

VPP_FLASH

MBUS

XEAR

SGND

XMICP

L_GND

V_IN

WDDIS

1

2

3

4

5

6

7

8

9

10

11

FBUS_TX

FBUS_RX

MBUS

XEAR

SGND

XMIC

L_GND

CHRG_CTRL

VIN

VPP

WDDIS

FLASH CONNECTOR

PARTS PLACED ON PANEL

VR1

VR2

VR3

VR4

VR5

CCONT

X051

VBATT

BSI

BTEMP

GND

VR7

5V

PA_TEMP

VMAD

VBB

VR1

VR2

VR3

VR4

VR5

VR7

5V

PA_TEMP

VMAD

VBB

VR1

VR2

VR3

VR4

VR5

VR7

5V

PA_TEMP

VMAD

VBB

BVOLT

E050

E051

E052

E053

E056

E057

E054

Issue 1 05/02 Nokia Corporation Page A-2

Page 3

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of MAD4

LCD_RESETX

HF_MUTE

BACKLIGHT

LCD_CS

STOP_CH

EEPROMSDA

EEPROMSCLK

LCD_CD

DATA(15:0)

SLEEPCLK

CCONT_INT

PURX

HOOKINT

EAD_HEADINT

TX_LIM

ROW(5:0)

UIF_CCONT_SDIO

CLK9M83

CLK19M2O

RXD(11:0)

MBUS

FBUS_TX

FBUS_RX

CLK19M2O

BLM11A601SPT

R123 1

Z100

/2 47R

/2 47R1R122

C123

D100

MAD4_V14_F741718B

LCD_RESETX

BACKLIGHT

TP100

TP101

TP102

EEPROMSDA

EEPROMSCLK

TP103

TP105

DATA(0)

DATA(1)

DATA(2)

DATA(3)

DATA(4)

DATA(5)

DATA(6)

DATA(7)

DATA(8)

DATA(9)

DATA(10)

DATA(11)

DATA(12)

DATA(13)

DATA(14)

DATA(15)

VBB

R100

220k

C100

12p

ROW(0)

ROW(1)

ROW(2)

ROW(3)

ROW(4)

ROW(5)

RXD(0)

RXD(1)

RXD(2)

RXD(3)

RXD(4)

RXD(5)

RXD(6)

RXD(7)

RXD(8)

RXD(9)

RXD(10)

RXD(11)

VBB

VBB

R125

R124

4k7

47k

2R123

/2 47R

2/2 47R

R122

R120

100R

C122

12p

12p

R126

220k

C120

150p

FBUS_TX’

FBUS_RX

R127

C121

R101

10k

C154

C150

33n

C151

33n

33n

TP106

O01

O02

O03

O04

O05

O06

O07

EAD_HEADINT’

TP110

TP111

TP112

TP113

TP114

UIF_CCONT_SDIO

TP115

VBB

C153

33n

CCONT_INT

CLK19M2O

CAFESIO(1)

C152

33n

A2

T10

P10

U11

T11

R11

P11

U12

T12

U13

T13

R13

U14

T14

U15

T15

U16

H15

E15

C16

N16

N17

M15

M16

A14

C13

B10

H14

N15

D10

R12

G14

M17

C17

F15

M3

M1

M2

L14

L15

J16

L17

J17

B3

A3

C4

N1

J3

A4

C5

B5

A5

H3

R2

G3

G2

H1

J1

K2

K3

L1

L3

L4

P2

R1

A9

D9

C9

A8

B8

D8

C8

A7

B7

C7

A6

B1

L2

P1

H4

P9

G1

D7

U5

K1

R4

P3

U7

mdP0GPIO0

mdP0GPIO1

mdP0GPIO2

mdP0GPIO3

mdP0GPIO4

mdP0GPIO5

mdP0GPIO7

mdP2GPIO0

mdP2GPIO1

mdP2GPIO2

mdP2GPIO3

mdMCUSDIO

mdMemDa0

mdMemDa1

mdMemDa2

mdMemDa3

mdMemDa4

mdMemDa5

mdMemDa6

mdMemDa7

mdMemDa8

mdMemDa9

mdMemDa10

mdMemDa11

mdMemDa12

mdMemDa13

mdMemDa14

mdMemDa15

ccSleepClk

ccInt

ccPURX

acHookInt

acHeadInt

acAccRxData

rfTXLim

teqDSPSerClk

tmTstMode

emEMU0

emEMU1

emJTDI

emJTSClk

emJTRstX

emJTMS

mdP1UIF0

mdP1UIF1

mdP1UIF2

mdP1UIF3

mdP1UIF4

mdP1UIF5

mdUIFSDIO

cfCDMAClk

cfSysClk

cfAData

cf2MDSerD

cfRXD0

cfRXD1

cfRXD2

cfRXD3

cfRXD4

cfRXD5

cfRXD6

cfRXD7

cfRXD8

cfRXD9

cfRXD10

cfRXD11

LEADVCC

LEADVCC

LEADVCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

ARMVCC

LEADGND

LEADGND

LEADGND

ARMGND

GND

GND

GND

GND

HF_MUTE

LCD_CS

STOP_CH

LCD_CD

MBUS’ FILT_SEL_N’

SLEEPCLK

PURX

HOOKINT

FBUS_RX

TX_LIM

SER_CLK

JTAG(1)

JTAG(2)

JTAG(3)

JTAG(4)

CLK9M83

VMAD

C155

33n

mdP1GPO0

mdP1GPO1

mdP1GPO2

mdP1GPO3

mdP1GPO4

mdP1GPO6

mdGPPDM0

mdGPPDM1

mdGPPDM2

mdGPPDM3

mdGPPDM4

mdTXIFAGC

mdTXRFAGC

mdRFTXPGate

mdMemAd0

mdMemAd1

mdMemAd2

mdMemAd3

mdMemAd4

mdMemAd5

mdMemAd6

mdMemAd7

mdMemAd8

mdMemAd9

mdMemAd10

mdMemAd11

mdMemAd12

mdMemAd13

mdMemAd14

mdMemAd15

mdMemAd16

mdMemAd17

mdMemAd18

mdMemAd19

mdMemAd20

mdMemAd21

mdRFTXCGate

mdRFSLE2

mdRFSLE1

mdRFSData

mdModeSel

mdBandSel

mdLoByteSelX

mdVibraPWM

mdBuzzPWM

mdAccTxData

mdDSPSerFSync

mdCContCSX

mdVCTCXOEn

mdRXIFAGC

md2CFSerD

mdCAFETXGate

mdCAFEFSync

mdROM1SelX

mdROM2SelX

mdRAMSelX

mdEEPROMSelX

mdMemWrX

mdMemRdX

mdRXGS

mdRFSClk

mdTXD0

mdTXD1

mdTXD2

mdTXD3

mdTXD4

mdTXD5

mdTXD6

mdTXD7

mdP0UIF0

mdP0UIF1

mdP0UIF2

mdP0UIF3

mdP0UIF4

mdJTDO

mdLCDCS

mdUIFSClk

mdResetX

mdDSPXF

mdAFC

mdIQSel

GND

GND

GND

GND

GND

GND

GND

E3

D1

RIF_EN’

D2

D3

C1

TIF_EN

J4

G16

D17

TX_LIM_ADJ’

D16

FILT_SEL_P’

D15

B15

TX_IF_AGC’

A15

TX_RF_AGC’

C14

B14

RX_GS’

C2

U10

T9

R9

U9

T8

R8

P8

U8

T7

R7

P7

U6

T6

R6

T5

R5

U4

T4

U3

T3

U2

T1

SYN_CLK

E16

G15

F17

SYN_LE1

F16

SYN_DAT

E17

B12

A12

D11

C11

B11

A11

A10

C10

L16

K17

K14

K15

K16

XIECD

E2

XIECLOCK

E1

F2

VIBRA

F1

BUZZER

G4

FBUS_TX’

H2

DSP_SER_FSNC

J2

JTAG(0)

K4

CCONTCSX

J14

J15

UIF_CCONT_SCLK

H17

RESETX

H16

CLK_EN

G17

RX_IF_AGC’

A16

N3

B17

IQSEL

C6

CAFESIO(0)

B13

CAFE_TX_GATE

B6

CAFESIO(2)

C12

MEM(0)

T17

R16

MEM(1)

R17

VLIM

P15

MEM(2)

P16

MEM(3)

P17

F3

N2

R10

R14

A13

B9

B4

TP132

J130

TP131

O08

O09

O10

O11

O12

O13

TXD(0)

TXD(1)

TXD(2)

TXD(3)

TXD(4)

TXD(5)

TXD(6)

TXD(7)

COL(0)

COL(1)

COL(2)

COL(3)

COL(4)

TP133

TP134

TP140

TP141

TP143

TP144

TP145

TP146

TP147

ADD(0)

ADD(1)

ADD(2)

ADD(3)

ADD(4)

ADD(5)

ADD(6)

ADD(7)

ADD(8)

ADD(9)

ADD(10)

ADD(11)

ADD(12)

ADD(13)

ADD(14)

ADD(15)

ADD(16)

ADD(17)

ADD(18)

ADD(19)

ADD(20)

ADD(21)

MEM(3)

MEM(2)

MEM(1)

MEM(0)

R143

10k

CAFESIO(0)

CAFESIO(2)

R142

R131

100R

R134 10k

2k2R144

R145 2k2

2k2R135

D130

2

1

10k

TC7S00F

4

&

5= VBB3= GND

R136 2k2

R133

R146 1k0

R140

R141

560RR137

10R

C134

C141

C144

10n

10n 10n

1n0

C131

10n

18k

47k

C140

10n

C145

C135

10n

C136

10n

D140

TC7SL08FU

1

2

C138

C146

10n

100p

&

4

VBB5=

GND3=

RIF_EN

TIF_EN

TX_LIM_ADJ

FILT_SEL_P

FILT_SEL_N

TX_IF_AGC

TX_RF_AGC

RF_TX_GATE_P

RX_GS

ADD(21:0)

SYN_CLK

SYN_LE1

SYN_DAT

TXD(7:0)

COL(4:0)

VIBRA

BUZZER

CCONTCSX

UIF_CCONT_SCLK

RESETX

RESETX

CLK_EN

RX_IF_AGC

AFC

IQSEL

CAFE_TX_GATE

VLIM

RPX

MEM(3:0)

CAFESIO(2:0)

Issue 1 05/02 Nokia Corporation Page A-3

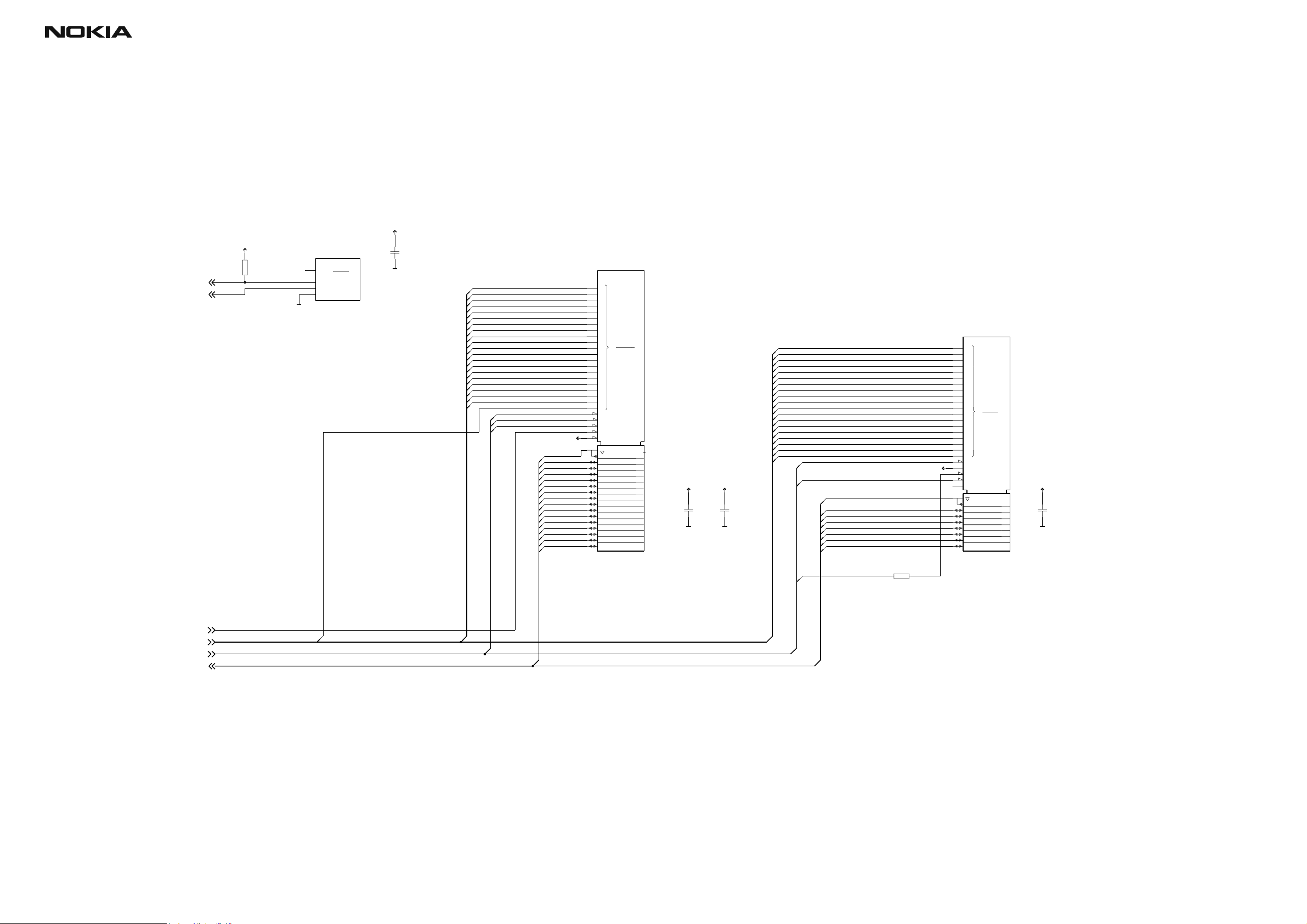

Page 4

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of Memory

EEPROMSDA

EEPROMSCLK

R162

VBB

VBB

10k

D180

AT24C1024C1-10C1-2.7

EEPROM 128Kx8

2

0

A1

131071

5

SDA

6

SCL

7

WP

GND4= VBB8=

C180

33n

ADD(1)

ADD(2)

ADD(3)

ADD(4)

ADD(5)

ADD(6)

ADD(7)

ADD(8)

ADD(9)

ADD(10)

ADD(11)

ADD(12)

ADD(13)

ADD(14)

ADD(15)

ADD(16)

ADD(17)

ADD(18)

ADD(19)

ADD(20)

MEM(0)

MEM(3)

MEM(2)

VBB

DATA(0)

DATA(1)

DATA(2)

DATA(3)

DATA(4)

DATA(5)

DATA(6)

DATA(7)

DATA(8)

DATA(9)

DATA(10)

DATA(11)

DATA(12)

DATA(13)

DATA(14)

DATA(15)

M28W320BT100ZB6T

D8

0

C8

B8

C7

A8

B7

C6

A7

A3

C3

B2

A2

C2

A1

B1

C1

D1

B6

B5

A6

C5

20

D7

_E

F8

_G

B3

_W

B4

_RP

A5

_WP

E7

F7

D5

E5

F4

D3

E3

F2

D6

E6

F6

D4

E4

F3

D2

E2

D160

FLASHM 2Mx16

0

A

2097151

DATA IXO

F5= VBB

A4= VPP_FLASH

E1=

VBB

E8,F1= GND

C160

D170

K6F4008U2E-EF70

ADD(0)

ADD(1)

ADD(2)

ADD(3)

ADD(4)

ADD(5)

ADD(6)

ADD(7)

ADD(8)

ADD(9)

ADD(10)

ADD(11)

ADD(12)

ADD(13)

ADD(14)

ADD(15)

ADD(16)

ADD(17)

ADD(18)

MEM(1)

VPP_FLASH

C161

33n

33n

MEM(3)

MEM(2)

DATA(0)

DATA(1)

DATA(2)

DATA(3)

DATA(4)

DATA(5)

DATA(6)

DATA(7)

R175

0R

VBB

SRAM 512Kx8

A1

0

A2

B2

A4

B4

C4

A5

B5

A6

H1

H2

H3

H4

H5

H6

G5

G4

F4

F3

G3

A3

B3

G2

C3

B6

C6

F6

G6

B1

C1

F1

G1

18

_CS1

CS2

_WE

_OE

DNU

A

524287

DATA I/O

0

VBBVBB

C170

100n

VBBE1,D6=

GNDD1,E6=

RPX

ADD(21:0)

MEM(3:0)

DATA(15:0)

ADD(21)

Issue 1 05/02 Nokia Corporation Page A-4

Page 5

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of CCONT

VBB

R333

1M0

CLK_EN

CAFE_TX_GATE

R332

100k

BSI

BTEMP

PA_TEMP

EAD

CCONTCSX

UIF_CCONT_SDIO

UIF_CCONT_SCLK

R331

100k

F300

1.5A

R330

10k

L300

33R/100MHz

L302

33R/100MHz

L301

33R/100MHz

R301

30V/0.1J

PWRONX

BVOLT

V_IN

STOP_CH

VLIM

TP331

TP330

TP301

C331

22p

R735

R334

47k

R338

10k

C332

22p

R302

10R

C300

33n

V300

PDTC114EE

2x10k

R1

VBAT

BC858W

V310

R316

4k7

CHAPS_U423V2G36T

A2

VCH

A3

VCH

A4

VCH

A5

VCH

F2

PWM

F3

CTIM

F4

LIM

B2

GND

B3

GND

B4

GND

B5

GND

C2

GND

C3

GND

E2

GND

E3

GND

A1

NC

A6

NC

B1

NC

B6

NC

R337

1M0

C316

10n

RSENSE

RSENSE

VBAT

VBAT

VBACK

N301

GND

GND

GND

GND

GND

GND

GND

GND

VBAT

CLK_EN

PA_TEMP

CCONTCSX

UIF_CCONT_SDIO

UIF_CCONT_SCLK

WD_DIS

C321

33p

R321

150k

C312

100n

R322

68k

VBAT

R323

18R

C325 1u0

C311

10u

R320

2M2

B320

32.768kHz

C320

12p

C310

R310

0R22

R311

100R

1u0

C1

D1

C6

D6

F5

C4

C5

D2

D3

D4

D5

E4

E5

E1

NC

E6

NC

F1

NC

F6

NC

CRA

CRB

EAD

VBB

C330

10u

G4

D1

C2

H1

C3

H2

D2

B1

A3

B3

C4

D5

A1

A2

C1

G6

C8

E7

D8

F6

A7

A6

A8

E4

E5

C7

D6

F1

G1

G3

G5

A4

H6

B6

N302

CCONT2M_WFD163ME64T_8

SLEEPX

CNTVR2

CNTVR3

CNTVR4

CNTVR5

TXPWR

VBAT

ICHAR

VCHAR

BSI

BTEMP

VCXOTEMP

RSSI

EAD

MODE_SEL

SIM_PWR

DATA_A

SIMRST_A

SIMCLK

SIM I/O_C

DATASELX

DATA_IN/OUT

DATA_CLK

PWRONX/WDDISX

VBACK

CRA

CRB

VBAT

VBAT

VBAT

VBAT

VBAT1

VBAT2

TEST

VR1_SW

VR3/RAM_BCK

VREF

VR7BASE

V5V_2

V5V_3

V5V_4

VSIM

DATA_O

SIMRST_O

SIMCLK_O

PURX

PWM_OUT

CCONTINT

SLCLK

GND

GND

GND

GND

GND

GND

C324

1p8

VR1

VR2

VR4

VR5

VR6

VBB

VR7

V2V

V5V

H5

F4

E1

B2

E3

E2

H4

C6

D4

H3

G2

B4

H7

H8

F8

G8

G7

D7

E6

E8

A5

B5

B7

B8

D3

F2

F3

F5

F7

C5

VR1

VR1_SW

VR2

VR3

VR4

VR5

VR6

VBB

VREF

VMAD

5V

V5V_2

V5V_3

V5V_4

PURX

CCONT_INT

SLEEPCLK

D301

TC7SL08FU

4

5=VBB

3=GND

TP380

TP381

TP382

TP390

R736

0R

&

C375

1u0

1

2

10k

1u0

C380

1u0

C370

2u2

C352C351

1u0

V370

STPS0520Z

C353

C354

C355

1u0

1u01u0

C371

2u2

1u0

C372

2u2

R733

C350

C373

2u2

C356

C374

2u2

C357

C358

1u01u0

1u0

C360C359

1u0

1u0

R335

100k

TP334

TP333

TP332

R2

R339

10k

C301

33n

C315

1u0

R336

47k

R315

47k

VR7

VR1

VR1_SW

VR2

VR3

VR4

VR5

VR6

VBB

VREF

VMAD

5V

VPP_CCONT

PURX

CCONT_INTWD_DIS

SLEEPCLK

Issue 1 05/02 Nokia Corporation Page A-5

Page 6

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of CAFE

HF_MUTE

VR1_SW

VREF

RXIQ(3:0)

CLK19M2RF

TXIQ(3:0)

R272

1k0

R242

82K

C244

12p

C252

12p

V290

RSA6.1EN

R243

68k

VBB

C241

33n

BLM11A601SPT

C245

12p

BLM11A601SPT

C253

12p

C264

12p

R732

100k

R273

22k

Z240

Z250

N270

LMV321M7X

3

-

1

+

5= VBB 2= GND

R274

680k

E280

E290

4

E281

E291

R245

47k

VBB

J281

J280

R275

100k

EARP’

EARN’

MICP

MICN

2

1

EAD

XEAR

C246

1n0

SGND

C247

1n0

XMICP

C248

1n0

XMICN

C249

1n0

HOOKINT

Microphone

Speaker

B290

CAFESIO(2:0)

RXD(11:0)

TXD(7:0)

RESETX

IQSEL

CAFE_TX_GATE

CLK9M83

CLK19M2O

CLK_EN

R292

47R

C240

1u0

C242

10U

C243

100p

V281

PDTC114EE

2x10k

R1

R2

V280

BC848W

VR6

R205

10k

C210

C211

VDIG

3u3

C234

100n

R202

22k

C216

C212

3u3

R203

47k

C217

470p

6n8

C219

1n0

RXIQ(0)

RXIQ(1)

C202

C201

33n

33n

C205

C206

33n

33n

TXIQ(2)

TXIQ(3)

VR6

C230

12p

C231

3u3

RXIQ(2)

C203

33n

C207

33n

TXIQ(0)

RXIQ(3)

C204

33n

C208

33n

TXIQ(1)

VR6

C232

100n

C213

470n

L230

33R/100MHz

C214

470n

C233

100n

3u3

C215

470n

R201

100k

R200

3k3

C218

100p

C220

1n0

TP207

TP206

CLK19M2RF

VDIG

VR6

K6

L6

K10

D10

D9

C11

L8

J7

K8

J8

K1

J2

H9

J9

J11

H11

H10

L10

L11

K9

L9

L1

K4

L3

L4

B1

G2

H3

J3

K5

J6

K7

K11

G9

G11

A10

A8

J4

K2

H7

L7

B2

G1

J1

K3

J5

L5

H8

J10

G10

G8

C9

B8

D7

E7

F7

G7

F8

E8

D8

C10

A11

D200

WFA157DG120T_CAFE_D

AUXOUT

TEST1

ADCTEST

TEST2

DACTEST

VREF

VAREF

VSUB_C

AGND

IFILIP

IFILIN

QFILIP

QFILIN

IF2AP

IF2AN

AMPSTX

TXIP

TXIN

TXQP

TXQN

ROUT1

VFILREF

VRXTUNE1

VRXTUNE2

CLK19M2I

RBIAS

CHARGEP

VCOIN

VDDD1

VDDD2

VDDD3

VDDA1

VDDA2

VDDA3

VDDA4

VDDA5

VDDA6

VDDA7

VDDA8

VDDA9

VSUB

BIST_TEST

OFFQ

OFFI

VSSD1A1TXGATE

VSSD2

VSSD3

VSSA1

VSSA2

VSSA3

VSSA4

VSSA5

VSSA6

VSSA7

VSSA8

VSSA9

GND

GND

GND

GND

GND

GND

GND

GND

GND

HFCM

MIC1N

MIC1P

MIC3N

MIC3P

MICBIAS

MIC2P

MIC2N

EARP

EARN

SYNC

SDO

XRESET

RXD0

RXD1

RXD2

RXD3

RXD4

RXD5

RXD6

RXD7

RXD8

RXD9

RXD10

RXD11

ADATA

IQSEL

TXD0

TXD1

TXD2

TXD3

TXD4

TXD5

TXD6

TXD7

CLK9M8

CLK19M2O

ENA19M2CLK

FUSETEST

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

B11

TP208

C7

TP209

B7

B9

HF

C8

E11

F11

E9

F9

D11

MICP’

F10

MICN’

E10

EARP

A9

EARN

B10

A6

TP201

TP202

C6

SDI

TP203

B6

RESETX

A7

C3

C1

C2

D3

D2

D1

E2

E3

E1

F3

F2

F1

H2

IQSEL

A5

B5

C5

A4

D4

B4

C4

A3

B3

CAFE_TX_GATE

CLK9M83

H1

CLK19M2O

G3

CLK_EN

L2

A2

E4

F4

G4

H4

H5

G5

F5

E5

D5

D6

E6

G6

H6

RXD(10)

RXD(11)

TP204

TP205

RXD(0)

RXD(1)

RXD(2)

RXD(3)

RXD(4)

RXD(5)

RXD(6)

RXD(7)

RXD(8)

RXD(9)

TXD(0)

TXD(1)

TXD(2)

TXD(3)

TXD(4)

TXD(5)

TXD(6)

TXD(7)

CAFESIO(2)

CAFESIO(0)

CAFESIO(1)

R280

100k

C265

1u0

R281

RXD(11:0)

TXD(7:0)

C280

12p

C290

12p

R283

470R

R284

470R

C281

12p

C282

12p

C263

12p

C283

100n

C284

100n

R260

470R

R270

470R

R290

27R

R291

27R

C250

10U

C285

12p

C251

100p

C261

12p

C271

12p

C255

3u3

C286

12p

C260

100n

C270

100n

R285

470R

R286

470R

R250

100R

C262

12p

C272

12p

C291

12p

R241

1k0

R244

47R

R251

47R

R261

470R

R271

470R

R282

1k8

R287

1k8

C292

12p

Issue 1 05/02 Nokia Corporation Page A-6

Page 7

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of UI Module

VIBRA

BACKLIGHT

BUZZER

LCDRSTX

LCD_CS

LCD_CD

UIF_CCONT_SDIO

UIF_CCONT_SCLK

R424

VBB

VBB

C430

100n

VBAT

C460

1u0

TM23A

1

VBAT

2

ENABLE

3

BUZZ_CNT

6

BUZZER

7

LCDLED

_CNT

8

LCDLED

_ADJ

9

LCD_LED

4

GND

5

GND

10 11

GND

XCS

XRES

C431

100n

N420

VIBRA_CNT

VIBRA

KBDLED

KBDLED

KBD_LED

L1F01239P00

SI

A0

VSS

TEST

_CNT

_ADJ

GND

GND

GND

GND

H430

LCD 96X60

SCL

VDDI

C432

1u0

VDD

BVOLT

R410

10R

V410

STPS0520Z

R411

10R

R425

10R

20

19

16

15

14

13

18

17

12

VOUT

CAP2+

CAP2-

1u0

C433

CAP1-

CAP1+

CAP3+

R421

15k

1u0

C434

1u0

C435

A410

PCB

UX7V

3

NC

4

NC

1

sig

2

sig

VIBRA

BVOLT

B400

V425

CL-191B1-X-T

N431

MC78PC18NTR

GND

+

-

CE

BUZZER

BVOLT

V420

CL-191B1-X-T

10k

V421

CL-191B1-X-T

LCD ILLUMINATION

V422

CL-191B1-X-T

V423

CL-191B1-X-T

VBB

V424

CL-191B1-X-T

VIN VOUT

NC

V400

1SS355

R420

15k

R430

10k

PWRONX

ROW(5:0)

COL(4:0)

VPP_FLASH

VPP_CCONT

C440

100p

ROW(4)

R440

1k0

C441

ROW(3)

R441

1k0

C442

100p

COL(2)

R442

1k0

C443

100p

COL(1)

ROW(2)

R443

1k0

100p

ROW(0)

ROW(1)

R445

R444

1k0 1k0

C445

100p100p

R446

1k0

1k0

C447

C446

100p

100p

COL(3)

R447

1k0

C448

100p

COL(4)

VOLUME

UP/DOWN

VOL_UP

GND

POWER

ON/OFF

3

COL(0)

R449R448

1k0

COL1 COL1

ROW0 ROW0

ROW1

COL3

COL4

COL0

C449C444

100p

V450

1SS355

C450

12p

S450

4

VOL_DOWN

S451

12pC471

C472 12p

C473 12p

R426

1

VPP_FLASH

2

3

VPP_CCONT

4

ROW4ROW4

5

ROW3ROW3

6

COL2COL2

7

ROW2ROW2

8

9

10

V_LED

11

ROW1

12

COL3

13

COL4

14

COL0

X460

KEYPAD PCB CONNECTOR

VBAT

Issue 1 05/02 Nokia Corporation Page A-7

Page 8

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of RF

TX

FILT_SEL_P

FILT_SEL_N

RF_TX_GATE_P

TX_IF_AGC

TX_LIM_ADJ

TX_RF_AGC

TIF_EN

CAFE_TX_GATE

TXIQ(3:0)

VR4

VR5

BVOLT

FILT_SEL_P

FILT_SEL_N

RF_TX_GATE_P

TX_IF_AGC

TX_LIM_ADJ

TX_RF_AGC

CAFE_TX_GATE

VR1

VR2

VR3

VR7

5V

TIF_EN

TXIQ(3:0)

LO_TIF

LO_PTX

VR4

VR5

VR7

BVOLT

5V

FILT_SEL_P

FILT_SEL_N

RF_TX_GATE_P

TX_IF_AGC

TX_LIM_ADJ

TX_RF_AGC

TIF_EN

CAFE_TX_GATE

TXIQ(3:0)

LO_TIF

LO_PTX

VR4

VR5

VR7

5V

BVOLT

TX_LIM

PA_TEMP

PCS_TX

TX_LIM

PA_TEMP

PCS_TX

TX_LIM

PA_TEMP

AFC

SYN_LE1

SYN_DAT

SYN_CLK

RX_IF_AGC

RX_GS

RIF_EN

VR7

VR3

VR1

AFC

SYN_LE1

SYN_DAT

SYN_CLK

VR7

VR3

VR1

AFC

SYN_LE1

SYN_DAT

SYN_CLK

LO_TIF

LO_PTX

CLK19M2RF

LO_RIF

LO_PRX

LO_TIF

LO_PTX

CLK19M2RF

LO_RIF

LO_PRX

VR2

PCS_TX

LO_RIF

LO_PRX

RX_IF_AGC

RX_GS

RIF_EN

RXSYNTH

VR2

PCS_TX

LO_RIF

LO_PRX

RX_IF_AGC

RX_GS

RIF_EN RXIQ(3:0)

RXIQ(3:0)

RXIQ(3:0)

CLK19M2RF

Issue 1 05/02 Nokia Corporation Page A-8

Page 9

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

X

Circuit Diagram of RX

PCS_TX

Antenna 50 ohms

X701

L711

C701

2p2

L704

5n6H

TX RX

Z701

DUPLEX

FILTER

X702

2

1

ANT

L703

6n2H

R701

VRX

C709

100n

4R3

RX_GS

LO_PRX

R702

47k

L701

4n7H

C702

L706

1p0

C708

3n9H

C710

D1

D2

A1

B1

E3

F4

D3

D6

F2

F3

C1

A2

C2

C6

E4

E5

C722

RIF_LFBGA36

RIF_EN

RX_IF_AGC

RX_IFP

RX_IFN

LIM_IN

LIM_NIN

LIM_FB

LO_RIF

RX_IF_FM

RX_FM1

MODE_SEL

VCC1A

VCC1B

VCC2

VCC3

VCC3

VCC4

12p

R708

C723

0R

N702

1n0

RX_QP

RX_QN

RX_IN

RX_IP

LIM_P

LIM_N

RSSI

GND1A

GND1B

GND1C

GND2

GND3

GND3

GND4

C726

12p

C725

RXIQ(1)

D4

RXIQ(0)

C5

RXIQ(2)

A6

RXIQ(3)

A5

F6

E6

F5

B2

NC

B3

NC

B6

NC

C3

NC

E2

NC

C4

A3A4

B4

F1

E1

B5

D5

10n

12p

VRX

C712

C711

L707

82nH

1p0

C714

39p

C713

3n3

100n

128.1MHz

B39131-B7106-F810

In

/In_Gnd

C716

Z703

Bal_Out

Bal_Out

NC

Case_Gnd

56nH

L708

C715

33p

L709

120nH

2p2

C717

33p

L710

120nH

C719

VR2

C718

4n7

VR2

R706

0R

R707

0R

C721

C720 C724

12p

12p

Z702

1930/1990MHz

L705

180nH

IN-GND

C705

47n

IN

C707

4p7

C766

100p

R705

68R

VRX

OUT

OUT-GND

VRX

12p

L702

82nH

N701

ALFRED_VQFN-24

AMPS_OUT 20

P_MIX _IN4

C_MIX_IN16 MIX_OUT 17

P_LNA_IN10

11

3

7

18

19

23

24

C_LNA_IN

BAND

GAIN_CTL

IFA_IN

IFA_SRC

IF_SEL

LO_IN

C_LNA_OUT 13

P_RFA_VDD

RFA_VDD_C

LO_VDD_C

LO_VDD_P

VDD

GND

GND

GND

8P_LNA_OUT

22CDMA_OUT

1

2

5

14

15

6

9

12

C704 C706

12p 1n0

VRX

LO_RIF

RX_IF_AGC

RIF_EN

RXIQ(3:0)

R709

VRX

0R

A701

DUPLEXER

SHIELD ASSY

DMC04944

C703

R703 R704

(X702)

(Z703)

(N702)

(L711)

(C727)

(R709)

R

VR2

VR2

Issue 1 05/02 Nokia Corporation Page A-9

Page 10

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

r

Circuit Diagram of Synthesizer

SYN_LE1

SYN_DAT

SYN_CLK

LO_PRX

LO_PTX

LO_TIF

CLK19M2RF

LO_RIF

R535

270R

R537

18R

R536

270R

VR3

120R/100MHz

C552

VR7

R502

10R

C502

C503

10U

8p2

8

RF1

1

ENFVD6L2S05

C550

C549

C548

RF2

7

R519

68R

R520

100R

VR3A

R525

1u0

100R

L506

39p

10nH

V503

BFR93AW

R527

22p

390R

R501

120R

C501

22p

R518

100R

L507

C551

1n0

R524

1n0

68R

C558

C505

C506

10U

10

G501

9

VCC

6

Vt

2345

C504

1n0

C555

L508

10nH

8p2

C554

8p2

C553

8p2

C546

R526

1u0

3k3

C545

C547

15p

R528

22p

L505

15nH

3k3

VR3

R504

10R

C507

1n0

8p2

R503

470R

R521

33R

R505

C508

4k7

R522

18k

47n

L501

10nH

C544

150p

1SV229

V505

C509

4n7

C556

V501

BFP420

C543

100n

VR7

R523

47R

C557

8p2

R529

100n

R530

1k0

2k2

C542

C541

1u0

R531

100R

4n7

C510

100n

C511

12p

R506

5R6

N502

MB15C130PV1

11

Do

4

LD

3

fout

10= VR3A

12= GND

VR3

OSCin

C512

DIV

fin

VR3

C514

C513

10U

1n0

LMX2330LSLB

15

LE

14

Data

12

Clock

2

Vp1

3

Do RF

5

fin RF

6

fin RF

8

OSCin

8p2

C519

33p

C539

33p

5

2

13

C540

100p

24= VCC

23=VCC1

4,7,10,16,19= GND

N501

Do IF

fin IF

fin IF

FoLD

R507

5R6

C517

C518

12p

100n

GND

22

Vp2

20

18

17

11

C515

470p

GND

C516

100p

C536

L504

15nH

C538

6p8

C520

100n

C522

100n

C524

10n

120R/100MHz

C535

C537

100p

C534

6p8

22p

2p2

R508

10R

R509

10R

C525

100n

R538

1k5

L502

V502

BFR93AW

R517

330R

C521

100n

C523

100n

VCC

VCC1

R515

C533

12p

R510

2k2

C526

1n2

R532

VR1

R533

47k

47k

R511

2k2

VR7

R514

100R

C529

C530

C531

18p

L503

6n8H

1u0

C532

47p

BBY57-02WV504

2k2

470p

R516

3k3

R512

OUT

VR1

10R

+VCC G502

KT17-CCW28B

GND

19.2MHz

C527

VR1

R534

82k

1u0

Vcon

C528

1n0

R513

100k

AFC

VR1

VR3

VR7

Issue 1 05/02 Nokia Corporation Page A-10

VR1

VR3

VR7

Synthesize

Page 11

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Circuit Diagram of TX

FILT_SEL_P

FILT_SEL_N

TX_RF_AGC

C636

BVOLT

Z600

FAR-F6CE-1G8800-L2XA

C661

12p

1RF2

3

RF

N601

GND

AT-119

VCTL5VCC

VR4

4

C602

33n

12p

1880MHz

IN

C601

1n0

OUT

C662

12p

C603

12p

N602

HORNET_RF2357E7

3

IN

1

CH

12

PD

7= BVOLT

C604

12p

BVOLT9=

GND2,5,8,13=

OUT1

OUT2

CAP1

CAP2

C605

1850-1885/1875-1910MHz

Z602

6

10

4

11

C607

C606

3n3

3n3

BVOLT

10n

TQS-946AB-7R

IN_2

IN_1

G1

G2

G3

OUT_2

OUT_1

G4

C608

12p

C609

12p

N603

SW-438TR

RF2

V2

34

GND

RFC

2

1

5

RF1

V1

6

C610

12p

C611

12p

C612

C613

10u

C615

C614

10u

12p

12p

2

1

5

N604

RF9208E8.3

RFin

MODE

Vcc

Vcc

GND7,8=

RFout

VR4

R601

330R

6

4

3

Iref

R602

R603

PUMT1

V601

R605

180R

5V

R604

68R

680R

4

2

5

3

R606

C637

12p

1

PUMT1

V601

6

10k

IN

Z603

SI-4BAL1.880G

OUT

R607

PCS_TX

PA_TEMP

47k

LO_PTX

TXIQ(3:0)

LO_TIF

TIF_EN

CAFE_TX_GATE

TX_IF_AGC

TX_LIM

BVOLT

RF_TX_GATE_P

TX_LIM_ADJ

Tx

C623

1n0

8p2

L603

3n9H

E6

D6

C6

B6

F1

F2

F3

E2

F5

B2

C3

C5

D4

D5

E5

F6

B1

B4

A4

A5

L613 L612

R619

C625

L604

6n8H

VR5

C627

L605

3n3H

8p2

N605

CMY211

VDD

OUT/IN

IF

C622

1p8

R618

1k2

(L617)

(V605)

(N606)

(R629)

R616

(C662)

C640

R617

15k

4

6

C643

10n

LOin

3

IN/OUT

RF

1

5

2

G

G

L606

3n9H

C626

1p8

C642

2p2

C628

47n

1n0

C629

1n0

L614

150nH

C641

2p2

L608

100nH

V604

BFR93AW

C633

R612

L607

18nH

VR5

R613

150R

L615

220nH

R614

22k

C630

C634

C631

1n0

47n

R623

100R

C654

1n0

1n0

C638

2p7

C655

12p

C659

10n

L609

82nH

R615

22R

VR7

C635

V603

HSMS2825

V603

HSMS2825

R624

VR7

C656

12p

10k

R625

33k

R628

33k

VR4

R608

10R

C617

C616

R620

100R

R621

C644

10n

C645

VR7

1n0

R622

220k

VR7

C647

C646

1n0

C649

C648

C650

C652

1n0

C651

1n0

C653

1n0

L616

100nH

L617

100nH

VR4

VR5

VR7

5V

VR4

VR5

VR7

5V

BVOLT

L601

12p

5n6H

C618

1p5

V605

BFP420

R609

TXIQ(3)

TXIQ(2)

TXIQ(0)

TXIQ(1)

R610

R611

5k6

L602

5n6H

15R

R629

1k0

C639

100n 33R

C624

C620

C619

100n

12p

C621

1p5

L610

2n7H

N606

TIF_LFBGA36

A3

TX_IP

C4

A2

B3

C1

D2

E1

E4

D3

E3

B5

D1

C2

F4

A1

A6

RF_1P

TX_IN

RF_1N

TX_QP

RF_2P

RF_2N

TX_QN

LO_TIF

P_DET

P_REF C2

R_EXT

TIF_EN

TX_IF_AGC

TX_LIM

BAND_SEL

MODE_SEL

GND3

VCC1

GND1

VCC3

GND4A

VCC4A

GND4B

VCC4B

GND4C

R1

R2

C1

NC

NC

NC

NC

NC

NC

PDTC114EE

GND

C657

12p

L619

10nH

C660

V602

R1

2x10k

R2

R627

1k0

C658

3p3

R626

330R

1n0

Issue 1 05/02 Nokia Corporation Page A-11

Page 12

PAMS Technical Documentation Schematics / Layouts 8270 NSD-5

Component Layout - Top

Component Layout - Bottom

Issue 1 05/02 Nokia Corporation Page A-12

Loading...

Loading...