Page 1

After Sales Technical Documentation

NHK–6 Series Transceiver

Chapter 4

SYSTEM MODULE

Original 12/97

Page 2

NHK–6

After Sales

System Module

CHAPTER 4 – SYSTEM MODULE

Contents

Introduction Page 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Section Page 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External and Internal Connections Page 4–5. . . . . . . . . . . . . . . . . . . . . . . .

External Connections Page 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Connector X100 Page 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UI Connector X101 Page 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash Connector X103 Page 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM Connector X102 Page 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband Block Page 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction Page 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modes of Operation Page 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Description Page 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply Page 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Charging Control Switch Functional Description Page 4–12. . . . . .

Power Supply Regulator PSCLD, N301 Page 4–14. . . . . . . . . . . . .

PSCLD, N300 External Components Page 4–14. . . . . . . . . . . . . . .

PSCLD, N300 Control Bus Page 4–15. . . . . . . . . . . . . . . . . . . . . . . .

Charger Detection Page 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM Interface and Regulator in N301 Page 4–16. . . . . . . . . . . . . . .

Power Up Sequence Page 4–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU Page 4–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU Access and Wait State Generation Page 4–19. . . . . . . . . . . .

MCU Flash Loading Page 4–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash Prommer Connection Using Dummy Battery Page 4–22. . . . . .

Flash, D400 Page 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SRAM D402, D403 Page 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EEPROM D401 Page 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU and Peripherals Page 4–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband A/D Converter Channels usage in N450 and D150 Page 4–23

Battery Voltage Measurement Page 4–24. . . . . . . . . . . . . . . . . . . . .

Charger Voltage Measurement Page 4–25. . . . . . . . . . . . . . . . . . . .

Battery Size Resistor Measurement Page 4–25. . . . . . . . . . . . . . . .

Battery Temperature Measurement Page 4–26. . . . . . . . . . . . . . . . .

External Accessory Detection via XMIC/ID –line Page 4–26. . . . .

Keyboard Interface Page 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Keyboard and Display Light Page 4–28. . . . . . . . . . . . . . . . . . . . . . . . .

Audio Control Page 4–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Audio Page 4–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Audio Page 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSP Page 4–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Documentation

Page 4–2

Original 12/97

Page 3

After Sales

NHK–6

Technical Documentation

DSP Interrupts Page 4–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSP Serial Communications Interface Page 4–31. . . . . . . . . . . . . .

RFI2, N450 Operation Page 4–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM Interface Page 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BART ASIC Page 4–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Display Driver Interface Page 4–35. . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Block Page 4–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction Page 4–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver Page 4–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency Synthesizers Page 4–37. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter Page 4–38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Charcteristics Page 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver Page 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Duplex Filter Page 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pre–Amplifier Page 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RX Interstage Filter Page 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

First Mixer Page 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

First IF Amplifier Page 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

First IF Filter Page 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Second Mixer Page 4–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Second IF filter Page 4–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver IF Circuit, RX part of CRFRT Page 4–44. . . . . . . . . . . . . . . .

Third IF Filter Page 4–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter Page 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modulator Circuit, TX part of CRFRT Page 4–45. . . . . . . . . . . . . . . . . .

Upconversion Mixer Page 4–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX Interstage Filters Page 4–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX amplifier Page 4–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX buffer Page 4–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Amplifier Page 4–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power control circuit Page 4–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VCTCXO Page 4–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VHF PLL Page 4–50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VHF VCO + Buffer Page 4–50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF PLL Page 4–51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF VCO Page 4–51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF VCO Buffer Page 4–52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLL Circuit Page 4–52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Module

Interconnection Diagram of Baseband Page 4–53. . . . . . . . . . . . . . . . . . . . .

Block Diagram of RF Page 4–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Distribution Diagram of RF Page 4–55. . . . . . . . . . . . . . . . . . . . . . . . .

Parts list of GJ9 (EDMS Issue 13.2) Code 0200592 Page 4–56. . . . . . . . .

Original 12/97

Page 4–3

Page 4

NHK–6

After Sales

System Module

Schematic Diagrams of GJ9: layout version 16

Block Diagram of Baseband (V. 3.5 Ed.177) layout version 16 4/A3–1

Circuit Diagram of Power Supply & Charging (V. 3.5 Ed.140) layout 16 4/A3–2

Circuit Diagram of Central Processing Unit (V. 3.5 E. 161) layout 16 4/A3–3

Circuit Diagram of MCU Memory Block (V. 3.5 Ed. 58) layout 16 4/A3–4

Circuit Diagram of Keyboard & Display Interface (V. 3.5 E. 48) layout 16 4/A3–5

Circuit Diagram of Audio (V. 3.5 ; Ed. 92) layout version 16 4/A3–6

Circuit Diagram of DSP Memory Block (V. 3.5 Ed. 48) layout version 16 4/A3–7

Circuit Diagram of RFI (Version: 3.5 ; Edit 94) for layout version 16 4/A3–8

Circuit Diagram of Receiver (V. J3.7 Ed. 171) layout version 16 4/A3–9

Circuit Diagram of Transmitter (V. J3.7 Ed. 403) layout version 16 4/A3–10

Circuit Diagram of System Connector (V. 3.5 Ed. 98) layout version 16 4/A3–11

Technical Documentation

Layout Diagrams of GJ9 (Version: 16) 4/A3–12

Page 4–4

Original 12/97

Page 5

After Sales

NHK–6

Technical Documentation

Introduction

The GJ9 is the RF module of the NHK–6 cellular transceiver. The GJ9 module

carries out all the RF and system functions of the transceiver. This module

works in the PCN system.

Technical Section

The GJ9 is the RF module of the NHK–6 cellular transceiver. The GJ9 module

carries out all the RF and system functions of the transceiver. This module

works in the DCS1800 system and contains the same baseband block as the

GJ8 which operates in the GSM system.

The GJ9 module is constructed on a 1.0 mm thick FR4 eight–layer printed wir-

ing board. The dimensions of the PWB are 126 mm x 43 mm.

Components are located on both sides of the PWB. The RF components are

located on the top end of the PWB. The both sides of the board includes high

and low components. The maximum usable height is 5 mm.

EMI leakage is prevented by metallized plastic shield A on side 1/8 and me-

tallized plastic shield B on side 8/8. Shield B also conducts heat out of the in-

ner parts of the phone, thus preventing excessive temperature rise.

System Module

External and Internal Connections

The system module has two connectors, external bottom connector and inter-

nal display module connector.

External Connections

Charging Connectors

Battery Connector

4

3

34

+

1

RF–connector

12

712

6

Locking

1

–

2

Original 12/97

System Connector

Page 4–5

Page 6

NHK–6

After Sales

System Module

System Connector X100

Accessory Connector

Pin: Name: Description:

1 GND Charger/system ground

2 V_OUT Accessory output supply

3 XMIC External microphone input and accessory

ID identification

Technical Documentation

• min/typ/max: 3.40...10 V

(output current 50 mA)

• typ/max: 8...50 mV (the maximum value

corresponds to 0 dBm network level with input

amplifier gain set to 20 dB, typical value is

maximum value –16 dB)

Accessory identification

• 1.7...2.05 V headset adapter connected

• 1.15...1.4 V compact hadsfree unit connected

• 2.22... 2.56 V Infra Red Link connected

4 EXT_RF External RF control input

• min/max: 0...0.5 V External RF in use

• min/max: 2.4...3.2 V Internal antenna in use

5 TX FBUS transmit

6 MBUS Serial control bus

• logic low level: 0...0.5 V

• logic high level: 2.4...3.2 V

7 BENA No connection

8 SGND Signal ground

9 XEAR External speaker and mute control

• min/nom/max: 0...32...500 mV (typical level

corrensponds to –16 dBm0 network level with

volume control in nominal position 8 dB below

maximum. Maximum 0 dBm0 max. volume

codec gain –6 dB)

• mute on (HF speaker mute): 0...0.5 V d.c.

• mute off (HF speaker active): 1.0...1.7 V d.c.

10 HOOK Hook signal

• hook off (handset in use) : 0...0.5 V

• hook on, (handset not in use): 2.4...3.2 V

Page 4–6

11 RX FBUS receive

• accessory FBUS receive signal,

Serial data bus

12 V_IN Charging supply voltage

Original 12/97

Page 7

After Sales

NHK–6

Technical Documentation

Battery Connector

Pin: Name: Description:

13 BGND Battery ground

14 BSI Battery size indicator

15 BTEMP Battery temperature

16 VB Battery voltage

Charging connectors

Pin: Name: Description:

12,17,19 V_IN Charging voltage input

18, 20 GND Charger/system ground

System Module

(used also for SIM card detection)

(used also for vibration alert)

• min/typ/max: 5.3...6...10.26 V

• ACH–6 min/nom/max: 9.8...10.3...10.8 V

UI Connector X101

Pin: Name: Description:

1 MICP Microphone

2 MICN Microphone

3 GND Ground

4 VL Display supply

5 SYSRESETX Reset, Edge sensitive

6 GND Ground

7 KEYLIGHT Keyboard Light

• min/typ/max: 0...2...12.5 mV Connected to

Audio Codec Microphone input. The maximum

value corresponds to 1 kHz, o dBmO network

level input amplifier gain set to 32 dB. Typical

value is maximum value –16 dB.

• min/max: 0...12.5 mV Connected to Audio

Codec and over resistor to AGND

• min/max: 3.0...3.2 mV

Original 12/97

Page 4–7

Page 8

NHK–6

After Sales

System Module

Pin: Name: Description:

8 LCDLIGHT Display light

9 BUZZER PWM signal Buzzer control

10 CS2 Not in use

11 SLIDEON Slide indication

12 GENSCLK Serial clock

13 GENSD Serial data

14 LCDENX LCD enable

15 VB Battery supply

16 XPWRON Power ON/OFF

17 EARN Earphone

Technical Documentation

• min/typ/max: 0...14...220 mV. Connected to

Audio Codec Inverted Output. Typical level

corresponds to –16 dBmO network level with

volume control giving nominal RLR (=+2 dB)

8 dB below max. Max level is 0 dBmO with max

volume (codec gain –11 dB).

18 EARP Earphone (see above)

19 CALL_LED Call indication led

20–25 ROW(0–5)

26–29 COL(0–4)

30 GND Ground

Flash Connector X103

Pin: Name: Description:

1 VPP Flash programming voltage

2 FRX Flash data receive, test point J311

3 FTX Flash acknowledge transmit, test point J312

4 FCLK Flash serial clock, test point J313

5 WDDIS Watchdog disable, signal pulled down to

• min/typ/max: 11.4...12...12.6 V

(values when VPP active), test point J310

disable watchdog, test point J314

Page 4–8

6 GND Digital ground, test point J315

Original 12/97

Page 9

After Sales

NHK–6

Technical Documentation

SIM Connector X102

Pin: Name: Description:

1 GND Ground for SIM

2 VSIM SIM voltage supply

3 SDATA Serial data for SIM

4 SRES Reset for SIM

5 CLK Clock for SIM data (clock frequency minimum

System Module

• min/typ/max: 4.8...4.9...5.0 V

1 MHz if clock stopping not allowed)

Original 12/97

Page 4–9

Page 10

NHK–6

After Sales

System Module

Baseband Block

Introduction

The GJ8/GJ9 module is used in GSM/PCN products. The baseband is implemented using DCT2 core technology. The baseband is built around one DSP,

System ASIC and the MCU. The DSP performs all speech and GSM/PCN related signal processing tasks. The baseband power supply is 3V except for the

A/D and D/A converters that are the interface to the RF section. The A/D converters used for battery and accessory detection are integrated into the same

device as the signal processing converters.

The audio codec is a separate device which is connected to both the DSP and

the MCU. The audio codec support the internal and external microphone/earpiece functions. External audio is connected in a dual ended fashion to improve

audio quality together with accessories.

The baseband implementation support a 32.768 kHz sleep clock function for

power saving. The 32.768 kHz clock is used for timing purposes during inactive

periods between paging blocks. This arrangement allows the reference clock,

derived from RF to be switched off.

Technical Documentation

The baseband clock reference is derived from the RF section and the reference

frequency is 13 MHz. a low level clipped sinusoidal wave form is fed to the

ASIC which acts as the clock distribution circuit. The DSP is running at 39 MHz

using an internal PLL. The clock frequency supplied to the DSP is 13 MHz. The

MCU bus frequency is the same as the input frequency. The system ASIC provides both 13 MHz and 6.5 MHz as alternative frequencies. The MCU clock frequency is programmable by the MCU. The HD843 baseband uses 13 MHz as

the MCU operating frequency. The RF A/D, D/A converters are operated using

the 13 MHz clock supplied from the system ASIC

The power supply and charging section supplies Lithium type of battery

technology. The battery charging unit is designed to accept constant current

type of chargers, that are approved by NMP.

The power supply IC contains three different regulators. The output voltage

from each regulator is 3.15V nominal. One of the regulators uses an external

transistor as the boost transistor.

Page 4–10

Original 12/97

Page 11

After Sales

NHK–6

Technical Documentation

Modes of Operation

The Baseband in HD843 Operates in the following Modes

1 Active, as during a call or when baseband circuitry is operating

2 Sleep, in this mode the clock to the baseband is stopped and timing

is kept by the 32.768 kHz oscillator. All Baseband circuits are powered

3 Acting dead, in this mode the battery is charged but only necessary

functions for charging are running

4 Power off, in this mode all baseband circuits are powered off. The

regulator IC N300 is powered

Circuit Description

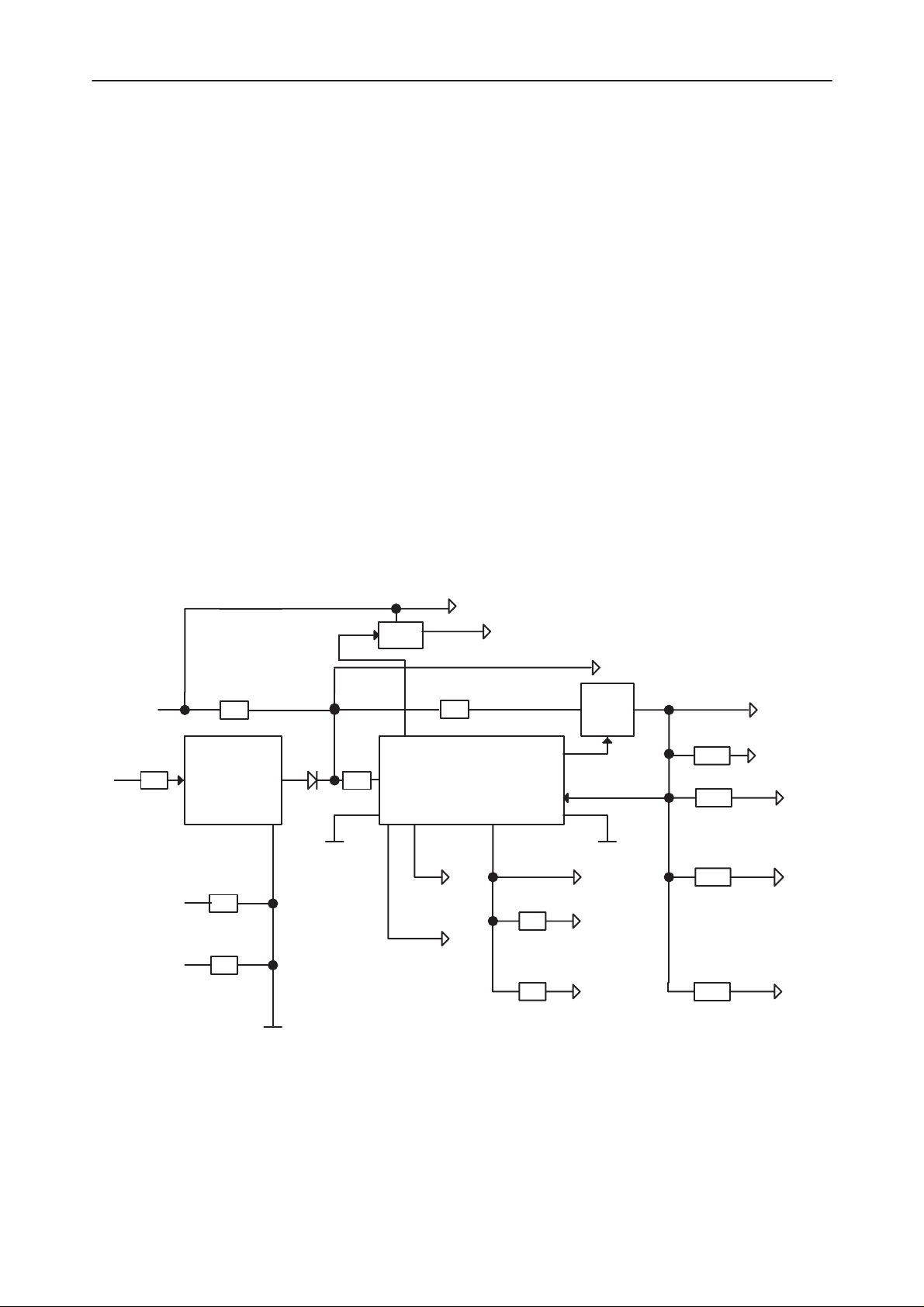

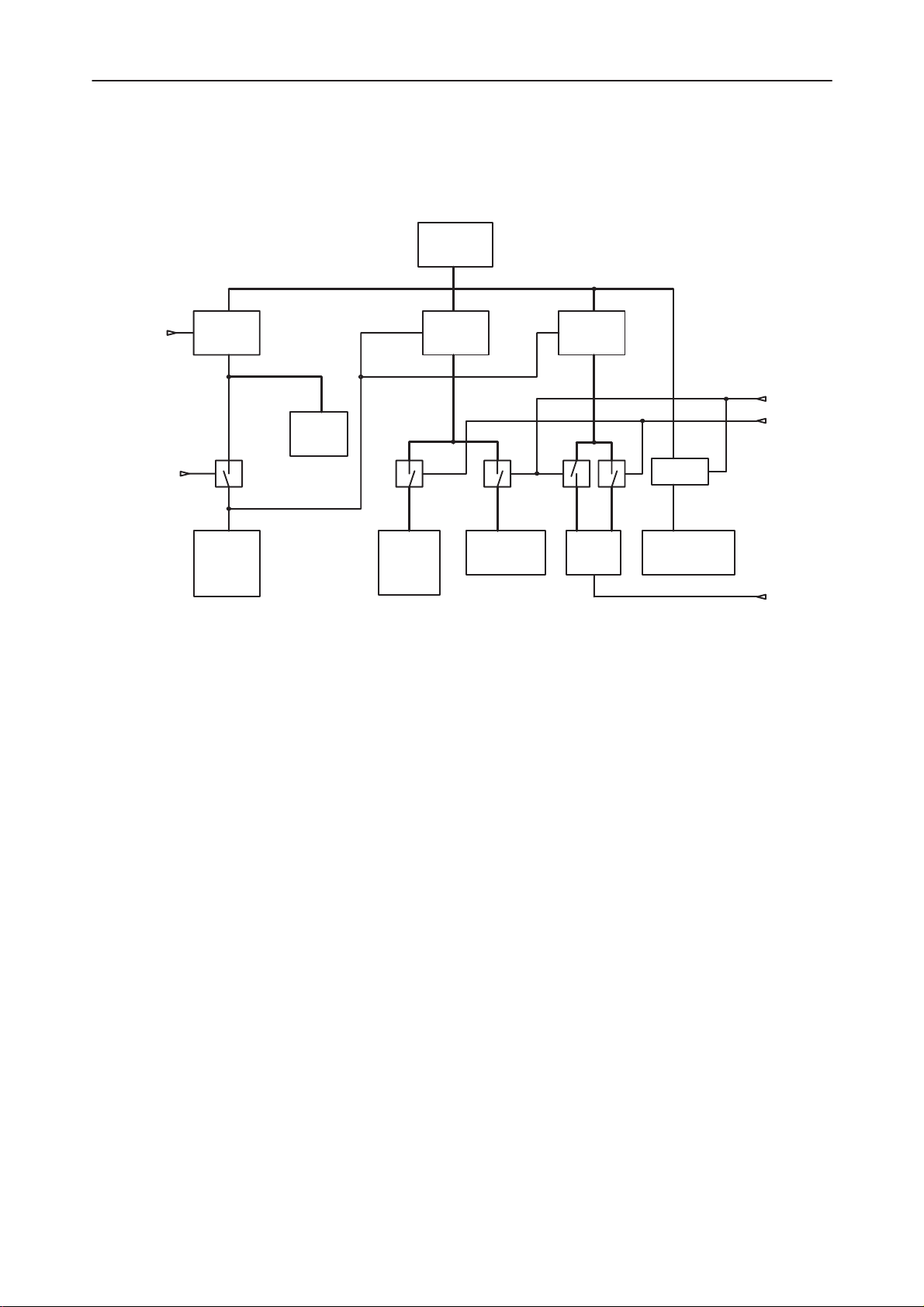

Power Supply

System Module

VBAT

CHARGER +

L107

CHGND

BGND

L300

CHARGER

UNIT

L108

L101

GND

V305

9,10,45,46

AGND

L311

V450

7..

PSCLD

60

4.50 V

L312

N300

51

VA

3.16 V

VSIM

5/3V

VBATT to RF

VRFI

N450

59

43

42

5..

Z152

Z151

VB (to illumination leds)

V306

GND

VSL

VSLRC

3.16 V

D151; pin 124

VSLC

3.16 V

D151

D401

D403

VL

3.16 V

L306

Z150

Z153

Z450 VLRFI

VLCD

3.16 V3.16 V3.16 V

VLMCU

VLDSP

D152

D404

D405

D150

D400

3.16 V

3.16 V

N450

The power supply for the baseband is the main battery. The main battery consists of 2 LI–ION cells. A charger input is used to charge the battery. Two differ-

Original 12/97

Page 4–11

Page 12

NHK–6

After Sales

System Module

ent chargers can be used for charging the battery. A switch mode type fast

charger that can deliver 780 mA and a standard charger that can deliver 265

mA. Both chargers are of constant current type.

The baseband has one power supply circuit, N300 delivering power to the different parts in the baseband. There are two logic power supply and one analog

power supply. The analog power supply VA is used for analog circuits such as

audio codec, N200 and microphone bias circuitry. Due to the current consumption and the baseband architecture the digital supply is divided into to parts.

Both digital power supply rails from the N300, PSCLD are used to distribute the

power dissipation inside N300, PSCLD. The main logic power supply VL has an

external power transistor, V306 to handle the power dissipation that will occur

when the battery is fully charged or during charging.

D151, ASIC and the MCU SRAM, D403 are connected to the same logic supply

voltage. All other digital circuits are connected to the main digital supply. The

analog voltage supply is connected to the audio codec.

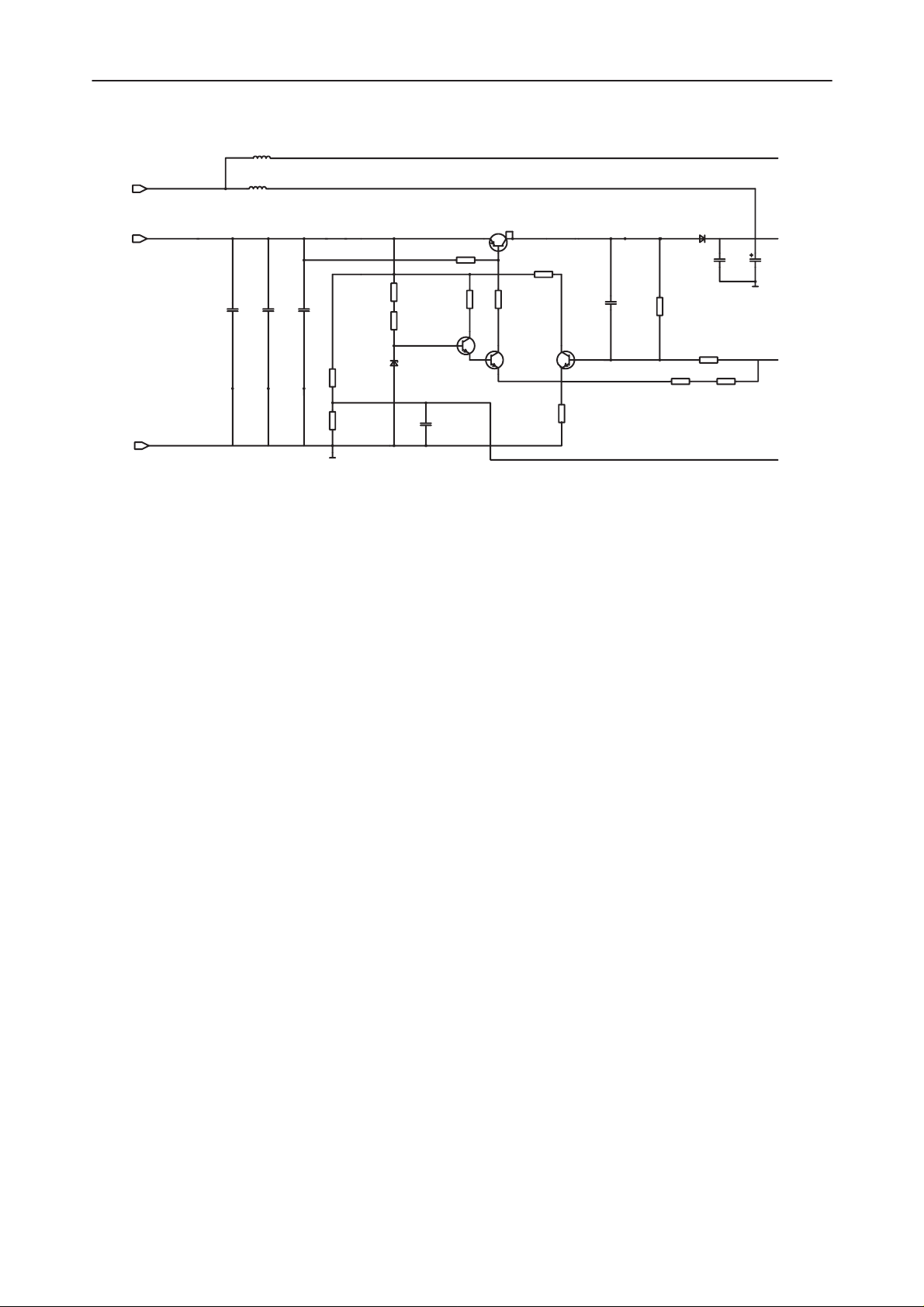

Charging Control Switch Functional Description

Technical Documentation

The charging switch transistor V304 controls the charging current from the

charger input to the battery. During charging the transistor is forced in saturation and the voltage drop over the transistor is 0.2–0.4V depending upon the

current delivered by the charger. Transistor V304 is controlled by the PWM output from N300, pin 34 via resistors R309, R308 and transistor V311. The output

from N300 is of open drain type. When transistor V304 is conducting the output

from N300 pin is low. In this case resistors R305 and R306 are connected in

parallel with R304. This arrangement increases the base current thru V304 to

put it into saturation.

Transistors V304, V302, V303 and V311 forms a simple voltage regulator circuit. The reference voltage for this circuit is taken from zener diode V301. The

feedback for the regulator is taken from the collector of V304. When the PWM

output from N300 is active, low, the feedback voltage is determined by resistors

R308 and R309. This arrangement makes the charger control switch circuitry to

act as a programmable voltage regulator with two output voltages depending

upon the state of the PWM output from N300. When the PWM is inactive, in

high impedance the feedback voltage is almost the same as on the collector of

V304. Due to the connection the voltage on V303 and V311 emitters are the

same. The influence of the current thru R305 and R306 can be neglected in

this case.

The charging switch circuit diagram is shown in following figure. The figure is

for reference only.

Page 4–12

Original 12/97

Page 13

After Sales

NHK–6

Technical Documentation

L303

L300

VBAT

CHARGER

C300 C301 C302

GND

This feedback means that the system regulates the output voltage from V304 in

such a way that the base of V303 and V311 are at the same voltage. The voltage on V302 is determined by the V301 zener voltage. The darlington connection of V303 and V302 service two purposes ; 1 the load on the voltage reference V301 is decreased, 2 the output voltage on V304 is decreased by the

VBE voltage on V302 which is a wanted feature. The voltage reduction allows a

relative temperature stable zener diode to be used and the output voltage from

V304 is at a suitable level when the PWM output from N300 is not active.

R302

R303

R301

R326

V301

C303

V304 V305

R308

R343

V302

R342

R327

V311

V303

R304

C304

System Module

R308

C305

R309

R306R305

VBATT

C308

PWM

The circuitry is self starting which means that an empty battery is initially

charged by the regulator circuitry around the charging switch transistor. The

battery is charged to a voltage of maximum 4.8V. This charging switch circuitry

allows for both NiCd, NiMH and Lithium type of batteries to be used.

When the PWM output from N300 is active the feedback voltage is changed

due to the presence of R308 and R309. When the PWM is active the charging

switch regulator voltage is set to 10.5V maximum. This means that even if the

voltage on the charger input exceeds 11.5V the battery voltage will not exceed

10.5 V. This protects N300 from over voltage even if the battery was to be detached while charging.

The RC network C304, R308 and R309 also acts as a delay circuit when

switching from one output voltage to an other. This happens when the PWM

output from N300 is pulsing. The reason for the delay is to reduce the surge

current that will occur when V304 is put into conducting state. Before V304 is

put in conducting state there is a significant voltage drop over V304. The energy is stored in capacitors in the charger and these capacitors must first be

drained in order to put the charger in constant current mode. This is done by

discharging the capacitors into the battery. The delay caused by C304 will reduce the surge current thru V304 to an acceptable value.

R301 and R326 are used to regulate the zener current. During charging with

empty battery the zener voltage might drop due to low zener current but this is

no problem since the regulator is operating in constant current mode while

Original 12/97

Page 4–13

Page 14

NHK–6

After Sales

System Module

charging. The zener voltage is more important when the charger voltage is high

or in case that the PWM output from N300 is inactive. In this case the charger

idle voltage is present at the charger supply pins.

R300 and R327 together with V304 forms a constant current source. The surge

current limitation behavior is frequency dependent since L107 is an inductor.

The purpose of these circuits is to reduce the surge current thru V304 when it is

put in conducting state. Due to the low resistance value required in L107 this

arrangement is not very effective and the RC network R308, R309 and C304

contributes more to the surge current reduction.

V305 is a schottky diode that prevents the battery voltage from reverse bias

V304 when the charger is not connected. The leakage current for V305 is increasing with increasing temperature and the leakage current is passed to

ground via R308, V311 and R304. This arrangement prevents V304 from being

reversed biased as the leakage current increases at high temperatures.

Components L107, C300, C301, C302 and L108 forms a filter for EMC attenuation. The circuitry reduces the conductive EMC part from entering the charger

cable causing an increase in emission as the cable will act as an antenna.

V100 is a 18V transient suppressor. V100 protects the charger input and in particular V304 for over voltage. The cut off voltage is 18V with a maximum surge

voltage up to 25V. V100 also protects the input for wrong polarity since the transient suppressor is bipolar.

Technical Documentation

Power Supply Regulator PSCLD, N301

The power supply regulators are integrated into the same circuit N300. The

power supply IC contains three different regulators. The main digital power supply regulator is implemented using an external power transistor V306. The other two regulators are completely integrated into N300.

PSCLD, N300 External Components

N300 performs the required power on timing. The PSCLD, N300 internal power on and reset timing is defined by the external capacitor C330. This capacitor

determines the internal reset delay, which is applied when the PSCLD, N300 is

initially powered by applying the battery. The baseband power on delay is determined by C311. With a value of 10 nF the power on delay after a power on

request has been active is in the range of 50–150 ms. C310 determines the

PSCLD, N300 internal oscillator frequency and the minimum power off time

when power is switched off.

The sleep control signal from the ASIC, D151 is connected via PSCLD, N300.

During normal operation the baseband sleep function is controlled by the ASIC,

D151 but since the ASIC is not power up during the startup phase the sleep

signal is controlled by PSCLD, N300 as long as the PURX signal is active. This

arrangement ensures that the 13 MHz clock provided from RF to the ASIC,

D151 is started and stable before the PURX signal is released and the base-

Page 4–14

Original 12/97

Page 15

After Sales

NHK–6

Technical Documentation

band exits reset. When PURX is inactive, high, sleep control signal is controlled

by the ASIC D151.

To improve the performance of the analog voltage regulator VA an external capacitor C329 has been added to improve the PSRR.

N300 requires capacitors on the input power supply as well as on the output

form each regulator to keep each regulator stable during different load and temperature conditions. C305 and C308 are the input filtering capacitors. Due to

EMC precautions a filter using C305, L300 and C308 has been inserted into the

supply rail. This filter reduces the high frequency components present at the

battery supply from exiting the baseband into the battery pack. The regulator

outputs also have filter capacitors for power supply filtering and regulator stability. A set of different capacitors are used to achieve a high bandwith in the suppression filter.

PSCLD, N300 Control Bus

The PSCLD, N300 is connected to the baseband common serial control bus,

SCONB(5:0). This bus is a serial control bus from the ASIC, D151 to several

devices on the baseband. This bus is used by the MCU to control the operation

of N300 and other devices connected to the bus. N300 has two internal 8 bit

registers and the PWM register used for charging control. The registers contains information for controlling reset levels, charging HW limits, watchdog timer

length and watchdog acknowledge.

System Module

The control bus is a three wire bus with chip select for each device on the bus

and serial clock and data. From PSCLD, N300 point of view the bus is used as

write only to PSCLD. It is not possible to read data from PSCLD, N300 by using

this bus.

The MCU can program the HW reset levels when the baseband exits/enters reset. The programmed values remains until PSCLD is powered off, the battery is

removed. At initial PSCLD, N300 power on the default reset level is used. The

default value is 5.1 V with the default hysteresis of 400 mV. This means that reset is exit at 5.5 V when the PSCLD, N300 is powered for the first time.

The watchdog timer length can be programmed by the MCU using the serial

control bus. The default watchdog time is 32 s with a 50 % tolerance. The complete baseband is powered off if the watchdog is not acknowledged within the

specified time. The watchdog is running while PSCLD, N300 is powering up the

system but PURX is active. This arrangement ensures that if for any reason the

battery voltage doesn’t increase above the reset level within the watchdog time

the system is powered off by the watchdog. This prevents a faulty battery from

being charged continuously even if the voltage never exceeds the reset limit.

As the time PURX is active is not exactly known, depends upon startup condition, the watchdog is internally acknowledged in PSCLD when PURX is released. This gives the MCU always the same time to respond to the first watchdog acknowledge.

Original 12/97

Page 4–15

Page 16

NHK–6

After Sales

System Module

Baseband power off is initiated by the MCU and power off is performed by writing the smallest value to the watchdog timer register. This will power off the

baseband within 0.5 ms after the watchdog write operation.

The control bus can also be used to setup the behavior of the N300 regulators

during sleep mode, when sleep signal is active low. In order to reduce power

during sleep mode two of the three regulators can be switched off. The third

regulator, VSL which is kept active then supplies the output of the other regulators. All regulator outputs from PSCLD, N300 are supplied but the current consumption is restricted. It is also possible to keep the VL regulator active during

sleep mode in case the power consumption is in excess of what the VSL regulator can deliver in sleep mode to the VL output.

The PSCLD, N300 also contains switches for connecting the charger voltage

and the battery voltage to the base band A/D converters. Since the battery voltage is present and the charger voltage might be present in power off the A/D

converter signals must be connected using switches. The switch state can be

changed by the MCU via the serial control bus. When PURX is active both

switches are open to prevent battery/charger voltage from being applied to the

baseband measurement circuitry which is powered off. Before any measurement can be performed both switches must be set in not closed mode by MCU.

Technical Documentation

Charger Detection

A charger is detected if the voltage on N300 pin 41 is higher than 0.5V. The

charger voltage is scaled externally to PSCLD, N300 using resistors R302 and

R303. With the implemented resistor values the corresponding voltage at the

charger input is 2.8V. Due to the multifunction of the charger detection signal

from PSCLD, N300 to ASIC, D151 the charger detection line is not forced, active high until PURX is inactive. In case PURX is inactive the charger detection

signal is directly passed to D151. The active high on pin 21 generates an interrupt to MCU which then starts the charger detection task in SW.

The reason for not passing the charger detection signal to the ASIC, D151

when PURX is active is the RTC implementation in ASIC, D151., This same

signal is used to power up the system if the RTC alarm is activated and the system is power up. Due to this the PSCLD, N300 pin 21 is in input mode as long

as PURX is active. Correspondingly at the ASIC end this pin is an output as

long as PURX is active. The RTC function needs SW support and is not implemented in NHK–6. The baseband architecture provides for the functionality required.

SIM Interface and Regulator in N301

Page 4–16

The SIM card regulator and interface circuitry is integrated into PSCLD, N300.

The benefit from this is that the interface circuits are operating from the same

supply voltage as the card, avoiding the voltage drop caused by the external

switch used in previous designs. The PSCLD, N300 SIM interface also acts as

voltage level shifting between the SIM interface in the ASIC, D151 operating at

3V and the card operating at 5V. Interface control in PSCLD is direct from

Original 12/97

Page 17

After Sales

NHK–6

Technical Documentation

ASIC, D151 SIM interface using SIM(5:0) bus. The MCU can select the power

supply voltage for the SIM using the serial control bus. The default value is 3V

which needs to be changed to 5V before power up the SIM interface in ASIC,

D151. Regulator enable and disable is controlled by the ASIC via SIM(2).

Power Up Sequence

The baseband can be powered up in three different ways.

– When the power switch is pressed input pin 37 to PSCLD, N300 is con-

nected to ground and this switches on the regulators inside PSCLD.

– An other way to power up is to connect the charger. Connecting the charger

causes the baseband to power up and start charging the battery.

– The third way to power the system up is to attach the battery.

Power up using Power on Button

This is the most common way to power the system up. This power up is successful if the battery voltage is higher than power on reset level set by the

MCU, default value 5.4 V DC in PSCLD, N300. The power up sequence is

started when the power on input pin 37 at PSCLD is activated, low. The PSCLD

then internally enters the reset state where the regulators are switched on. At

this state the PWM output ( pin 34) from PSCLD is forced active to support

additional power from any charger connected. The sleep control output signal is

forced high enabling the regulator to supply the VCO and startup the clock. After the power on reset delay of 50–150 ms PURX is released and the system

exits reset. The PWM output is still active until the MCU writes the first value to

the PWM register. The watchdog has to be acknowledged within 16 s after that

PURX has changed to inactive state

System Module

Power Up with Empty Battery using Charger

When the charger is inserted into the DC jack or charger voltage is supplied at

the system connector contacts/pins, PSCLD ( N300) powers up the baseband.

The charging control switch is operating as a linear regulator, the output voltage

is 4.5V–5V. This allows the battery to be charged immediately when the charger is connected. This way of operation guarantees successful power up procedure with empty battery. In case of empty battery the only power source is

the charger. When the battery has been initially charged and the voltage is

higher than the PSCLD, N300 switches on the sleep control signal, which is

connected to the PSCLD for power saving function. Sleep mode enters inactive

state, high, to enable the regulator that controls the power supply to the VCO to

be started. The ASIC, D151 which normally controls the sleep control line has

the sleep output inactive, low as long as the system reset, PURX is active, low,

from PSCLD. After a delay of about 5–10 ms the system reset output PURX

from PSCLD enters high state. This delay is to ensure that the clock is stable

when the ASIC exits reset. The sleep control output from the PSCLD that has

been driving an output until now, returns the control to the sleep signal from the

ASIC as the PURX signal goes inactive. When the PURX signal goes inactive,

high, the charge detection output at PSCLD, that is in input mode when PURX

Original 12/97

Page 4–17

Page 18

NHK–6

After Sales

System Module

is active, switches to output and goes high indicating that a charger is present.

When the system reset, PURX, goes high the sleep control line is forced inactive, high, by the ASIC, D151 via PSCLD, N300.

Once the system has exited reset, the battery is initially charged until the MCU

writes a new value to the PWM in PSCLD. If the watchdog is not acknowledged

the battery charging is switched off when the PSCLD shuts off the power to the

baseband. The PSCLD will not enter the power on mode again until the charger

has been extracted and inserted again or the power switch has been pressed.

The battery is charged as long as the power on line, PWRONX is active low.

This is done to allow the phone to be started manually from the power button

when the charger is conncted and there is no need to disconncet the charger to

get a power up if the battery is empty.

Power On Reset Operation

The system power up reset is generated by the regulator IC, N300. The reset is

connected to the ASIC, D151 that is put into reset whenever the reset signal,

PURX is low. The ASIC ( D151 ) then resets the DSP (D152) the MCU ( D150)

and the digital parts in RFI2 (N450). When reset is removed the clock supplied

to the ASIC, D151 is enabled inside the ASIC. At this point the 32.768 kHz oscillator signal is not enabled inside the ASIC, since the oscillator is still in the

startup phase. To start up the block requiring 32.768 kHz clock the MCU must

enable the 32.768 kHz clock. The MCU reset counter is now started and the

MCU reset is still kept active, low. 6.5 MHz clock is started to MCU in order to

put the MCU( D150 ) into reset, MCU is a synchronous reset device and needs

clock to reset. The reset to MCU is put inactive after 128 MCU clock cycles and

MCU is started.

Technical Documentation

DSP ( D152) and RFI2 (N450) reset is kept is kept active when the clock inside

the ASIC, D151 is started. 13 MHz clock is started to DSP (D152) and puts it

into reset. D152 is a synchronous reset device and requires clock to enter reset. N450 digital parts are reset asynchronously and do not need clock to be

supported to enter reset.

As both the MCU D151 and DSP D152 are synchronous reset devices all interface signals connected between these devices and ASIC D151 which are

used as I/O are set into input mode on the ASIC, D151 side during reset. This

avoids bus conflicts to occur before the MCU, D150 and the DSP, D152 are actually reset.

The DSP ( D152) and RFI2 (N450) reset signal remains active after the MCU

has exited reset. The MCU writes to the ASIC register to disable the DSP reset.

This arrangement allows the MCU to reset the DSP, D152 and RFI2, N450

when ever needed. The MCU can put DSP into reset by writing the reset active

in the ASIC, D151 register.

Page 4–18

Original 12/97

Page 19

After Sales

NHK–6

Technical Documentation

MCU

The baseband used a Hitachi H3001 type of MCU. This is a 16–bit internal

MCU with 8–bit external data bus. The MCU is capable of addressing up to 16

MByte of memory space linearly depending upon the mode of operation. The

MCU has a non multiplexed address/data bus which means that memory access can be done using less clock cycles thus improving the performance but

also tightening up memory access requirements. The MCU is used in mode 3

which means 8–bit external data bus and 16 Mbyte of address space. The

MCU operating frequency is equal to the supplied clock frequency. The MCU

has 512 bytes of internal SRAM. The MCU has one serial channel, USART that

can operate in synchronous and asynchronous mode. The USART is used in

the MBUS implementation. Clock required for the USART is generated by the

internal baud rate generator. The MCU has 5 internal timers that can be used

for timing generation. Timer TIOCA0 input pin 71 is used for generation of netfree signal from the MBUS receive signal which is connected to the MCU

USART receiver input on pin 2.

The reason for generating the MBUS netfree using the counter is the fact that

the 32.768 kHz clock that would have been used for this timing is a slow starting oscillator. This means that in production testing the MBUS can not be operated until the netfree counter is operational. As the netfree counter is implemented using the MCU internal counter the netfree counter is available

immediately after reset. In the same way the MCU OS timer is operated from

an internal timer in the early stage until the 32.768 kHz clock can be enabled

and the OS timer provided in the ASIC can be used.

System Module

The MCU contains 4 10–bit A/D converters channels that are used for baseband monitoring.

The MCU, D150 has several programmable I/O ports which can be configured

by SW. Port 4 which multiplexed with the LSB part of the data bus is used

baseband control. In the mode the MCU is operating this port can be used as

an I/O port and not as part of the data bus, D0–D7.

MCU Access and Wait State Generation

The MCU can access external devices in 2 state access or 3 state access. In

two state access the MCU uses two clock cycles to access data from the external device In 3 state access, the MCU uses 3 clock cycles to access the external device or more if wait states are enabled. The wait state controller can operate in different modes. In this case the programmable wait mode is used.

This means that the programmed amount of wait states in the wait control register is inserted when an access is performed to a device located in that area.

The complete address space is divided into 8 areas each area covering 2

MByte of address space. The access type for each area can be set by bits in

the access state control register. Furthermore the wait state function can be enabled separately for each area by the wait state controller enable register. This

means that in 3 state access, two types of acccess can be performed with a

fixed setting:

Original 12/97

Page 4–19

Page 20

NHK–6

After Sales

System Module

– 3 state access without wait states

– 3 state access with the amount of wait states inserted determined by the

wait control register

If the wait state controller is not enabled for a 3 state access area no wait

states are inserted when accessing that area even if the wait control register

contains a value that differs from 0 states.

MCU Flash Loading

MCU Boots from ASIC ROM. The flash loading equipment is connected to the

baseband by means of the test connector before the module is cut out from the

frame. Updating SW on a final product is done by removing the battery and

connect a special battery that contains the necessary contacting elements. The

contacts on the baseband board are test points that are accessable when the

battery is detached. The power supply for the base band is supplied via the

adapter and controlled by the flash programming equipment. The base band

module is powered up when the power is connected to the battery contact pins.

Technical Documentation

The interface lines between the flash prommer and the baseband are in low

state when power is not connected by the flash prommer. The data transfer between the flash programming equipment and the base band is synchronous

and the clock is generated by the flash prommer. The same USART that is

used for MBUS communication is used for the serial synchronous communication. The PSCLD watchdog is disabled when the flash loading battery pack and

cable is connected.

After the flash battery pack adapter has been mounted or the test connector

has been connected to the board the power to the base band module is connected by the flash prommer or the test equipment. All interface lines are kept

low except for the data transmit from the baseband that is in reception mode on

the flash prommer side, this signal is called TXF. The MCU boots from ASIC

and investigates the status of the synchronous clock line. If the clock input line

from the flash prommer is low or no valid SW is located in the flash, MCU

forces the initially high TXF line low, acknowledging to the flash prommer that it

is ready to accept data . The flash prommer sends data length, 2 bytes, on the

RXF data line to the baseband. The MCU acknowledges the 2 data byte reception by pulling the TXF line high. The flash prommer now transmits the data on

the RXF line to the MCU. The MCU loads the data into the internal SRAM. After

having received the transferred data correctly, MCU puts the TXF line low and

jumps into internal SRAM and starts to execute the code. After a guard time of

1 ms the TXF line is put high by the MCU. After 1 ms the TXF is put low indicating that the external SRAM test is going on. After further 1 ms the TXF is put

high indicating that external SRAM test has passed. The MCU performs the

flash memory identification based upon the identifiers specified in the Flash

Programming Specifications. In case of an empty device, identifier locations

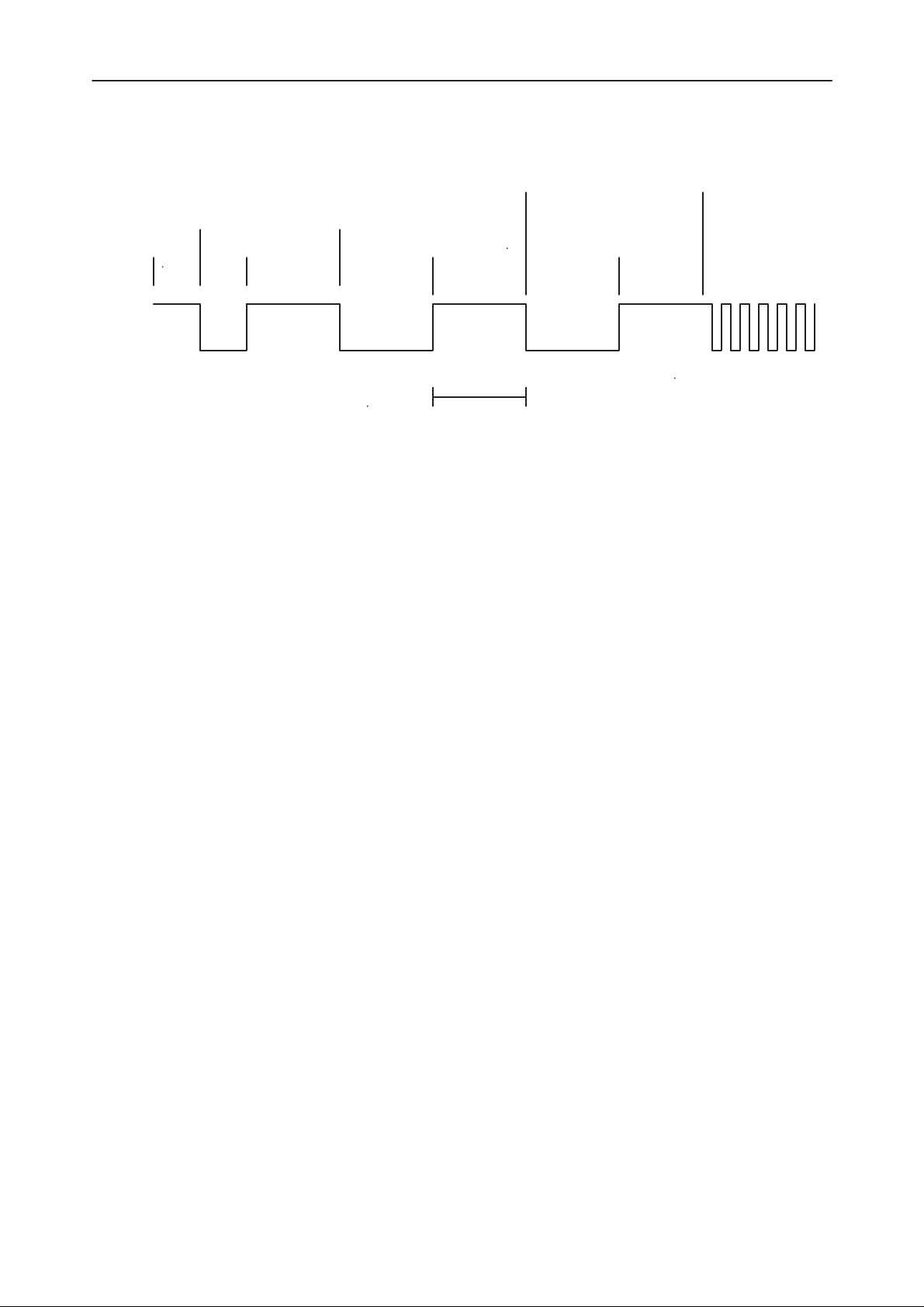

shows FFH, the flash device code is read and transmitted to the Flash Prommer. The TXF line functional timing is shown in the following diagram.

Page 4–20

Original 12/97

Page 21

After Sales

NHK–6

Technical Documentation

Boot OK

Reset

TXF

Length OK

After that the device mounted on base band has been identified, the Flash

Prommer down loads the appropriate algorithm to the baseband. The programming algorithm is stored in the external SRAM on the baseband module and

after having down loaded the algorithm and data transfer SW, MCU jumps to

the external SRAM and starts to execute the code. The MCU now asks the

prommer to connect the flash programming power supply. This SW loads the

data to be programmed into the flash and implements the programming algorithm that has been down loaded. The flash data is loaded in bytes.

External SRAM

Internal SRAM

execution begin External SRAM

test going on

test passed

1 ms

Ready to send

Flash ID

System Module

Original 12/97

Page 4–21

Page 22

NHK–6

After Sales

System Module

Flash Prommer Connection Using Dummy Battery

For MCU SW updating in the field, a special battery adapter can be used to

connect to the test points which are accessable through SIM opening in the

chassis, located behind the battery. Supply voltage must be connected to this

dummy battery as well as the flash programming equipment

Flash, D400

A 8 MBit flash is used as the main program memory D400. The device is 3 V

read/program with external 12V VPP for programming. The device is sectored

and contains 16 64 kByte blocks. The sector capability is not used in the

HD843 application. The speed of the device is 180 ns. The MCU operating at

13 MHz will access the flash in 3 state access, requiring 190 ns access time

from the memory.

The flash has a deep power down mode that can be used when the device is

not active. There is a requirement for a longer access time if the device is accessed immediately after exiting power down. This requirement is met since the

signal controlling the VCO power control is used for this purpose. The flash

power down pin, pin 12 is connected to ASIC, D151 pin 130. The reason for

connecting it to the ASIC and not direct to the VCO power control signal is that

this pin on the ASIC is low as long as the ASIC is in reset. This signal also resets the flash memory as this pin also acts as a power up reset to the memory.

Technical Documentation

SRAM D402, D403

The baseband is designed to use SRAM size 128kx8. The required speed is

100 ns as the MCU will operate at 13 MHz and the SRAM will be accessed in 3

state access. The SRAM has no battery backup which means that the content

is lost even during short power supply disconnections. As shown in the memory

map the SRAM is not accessable after boot until the MCU has enabled the

SRAM access by writing to the ASIC register.

EEPROM D401

The baseband is designed to use an 8kx8 parallel EEPROM.

The parallel device is connected to the MCU data and address bus. The ASIC

generates chip select for the EERPROM. To avoid unwanted EEPROM access

there is an EERPOM access bit in the ASIC MCU interface. This bit must be set

to allow for EERPOM access. This bit is cleared by default after reset. After

each access this bit should be cleared to prevent unwanted EEPROM access.

The parallel device uses support page mode writing, 64 byte page. One page

can be written by the MCU, and after that, the internal programming procedure

is started. The page write operation is internally timed in the device and consecutive bytes must be written within 150 us. During this operation all interrupts

must be disabled.

Page 4–22

Original 12/97

Page 23

After Sales

NHK–6

Technical Documentation

The device also supports SW protection to prevent accidental write operations

to the device. The protection algorithm can be enabled and disabled by writing

a predefined sequence to the device. Writing to the device while protected can

be done by first writing the key sequence followed by the data.

MCU and Peripherals

MCU Port P4 Usage

MCU, D150 port 4 is used for baseband control.

Port Pin MCU pin Control Function Remark

P40 5 Display driver reset Active low

P41 6

P42 7 Call Led Control

P43 8 External RF Switch input

P44 9

System Module

P45 10

P46 11

P47 12 External accessory Supply Active low

voltage control

MCU Port PB Usage

MCU, D150 port B is used for baseband control.

Port Pin MCU pin Control Function Remark

PB0 77 Information of Sliding cover

position

PB1 76

PB2 79 External RF output control

PB3 80

Baseband A/D Converter Channels usage in N450 and D150

The auxiliary A/D converter channels inside RFI2, N450 are used by MCU to

measure battery voltage, charger voltage etc. The A/D converters are accessed

by the DSP, D152 via the ASIC, D151. The required resolution is 10 bit. The

scaling factor is created using 5% resistors and it is therefore a requirement to

have an alignment procedure in the production phase. Each resistor network is

supplied with a known input voltage and the measured value is used against

the theoretically calculated value. As a result of this operation standard 5% resistors can be used in the voltage scaling circuitry.

Original 12/97

Page 4–23

Page 24

NHK–6

After Sales

System Module

The A/D converter used in RFI2, N450 for the measurement are sigma–delta

type and the zero value is centered around 50 % of the supply voltage, 1.6V.

This means that the A/D converter reading is negative when the input voltage

to the converter is less than half of the supply voltage. In calculations the true

A/D reading is got by adding 800H to the read value modulo 4096.

The MCU has 4 10 bit A/D channels which are used in parallel to the channels

in N450. The MCU can measure charger voltage, battery size, battery temperature, and accessory detection by using it’s own converters.

Baseband N450 A/D Converter Channel Usage

Name: Usage: Input volt. range Remark

Chan 0 Battery voltage 5...9 V Battery voltage when

Chan 1 Charger voltage 5...25 V

Chan 2 Battery size indic. 0...3.2 V

Chan 3 Battery temperature 0...3.2 V

Technical Documentation

TX is active

Chan 4 System board temp. 0...3.2 V Not used

Chan 5 Accessory detection 0...3.2 V

Chan 6 0...3.2 V Not used

Chan 7 Battery voltage 5...9 V Battery volt. TX inactive

MCU Baseband A/D Converter Channel Usage

Name: Usage: Input volt. range Remark

Chan 0 Battery temperature 0...3.2 V

Chan 1 Charger voltage 5...25 V

Chan 2 Accessory detection 0...3.2 V

Chan 3 Battery size indicator0...3.2 V

Battery Voltage Measurement

The battery voltage is measured using RFI2, N450 A/D converter channel 0

and 7. The converter value supplied from channel 7 is measured when the

transmitter is inactive. This measurement gives the minimum battery voltage.

The value from channel 0 is measured when the transmitter is active. The battery voltage supplied to the A/D converter input is switched off when the baseband is in power off. The battery voltage measurement voltage is supplied by

PSCLD, N300 which performs scaling, the scaling factor is R1(R1+R2), and

switch off. The measurement voltage is filtered by a capacitor to achieve an average value that is not depending upon the current consumption behavior of the

baseband. To be able to measure the battery voltage during transmission pulse

the time constant must be short. The value for the filtering capacitor is set to 10

Page 4–24

Original 12/97

Page 25

After Sales

NHK–6

Technical Documentation

nF, C319. The scaling factor used to scale the battery voltage must be 1:3,

which means that 9V battery voltage will give 3V A/D converter input voltage.

The A/D converter value in decimal can be calculated using the following formula:

A/D = 1023 x R1 x U

where K is the scaling factor. K = R1/((R1+R2) x U

Charger Voltage Measurement

The charger voltage is measured to determine the type of charger used. Auxiliary A/D converter channel 1 is used for this purpose and MCU /D converter

channel 1. The input circuitry to the charger measurement A/D channel implements an LP filter. The input voltage must be scaled before it is fed to the A/D

converter input. Due to the high input voltage range, scaling is performed outside PSCLD, N300. The scaling factor required is 22/(22+100) = 0.18. The

charger voltage measurement switch is integrated into PSCLD, N300. Charger

voltage is not supplied to the A/D converter input in power off mode. This is

done to protect the A/D converter input in case power is switched off and the

charger remains connected to the baseband. The resistor values are different

since the scaling factor is larger.

/((R1+R2) x U

BAT

) = 1023 x U

ref

ref).

BAT

x K

System Module

Battery Size Resistor Measurement

The battery size, capacity is determined by measuring the voltage on the BSI

pin on the battery pack when the battery is attached to the phone. The auxiliary

channel 2 is used for this purpose. The BSI signal is pulled up on the base

band using a 47 kohm resistor and the resistor inside the battery pack is reflecting the capacity of the battery. There are two special cases to be detected by

the MCU. The first case is the Lithium battery. The Lithium battery has reserved

values in the battery size table. Lithium type batteries are all the same from

charging point of view. Lithium batteries are charged to a constant voltage and

charging is aborted when the predefined voltage is reached. The Lithium battery capacity is a function of the battery voltage. The battery voltage drops linearly as the battery is discharged. The other case that has to be handled is the

dummy battery. This battery is used for A/D converter field calibration at service

centers and together with a defined voltage on the BTEMP pin on the battery

pack to put the baseband into Local mode in production. Battery sizes below

143 mAh will be treated as dummy battery. The battery size A/D converter value can be calculated using the following formula:

A/D = RSI/(RSI+47 kohm) x 1023

where RSI is the value of the resistor inside the battery pack.

Original 12/97

Page 4–25

Page 26

NHK–6

After Sales

System Module

Battery Size and A/D Converter Value

Battery Type Battery pack resistor Capacity BSI volt. A/D conv value

Dummy 1 kΩ 2 % <143 mAh0.07 24 h (36)

Lithium type 1 68 kΩ 2 % 400 mAh 25 C (605)

standard battery

Lithium type 1 68 kΩ 2 % 900 mAh 25 C (605)

extended battery

Lithium type 2 82 kΩ 2 % 400 mAh 28 A (650)

Battery Temperature Measurement

The battery temperature is measured during charging. The BTEMP pin to the

battery is pulled up on baseband by a 47 kohm resistor to logic supply voltage,

3.2V. The voltage on the BTEMP pin is a function of the battery pack temperature. Auxiliary A/D channel 3 is used for this purpose. Inside the battery pack

there is a 47 kohm NTC resistor to ground. The A/D converter value can be calculated from the following formula:

Technical Documentation

A/D = RNTC/(RNTC+47 kohm) x 1023

where RNTC is the value of the NTC resistor inside the battery pack.

The relationship between different battery temperatures, BTEMP voltage and

A/D converter values are shown in the table below. Battery temperature is measured from –56 to 76 Centigrade. ( 9 HEX to 383 HEX)

A/D Converter Values for Different Battery Temperatures

Bat. temp.NTC value BTEMP voltage A/D conv. value

–25 745.60 k Ω 2.96 V 962

0 164.96 kΩ 2.45 V 796

25 47 kΩ 1.58 V 512

50 16.26 kΩ 0.81 V 263

70 7.78 kΩ 0.45 V 145

External Accessory Detection via XMIC/ID –line

Auxiliary A/D channel 4 is used to detect accessories connected to the system

connector using the XMIC/ID. To be able to determine which accessory has

been connected MCU measures the DC voltage on the XMIC/ID input. The accessory is detected in accordance with the CAP Accessory specifications. The

base band has a pull–up resistor network of 32 kohm to VA. The accessory has

a pull down. The A/D converter value can be calculated using the following formula:

Page 4–26

A/D = (ACCI+10 kohm)/(ACCI+32 kohm) x 1023 .

Original 12/97

Page 27

After Sales

NHK–6

Technical Documentation

where ACCI is the DC input impedance of the accessory device connected to

the system connector

The different values for acceptable accessories are given in the following

table.The values in the table are calculated using 5 % resistor values and power supply range 3–3.3 V. Due to that the pull up resistor in the XMIC line is divided into two resistors the voltage at the A/D converter input is different from

that on the XMIC.

Accessory Detection Voltage

Acc. type Acc. resistance Voltage on A/D converter A/D converter

IR Link 100 kΩ 2.46...2.63...2.79 853

Headset 47 kΩ 2.1...2.3...2.45 739

Compact 22 kΩ 1.7...1.9...2.05 607

HF

Keyboard Interface

System Module

channel 5 (min/typ/max) value(Dec)

The keypad matrix is located on a UI module Flex PCB and the interface to the

base band is by using connector X101. The power on key is also connected to

the PSCLD to switch power on. Due to the internal pull up inside PSCLD, N300

to a high voltage, a rectifier, V418 is required in the keypad matrix for the power

on keypad to prevent the high voltage to interfere with the keypad matrix.

Series resistors, R261–R264 are implemented in the Column output to reduce

the EMI radiation to the UI Flex. Capacitors C257–C260 reduces the EMC radiation and absorbs any ESD produced over an air gap to the keymat. As the serial display driver interface uses ROW5 for data transmission, series resistors

are needed to prevent keypad or double keypad pressing from interfering with

the display communication. In a similar way R265–R269 in the ROW lines reduces the EMI to the UI board. Capacitors C251–C256 implements a LP–filter

together with each resistor in the ROW line. The capacitors also absorbs ESD

pulses over an air gap to the keymat.

During idle when no keyboard activity is present, the MCU sets the column outputs to ”0” and enables the keyboard interrupt. An interrupt is generated when

a ROW input is pulled low. Each ROW input on the ASIC, D151 has an internal

pull–up. The keyboard interrupt starts up the MCU, and the MCU starts the

scanning procedure. As there are keypads to be detected outside the matrix,

the MCU sets all columns to ”1” and reads the ROW inputs if a logic ”0” is read

on any ROW this means that one of the 6 possible non matrix keypads has

been pressed. If the result was a ”1” on each ROW the MCU writes a ”0” on

each column consecutively while the rest of the column outputs are kept in tri–

state to allow dual keypad activation to be detected. After that the keyboard

scanning is completed and if no activity is found the MCU writes ”0” to all columns, enables the keyboard interrupt and enters sleep mode where the clock

to the MCU is stopped. A key press will again start up the MCU.

Original 12/97

Page 4–27

Page 28

NHK–6

After Sales

System Module

Keyboard and Display Light

The display and keyboard are illuminated by LED’s. The light is normally

switched on when a keypad is pressed. The rules for light switching are defined

in the SW UI specifications. The display and keyboard lights are controlled by

the MCU. The LED’s are connected two in series to reduce the power consumption. Due to the amount of LED’s required for the keyboard and display

light they are divided into two groups. Each group has it’s own control transistor. The LED switch transistor is connected as a constant current source, which

means that the current limiting resistor is put in the emitter circuit. This arrangement will reduce LED flickering depending upon battery voltage and momentary

power consumption of the phone. The LED’s are connected straight to the battery voltage. This connection allows two LED’s to connected in series. The battery voltage varies a lot depending upon if the battery is charged, full or empty.

The switching transistor circuitry is designed to improve this as mentioned earlier.

The light requirement is different for the display and the keyboard. This is one

of the reasons for splitting the LED control among three transistors. Each LED

group can now be set to different LED current, thus affecting the illumination.

The reason for splitting the LED control is the power dissipation in the control

transistor and the current limiting resistor. This is particular the problem during

charging when the battery voltage is high.

Technical Documentation

The LED transistor control lines are coming from PSCLD. The MCU controls

these lines by writing to PSCLD using the serial control bus. There are two LED

control lines provided by the PSCLD. The display and keyboard light controls

are connected to separate control lines. This means that the keyboard and display light can be controlled separately. The advantage of this is that the power

dissipation and heating of the phone can be reduced by only having the required lights switched on.

There is no PWM control on these PSCLD control lines to allow dimming of the

keyboard and display lights. These control outputs from PSCLD are low when

PSCLD exits reset, lights are off, and MCU then switches them on according to

the user settings or user actions.

Audio Control

The audio codec N200 is controlled by the MCU, D150. Digital audio is transferred on the CODECB(5:0). PCM data is clock at 512 kHz from the ASIC and

the ASIC also generates 8 kHz synchronization signal for the bus. Data is put

out on the bus at the rising edge of the clock and read in at the falling edge.

Data from the DSP, D152 to the audio codec, N200 is transmitted as a separate

signal from data transmitted from the audio codec, N200 to the DSP, D152. The

communication is full duplex synchronous. The transmission is started at the

falling edge of the synchronization pulse. 16 bits of data is transmitted after

each synchronization pulse.

Page 4–28

Original 12/97

Page 29

After Sales

NHK–6

Technical Documentation

The 512 kHz clock is generated form 13 MHz using a PLL type of approach,

which means that the output frequency is not 512 kHz at any moment. The frequency varies as the PLL adjusts the frequency. The average frequency is 512

kHz. The clock is not supplied to the codec when it is not needed. The clock is

controlled by both MCU and DSP. DTMF tones are generated by the audio codec and for that purposes the 512 kHz clock is needed. The MCU must switch

on the clock before the DTMF generation control data is transmitted on the serial control bus.

The serial control bus uses clock, data and chip select to address the device on

the bus. This interface is built in to the ASIC and the MCU writes the destination

and data to the ASIC registers. The serial communication is then initiated by

the ASIC. Data can be read form the audio codec, N200 via this bus.

Internal Audio

The bias for the internal microphone is generated from the PSCLD, N300 analog output, VA using a bias generator. The bias generation is designed in such

a way that common mode signals induced into the microphone capsule wires

are suppressed by the input amplifier in the audio codec. The bias generator is

controlled by the MCU to save power. The control signal is taken from the audio

codec, N200 output latch, pin 26, when the microphone is not used, in idle the

bias generator is switched off. The microphone amplifier gain is set by the MCU

to match with the used microphone, 35 dB. The microphone amplifier input to

the audio codec is a symmetrical input.

System Module

The microphone signal is connected to the baseband using filtering to prevent

EMC radiation and RF PA signal to interfere with the microphone signal. L201

and C201 forms the first part of this filter in main radio unit. R203 and C202

forms the second part of this filter. A similar filter is used in the negative signal

path of the microphone signal. R205 is connected in the ground path for the microphone bias current. R202 supplies the bias current to the microphone from

the generator circuitry R201, C200 and V200.

The earpiece amplifier used for the internal earpiece is of differential type and

is designed as a bridge amplifier to give the output swing for the required sound

pressure. Since the power supply is only 3V, a dynamic type ear piece has to

be used to achieve the sound pressure. This means that the ear piece is a low

impedance type and represents a significant load to the output amplifier. Series

inductors are implemented to prevent EMC radiation from the connection on

baseband to the earpiece. The same filter also prevents the PA RF field from

causing interference in the audio codec, N200 output stage to the earpiece.

The buzzer is controlled by the PWM output provided by the audio codec,

N200. Transistors V403in UI flex board acts as an amplifier and impedance

conversion for the low impedance buzzer. The buzzer is driven directly from the

battery voltage. As the buzzer is connected to the baseband via the keyboard,

the battery voltage provided by VBKEY and the buzzer driving signal BUZZER

are EMC protected. As the buzzer is a dynamic one, the impedance shows a

Original 12/97

Page 4–29

Page 30

NHK–6

After Sales

System Module

clear inductance. Therefore a free running diode V413 in UI flex is used to clip

the voltage spikes induced in the Buzzer line when the buzzer is switched off.

The buzzer frequency is determined by the internal setup of N200. The frequency is determined by the MCU via the serial control bus. The output level

can be adjusted by the PWM function which is attached to the buzzer output in

N200.

External Audio

The external microphone audio signal is applied to the baseband system connector and connected to the audio block using signals XMIC and SGND. In order to improve the external audio performance, the input circuitry is arranged in

a sort of dual ended. A wheatstone type of bridge configuration is created by

resistors R216, R217, R219 and R220. The signal is attenuated around 20 dB

to not cause distortion in the microphone amplifier. The microphone signal is

attenuated by resistors R216, R207 and R217. To allow the external earpiece

to be driven dual ended the external microphone signal ground is connected to

the negative output of the external audio earpiece amplifier. This means that

with reference to audio codec, N200 ground there is a signal level on the SGND

line. This arrangement requires that the external microphone amplifier supplies

the signal on the SGND line to the XMIC line. With this arrangement the differential voltage over R207 caused by the signal in the SGND line is canceled.

There is however a common mode component which is relatively high presented at both the external microphone input pins at the audio codec input, pins

31 and 30. The microphone amplifier has a good common mode rejection ratio

but a slight phase shift in the signals will remove the balance. To compensate

for this the signal from the external earpiece amplifier positive output, which

also feeds the external audio output from the baseband is feed to the remaining

resistors in the bridge, R219 and R220. This arrangement will attenuate the

common mode signal presented to the microphone amplifier caused by the audio signal in the SGND line. Since the positive output from the audio codec,

XEAR signal introduces a DC signal to the microphone amplifier the DC signal

on the XMIC and SGND lines are blocked by capacitors C218 and C220.

Technical Documentation

Page 4–30

XMIC

R216 R219

Microphone +

R207

Microphone –

R217

SGND

The external audio output is the XEAR signal on the system connector pin. The

XEAR signal is taken from audio codec N200 pin 3. The output impedance is

increased to 47 ohms by resistor R214. This resistor prevents the output ampli-

R220

XEAR

XEAR

Original 12/97

Page 31

After Sales

NHK–6

Technical Documentation

fier from being short circuited even if the pin at the system connector is short

circuited. The DC voltage at the XEAR output is used to control the mute function of the accessory. When internal audio is selected the XEAR amplifier in

N200 is switched off and the DC voltage at the output on pin 2 is removed. External audio output level is adjusted by the variable gain amplifier in the N200

by MCU via the serial control bus from the ASIC, D151. L104 and C102 is EMC

protection for the XEAR signal at the system connector. This filter also prevents

RF signals induced in the external cables from creating interference in the audio codec output stage.

DSP

The DSP, D152 executes code from the internal ROM. The baseband also provides external fast memories for the DSP, D404 and D405. The DSP is capable

of addressing 64 kword of memory. The memory area is divided into a code

execution area and a data storage area. The code execution area is located at

address 8000H–FFFFH. The external memories are arranged in such a way

that the DSP can access the external memories both as data storage and code

execution. The memory chip select is taken from the memory access strobe

signal from the DSP. This means that the memory is active during any memory

access. The memories are connected in such a way that the write control is CE

controlled write. This means that both the write signal and the output enable

signal are active at the same time. This implementation is required since the

DSP supports only one signal for write/read control.

System Module

The DSP is operating form the 13 MHz clock. In order to get the required performance the frequency is internally increased by a PLL by a factor of 3. The

PLL requires a settling time of 50 us after that the clock has been supplied before proper operation is established. This settling counter is inside the DSP although the ASIC, D151 contains a counter that will delay the interrupt with a

programmable amount of clock cycles before the interrupt causing the clock to

be switched on is presented to the DSP.

The DSP has full control over the clock supplied to it. When the DSP is to enter

the sleep mode the clock is switched off by setting a bit in the ASIC register.

The clock is automatically switched on when an interrupt is generated.

DSP Interrupts

The DSP supports 4 external interrupts. Three interrupts are used. The ASIC,

D151 generates two of the interrupts. One interrupt is generated by RFI2, N450

auxiliary A/D converter. This interrupt is generated when a baseband measurement A/D conversion is completed. The interrupts to the DSP are active low.

DSP Serial Communications Interface

The DSP contains two synchronous serial communications interface. One of

the interfaces are used to communicate with the audio codec, N200.

The 512 kHz clock required for the data transfer is provided by D151 as well as

Original 12/97

Page 4–31

Page 32

NHK–6

After Sales

System Module

the 8 kHz synchronization signal. Data is transferred on to lines, RX and TX

creating a full duplex connection. Data is presented on the bus on the first rising edge of the clock after the falling edge of the synchronization pulse. Data is

read in by each device on the falling edge of clock. Data transfer is 16 bits after

each synchronization pulse.

The DSP, D152 has control over the clock provided to the audio codec. The

DSP can switch on the clock to start the communication and switch it off when it

is not needed. This clock is also under control of MCU, D150 as described in

the previous section Audio Control.

The second serial interface is used for debugging and Digital Audio Interface.

The ASIC provides the clock and the synchronization for this serial interface as

well since the two serial interfaces need to be operated synchronously in case

of DAI measurements.

RFI2, N450 Operation

The RFI2, N450 contains the A/D and D/A converters to perform the A/D conversion from the received signal and the D/A converters to perform the conversion for the modulated signal to be supplied to the transmitter section. In addition to this the RFI2 chip also contains the D/A converter for providing AFC

voltage to the RF section. This AFC voltage controls the frequency of the 13

MHz VCO which supplies the system clock to the baseband. The RFI2, N450

also contains the D/A converter to control the RF transmitter power control. The

power control values are stored in the ASIC, D151 and at the start of each

transmission the values are read from the ASIC, D151 to the D/A converter producing the power control pulse. This D/A converter is used during the reception

to provide AGC for the receiver RF parts.

Technical Documentation