Page 1

Programmes After Market Services

NPE-4 Series Cellular Phones

2 - Broadband System

Original ãNokia Corporation. Page 2-1

Page 2

NPE-4

2 - Broadband System PAMS Technical Documentation

Table of Contents

Description Page No.

Introduction ......................................................................................................................................

Abbreviations .................................................................................................................................... 5

Environmental specification ......................................................................................................... 7

Absolute maximum ratings .................................................................................................... 7

Normal and extreme voltages ............................................................................................... 7

Temeperature conditions ........................................................................................................8

Humidity and water resistance ............................................................................................. 8

Vibration and bump ................................................................................................................. 8

EMC / ESD immunity ............................................................................................................... 8

Technical specifications ................................................................................................................. 8

UEM .............................................................................................................................................. 8

Reset sequence .................................................................................................................. 8

No supply ............................................................................................................................. 10

Backup .................................................................................................................................. 11

Power off ............................................................................................................................ 11

Reset .................................................................................................................................... 11

Power on ............................................................................................................................. 11

Sleep .................................................................................................................................... 11

Protection mode ...............................................................................................................12

DC characteristics ................................................................................................................... 12

Charging .................................................................................................................................... 15

Battery ........................................................................................................................................ 18

UPP (Universal Phone Processor) ........................................................................................ 19

Bluetooth ................................................................................................................................... 21

Ul .................................................................................................................................................. 21

LCD cell ............................................................................................................................... 21

LCD Backlight .................................................................................................................... 23

Keyboard light ................................................................................................................... 24

LED driver circuit .............................................................................................................. 24

Vibra .................................................................................................................................... 24

Buzzer ................................................................................................................................. 24

Keypad ................................................................................................................................ 25

IR-module .................................................................................................................................. 25

SIM .............................................................................................................................................. 25

Memory description ....................................................................................................................... 26

Read cycle ................................................................................................................................. 27

Write cycle ................................................................................................................................ 27

Power saving signal (PS) ........................................................................................................ 28

Memory block ........................................................................................................................... 30

Block locking ............................................................................................................................ 30

Read while write (RWW) ....................................................................................................... 31

Burst mode ................................................................................................................................ 32

5

Page 2-2 ãNokia Corporation. Original

Page 3

NPE-4

PAMS Technical Documentation 2 - Broadband System

Description Page No.

Flash programming ................................................................................................................. 32

MCU boot .................................................................................................................................. 33

Flash identifiers ....................................................................................................................... 33

First word ........................................................................................................................... 33

Second word ...................................................................................................................... 33

Third word .......................................................................................................................... 33

Fourth word ....................................................................................................................... 33

Fifth word ............................................................................................................................ 34

Absolute maximum ratings (AMD 64bit) ........................................................................... 34

Absolute maximum ratings (INTEL 64bit) .......................................................................... 34

HW Interfaces .................................................................................................................................. 35

Keypad interface ...................................................................................................................... 35

LCD interface ............................................................................................................................ 36

SIM interface ............................................................................................................................ 37

Ostrich ........................................................................................................................................ 38

JTAG interface .......................................................................................................................... 38

BT module interface ................................................................................................................ 39

SW interface ...................................................................................................................... 39

BT102 flash programming ............................................................................................. 39

HW interface ..................................................................................................................... 40

Baseband - RF interface ........................................................................................................ 42

Digital signals ................................................................................................................... 42

Analogue signals ..............................................................................................................44

Voltage supplies and references .................................................................................. 48

Accessory interfaces ............................................................................................................... 49

MBus ........................................................................................................................................... 49

FBus ............................................................................................................................................. 50

Baseband EMC strategy ................................................................................................................ 50

EMC design ............................................................................................................................... 51

SIM and keypad ................................................................................................................52

ESD test ...................................................................................................................................... 52

Conducted and radiated immunity tests ............................................................................ 53

TDMA noise ............................................................................................................................... 53

Baseband testing ............................................................................................................................ 53

Test Points .......................................................................................................................................... 53

List of Figures

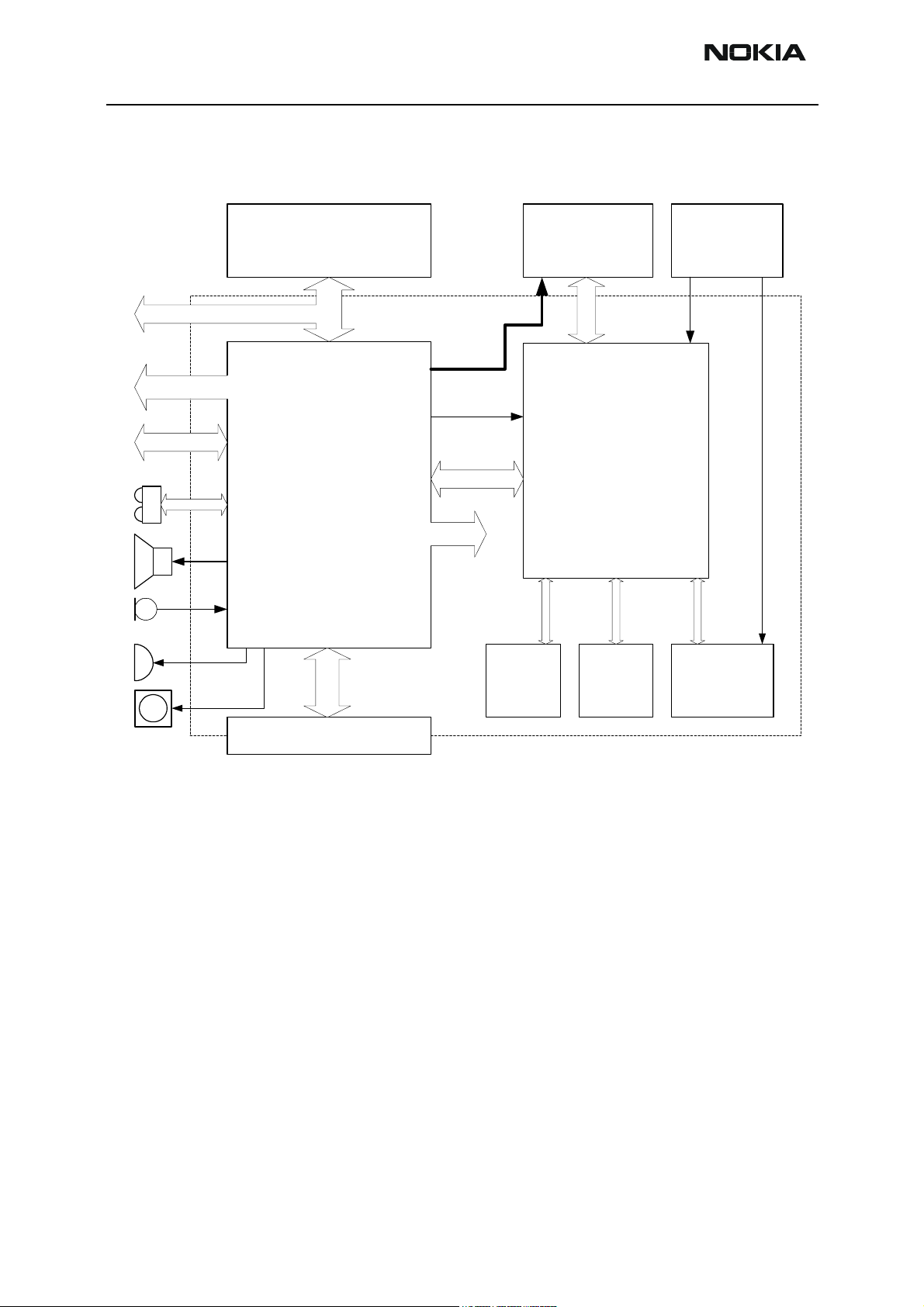

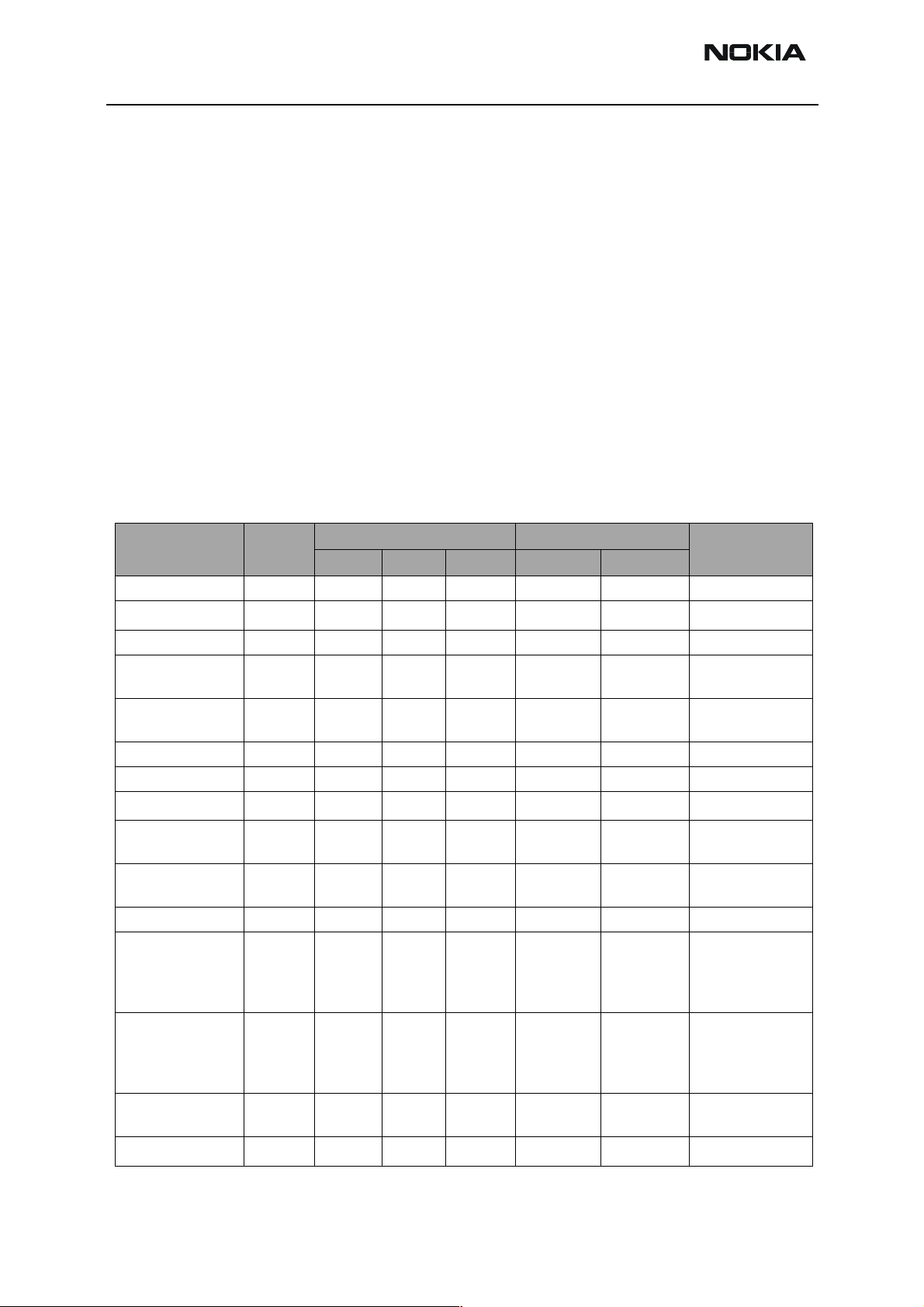

Figure 1 NPE-4 Baseband block diagram ............................................................................ 6

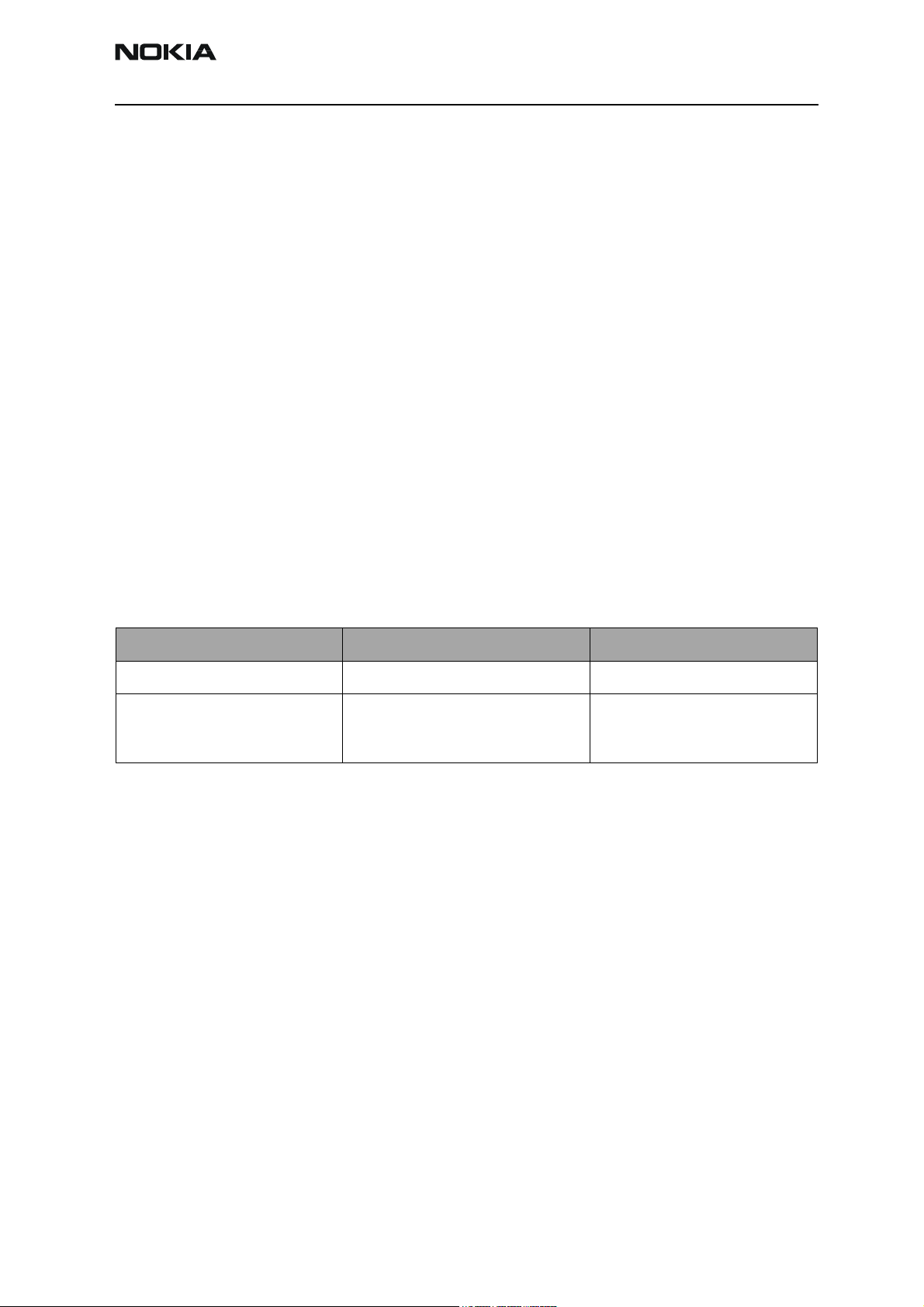

Figure 2 UEM state disgram .................................................................................................... 9

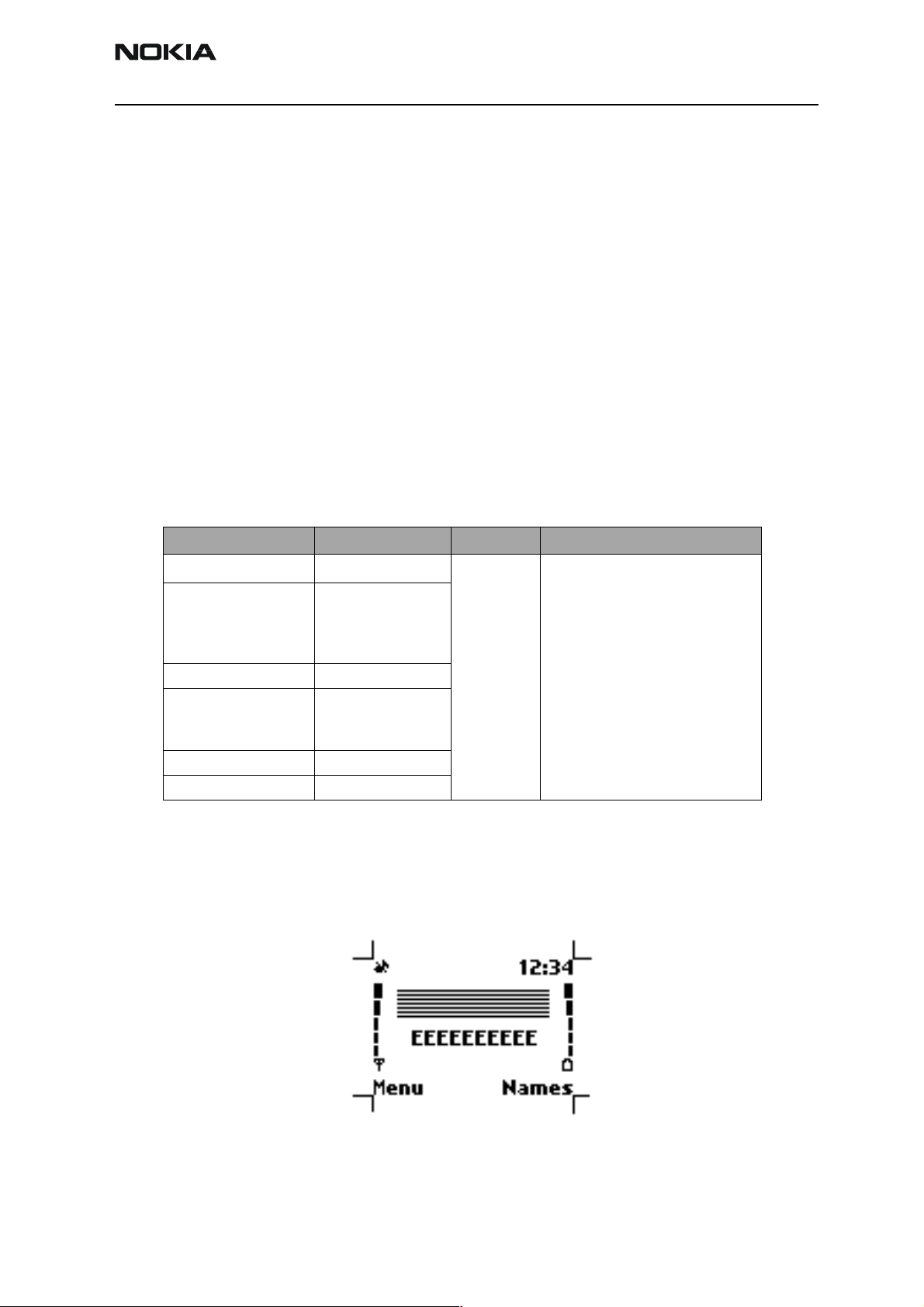

Figure 3 LCD worst case test image ...................................................................................... 13

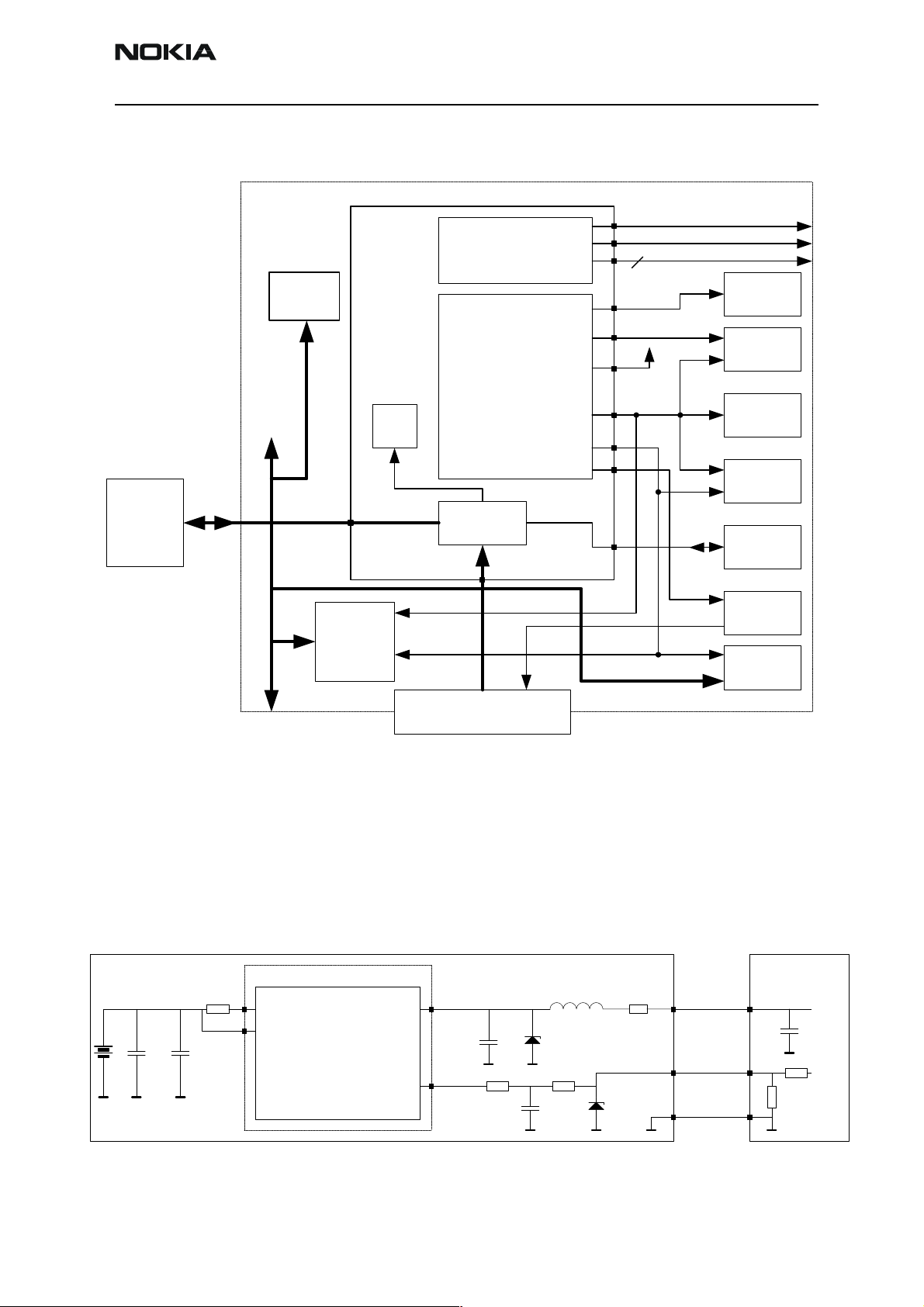

Figure 4 Baseband power distribution ................................................................................. 15

Figure 5 Charging configuration ............................................................................................ 15

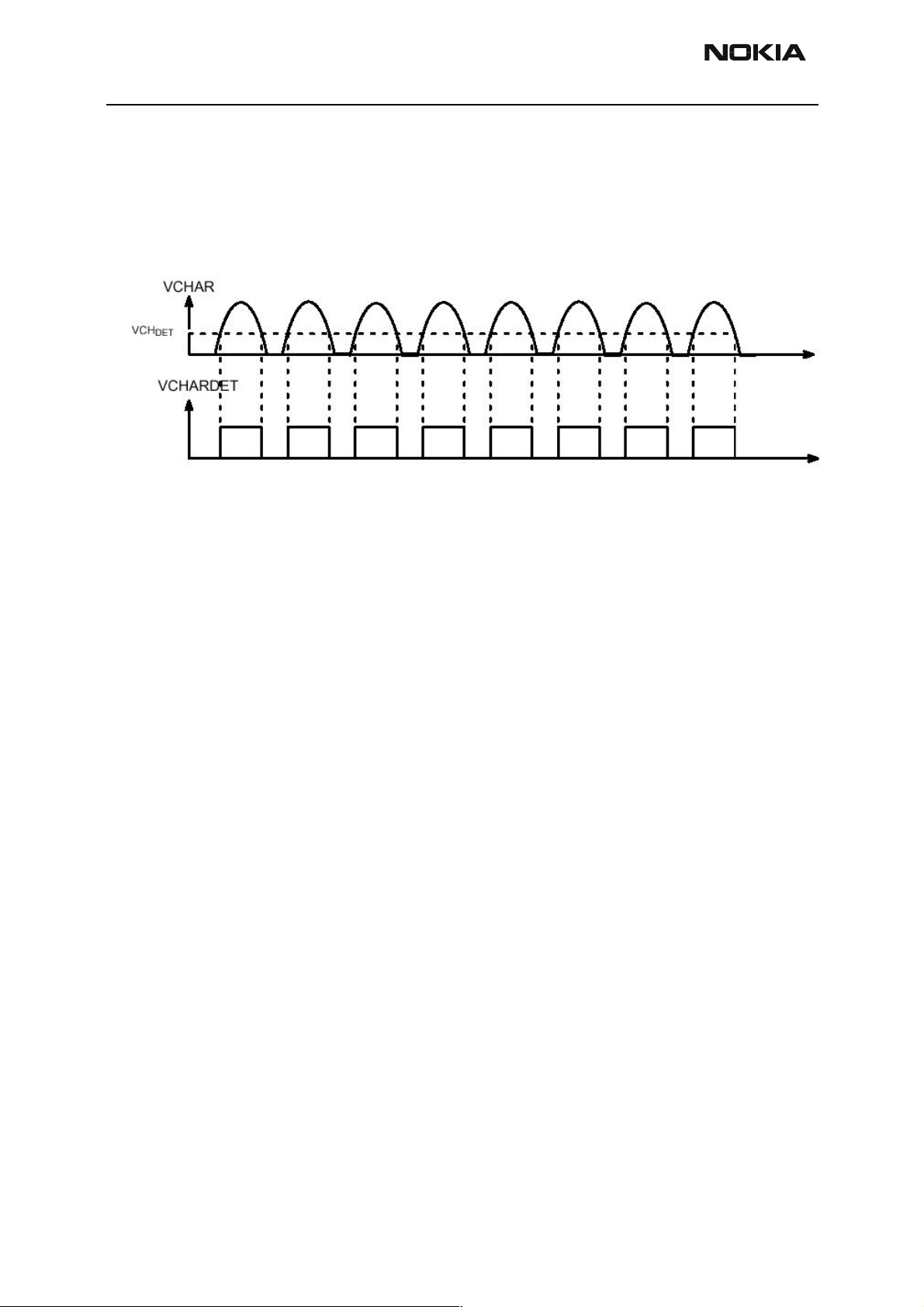

Figure 6 Detection of charger ................................................................................................. 16

Original ãNokia Corporation. Page 2-3

Page 4

NPE-4

2 - Broadband System PAMS Technical Documentation

Description Page No.

List of Figures (continued)

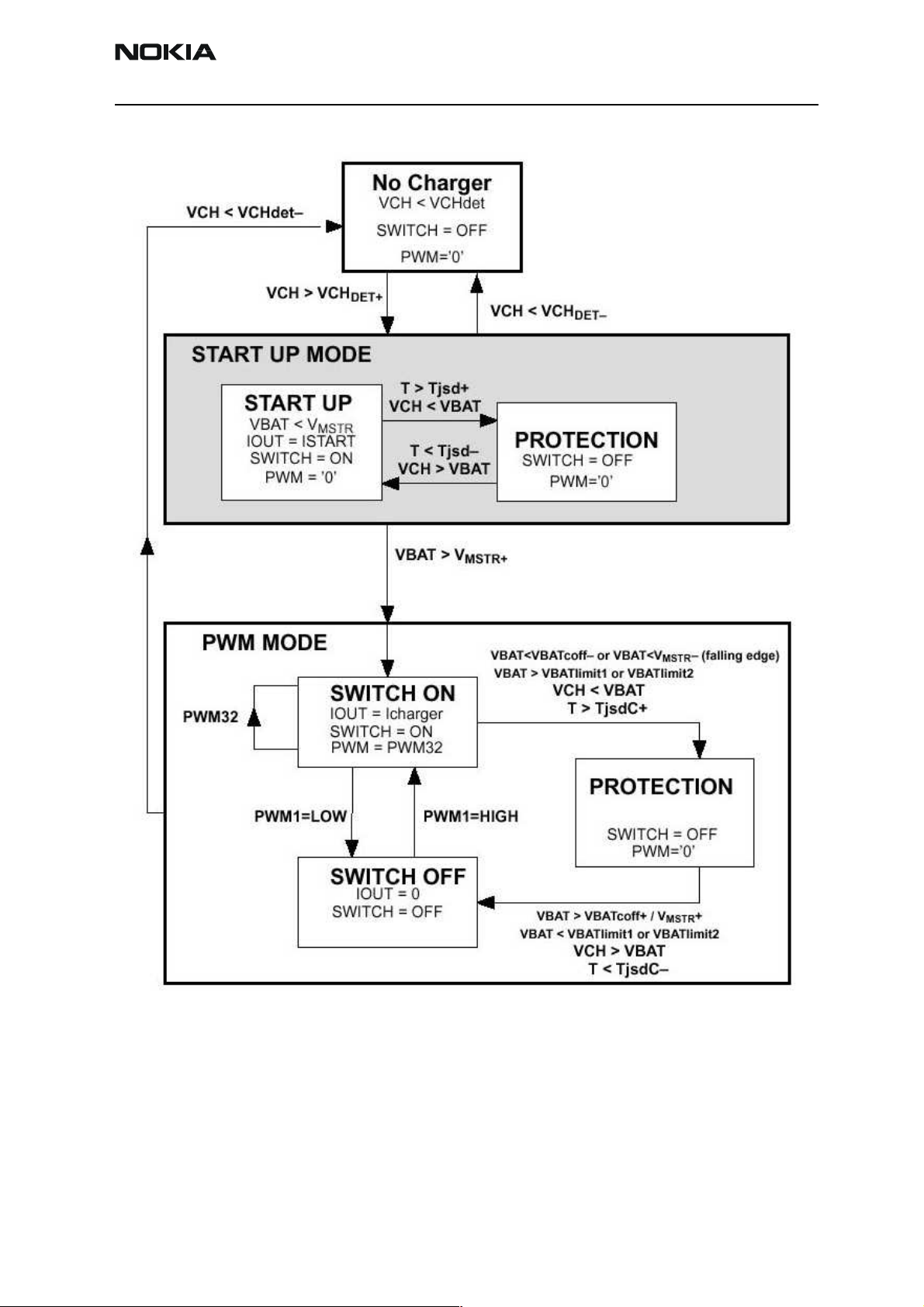

Figure 7 UEM charging state diagram, PWM mode only ................................................ 17

Figure 8 Charging scenario where the battery is abruptly removed ............................ 18

Figure 9 Mechanical layout of DCT-3 battery .................................................................... 19

Figure 10 UPP architecture ........................................................................................................ 20

Figure 11 Complete overview of LCD module ....................................................................... 22

Figure 12 LCD module ................................................................................................................. 23

Figure 13 LED driver circuit for display and key light ......................................................... 24

Figure 14 NPE-4 IR connectivity ............................................................................................. 25

Figure 15 UPP, UEM and SIM connections ............................................................................ 26

Figure 16 Basic reading (random access) ............................................................................... 27

Figure 17 Write waveform (random access) ......................................................................... 28

Figure 18 The data is compared by using an XOR-function ............................................. 29

Figure 19 The comparison shows more unequal bits .......................................................... 30

Figure 20 Burst mode reading from the flash ....................................................................... 32

Figure 21 NPE-4 keypad ............................................................................................................ 35

Figure 22 Placement of SIM pins (phone bottom view) ..................................................... 37

Figure 23 SW interface diagram ............................................................................................... 39

Figure 24 BT102 Flash programming ...................................................................................... 39

Figure 25 BT102 HW interface .................................................................................................. 40

Figure 26 XEAR connection .......................................................................................................51

Figure 27 XMIC connection ....................................................................................................... 52

List of Tables

Table 1 Absolute max. ratings ............................................................................................... 7

Table 2 Temperature conditions for NPE-4 ...................................................................... 8

Table 3 UEM regulator outputs and state in SLEEP ........................................................ 12

Table 4 NPE-4 current consumption from VFLASH during SLEEP mode .................. 13

Table 5 LCD current consumption ........................................................................................ 23

Table 6 Absolute max. ratings for AMD 64Mbit .............................................................. 34

Table 7 Absolute max. ratings for Intel 64Mbit ............................................................... 34

Table 8 LCD module pin-out to PWB .................................................................................. 36

Table 9 SIM connector interface .......................................................................................... 37

Table 10 Ostrich interface ........................................................................................................ 38

Table 11 JTAG interface levels ................................................................................................. 38

Table 12 BT - BB interface description ................................................................................. 40

Table 13 Digital signals ............................................................................................................. 43

Table 14 Analoge signals .......................................................................................................... 44

Table 15 Regulators and references ....................................................................................... 48

Table 16 MBus interface .......................................................................................................... 50

Table 17 FBus interface ............................................................................................................ 50

Page 2-4 ãNokia Corporation. Original

Page 5

NPE-4

PAMS Technical Documentation 2 - Broadband System

Introduction

This Chapter specifies the baseband module for the NPE-4 program. The baseband module includes the baseband engine chipset, The UI components and the acoustical parts

for the transceiver.

NPE-4 is a hand-portable GSM900/GSM1800 phone for the classic segment, having the

DCT4 generation baseband- and RF circuitry. The key drivers for this product are GPRS

data transmission and short time to market.

The mechanical solution is based on the NPE-3 phone, modified with a new A-cover

design. The acoustical design is very similar to that implemented in NPE-3.

NPE-4 is having the DCT3 system connector and supports accordingly most DCT3 accessories. The battery interface is the one known from DCT3 phones and NPE-4 will support

both Nickel- and Lithium batteries.

New features in NPE-4 project is Bluetooth wireless data and audio connection and

GPRS for TCP/IP protocol data transmission.

Abbreviations

BSI Battery Size Indicator

NO_SUPPLY UEM state where UEM has no supply what so ever

VBAT Main battery voltage

V

VBACK Backup battery voltage

V_BU

BACK_UP UEM state where UEM has backup voltage

RESET UEM state where regulators are enabled

RTC UEM internal Real Time Clock

VRTC Regulator voltage for RTC

PWR_OFF UEM state where phone is off

SLEEP UEM power saving state controlled by UPP

SLEEPX SLEEP control signal from UPP

PWRONX Signal from power on key. '1' = key pressed.

VCHAR Charger input voltage

MSTR+

COFF+

, V

MSTR-

, V_BU

COFF-

Master Reset threshold level (2.1 V / 1.9 V)

Backup battery threshold level (3.1 V / 2.8 V)

VCHAR

DET

Charger detection threshold level

UEM Universal Energy Management

UPP Universal Phone Processor

IMD In-Mould Decoration

Original ãNokia Corporation. Page 2-5

Page 6

NPE-4

2 - Broadband System PAMS Technical Documentation

Technical Summary

PA Supply

RF Supplies

RF RX/TX

IRDA

EAR

MIC

BUZZO

VIBRA

M

Battery

UEM

Baseband

DLIGHT

KLIGHT

SLEEPCLK

32kHz

BB

Supplies

MBus/FBus

External Audio

Charger connection

CBUS/

DBUS

UI

UPP

MEMADDASIMIF

SIM FLASH

13MHz

HAGAR

26MHz

CBUS

USART

Bluetooth

DCT3 System connector

Figure 1 NPE-4 baseband block diagram

A draft block diagram is shown in Figure 1 NPE-4 baseband block diagram.

The baseband module contains 2 ASICs namely the Universal Energy Management (UEM)

and the Universal Phone Processor (UPP). The baseband module furthermore contains the

Bluetooth module. The baseband is based on the DCT4 engine program.

The UEM supplies both the baseband module as well as the RF module with a series of

voltage regulators. The RF module is supplied with regulated voltages 4.75 V and 2.78 V

and the baseband module with 2.78 V and 1.80 V. The UEM is furthermore supplying the

baseband SIM interface with a programmable voltage of either 1.8 V or 3.0 V and the

core of the UPP is supplied with a programmable voltage of 1.0 V, 1.3 V, 1.5 V or 1.8 V.

The UEM contains a series of PWM sourced drivers. The individual PWM signals are generated internally within the digital part of the UEM and distributed to the drivers. The

Page 2-6 ãNokia Corporation. Original

Page 7

NPE-4

PAMS Technical Documentation 2 - Broadband System

buzzer driver receives a PWM signal where both frequency and duty-cycle are pre-set by

register writings. For the vibra, a set of frequencies can be chosen. The frequencies are 64

Hz, 128 Hz, 258 Hz and 520 Hz and the duty cycle 2.9 % to 96.9 %. LCD and keyboard

light LED drivers receive a PWM signal of 128 Hz where the duty-cycle can be programmed by setting a 4-bit register.

The UEM also contains an IR driver supporting 9600 bps to 1152 kbps, semi duplex. This

driver works as a level shifter on the RX and TX lines to and from the UPP.

The UEM contains a real-time clock sliced down from the 32768 Hz crystal oscillator. The

32768 Hz clock is fed to the UPP as a sleep clock.

The communication between the UEM and the UPP is done on the bi-directional CBUS

and DBus. The CBUS is controlled by the MCU and can operate at a speed of maximum 1

MHz. The DBus is controlled by the DSP and can operate at a maximum speed of 13 MHz.

Both processors are located in the UPP.

Environmental Specifications

Absolute maximum ratings

Table 1: Absolute maximum ratings

Parameter Rating Remarks

Supply voltage, VBAT -0.3 V - 5.5 VDC Supply voltage for UEM

Charger input voltage, VCH -0.3 V - 16 VDC Conditions set by UEM. Input

clamped @16 VDC.

, Hardware cut-off voltage)

, Upper charger limit)

Normal and extreme voltages

Nominal voltage: 3.6 V (VBAT, Main battery voltage)

Lower extreme voltage: 2.9 V (V

Higher extreme voltage 5.4 V (VBAT

-0.3 – 20 VDC

pk

COFF-

LIM2+

Conditions set by UEM.

Minimum guarantied

operating voltage 3.04 V (DCT4 Engine minimum cut-off voltage)

Original ãNokia Corporation. Page 2-7

Page 8

NPE-4

2 - Broadband System PAMS Technical Documentation

Temperature Conditions

Table 2: Temperature conditions for NPE-4

Environmental condition Ambient temperature Remarks

Normal operation

Reduced performance

No operation or storage

Long term storage

conditions

-25 ° C … +55 °C

+55 °C … +70 °C

-40 °C > T > 85 °C

Humidity and water resistance

The baseband module will comply with the SPR4 Operating Conditions.

Vibration and bump

The baseband module will comply with the SPR3 Mechanical Functionality.

EMC / ESD immunity

The baseband module will comply with the SPR4 Operating Conditions. See also baseband EMC strategy in section Baseband EMC Strategy on page Baseband EMC Strategy.

Technical Specifications

0 °C … +40 °C

Specifications fulfilled

Operational for short periods only

No storage. An attempt to operate may

damage the phone permanently

Condition is without battery

The following chapters describe the NPE-4 baseband module in overview. If further information is needed, check with the references at the end of the Specification section References and/or with references mentioned in the individual chapters.

UEM

The UEM is one of the two ASICs in the baseband module.

Reset sequence

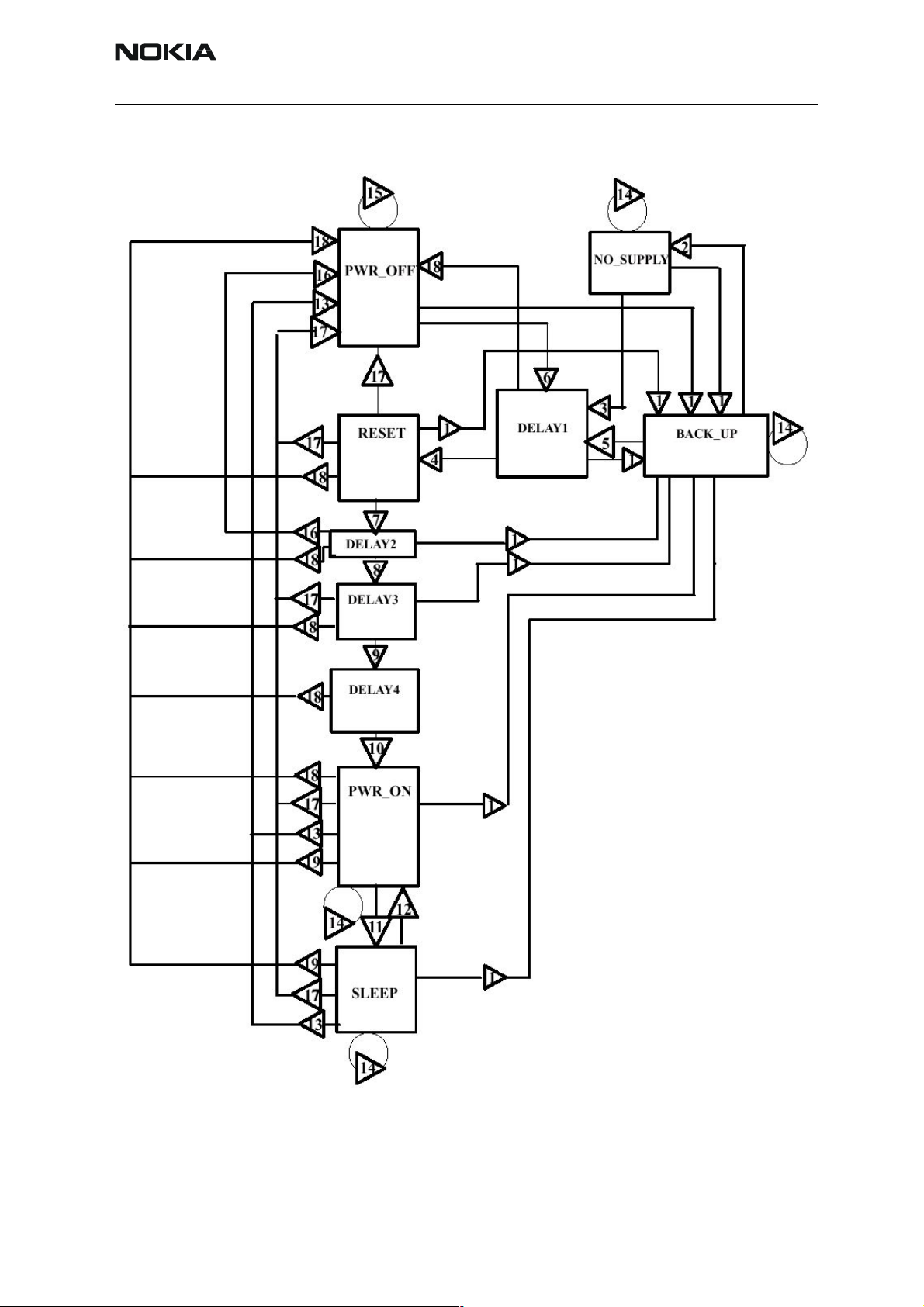

The functional behaviour of the UEM can be divided into 7 different states. Since the

UEM controls the regulated power distribution of the phone, each of these states affects

the general functionality of the phone:

• No supply

•Backup

•Power off

•Reset

•Power on

•Sleep

•Protection

Page 2-8 ãNokia Corporation. Original

Page 9

NPE-4

PAMS Technical Documentation 2 - Broadband System

Figure 2 UEM state diagram

Original ãNokia Corporation. Page 2-9

Page 10

NPE-4

2 - Broadband System PAMS Technical Documentation

The text below explains the state diagram. The symbol 'ä' means that the voltage rises

and 'æ' that the voltage drops. '®' Means the result of the conditions set on the left

most side.

VBAT < V

VBAT < V

VBAT ä V

VBAT > V

VBAT ä V

and VBACK > V_BU

MSTR

and VBACK < V_BU

MSTR

. VBACK < V_BU

MSTR+

. DELAY1 elapses ® Go to RESET

MSTR

. VBACK > V_BU

MSTR+

COFF

COFF

PWRONX = '0' or VCHAR ä VCHAR

VBAT > V

® Go to DELAY2

COFF+

DELAY2 elapses ® Go to DELAY3

VBAT > C

. DELAY3 elapses ® Go to DELAY4

OFF+

DELAY4 elapses ® Go to PWR_ON

SLEEPX = '0' ® Go to SLEEP

SLEEPX = '1' ® Go to PWR_ON

® Go to BACK_UP

COFF

® Go to NO_SUPPLY

COFF

® Go to DELAY1

® Go to DELAY1

or ALARM = '1' ® Go to DELAY1

DET+

VBAT æ V

No change

VBAT > V

PWRONX ä detection during DELAY2 ® Go to PWR_OFF

Watchdog elapses (approx. 100 ms) ® Go to PWR_OFF

Thermal shutdown ® Go to PWR_OFF

PwrKeyWatchdog (4 sec.) elapses ® Go to PWR_OFF

The different states of the UEM are explained further below:

No supply

In the NO_SUPPLY mode the UEM has no supply voltage (VBAT < V

V_BU

tery is either disconnected or both discharged to a low voltage level.

The UEM will recover from NO_SUPPLY into RESET mode if the VBAT voltage level rises

above the V

and VBAT > V

COFF-

® Stay in PWR_OFF

MSTR

). This mode is due to the fact, that both the main battery and the backup bat-

COFF-

level by either reconnecting the main battery or charge it to such level.

MSTR+

® Go to PWR_OFF

MSTR-

and VBACK <

MSTR

Page 2-10 ãNokia Corporation. Original

Page 11

NPE-4

PAMS Technical Documentation 2 - Broadband System

Backup

In BACK_UP mode the main battery is either disconnected or has a low voltage level

(VBAT < V

and VBACK > V_BU

MSTR-

COFF+

).

The regulator VRTC that supplies the real time clock is disabled in BACK_UP mode.

Instead the unregulated backup battery voltage VBACK supplies the output of the VRTC.

All other regulators are disabled and the phone has no functionality.

The UEM will recover from BACK_UP mode into RESET mode if VBAT rises above V

Power off

In order for the UEM to be in PWR_OFF mode, it must have supply voltage (VBAT >

V

The regulator VRTC regulator is enabled and supplying the RTC within the UEM. The UEM

will enter RESET mode after a 20 ms delay whenever one of the below listed conditions is

logically true:

The UEM will enter PWR_OFF from all other modes except NO_SUPPLY and BACK_UP if

the internal watchdog elapses.

Reset

).

MSTR+

• The power button is activated

• Charger connection is detected

• RTC alarm is detected

MSTR+

.

When the UEM enters RESET mode from PWR_OFF mode the watchdog is enabled. If the

VBAT fails to rise above the power-up voltage level V

elapses, the UEM will enter PWR_OFF mode. Otherwise after a 200 ms delay the regulator VFLASH1 will be enabled and after a additional delay of 500 ms the regulators VANA,

VIO, VCORE and VR3 will be enabled. All other regulators i.e. VFLASH2, VSIM, VR1, VR2

and VR4 – VR7 are software controlled and disabled by default. After an additional delay

of 20 ms the UEM enters PWR_ON mode.

Power on

In PWR_ON the UEM is fully functional in the sense that all internal circuits is powered

up or can be by means of software. The UEM will enter PWR_OFF mode if VBAT drops

below V

PWR_OFF mode if either of the watchdogs Operational State Machine (approx. 100 ms),

Security (32 sec.) or Power Key (4 sec.) elapses or if any of the regulators triggers the

thermal protection circuitry

Sleep

The UEM can be forced into SLEEP mode by the UPP by setting the input SLEEPX low for

more than 60 ms. This state is entered when the external UPP activity is low (phone in

(3.1 V) before the watchdog

COFF+

for a period of time longer than 5 ms. The UEM will furthermore enter

COOF-

Original ãNokia Corporation. Page 2-11

Page 12

NPE-4

2 - Broadband System PAMS Technical Documentation

sleep) and thereby lowering the internal current consumption of the UEM. The regulator

VANA is disabled and VR1 – VR7 are either disabled or in low quiescent mode.

From SLEEP the UEM enters PWR_ON if SLEEPX goes high, PWR_OFF mode if watchdog

elapses or BACK_UP mode if VBAT drops below V

MSTR-

.

Protection mode

The UEM has two separate protection limits for over temperature conditions, one for the

charging switch and one for the regulators. The temperature circuitry measures the onchip temperature. In case of charging over temperature, the circuit turns the charging

switch off. In case of over temperature in any of the regulators, the UEM powers off.

DC characteristics

The figures in the following table reflect the specifications of the voltage and current

regulators within the UEM.

Table 3: UEM regulator outputs and state in sleep

Regulator Tar get Output Voltage [V] Output Current [mA]

Min Typ Max Min Max

VR1A, VR1B RF 4.6 4.75 4.9 0 10 Off

6

VR2

VR3 RF 2.70 2.78 2.86 0.1 20 Off

2

VR4

VR5, VR6

VR7 RF 2.70 2.78 2.86 0.1 45 Off

VrefRF01 RF 1.334 1.35 1.366 - 0.1 On

VrefRF02

VIO

VSIM

VANA BB 2.70 2.78 2.86 0.005 80 Off

VCORE

VFLASH1 BB 2.70 2.78 2.86 0.005

VFLASH2

2

1

2

2

3

5

RF 2.70 2.78 2.86 0.1 100 Off or Low Iq

RF 2.70 2.78 2.86 0.1 50

0.1

RF 2.70 2.78 2.86 0.1 50

0.1

RF 1.323 1.35 1.377 - 0.1 On or Off

BB 1.72 1.8 1.88 0.005

0.005

BB 1.745

2.91

BB 1.000

1.235

1.425

1.710

0.974

1.215

1.410

1.692

BB 2.70 2.78 2.86 0.005 40 On or Off

1.8

3.0

1.053

1.3

1.5

1.8

1.053

1.3

1.5

1.8

1.855

3.09

1.106

1.365

1.575

1.890

1.132

1.365

1.575

1.890

0.005

0.005

0.005

0.005

0.005

0.005

70

85

100

120

0.005

150

0.500

25

0.500

70

85

100

120

200

200

200

200

70

1.5

UEMSLX = '0'

Off

Off

Low Iq

Low Iq

Low Iq

Low Iq

4

Page 2-12 ãNokia Corporation. Original

Page 13

NPE-4

PAMS Technical Documentation 2 - Broadband System

1) Controlled by MCU writing to UEM references register.

2) The second current value indicates the maximum possible output current of the

regulator when in low quiescent mode.

3) The output voltages are split into two different current categories. The upper part

is the lower range of output current, and the lower part is the higher range of

output current.

4) UEMSLX is slave to SleepX from the UPP. Sets the UEM into sleep mode.

5) Condition in sleep-mode depends on MCU writings to UEM regulator registers

solely.

6) Condition in sleep-mode depends on DSP writings to UEM register.

Due to the low output current from the VFLASH1 regulator during sleep, the following

table with estimated current consumption drawn from the regulator in sleep mode was

made.

Table 4: NPE-4 current consumption from VFLASH1 during Sleep mode

Consumer Max current

1

LCD

Audio area

- XMIC

- XEAR

- DLR-3P

Bluetooth 8

UEM

- 2 x slow ADC

- BSI

IR 5

Total 482

376 mA All figures are estimates @25 °C

60

1

1

2

29

Unit

Note

1) Maximum current measured on 10 samples.

The current consumed by the LCD has been measured by vendor using worst case normal

mode displayed image as shown in Figure 3.

Figure 3 LCD worst case test image

Original ãNokia Corporation. Page 2-13

Page 14

NPE-4

2 - Broadband System PAMS Technical Documentation

Under normal conditions, the battery powers the baseband module. The battery voltage

VBAT is regulated by individual regulators located within the UEM. These regulators supply the different parts of the phone. 8 regulators are dedicated to the RF module of the

phone, and 6 to the baseband module.

The VSIM regulator is able to deliver both 1.8 and 3.0 Vdc and thus supporting two different SIM technologies. A register internally in the UEM controls the output of VSIM

and can be written to by the MCU via the CBUS. The regulator VCORE is likewise adjustable and controlled by register writings by the MCU. VCORE supplies the core of the UPP

and can be adjusted on the fly by the MCU if DSP capacity is inadequate. Higher VCORE

supply (1.8 V) results in faster core operations in the UPP.

The regulator VFLASH2 supplies audio circuitry and is controlled by the MCU

The regulators VANA, VFLASH1 and VIO are solely controlled by the UEM and cannot be

en-/disabled by MCU writings. Furthermore, VFLASH1 and VIO are both ON, though in

low quiescent mode when the phone is in sleep mode. An output current of 500 mA can

be drawn from the VIO regulator and 1.5 mA from the VFLASH1 regulator. VIO supplies

the UPP, FLASH and LCD, VFLASH1 supplies LCD, DLR-3 cable, IRDA and the Bluetooth

module. VANA is supplying analogue parts internally in the UEM as well as the baseband

audio circuitry and pull-up resistors on the input of the UEM slow AD converters.

When the plug and play DLR-3 cable is connected to the phone, it must be supplied by

the phone with 2.78 Vdc / 25 mA. This is delivered via a switch from VFLASH1. The switch

is controlled by the MCU and the control signal originates from a general IO pin on the

UPP.

The regulators VR1A, VR1B, VR2 – VR7 and IPA1 – IPA4 are all controlled by the DSP via

the DBus. VR3 – VR7 are controlled by the UEM as well and are disabled in sleep regardless of DSP writings.

VBAT is furthermore distributed, unregulated, to the RF power-amplifier and the BT102

Bluetooth module as well as filters in the baseband module.

The CHACON module in the UEM controls the charging of the main battery. Furthermore

it contains a 3.2 Vdc regulator for charging of the backup battery and a 1.8 Vdc regulator

supplying the internal real time clock.

Page 2-14 ãNokia Corporation. Original

Page 15

NPE-4

PAMS Technical Documentation 2 - Broadband System

Baseband

UEM

RF Regulators

Boomer

VR1A

VR1B

VR2-7

6

SIM

VSIM

Battery

VCORE

VANA

VFLASH1

VFLASH2

VBAT

Bluetooth

PA Supply

Baseband

Regulators

RTC

CHACON

System Connecter

Figure 4 Baseband power distribution

VIO

UPP

FLASH

LCD

Backup

battery

DLR-3

switch

IRDA

Charging

The charging of the main battery is controlled by the UEM. External components are

needed in order to sense charging current and voltage that are needed by the Energy

Management (EM) software and to protect against EMC into the baseband area. The

charger is connected to the phone via the DCT3 bottom connector and routed from here

to the UEM via the PWB.

Transceiver

0R22

VBATREGS

1u10n

UEM

VCHARINVCHAROUT

CHACON

PWM

VCHAR

1n

10k

33R/100MHz

10k

10n

VCHAR

1.5A

CHRG_CTRL

GND

Figure 5 Charging configuration

Original ãNokia Corporation. Page 2-15

Charger

Filter

cap.

Zmin. 20k

Pull-

down

100k

1000uF

max.

Page 16

NPE-4

2 - Broadband System PAMS Technical Documentation

Connecting a charger to the telephone creates a voltage, VCH, on the UEM VCHAR input.

When the VCH level is detected to rise above the VCH

threshold (2.0 Vdc) by CHACON,

DET

charging starts. Level crossing detection of the VCHAR line is used to generate synchronizing pulses for UEM’s state machine for control of rectifier type chargers, e.g. ACP-7.

Figure 6 Detection of charger / generation of charger synchronization pulses

In case the main battery is fully discharged and the UEM subsequently is without power

i.e. in NO_SUPPLY or BACKUP mode, the start-up charging circuitry is in control, giving

the possibility to detect a charger and engage charging. If the VBAT level is detected to

be lower than the master reset voltage (V

with a constant current of 100 mA until VBAT exceeds V

) the CHACON will charge the battery

MSTR-

. When this happens, from

MSTR+

a charging point of view, normal PWM charging situation resumes. A PWM signal is generated by the digital part of the UEM, which sources the CHACON. The frequency of the

signal can be either 1 Hz or 32 Hz. If the connected charger is of a 2-wire kind e.g. ACP7, the PWM signal has the frequency 1 Hz. If the charger on the other hand is a 3-wire

type e.g. ACP-9, the switch is left on permanently and the 32 Hz PWM control signal

routed to the charger in order to produce a constant voltage. Figure 7 shows a state diagram of the PWM charge situation.

Page 2-16 ãNokia Corporation. Original

Page 17

NPE-4

PAMS Technical Documentation 2 - Broadband System

Figure 7 UEM charging state diagram, PWM mode only

In order to protect the phone from damage resulted by over voltage in the case that the

battery is abruptly removed when charging is ongoing, the charger switch is closed

immediately. This is detected by means of VBAT that will rise fast above VBAT

LIM1,2+

when the battery is removed. A scenario like this can be seen in Figure 8.

Original ãNokia Corporation. Page 2-17

Page 18

NPE-4

2 - Broadband System PAMS Technical Documentation

Figure 8 Charging scenario where the battery is abruptly removed

1) Battery disconnected abruptly during charging

2) VBAT reaches VBAT

LIM1,2+

3) VBAT falls below VBAT

4) VBAT reaches VBAT

LIM1,2+

5) VBAT falls below VBAT

® charging switch is turned off immediately

® charging switch is turned on (soft switching)

LIM1,2-

again ® charging switch is turned off

once again ® charging switch is turned back on

LIM1,2-

6) The PWM signal from the UEM digital part turns logical ´0´ because the system

has acknowledged the absence of a battery and this subsequently turns the

charging switch off.

7) VBAT falls below VBAT

but the charging switch is not turned back on since

LIM1,2-

the PWM signal is logical ´0´.

Note: that if the battery voltage level is below V

level when the battery is discon-

MSTR-

nected from the phone, and if the charger is still connected when the battery is

once again attached to the phone, the UEM will remain in NO_SUPPLY or

BACKUP mode. This will keep the phone OFF until the charger is first disconnected and then reconnected.

Battery

The battery is external and will be connected to the phone via four terminals as shown in

Figure 9. In order to detect the capacity and chemistry of the battery, the phone uses the

Page 2-18 ãNokia Corporation. Original

Page 19

NPE-4

PAMS Technical Documentation 2 - Broadband System

BSI connection in conjunction with 100 k_ pull-up resistors in the baseband module or in

the desk-stand DCH-9 extra battery slot, which allows charging of extra battery. 2.78 V

from VFLASH1 feeds the resistor in the baseband module and the resulting divided voltage is routed to the BSI ADC input in the UEM.

Figure 9 Mechanical layout of DCT-3 battery

The battery also contains a 47 k_ NTC resistor used for battery temperature measurements. The measurement of the temperature by means of resistors follows the same

principal as with the BSI resistor.

UPP (Universal Phone Processor).

The UPP used for NPE-4 is a version with 8 Mbit internally RAM. It is clocked by a 13MHz

frequency from the RF-chip "HAGAR".

It can operate on 4 different voltages; 1.05,1.3,1.5 and 1.8V. The voltage can be programmed "on the fly" by the SW. For example in standby-mode, 1.3V is used for power

saving, but in active-mode (i.e. call) the voltages is increased to 1.8V to get maximum

numbers of MIPS.

The UPP can be divided into two functional sections, Body and Brain. Body contains system logic, and Brain contains processor subsystem including DSP, MCU, memories and

Bus Controller. The function of the Body is mainly the same as in DCT3 system Logic. The

Body is connected to Brain via RHEA bus. The Body and Brain is shown below.

Original ãNokia Corporation. Page 2-19

Page 20

NPE-4

2 - Broadband System PAMS Technical Documentation

Figure 10 UPP architecture

Page 2-20 ãNokia Corporation. Original

Page 21

NPE-4

PAMS Technical Documentation 2 - Broadband System

The DSP inside the Brain is a Lead3 16–bit DSP core from TI (Texas Interments), with a

DMA controller, wait state generator and a program fetch of 32-bits. Furthermore, the

DSP core has an instruction-length flexibility of 8 to 48-bits. The maximum frequency

for the DSP core is 145MHz for the NPE-4 baseband, although the maximum frequency

for the core itself is 400 MHz. The core can do single and dual mac-operations per clockcycle. This means that the NPE-4 baseband has a maximum of 290 MIPS (mac-operations) on the DSP-core.

The DSP core has three different RAM-banks; cache RAM, dual access RAM for storing

and manipulating data and last, single access RAM for storing and manipulating SW

variables. All the RAM-banks have a 145 MHz clock and 32-bit organization. It has also

an ARM port interface, which is used for MCU/DSP message transfer (API).

The MCU consist of a 16/32–bit RISC core (ARM7). The block has a small ROM (768x32

bits) for MCU boot code. It interfaces to DSP through the 8Mbit PDRAM. The MCU has it

own sectors in the RAM as well as the DSP. RAM blocks or sectors are divided into the

following:

The rest of the PDRAM is used for program code, mainly GPRS SW.

Bluetooth

NPE-4 has a Bluetooth module BT102 that receives and transmit at 2.4GHz. The module

makes it possible for the phone to communicate via a radio link with other Bluetooth

units e.g. headsets, carkits or printers.

The Bluetooth module is itself made as a multilayer PWB – covering all the needed Asics

and discrete components – with a shielding frame- and lid. The module is soldered onto

the phone PWB in the same way as other SMD components.

UI

LCD cell

• 4 x 64Kbytes for the DSP and MCU.

• 4 x 64KB Banks, MCU only.

• 2 x 4KB Banks, for the DSP, and MCU.

The LCD is a black and white LS2 96x65 full dot matrix display. The LS2 display has a

standard DCT4 interface. The LCD cell consists of a single COG driver, 3 boosting capacitors and a FPC, where the capacitors are placed. The LCD interface between the LCD cell

and the main PWB can be viewed in section LCD Interface page LCD Interface.

The LCD cell is part of the complete LCD module, which includes metal frame, gasket,

light guide, spring connector, RTC battery, transflector (not shown) and dome sheet. The

figure below illustrates the complete overview of the LCD module.

Original ãNokia Corporation. Page 2-21

Page 22

NPE-4

2 - Broadband System PAMS Technical Documentation

Dome sheet

Light guide

Frame

Gasket

LCD

Figure 11 Complete overview of LCD module

Connector

"Displa

RTC Battery

Below is the general specifications listed:

• Glass size, width x height x thickness (incl. caps) : 38.4 mm x 37.6 mm x 2.75 mm

• Viewing area (width x height) : 35.4 mm x 27.7 mm

• Active pixel area (width x height) : 30.609 mm x 24.1 mm

• Number of pixels : 96 columns x 65 rows

• Pixel height to width ratio : 1.17:1

• Pixel gap : 0.015 mm

• Technology : FSTN

• Display type : Positive

• Main viewing direction : 6 o’clock

• Illumination Mode : Transflective

• Driver chip : DCT4 driver

Page 2-22 ãNokia Corporation. Original

Page 23

NPE-4

PAMS Technical Documentation 2 - Broadband System

Au Connector pads

C

FPC

C

SEG 0 SEG 95

COM 0COM 64

Figure 12 LCD module.

C

Driver

Viewing area

Active area

96 x 65

Top View

The LCD is powered from both V

FLASH1

and VIO. V

is used for the boosting circuit

FLASH1

and VIO for the driver chip. The total LCD current consumption specified by vendor is

described below:

Table 5: LCD current consumption

Typ Max Unit/Note

I

total

250 400

400

mA @ +25oC

I

total =IDD+IDDI

I

measured with normal mode test pattern.

total is

mA @ Top, measured with normal mode test

pattern.

900 1300

mA using worst case test pattern @25 °C

1

This test pattern is used for R&D purpose only and is not possible to recreate by end user.

LCD Backlight

The LCD backlight consists of 4 yellow/green LED's (NPE-3 type) which are placed on the

main PWB below the LCD area. They lit into the light guide where the light is distributed

to generate sufficient backlight for the LCD.

The LED driver circuit is shown below in Figure 13 LED driver circuit for display and key

light. The voltage drop over R307 produces a constant current of 40 mA, i.e. 10 mA pr.

LED (same as NPE-3).

The UEM output pin, DLIGHT, controls the driver circuit. This output is an open drain

driver. The output frequency is 128 Hz and the duty cycle can be changed from 0 – 100

% with 4 bit resolution. By changing the duty cycle of the PWM signal it is possible to

change the average current of the LED's.

Original ãNokia Corporation. Page 2-23

Page 24

NPE-4

2 - Broadband System PAMS Technical Documentation

Keyboard light

The keyboard light consists of 6 yellow/green LED's (NPE-3 type) which are placed under

the keyboard and use the light guide to distribute the light. The driver circuit is the same

as described above in section LCD Backlight, with the difference of a current of 60 mA,

i.e. 10 mA pr. LED.

The keyboard LED's can also be controlled by a 128 Hz PWM signal from the UEM,

KLIGHT.

LED driver circuit

V

BAT

LCD: R307 = 15R

KEY: R309/R310 = 10R

LCD: V311a

KEY: V313a

LCD: V311b

LCD: R306 = 1K

KEY: R308 = 1K

KEY: V313b

Vibra

Buzzer

x4 LEDs for LCD

DLIGHT

or

KLIGHT

x6 LEDs for key

Figure 13 LED driver circuit for display and key light.

A vibra-alerting device is used to generate a vibration signal for an incoming call. The

vibra is placed in the top of the phone. It is fastened to the A-cover by means of two

wings that are pressed into the A-cover.

The vibra is electrically connected to the PWB by spring contacts.

The vibra is controlled from the UEM by a PWM (Pulse Wide Modulated) square wave

signal.

Alerting tones and/or melodies are generated by a buzzer, which is controlled by a PWM

signal from the UEM. The SPL requirement is 105dB (A) at 5cm, however end of line

requirement from sup-supplier is 102dB at 5 cm.

The buzzer is designed to a first resonant peak at 2500 Hz. The ringer melodies will be

optimised in MCU so the main frequency of any given melody is shifted to near the resonant peak. For this optimisation a program called BuzzCalc will be used for the calculation of the dominating frequency of a given ringing melody or tone.

The design of the buzzer is a direct copy from the NPE-3 project. The Buzzer is glued to a

gasket. Vendor delivers this final assembly. Sound holes are placed in the A-cover

Page 2-24 ãNokia Corporation. Original

Page 25

NPE-4

PAMS Technical Documentation 2 - Broadband System

The buzzer is electrically connected to the PWB by spring contacts.

Keypad

See keypad interface in section Keypad interface on page Keypad interface.

IR-module

The IR module CIM-93M4 is fully compliant with the IrDA1.2.a and supports data rates

of 9600 bps to 1152 kbps. The module is connected to the UEM IR module, which acts as

a level-shifter between the IR module and the UPP. The UEM IR module supports the

data rates of the CIM-93M4.

VBAT

SIM

UPP

GenIO10

IRRX

IRTX

1.8 V

IRRX

1.8 V

IRTX

Figure 14 NPE-4 IR connectivity

UEM

IRLEDC

IRRXN

VFLASH1

V350

100k

2.78 V

2.78 V

LEDA

TXD

RXD

VCC

CIM-93M4

Hi/Low

Speed

CIM-93M4 operates on 2.7 V logic, thus the transistors. A future module will be operating by 1.8 V logic and the level shifter V350 in Figure 14, will be obsolete.

A metal shield covers the IR module in order to maximise performance in the high RF

field it operates in (Directly beneath the antenna).

NPE-4 uses a product specific SIM-card reader (SIM reader). Electrical connection of SIM

reader is similar to other DCT4 products. The SIM interface is split between UEM and UPP

(see Figure 7.14 UPP, UEM and SIM Connections below). This has been done in order to

reduce the amount of interconnections on the SIM interface between the UPP and the

UEM. The SIM interface control logic and UART is integrated into the UPP. The SIM interface start-up and power down sequence, including timing and reset generation is implemented in UEM. The SIM interface in the UPP supports the SIM speed enhancement

features, which improves the data transfer rate in the SIM interface.

The UEM contains the SIM interface logic level shifting. UPP SIM interface logic levels

are 1.8V. The SIM interface can be programmed to support 3V and 1.8V SIMs. A 5V SIM

interface is not supported. A register in the UEM selects the SIM supply voltage. It is only

allowed to change the SIM supply voltage when the SIM IF is powered down.

Original ãNokia Corporation. Page 2-25

Page 26

NPE-4

2 - Broadband System PAMS Technical Documentation

The SIM power up/down sequence is generated in the UEM. The Battery Type contact signal (BSI) is used to recognise if the battery suddenly is removed from the transceiver

block. The SIMCardDet is not used. If the BSI goes low, the power down sequence is

automatic initiated. The SIMIF will then force all the connections low, i.e. SIMRST, SIMCLK, SIMDATA and VSIM. A comparator inside the UEM does the monitoring of the BSI

signal. The comparator offset is such that the comparator output does not alter state as

long as the battery is connected. The BSI comparator threshold level is 2.1 V with 75 mV

hysteresis.

Figure 15 UPP, UEM and SIM Connections

Memory description

The NPE-4 baseband consists of 64Mbit (8MB) external flash memory. Access to the flash

is performed as 16-bit access in order to improve the data rate on the bus.

The purpose of the memory interface is to reduce the amount of connections by multiplexing the address and data bus on to the same signals. If the memory address space is

more than 16 bits, which is the case, then 16-bit data can be multiplexed on the address

inputs. This requires the memory to store the address during the first cycle in the access

as described in Figure 8.1 Basic reading (Random access).

In addition to this, the system provides a Power Save signal (PS), which is used to reduce

the switching on the external bus between the memory and the UPP. In case of writing to

the flash, the UPP provides the information on the PS signal, and in case data is read

from the flash, the memory provides the status of the PS signal. The PS signal is used to

indicate if data should be inverted at the receiver end. If PS = “1” the data shall be

inverted at the receiver end before it is stored/processed. The PS-signal will be described

more in details in section Power saving signal (PS)..

Page 2-26 ãNokia Corporation. Original

Page 27

NPE-4

PAMS Technical Documentation 2 - Broadband System

Furthermore the memory is capable of handle burst-mode (multiplexed address/databus) and memory blocking, which is controlled by the UPP.

Read cycle.

The read cycle is initiated by first applying the address to the multiplexed address/databus. The address is latched at the rising edge of the AVD-signal. The memory device captures the address/data bus-state at point B. The captured data is compared on a bit by bit

base (MSB–MSB, LSB–LSB), with the data inside memory. If the comparison shows more

equal bits than unequal bits, the data is not inverted before it is send out on the address/

data bus as output data. The result of the comparison is indicated, by using the PS signal

before the data is read (at point C) by the Bus Controller. This allows the receiving device

to invert the data before it is read into a register. The valid PS signal needs to be available in advance before the actual read operation takes place.

Figure 16 Basic reading (Random access)

Write cycle.

The write cycle is initiated by first applying the address to the multiplexed address/data

bus and to the address lines Axx-A16, (Axx is the MSB address for that memory density).

The address latch is transparent from A to B. The address is latched at the rising edge of

the AVD signal. Latching address Axx-A16 is mandatory. The random access time is mea-

Original ãNokia Corporation. Page 2-27

Page 28

NPE-4

2 - Broadband System PAMS Technical Documentation

sured from a stable address, falling-edge of AVD or falling-edge of CE which ever occurs

last. No clock is provided for a random access.

The below figure shows a basic write waveform.

Figure 17 Write waveform (Random access)

Power saving signal (PS).

In order to reduce the power consumption on the bus a Power Save function is introduced. This function reduces the amount of switching on the external bus.

Power is consumed in a digital system when a signal changes state. The power is consumed when the capacitive load is either charged or discharged. The capacitive load is

introduced by the interconnection itself and of cause by the input at the receiving

device. Internally in digital circuits the capacitive load is lower, than at the interconnect

level at the printed circuit board. Therefore it is an advantage if the amount of changes

on the external interconnection, i.e. between two digital circuits, can be minimised.

Therefore on a wide bus like an address/data bus in a microprocessor system, power is

saved, if the data to be transmitted on the external bus, causes a minimum amount of

transitions. This can be achieved by comparing the previously data on the bus, with the

data to be transmitted, and if inverting the data to be transmitted causes less transitions

to be performed on the external bus, the data is inverted, before it is output on the data

bus. To inform that the data is inverted, a control signal is used to inform the receiving

device, that the data must be inverted before any further processing.

Page 2-28 ãNokia Corporation. Original

Page 29

NPE-4

PAMS Technical Documentation 2 - Broadband System

Data on the address/data bus is bit wise compared which means that the data previously

on D0 (D0e) is compared with the new data to be output on D0 (D0i). If the two data elements are the same (D0e=D0i) a logic “0” is indicated to the comparing device. If the two

data elements are not the same (D0e=NOT(D0i)) a logic “1” is indicated to the comparing

device. If there are more equal signal than unequal signals on the address/data bus, the

new data is not inverted before it is sent out on the bus. If there are more unequal than

equal data on the address/data bus, the data is inverted before it is sent out on the bus.

The status whether the data that is presented on the address/data bus is inverted or not,

is indicated by a separate signal to the memory device. If the data on the bus is not

inverted this power control signal (PS), is at logic “0” state. If the data that is presented

on the bus is inverted, this is indicated by PS = logic “1”. This PS signal is a common signal for all the devices connected to the address/memory bus. The transmitting device

uses the PS signal to indicate non-inverted or inverted data. As only one device at a time,

can present data on the address/data bus, this signal is shared and only one additional

control signal PS is needed for the address/data bus, although the data bus may be connected to several devices. The below figure shows how this PS-signal actually works.

Figure 18 The data is compared by using an XOR-function. The result can be seen above.

In Figure 18 there are more equal bits than unequal bits, so therefor the data is not

inverted before it is sent out to the flash. This means that the PS-signal is "0". The next

scenario shows the opposite situation.

Original ãNokia Corporation. Page 2-29

Page 30

NPE-4

2 - Broadband System PAMS Technical Documentation

Figure 19 The comparison shows more unequal bits than equal bits,

and the bits are inverted on the bus.

The power save (PS) function is only active in burst mode due to delay in the readings

(Random access). If it were used in random access, it would have introduced a delay of

10 – 15 ns. The PS is not activated in the first access in the burst, only from the second

access in the burst.

In particular in burst mode it is important to keep the performance. In order to reduce

complexity in the memory, the power save function does not apply to the address. This

means that the address will always be presented in its true value. This means that the

memory do not have to manage the inversion of the address. In case of burst access it is

possible to reduce the power on the external bus by comparing the contents of the data

in the burst, not with the data on the bus. This results in that the random access data is

presented on the bus, as such but the following data in the burst is presented using the

power save function. By pipelining the power save information in this manner the additional delay caused by the comparison logic is removed.

Memory block.

The memory or flash is organised in four Banks, A, B, C and D. Bank A and B each contain

eight 8 Kword sectors and thirty-one 32 Kword sectors. Bank C and D each contain

thirty-two 32 Kword sectors. The total sector Architecture is eight 8 Kword sectors and

one hundred twenty-six 32 Kword sectors.

Block locking.

To prevent accidental writings to some of the sectors in the flash, block locking has to be

used. This can, depending on the vendor, bee implemented by using different methods.

AMD and Intel are the to only vendors that NPE-4 is going to use for the flash purpose.

AMD and Intel will implement their block locking in the following way.

Intel: The locking scheme offers two levels of protection. The first allows software-only

control of block locking (useful for frequently changed data blocks) while the second

Page 2-30 ãNokia Corporation. Original

Page 31

NPE-4

PAMS Technical Documentation 2 - Broadband System

requires hardware interaction before locking can be changed (protects infrequently

changed code blocks). For this purpose, a dedicated pin called WP is used. The WP-pin or

signal is only controlled by the hardware.

Lock block:

The blocks’ default power-up or reset status is locked. Locked blocks are fully protected

from alteration. Attempted program or erase operations to a locked block will return an

error in a status register inside the flash. A locked block’s status can be changed to

unlocked or lock-down using the appropriate software commands. Writing the "Lock

block command" sequence can lock an unlocked block.

Unlock block:

Unlocked blocks can be programmed or erased. All unlocked blocks return to the locked

state when the phone is or powered down. An unlocked block’s status can be changed to

the locked or locked-down state using the appropriate software commands. A locked

block can be unlocked by writing a "unlock block command" sequence, if the block is not

locked-down.

Lock-down block.

Locked-down blocks are protected from program and erase operations (just like locked

blocks), but software commands alone cannot change their protection status. A lockeddown block can only be unlocked when the WP-signal is high. When the WP-signal goes

low, all locked-down blocks revert to locked. A locked or unlocked block can be lockeddown by writing a "Lock-Down Block command" sequence. Locked-down blocks revert to

the locked state at device reset or power-down.

AMD:

a block a command sequence must be written, once the command unlock sequence is

written the SW can unlock as many blocks as required by entering the block address

while keeping a specific address high. If the address is taken to low, the block will be

locked instead of unlocked. The SW locking is similar to the Intel SW locking.

The AMD flash does also have the same hardware lock as Intel. The signal or pin is called

WP (write protect). The blocks are locked if WP is set to low. If the WP-signal is set high

then the SW can control the locking of the blocks. Finally, if the VPP pin is set to low all

blocks are locked.

It is not yet specified which flash type NPE-4 is going to use, but the SW-team has to

implement one of the above block-locking methods.

All blocks have a locking latch and upon power up all blocks are locked. To unlock

Read while Write (RWW).

The device is capable of reading data from one Bank of the memory while programming

or erasing in the other Bank of the memory. An erase operation may also be suspend to

read from or program to another location within the same Bank (except the sector being

erased).

Original ãNokia Corporation. Page 2-31

Page 32

NPE-4

2 - Broadband System PAMS Technical Documentation

Burst mode.

The flash device supports burst-mode. The purpose is to improve the date rate between

the flash and the UPP. The burst-mode can only be used for read operations. It is possible

to access the memory in burst-mode over the entire memory except for the 8 x 8 Kbytes

sectors. When using burst-mode at least 4 word (4*16 bits) is read from the flash. A read

operation from the flash, normally first set-up the address, and then the UPP will get the

data from this particular address. The address has to be set-up or sent to the flash ever

time the UPP wants to read from the flash. By using burst-mode the address only needs

to be sent one time, then flash will keep sending data as long as there is a clock-signal.

Figure 20 Burst-mode reading from the flash. Note that the address only is sent ones.

The flash keeps sending data to the UPP as long as the CS-signal and CLK are valid.

Flash programming.

The actual programming is indicated to the UPP by using the MBUS_RX signal between

the UPP and the UEM. The MBUS signal from the UEM to the flash prommer (FPS8 box) is

used as clock for the synchronous communication. The flash prommer keeps the MBUS

line low during UPP boot, to indicate that the flash prommer is connected. If the UPP

MBUS_RX signal is low on UPP, the MCU enters flash programming mode. If the signal is

high, the MCU starts loading software from the flash.

In order to avoid accidental entry to the "flash programming mode" the MCU only waits

for a specified time, to get input data from the flash prommer. If the timer expires without any data being received, the MCU will continue the boot sequence. The MBUS signal

from UEM to the external connection is used as clock during flash programming. This

means that flash programming clock is supplied to the UPP on the MBUS_RX signal. The

flash prommer indicates to the UEM that flash programming/reprogramming by writing

an 8 bit password to the UEM. The data is transmitted on the FBUS_RX line and the UEM

clocks the data on the FBUS_RX line into a shift register. When the 8-bits have been

shifted in the register, the FPS8-box generates a falling-edge on the BSI line. This loads

the shift register content in the UEM into a compare register. These 8-bits will be compared in a register to see if they match the "secret" default value inside the UEM. At this

point the flash prommer must pull the MBUS signal to UEM low, in order to indicate to

the MCU that the flash prommer is connected. The UEM reset-state machine performs a

reset to the system (PURX low for 10–100 ms). The UEM "flash programming mode" is

Page 2-32 ãNokia Corporation. Original

Page 33

NPE-4

PAMS Technical Documentation 2 - Broadband System

valid until MCU sets a bit in the UEM register, which indicates the "end of flash programming". Setting this bit also clears the compare register in the UEM previously loaded, at

the falling edge of the BSI signal. During the "flash programming mode" the UEM watchdog is disabled. When the bit is set it indicates "end of flash programming" and it resets

the UEM watchdog timer to it’s default value. Clearing the flash programming bit also

causes the UEM to generate a reset to the UPP. The BSI signal is used to load the value

into the compare register. In order to avoid spurious loading of the register, the BSI signal will be gated during UEM "master-reset", and during "power-on" when PURX is

active. The BSI signal should not change state during normal operation unless the battery is extracted, in this case the BSI signal will be pulled high, note a falling edge is

required to load the compare register.

MCU Boot.

When the MCU boots, it looks for flash programming indication by reading the status on

the MBUS signal. If this signal is pulled low the MCU sets up the UART in synchronous

mode, and indicates to the flash prommer, by setting FBUS_TX low, that it is ready to

accept the secondary boot-code. All flash programming related SW that is downloaded is

done so to the UPP internal MCU SRAM. The MCU also ends up in "flash programming

mode", if the contents of the flash is empty (reading FFH from the first memory location

in the flash).

Flash Identifiers.

Due to that DCT4 supports many different manufacturers; NMP needs to have so called

flash identifiers. The flash identifier tells the MCU which HW environment it is working

in, and also block size and configuration of the flash.

First Word.

The word contains the information about the number of flash devices connected to the

UPP. It is possible to setup the UPP so that it supports two devices. The MSB bit in the

word indicates the amount of flash devices used by the baseband. The amount of wait

states for the random access is specified over 3-bits in this word. The amount of wait

states is specified related to the system clock used in that system. The MCU PLL factor is

also specified in this word (2-bits).

Second Word.

This word contains information about flash sectors available for EEPROM emulation. If

no RWW capability is indicated, this field then contains information of the serial

EEPROM that is used in the system.

Third Word.

This word contains similar information as the first word but for the second flash if such

is used.

Fourth Word.

This word contains information about the sector configuration of the second flash.

Original ãNokia Corporation. Page 2-33

Page 34

NPE-4

2 - Broadband System PAMS Technical Documentation

Fifth Word.

This word contains information of the external SRAM if it is available on the baseband,

the size of it and the amount of wait states to be used when accessing it.

Absolute maximum ratings (AMD 64Mbit).

Table 6: Absolute maximum ratings for AMD 64 Mbit

Parameter Rating Remarks

Supply voltage (Vcc)

(operational voltage is: 1.7 –1.9)

VPP and RESET -0.5 V to +12.5

Output Short Circuit Current 100 mA No more than one output may be

Voltage with Respect to Ground.

All pins except VPP and RESET

-0,5 V to +4,0 Volt Minimum DC voltage on input or I/O

pins is -0.5 V

Minimum DC input voltage on pins

Volt

0.5 V to Vcc + 0.5

Volt

VPP, and RESET is -0.5 V

shorted to ground at a time. Duration

of the short circuit should not be

greater than one second.

Minimum DC voltage on input or I/O

pins is -0.5 V

Absolute maximum ratings (INTEL 64Mbit).

Table 7: Absolute maximum ratings for INTEL 64 Mbit

Parameter Rating Remarks

Voltage on any pin (except Vpp, Vpp) -0.5V to +2.45V See reference for details

Vpp Voltage -0.2V to +14V

Vcc and Vccq -0.2V to +2.45V

Output short circuit current 100mA

Page 2-34 ãNokia Corporation. Original

Page 35

NPE-4

PAMS Technical Documentation 2 - Broadband System

HW Interfaces

Keypad interface

The NPE-4 phone doesn't have separate keyboard PWB. The keys are directly connected

via the KEYB(10:0) bus to the UPP. The keypad consist of a 5x4 matrix, meaning 5 rows

(R0 – R4) and 4 columns (S1 – S4).

Figure 21 NPE-4 keypad

When there is no key pressed, all the inputs from the rows are high due to that the UPP

has internally pull-up resistors on those lines. All the columns are low at this state. When

a key is pressed, the specific row where the key is placed is pulled low. This generates an

interrupt to the MCU and the MCU now starts its scanning procedure. The procedure first

set all the columns high (KEYB (0) to KEYB (4)) and then one by one set them low again.

Only one of the columns is low at the time. While one of the columns is low, the row is

(KEYB (5) to KEYB (10)) is read by MCU to find the active low signal. If the input is low

the MCU knows that a key is pressed. When the key has been detected all the keypadregister inside the UPP is reset and it's ready receiving new interrupt.

Original ãNokia Corporation. Page 2-35

Page 36

NPE-4

2 - Broadband System PAMS Technical Documentation

LCD Interface

LCD connection from main PWB to FPC contact on LCD is made with an 8-pin spring

connector (same as in Hda12).

Table 8: LCD Module pin-out to PWB

Pin Signal Symbol Parameter Min. Ty p. Max. Unit Notes

1 XRES Reset 0.3 x V

t

rw

2 XCS Chip Select 0.7 x V

t

CSS

t

CSH

1000 ns for valid reset

DDI

60 ns setup time

100 ns hold time

0.3 x V

DDI

DDI

3 VSS GND Ground 0 V

4 SDA Bi-directional serial

0.7 x V

DDI

interface

0.3 x V

DDI

t

sds

t

sdh

5 SCLK Serial clock input 0.7 x V

t

scyc

100 ns Data setup time

100 ns Data hold time

DDI

0.3 x V

DDI

250 ns Serial clock cycle

V Logic Low, active

V Logic High

V Logic Low, active

V Logic High

V Logic Low

V Logic High

V Logic Low

(4MHz)

t

shw

100 ns Serial clock high pulse

width

t

slw

100 ns Serial clock low pulse

width

6

VDDI

VDD digital power sup-

1.6 1.8 1.88 V

ply

7 VDD Booster power supply 2.6 2.78 2.86 V

8 VOUT Booster output 12 V Decoupled to Vflash1

on main PWB with 1uF

Page 2-36 ãNokia Corporation. Original

Page 37

NPE-4

PAMS Technical Documentation 2 - Broadband System

SIM interface

The SIM interface supports both 1.8V & 3V with 255 entries. The figure below shows the

placement of the individual SIM pins.

Bottom connector

RF area

Antenna

43

5

BB area

2

16

Component view

Figure 22 Placement of SIM pins (Phone bottom view)

Table 9: SIM Connector Interface

Pin Name Parameter Min Typ Max Unit Notes

1 SIMCLK Frequency

T

rise/Tfall

2 SIMRST V

oh

V

ol

1.05 3.25 3.36

0.9*VSIM

0

0.15*VSIM

26

VSIM

MHznsSIM clock

V SIM reset

3 VSIM 3V SIM Card 2.8 3.0 3.2

25

1.8V SIM Card 1.6 1.8 2.0

25

VmASupply voltage

Icc, 4MHz

VmASupply voltage

Icc, 4MHz

4 GND GND 0 0 V Ground

6 DATA V

oh

V

ol

V

ih

V

il

0.9*VSIM

0

0.7*VSIM

0

VSIM

0.15*VSIM

VSIM

0.15*VSIM

V SIM data

Trise/Tfall max 1us

Original ãNokia Corporation. Page 2-37

Page 38

NPE-4

2 - Broadband System PAMS Technical Documentation

Ostrich

The STI-block, placed in the UPP "brain block", has a trace interface that can be used for

tracing messages written by the DSP or the MCU. Writings or reading to a specific I/O

register or an address match on the MCU address bus can be traced on the interface. The

interface consists of three lines plus a GND line. One of the great advantages, compared

to JTAG, is that the SW in the phone can run normally while trace messages is lead out to

the Ostrich box. Data can be captured at 40MHz on the interface.

The main purpose for the interface is debugging in R&D phases. It can also be used for

flashing interface.

Table 10: Ostrich interface

Signal Pin (test point) Min. Max. Unit Remarks

STITxD J471 0 1.8 Volt Data to transmit

STISClK J472 0 1.8 Clock

STIRxD J473 0 1.8 Data to receive

VBAT J470 2.9 5.3 Supply to Ostrich

GND J474 0 GND

JTAG interface

The JTAG interface is used to monitor and or debug DSP activity. The connections from

the UPP are routed to PWB pads, which are free for access.

Table 11: JTAG interface levels

Signal Pin (test point) Parameter Min Typ Max Unit Remarks

JTMS J480 Logic "1"

Logic "0"

JRst J481 Logic "1"

Logic "0"

JTDI J482 Logic "1"

Logic "0"

VIO J483 1,72 1,8 1,88 JTAG supply voltage

JTDO J484 Logic "1"

Logic "0"

JTCK_ret J485 Logic "1"

Logic"0"

1,2

0

1,2

0

1,2

0

1,2

0

1,2

0

1,8

0,5

1,8

0,5

1,8

0,5

1,8

0,5

1,8

0,5

Volt

JTAG reset.

JTAG data output

JTAG return clock

JTCLK J486 Logic "1"

Logic "0"

EMU0 J487 Logic "1"

Logic "0"

EMU1 J488 Logic "1"

Logic "0"

GND J489 0 JTAG GND

1,2 1,8 JTAG clock

1,2

0

1,2

0

1,8

0,5

1,8

0,5

Emulation pin 0

Emulation pin 1

Page 2-38 ãNokia Corporation. Original

Page 39

NPE-4

PAMS Technical Documentation 2 - Broadband System

BT module interface

SW interface

The BT102 component differs from all other components by having its own controlling

software. Bluetooth MCM represents the controlling SW physically programmed into the

BT102 module.

UI SW

BT102 Flash programming

Core SW Servers

CM

CM

PhoNet Router

Bluetooth Media Module

Bluetooth HW driver

Bluetooth MCM

Figure 23 SW interface diagram

PhoNet Pipe Service

PhoNet Name Service

The Bluetooth MCM SW needs to be programmed when the module is assembled into the

phone. This is implemented by interleaving so that code data is being transferred to the

BT102 while the main flash is performing the internal programming of the phone SW.

The figure below illustrates the set-up used for BT102 flash programming.

Prommer

MBUS

FBUS-Tx