Page 1

Nokia Customer Care

Service Manual

RM-396 (Nokia 6212 classic)

Schematics

Part No: (Issue 1)

COMPANY CONFIDENTIAL

Copyright © 2008 Nokia. All rights reserved.

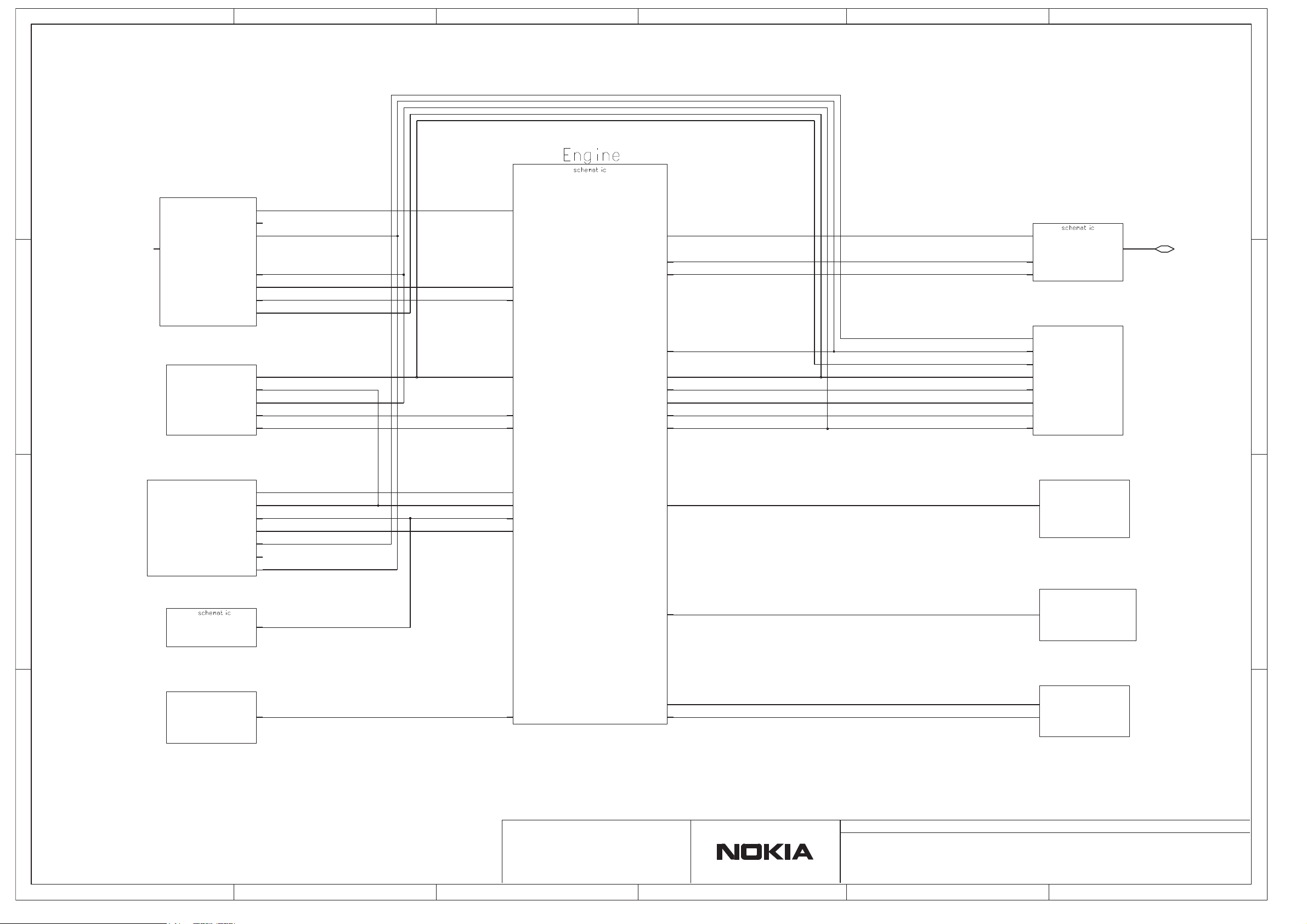

Page 2

7000-7999

1

B

43

B

2 31 4

D

6

5

A

D

C

6

C

5

A

2

2400-2599

2100-2199

AUDIO(6:0)

FM_ANT

GEN_CTRL_CMT(20:0)

I2C(1:0)

LPRFCLK_I

LPRF_CMT(6:0)

PCM(3:0)

PUSL(7:0)

2000-2059

2060-2069

2070-2099

1400-1489

6000-6099

2700-2799

3200-3299

3100-3199

2200-2399

2800-3099

KEYB_CMT(20:0)

MESSI_CMT(25:0)

PUSL(7:0)

PWRONX

SLOWAD(6:0)

UI_BTB(25:0)

schematic

SIM

SIMIF(6:0)

Audio

schematic

AUDIO(6:0)

DIG_AUDIO(5:0)

GEN_CTRL_CMT(20:0)

H_BRIDGE(3:0)

XAUDIO(5:0)

schematic

LPRF

tomahawk

SYS_CONN

AUDIOCTRL(5:0)

CHARGER

FM_ANT

I2C(1:0)

SLOWAD(6:0)

USB_ACI(7:0)

XAUDIO(5:0)

Camera

CAM_CTRL_CMT(7:0)

CCP_CMT(3:0)

FLASH_CONN(2:1)

SPI_CMT(3:0)

UI

schematic

GEN_CTRL_CMT(20:0)

I2C_CMT(1:0)

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

Main Board

Name

MESSI_CMT(25:0)

MMC_CMT(15:0)

PCM(3:0)

PUSL(7:0)

PwrOnX

SIM(6:0)

SLOWAD(6:0)

SPI_CMT(3:0)

USB_ACI(7:0)

VCHARIN

XAUDIO(5:0)

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

BATTERY_CONN

SLOWAD(6:0)

MMC_SD_CARD

schematic

MMC_CMT(15:0)

AUDIO(6:0)

AUDIOCTRL(5:0)

CAM_CTRL_CMT(7:0)

CCP_CMT(3:0)

DIG_AUDIO(5:0)

ETM(16:0)

GEN_CTRL_CMT(20:0)H_BRIDGE(3:0)

I2C_CMT(1:0)

JTAG(6:0)

KEYB_CMT(20:0)

LPRFCLK_I

LPRF_CMT(6:0)

H_BRIDGE(3:0)

DIG_AUDIO(5:0)

SIM(6:0)

MMC_CMT(15:0)

SLOWAD(6:0)

PCM(3:0)

LPRF_CMT(6:0)

PUSL(7:0)

FLASH_CONN(2:1)

CCP_CMT(3:0)

CAM_CTRL_CMT(7:0)

VCHARIN

FM_ANT

FM_ANT

USB_ACI(7:0)

USB_ACI(7:0)

PROD_TEST_PATTERN

USB_ACI(7:0)

schematic

EMU_RAP

ETM(16:0)

JTAG(6:0)

schematic

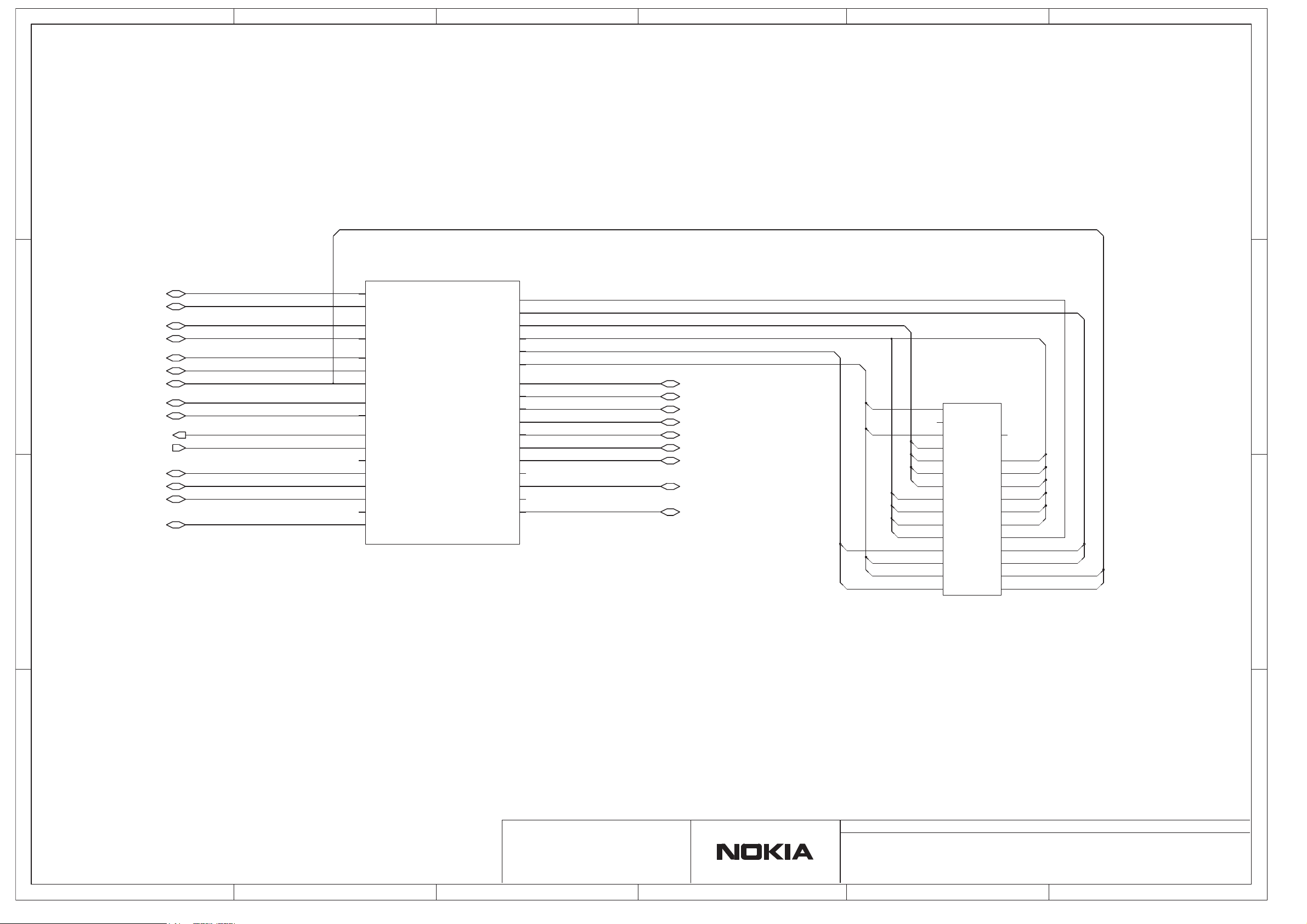

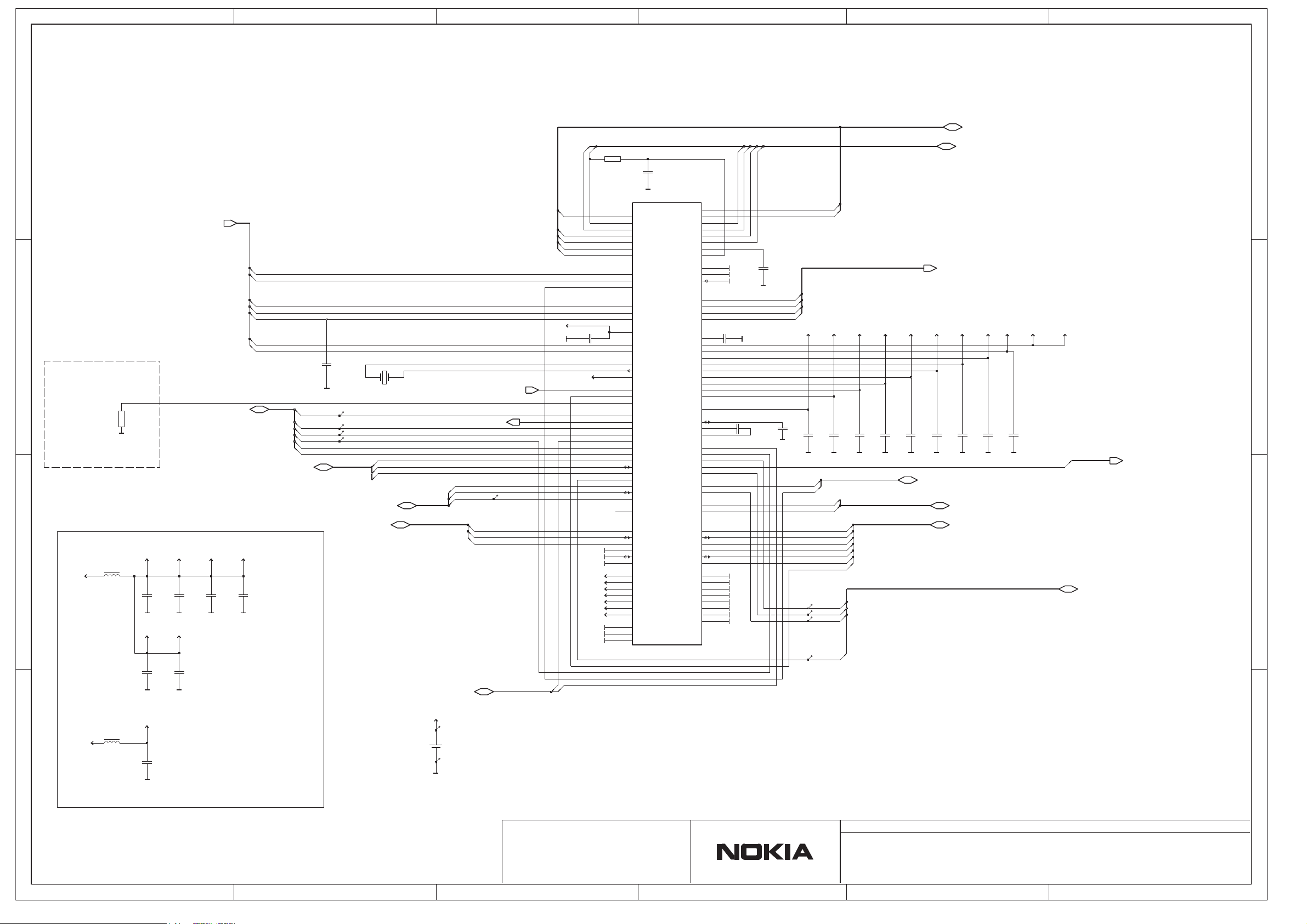

Page 3

5

A

1

2

B

6

1

A

3

CC

3

4

4

6

5

D

B

D

1

7

6

0

2

2

7000-7999

2200-2399

2800-3099

MESSI_CMT(25:0)

MMC_CMT(15:0)

PCM(3:0)

PUSL(7:0)

PWRONX

RFCLK(1:0)

RFCONV(11:0)

RFCTRL(8:0)

RFPWR(4:0)

SIM(6:0)

SLOWAD(6:0)

SPI_CMT(3:0)

TXCCONV(1:0)

USB_ACI(7:0)

XAUDIO(5:0)

3

CBUS(3:0)

CCP_CMT(3:0)

CHARGER

DIG_AUDIO(5:0)

ETM(16:0)

FCI_CMT(3:0)

GEN_CTRL_CMT(20:0)

H_BRIDGE(3:0)

I2C_CMT(1:0)

INTUSB(8:0)

IRDA_CMT(2:0)

JTAG(6:0)

KEYB_CMT(20:0)

LPRFCLK

LPRFCLK_I

LPRF_CMT(6:0)

VXO

WTXDET

8

7

9

CMT_ENGINE

1tqa_05_0203189

AUDIO(6:0)

AUDIOCTRL(5:0)

CAM_CTRL_CMT(7:0)

RFTEMP

RXIN

RXIP

RXQN

RXQP

TXC

TXIN

TXIP

TXQN

TXQP

TXRESETX

VBAT

VCP1

VCP2

VREFCM

VREFRF01

RF

AFC

DAC_REF1RFBUSCLK

RFBUSDAT

RFBUSENA

RFCLKEXT

RFCLKEXT_GPS

RFCLKN

RFCLKP

3

5

2

1

8

4

0

1

0

6

Name

Engine

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

1

1

0

0

XAUDIO(5:0)

USB_ACI(7:0)

TXCCONV(1:0)

SPI_CMT(3:0)

SLOWAD(6:0)

SIM(6:0)

RFPWR(4:0)

RFCTRL(8:0)

RFCONV(11:0)

RFCLK(1:0)

PwrOnX

PUSL(7:0)

PCM(3:0)

MMC_CMT(15:0)

MESSI_CMT(25:0)

LPRF_CMT(6:0)

LPRFCLK_I

KEYB_CMT(20:0)

JTAG(6:0)

I2C_CMT(1:0)

H_BRIDGE(3:0)

GEN_CTRL_CMT(20:0)

ETM(16:0)

VCHARIN

CCP_CMT(3:0)

CAM_CTRL_CMT(7:0)

AUDIOCTRL(5:0)

AUDIO(6:0)

DIG_AUDIO(5:0)

0

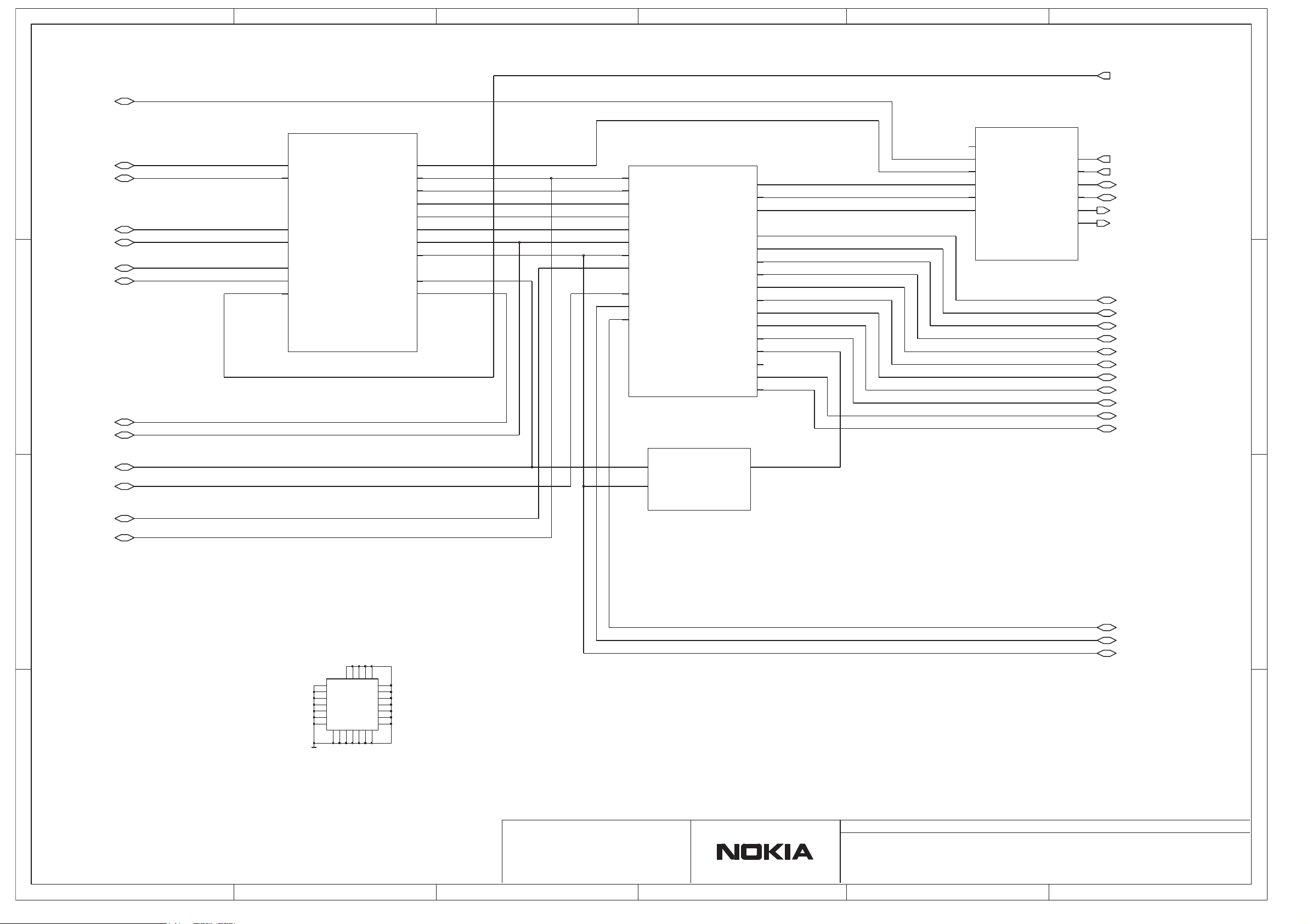

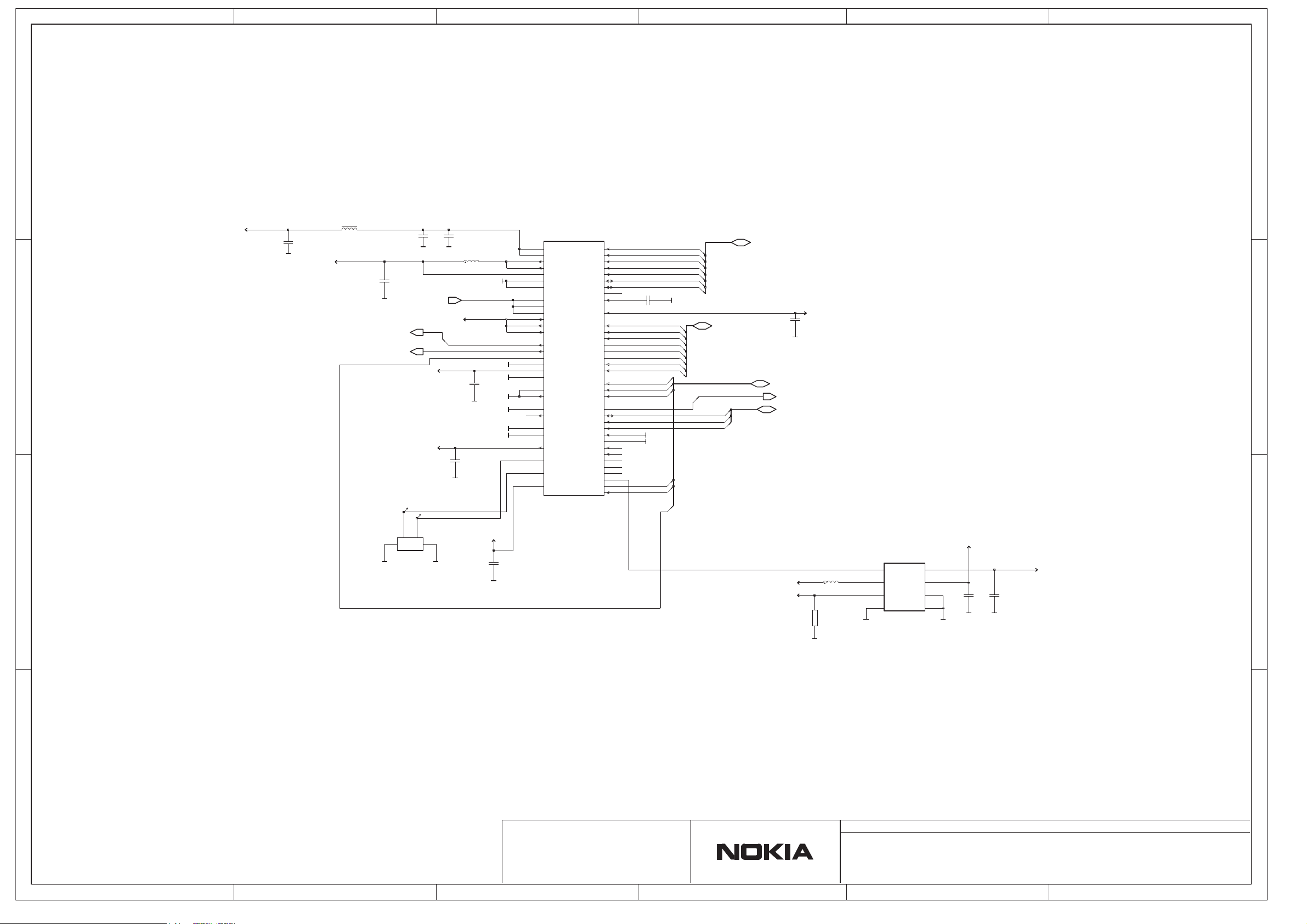

Page 4

1

2800-2899

2900-2999

2200-2399

D

C

B

A

D

C

6

2 3 4 5 6

B

A

1 2 3 4 5

SIM(6:0)

SLOWAD(6:0)

TXC(2:0)

TXC_CONV(1:0)

USB_ACI(7:0)

XAUDIO(5:0)

A2200

BB_ASSEMBLY

POWER

basic

ACI(1:0)

AUDIO(6:0)

CBUS(3:0)

CHARGER

DIG_AUDIO(5:0)

EMINT(1:0)

H_BRIDGE(3:0)

INTUSB(8:0)

INT_SIM(5:0)

PUSL(7:0)

PWRONX

MESSI_CMT(25:0)

MMC_CMT(15:0)

NAND(15:0)

PCM(3:0)

PUSL(7:0)

RFCLK_I(1:0)

RFCONV_I(11:0)

RFCTRL_I(8:0)

SPI_CMT(3:0)

TXC(2:0)

USB_CMT(8:0)

ACI(1:0)

AUDIOCTRL(5:0)

CAM_CTRL_CMT(7:0)

CBUS(3:0)

CCP_CMT(3:0)

DIG_AUDIO(5:0)

EMINT(1:0)

ETM(16:0)

FCI_CMT(3:0)

GEN_CTRL_CMT(20:0)

I2C(1:0)

INT_SIM(5:0)

IRDA_CMT(2:0)

JTAG(6:0)

KEYB_CMT(20:0)

LPRF_CMT(6:0)

no_ape

USB_CONN

INTUSB(8:0)

PUSL(7:0)

USB_CMT(8:0)

RAP

rapstack

GPSCLK

LPRFCLKLPRFCLK_I

RFCLK(1:0)

RFCLK_I(1:0)

RFCONV(11:0)

RFCONV_I(11:0)

RFCTRL(8:0)

RFCTRL_I(8:0)

RFPWR(4:0)

TXCCONV(1:0)

TXCCONV_I(1:0)

schematic

RF_BB

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

GND

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

Name

CMT_Engine Top level

This document is property of Nokia Corporation

SPI_CMT(3:0)

SPI_CMT(3:0)

AUDIOCTRL(5:0)

IRDA_CMT(2:0)

I2C_CMT(1:0)

XAUDIO(5:0)

USB_ACI(7:0)

TXC_CONV_I(1:0)

TXC(2:0)

SLOWAD(6:0)

SIM(6:0)

PWRONX

PUSL(7:0)

PUSL(7:0)

PUSL(7:0)

INT_SIM(5:0)

INTUSB(8:0)

H_BRIDGE(3:0)

EMINT(1:0)

DIG_AUDIO(5:0)

DIG_AUDIO(5:0)

CHARGER

CBUS(3:0)

CBUS(3:0)

AUDIO(6:0)

ACI(1:0)

RFPWR(4:0)

TXCCONV(1:0)

RFCONV(11:0)

RFCTRL(8:0)

RFCLK(1:0)

LPRFCLK

LPRFCLK_I

LPRFCLK_I

CAM_CTRL_CMT(7:0)

CAM_CTRL_CMT(7:0)

CCP_CMT(3:0)

CCP_CMT(3:0)

ETM(16:0)

ETM(16:0)

FCI_CMT(3:0)

FCI_CMT(3:0)

GEN_CTRL_CMT(20:0)

GEN_CTRL_CMT(20:0)

JTAG(6:0)

JTAG(6:0)

KEYB_CMT(20:0)

KEYB_CMT(20:0)

LPRF_CMT(6:0)

LPRF_CMT(6:0)

MESSI_CMT(25:0)

MESSI_CMT(25:0)

MMC_CMT(15:0)

MMC_CMT(15:0)

PCM(3:0)

RFCLK_I(1:0)

RFCONV_I(11:0)

RFCTRL_I(8:0)

Page 5

B

D D

2200-2299

2300-2399

A

4 5 6

1

B

A

31

C

2

2 3 4

without_diode

BETTY

CBUS(3:0)

CHARGER

CHSWSTAT

EMINT(1:0)

INTUSB(8:0)

PUSL(7:0)

SLOWAD(6:0)

USB_ACI(7:0)

5 6

C

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

USB_ACI(7:0)

XAUDIO(5:0)

Energy management

Name

VILMA

vilma_nokia_av

ACI(1:0)

AUDIO(6:0)

CBUS(3:0) CHSWSTAT

DIG_AUDIO(5:0)

EMINT(1:0)

H_BRIDGE(3:0)

INT_SIM(5:0)

PUSL(7:0)

PWRONX

SIM(6:0)

SLOWAD(6:0)

TXC(2:0) TXC_CONV(1:0)

ACI(1:0)

XAUDIO(5:0)

TXC(2:0)

INT_SIM(5:0)

INTUSB(8:0)

PWRONX

CHARGER

AUDIO(6:0)

H_BRIDGE(3:0)

SIM(6:0)

TXC_CONV(1:0)

DIG_AUDIO(5:0)

CBUS(3:0)

EMINT(1:0)

PUSL(7:0)SLOWAD(6:0)

USB_ACI(7:0)

Page 6

BTEMP

WTXDET

LST

RFTEMP

LS

BSI

VCHAR

EARN

EARP

HFSPN

HFSPP

VIBRAN

VIBRAP

WATCHDOG ENABLE

C2231 between pins VBATH and GNDH

Note: With SleepClk line should be used Near-End Star Cluster topology,

which means that every conponent has own branch so they are not chained.

It is very important these branches are equal lenght and the star point

(dividing point) is near Vilma

3 6

1 52 4 6

B

D

2

B

A

3

C

4

A

5

C

1

D

WATCHDOG ENABLE

2k

R2200

GND

0

2

3

GND

2u2

C2202

C2203

2u2

VRCP1

3

GND

1 0

VBAT2

VBAT5

GND

VSIM2 VR1

GND

1

0

0

3

GND

/2 1u51

C2215

2x1u5

4

GND

GND

GND

4

J2222

J2223

1

GND

1u5

C22172x1u5

C2220

1 /2 1u5

2

GND

GND

GND

GND

J2216

J2217

VBAT

6

7

GND

Name

Vilma

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

0

2

1

3

GND

VBACK

VRFC

3 4 562

0

3

1

2

GND

C2232

2x1u5

1 /2 1u5

J2201

VBAT4

VBATH

GND

4

GND

GND

J2200

GND

/2 1u52

2x1u5

C2213

2

/2 1u51

2x1u5

C2213

1

2

4

5

GND

VBAT4

VBAT3

VBAT1

VBATCP

VBACK

1n0

C2205

2

VBAT3

VREF

/2 1u52

2x1u5

C2215

VBAT2

J2218

J2219

GND

2x1u5

C2228

1 /2 1u5

GND

0

GND

2

GND

VREF_INT

GND

1

0

1

VIO

5

2

GND

GND

0

VANAPMUVCC VAUX

G2200

VBAT5

1

VBATH

GND

3

5

1

0

1u0

C2226

GND

GND

0

1u0

C2225

VBAT

L2202

GND

220R/100MHz

1

VBAT

VBATCP

C2231

10u

1

VDRAM

5

6

3

0

B2200

32.768kHz

CrO

L9

R2210

100R

K9

LST

L1

L10

VDRAM

L11

BSI

MicData

L2

L3

AudClk

SerClk

L4

SlClk

L5

Gnd4

L6

TxCClk

L7

L8

CrI

Gnd2

RFTemp

K1

K10

Gnd6

K11

VBat2

K2

SIMDetX

PURX

K3

MBusTx

K4

K5

SerData

K6

VilmaInt

K7

TxCDa

K8

TM

HV

MicSub

J1

J10

HeadDet

AFC

J11

J2

LS

J3

WTxDet

J4

MBusRx

J5

SerSelX

ChSwS

J6

J7

TxC1

J8

VBack

J9

Mic2P

SleepX

G5

G6

TxCCtrl

WDDis

G7

VRef

G9

H1

Mic1P

H10

VRFC

H11

VR1

H2

Gnd5

MicB1

H3

H9

MBus

F11

VSATx

F2

F3

XEarR

Mic3PR

F5

GndTH

F6

Gnd1

F7

F9

RstX

G1

Mic2N

G10

VBG

G11

VIO

G2

MicB2

G3

E10

VAux

VBat6

E11

E2

XEarLC

XEarL

E3

Mic3NR

E5

E6

SIMIOC1

E7

SIMIOC2

E9

BTemp

XEarRC

F1

F10

VBat4

VBat1

C6

SIMDaC1

C7

C8

SIMDaC2

C9

VRCP1

Mic3P

D1

D10

VChar

D11

VBat5

Mic3N

D2

D3

EarN

PwrOnX

D9

E1

VAna

B6

B7

SIMClkC1

B8

Gnd3

B9

VSIM2

VSARx

C1

GndCP

C10

VBatCP

C11

C2

EarP

C3

HFSpN

C4

PMARN

C5

SIMRstC2

SIMDa2

A7

VSIM1

A8

VBat3

SIMClkC2

A9

B1

GndH

B10

FlyHigh

Gnd7

B11

B2

HFSpP

VBatH

B3

EarDaL

B4

B5

SIMRstC1

SIMDa1

N2200

AVILMA_1.05C

VibraN

A1

A10

VCP

A11

FlyLow

VibraP

A2

A3

PMARP

A4

EarDaR

SIMClk1

A5

A6

SIMClk2

GND

J2202

J2203

VBAT1

GND

2x1u5C2228

2/2 1u5

C2211

4u7

2x1u5

C2227

2 /2 1u5

GND

C2220

2 /2 1u5

GND

GND

2x1u5

220R/100MHz

1u0

C2222

2x1u5

2 /2 1u5

L2205

C2232

0

GND

1u5

C2201

GND GND

1u5

C2216

C2227

2x1u5

1 /2 1u5

J2212

ACI(1:0)

DIG_AUDIO(5:0)

XAUDIO(5:0)

EMINT(1:0)

USB_ACI(7:0)

SLOWAD(6:0)

PWRONX

TXC_CONV(1:0)

AUDIO(6:0)

INT_SIM(5:0)

CBUS(3:0)

PUSL(7:0)

SIM(6:0)

TXC(2:0)

CHSWSTAT

H_BRIDGE(3:0)

Page 7

1

C

4

A

5

B

5

A

1

B

D

3

3

6

6

2

C

4

D

2

H5

DP_RXD

DM_TXD

H6

VCC

H7

H8

Master_PD1

0

FTX

G5

RXD2

G6

GND3

Master_PD2

G7

Slave_PU

G8

GenOut1

H1

H2

VM_CLK

H3

VO

CLK

H4

FSE0

F5

F6

VCCint

F7

VBAT3

VOUT

F8

G1

SenseM

RCV_FRX2

G2

VP_FRX

G3

G4

ChSwS

SlaveSWSet

E5

E6

VCharADC

VCharOut2

E7

E8

VCharOut1

SenseP

F1

PWM300

F2

F3

GenOut2

OEX

F4

RstX

D5

VCharOutK

D6

VCharIn2

D7

VCharIn1

D8

SMPSClk

E1

GND4

E2

E3

SleepClk

E4

C4

VCore

TestMode

C5

VCoreDef

C6

C7

VCharInK

LedOut

C8

D1

PurX

SleepX

D2

BettyInt

D3

Clk600

D4

B4

VBAT1

B5

SetCurr

B6

B7

GND5

B8

LedCoil

C1

CbusData

C2

CbusClk

CbusSelX

C3

A4

VBAT1

A5

VcoreDis

A6

TestOut

A7

GND5

A8

LedCoil

B1

VIO

VPP_VIO

B2

GND1

B3

VCoreCoil

N2300

BETTY_V2.1_V2.2_LFA

A1

FlashM

GND1

A2

A3

VCoreCoil

C2301C2300

10n

1

7

22u

FB

B3

OUT

C1

SW

C2

C3

PGND

GND

VOUT

GND

GND

N2301

TPS61061YZFR

A1

GND

EN

A2

A3

ILED

B1

VIN

4u7

C2315

VBAT

VBAT

GND GND

22uH

L2304

VBAT

C2314

1u

10n

C2304

GND

5

6

3

2

0

VIO

2x1u5

VBUS

GND

GND

/2 1u52

C2312

GND

GND

GND

2

1

0

1u0C2303

J2307

J2306

VBAT

GND

5

6

3

SENSE

CURRENT

PMR03EZPJU10L

R2300

1

23

4

7

VBAT

BGND GND

4

GND

4

4

GNDGND

C2309

22u

C2307

1u0

GND

220R/100MHz

L2301

C2312

2x1u5

GND

5

GND

/2 1u51

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

VCORE

C2302

22u

Betty

Name

GND

GND

GND

GND

SETCURR

R2303

33R

10uH

L2302

1

VLEDOUT

1

GND

3

2

1

2

0

CHARGER

SLOWAD(6:0)

USB_ACI(7:0)

INTUSB(8:0)

CHSWSTAT

PUSL(7:0)

CBUS(3:0)

EMINT(1:0)

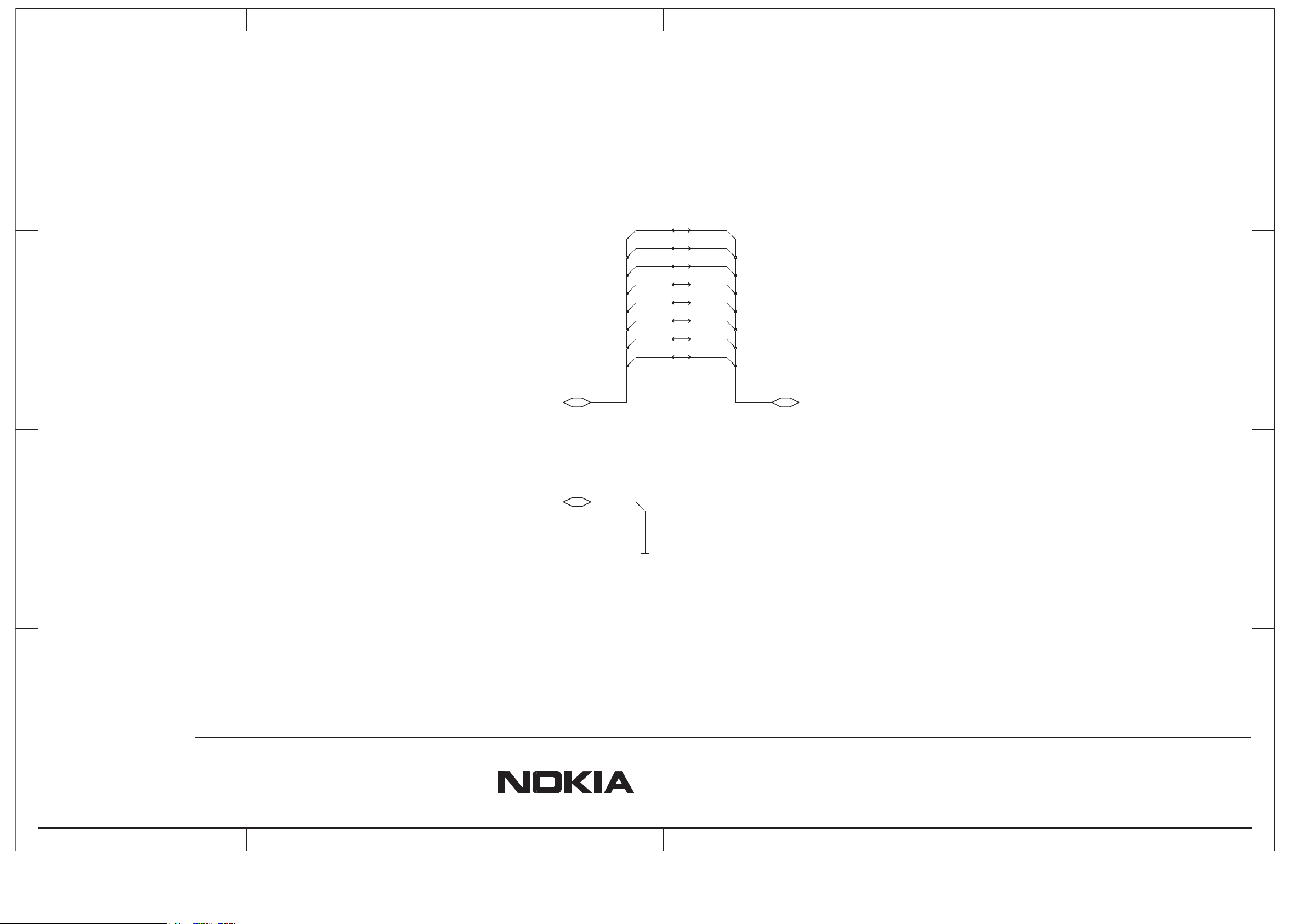

Page 8

B

A

APESleepX

4 5 6

21

1 3

4

GND

2

3 4 5 6

D

C

B

A

D

C

5

4

6

1

2

3

44

5

6

7

00

1

2

3

Name

USB Connections without APE

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

INTUSB(8:0) USB_CMT(8:0)

PUSL(7:0)

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

Page 9

5432

2 3 4 5 6

D

C

TOP SHEET

CBB5X

B

A

D

C

A

1

1

B

6

1

VRCP1

RF IF

Name

VREF

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

3

VR1

2

RFCTRL(8:0)RFCTRL_I(8:0)

LPRFCLK_I

GPSCLK

RFCLK_I(1:0) RFCLK(1:0)

LPRFCLK

RFPWR(4:0)

RFCONV_I(11:0) RFCONV(11:0)

TXCCONV(1:0)TXCCONV_I(1:0)

0

VBAT

Page 10

SIMVCC

1V8

MMCCmdDir

PUEN (NOT USED)

MMCCClk

MMCDa1

D1

VBAT

IRTX

!WR

SPI_DATA_IN

A

!RD

D7

3

D5

2

D3

ROW3

Bypass for memory

D

Not_Used

TIMESTAMP

TE Main

Bypass for CPU

INT

B

MMC_Hotswap

B

MMC_WP

Test point for SPI CLK in EMU block

D/!C

5

COL1

3

MMCDaDir1

D

ROW5

COL4 (free)

!CS Main

SWP

!CSSub

NOTE! D2801 must have same coordinates and rotation as D2800

MMCL_SShut_Dn

1

IRSD

RESET

COL0

PMUVCC

IRQ

MMCFb_Clk

ROW0

C

ROW4 (free)

RXRESET (NOT USED)

MMCDet

4

MMCDaDir

D2

Not_Used

C

IRQ

VEN

RESET

MMCDa2

COL2

D6

PA EN

1

FCIINT

SPI_CLK

PLUG DET

6

ENA

Genio 72, internal or external boot

COL3

4

ROW2

FCIPWREN

Not_Used

MMCDa3

AUDIO/DATA CTRL

SPI_DATA_OUT

1V8

2

IRRX

A

MMCCmd

FCISDA

Not_Used

5

MMCDa0

ROW1

SPI_CS

D0

TESub

6

VEN

XTAL1

FCISCL

D4

C2804

100n

na

FDG6308P

V2801

6 D1

3D2

G1 2G25

S1 1

4 S2

100n

C2811

0

8

1

9

3

3

C2823

1n0

11

0

1

9

14

1

GND

16

2

VRFC

100n

C2802

C2817

100n

3

VCORE

4k7

R2803

1

VIO

13

11

0

6

GND

100n

C2814

1

VIO

8

10

7

2

1

1

GND

6

VCORE

GND

VIO

VIO

3

J2803

VIO

9

R2801

3

R2807

100R

5

6

7

8

9

3

4k7

X2800

1

10

11

12

13

14

15

16

2

3

4

0

15

2

0

VDRAM

10

5

2

0

4

1

GND

C2803

100n

0

2

1

3

GND

GND

9

0

11

5

7

5

GND

VIO

6

C2810

100n

GND

1

VRFC

13

R2800

10R

GND

5

0R

R2805

C2806

100n

GND

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

3

8

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

RAPStack

Name

2

7

GND

3

1

0

13

2

GND

VCORE

VIO

100n

C2820

GND

0

1

1

GND

C2821

100n

S72NS512PE0KJFLG

D2801

16Mx16 DDR DRAM

COMBO 32Mx16 NOR

dangle

A1

2

0

1

Y21

GenIO9

USBVP_FRX

Y3

SysClk

Y4

Y5

GenIO25

Y6

GenIO23

USBVO

Y7

VSSCORE6

Y8

GenIO18

Y9

Y13

GenIO31

Y14

CBusClk

GenIO44

Y15

GenIO39

Y16

Y17

VDDSIO4

GenIO34

Y18

GenIO13

Y19

GenIO8

Y20

USBRCV_FRX2

GenIO5

W20

GenIO4

W21

GenIO6

W22

W3

USBFSE0_FTX

VDDCORE4

W4

PMARN

Y10

Y11

VDDSIO3

Y12

GenIO65

V2

V20

GenIO33

GenIO1

V21

V22

GenIO3

GenIO7

V23

VSSCORE5

V3

V4

USBOEX

W1

GenIO62

W2

VDDDSP2

U17

VSSDSP2

U20

GenIO2

U21

GenIO0

U4

GenIO69

U7

GenIO73

VDDCORE5

U8

GenIO19

U9

USBDSyncClk

T3

GenIO58

T4

T7

GenIO70

AudioClk

U10

U11

VDD2

U12

CBusDa

U13

VDDDSP1

U14

VSSDSP1

GenIO43

U15

U16

VDDDSP3

GenIO15

R21

GenIO32

R22

R3

RX2

GenIO57

R4

R7

GenIO71

GenIO37

T17

T20

VDDSIO5

GenIO64

P20

VSSDSP3

GenIO38

P21

P3

TXA

GenIO59

P4

GenIO60

P7

GenIO52

R1

R17

VDDSIO6

GenIO56

R2

R20

RX1

N2

I2SSCLK

N20

GenIO36

N21

N22

GenIO41

RFBusDa

N3

TXReset

N4

N7

TXP

VDDCORE7

P17

VDDCORE3

L7

M1

RFBusEn1X

I2SWS

M17

VSSCORE9

M20

M23

GenIO42

M3

VSSATX

M4

VDDCORE2

M7

VDDSIO1

N17

GenIO47

VDDCORE8

K20

K22

VDD1

VDDATX

K3

K4

TxIP

RxQP

K7

GenIO46

L17

VSSCORE10

L20

VSSASUB

L3

L4

TxIN

RxIN

J2

GenIO49

J20

GenIO48

J21

J22

GenIO68

RxIP

J3

J4

VSSCORE3

J7

RxQN

K17

GenIO67

VDDSIO7

H20

GenIO51

H21

GenIO16

H22

TahvoInt

JTDO

H3

H4

RFClkN

H7

VSSA

J1

VSSCORE2

J17

VDDMCU1

GenIO72

G16

VSSMCU2

G17

ACIRx

G20

SIMIODa1

VSSMCU1

G21

G3

VDDA

RFClkP

G4

VrefN

G8

G9

VrefP

H17

EarDataR

F23

F3

JTrst

F4

JTClk

G10

Iref1

G11

TXQP

G12

TXQN

VDDCORE11

G13

G14

VSSCORE14

G15

VDDCORE1

E1

VDDARX

E20

GenIO54

E22

E3

TMAct

E4

EMU0

VSSARX

F20

GenIO17

F21

SIMIOCtrl1

F22

GenIO55

D21

D22

VSSCORE11

APESleepX

D3

D4

VDDSIO10

JTDI

D5

ETMPipeB1

D6

D7

SleepClk

JTMS

D8

ETMPipe2

D9

D13

VDDCORE9

ETMPkt5

D14

SpecialIO3

D15

D16

SpecialIO2

GenIO61

D17

TxCClk

D18

D19

TxCDa

RetuInt

D20

C3

C4

PURX

ETMPkt4

C5

ETMPkt7

C6

ETMSyncB

C8

C9

ETMPkt0

D10

ETMSync

VDDCORE10

D11

D12

VDDSIO9

VSSCORE4

C14

C15

ETMPkt3

SIMClk1

C16

C17

GenIO63

VDDCORE12

C18

SpecialIO1

C19

SpecialIO0

C20

C21

VDDSIO8

VSSCORE1

GenIO53

B21

NC_BGA

B23

B3

SleepX

ETMClk

B9

C10

ETMPipe0

C11

VSSCORE13

C12

RFBusClk

VDDMCU2

C13

AC9

GenIO22

B1

NC_BGA

B10

ETMPipe1

B12

ETMPkt6

B15

VSSCORE12

B17

ACITx

B19

TxCDaCtrl

B2

NC_BGA

AC1

NC_BGA

MicData

AC13

AC15

SMPSClk

VSSCORE8

AC19

AC2

NC_BGA

NC_BGA

AC22

NC_BGA

AC23

GenIO26

AC4

GenIO20

GenIO50

AA9

NC_BGA

AB1

AB13

I2SSD1

AB16

GenIO35

VDDCORE6

AB19

NC_BGA

AB23

AB4

VDDSIO2

AB8

GenIO24

GenIO11

GenIO12

AA20

AA21

GenIO10

USBVM_Clk

AA3

GenIO28

AA4

AA5

GenIO27

GenIO29

AA6

GenIO21

AA7

AA8

VSSCORE7

AA11

AA12

PMARP

AA13

GenIO30

CBusEn1X

AA14

GenIO45

AA15

AA16

I2SSD2

AA17

GenIO40

GenIO14

AA18

AA19

NC_BGA

A2

A22

NC_BGA

A23

NC_BGA

A3

ETMPipeB2

A4

ETMPipeB0

ETMPkt2

A5

ETMPkt1

A7

AA10

EarDataL

4

D2800 RAP3GS_V2.0E-PA

A1

NC_BGA

VPP

2k2

R2808

VPP

0

GND

1

GND

6

7

10

2

0

5

C2812

0

100n

2

6

13

0

0

100n

C2808

5

VIO

6

4

4

PMUVCC

1

1

4

7

1

GND

VIO

C2809

100n

3

1

0

VBAT

6

GND

0

6

4

2

4

C2815

100n

VCORE

6

2

3

100R

R2806

9

2

0

1

9

0

5

VDRAM

2

5

8

GND

8

VIO

SIMVCC

3

GND

100n

C2818

1

0

7

0

10

R2802

4k7

6

C2813

100n

1

14

SWP

J2801

J2802

0

10

2

5

2

1

3

5

12

4

0

0

1

3

VCORE

C2800

100n

8

2k2

R2809

GND

12

100n

C2805

1

100n

C2807

15

0

0

14

VCORE

C2819

100n

1

GND

2

12

8

8

12

GND

11

7

5

0

R2804

1k0

15

5

2

4

1

6

4

2

2

6

3

100n

C2822

C2801

GND

GND

2

4

100n

GND

7

4

3

3

0

1M0

R2810

na

SDRLDQS

U3

19

V1

TOP_VCCnor0

W23

TOP_Vddq0

17

Y1

Y2

22

TOP_Vssq5

Y22

Y23

TOP_Vssq4

16

T2

T21

4

T22

2

1

T23

TOP_Vpp

U1

TOP_VCCnor1

U2

U22

0

U23

M22

N1

FlsCSX

N23

5

20

P1

18

P2

P22

SDRDQML

P23

6

R23

3

T1

21

K23

L1

TOP_Vss5

TOP_Vss6

L2

8

L21

L22

SDRDQMU

SDRCLKX

L23

M2

23

M21

SDRCLK

7

G23

TOP_Vss2

H1

H2

TOP_Vss1

12

H23

11

J23

TOP_Vss3

K1

K2

TOP_Vss4

9

K21

10

E2

SDRUDQS

E21

15

E23

TOP_Vccq0

F1

F2

FlsWEX

G1

TOP_Vccq1

G2

TOP_Vss0

13

G22

14

C1

C2

0

TOP_Vssq2

C22

TOP_Vssq1

C23

C7

2

FlsRSTX

D1

FlsOEX

D2

D23

TOP_Vssq3

FlsWaitX

B20

TOP_Vdd0

B22

TOP_Vssq0

8

B4

B5

9

1

B6

3

B7

4

B8

FlsADVX

AC6

TOP_Vdd5

TOP_Vdd4

AC7

AC8

2

5

B11

B13

7

TOP_Vssd5

B14

B16

TOP_Vssd3

B18

TOP_Vddq4

TOP_Vssd0

AC14

AC16

TOP_Vssd1

AC17

TOP_SDRAdres

AC18

8

AC20

SDRRASX

AC21

6

TOP_VCCmm0

AC3

AC5

TOP_VCCmm1

AB3

TOP_/CEmm

AB5

TOP_INT

TOP_/CEd

AB6

AB7

3

AB9

1

AC10

0

AC11

14

AC12

13

AB14

11

AB15

SDRWEX

AB17

9

AB18

7

AB2

GenIO66

SDRCASX

AB20AB21

5

AB22

4

A9

12

FlsCS2X

AA1

AA2

24

AA22

TOP_Vssd2

TOP_Vdd3

AA23

AB10

10

SDRCKE

AB11

AB12

12

A15

A16

TOP_Vddq3

TOP_Vddq5

A17

A18

TOP_Vddq2

TOP_Vddq1

A19

A20

TOP_Vdd2

TOP_Vdd1

A21

A6

10

A8

11

SDRDa

SDRAd

RAP3GS_V2.0E-PA

D2800

ExtAdDa

13

A10

A11

14

6

A12

15

A13

A14

FlsClk

TOP_Vssd4

2

5

VIO

1

1

100n

C2816

IRDA_CMT(2:0)

DMIC_EN

AuxMicData

GEN_CTRL_CMT(20:0)

INT_CAM_to_HOST

CAM_CLOCK

INT_CAM_to_HOST

INT_HOST_to_CAM

CAM_VCTRL_1V82V8

CAM_Reset

PUSL(7:0)

PUSL(7:0)

I2C(1:0)

I2C(1:0)

BTRSTX

BTDAIN

BTDAOUT

BTCTS

BTRTS

BTWAKE

BTHOSTWAKE

GPS_CMT(2:0)

SPI_CMT(3:0)

AuxMicData

VPPLOCK

AUDIOCTRL(5:0)

I2C_SCL

CCP_CMT(3:0)

BTH_CLK_REQ

KEYB_CMT(20:0)

!Reset

MESSI_CMT(25:0)

CAM_CTRL_CMT(7:0)

!Reset

DMIC_EN

BTWAKE

CAM_Reset

CAM_VCTRL_1V82V8

INT_HOST_to_CAM

CAM_CLOCK

MMC_CMT(15:0)

I2C_SDA

BTH_CLK_REQ

I2C(1:0)

VPPLOCK

INT_SIM(5:0)

NAND(15:0)

BTHOSTWAKE

BTRTS

BTCTS

BTRSTX

BTDAOUT

BTDAIN

LPRF_CMT(6:0)

FCI_CMT(3:0)

RFCLK_I(1:0)

RFCONV_I(11:0)

ACI(1:0)

DIG_AUDIO(5:0)

CBUS(3:0)

ETM(16:0)

PCM(3:0)

EMINT(1:0)

JTAG(6:0)

RFCTRL_I(8:0)

TXC(2:0)

USB_CMT(8:0)

Page 11

SCL_LORES

HIRES_CCPCLKN

4

5

5

VCAP

CLK_LORES

D

3 5

SDA_HIRES

1 3

2

CCPClkP

CAM_VCTRL_1V82V8

D

4

SPI_DAO CCPCLKN

CCPDATAP

LORES_CCPDATAP

2

SPI_CS

SPI_CLK

C

SPI_DAIN

B

have switched

SDA_LORES

(Second source 4858138)

SMD mounted camera (ACME Lite)

If needed

B

CAM_CLOCK

A

6

GEMINI

Note: When compare to Julie unstack LORES_I2C and HIRES_I2C

Use TxMask ?

Connect to VCAM_1V8 or VBAT ??

FLASH_EN

4

CCPDATAN

HIRES_CCPDATAN

FLASH_LED_Anode

A

INT_HOST_to_CAM

VCAM_2V8

6

HIRES_CCPCLKP

4

A

62

VCAM_1V8

C

1

FLASH_INT

FLASH_SYNC

LORES_CCPDATAN

1

B

Julie PDM code change from 4341530(B0.5) to 4342492(B1) start B1

D

CAM_RESET

3

5

CCPClkN

XSHUTDOWN_LORES

SCL_HIRES

C

CLK_HIRES

6

INT_CAM_to_HOST

D

DGND

1

A

3

B

FLASH_LED_Cathode

CCPDATAP

HIRES_CCPDATAP

CCPCLKP

CCISDA

If needed

XSHUTDOWN_HIRES

CCPDATAN

2

JTAG

XSHUTDOWN

EXTCLK

CCISCL

LORES_CCPCLKP

LORES_CCPCLKN

C

100n

2351017

C1421

J1412

1

GND

2351017

C1405

GND

100n

Z1402

VCAM_1V8

VCAM_1V8

2

Z1403

VCAM_1V3

VCAM_1V8

VBAT

1

GND

L1403

3203841

120R/100MHz

1

/2 1u52

2710203

2x1u5

C1415

100n

C1411

0

GND

J1410

1

0

VCAM_1V8

0

0

VCAM_1V8

3

R1400

1430778

10k

2351061

GND

SHIELD

A1401

FLASH

GND

C1402

10u

J1406

3

MA21D34001JN

4111149

V1400

C1409

27p

120R/100MHz

3203841

L1402

31

GND

GND

32

4

CLKP

5

CLKN

EMC_GND

6

7

GND

VANA

8

DATAP

9

24

EMC_GND

25

GND

GND

26

27

GND

GND

28

29

GND

3

GND

GND

30

VCAP1V2

18

EMC_GND

19

DATAN

2

VCAP

20

21

GND

EXTCLK

22

23

DGND

1

EMC_GND

VDIG

10

11

NC

GND

12 13

AGND

14

XSHUTDOWN

15

SCL

SDA

16

NC

17

VS6555R0H9

N1402

J1404

GND

1

C1412

100n

VCAM_2V8

GND

GNDGND

R1410

100R

2x1u5

VCAM_1V8

0

J1411

GND

J1402

/2 1u51

C1415

2710203

C1416

2u2

J1403

GND

C1406

0

VCAM_2V8

R1401

1430796

47k

C1424

2351017

100n

2351017

100n100n

2351017

VCAM_1V3

GND

C1425

Z1404

GND

Z1401

GND

0

2

L1404

600R/100MHz

120R/100MHz

3203855

L1410

VCAM_2V8

5

R1404

100R

33R

1430714

R1412

C1418

2351017

100n

3649178

2u2H

0

1

L1401

L1407

100n

2351017

C1403

100R

R1405

1uH

600R/100MHz

3203755

3

L1405

GND

120R/100MHz

3203841

L1406

100n

2351017

C1417

J1408

GND

JULIE

A1402

SHIELD

GND

0

R1403

3k3

100n

C1414

C1419

2351017

100n

100R

C1400

4u7

2351015

J1407

GND

VCAM_1V8

R1411

X1400

5469543

1

2

J1413

27p

C1427

VCAM_1V8

6

3

2

HPLED

9

GND

1

GND

GND

GND

16

STR

2

SETF

3

SCL/CTRL1

4

SDA/CTRL0

SETI

5

6

ILED

7

OUT

GND

8

ADP1653ACPZ-R7

SETT

1

INTF

10

11

_INT

12

PGND

13

LX

VDD

14

EN

15

2

J1401

N1400

17= GND

4348519

GND

3

0

J1400

/2 1u51

C1426

2710203

2x1u5

1

GND

R1409

1419075

2kGND

600R/100MHz

L1411

GND

2

C1429

27p

3k3

R1408

GND

GND

VCAM_1V3

R1407

3k3

0

J1409

C1

EN

FB

C3

GND

GND

C1410

10u

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

4348537

N1403

LM3677TLX-1.82_NOPB

U//U

A1

Vin

GND

A3

SW

B2

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

Camera

Name

2k

1419075

R1406

GND

C1407

2320546

27p

2320143

C1431

GND

2

GND

220n

GND

L1409

3203855

120R/100MHz

GND

1

C1401

27p

10u

GND

GND

GND

2

C1413

GND

28R/100MHz

3203775

L1400

GND

3

VBAT

3

4

5

6

7

8

9

R1413

1430714

33R

12

2

P7

GIO4/INT2

P8

GIO17

P9

GIO16

GND

X1402

5407315

Part is not suitable for dual pass SMD process

1

10

11

N8

GIO8

N9

GIO11

P11

GIO29

P12

GIO28/INT1

P3

COIN7

P4

VD0

P5

COIN3

P6

PCLK0

N11

GIO30

GIO27

N12

COIN8

N2

N3

COIN6

N4

COIN5

N5

COIN2

N6

GIO23

N7

GIO7/INT3

M14

NC

M2

COIN9

M3

CLK_TX_THRU0

M4

HD0

M5

COIN1

M7

GIO22

GIO9

M8

M9

GIO10

L3

CLK_TX_THRU1

COIN4

L4

COIN0

L5

SYSCLK

M1

M10

GIO12

SCL0

M11

M12

SDA0

M13

NC

J4

VDDA

K1

HSSIX_SN

K13

NC

K14

DNC

K2

HSSIX_SP

VSSA

K3

L13

NC

DNC

L14

HSSIX_IREF

TXVSSA1

G4

G5

TXVDDA1

H13

DNC

DNC

H14

H4

TXVSSA

HSSIX_DN

J1

HSSIX_DP

J2

J3

TXVDDA

RXVSSA

F4

RXVDDA

F5

HSSIR_DN1

G1

VDDDLL

G10

G13

DNC

DNC

G14

HSSIR_DP1

G2

G3

E1

HSSIR_SN0

E2

HSSIR_SP0

HSSIR_SN1

F1

VSSDLL

F10

F13

DNC

F14

DNC

HSSIR_SP1

F2

HSSIR_IREF

F3

C7

DNC

DNC

C8

C9

DNC

D1

HSSIR_DN0

DNC

D14

D2

HSSIR_DP0

D3

TDO

D4

TDI

C11

DNC

C12

DNC

C13

DNC

DNC

C14

C2

TMS

C4

WAKEUPX/INT0

SDI0

C5

C6

GIO2

DNC

B2

TRSTN

B3

TCK

B4

BTSEL

SDO0

B5

B6

RSTNX

B8

DNC

B9

DNC

DNC

C10

A5

SDEN0

A6

GIO0

DNC

A8

DNC

A9

DNC

B10

B12

DNC

B13

DNC

B14

B7,B11,E9,E10,E11,E13,D13,F11,G11,H10,H11,J11,J13,N14= GND

L9,L10,L11,L12,P10,P13=

A1,A2,D5,H5=

A7,A11,D10,D11,D12,E12,E14,F12,G12,H12,J12,J14,K10,K11,K12,N13=

D8,D9,E8,J10=

OMAP-DM500

N1401

A10

DNC

DNC

A12

A13

DNC

A14

DNC

A3

TEST

SCLK0

A4

VCAM_1V8

VCAM_1V8

VCAM_1V8

VCAM_1V8

F6,F7,F8,F9,G6,G7,G8,G9,H6,H7,H8,H9,J6,J7,J8,J9,H1,H2= VCAM_1V3

B1,C1,L1,N1,P1,L2,E4,K4,E5,J5,K5,E6,K6,E7,K7,K8,L8,K9,N10,P14,E3,H3,D6,D7= GND

L6,L7,M6,P2= VCAM_1V8

2

GND

C1422

2351017

100n

C1408

J1405

1

27p

2320546

2x1u5 27p

C1430

3k3

R1402

/2 1u52

2710203

C1426

C1404

1

-2.85-NOPB

N1405

4341561

VEN

MODE

GND

VOUT

VIN

2351017

100n

GND

VBATT

EN

1

GND

VCAM_1V3

LP3987ITLX

2351017

C1423

-1.3

N1404

4346967

LP5952TLX

VIN

VOUT

0

3

100n

LORES_CCP(3:0)

100n

2351017

C1420

FLASH_CONN(2:1)

HIRES_I2C(1:0)

LORES_I2C(1:0)

LORES_I2C(1:0)

CAM_CTRL_CMT(7:0)

SPI_CMT(3:0)

CCP_CMT(3:0)

HIRES_CCP(3:0)

Page 12

D

SOFT RIGHT

B

D/!C

!RD

63

LED2+

Vdd

LED1+

LED2-

LED1-

1

B

1

D

5

#

5

Vddi

D

D4

5

D5

D0

COL2

ROW5

2

D/!C

1

3

!RD

D7

D0

!WR

D4

D2

D1

D3

!Reset

D

A

!Reset

D5

!CS Main

C2407 is a "nice to have" component

COL2

Vol+ Vol-

ROW4

Keyboard Light

7

4

*

4

!WR

On Off Buttom

6

!WR

D5

TE Main

D0

D2

D3

D1

D4

343

A

SOFT LEFT

END

B

ROW2

SEND

5

2

CC

1

ROW3

ROW1

COL1

D7

TE Main

!CS Main

C

!CS Main

D6

2

2

ROW0

D6

0

3

D7

TE Main

A

!Reset

COL0

1

COL3

D/!C

!RD

9

4

4

ROW2

ROW1

6

COL0 COL1 COL3

B

ROW3

A

6

C

Display

COL4

D3

LCD

D2

D1

D6

Main Disp.

5

2

KEYS ( ROW must be more positive than COL )

S2425

1

2 3

4

8

6

ROW0

GND

1

1

0

8

D2

In6

D3

GND

D4

Out7

D5

Out6

S2412

A4

Out2

A5

Out1

B1

In3

B3

GND

B5

Out3

C1

In5

C2

In4

C3

GND

C4

Out5

C5

Out4

D1

In7

EMIF07-LCD02F3

Z2400

A1

In2

A2

In1

GND

A3

1

2 3

4

6

S2413

S2400

600R/100MHz

L2401

4

S2420

2

10

5.6V/15V/0.05J

R2414

GND

C2401

LWV38G-Q2R2-3K5L-3X4X-5-R18

V2410

1u0

GND

GND

V2412

LWV38G-Q2R2-3K5L-3X4X-5-R18

5.6V/15V/0.05J

6

GND

R2403

S2418

RIGHT

UP

LEFT

DOWN

S2404

S2416 S2417

100k

S2406 S2408

R2400

VAUX

S2407

GND

R2412

5.6V/15V/0.05J

C2400

1u0

5

2

S2403

9

S2405

GND

S2415

GND

OUT3

E3

E4

OUT4

OUT5

E5

S2411

GND

GND

GND

C2

GND

C3

GND

C4

GND

C5

OUT6

D1

OUT7

D2

OUT8

D3

OUT9

D4

D5

OUT10

OUT1

E1

OUT2

E2

IN2

A2

IN3

A3

IN4

A4

IN5

A5

IN6

B1

IN7

B2

IN8

B3

IN9

B4

IN10

B5

C1

GND

3

4

5

6

7

8

9

3

4129035

Z2402

EMIF10-COM01F2

IN1

A1

15

16

17

18

19

2

20

21

22

23

24

GND

VIO

X2400

5469499

1

10

11

12

13

14

L2400

600R/100MHz

8

330R

R2416

10

7

7

5

9

C2

GND

C3

Out5

C4

Out4

C5

In7

D1

In6

D2

GND

D3

Out7

D4

Out6

D5

VLEDOUT

In2

A1

In1

A2

A3

GND

Out2

A4

Out1

A5

In3

B1

GND

B3

Out3

B5

In5

C1

In4

3

0

Z2401

EMIF07-LCD02F3

GND

GND

R2410

330R

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

S2421

1

2 3

4

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

Name

UI

VLEDOUT

S2401

S2410

S2402

S2426

11

12

13

27p

C2402

SLOWAD(6:0)

UI_BTB(25:0)

I2C_CMT(1:0)

GEN_CTRL_CMT(20:0)

MESSI_CMT(25:0)

PUSL(7:0)

I2C_CMT(1:0)

KEYB_CMT(20:0)

PWRONX

SETCURR

Page 13

VIBRAP

D

AudioClk

EarP

EARPIECE

NOTE:

HFSPN

XearL

A

2

B B

XearLC

XAUDIO TESTPADS

To be placed close to Engine

IHF lines must be wide and low impedance

4 6

3

Microphone

DMIC_En

2

Vibra

4

Place near IHF pads

5

C

64

3

AuxMicData

To be placed close to Engine

HFSPP

1

A

C

EarN

DONAU

D

IHF

Vibra 6801147 change to 6800065 in B2

VIBRAN

1

5

Mic2P

Earpiece lines must be wide and low impedance

Mic2N

3

R2102

2 /2 16V

3

0

GND

0

1

2

9900821

E2101

E2103

9900821

GND

9900821

E2102

E2100

9900821

/2 16V1

R2105

GND

C2109

2320744

C2108

27p

1n0

GND

0

3

DATA

VDD

4

5GND

/2 16V2

R2105

7

B2100

MAB-03A-T-D

1

L/R

CLK

2

C2107

220R/100MHz

L2109

2

E2104

9900821

1

27p

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

Audio

Name

Copyright (C) Nokia Corporation. All rights reserved.

J2104 900X910

GND

9900821

E2105

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

27p

C2106

100n

C2100

GND

L2105

220R/100MHz

R2102

1 /2 16V

1 2

J2102

J2103

J2101

M

M2100

FM-0035-C1

GND

-

+

J2100

3

na

B2101

1

2-

+

3

4

L2107

3648903

30nH

L2110

220R/100MHz

na

5149037

B2102

+

-

GND

L2108

3648903

30nH

L2106

220R/100MHz

R2100

8

1

0

27p

1k0

1

2 3

4

C2105

H_BRIDGE(3:0)

AUDIO(6:0)

EARP

EARN

XAUDIO(5:0)

GEN_CTRL_CMT(20:0)

DIG_AUDIO(5:0)

MCZ1210AD102T

L2101

Page 14

CHARGER PLUG

C

3

2

XEARRC

2.5mm AV CONNECTOR

XEARR

C

MASTPD1

Pick and place pads

ID

VBUS

HS_EAR_R

3

2

SLAVEPU

NOTE! Place Z2002 near X2001

HS_GND

MASTPD2

6

ACI

DMTXD

PLUG_DET

5

XEARLC

A

61

PLUG_DET

5

FCC ID: QTKRM-396

IC: 661AD-RM396

Micro USB Connector (B-Type)

D+

AUDIO/DATA_CTRL

1

4

MIC2P

Use together with vilma_nokia_av

1825133

R2002

VAR

na

0

D-

HS_EAR_L

XEARL

4

DD

PA_EN

A

B

DPRXD

HS_MIC

MIC2N

B

W=0.10

Microstrip

900X822

Z2002

STRIPLINE_0.1

RES_NTC

VAR

CHIP VARISTOR VWM14V VC50V 0402

14V/50V

34

GND

GND

1

Mlin

W=0.10mm L=mm

L=

GND

DLM11GN601SZ2D

L2002

3203805

CHIP BEAD ARRAY 2X600R 0405

DLM11GN601SZ2D

1 2

CAP

1u

Cap

CHIPCAP X5R 1U K 6V3 0402

1u0

2351009

CAP

C2023

GND

2

CAP

1u

Cap

CHIPCAP X5R 1U K 6V3 0402

1u0

2351009

CAP

C2021

C2022

CAP

2351009

1u0

CHIPCAP X5R 1U K 6V3 0402

Cap

1u

CAP

Chipcap X7R 10% 16V 0402

10n

2320778

C2014

CAP

C2020

CAP

2351009

1u0

CHIPCAP X5R 1U K 6V3 0402

Cap

1u

CAP

2351053

C2012

CAP

3

CAP

10.0n

Cap

2320604

C2008

CAP

CAP

470n

Cap

CHIPCAP X5R 470N K 25V 0603

470n

VBUS

CAP

18.0p

Cap

Chipcap 5% NP0

18p

SMD CONN AUD/VID 4POL 30V 2A 2.5MM DIA

1

2

3

4

5

6

7

8

F2000

F0603E2R00FSTR

5119039

SM FUSE F 2.0A 32V

2A

GND

GND

GND

LGK1509-2301F

X2001

5469840

CAP

10.0n

Cap

Chipcap X7R 10% 16V 0402

10n

2320778

C2013

CAP

CAP

1u

Cap

CHIPCAP X5R 1U K 6V3 0402

1u0

2351009

CAP

C2006

CAP

2.2u

Cap

CHIPCAP X5R 2U2 K 6V3 0603

2316001

C2005

5

4

1

0

4

1

2

CAP

2u2

CAP

IN

OUT

VIO

C2004

2 /2 1u5

CAP

C2003

2318015

100n

CHIPCAP FEEDTHRU 100N M 25V 0805

Cap

100.0n

CAP_NETWORK

2x1u5

2x1u5

CAP_NETWORK

CAP_NETWORK

CHIPCAP NETWORK X5R 2X1U5 K 6V3 0405

2710203

C2004

1 /2 1u5

CAP_NETWORK

2x1u5

2x1u5

CAP_NETWORK

CAP_NETWORK

CHIPCAP NETWORK X5R 2X1U5 K 6V3 0405

2710203

A

1

VIO

VBAT

ESDA18-1F2

R2010

ASIP TVS BGA4

K

CAP

CAP

C2009

2320604

18p

Chipcap 5% NP0

Cap

18.0p

CAP

1

2

C2000

2320546

27p

Chipcap 5% NP0

Cap

27.0p

CAP

2

3

4

5

GND

na

X2000

CONN CHR DIA 2.0MM SHORT COMPRESS

5469849

DC_JACK_SHORT_2MM

SCL

D2

D3

SDA

D4

_SD

GND

GX60-5P_TYPE_B

CONN USB 5POL MICRO-USB B TYPE P0.65

X2002

1

LEFTINP

LEFTINM

B4

C1

VDD

GND

C2

RIGHTINP

C3

C4

RIGHTINM

D1

HPRIGHT

N2000

CPN

A1

A2

CPP

A3

GND

A4

VDD

HPLEFT

B1

B2

CPVSS

B3

220k

1430812

R2009

RES

0

GND

4346955

TPA6130A2YZHR

AF AMP TPA6130A2WCSP 2.5/5.5V

L2003

IND

7

VOUT

RES

220.0k

Res

Resistor 5% 63mW

GND

IND

68.0n

Ind

CHIP COIL 68NH J Q12/100MHZ 0603

68nH

3645011

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

GND

COM 7

SEC DISPLAY FRAME GND SPRING P2910

6443094

X2003

040-024131

System connector

Name

E2001

411CSC-054-50E

SPACER METAL

1

TS5A6542YZTR

N2001

4346887

IC ANALOG SWITCH SPDT LOW THRESHOLD CSP8

5= VOUT

GND2,8=

1 NO

3 NC

4

VIO

6 IN

R2011

6

0

SPACER METAL

411CSC-054-50E

E2000

9901006

1

9901006

RES

10.0k

Res

Resistor 5% 63mW

10k

1430778

RES

R

IP5311CX5_LF

Z2000

AVIF ASIP DOUBLE CHANNEL BGA5

C

C

R

A1 A2

B2

C1 C2

GND

VAR

R2003

1825133

14V/50V

CHIP VARISTOR VWM14V VC50V 0402

VAR

-

RES_NTC

RES

R2006

1430778

10k

Resistor 5% 63mW

Res

10.0k

RES

GND

IP4065CX11_LF

R2007

ASIP SILIC USB OTG / ESD BGA11

GND

900X910|1.3_CARBON

J2002

TEST_POINT

1k3

17k

33R

33R

15k

GND

GND

TEST_POINT

J2001

900X910|1.3_CARBON

CAP

C2002

2320546

27p

Chipcap 5% NP0

Cap

27.0p

CAP

IND

L2001

3203755

600R/100MHz

FERRITE BEAD 0.6R 600R/100MHZ 0402

Ind

IND

600R/100MHz

3203755

Z2001

IND

RES

R2001

1430804

100k

Resistor 5% 63mW

Res

100.0k

RES

GND

5

IND

Ind

FERRITE BEAD 0.6R 600R/100MHZ 0402

CHARGER

USB_ACI(7:0)

SLOWAD(6:0)

XAUDIO(5:0)

FM_ANT

AUDIOCTRL(5:0)

I2C(1:0)

GND

Page 15

1

A

Traceability pad

6

CLK

D

B

RXD2

C

A

42 5

32 5

ESD protection ??

C

B

BB5.0 have defined 7-pin test pad pattern

3

4 6

D

TXD

GND

X2060

5409309

1

RXD

1

10R

R2063

R2062

10R

R2064

ESDA14V2-4BF3

A1

A3

B2 GND

C1

C3

GND

10RR2061

VPP

J2060

1 2 3 4

6 7 8

1

3

0

GND

2

10R

R2060

Name

Production test pattern

USB_ACI(7:0)

VBUS

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

Page 16

D

2

Place C3401 colse to battery connector

C

6

B

4

BTEMP NTC

1

PLACE R3401 NEAR BATTERY CONNECTOR !!!

543

D

C

BTemp

BSI

B

A A

NOTE !! R3400 IS NEEDED IF VILMA IS FAR FROM BATTERY CONNECTOR !!!

5

6

1 2 3

C3403

15p

GND

C3401

22p

12p

C3402

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

GND

Name

Battery Connector

R3401

-t

GND

GND

BGND

+

1

GND2

BSI3

47k

2

3

X3400

VBAT

C3400

150u_10V

SLOWAD(6:0)

14V/50V

R3400

Page 17

MMCDa2

GND

4

C

B

D

3

MMC_WP

GND at the inner layer

after previous usage.

Connect to HOT_SWAP pin of MMC reader

D

3

C

DAT1

DAT0

to GND on top layer

if they are not discharged

CS/DAT3

DAT2

CMD

CLK

DAT0

DAT1

CS/DAT3

2

VDD

ALL LINES MUST BE SEPARATED AND SURROUNDED BY GND

5

CLK

MMCDa3

MMCLSShutDn

PIN 3 GND MUST NOT BE CONNECTED TO TOP LAYER GND

B

4

A

2

MMC_HotSwap

Don’t connect direct

Cards may not start properly,

61

Connect to massive

MMCDaDir1

651

A

CLK and DATA lines must be placed in strip-line layer

and routed with GND on all sides (transmission line)

DAT2

CMD

R4805 is to discharge VSD.

MMCFb_clk

MMCClk

MMCCmd

MMCCmdDir

MMCDaDir

MMCDa0

MMCDa1

GND

D1_B

11

5

4

C3205

100n

CLK_B

D0_A

CMD_ACDCMD_B

D0_B

D1_A

fCLK_A

DIR_1-3

WP

DIR_0

VBAT

D2_B

D3_A

VDDA

VDDB

D3_B

CLK_A

EN

GND

GND

3

4

5

6

7

8

SW1

N3200

LP3929TMEX-AACQ_NOPB

4346715

D2_A

CMD_DIR

X3200

1

Vss

SW2

GND

2

13

GND

GND

C3207

27p

2

C3203

100n

100n

9

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

SD-Card Interface

Name

C3201

R3200

Appr

Copyright (C) Nokia Corporation. All rights reserved.

GND

VIO

100k

C3202

27p

C3206

GND

2u2

100R

R3201

2u2

GND

GND

6

7

C3200

12

1

10

0

GND

8

GND

VBAT

GND

R3202

100R

100n

C3204

GND

GND

MMC_CMT(15:0)

Page 18

XTI_TX2

4

B

A

2

1

C

D

XTI_CLK

C

4

ETM Interface

D

JTClkRet

B

JTClk

6

JTRst

JTMS

XTI_TX3

3

3

A

2

1

EMU0

JTDO

JTAG Interface

XTI_TX1

XTI_RX

XTI_TX0

EMU1

5 6

JTDI

5

J3103

0

4

0

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

3

1

3

Test Interface

Name

4

J3100

5

VIO

27p

C3100

J3105

J3101

GND

2

VBAT

1

14

GND

J3114

J3113

J3104

J3110

J3117

J3112

J3116

J3111

J3119

J3120

2

15

J3115

ETM(16:0)

JTAG(6:0)

5

J3102

J3118

Page 19

B

1

D

SIMDaC1

SIMClkC1

SIMRstC1

1

SIMDetX

C

A A

B

Check routing near Pin 6 to avoid ESD problem

432

Use together with Vilma

2

D

6

5

5

3

Route SIM_CLK and SIM_IO signals as striplines (EMC)

64

IO

Rst

Clk

Use gnd to protect other signals (ESD)

9

GND

GND

SIMVCC

SWP

C

GND

10

2

3 4

5

6

7

GND

GND

8

C2704

27p

X2700

47067-0006

1

na

5p6

na

27p

C2703

GND

C2702

Copyright (C) Nokia Corporation. All rights reserved.

Name

SIM interface

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

GND

GND

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

12p

C2701 C2700

100n

GND

SIMIF(6:0)

6

2

0

1

Page 20

I2S/PCM_SYNC

5

1

B

2

SYSCLK

BTDaIn

BTDaOut

BTCTS

3 4

D

1 6

C

BTWake

BT_RESETX

BTHostWake

BTH_CLK_REQ

I2S/PCM_CLK

I2SSD2

I2SClk

Matching components for the ant.

MIC3P

MIC3PR

MIC3N

MIC3NR

6

A

I2S/PCM_OUT

I2SWS

I2SSD1

D

4

B

5

3

A

UART_RX

UART_CTS

BT_WAKEUP

C

SLEEPCLK

PURX

BTRstX

UART_WAKE

UART_RTS

BTRTS

Must be placed close to antenna

UART_TX

2

I2S/PCM_IN

470nH

L6001

8

L6002

2n2H

5

0

7

GND

C6005

56p

R6000

220R

1

0

0

SHIELDING ASSY

FMBT

A6000

56p

C6001

VIO

4

2

0

1

9

6

3

1

3

6442619

X6001

GND

5

12

6

smashed

fm_radio3_0

fm_radio

BUS_CLOCK

BUS_DATA

BUS_ENABLE

BUS_MODE

FMANT

PUSL(3:0)

VCC_FM

VIO_FM

XAUDIO(17:0)

GND

Name

BTHFMRDS

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

0

GND

47nH

3648993

L6000

na

Copyright (C) Nokia Corporation. All rights reserved.

4

GND

3

11

2

VIO

0

X6000

6442619

5

13

GND

49

VANA

2

1

2

6

1

3

GND

na

10

LPRFCLK

PUSL(3:0) SPI(3:0)

6

8

C6004

2320518

1p8

FM_ANT

PUSL(7:0)

LPRFCLK_I

IPUSL(3:0)

LPRF_CMT(6:0)

GEN_CTRL_CMT(20:0)

PCM(3:0)

ILPRF(23:0)

IAUDIO(17:0)

AUDIO(6:0)

I2C(1:0)

smashed

Perf2.3_filter

Perf2.3_filter

ANT_BTH

BC4_TEST(3:0)G_LPRF(23:0)

Page 21

2

BT_WAKEUP

UART_RTS

5

(1) VREG_EN (C3) is noise sensitive. L6032, R6031, C6038 are required for filtering

(2) R6037 & R6038 may be located where convenient and do not have to be in the Bluetooth area.

(R6038, 100K, 1430804 not fitted)

PURX

C

PCM_CLK

PCM_SYNC

6

AUX_DAC

PCM_CLK

PCM_IN

UART_CTS_P

ANT

BTH_CLK_REQ

UART_TX

UART_RX

UART_TX

A

TEST_EN

D

SEE NOTES 2 & 3

4

SLEEPCLK

SEE NOTE 2

SPI_CSB

BT_RESETX

UART_CTS

PCM_OUT

PA_ENABLE

UART_RTS

SPI_CLK

SPI_MOSI

(a) Host is running from different VCTCXO than BC4.

OR (b) BT_RESETX line is being used to gate REF_CLK for BC4.

For all other cases R6038 is Not Fitted.

6

D

C

UART_WAKE

BT_RESETX

B

UART_RX

SYSCLK

A

SPI_MISO

BTH PERF2.3 (BC4 ROM1.0) A3.0 2006 WK 10

B

3

3

5

BT_WAKEUP

Notes

PURX

(3) R6038 to be fitted if :-

3n3H

L6031

UART_CTS

SLEEPCLK

1

4

2

PCM_SYNC

PCM_IN

1

UART_WAKE

PCM_OUT

BTH_CLK_REQ

LNA_ENABLE

L6030

3n3H

1u5

2351039

C6037

GND

1

0

9

8

7

6

5

4

3

2

C6035

2320778

10n

10

C6055

GND

VBAT_BTH

GND

1u0

2351009

7

10

8

9

GND

GND

GND

VIO_BTH_1V8

VIO_BTH_1V8

GND

2

0

C6031

2320604

18p

18p

2320604

C6039

100p

GND

G2

PIO3

VSS_PADS

G3

G4

VDD_PIO

NC

G5

NC

G6

G7

NC

2320560

C6032

F1

PIO9

F2

AUX_DAC

PIO8

F3

PIO1

F4

SPI_CLK

F5

F6

SPI_CSB

F7

SPI_MISO

PIO2

G1

D7

PIO6

RF_B

E1

E2

RF_A

PIO0

E3

SPI_MOSI

E4

PIO5

E5

PIO4

E6

E7

RESETB

PCM_SYNC

C5

VDD_CORE

C6

C7

VSS_DIG

RF_IN

D2

TEST_EN

D3

D4

PIO7

D5

PCM_OUT

D6

VDD_PADS

AIO2

B4

B5

UART_TX

PCM_CLK

B6

B7

PCM_IN

VSS_RADIO

C1

C2

VDD_RADIO

C3

VREG_EN

AIO0

C4

XTAL_IN

A3

VDD_ANA

A4

A5

UART_RX

UART_CTS

A6

UART_RTS

A7

VSS_VCO

B1

B2

VDD_VCO

B3

VSS_ANA

BC4-ROM1.0RDL

N6030

4376495

A2

VREG_IN

GND

10n

2320778

C6038

E6048

R6034

1430778

10k

2

VBAT_BTH

5

4

11

C6003

2p2

100k

1430804

R6037

GND

6

3

GND

0

C6040

2351009

1u0

C6002

2p2

Unbal

DC

GND

Bal

Bal

VIO

3

10k

LFB2H2G44BB2A257

Z6030

4551041

2441.75MHz

VBAT

1430778

R6030

10k

E6049

C6036

1430778

R6031

1

6

11

VIO_BTH_1V8

10n

2320778

0

GND

GND

2

GND

C6033

2320778

10n 10n

2320778

C6034

R6032

1430691

GND

22nH

3646063

L6032

2R2

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

SPI(3:0)

BC4_TEST(3:0)

LPRFCLK

BTHPERF 2.3 (BC4 ROM1.0)

Name

PUSL(3:0)

PUSL(3:0)

G_LPRF(23:0)

G_LPRF(23:0)

ANT_BTH

Page 22

3 5 6

1 2 43 65

D

C

B

A

1) CONNECTION FROM ENGINE GLOBAL NET 2V5/2V8 TO VCC_FM ON THIS

D

C

B

A

MIC3P

MIC3PR

MIC3N

MIC3NR

REUSE BLOCK SHOULD BE MADE AT R6102 PIN 2 ON LAYER 4

NOTE :-

SEE NOTE 1

CBUS Mode: BUS=CBUS

CBUS Mode: Connect BUS_MODE to VIO

I2C Mode: BUS=I2C & BUS_ENABLE Connect to VIO

I2C Mode: Connect BUS_MODE to GND

1 2

REF RANGE = 6100-6199

FM COST 3.0 A1.5 2006 WK32 RELEASE

C6101

SLEEPCLK

4

120nH

L6101

GND

100n

C6109

1u5

Copyright (C) Nokia Corporation. All rights reserved.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

This document is property of Nokia Corporation

FM Cost 3.0 Reuse Block

Name

GND

VCC_FMVIO_FM

22R

2 /2 100n

C6107

R6103

C6107

/2 100n1

J6102

VCC_FM

9

GND

2 /2 100n

C6108

J6103

J6104

J6105

10k

R6101

J6101

C6103

GND

100n

C6104

47p

C6105

100p

10n

C6102

100k

R6100

2

VIO_FM

GND

DATA

E1

E2

CLOCK

VREFDIG

E3

E4

MPXOUT

E5

VAFL

VAFR

E6

L6100

47nH

BUSEN

C5

RFGND

C6

RFIN2

VDD

D1

D2

DGND

BUSMODE

D3

D5

AGND2

D6

TMUTE

A4

A5

VCCVCO

VCC

A6

B1

SWPORT

INTX

B2

AGND1

B5B6

RFIN1

C1

FREQIN

C2

TEA5760UK_N1C

N6100

CPOUT

A1

A2

LOOPSW

LO1

A3

LO2

C6106

27p

VCC_FM

J6100

C6108

/2 100n1

8

12

13

GND

GND

XAUDIO(17:0)

FMANT

PUSL(3:0)

BUS_CLOCK

BUS_ENABLE

BUS_DATA

BUS_MODE

VCC_FM

VIO_FM

Page 23

Remove Harmonics

With WG3.2 BB VCP1 and VCP2 pins are connected together

8.2nH

L7811

7500-7599

R7800 must be placed on top of Z7800

EXT_COMP

7800-7899

(MODIFICATION !!!)

RFC8

Place closed to ant.

8.2nH

L7810

GND

100p

2320560

C7802

C7804

2320560

100p

Name

Ritsa RF schematics

C7901

2320151

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

Copyright (C) Nokia Corporation. All rights reserved.

2p7

GND

X7803

J7806

J7805

J7809

3203769

L7808

240R/100MHz

GND

RF3

RF1

RF2

VBAT

VDD

CTRL2

CTRL1

RF4

RF1450_E5.2

4510519

Z7001

ANT

22nH

L7800

VBAT

VBAT_PA

VBAT_WPA

VCP1

VREFCM

VREFRF01

VXO

WTXDET

GND

na

RFC6

RFC8

RFCLKEXT

RFCLKN

RFCLKP

RFTEMP

RXIN

RXIP

RXQN

RXQP

TXC

TXIN

TXIP

TXQN

TXQP

TXRESETX

RF

RF

AFC

ANT

DAC_REF1

RFBUSCLK

RFBUSDAT

RFBUSENA

RFC10

RFC11

6442619

X7804

J7808

1p8

na

100p

2320560

C7803

C7810

10n

2320778

C7809

GND

8p2

2320534

C7807

L7809

3203769

240R/100MHz

G

OUT

G

IN

Z7800

Phase

Shifter

1800/1900MHz

GND

8.2nH

3649099

L7801

3

4

GNDGND

5429037

X7800

8.2nH

3649099

L7804

L7807

3648963

10nH

GND

X7802

X7801

10p

GND

10p

2320536

C7806C7805

2320778

GND

VBAT

RFCLKEXT_GPS

GND

10n

C7808

TXRESETX

RFBUSENA

RFBUSDAT

RFBUSCLK

TXIN

TXIP

TXQP

TXQN

AFC

VXO

VREFRF01

TXC

VCP2

VCP1

DAC_REF1

RFCLKEXT

RFCLKN

RFCLKP

RFTEMP

RXIN

RXIP

RXQN

RXQP

VREFCM

WTXDET

Page 24

A

E

7 8

87

C

6

4

D

FF

B

1 4

C

B

A

1% TOLERANCE

31 2

E

6

5

5

D

2 3

C7525

10p

1k0

100n

R7524

C7581

0R

R7544

RFC11

TXC

M4

SCLK

M5

M6

XRESET

M7

VVCO_CAP

LO_IN

M8

REFP

M9

DAC201

RFTEMP

L4

RXOUT_PQ

RXOUT_NQ

L5

L6

SDATA

VDIG

L7

L8

VCO_CTRL

L9

OSCIN

M10

REFGGNDCP_TX

M11

VCP

M2

M3

TXVCO_SUB

RXOUT_NI

K5

K6

GNDDIG

GNDDIG_TX

K7

GNDPRE_TX

K8

REFN

K9

RFC10

L1

L10

CBUF_CAP

TXLOOP_SUB

L11

L12

VBAT_TX

VREF_CM

L2

RFC11

L3

TXQ_0

J12

TXQ_180

GNDBB_RX

J2

GNDPRE_RX

J3

GNDPRE_RX2

K1

K10

DAC_REF1

RFC5

K11

VDAC

K12

K2

GNDCP

K3

GNDVCO

RXOUT_PI

K4

XENA

G2

C2IP

G3

C1IP

H1

RBEXT_RX

DAC2O1

H10

H11

TXI_180

TXI_0

H12

VBAT_RX

H2

C1IN

H3

GNDBB_RX2

J1

GNDBB_TX

J10

J11

C1QP

C2QP

F1

GNDRF_TX

F10

TX_SUB

F11

F12