Introduction

Important:

This document is intended for use by authorized service centers only.

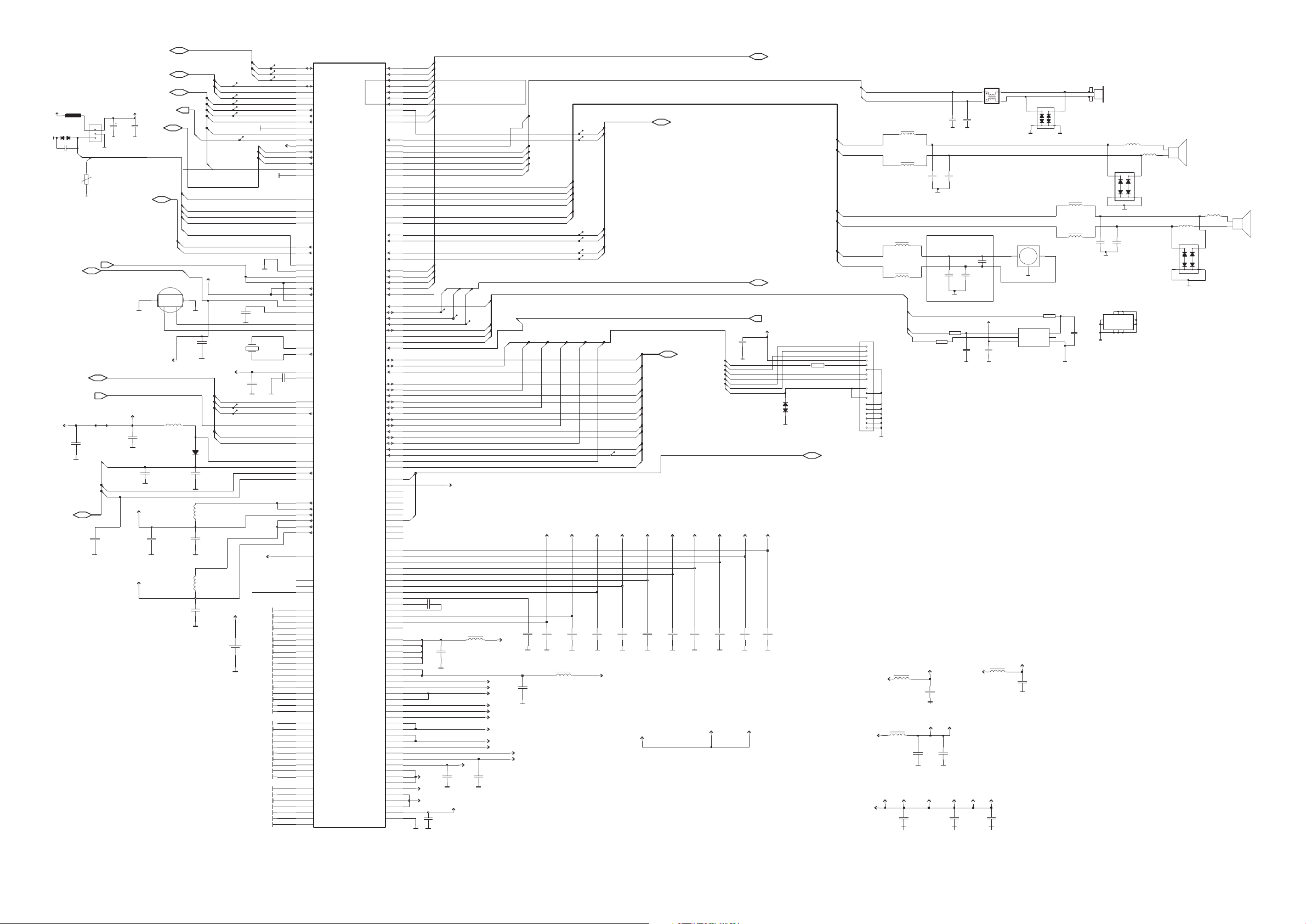

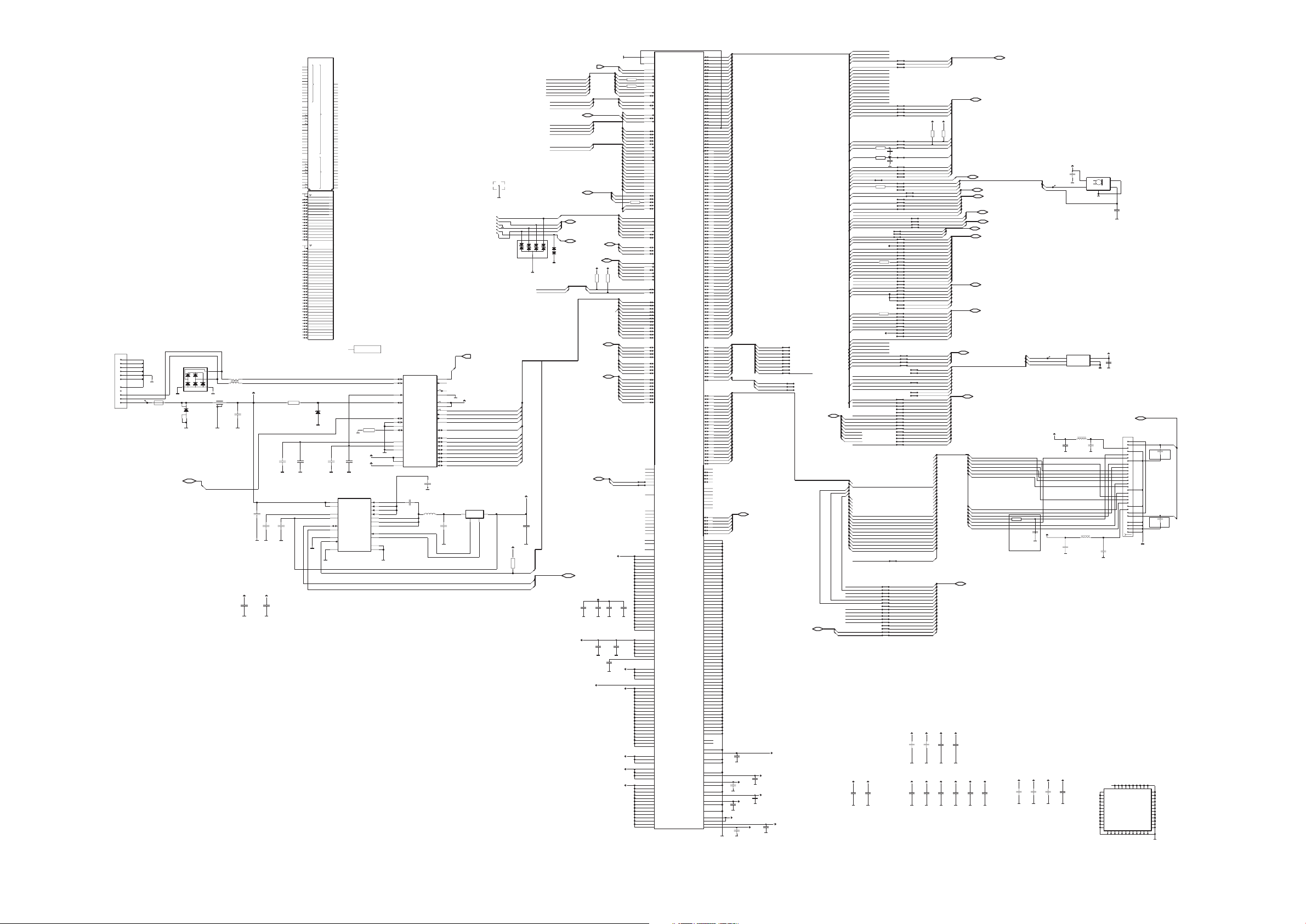

Service Schematics

RM-431

Table of contents

“Service Schematics“ was created with focus on customer care.

The purpose of this document is to provide further technical repair information for

NOKIA mobile phones on Level 3/4 service activities.

It contains additional information such as e.g. “Component nder”.

Saving process time and improving the repair quality is the aim of this document.

It is to be used additionaly to the service manual and other training

or service information such as Service Bulletins.

While every endeavour has been made to ensure the accuracy of this document, some

errors may exist. If the reader nds any errors, NOKIA should be notied in writing.

Please send E-Mail to: TrainingAndVendor.Development@nokia.com

Frontpage 1

GAZOO, HS USB charging, SIM, MMC, Audio 2

MUX, RAPU-YAMA, Memory, UI 3

AV Connector 4

Bluetooth, WLAN 5

Keyboard 6

RF 7

Cameras 8

Component Finder 9

Copyright © NOKIA

This material , including documentation and any related computer programs is

protected by copyright, controlled by NOKIA. All rights are reserved. Copying,

including reproducing, modifying, storing, adapting or translating any or all of this

material requires the prior written consent of NOKIA. This material also contains con-

dential information, which may not be disclosed to others whitout the prior written

consent of NOKIA.

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 1(9)

Frontpage

Digimic, no need for MICB1 capacitor

Note!

FM Left and Right inputs

swapped for SW fix for

audible ECI crackle

noise removal in Gazoo.

VBUS SMPS components are not needed if USB charging supported!

2u2/6V3

VAUX 1 and 2 not close to VMEM!

directly to resistor pads

connect to TestNet3 T1

connect to ClassDKelvin N6

2u2/6V3

is moved to flex

Lines must be connected

CHARGING INDICATOR LED

2u2/6V3

2u2/6V3

GND

10

3

J2215

VBACK

J2225

10

L2300

2u2H

GND

GND

56p

C2253

EMC

Near RAPU

27p

C2251C2250

68p

SetCurrKB EMC

J2201

VIO

0

GND

GND

J2202

GND

J2218

VBAT

3

GND

J2219

5

VDigimic

GND

0

C2280

2u2

VMEM

VBatLED

11

C2230

22u

GND

GND

0

VBAT8

GND

4

1

GND

GND

2

1u0

C2314

GND

5

0

2

1

T6

IHFSpRN

VCharIn1

T7

0

5

0

7

TestNet3

T1

VCharOut2

T10

GndUSB

T11

VCore

T13

T14

GndVCore

GndVCore

T15

T16

GndVCore

T2

TestNet2

T3

VBatIHFLN

GndIHFLP

T4

GndVCore

R16

GenOut2

R2

R3

IHFSpLN

R4

GndIHFLN

R5

IHFSpRP

GndIHFRP

R6

VBatIHFRN

R7

VCharOut1

R8

VCharIn2

R9

P6

VBatIHFRP

P7

GndINFRN

P8

CBusSelX

VBUS

P9

TestNet1

R1

VUSB

R10

VBUSCoil

R11

DM

R12

DP

R13

R14

GndVCore

GndVCore

R15

P12

BTemp

USBCharDis

P13

P14

VPROGID

VCoreCoil

P15

VCoreCoil

P16

RSTX

P2

P3

EarDataR

P4

IHFSpLP

VBatIHFLP

P5

N4

EarDataL

N5

ClassDKelvin

N6

N7

CBusClk

N8

CBusData

N9

ChInd

P1

GenOut1

VBUSSMPSOut

P10

VBatUSB

P11

N10

VBatChacon

SMPSClk

N11

N12

GndPVSS2

N13

RFTemp

VBack

N14

N15

VBatVCore

VBatVCore

N16

MicData

N2

AudClk

N3

PMARN

VCharInTest

L8

L9

GndCHInd

VCoreDef

M13

CMDDir

M14

LedOut

M15

Speed

M2

VDDAudRx3

M3

M4

VBUSCtrl

N1

PMARP

L10

L13

VBatLED

L14

SIMClkC

GndLED

L15

L16

SIMDaC

LineInRN

L2

XEarR

L3

L4

XEarRC

L7

GndChacon

K2

XEarLC

XEarL

K3

K4

EarN

Mic1P

K6

K7

GndAudRx

GndAVSS2

K8

USBCharDetX

K9

L1

LineInRP

ID

Suspend

J7

GndAVSS1

J8

J9

LST

VDDAudRx

K1

SetCurrD

K10

K11

GndLED2

GndPVSS3

K13

ClkB

K14

K15

VBatVSIM

K16

VSIM

J10

Data4Dir

J11

Data4B

J13

J14

Data3B

VBatVAux

J15

SlaveSW

J2

J3

MicB2

J4

Mic3RN

LineInLN

J6

Data2B

H14

H15

VBatVAux

H2

VDDAudRx2

MicB1

H3

H4

MicSub

H6

LineInLP

H7

WTxDet

VOut

H8

ExtPWMOut

H9

SetCurrKB

G3

Mic3LP

G4

Mic3RP

G6

HeadDet

VRef

G7

G8

VDIGI

MBus

G9

OVVLed

H10

SIMRstC

H11

VAux1

H13

F9

SIMDetX

G1

EarP

G10

Data1A

G11

GndLDO2

G13

VAux2

Data1B

G14

G15

CMDB

G16

GndVMEM

Mic2P

G2

ClkFB

F13

F14

GndPVSS5

VBatVMEM

F15

F16

VMEM

VDDAudTx

F2

F3

Mic2N

F4

Mic3LN

GndRef

F7

VBatVDigi

F8

E13

ClkA

Data3Dir

E14

CMDA

E15

GndVibra

E2

E3

SleepX

E4

SenseM

E5

VR1

GndAudTx

F1

F10

VDD18

GndVIO

D15

D16

GndVIO

D2

VibraN

TxCData

D3

D4

TxCOut

D5

VBatVR1

D6

GndXTAL

VBatVAna

D7

D8

VDigiMic

D9

VCP

C7

VRTC

C8

FlyHigh

C9

FlyLow

D1

VBatVibra

D10

HookDet

MBusRx

D11D12

Data2Dir

D13

Data1Dir

Data4A

D14

Data3A

C14

Data2A

VIOCoil

C15

VIOCoil

C16

C2

TxCClk

AFCOut

C3

SleepClk

C4

WDDis

C5

VRFC

C6

B5

GndLDO1

CrO

B6

B7

VAna

GndCPump

B8

VBatVCP

B9

C1

VibraP

BSI

C10

GndPVSS6

C11

C12

SIMDa

C13

UserResetX

B11

B12

MBusTx

B13

SIMIOC

B14

SIMClk

B15

VBatVIO

VBatVIO

B16

B2

TxCCtrl

SenseP

B3

GndLDO1

B4

A14

A15

VBatVIO

A16

VBatVIO

A2

ATM

A3

EMInt

A4

PURX

A6

CrI

VBg

A7

B1

VBatVibra

PwrOnX

B10

6

N2200

GAZOO_V3.4

VBatVibra

A1

GndPVSS7

A10

A11

VRCP1

VIO

A13

VBatVIO

4111107

PMEG3002AEL

V2300

GND

C2252

56p

VBatLED

VDDAUDRX

4

GND

-

+

2

L2340

1uH 1uH

L2310

1

G2200

2.6V

GND

GND

GND

VRCP1

2

GND

L2206

15

GND

120R/100MHz

GND

6

J2227

VRFC

VBAT10

GND

GND

5

GND

GND

8

VOUT

22u

C2231

C2326

J2212

0

1

2u2

1

GND

C2275

GND

VBUS

0

2u2C2316

GND

GND

GND

14

4

GND

1

3

VR1

GND

VBACK

12

2

VBAT11

CHG_IND_LED

GND

GND

J2206

3

VDDAUDTX

6

VBAT

7

1

VIO

GND

VBAT9

2

5

GND

J2210

GND

5

2

J2200

2

GND

VCORE

C2271

2u2

VDDAUDTX

GND

0

2

11

GND

1

VBAT

2u2

C2319

GND

BGND

Near to L2300

GND

C2245

2u2

C2269

C2317

VAUX1

2

13

VBAT13

2u2

GND

3

GND

4

VBAT3

J2220

VANA

GND

2

1

8

C2315

8

B2200

32.768kHz

GND

2u2

2u2

C2266

10u

C2211

0

J2208

2

GND

GND

C2213

2u2

GND

9

GND

J2236

C2281

VANA

J2211

GND

GND

VREF

VDDAUDRX

3

J2217

J2207

0

1

VBAT4

4

0

C2267

2u2

23

4

J2216

GND

J2205

2

CURRENT

SENSE

PMR03EZPJU10L

R2200

1

1

VBAT

7

GND

3

GND

GND

GND

GND

GND

3

VBAT

0

J2214

VBAT12

L2204

120R/100MHz

1

6

3

GND

1

GND

C2282

C2214

2u2

J2203

2u2

VBAT5

5

4

C2296

VBAT

GND

C2227

68p

0

4

2u2

C2268

2u2

C2222

VBAT

2u2

C2265

1

0

VAUX2

0

1

GND

GND

VBAT1

GND

GND

2

VSIM

3

5

1

0

GND

VBAT_VCORE_SMPS

GND

SleepCLK

VBAT_VIO_SMPS

CBusCLK

CHARGER

TXCCtrl

CbusSelX

TXCDa

RSTX

SleepX

PURX

kelvin

INT_SIM(5:0)

FBCLK

LED(6:0)

Vchar_det

audclk0

mic_data

PWRONX

kelvin

TXCCLK

LED(6:0)

SLOWAD(6:0)

SenseN

GAZOOIO(3:0)

SenseP

SMPSCLK

CbusData

Use VBAT distripution plane underneath ASIC for proper power supply

L2203

120R/100MHz

VBAT12

VBAT

GND

C2247

2u2

VBAT9VBAT1

GND

VBAT4 VBAT5

GND

VBAT13 VBAT8

VBAT

GND

2u2

C2229C2294

2u2

C2228

2u2

120R/100MHz

L2205

3203855

VBAT11

2u2

C2249

VBAT

GND

VBAT10

GND

10U

C2232

GND

2u2

C2285

120R/100MHz

L2202

VBAT

VBAT3

"VBAT plane underneath Gazoo intput"

XAUDIO(7:0)

AUDIO(13:0)

H_BRIDGE(5:0)

CBUS(3:0)

TXC(2:0)

ACI(7:0)

EMINT(3:0)

TXC_CONV(4:0)

PUSL(15:0)

INT_MMC(13:0)

SIM(6:0)

NC

SIMCLK

SIMRST

VSIM

SIMDATA

GND

CLK

Da

Reset

0R

0R

R2702

R2701

0R

27p

C2702

R2703

GND

FOOT

A2700

040-056369

SIM HOLDER

GNDGND

C2701

27p

2

C2700

100n

2

3

5

6

7

GND

3

VSIM

X2700

C707_10M006_107_2

1

1

"SIM RST"

"SIM Data"

"SIM_CLK"

SIM_RST

SIM_clk

MMCDa

MMCCmd

PreWarning

MMCClk

MMCDet

VMEM

MMCDa3

present_det

pre_warning

MMCDet

MMCDa1

MMCDa2

R3206

MODELNA

5

GND

GND

GND

2

3

4

5

6

7

8

SW1

GND

0

X3200

1

Vss

SW2

3

4

R3200

47R

VMEM

12

1

2

MMCDa3

MMCDa2

MMCDa

MMCDa1

MMCCmd

MMC(15:0)

MMCDet

C3205

100n

Stout earpiece

A1 A2

B1

B2

V2100

ESDA14V2-2BF3

L2100

DLM11GN601SZ2D

12

34

GNDGND

NA

B2101

1

2-

3

+

4

NA

27p

C2104

27p

GND

NA

C2103

0

1

GND

DIG_AUDIO(8:0)

Vibra

WLAN

sensitivity

VIBRAN

VIBRAP

IHF- connection

IHF speaker Tiny

connection

IHFSpRP

IHFSpRN

L2108

220R/100MHz

NANA

1n0

C2113

C2112

1n0

56nH

L2110

B2103

NA

GND

GND

M

+

-

GND

120R/100MHz

L2106

BNK-3266

M2100

120R/100MHz

6p8

C2108

GND

L2105

C2109 C2110

6p8

4

5

6p8

ESDA14V2-2BF3

V2103

A1

A2

B1

B2

3

220R/100MHz

L2107

2

56nH

L2109

IHFSpLP

IHFSpLN

1

0

connection

IHF speaker Tiny

GND

A2

B1

B2

B2102

V2104

ESDA14V2-2BF3

A1

N

A

NA NA

1n0

C2106

C2107

1n0

GND

L2102

56nH

L2101

220R/100MHz

220R/100MHz

L2104

56nH

L2103

USB(20:0)

BTEMP NTC

GND

C2072

56p

Vchar

C2071

56p

GND

3BSI

2

3

Z2070

W=0.80

L=1

GND

X2070

+

1

2

IP4302CX2LF

R2070

GND

C2070

150u_6V3

VBAT

-t

R2071

47k

GND

BGND

GAZOO, HS USB charging, SIM, MMC, Audio

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 2(9)

LCDReset

Reserved SDRAM AD13

AVVideoCTRL

SDRAMxCS2

MMCDaDir1-3

25

10

53

54

22

78

9

70

69

11

75

3

52

4

76

50

82

12

74

5

8

77

73

79

80

15

6

83

13

0

0201

I2C PULL UP RESISTORS VIO

3k3 R2853

VIO

R28523k3

11

49

7

84

72

31

32

37

14

39

81

2

47

48

82

84

85

83

20

85

68

14

6

8

7

Place near RAPU

47R

R2856

genio72

genio39

DigiMICClk

DigiMIC_Data

HACPAEn

1

2

3

0

AUDIOTEST(5:0)

CLK

FrameSync

DOUT

DIN

genio82

genio83

genio84

genio85

12

genio25 MMCCardDet

MMC(15:0)

16

15

SDRAMCTRL(17:0)

SDRAMxCS2

SDRCKE2

genio6

genio34

Not use if I2C is in use

Not use if I2C is in use

Not use if I2C is in use

Not use if I2C is in use

Not use if I2C is in use

11

15

7

12

13

10

1

2

6

9

8

4

3

5

0

CBUSENX_IN

BUSMODE

SLEEPCLK

FM_AUDIO_PR

FM_AUDIO_NR

FM_AUDIO_PL

FM_AUDIO_NL

I2SMOSI

I2SMISO

I2SSCLK

I2SWS

SleepClk

I2C2SDA

I2C2SCL

ReferenceClkSysClk192

FMRADIO(20:0)

I2C2SDA

I2C2SCL

FMIRQgenio23

1

0

ACI(7:0)

ACIRX

ACITX

genio31

genio32

0

1

4

5

2

3

I2C2SDA

I2C2SCL

AV(5:0)

ConnDet

AVPAEn

BufferSleep

AVVideoCTRL

genio37

genio14

11

10

15

9

8

14

20

13

12

TCLKretRXDa0

ETM(20:0)

ETMDa8

ETMDa9

ETMDa10

ETMDa11

ETMDa12

ETMDa13

ETMDa14

ETMDa15

2

3

1

Emint0

BootModeSel

LDOPowerDown

LCD_CS

WRX

LCD_TE

LCD_RESX

MESSI5

MESSI6

MESSI7

MESSI8

RDX

LCD_D/CX

ROW4

ROW5

ROW4

ROW5

MESSI4

11

MESSI3

ROW1

MESSI1

MESSI2

ROW1

19

4

0

0

9

4

2

17

14

24

20

5

8

9

13

0

12

10

28

6

1

23

8

10

13

8

13

1

2

18

12

7

12

3

15

14

6

5

15

4

14

7

20

22

1

2

25

26

3

11

27

11

16

17

18

10

3

19

7

15

6

21

16

29

21

9

5

30

LCD(99:0)

genio26genio26

genio35genio35

genio24genio24

genio61genio61

genio60genio60

genio59genio59

genio58genio58

genio62genio62

ROW6

COL0

ExpanderInt

DISPCDataLCD5

DISPCDataLCD6

DISPCDataLCD7

DISPCDataLCD16

DISPCPCLK

DISPCHSYNC

DISPCVSYNC

DISPCACBIAS

COL5

VISSI(27:0)

DISPCDataLCD0

DISPCDataLCD1

DISPCDataLCD2

DISPCDataLCD3

DISPCDataLCD4

LCDResetgenio9

KEYB(15:0)

ROW0

ROW1

ROW2

ROW3

ROW4

ROW5

COL1

COL2

COL3

COL4

20

7

Near RAPU

0

47R

R2857

2

8

4

9

21

BTH_CLK_REQ

5

10

3

6

11

22

1

HostWakeUp

PURX

SleepClk

SleepX

genio20

PURX

SleepClk

SleepX

BT(23:0)

BTCTS

BTRTS

BTUARTIn

BTUARTOut

BTWakeUp

BTH_Clk_Req

BTResetX

BTPCMClk

BTPCMSync

BTPCMIn

BTPCMout

genio85

genio47

genio48

genio49

genio50

genio53

genio54

genio82

genio83

genio84

7

8

9

genio22 FlashINT

FlsCS1X

MEMCONT(9:0)

VPPLock

0201

0201

0201

020111NA

C2850

10p0

9

8

GND

GND

R2854

47R

12

17

10p0

C2851

NA

47R

R2855

19

15

14

20

13

10

16

LedFlashStrobe

TXP

LedFlashInt

genio87

TxMask

"Cam1Clock -> noisy signal "

Cam1Clk

genio1

genio18

genio19

CCP(20:0)

Cam_Reg_1V8

Cam_Reg_2V8

LedFlashEn

2nd_Cam_ShutdownX

I2C0SCLgenio28

genio4343

56

17

16

27

28

86

87

1

18

19

genio56

genio17

Cam_ShutdownXgenio16

I2C0SDAgenio27

"Cam0Clock -> noisy signal "

Cam0Clkgenio86

Out

InIn

Out

4

3

Near RAPU

47R

R2858

7

0

WLAN_CLK_REQ

2

5

6

8

1

genio74

RX2

genio75

genio76

genio77

genio73

SleepClk

"Data -> noisy signal "SPI_MISO

CLK_REQ

SQCLKIP

SPI_CSX

"Data -> noisy signal "SPI_MOSI

WLANENABLE

WLAN_IRQ

WLAN(15:0)

"Clock -> noisy signal "SPI_Clk

16

12

13

USBChargeINTgenio4

USBSyncClk

genio52 ULPICS

9

3

7

10

1

11

5

MMCDaDir3

MMCDaDir2

MMCDaDir0genio69

SDMMCLSSHutDn

MMCCmdDirgenio70

INT_MMC(13:0)

MMCFbClk

MMCDaDir1genio11genio11

genio78

genio79

genio80

genio81

3

6

13

5

4

11

12

10

Mic3Rn

Mic3RP

Mic3LN

Mic3LP

AUDIO(13:0)

LineInLP

LineInLN

LineInRP

LineInRN

0

1

I2C0SCL

genio27

genio28

I2C0(1:0)

I2C0SDA

genio15

GENIO(99:0)

genio0

genio3

genio2

genio5

genio6

genio7

genio8

genio9

genio10

genio11

genio12

genio13

genio14

GND

BASEBAND SHIELD

A2800

040-056208

ASSEMBLY

Bypass for CPU

100n

Bypass for CPU

100n

C2821

/2 100n

VIO

GND

2

VIO

VIO

GNDGND

2

C2811

/2 100n

VIO

GNDGND

GNDGND GND

VIO

C2818

2

GND

/2 100n1

C2818

/2 100n2

C2817

/2 100n

GND

VIO

GND

C2810

2/2 100n1

C2810

/2 100n

1/2 100n

C2820

VIO

VIO

GND

VIO

VIO

VIO

C2816

GND

/2 100n1

GND

C2811

1/2 100n

C28162C2817

1/2 100n/2 100n/2 100n

GND

2

C2814C2814

1/2 100n

VIO

GND

VIOVIO

VIO

VIO

C2820

/2 100n

C2821

1/2 100n2

0201

REMOVE

RAPU 2.0

0201

0

15

17

70

71

72

81

6

4

2

R2805

3k3

6

15

12

13

11

10

3

7

1

2

16

1

33

0

8

1

55

58

8

3

4

12

2

10

25

1

2

R2801

100R

3

2

74

75

76

3

4

86

87

82

0

7

11

10

1

7

4

40

78

79

6

11

3k3

R2804

37

0

6

21

3

5

0

9

2

0

46

41

47

0

1

5

77

6

69

68

2

31

3

29

24

1

35

5

6

60

0

1

61

62

19

4

27

44

45

36

0

5

57

56

1

2

28

4

8

49

50

51

22

3

7

2

0

1

0

20

9

32

VIO

80

4

3

4

5

2

66

67

VIO

4

30

2

3

13

14

65

34

6

7

8

17

9

2

84

14

5

20

63

19

4

0

23

16

7

7

26

DISPC_VSYNC

Y4

Y5

GenIO23

GenIO22

Y6

Y7

DISPC_DATA_LCD7

DISPC_DATA_LCD14

Y8

DISPC_DATA_LCD0

Y9

CBusClk

Y15

Y16

ETMDa7

Y17

ETMDa5

ETMCtrl

Y18

GenIO69

Y19

GenIO75

Y20

Y21

GenIO13

GenIO25

Y3

GenIO46

W21

GenIO5

W22

W3

DISPC_DATA_LCD13

W4

DISPC_DATA_LCD16

GenIO3

Y10

Y11

GenIO0

Y13

CCPStrbP1

Y14

CCPStrbN1

U8

DISPC_DATA_LCD10

DISPC_DATA_LCD15

U9

V20

GenIO39

V21

GenIO37

GenIO74

V22

DISPC_DATA_LCD17

V3

V4

DISPC_DATA_LCD11

W20

GenIO11

I2C2SCL

U16

U17

GenIO1

U20

GenIO65

U21

EarDataR

U22

GenIO71

DISPC_DATA_LCD5

U3

GenIO8

U4

U7

DISPC_DATA_LCD4

GenIO7

T4

T7

GenIO17

GenIO2

U10

U11

GenIO86

GenIO43

U12

U13

CCPStrbN0

U14

CCPStrbP0

I2C2SDA

U15

GenIO18

R7

T13

GenIO87

GenIO31

T17

T20

EarDataL

T21

PMARP

MicData

T22

T23

GenIO12

T3

GenIO26

GenIO33

R17

GenIO9

R2

R20

GenIO47

PMARN

R21

GenIO48

R22

GenIO14

R3

GenIO20

R4

GenIO76

P17

SleepX

P21

P22

AudioClk0

GenIO35

P23

P3

GenIO10

RFBusClk

P4

GenIO82

P7

GenIO16

R1

GenIO38

N17

N20

PURX

GenIO73

N22

N23

GenIO40

RFBusEn1X

N3

RFBusDa

N4

N7

GenIO79

GenIO50

N9

M2

DRXIN

M20

SIMIOCtrl1

M21

SIMIODa1

ULPIData2

M22

M3

DRXIP

GenIO84

M4

GenIO85

M7

N1

GenIO81

L20

SIMClk1

L21

ULPIData4

GenIO60

L22

L23

GenIO6

VREFP

L3

L4

VREFN

L7

GenIO83

GenIO45

M17

GenIO41

K17

K20

ULPIClock

ULPIDir

K21

GenIO57

K23

RXIP

K3

RXQP

K4

K7

DRXQP

GenIO58

L17

GenIO55

J17

J2

RXIN

ULPIData1

J20

J21

ULPIData0

GenIO34

J22

TXQN

J3

J4

RXQN

DRXQN

J7

G7

GenIO78

G9

RX2

GenIO42

H12

H17

GenIO62

H20

ULPIData3

ULPINxt

H21

H3

TXQP

IREF

H4

GenIO36

G15

G17

GenIO56

RFClkN

G2

ULPIStp

G20

G21

GenIO61

G23

GenIO52

RFClkP

G3

TXIN

G4

E4

HissiData0N

ULPIData6

F20

ULPIData5

F21

TXIP

F4

G11

GenIO51

TxCClk

G12

G13

GenIO29

G14

GenIO64

HissiClkP

D3

D4

HissiData0P

D5

HissiData1P

EMU1

D6

SleepClk

D7

E20

ULPIData7

SMPSClk

E21

E22

GenIO59

ExtSysClkReq

D10

D11

GenIO49

D13

GenIO32

D14

TMAct

GenIO27

D15

D16

GenIO28

D19

GenIO53

D20

GenIO54

C14

TxCDa

C2

HissiClkN

HissiData2N

C3

C4

HissiData2P

C5

HissiData1N

C6

EMU0

TXA

C7

C8

RXDa0

GenIO63

B14

RXDATAClk

B2

GenIO67

B21

B6

SysClk384

GenIO68

B9

C1

TXP

C11

GenIO80

GenIO30

C13

AC10

GenIO72

AC16

SysClk192

ETMDa6

AC17

ETMClk

AC18

AC3

DISPC_ACBIAS

GenIO21

AC9

JTDI

B1

B13

GenIO4

ETMDa1

AB18

AB22

GenIO77

AB3

DISPC_DATA_LCD1

DISPC_DATA_LCD6

AB4

DISPC_DATA_LCD9

AB6

AB7

DISPC_DATA_LCD3

AB9

INT0

JTMS

AC1

DISPC_PCLK

AA7

AA8

GenIO15

AA9

DISPC_DATA_LCD2

AB1

JTDO

CCPDaP1

AB14

AB15

CCPDaN1

ETMDa4

AB16

CBusEn1X

AB17

ETMDa2

AA17

ETMDa3

AA18

AA19

ETMDa0

GenIO70

AA21

AA3

DISPC_DATA_LCD12

AA4

GenIO19

DISPC_HSYNC

AA5

DISPC_DATA_LCD8

AA6

A20

RX1

TXReset

A3

TxCDaCtrl

A8

GenIO24

AA10

AA11

GenIO44

AA12

CCPDaP0

CCPDaN0

AA13

AA16

CBusDa

RAPUYAMA_V1.11_PR_RITSA_BGA401

D2800

JTRSTn

A1

GenIO66

A19

A2

JTClk

2

0

52

53

1

9

1

15

16

38

10

48

6

1

42

11

1

54

0

7

39

0

5

6

7

73

3

4

5

64

5

6

1

18

16

17

27R

R2803

100R

R2802

12

8

9

18

59

13

5

GND

1

5

0

85

83

100n

C2841 and C2803 combined to one 0203

0203/1

0402

C2806 and C2807 combined to one 0203

0203/1

0203/2

0203/2

0203/1

Internal LDO

100n

Bypass for CPU

100n

0402

0402

0203/2

Bypass for CPU

100n

Bypass for CPU

GND

Bypass for CPU

0203/2

0203/1

C2826

18p

2

C2825

/2 100n1

C2825

/2 100n

2X100n

/2 100n2

C2806

VCORE

GND

VCORE

100n

C2801

VCORE

GNDGND

VIO

/2 100n2

C2824

VRFC

VIO

GND

C2823

2u2

VIO

VIO

GND

GND

VIO

VIO

GND

C2830

2u2

/2 100n1

C2824

GND

GNDGND

C2806

2X100n

/2 100n1

VRFC

2

2X100n

C2841

/2 100n

VIO

C2800

100n

GND

VRFC

100n

GND

VIO

C2802

VIO

VIO

GND

C2841

2X100n

/2 100n1

GND

VCORE

T8

VDDSTACK

VDD5

T9

U1

VCCQ_POP2

VSS

U2

U23

VSS

VDDS3

V23

VSS

Y12

Y23

VDD_POP12

R16

R8

VDDSRAMOUT

VDD5

R9

VDDS_1_4

T1

VDDRAM

T10

T11

VSS

VDDSTACK

T12

T14

VSS

T15

VDD

VSS

T16

VDDS1

T2

VSS

VSS

P2

VSS

P20

P8

VDD5

P9

VSS

R10

VSS

VDD

R11

R12

VDD

VDD

R13

VDD

R14

R15

VDD

VDD

VDD3

M16

VDDSTACK

M8

M9

VDD5

N15

VDD3

N16

VSS

N2

VDDS_1_1

N21

VDDS8

VDD5

N8

VCCQ_POP1

P1

P15

VSS

P16

VSS

K8

VDDSTACK

VSS

K9

VCC_POP3

L1

VSS

L15

VDD3

L16

L2

VSS

L8

VDD5

L9

VSS

VSSASUB

M1

M15

VDD3

VDD2

VSS

J13

VSS

J14

VDD3

J15

VDD3

J16

J8

VDD4

J9

VDDSTACK

K1

VDD_POP11

VSS

K15

VSS

K16

K2

VSS

K22

H16

VSS

H2

VSS

H22

VSS

H23

VDD_POP10

VDDARX

H7

VSS

H8

H9

VDDA18V1

VDDATX

J1

VDD2

J10

J11

VDDSTACK

J12

VSSATX

G1

VSS

VDDS9

G10

VSS

G16

G8

VSS

VDD_POP13

H1

H10

VSS

VSS

H11

H13

VDDRAM

VDD3

H14

H15

VDD3

VDDS9

VDDS9

D9

E1

VDD_POP9

VSSAPLLStack

E2

VDDS12

E23

E3

VDDAPLLStack

VSSARX

E5

VDDA_ACS

F1

F2

VSSA_ACS

F2

2

VSS

VDD_POP8

F23

F3

C22

VSS

VDD_POP7

C23

VSS

C9

VDDS_1_3

D1

D12

VDDA18V2

D17

VSS

D18

VDDS5

VSS

D21

VSENSE

D22

VDDS12

D23

D8

VSSA

B7

VSS

VSS

B8

C10

VSS

VDDS10

C12

VSS

C15

C16

VSS

C17

VSS

C18

VDDS5

VSS

C19

VSS

C21

VDDS2

AC8

VCC_POP2

B10

VSS

B12

VSS

B15

VSS

B18

VSS

B19

VDDS6

B22

VSS

B23

IFORCE

VDDA

B3

B4

VSS

B5

VSS

AB2

AB5

VSS

AB8

VSS

VPP_POP

AC11

VSSRX2

AC12

AC13

VCC_POP1

VDDS7

AC15

AC4

VSS

AC5

VCCQ_POP4

VDDS2

AC6

AC7

VDD_POP2

A9

VDDS_1_2

VCCQ_POP3

AA1

AA14

VSSRX1

VDDS7

AA15

AA2

VSS

AA20

VSS

AA22

VSS

AA23

VDD_POP12

AB10

VSS

VSS

AB13

VDD_POP4

A13

VSS

A15

VDD_POP5

A16

VDDS6

VDDS6

A17

A18

VDD_POP6

A21

VDDS6

A22

VPP2

VPP1

A23

VDD_POP1

A4

VDDS4

A5

A7

A10

VDD_POP3

A12

14

43

4

SCL2

CCP0_SP

CCP0_DP

CCP0_DN

CCP1_DP

SDA2

CCP1_SN

CCP1_SP

CCP1_DN

Flash_Int

21

CCP0_SN

0

EMInt1

R23

EMINT(3:0)

RFCLK(1:0)

HISSI(8:0)

CCP(20:0)

USB(20:0)

INT_SIM(5:0)

CBUS(3:0)

RFCONV(20:0)

TXC(2:0)

TXP

6

4

2

0

10

8

Y2

SDRAD14

Y22

SDRXCS2

M23

V1

FlsWEX

FlsOEX

V2

FlsADVX

W1

FlsClk

W2

W23

SDRAD13

Y1

CE1MMX

FlsCS0X

AC23

B11

SDRCLKX

B16

NC

SDRLDQS2

B17

B20

SDRUDQS2

NC

C20

D2

SDRLDQS

G22

NC

J23

SDRCKE2

AB23

NC

SDRAM_TEMP_SENSE

AC14

AC19

MMCDa2

AC2

NC

MMCDa3

AC20

MMCDa0

AC21

NC

AC22

NC

SDRCLK

A11

A14

NC

SDRUDQS

A6

FlsRstX

AB11

FlsWaitX

AB12

MMCDa1

AB19

AB20

MMCClk

AB21

MMCCmd

INT_MMC(13:0)

Traceability pad

BB5.44 have defined 6-pin test pad pattern

J2060

1

2

3

4

5

6

R2060

A1

A3

GNDB2

C1

C3

GND

1

4

6

6

5

7

ESDA14V2-4BF3

GND

GND

X2060

JTAG(6:0)

ETM(20:0)

RXD0

RXD1

ACI(7:0)

CLK2

TXD

CLK

GND

IP4302CX2LF

R2061

6

34

30

29z

1

0

I2C1SDA

I2C1SCL

genio29

genio30

I2C1(1:0)

0

2

1

CBusClk

BusDa

CBusEn1X

TXP2

RFCTRL(11:0)

WLAN_Enable

0

5

2

1

RX2

RX1

TXA

TXReset

7

0

3

1

4

6

ExtSysClkReq

SysClk192

PUSL(15:0)

PURX

SleepClk

SleepX

SysClk384

0

1

I2C2SDA

I2C2SCL

I2C2(1:0)

15

16

RXDATAClk

RXDa0

DIG_AUDIO(8:0)

13

14

SDRAd14

SDRAM_AD(15:0)

SDRAd13

8

4

5

0

6

1

2

3

7

I2C0SCL

I2C2SDA

I2C2SCL

ALSINTgenio68

ProxEnable

ProxInt

SENSORS(15:0)

MRInt

AccInt1

I2C0SDA

6

J1100

ALS

Agumon

4

SCL

SDA

5

INT

6

C1100

100n

GND

TSL2563CL

N1100

1

Vdd

2

GND

3

ADR_SEL

ALSINT

I2C2SCL

I2C2SDA

GND

4

5

VAUX2

GND

GND

RC-filter for display EMI.

D5

D3

Data2

VLED1-

VDDI

WRX

LCDTE

RESX

D0

D2

D4

D6

CSX

RESX

TE

D/CX

GND

TE

Data1

WRX

RDX

Data0

CS1 for main display

Data5

3

Data3

Data4

Data6

Data7

D7

GND

VLED2-

LEDOUT

VDD

D1

VLED2+

VLED1+

D/CX

RDX

MAIN DISPLAY (Piccadilly2) connector

EMC

1

16

0

C2457

6p8

100R

0

R2450

GND

GND

C2452

100n

C2455

100n

9

GND

GND

GND

5

2

20

21

22

23

24

GND

3

4

5

6

7

8

1

10

11

12

13

14

15

16

17

18

19

C2454

X2450

27p

VAUX1

L2451

120R/100MHz

7

26

C2453

27p

6

C2456

EMC

6p8

C2451

18p

2

30

GND

VIO

120R/100MHz

L2450

1

27

28

29

4

DISPCACBIASDISPCACBIAS

DISPCDataLCD16

DISPCDataLCD16

DISPCDataLCD2DISPCDataLCD2

DISPCDataLCD1

DISPCDataLCD1

DISPCDataLCD0

DISPCDataLCD0

LED(6:0)

LCDReset

LCDReset

LCD_WRX

SetCurrDS

DISPCPCLK

DISPCHSYNCDISPCHSYNC

DISPCDataLCD6

DISPCDataLCD6

DISPCDataLCD7DISPCDataLCD7

DISPCDataLCD4DISPCDataLCD4

DISPCDataLCD5

DISPCDataLCD5

DISPCDataLCD3

DISPCDataLCD3

DISPCVSYNC

DISPCVSYNC

A2

DM0d

AB16

AB17

GNDB12,H22,K2,K22,AA22=

GND1B4,B7,B10,B15,B18,C22,E2,F22,H2=

GND2L2,P2,U2,AA2,AB5,AB8,AB13=

P1,U1,AA1,AC5=

VCC

A1

NC

A11

CKd

A13

A14

A16

DM1d

A17

A19

NC

AC16

NC

A20

A21

A22

NC

A23

NC

A3

A5

A6

DM2d

A8

A9

AB1

NC

AB10

NC

_RPo

AB11

AB12

RDY0o

NC

AB14

NC

AB15

NC

AC7

NC

AB18

NC

NC

AB19

NC

AB2

AB20

NC

AB21

BA0d

NC

AB22

NC

AB23

INT0o

AB9

AC1

NC

RDY1o

AC10

NC

AC11

AC12

NC

NC

AC14

AC15

NC

NC

NC

B2

AC17

AC18

NC

NC

AC19

NC

AC2

AC20

NC

AC21

BA1d

NC

AC22

AC23

NC

INT1o

AC9

M2

M1

AB4

AC4

AB6

AC6

AB7

E22

N2

N1

R2

R1

T2

T1

AB3

AC3

B1

NC

_CKd

B11

B13

B14

B16

DQS1d

B17

B19

NC

0

B20

DQS0d

B21

NC

B22

B23

NC

B3

B5

B6

DQS2d

B8

B9

DM3d

C1

C2

DQS3d

D1

D2

D22

D23

12

W23

E23

F1

F2

G1

G2

G22

G23

J1

J2

CKEd

J22

NC

J23

_WEd

K23

L22

_CASd

L23

_RASd

M22

_CSd

M23

VCC2L1,AC8,AC13=

N22

N23

P22

P23

R22

R23

T22

T23

U22

U23

V1

_WEo

_OEo

V2

V22

V23

W1

_AVDo

W2

CLKo

W22

VCC3

COMBO 32Mx32 DDR

DDR

128Mx16 M3

43470S2

NAND

DDR

Data I/O

NAND

Ad

D3000

Addr/ Data Bus

K5W2G1GACI-AL60

A12,H23,K1,Y23,AA23=

VCC1A4,A7,A10,A15,A18,C23,E1,F23,H1=

A1

NC

_CE1o

Y1

Y2

_CE0o

NC

Y22

COMBO 32Mx32 DDR

128Mx16 M3

43470S2|NONET

D3000

K5W2G1GACI-AL60

USB(20:0)

Diff Impedance 90Ohm

0201

Pins E4 and E2 must be connected to the battery with separate wires

USB charger

detection to

EM ASIC

C3300

100n

VCC

F3

F4

VBUS

F5

XTAL1

F6

i.c.

GNDGND

D6

STP

E1

CHRG_DET_EN_N

E2

FAULT

REG3V3

E3

DIR

E5

REG1V8

E6

CHRG_DET_POL

F1

F2

CHRG_DET

C2

RREF

CHIP_SEL_N

C3

C4

TEST_N

C6

DATA7

DP

D1

D3

ID

PSW

D4

D5

NXT

DATA5

A6

DATA0

B1

B2

VCC(IO)

CHIP_SEL

B3

B4

CFG1

B5

VCC(IO)B6DATA6

C1

DM

GNDC5,D2,E4=

D3300

ISP1707AET

DATA1

A1

A2

DATA2

A3

DATA3

A4

CLOCK

DATA4

A5

R3367

ERJ2BWFR068X

SENSE

CURRENT 1

23

4

0

5

100n

C3316

VIO

GND

C3322

4u7

C3304

GND

4u7

16

10n

C3310

GND

8

GND

GND

GND

GND

2.0A

F3300

VIO

GND

27p

C3330

NA

GND

D-

D+

ID

GND

GND

A1

A2

B1

B2

X3300

VBUS

Z3300

USBULC6-2F3

GND

GND

VBAT

Vchar

GND

V3301

MAZA062029JN

GND

N3300

IP4387CX4_LF

KA

10u

C3365

GND

C3303

NA

GND

100n

R3348

10k

L3305

1uH

C3312

1u0

J3300

C3314

/2 1u52

C3313

VBUS

GND

C3313

1/2 1u5

4u7

GND

C3301

GND

Z3301

VIO

11

10

9

12

GND

D1

PGND

PGND

D2

PGND

D3

OTG

D4

CSIN

E1

E2

AUXPWR

VREF

E3

E4

CSOUT

B1

PMID

PMID

B2

B3

PMID

SDA

B4

SW

C1

C2

SW

SW

C3

C4

STAT

BQ24151YFFR

N3301

VBUS

A1

A2

VBUS

BOOT

A3

A4

SCL

1k0

GNDGND

R3300

12k

R3302

1

0

7

GND

1

7

6

5

4

3

2

SLOWAD(6:0)

"Charger det."

"Separate wire from R3367 pin1 to N2201 pin E2"

F3B2, B5

100n

C3306

VIO

VBAT

GNDGND

C3307

100n

"Vbus to ISP"

"ID pullup"

NoteDP_clean

NoteDM_clean

Noisy_CLK ULPI_CLK

PUSL(15:0)

I2C2(1:0)

DP_Dirty

DM_dirty

Near to digimic

7

6

VDigiMic

C2116

27p

GND

GND

VDD

5GND

GND

B2100

DSMO-431-5P-25

1

L/R

2

CLK3DATA

4

C2115

100n

J2101

Mic_CLK

Mic_Data

DIG_AUDIO(8:0)

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 3(9)

MUX, RAPU-YAMA, Memory, UI

XEARRC

AVPaEn

XEARR

ESD protection

Place near N2037

XEARLC

MicB2

Only USB charging

FM radio testpoints

place near Gazoo

6

7

I2C_2_SDA

PLUG_DET

I2C_2_SCL

for production testing

3.5mm AV CONNECTOR

HS_GND

HookDet1

XEARL

Balanced lines, route as a differential pair.

No impedance requirements.

2

GND

GND

4

VDD

C1

C2

GND

C3

RIGHTINP

RIGHTINM

C4

HPRIGHT

D1

D2

SCL

SDA

D3

_SD

D4

CPP

A2

GND

A3

A4

VDD

B1

HPLEFT

CPVSS

B2

LEFTINP

B3

B4

LEFTINM

GND

2

1

N2000

TPA6130A2YZHR

A1

CPN

C2002

GND

J2023

FM_TP_out_right

A1 A2

B2

C1 C2

27p

12

34

R

C

C

Z2000

IP5311CX5_LF

R

18p

C2008

DLM11GN601SZ2D

L2002

220R

GND

3

4

5

6

Shield

Shield

GND

R2044

2u2

GND

1

X2001

1

2

C2005

/2 1u52C2030

/2 1u5

C2009

18p

1/2 1u5

2

C2004

C2040

220n

5

VBAT

C2004

GND

8

2u2

C2007

FM_TP_in

J2011

FM_GND

5

4

J2022

FM_TP_out_left

GND

J2010

1

C2030

/2 1u5

IP4302CX2LF

V2059

68nH

L2003

2u2

120R/100MHz

C2006

GND

L2001

33n

R2037

10R

33n

C2033

B3

to ASICC1Mic2n

C2

C3

C2034

N2037

EMIF03-MIC06F3

C=1n0

2k2

1k0

2k2

2k0

A2 ECIMicBias A3

Mic2pB1

GND

B2

3

Z2001

W=0.10

L=

HS_EAR_R

HS_EAR_L

FMANT

MIC2N

MIC2P

ACI(7:0)

AUDIO(13:0)

XAUDIO(7:0)

HPLeft

HPRight

HS_MIC_N

HS_MIC

ECI_clean

AV(5:0)

MICB2

HeadDet

HS_MIC_P

Customer Care / Service Operations / Training and Vendor Development Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 4(9)AV Connector

1

WLAN/BT switch / antenna

J6400

Z6400

W=0.30

L=1

GND

X6400

3

4

GND

100R

R6000

FM_AUDIO_NR

FM_AUDIO_PL

See Note (2)

BT_TX_CONFX

BTH_CLK_REQ

See Note (5)

See Note (6)

BTH_CLK_REQ

UART_TX

UART_RX

UART_CTS

BT_WAKEUP

BT_RESETX

I2S/PCM_IN

I2S/PCM_OUT

UART_WAKE

SLEEPCLK

ANT_FM

FM_INTX

I2C_SCL

UART_RTS

BTH_CLK_REQ

See Note (1)

I2C_SDA

FM_AUDIO_PR

I2S/PCM_IN

I2S/PCM_OUT

SYSCLK

SLEEPCLK

I2S/PCM_CLK

I2S/PCM_SYNC

FM_AUDIO_NL

I2S_SDO

I2S_CLK

I2S_SDO

I2S_WS

I2S_CLK

I2S_WS

FM_AUDIO_NL

FM_AUDIO_NR

BT_RF_ACTIVE

BT_STATUS

BTH_CLK_REQ

BT_TX_CONFX

BT_RF_ACTIVE

BT_STATUS

BTHFMRDS_2.1M_WLAN A1.5 2007 WK 35 RELEASE

BLUETOOTH & FM RADIO MODULE WITHOUT RF FILTER

BT_RESETX

BT_WAKEUP

UART_RTS

UART_TX

SYSCLK

ANT_BT

UART_RX

UART_CTS

I2S/PCM_CLK

2

1

I2S/PCM_SYNC

ANT_BT

VBAT connected to VIO in CMT_IF sheet

FM_AUDIO_PR

FM_AUDIO_PL

FM_INTX

UART_WAKE

ANT_FM

I2C_SDA

I2C_SCL

8

VIO(1.8V)

9

VAFR

11

21

VReg.1.8

33

I2S_WS

34

I2S_SCK

35

I2S_SDO

36

4

BT_UART_RTS

BT_UART_CTS

5

6

BT_UART_RX

BT_UART_TX

7

25

BT_PCM_OUT/I2S_DO

26

27

TX_CONFX

28

RF_ACTIVE

STATUS

29

3

BT_PCM_SYNC/I2S_WS

UART_WAKEUP

30

31

BT_WAKEUP

INTX

32

19

GND

2

BT_PCM_CLK/I2S_CLK

20

FMANTENNA

GND

21

22

BT_RESETX

23

SLEEPCLK

GND

24

VBAT

VAFL

11

GND

REF_CLK

12

CLK_REQ

13

14

GND

15

BT_ANT

GND

16

SCL

17

SDA

18

1

0

BTHFMRDS2.2M_ES1.5

D6000

1

BT_PCM

10

11

3

6

5

4

27p

C6505

2

GND

GND

220n

C6001

GND

220n

C6002

7

9

2

6

2

1

0

2

1

0

8

7

6

5

4

3

2

GND

10

1

0

9

21

GND

NA

C6506

2u2

6

2

1

7

10

8

9

12

11

13

13

0

12

11

9

8

7

BT(23:0)

REFCLK_I

ANT_BT

FMRADIO(20:0)

FMANT

VBAT_BT

VDD1V8_BT

VIO_BT

0

8

6

J6308

J6306

J6301

J6312

J6309

J6310

J6311

J6300

J6307

J6303

J6304

J6305

8

VBAT

J6302

1

3

6

4

5

GND41

CLK

F3

F4

NC

GND42

F5

F6

VIO

F7

SLEEP_CLK

F8RS232_TX

RS232_RXF9

2

0

GND34

E4

GND35

E5

GND36

E6

E7

GND37

GND38

E8

GND39

E9

F1

GND40

F10

UART_TX

GND43

F11

F2

D5

GND26

GND27

D6

GND28

D7

GND29

D8

D9

GND30

ANT

E1

VBATT3

E10

VBATT

E11

E2

GND32

GND33

E3

GND17

C6

GND18

C7

C8

GND19

C9

GND20

GND22

D1

D10

GND31

D11

VBATT2

D2

GND23

D3

GND24

D4

GND25

B7

GND9

GND10

B8

B9

GND11

BT_PRIORITY

C1

GND21

C10

PMEN

C11

GND13

C2

C3

GND14

C4

GND15

GND16

C5

SPI_DOUT

SPI_DIN

A8

A9

SPI_CLK

B1

BT_RF

GND12

B10

B11

CLK_REQ

GND4

B2

B3

GND5

GND6

B4

B5

GND7

GND8

B6

8

GND

9

GND

GND1

A1 A10

WLAN_IRQ

A11

GND3

A2

GND2

BT_TX_CONFX

A3

A4

BT_FREQ

A5

BT_RF_ACTIVE

A6

SPI_CSX

A7

11

GND

12

13

GND

GND

14

2

GND

3

GND

GND

4

GND

5

6

GND

GND

7

ENW49701N_LGA80

N6300

GND

1

10

GND

GND

GND

ANT_WLAN

REFCLK_I

VIO_WLAN

BT_RF

BT_WLAN(6:0)

WLAN(15:0)

BT23:0)

GND

3

2

1

0

6

ExtSysClkReq

J6401

BTH_CLK_REQ

4

WLAN_CLK_REQ

PUSL(15:0)

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 5(9)

Bluetooth, WLAN

kbc_0

kbc_3

2

ROW1

Camera

3

9

5

SK

1

NOT

MK

COL0 COL1

9

*

Vol Up

kbr_4

MK2

APPS

5

ROW5

This can be also connected Genio.

UI

#

Vol Down

USED

1

RightSK

ROW3

MK1

USED

kbr_2

SK

#

UI

kbc_4

REFERENCE AREA FOR THIS SHEET 4400-4599

0

0

LeftSK

NaviLEFT

Keyboard DFO LEDs (Gazoo)

Player keys LEDs (NJOY)

MK

ROW0

7

Camera switch

UI

4

NaviDOWN

7

2

kbc_1

UI

8

6

4

UI

UI

*

COL3

Keyboard flex connector (B2B)

CLEAR

SCL

Keyb LED2(V2004)

Key matrix

kbr_1

6

COL2

SENDNaviUP

kbr_0

ROW4

COL4

kbc_2

MK3

UI

NaviRIGHT

kbr_5

Own TX filtering

8

kbr_3

SK

MK

NaviSELECT

UI

UI

NOT

D2

In6

D3

GND

D4

Out7

D5

Out6

ROW2

Keyb LED1(V2000)

SDA

3

UI

ESD filter

Out2

A5

Out1

B1

In3

B3

GND

B5

Out3

C1

In5

C2

In4

C3

GND

C4

Out5

C5

Out4

D1

In7

GND

7

EMIF07-LCD02F3

Z4404

A1

In2

A2

In1

GND

A3

A4

IP4302CX2LF

R1498

0

10k

R1499

GND

GND

3

C4430

GND

GND

1

0

1

2u2

E2

E3

INT

E4

TRIG

0u47

C4434

ADDR_SEL0

C3

GND

C4

VDD

SCL

D1

GPO

D2

D3

CLK_32K

GND

D4

E1

SDA

EN

VOUT

CFLY2N

A3

A4

CFLY2P

G

B1

ADDR_SEL1

B2

B3

CFLY1N

B4

CFLY1P

C1

R

C2

VBAT

N4431

LP5521TMX_NOPB

A1

B

A2

0

C4431

2u2

C4432

0u47

GND

5

2

VIO

VBAT

MESS_IND_LED

2

GND

3

4

5

6

7

8

9

S4400

1

X4400

1

10

11

12

13

14

15

16

17

18

19

2

20

27p

EMC

27p

GND

C4435

In7

D2

In6

D3

GND

D4

Out7

D5

Out6

C2500

A4

Out2

A5

Out1

B1

In3

B3

GND

B5

Out3

C1

In5

C2

In4

C3

GND

C4

Out5

C5

Out4

D1

GND

EMIF07-LCD02F3

Z4405

A1

In2

A2

In1

GND

A3

GND

GND

56p

GND

GND

56p

C4402

11

4

9

GND

C4401

LEDOUT

VBAT

GND

8

2

10

1

kbc_2

col3COL3

col4COL4

ROW5 row5

COL2 col2

COL0 col0

kbr_0

kbc_3

KEYB(15:0)

kbc_4

kbr_4

kbc_0

KB_LED1

SetCurrKB

kbr_5

PWRONX

kbr_2

kbr_3

PUSL(15:0)

LED(6:0)

ROW0 row0

ROW1 row1

ROW3 row3

I2C2(1:0)

KB_LED2

ROW4 row4

row2ROW2

kbc_1

kbr_1

col1COL1

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 6(9)

Keyboard

Band I&II

Band V&VI&VIII

Band II&III&IX

RFinRFout

ISO6CPLD

L7500

L7525

2u2

C7512

4u7

C7564

R7502

22k

2u2 C7574

L7543

NA

R7520

470R

C7514

10n

2u2

C7567

Z7542

NA

C7536

1p

824-849MHz

Z7544

28R/100MHz

L7501

C7560

10u

3p3

C7515

L7561

60R/100MHz

C7565

2u2

R7924

A7500

RITSA6 SHIELD ASSEMBLY

040-056209

29

Out2

31

Vcc2_amp2

Out1

33

Vbat

4

GND

5

Icntrl1

6

Vcc1_amp2

7

9

In1

In3

1618

Vcc1_amp3

19

GND

Vcc_amp1

2

Icntrl3

20

Vbat

21

Vcc2_amp3

23

Out3

25

27

GND

N7540

11

In2

13

Vcc1_amp2

14

Icntrl2

900/1800MHz

Z7521

47k

R7560

C7568

10n

2u2

C7572

C7571

100p

1uH

L7560

10n

C7502

G7500

R7921

C7500

100n

L7521

R7923

8p2

C7526

Z7541

Vb

10R

R7501

L7562

C7566

10n

100n

VC1

8

GND

9

Icont_h

C7503

Vsw

26

TX_1

27

28

Icont_I

29

GND

Vpd

3

Vdet

4

VC3

5

VC2

6

7

RX1

18

TRX3

19

Vgain

2

20

GND

Ant

21

22

GND

GND

23

24

Vcc1

25

GND

1

10

TX_2

11

Vcc3

12

GND

TRX1

13

14

Vcc2

GND

15

TRX2

16

17

RX2

N7520

GND

10n

C7573

L7522

NA

10k

R7510

J7536

10n

C7533

NA

L7544

10u

C7562

39R

R7521

C7569

10u

C7561

10n

L7540

2u2

C7570

120R/100MHz

L7563

L7541

C7510

L7575

120R/100MHz

18p

L7524

15nH

L7502

120R/100MHz

C7511

33p

2u2

C7509

C7504

100n

18p

C7548

Z7523

850/900MHz

Z7540

T7520

DEA201810BT-7090C1

J7537

GNDREFBUF

L2

NC

L3

GNDCP

GND_PRE

L4

L5RXOUT_PQ

GNDDIG

L6

L7

NC

GNDDIG3

L8

REFG

L9

GNDBB_TX

K11

DAC_REF1

RFC10

K2

K3

RFC11

K4RXOUT_PI

K5RXOUT_NQ

K7

GNDDIG2K8REFP

K9

VBAT_TX

L1

HV

L10

TXQ_0

J11

J2

RFC5

J3

VREF_CM

J4RXOUT_NI

J5SCLK

SDATA J6

GNDCP_TX

J7

J8

REFM

TXI_180

J9

K10

TXI_0

GND_VCO

H2

H3

GNDBB_RX

PRG

H4

H5XENA

XRESET

H6

GNDPRE_TX

H7

OSCIN

H8

NC

H9

GND_VCO_SUB

J1

TXQ_180

J10

G10

P_OUTP

G11

G_OUTP

C1PI

G2

C2NI

G3

G4

VBAT_RX

G7

DAC101

G9

DAC202

H1

VBAT_VCO

H10

DAC201

H11

C1PQ

E4

VBAT_WTX

F1

C2NQ

P_OUTM

F10

F11

G_OUTM

C2PI

F2

C2PQ

F3

C1NQ

F4

GND_RF_TX2

F8

GNDRF_TX

F9

C1NI

G1

W_OUTN_L

W_OUTN_H2

D11

D2

WTRP2

RFC4

D3

RFC9

D7

D9

DET

NC

E1

W_OUTM_L

E10

W_OUTP_H2

E11

E2

CLKONX

VBEXT

E3

W_OUTP_H

C10

GND_TX_SUB

C11

C2

DAC102

DAC203

C3

C4

RFC3

TRP2

C6

C7

RFC7

C8

MUX_IN

TXCC9

GNDVCO

D1

D10

W_OUTN_H

B10

B11

GNDVGA

B2

MUX_OUT

RFC1

B3

B4

RFC2

B5

GNDLNA

B6

SHLD_GND

RFC6

B7

B8

RFC8

WDET

B9

GNDMIX

C1

INP_850

A10

INM_850

A11

INP_2150

A2

INM_2150

A3

INP_1900

A4

A5

INM_1900

A6

INP_1800

A7

INM_1800

A8

INP_900

INM_900

A9

WTRP1

B1

N7500

TRP1

A1

10u

C7563

J7538

C7506

100n

10n

C7501

Z7543

1920-1980/1850-1910MHz

4k7

R7922

H7

H8

GND_SMPS

R7500

G5

MUX2

IND_SMPS

G6

IND_SMPS

G7

G8

IND_SMPS

H1

FB_SMPS

VHI

H2

VBB_VRX

H3

VREG50S

H4

H5

CB_SMPS

H6

GND_SMPS

GND_SMPS

GND_DIG

F3

F4

HV

F5

GND_VREG50_d

F6

INPUT_SMPS

F7

INPUT_SMPS

INPUT_SMPS

F8

SCLK

G1

SMPS_CNTRL

G2

G3

GND_DIG

GND_VREG50S

G4

D8

E1

GND_DIG

GND_DIG

E2

E3

GND_DIG

E4

XRESET

OUT_BOOST

E5

E6

OUT_BOOST

OUT_BOOST

E7

OUT_BOOST

E8

DATA

F1

F2

ENABLE

C6

GND_BOOST

C7

GND_BOOST

C8

GND_BOOST

VREF

D1

VXO

D2

D3

GND_DIG

GND_DIG

D4

D5

IND_BOOST

IND_BOOST

D6

D7

IND_BOOST

IND_BOOST

GND_DIG

CB_DCDC

B4

B5

GND_DCDC

GND_DCDC

B6

B7

IND_DCDC

B8

VBATT

C1

PA_DAC

ANT_T1

C2

GND_DIG

C3

C4

MUX1

C5

GND_BOOST

A1

FB_DCDC

GND_DIG

A2

VBB_VRX1

A3

A4

VREG50BD

GND_VREG50BD

A5

A6

CB_BOOST

A7

IND_DCDC

A8

VBATT

FB_BOOST

B1

B2

ANT_T2

B3

N7560

NA

C7547

18p

C7534

100p

NA

C7505

L7526

100n

C7576

100p

C7577

18p

C7578

18p

C7579

18p

C7575

18p

REFL_MEAS

FWD_MEAS

C7535

5p6

TXresetX

RFbusEna

RFbusDat

RFbusClk

Clk_Buf_en

Vcc_WPA

VCTCXO_out

VrefRF01

DAC102

VCTCXO_in

Vcp1

ANT

Clk_Buf_en

Vbat

Vbat_PA

TXFEM_Vpd

VXO

Vb

Vcc_Vapaus

Vcc_PA

Vb

Vbat

Band_sel

Aux_cntrl1

DAC203

DAC202

FWD_MEAS

REFL_MEAS

HW_id

Vcc_Vapaus

Aux_cntrl3

Vcc_Vapaus

Vcc_Vapaus

RFCLKEXT

Aux_cntrl2

TXFEM_Vpd

Band_sel

Vcc_WPA

Vbat_PA

Vcc_WPA

Vcc_WPA

TXFEM_VC3

TXFEM_VC2

TXFEM_VC1

TXFEM_Vgain

Vbat_PA

DAC102

DAC201

VrefRF01

DAC_REF1

VREFCM

TXresetX

RFbusClk

RFbusDat

RFbusEna

11

C7599

1p2

X7501

3

4

Z7505

W=0.30

L=

J7590

L7599

33nH

J7592

Clock buffer for WLAN/BT

R3394

GND

1k

GND

22k

R3392

100p

C3392

68k

R3393

C3390

18p

BFR93AW

V3390

L3390

33R/100MHZ

VCTCXO_out

RFCLKEXT_BT

VXO

01

VRCP2VBAT

432

VRCP1VREFVR1

RFPWR(5:0)

LPRFCLK RFClkExt

R7505

27R

2u2

C7544

K1

VCP

G8

VDAC

Vcp

Vcp1

C7508 10n

47R

R7506

VBAT_BAT

L11

E9

VrefRF01

10n

C7507

VDIG

K6

VXO

VXO

VCP1

VREFRF01

VBATRF

1

0

3

4

RFPWR(5:0)

RFClkN

RFClkP

0

1

RFCLK(1:0)

TXC

AFC

1

0

TXCCONV(4:0)

TXResetX

RFBusClk

RFBusDa

RFBusEn1X78

0

6

XENARFBUSENA

SDATARFBUSDA

SCLKRFBUSCLK

RFCTRL(11:0)

XRESETTXRESETX

RXIP

TXQP

TXQn

TXIP

TXIN

IREF

RXIN

RXQP

RXQN

VREF

8

4

5

3

0

1

6

7

9

2

RXIPRXIP

RXINRXIN

DACREF1DACREF1

RFCONV(20:0)

RXQNRXQN

VREFCMVREFCM

TXQPTXQP

TXQNTXQN

TXIPTXIP

TXINTXIN

RXQPRXQP

R7504

Vcc_PA

Vbat_PA

TXFEM_Vpd

TXFEM_VC2

TXFEM_VC3

TXFEM_VC1

TXFEM_Vgain

DAC203

Vcc_WPA

Vcc_WPA

DAC202

Vcc_WPA

DAC201

Aux_cntrl4

C7527

18p 18p

C7521

C7543

1n

C7528

2u2

C7531

18p

C7545

100p

C7542

1n

1n

C7541

18p

C7529 C7530

18p

C7520

3p3

10n

C7546

C7532

18p

Vcc_WPA

Vcc_WPA

Vcc_PA

TXFEM_Vgain

TXFEM_VC3

TXFEM_VC2

TXFEM_VC1

Vcc_WPA

Vcc_PA

Vbat_PA

DAC203

DAC202

DAC201

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 7(9)

RF

Socket model

- 5407157: compact board socket (SMK)

CCP_DATAN

Internal Pull-up in use

CCP_CLKN

RAPU’s internal termination in use

CCP_CLKP

LedFlashInt

3MPIX SMIA65 CAMERA + GEMINI FLASH

I2C0_SCL

I2C0_SDA

LedFlashEn

LedFlashStrobe

I2C_SDAToshiba used as default

CCP_DATAP

SMIA65 compact SOCKET

TxMask

XSHUTDOWN

I2C_SCL

Douple capacitor changed single ones for better layout!

CAMERA ACME LITE

RAPU’s internal termination in use

CAMCLK

VIN

GND

VCAM_2V8

DGND

Camera powers

Driver of GEMINI flash

Connected to I2C0

AGND

Not used

GND

BH28SA2WGUT

N1401

GND

STBY

VOUT

100n

GND

GND

C1450

GND

ASSY

A1400

FLASH SHIELD

040-056210

5

6

C1455

220n

VT6T12T2R

V1490

1

2

3

4

C1408

2u2

120R/100MHz

L1400

C1458

GND

9

GND

12

100n

2

3

4

5

6

7

8

9

Part is not suitable for dual pass SMD process

GND

X1400

1

10

11

12

220R

R1491

2u2

C1407

3

4

5

6

GND

13

10

GND

2

X1500

1

2

27p

C1452

NA

GND

6

ILED

OUT

7

GND

8

9

HPLED

6

13

LX

VDD

14

EN

15

16

STR

2

SETF

SCL/CTRL1

3

4

SDA/CTRL0

SETI

5

N1400

ADP1653ACPZ-R7

17= GND

1

SETT

INTF

10

11

_INT

12

PGND

4u7

GND

16

GND

C1409

VBAT

GND

GND

13

GND

GND

GND

GND

VBAT

FPF1003A

A1

VOUT

A2

VIN

B1

VOUT

B2

VIN

C1

GNDON

C2

VCAM_1V8

GND

19

12

N1402

13

10u

C1406

GND

VCAM_1V8

GND

GND

0

1k

R1492

4

1u

C1404

17

1

GND

VBAT

11

VCAM_1V8

14

GND

15

27p

C1453

NA

C1454

1u

27p

C1403

C1405

10u

GND

5

NA

33R

R1490

GND

MA21D34001JN

V1401

7

GND

VCAM_2V8

VIO

MESS_IND_LED

VCAM_1V8

2u2H

L1401

100n

CHG_IND_LED

100n

C1451

20

C1410

12

VCAM_2V8

3

27p

NA

GND

GND

VANA

8

DATA+

9

GND

8

C1400

29

GND

3

GND

GND

30

31

GND

GND

32

4

CLK+

CLK-

5

GND

6

7

GND

EXTCLK

22

23

DGND

24

GND

25

GND

GND

26

27

GND

GND

28

14

XSHUTDOWN

15

SCL

SDA

16

NC

17

18

NC

GND

19

2

DATA-

VCAP

20

21

TCM8330MD

N1450

4858138

1

GND

VDIG

10

11

NC

NC

12 13

AGND

ACME_VCAP1V2

CCP_CLK1_p

CCP_CLK1_n

CCP(20:0)

LX

"Cam2V8 enable"

"Cam1V8 enable"

ILED

CCP_Data1_n

CCP_Data1_p

CCP_CLK0_n

CCP_Data0_n

CCP_Data0_p

VCAP

CCP_CLK0_p

HPLED

CCP(20:0)

CCP(20:0)

CCP(20:0)

CCP(20:0)

ACME_VCAP

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 8(9)

Cameras

A

C2281 G 8C6505 T 4G7500 D2 N7560 C 8

X

A1400 R 7C2282 F 8C7500 B 3

JR

X1400 R 5

A2700 E 5C2285 H 7C7501 D 2J6400 T 2R1490 T 5X1500 U 5

A2800 G 5C2294 H 7C7502 D 2J7590 A 7R1491 T 6X2001 T 7

A7500 C 5C2296 F 7C7503 B 2J7592 A 7R1492 Q 7X2060 H 1

B

C2314 E 8C7504 B 2

L

R1498 F 9X2070 zF 7

B2100 A 4C2315 G 6C7505 B 3L1400 Q 6R1499 G 9X2450 H 2

B2200 G 7C2316 H 7C7506 B 2L1401 R 6R2037 T 7X2700 E 5

C

C2317 H 8C7507 C 2L2001 U 8R2044 H 8X3200 E 3

C1100 U 2C2319 G 7C7508 D 2L2002 T 7R2060 H 5X3300 U 3

C1404 R 4C2326 F 7C7509 B 7L2003 U 7R2061 H 6X4400 E 8

C1405 R 6C2451 I 4C7510 D 2L2100 U 7R2070 F 5X6400 U 2

C1406 R 7C2452 H 1C7511 E 3L2101 H 7R2071 U 6X7501 A 7

C1407 T 3C2453 G 1C7512 B 4L2102 C 5R2200 F 7

Z

C1408 T 3C2454 H 3C7514 C 2L2103 C 5R2450 H 4Z2000 T 8

C1409 T 3C2455 I 3C7515 C 3L2104 H 8R2701 D 7Z3300 T 2

C1410 T 3C2456 H 1C7520 C 7L2105 H 7R2702 D 7Z3301 T 2

C1450 U 3C2457 G 2C7521 C 6L2106 H 7R2703 D 7Z4404 D 7

C1451 U 2C2500 G 9C7526 E 5L2107 H 8R2801 H 5Z4405 D 7

C1454 U 3C2700 E 7C7527 C 7L2108 H 8R2802 F 6Z7521 C 3

C1455 S 6C2701 D 7C7528 B 5L2109 B 5R2803 I 6Z7523 D 3

C1458 T 3C2702 D 7C7529 E 6L2110 B 5R2804 H 5Z7540 C 5

C2002 U 7C2800 F 3C7530 E 6L2202 H 7R2805 H 5Z7541 C5

C2004 T 9C2801 E 5C7531 E 6L2203 E 7R2852 E 5Z7542 D 5

C2005 T 8C2802 F 3C7532 E 6L2204 F 8R2853 E 5Z7543 D 3

C2006 T 8C2806 F 3C7533 E 6L2205 G 8R2854 H 4Z7544 D 3

C2007 T 8C2810 H 6C7534 D 3L2206 F 7R2855 H 4

C2008 U 7C2811 H 5C7535 C 3L2300 E 7R2856 I 4

C2009 U 7C2814 H 4C7541 E 4L2310 F 6R2857 H 4

C2030 T 9C2816 G 3C7542 D 3L2340 E 8R2858 G 6

C2033 T 7C2817 G 3C7543 B 4L2450 H 1R3200 F 5

C2034 T 8C2818 F 3C7544 B 2L2451 H 3R3300 F 2

C2040 H 8C2820 E 4C7545 E 5L3305 Q 8R3302 G 2

C2070 E 7C2821 E 5C7546 B 4L3390 F 1R3367 R 8

C2071 F 7C2823 F 6C

7547 C 2L7500 C 6R3392 E 2

C2072 F 5C2824 E 6C7548 C 2L7501 E 8R3393 E 1

C2108 I 7C2825 E 6C7560 E 8L7502 C 7R3394 F 1

C2109 I 7C2826 E 5C7561 D 8L7521 C3 R6000 T 4

C2110 I 7C2830 H 4C7562 D 8L7524 E 3R7500 B 3

C2115 A 3C2841 E 4C7563 D 8L7525 C 3R7501 E 2

C2116 A 4C3100 F 4C7564 E 7L7540 D 5R7502 E 2

C2211 H 7C3205 F 4C7565 D 8L7541 B5 R7505 C 2

C2213 F 8C3300 G 3C7566 C 8L7560 D 8R7506 E 4

C2214 F 8C3301 F 3C7567 C 8L7561 E 7R7510 E 3

C2222 H 7C3303 G 2C7568 C 8L7562 B 8R7520 E 6

C2227 F 8C3304 G 3C7569 B 8L7563 B 3R7521 C 3

C2228 F 8C3306 G 2C7570 B 2L7575 E 5R7560 D 8

C2229 H 7C3307 F 3C7571 C 8L7599 A 7R7921 D 3

C2230 E 6C3310 Q 8C7572 D 8

M

R7922 D 3

C2231 F 8C3312 R 8C7573 C 8M2100 R 3R7923 D 3

C2232 G 8C3313 S 8C7574 C 8

N

R7924 D 3

C2245 E 7C3314 U 4C7575 B 3N1100 U 2

S

C2247 F 7C3316 R 8C7576 B 3N1400 R 7S4400 C 1

C2249 H 8C3322 R 8C7577 B 3N1401 T 3

T

C2250 E 8C3365 S 8C7578 B 3N1402 T 3T7520 D 3

C2251 F 6C3390 E 1C7579 B 4N1450 U 3

V

C2252 E 7C3392 E 2C7599 A 7N2000 T 8V1401 R 7

C2253 H 8C4401 D 7

D

N2037 U 8V1490 T 6

C2265 F 7C4402 D 7D2800 G 5N2200 G 8V2059 S 8

C2266 F 6C4430 H 5D3000 G 5N3300 U 4V2100 U 7

C2267 H 7C4431 I 5D3300 F 2N3301 R 8V2103 H 9

C2268 G 6C4432 I 5D6000 T 5N4431 I 5V2104 H 9

C2269 H 8C4434 I 5

F

N6300 S 2V2300 F 8

C2271 F 7C4435 H 6F3300 U 4N7500 C 2V3301 G 3

C2275 F 8C6001 S 6

G

N7520 D 6V3390 F 2

C2280 F 7C6002 S 6G2200 C 9N7540 D 4

Bottom

Top

Customer Care / Service Operations / Training and Vendor Development

Condential Copyright © 2007 NOKIA Only for training purposes Version: 1.0 | 26.1.2009 | 5630 | Board version: 2PP_05s | | Page 9(9)

Component nder

Loading...

Loading...