NEC uPD77213GJ-xxx-8EN, uPD77213F1-xxx-DA2, uPD77210GJ-8EN, uPD77210F1-DA2 Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

µµµµ

PD77210, 77213

16-BIT FIXED-POINT DIGITAL SIGNAL PROCESSOR

The µPD77210 and 77213 are 16-bit fixed-point digital signal processors (DSP).

Compared with the existing members of the µPD77111 Family, the µPD77210 Family consumes less power and is

ideal for battery-driven mobile terminal applications such as PDAs and cellular telephones. The µP77210 Family is

DSP is also compatible with the µPD77111 Family at the binary level.

The µPD77210 Family consists of the µPD77210 and 77213. Unless otherwise specified, the µPD77210 Family

refers to the entire family. If there are some differences in function or operation among family products, they are

described under their respective names.

The functions of the µPD77210 Family are described in detail in the following user’s manuals. Refer to these

manuals when designing your system.

PD77210 Family User’s Manual - Architecture: In preparation

µ

PD77016 Family User’s Manual - Instructions: U13116E

µ

FEATURES

• Instruction cycle (operating clock):

PD77210 6.25 ns MIN. (160 MHz MAX.)

µ

PD77213 8.33 ns MIN. (120 MHz MAX.)

µ

• Memory

-Internal instruction memory:

PD77210 :RAM 31.5 Kwords x 32 bits

µ

PD77213 :RAM 15.5 Kwords x 32 bits

µ

ROM 64 Kwords x 32 bits

-Data memory:

PD77210 :RAM 30 Kwords x 16 bits x 2 planes (X and Y data memories)

µ

External memory space 1 Mwords x 16 bits (common to X and Y data memories)

PD77213 :RAM 18 Kwords x 16 bits x 2 planes (X and Y data memories)

µ

ROM 32 Kwords x 16 bits x 2 planes (X and Y data memories)

External memory space 1 Mwords x 16 bits (common to X and Y data memories)

• Peripheral

-Audio serial interface: 1 channel

-Time-division serial interface: 1 channel

-16-bit host interface: 1 channel

-16-bit general-purpose port

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. U15203EJ3V0DS00 (3rd edition)

Date Published November 2001 NS CP(K)

Printed in Japan

-16-bit timer: 2 channels

-Peripheral-memory DMA transfer function

-SD (Secure Digital) card interface

:µPD77213 only

The mark shows major revised points.

©

2001

• Supply voltage

-DSP core supply voltage: 1.425 to 1.65 V (MAX. operating speed 120 MHz),

1.55 to 1.65 V (MAX. operating speed 160 MHz)

-I/O pin supply voltage: 2.7 to 3.6 V

ORDERING INFORMATION

Parts Number Package

PD77210F1-DA2 161-pin plastic fine pitch BGA (10 x 10)

µ

PD77210GJ-8EN 144-pin plastic LQFP (fine pitch) (20 x 20)

µ

PD77213F1-xxx-DA2 161-pin plastic fine pitch BGA (10 x 10)

µ

PD77213GJ-xxx-8EN 144-pin plastic LQFP (fine pitch) (20 x 20)

µ

Remark xxx indicates ROM code suffix.

µµµµ

PD77210, 77213

PD77210 only

µ

2

Data Sheet U15203EJ3V0DS

External memory

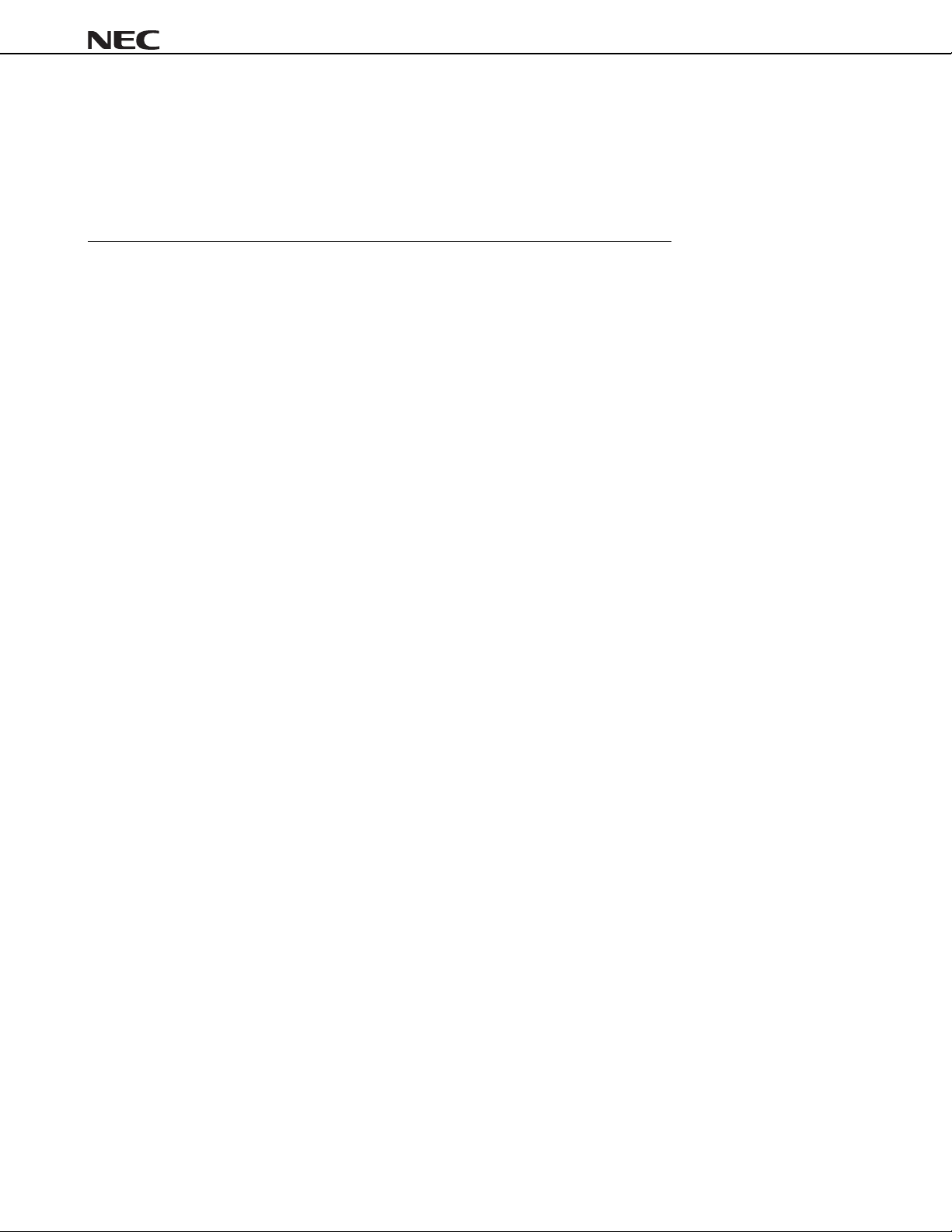

BLOCK DIAGRAM

Peripheral unit

X bus

External

memory I/O

unit

Y bus

Instruction

memory

MAC

16 × 16 + 40 → 40

R0 to R7

ALU (40)

Operation unit

BSFT

µµ

µ

µ

PD77210, 77213

Serial I/O

(AUDIO)

Serial I/O

(TDM)

Host I/O

DMA

controller

Interrupt

controller

Port

Timer

Note

Peripheral-memory transfer bus

Peripheral bus

Interrupt

control

Loop control

CPU control

X memory

X memory

data

addressing

unit

stack

Y memory

Y memory

data

addressing

unit

Data memory

Main bus

Program control

unit

PC stack

Clock control

SD Card I/O

Data Sheet U15203EJ3V0DS

IE

I/O

RESET

CSTOP

HALTS

STOPS

CLKOUT CLKIN

PLL

µ

Note PD77213 only

3

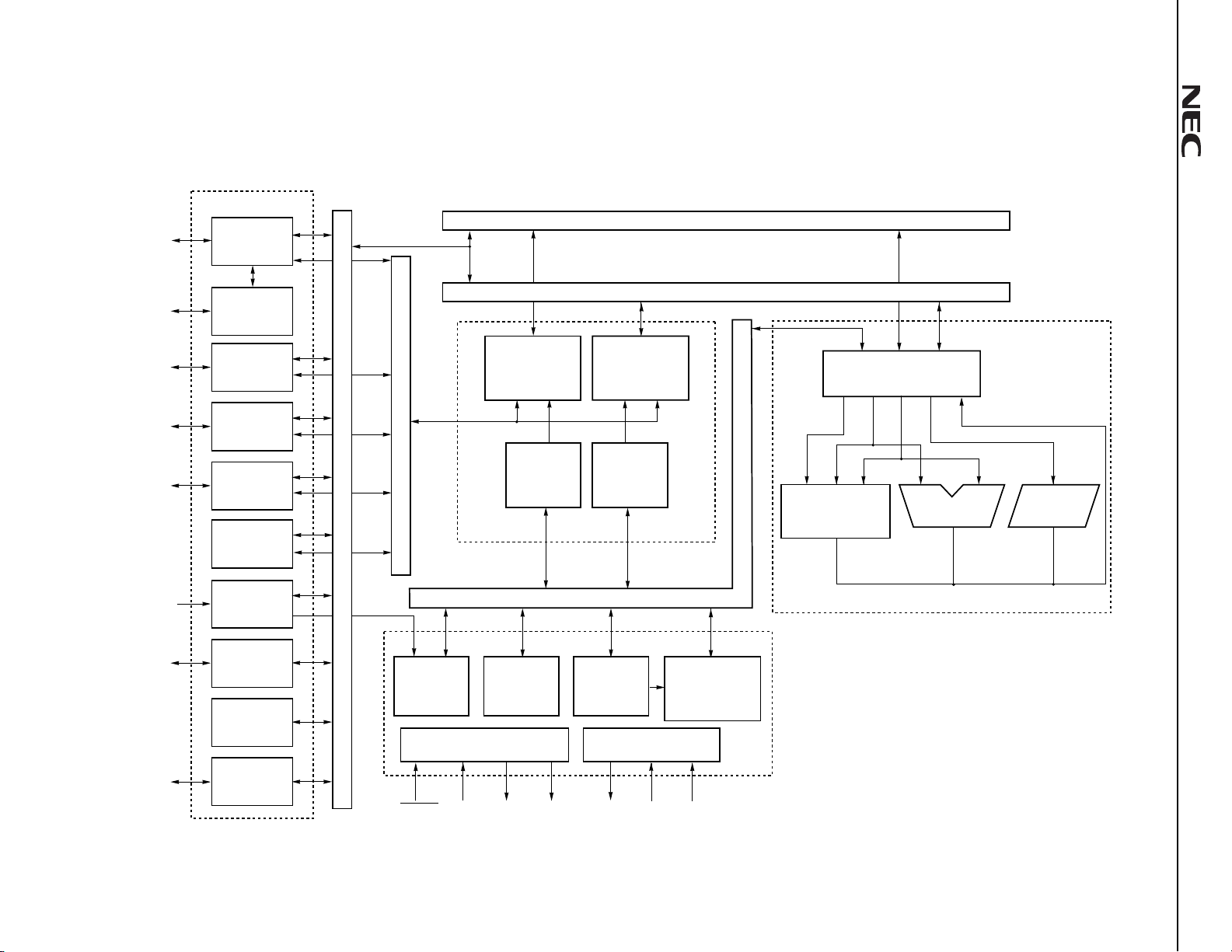

FUNCTIONAL PIN BLOCK

Serial interface

(time division serial)

Serial interface

(audio serial)

SD card interface

Host interface

Note

Port

TSO

TSORQ

TSOEN

TSCK

TSI

TSIEN

TSIAK

ASOEN/LRCLK

ASIEN/MCLK

ASCK/BCLK

ASI

ASO

SDDAT0

SDCR

SDCLK

SDMON

P0 to P15

16

HCS

HA0, HA1

2

HRD

HRE

HWR

HWE

HD0 to HD15

16

+1.5 V +3.3 V

IV

DD

EV

DD

PLL0 to PLL3

MA0 to MA19

MD0 to MD15

TCK, TDI, TMS, TRST

RESET

INTmn

CLKIN

CLKOUT

STOPS

CSTOP

HALTS

MRD

MWR

MHOLDRQ

MHOLDAK

MBSTB

MWAIT

TIMOUT

TDO, TICE

µµµµ

PD77210, 77213

Reset and interrupt

16

Clock

4

System control

20

16

External data memory

interface

Timer

2

For debugging

4

GND

Note

PD77213 only

µ

Caution Some port pins, host interface pins, serial interface pins, interrupt pins, and SD card interface

pins are alternate function pins.

Remark m, n = 0 to 3

4

Data Sheet U15203EJ3V0DS

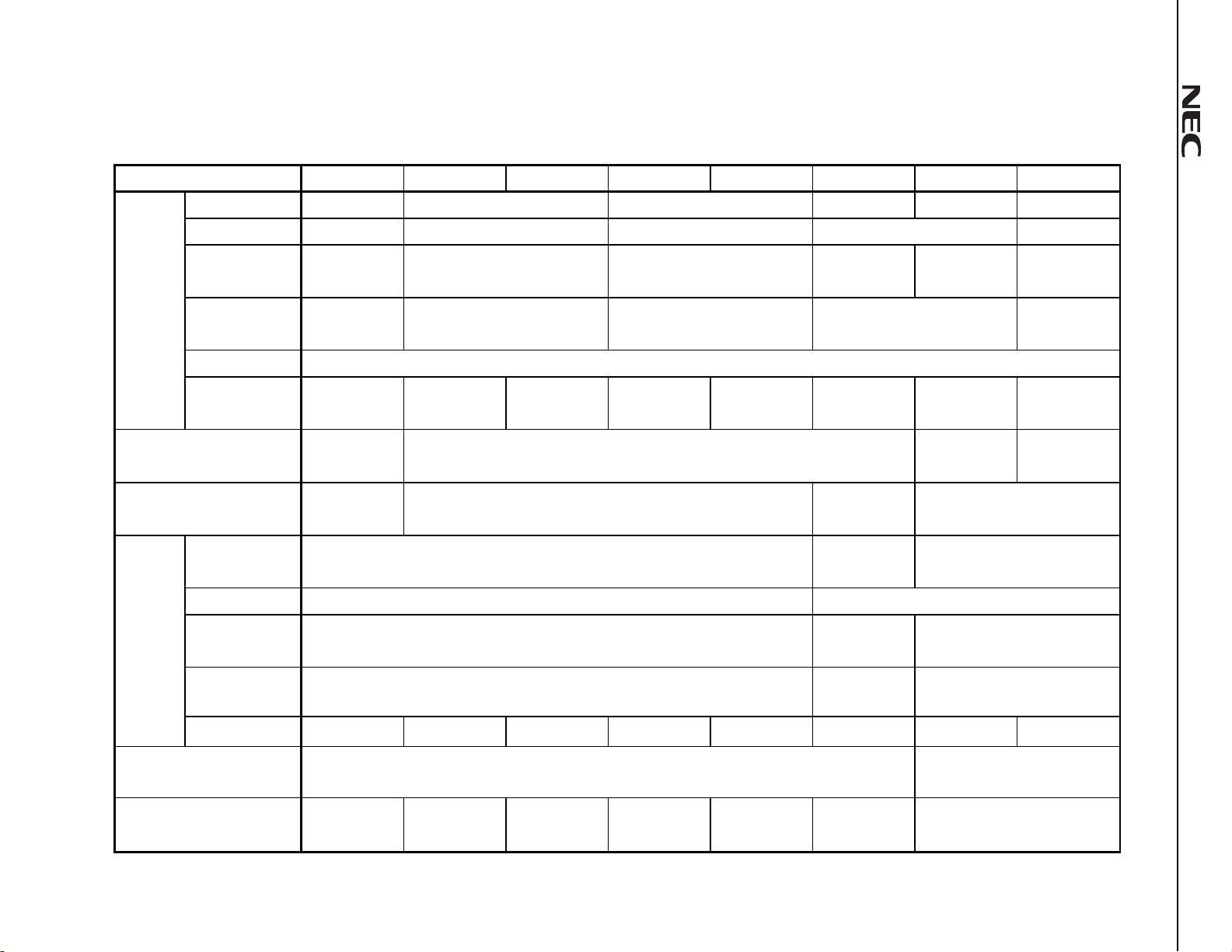

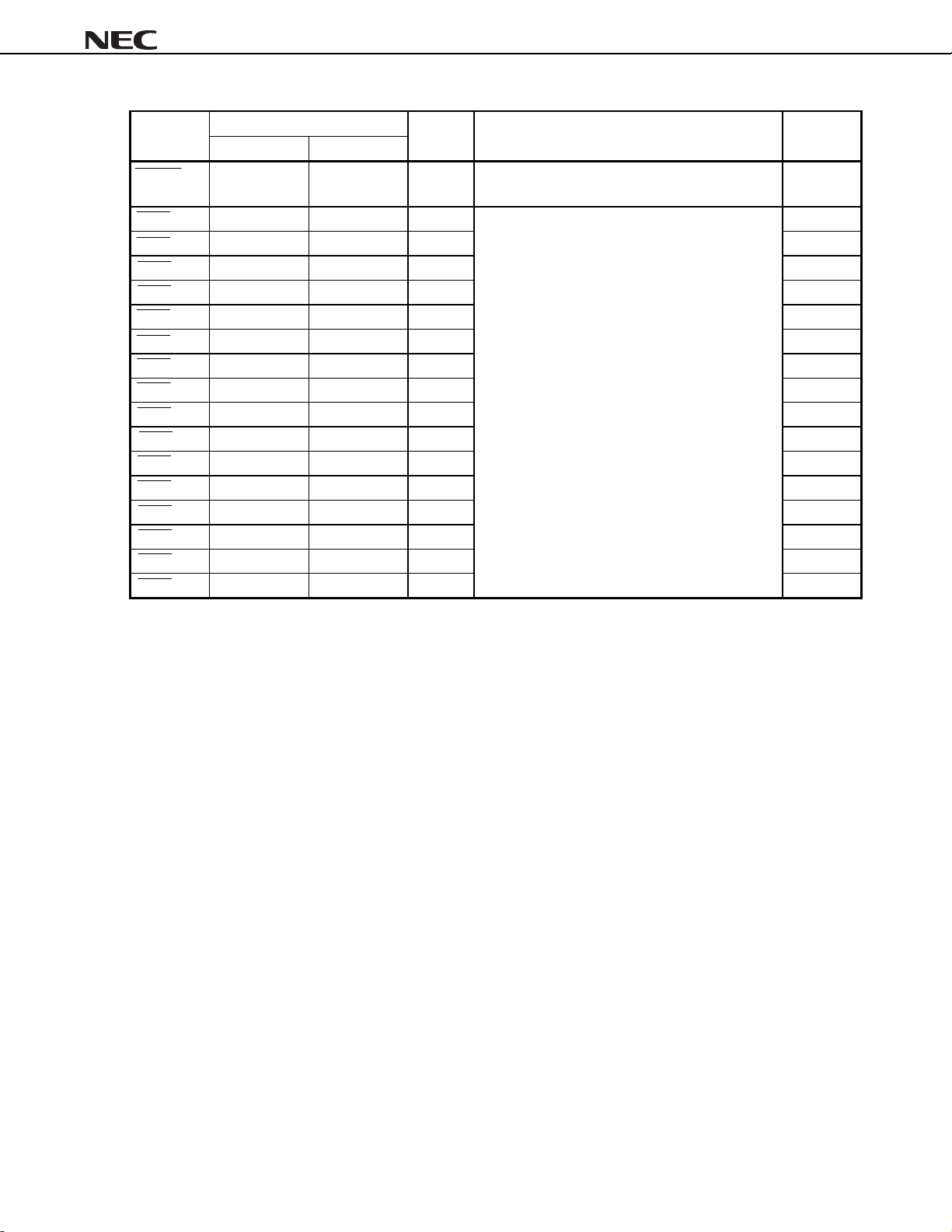

DSP FUNCTION LIST

PD77115

µ

11.5 K × 32

16 K × 16 each

None

Integer multiple

of ×1 to 16

(external pin)

1 channel

(audio CODEC)

8 bits

1 channel

(16-bit resolution)

None

PD77114

µ

8 K × 16 each

Item

Memory

space

(words ×

bits)

Data Sheet U15203EJ3V0DS

Instruction cycle (at maximum

operating speed)

Multiple

Peripheral

Int. instruction RAM

Int. instruction ROM

Data RAM

(X/Y memory)

Data ROM

(X/Y memory)

Ext. instruction memory

Ext. data memory (X/Y

memory)

Serial interface

Host interface

General-purpose

port (I/O

programmable)

Timer

PD77110

µ

35.5 K × 32

None

24 K × 16 each

None

32 K × 16 each

15.3 ns

(65 MHz)

Integer multiple

of ×1 to 8

(external pin)

PD77111

µ

None

1 K × 32

31.75 K × 32

3 K × 16 each

16 K × 16 each

PD77112

µ

16 K × 16 each

Integer multiple of ×1 to 16

(mask option)

2 channels

(speech CODEC)

8-bit bus

4 bits

None

PD77113A

µ

None

13.3 ns

(75 MHz)

3.5 K × 32

48 K × 32

16 K × 16 each

32 K × 16 each

PD77210

µ

31.5 K × 32

None

30 K × 16 each

None

1 M × 16

6.25 ns

(160 MHz)

Integer multiple of ×10 to 64

(external pin)

2 channels (time-division, audio)

16-bit bus

16 bits (some are alternative with host)

2 channels

(16-bit resolution)

PD77213

µ

15.5 K × 32

64K × 32

18 K × 16 each

32 K × 16 each

1 M × 16 (8 K ×

16, using SD I/F)

8.33 ns

(120 MHz)

µµ

µ

µ

PD77210, 77213

SD card I/F

80-pin TQFP

80-pin FBGA

−

DSP core: 1.5 V

I/O pins: 3.3 V

161-pin FBGA

144-pin LQFP

SD card I/F

Supply voltage

Package

Others

−

100-pin TQFP

−

80-pin TQFP

80-pin FBGA

−

DSP core: 2.5 V

100-pin TQFP

I/O pins: 3 V

−

80-pin FBGA

−

100-pin TQFP

5

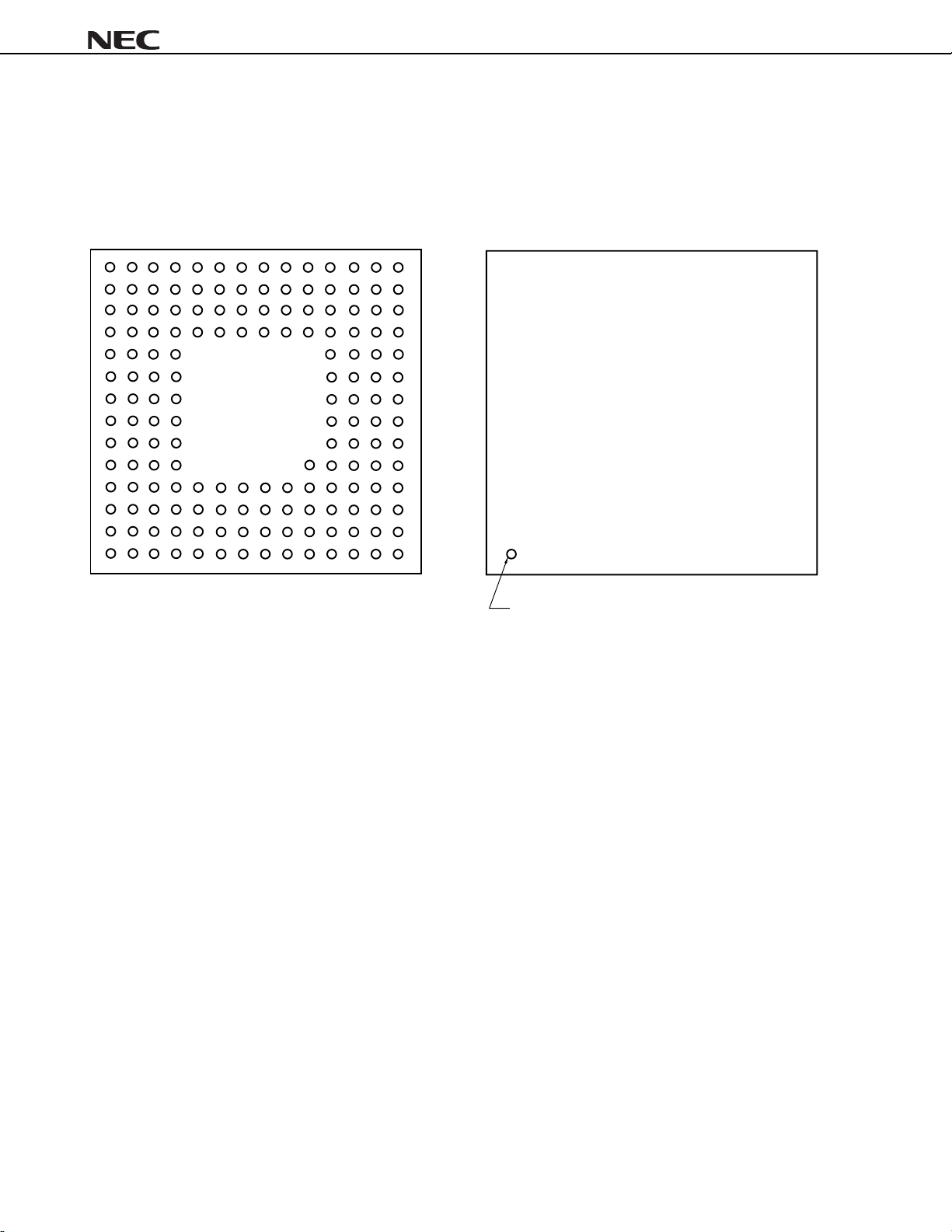

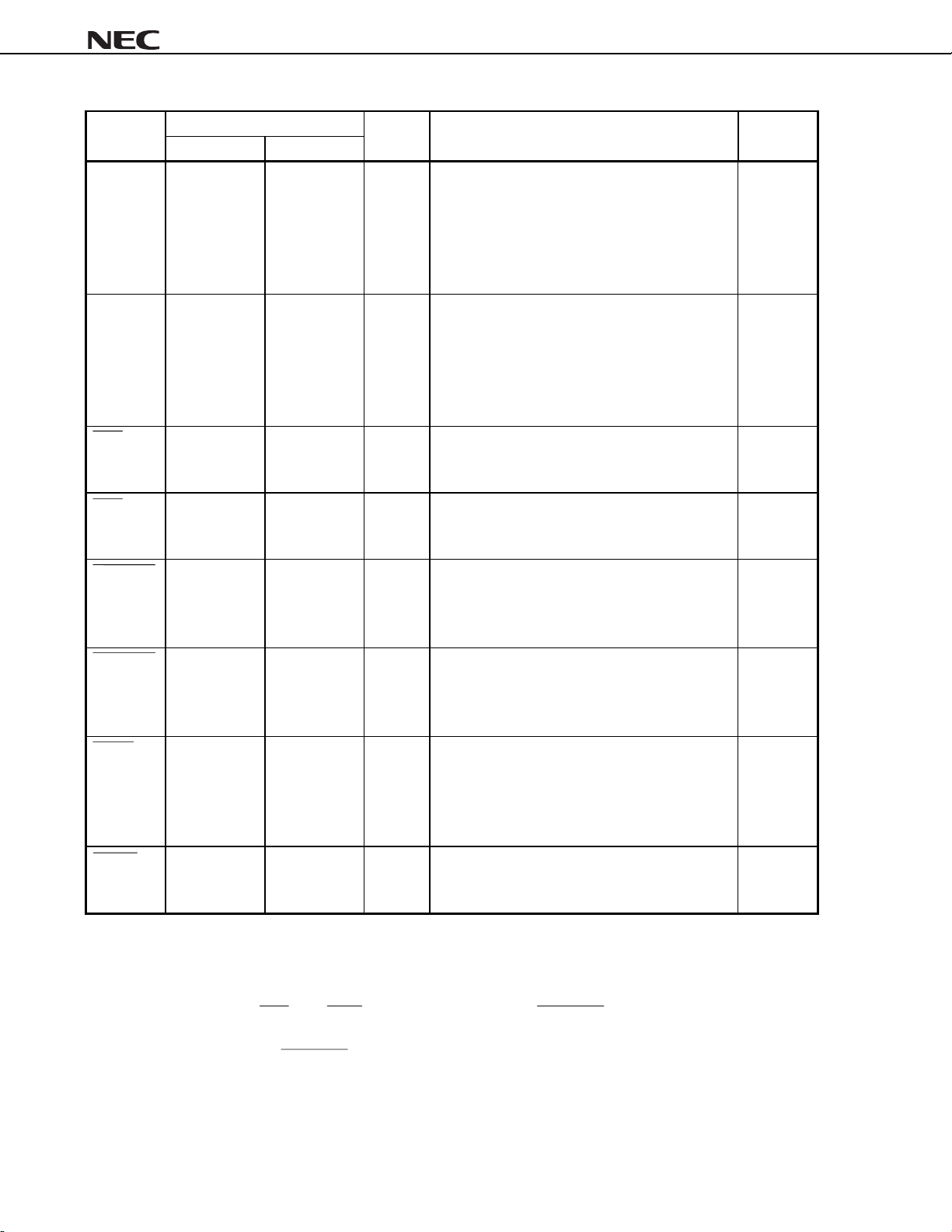

PIN CONFIGURATIONS

161-pin plastic fine pitch BGA (10 x 10)

•

µµµµ

PD77210F1-DA2

•

µµµµ

PD77213F1-xxx-DA2

(Bottom View) (Top View)

14

13

12

11

10

9

8

7

6

5

4

3

2

1

µµµµ

PD77210, 77213

MLK KLMPN PN

JHGFEDCBA ABCDEFGHJ

Index mark

6

Data Sheet U15203EJ3V0DS

µµµµ

PD77210, 77213

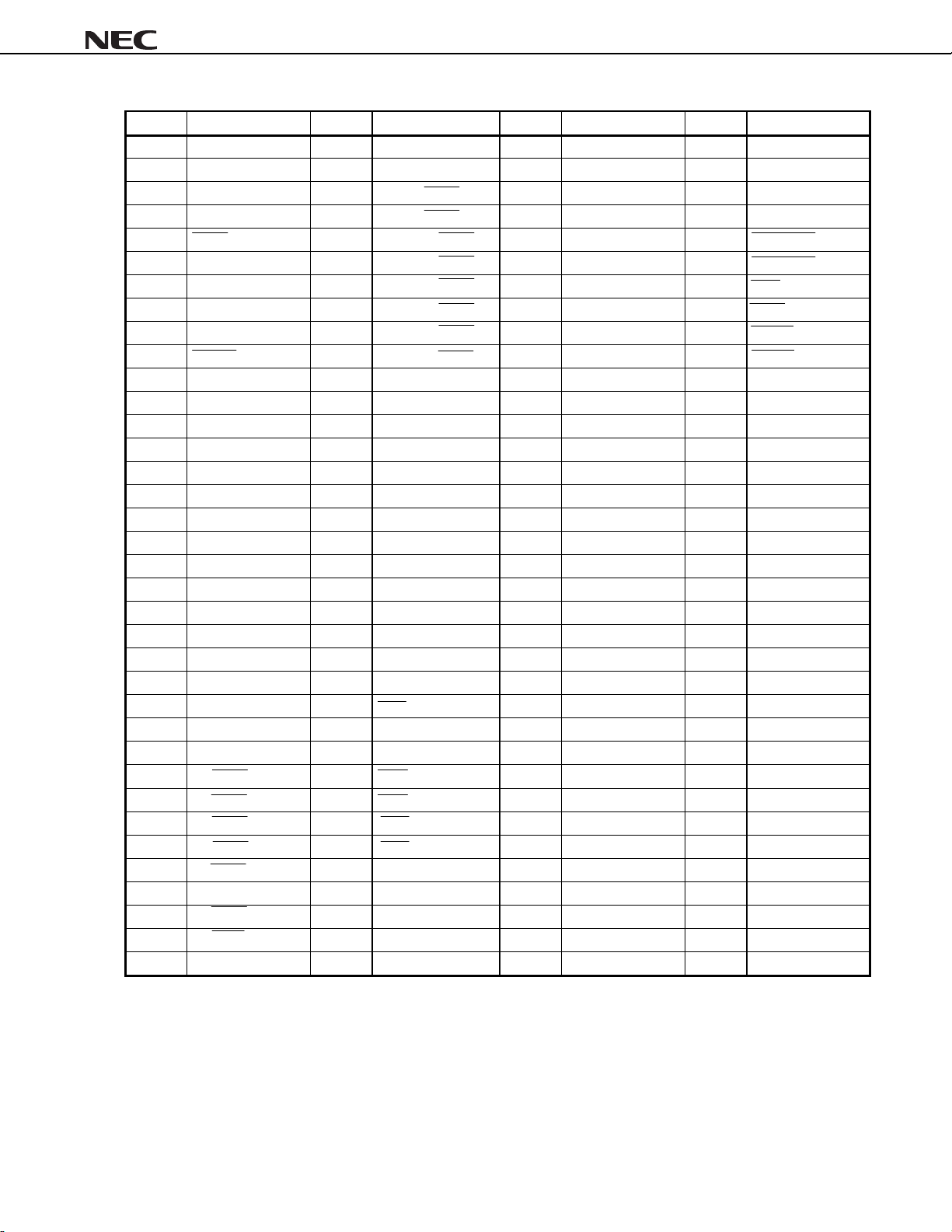

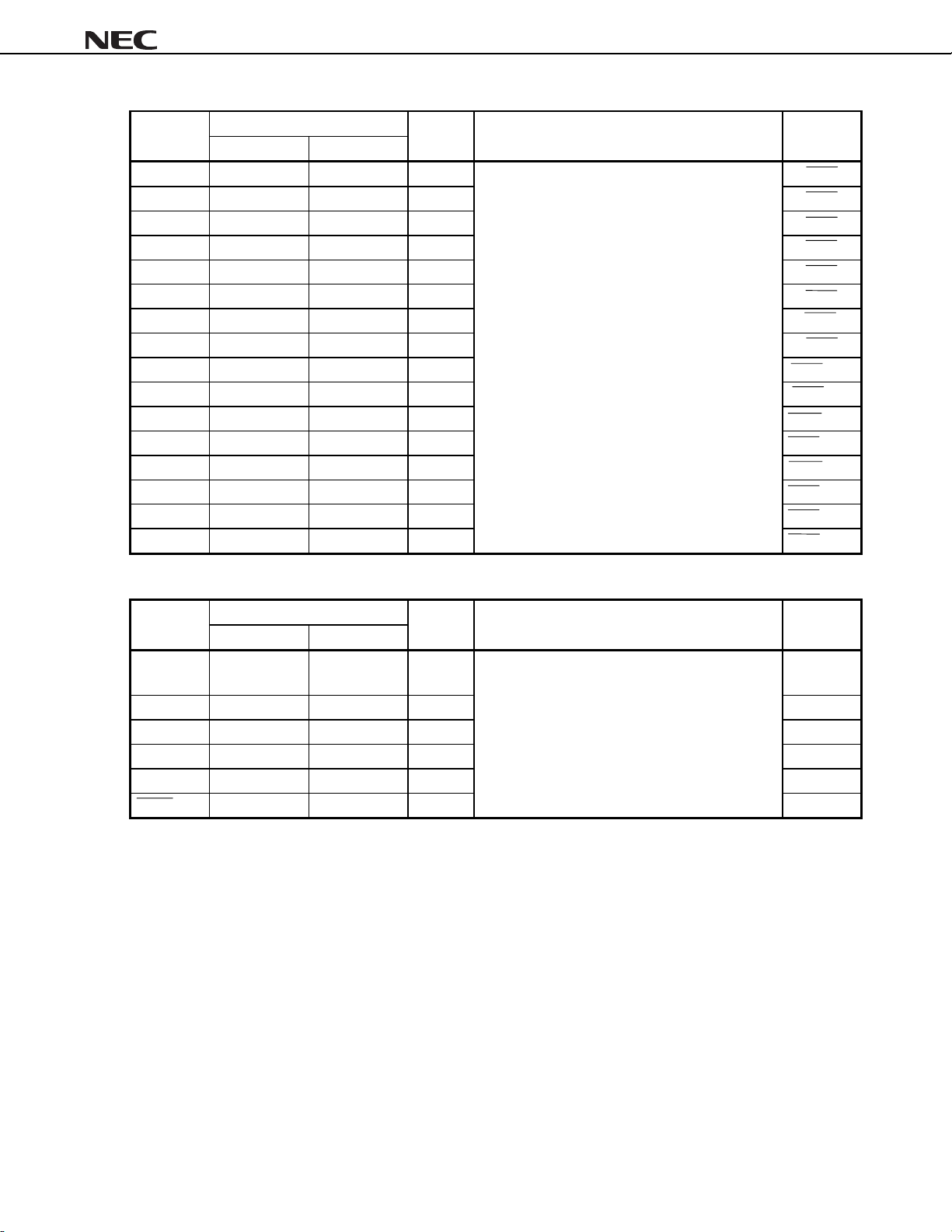

Pin No. Pin Name Pin No. Pin Name Pin No. Pin Name Pin No. Pin Name

A1 NC C14 EV

DD

H2 HD7 M5 TSORQ

A2 NC D1 P10/HD10/INT22 H3 HD6 M6 MA0

A3 P5/INT11 D2 P11/HD11/INT32 H4 GND M7 MA4

A4 P2/INT20 D3 P12/HD12/INT03 H11 MD5 M8 MA5

A5 GND D4 GND H12 MD4 M9 MA10

A6 EV

A7 IV

A8 IV

DD

DD

DD

D5 GND H13 MD1 M10 MA12

D6 P1/INT10 H14 MD3 M11 MA15/Reserved

D7 GND J1 EV

DD

M12 MA19/SDCLK

A9 PLL0 D8 GND J2 HCS M13 MA18/SDCR

A10 STOPS D9 GND J3 HA1 M14 EV

A11 EV

DD

D10 GND J4 HWR N1 NC

DD

A12 TRST D11 TMS J11 GND N2 NC

A13 NC D12 TICE J12 MD0 N3 ASIEN/MCLK

A14 NC D13 MD12 J13 MBSTB N4 TSCK

B1 NC D14 MD15 J14 IV

DD

N5 TSIAK

B2 NC E1 P14/HD14/INT23 K1 HA0 N6 MA1

B3 P7/INT31 E2 P15/HD15/INT33 K2 HRD N7 MA2

B4 P6/INT21 E3 P13/HD13/INT13 K3 TIMOUT N8 MA7

B5 P3/INT30 E4 GND K4 ASO N9 MA9

B6 CLKOUT E5 NC K11 GND N10 MA11

B7 IV

DD

E11 GND K12 MWR N11 MA16/Reserved

B8 PLL3 E12 MD14 K13 MWAIT N12 MA17/Reserved

B9 PLL1 E13 MD9 K14 EV

DD

N13 NC

B10 CSTOP E14 MD11 L1 HWE N14 NC

B11 I.C. F1 EV

DD

L2 HRE P1 NC

B12 TCK F2 HD1 L3 GND P2 NC

B13 NC F3 HD2 L4 GND P3 ASI

B14 NC F4 HD0 L5 TSIEN P4 TSO

C1 EV

DD

C2 P8/HD8/INT02 F12 MD13 L7 GND P6 EV

C3 P9/HD9/INT12 F13 MD7 L8 MA8 P7 IV

C4 P4/INT01 F14 EV

C5 P0/INT00 G1 HD3 L10 MA14/SDDAT0

C6 CLKIN G2 HD5 L11 GND P10 EV

F11 MD10 L6 GND P5 TSI

DD

L9 GND P8 MA3

Note

P9 MA6

DD

DD

DD

C7 PLL2 G3 HD4 L12 MHOLDRQ P11 MA13/SDMON

C8 HALTS G4 GND L13 MRD P12 EV

DD

C9 RESET G11 GND L14 MHOLDAK P13 NC

C10 I.C. G12 MD8 M1 EV

DD

P14 NC

C11 TDI G13 MD2 M2 ASCK/BCLK

C12 TDO G14 MD6 M3 ASOEN/LRCLK

C13 GND H1 IV

Note MA13 to MA19 pins of the

PD77213 are alternate function pins.

µ

DD

M4 TSOEN

Note

Note

Note

Note

Note

Note

Data Sheet U15203EJ3V0DS

7

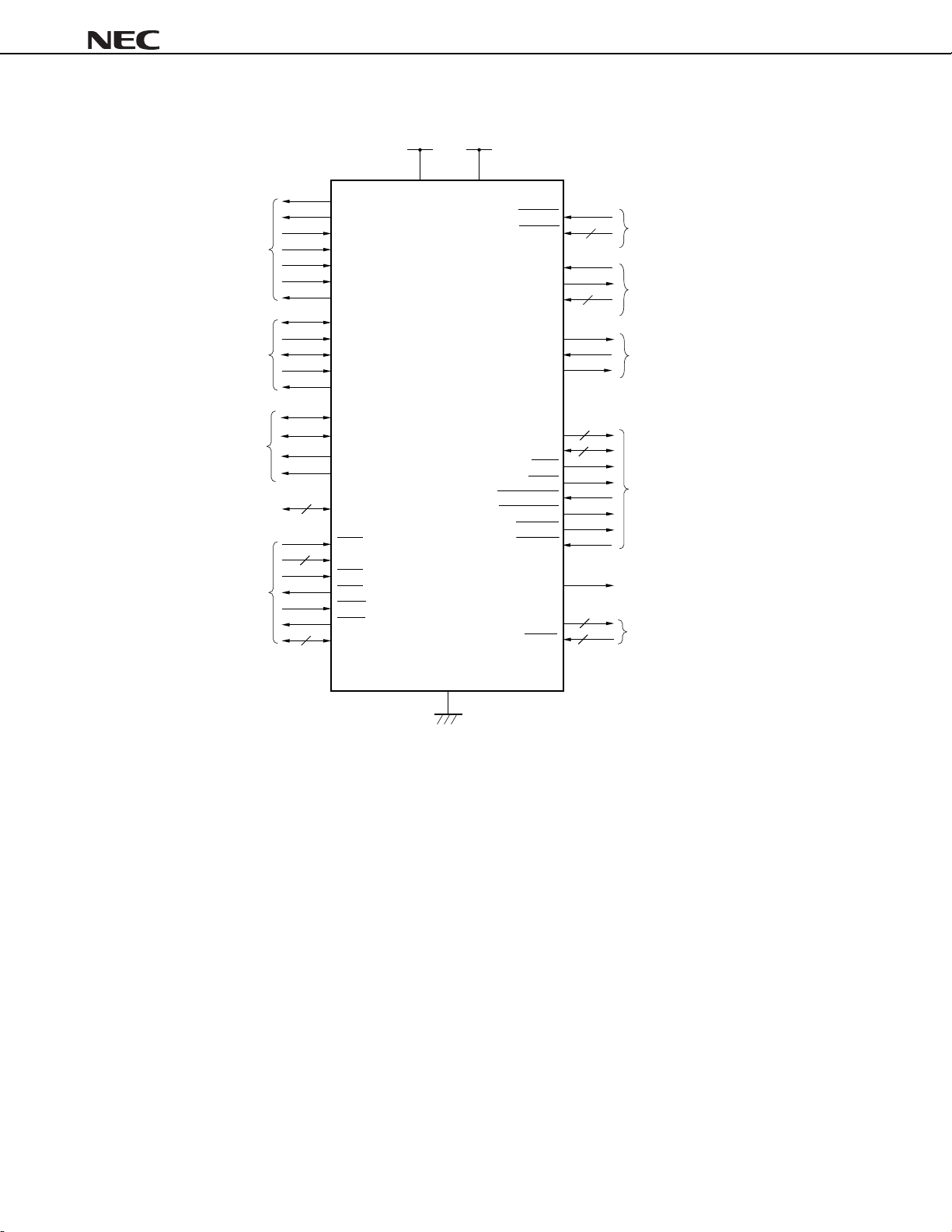

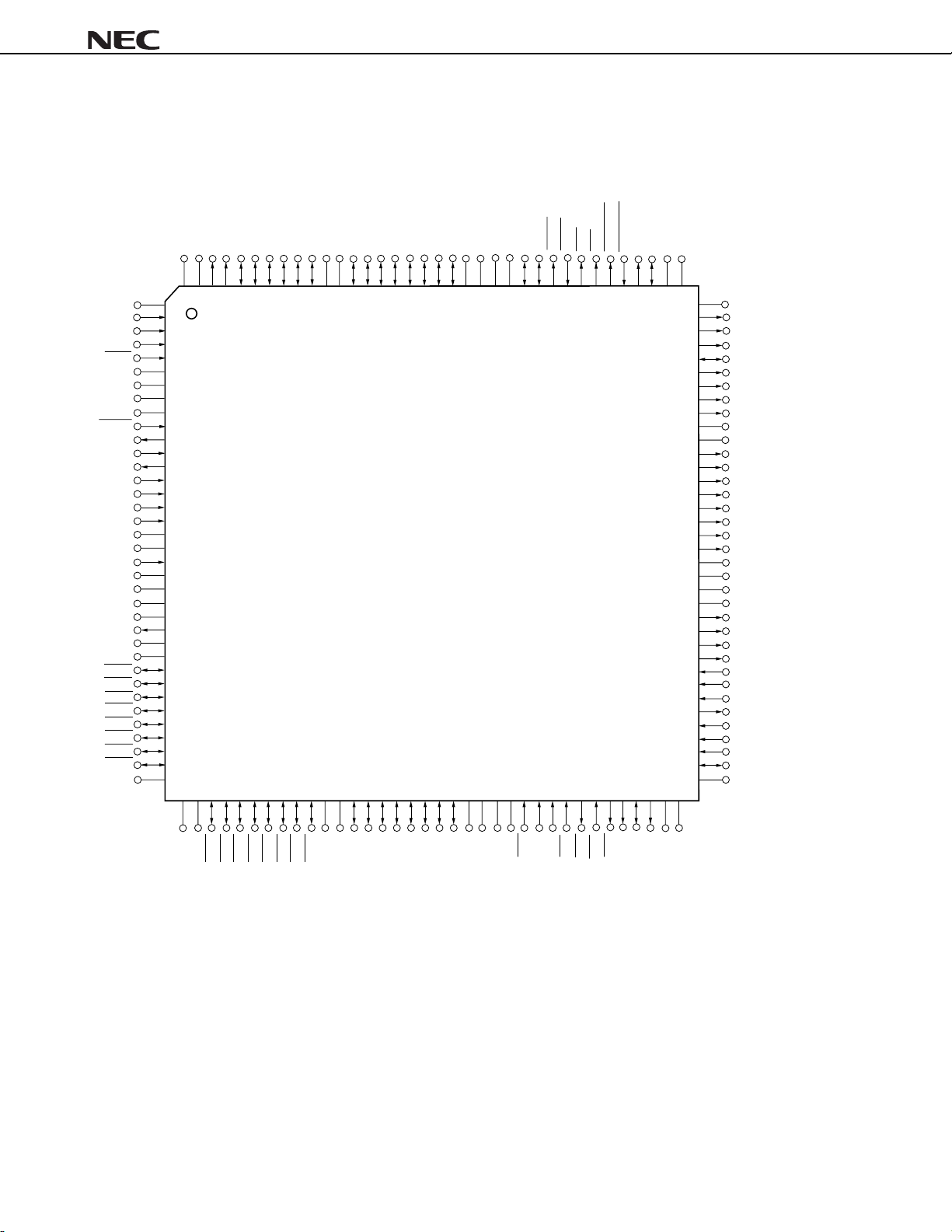

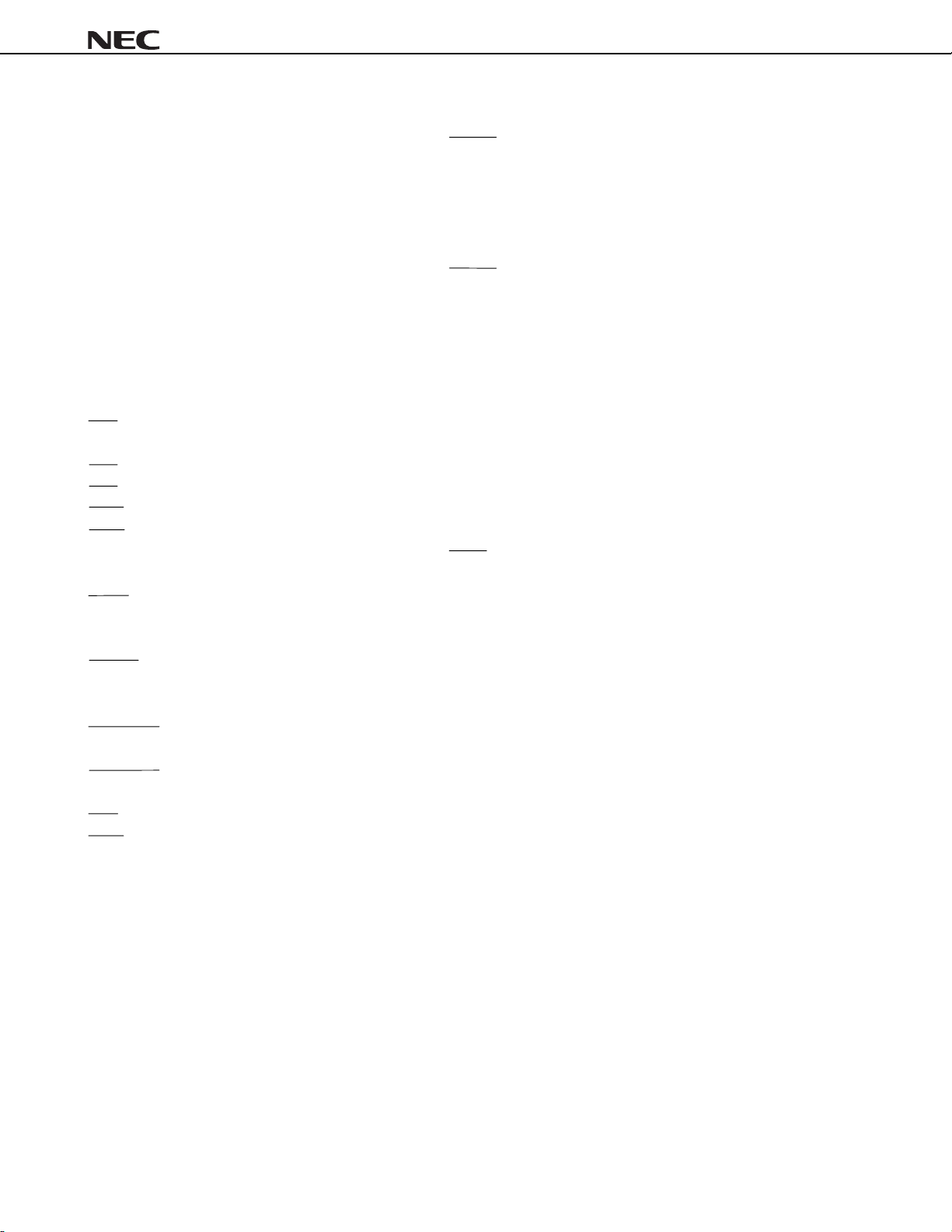

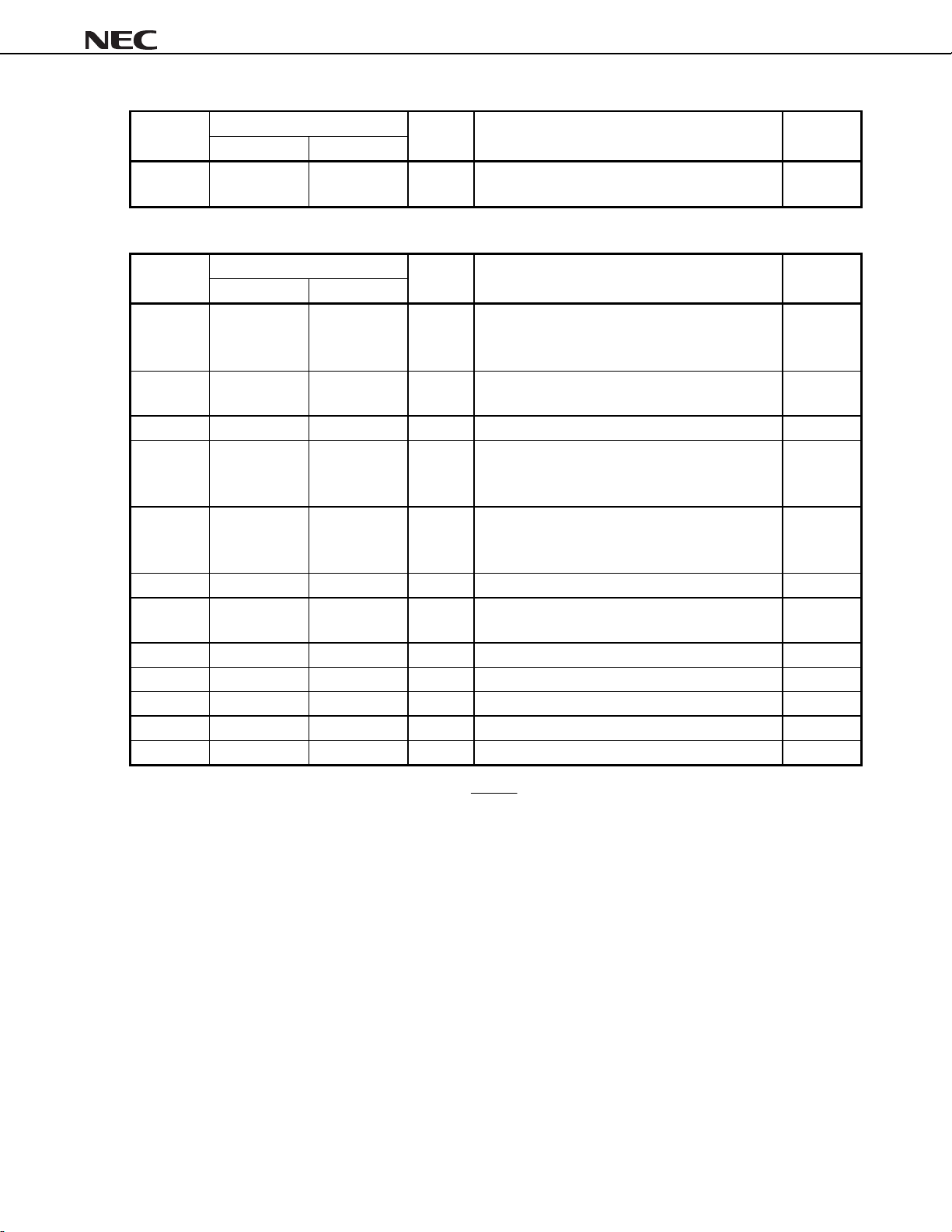

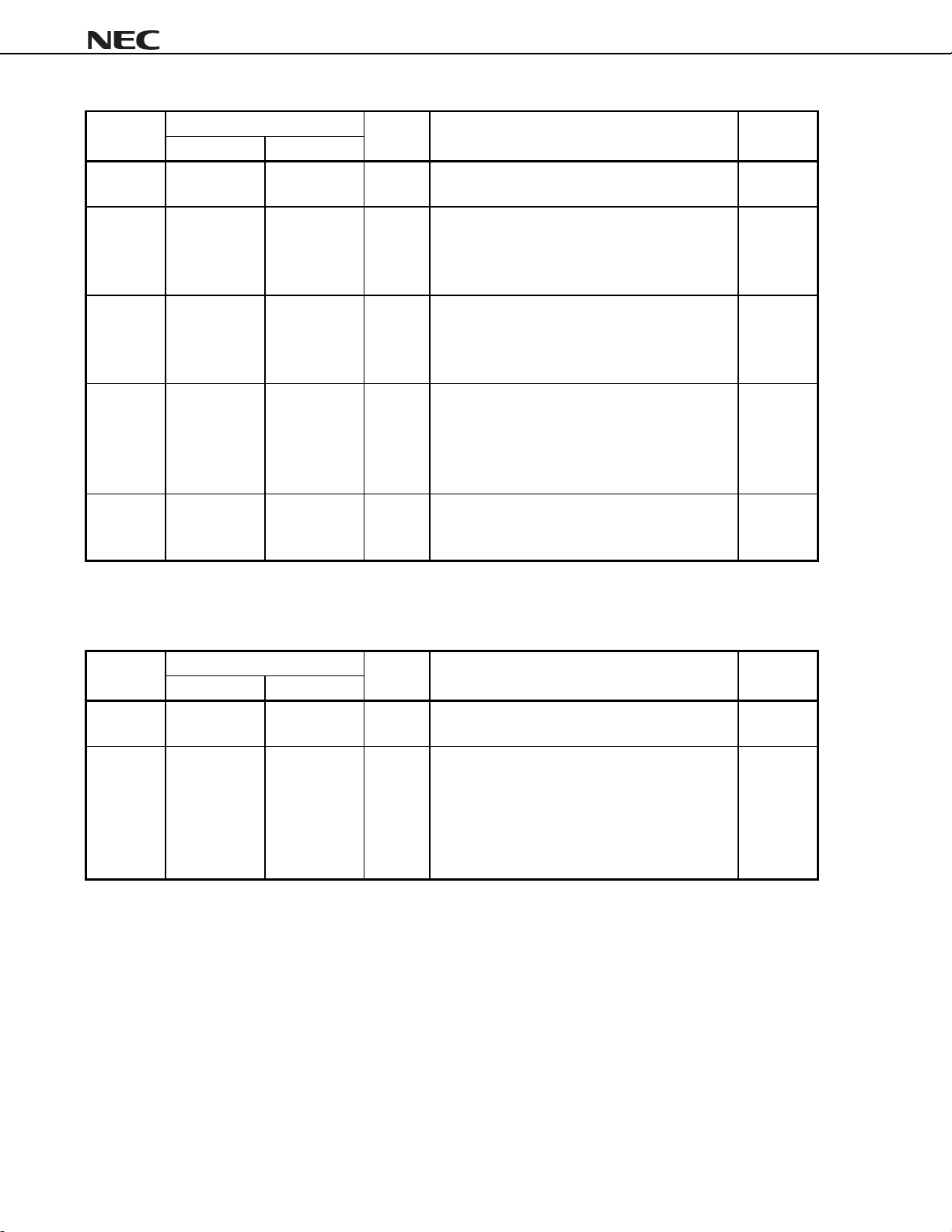

144-pin plastic LQFP (fine pitch) (20 x 20) (Top View)

•

µµµµ

PD77210GJ-8EN

•

µµµµ

PD77213GJ-xxx-8EN

Note

µµµµ

PD77210, 77213

Note

GND

TCK

TDI

TMS

TRST

I.C.

I.C.

EV

GND

RESET

STOPS

CSTOP

HALTS

PLL0

PLL1

PLL2

PLL3

IV

GND

CLKIN

IV

GND

IV

GND

CLKOUT

EV

GND

P0/INT00

P1/INT10

P2/INT20

P3/INT30

P4/INT01

P5/INT11

P6/INT21

P7/INT31

GND

DD

TDO

TICE

GND

EV

144 120121122123124125126127128129130131

1

2

3

4

5

6

DD

DD

DD

DD

DD

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

MD15

MD14

MD12

MD13

MD11

MD10

134135136137138139140141142143

GND

DD

EV

MD4

MD5

MD2

MD3

MD6

MD7

MD8

MD9

132133

GND

DD

DD

GND

EV

MBSTB

MWAIT

MD0

MD1

IV

5958575655545352515049484746454443424140393837

6160

MWR

MRD

MHOLDAK

676665646362

MA18/SDCR

MA19/SDCLK

MHOLDRQ

71706968

DD

EV

GND

109110111112113114115116117118119

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

EV

DD

MA17/Reserved

MA16/Reserved

MA15/Reserved

MA14/SDDAT0

MA13/SDMON

MA12

MA11

MA10

GND

EV

DD

MA9

MA8

MA7

MA6

MA5

MA4

MA3

MA2

GND

IV

DD

GND

EV

DD

MA1

MA0

TSIAK

TSORQ

TSI

TSIEN

TSCK

TSO

TSOEN

ASI

ASIEN/MCLK

ASCK/BCLK

GND

Note

Note

Note

Note

Note

DD

GND

EV

P8/HD8/INT02

P9/HD9/INT12

P10/HD10/INT22

P11/HD11/INT32

Note MA13 to MA19 pins of the

8

DD

EV

P12/HD12/INT03

P13/HD13/INT13

P14/HD14/INT23

P15/HD15/INT33

PD77213 are alternate function pins.

µ

HD5

HD4

HD3

HD2

HD1

HD0

GND

Data Sheet U15203EJ3V0DS

HD6

HD7

DD

DD

IV

GND

EV

GND

HCS

HA0

HA1

HRD

HRE

HWR

HWE

DD

ASO

EV

TIMOUT

ASOEN/LRCLK

GND

µµµµ

PD77210, 77213

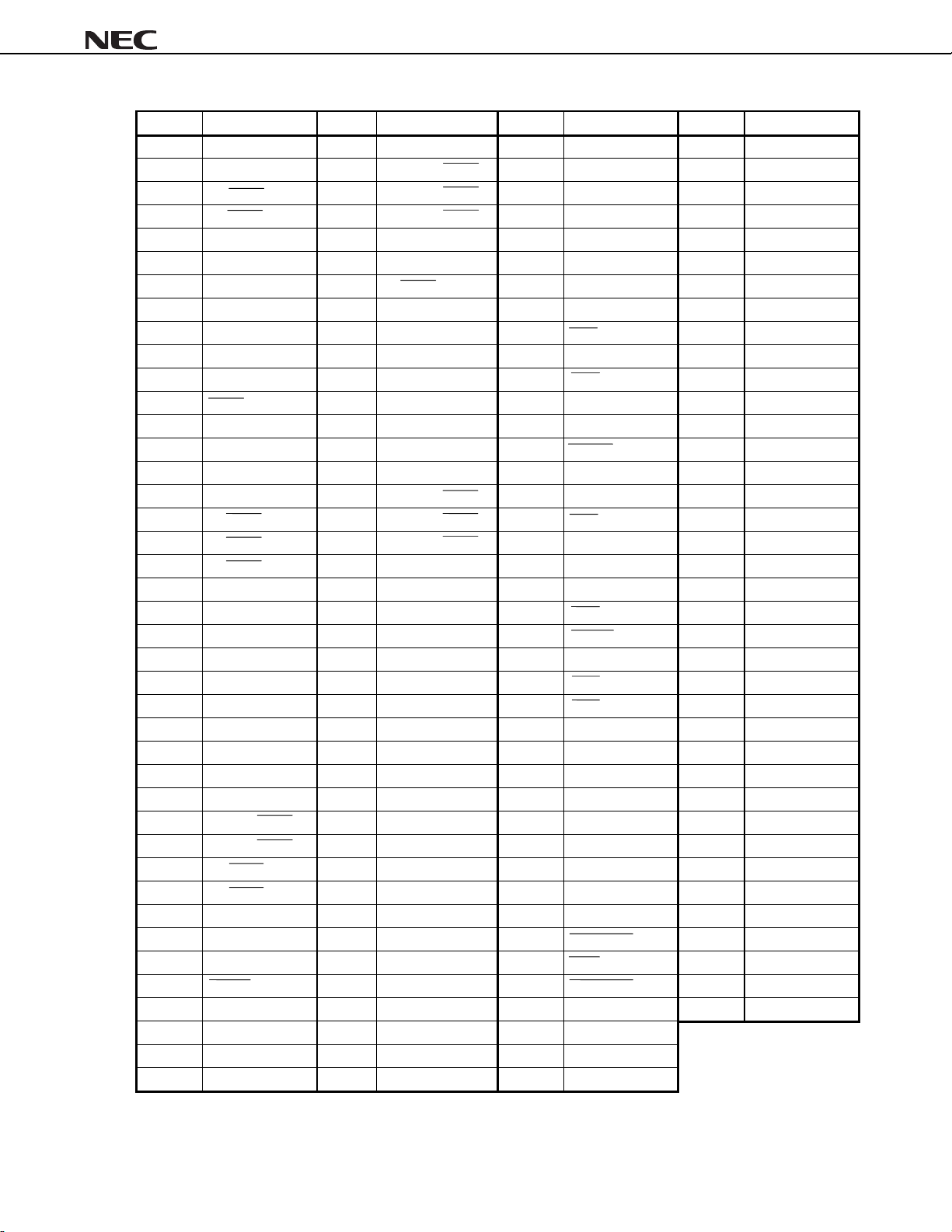

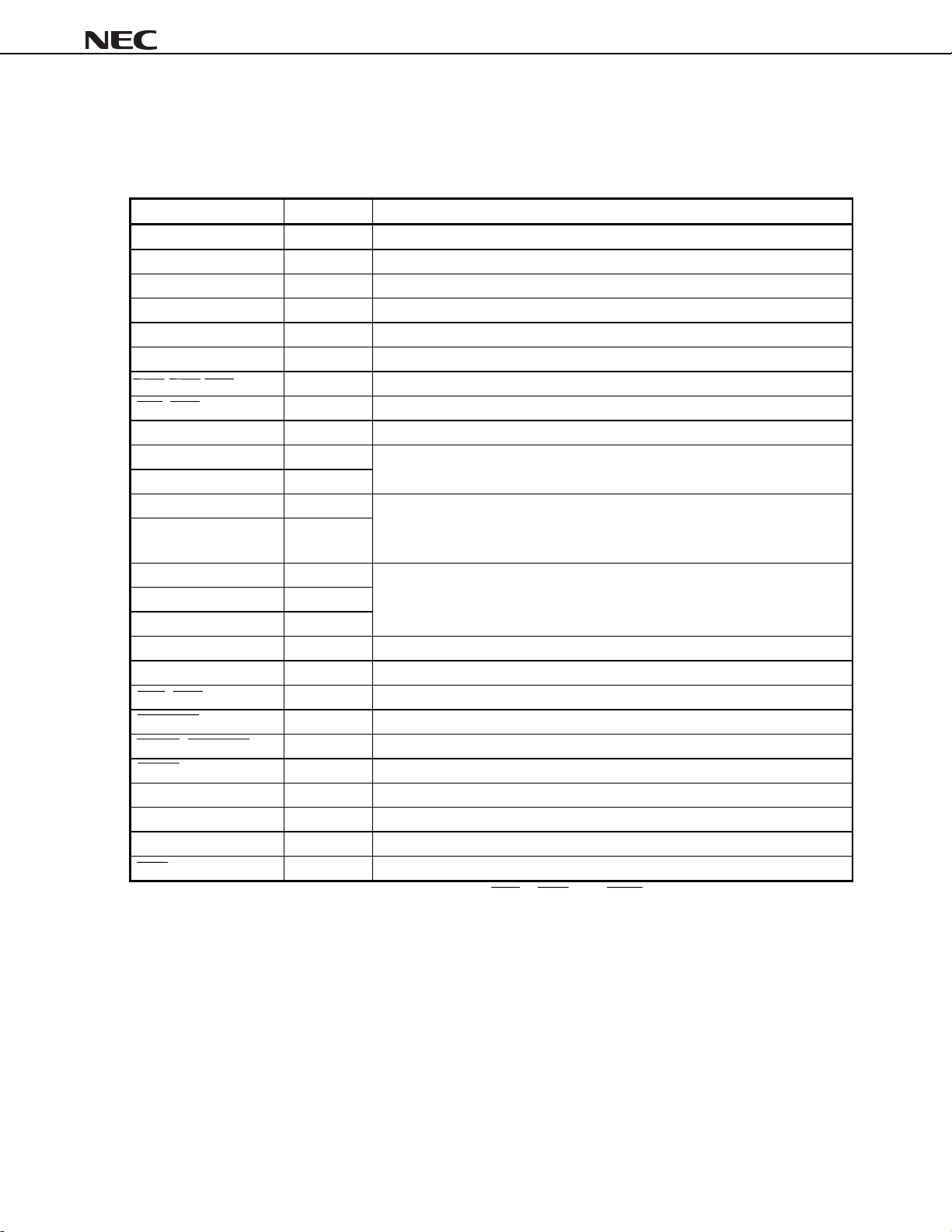

Pin No

.

1GND 37EV

2 TCK 38 GND 74 ASCK/BCLK 110 EV

Pin Name Pin No

.

Pin Name Pin No

DD

.

Pin Name Pin No

.

73 GND 109 GND

Pin Name

DD

3 TDI 39 P8/HD8/INT02 75 ASIEN/MCLK 111 MA18/SDCR

4 TMS 40 P9/HD9/INT12 76 ASI 112 MA19/SDCLK

5 TRST 41 P10/HD10/INT22 77 TSOEN 113 MHOLDRQ

6 I.C. 42 P11/HD11/INT32 78 TSO 114 MHOLDAK

7 I.C. 43 P12/HD12/INT03 79 TSCK 115 MRD

8EV

DD

44 P13/HD13/INT13 80 TSIEN 116 MWR

9 GND 45 P14/HD14/INT23 81 TSI 117 MWAIT

10 RESET 46 P15/HD15/INT33 82 TSORQ 118 MBSTB

11 STOPS 47 EV

DD

83 TSIAK 119 MD0

12 CSTOP 48 GND 84 MA0 120 MD1

13 HALTS 49 HD0 85 MA1 121 EV

14 PLL0 50 HD1 86 EV

DD

122 GND

15 PLL1 51 HD2 87 GND 123 IV

16 PLL2 52 HD3 88 IV

DD

124 GND

DD

DD

17 PLL3 53 HD4 89 GND 125 MD2

18 IV

DD

54 HD5 90 MA2 126 MD3

19 GND 55 HD6 91 MA3 127 MD4

20 CLKIN 56 HD7 92 MA4 128 MD5

21 IV

DD

57 IV

DD

93 MA5 129 MD6

22 GND 58 GND 94 MA6 130 MD7

23 IV

DD

59 EV

DD

95 MA7 131 MD8

24 GND 60 GND 96 MA8 132 MD9

25 CLKOUT 61 HCS 97 MA9 133 EV

26 EV

DD

62 HA0 98 EV

DD

134 GND

DD

27 GND 63 HA1 99 GND 135 MD10

28 P0/INT00 64 HRD 100 MA10 136 MD11

29 P1/INT10 65 HRE 101 MA11 137 MD12

30 P2/INT20 66 HWR 102 MA12 138 MD13

31 P3/INT30 67 HWE 103 MA13/SDMON

32 P4/INT01 68 TIMOUT 104 MA14/SDDAT0

33 P5/INT11 69 ASOEN/LRCLK 105 MA15/Reserved

34 P6/INT21 70 ASO 106 MA16/Reserved

35 P7/INT31 71 EV

DD

36 GND 72 GND 108 EV

Note MA13 to MA19 pins of the

PD77213 are alternate function pins.

µ

107 MA17/Reserved

DD

Note

Note

Note

Note

Note

139 MD14

140 MD15

141 TDO

142 TICE

143 GND

144 EV

DD

Note

Note

Data Sheet U15203EJ3V0DS

9

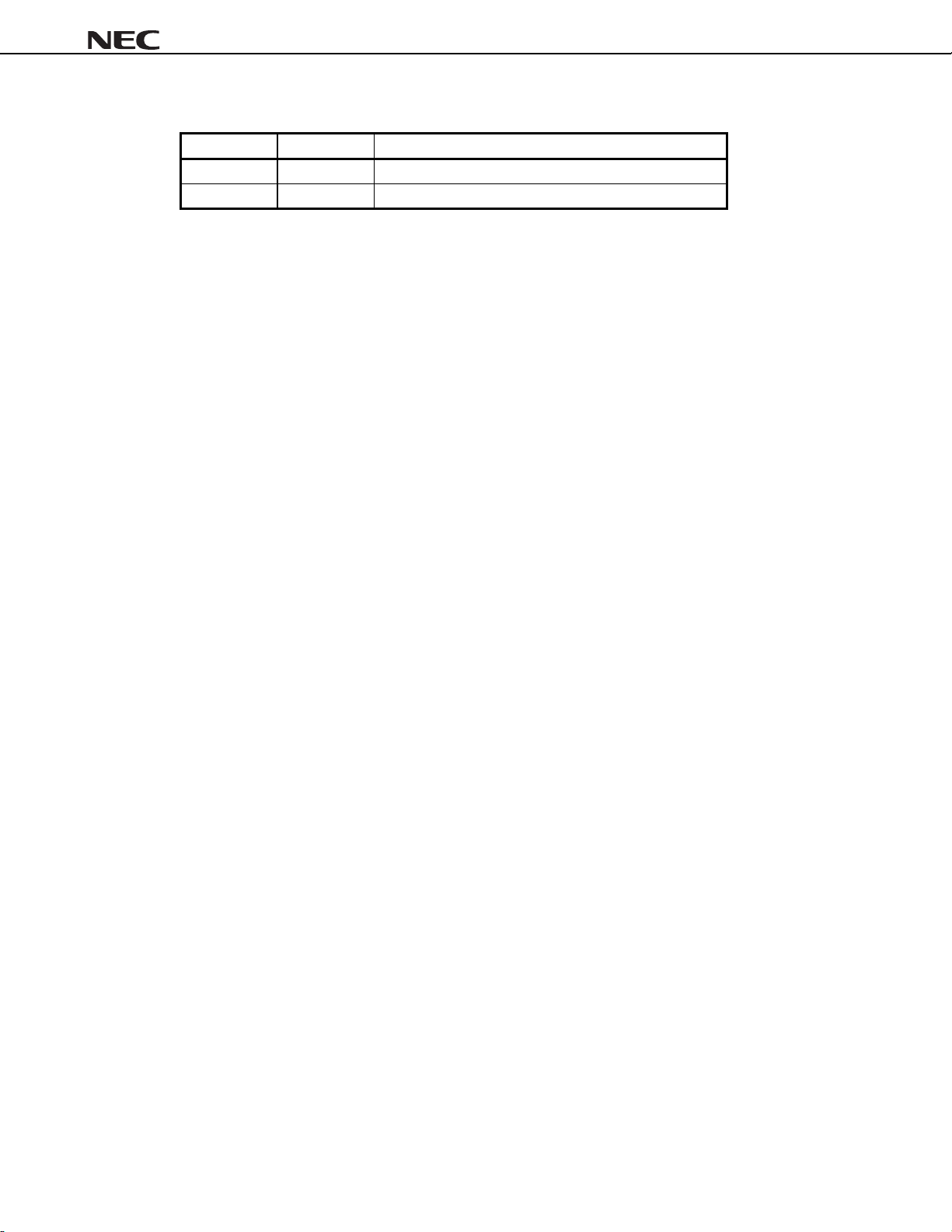

Pin Name

µµµµ

PD77210, 77213

ASCK :Audio Serial Clock Input/Output

ASI :Audio Serial Data Input

ASIEN :Audio Serial Input Enable

ASO :Audio Serial Data Output

ASOEN :Audio Serial Output Enable

BCLK :Bit Clock Input/Output

CLKIN :Clock Input

CLKOUT :Clock Output

CSTOP :Clear Stop Mode

EV

DD

GND :Ground

HALTS :Halt Status Signal Output

HD0 to HD15 :Host Data Bus

HCS :Host Chip Select

HA0, HA1 :Host Data Access

HRD :Host Read

HRE :Host Read Enable

HWE :Host Write Enable

HWR :Host Write

I.C. :Internal Connection

IV

DD

INTmn :Interrupt (m,n=0 to 3)

LRCLK :Left Right Clock Input/Output

MA0 to MA19 :External Data Memory Address Bus

MBSTB :External Data Memory Bus Strobe

MCLK :Master Clock Input

MD0 to MD15 :External Data Memory Bus

MHOLDAK :External Data Memory Bus Hold

MHOLDRQ :External Data Memory Bus Hold

MRD :External Data Memory Read Output

MWR :External Data Memory Write Output

:Power Supply for I/O Pins

:Power Supply for DSP Core

Acknowledge

Request

MWAIT :External Data Memory Access Wait

Input

NC :Non-Connection

P0 to P15 :Port

PLL0-PLL3 :PLL Multiple Rate Set

Reserved :Reserved

RESET :Reset

SDCLK :SD Card Clock Output

SDCR :SD Card Command Output/Response

Input

SDDAT0 :SD Card Data Input/Output

SDMON :SD Card Access Monitor

STOPS :Stop Status Signal Output

TCK :Test Clock Input

TDI :Test Data Input

TDO :Test Data Output

TICE :Test In-Circuit Emulator

TIMOUT :Timer Time Out Monitor Output

TMS :Test Mode Select

TRST :Test Reset

TSCK :Time Division Multiplex Serial Clock

Input

TSI :Time Division Multiplex Serial Data Input

TSIAK :Time Division Multiplex Serial Input

Acknowledge

TSIEN :Time Division Multiplex Serial Input

Enable

TSO :Time Division Multiplex Serial Data

Output

TSOEN :Time Division Multiplex Serial Output

Enable

TSORQ :Time Division Multiplex Serial Output

Request

10

Data Sheet U15203EJ3V0DS

µµµµ

PD77210, 77213

CONTENTS

1. PIN FUNCTIONS....................................................................................................................................13

1.1 Description of Pin Functions ........................................................................................................................13

1.2 Connection of Unused Pins ..........................................................................................................................21

1.2.1 Connection of functional pins ..................................................................................................................21

1.2.2 Connection of non-functional pin.............................................................................................................22

2. FUNCTIONAL OUTLINE .......................................................................................................................23

2.1 Program Control Unit.....................................................................................................................................23

2.1.1 CPU control .............................................................................................................................................23

2.1.2 Interrupt control .......................................................................................................................................23

2.1.3 Loop control stack ...................................................................................................................................23

2.1.4 PC stack ..................................................................................................................................................23

2.1.5 Clock control............................................................................................................................................23

2.1.6 Instruction memory ..................................................................................................................................24

2.2 Operation Unit ................................................................................................................................................24

2.2.1 General-purpose registers (R0 to R7) .....................................................................................................24

2.2.2 Multiply accumulator (MAC) ....................................................................................................................24

2.2.3 Arithmetic logic unit (ALU) .......................................................................................................................24

2.2.4 Barrel shifter (BSFT)................................................................................................................................24

2.3 Data Memory Unit...........................................................................................................................................24

2.3.1 Data memory ...........................................................................................................................................24

2.3.2 Data addressing unit................................................................................................................................25

2.4 Peripheral Unit................................................................................................................................................25

2.4.1 Serial interface (SIO) ...............................................................................................................................25

2.4.2 Host interface (HIO).................................................................................................................................25

2.4.3 General-purpose I/O port (PIO) ...............................................................................................................26

2.4.4 External memory interface (MIO).............................................................................................................26

2.4.5 Timers (TIM1 and TIM2)..........................................................................................................................26

2.4.6 Interrupt controller (INTC)........................................................................................................................26

2.4.7 DMA controller (PMT)..............................................................................................................................26

2.4.8 SD card interface (SDCIF).......................................................................................................................26

2.4.9 Debug interface (IEIO).............................................................................................................................26

3. CLOCK GENERATOR...........................................................................................................................27

4. RESET FUNCTION ................................................................................................................................28

4.1 Hardware Reset ..............................................................................................................................................28

5. FUNCTION OF BOOT-UP ROM ...........................................................................................................28

5.1 Boot at Reset ..................................................................................................................................................28

5.1.1 Memory boot............................................................................................................................................28

5.1.2 Host boot .................................................................................................................................................29

5.1.3 Serial boot ...............................................................................................................................................29

5.2 Reboot.............................................................................................................................................................29

5.2.1 Memory reboot ........................................................................................................................................29

Data Sheet U15203EJ3V0DS

11

µµµµ

PD77210, 77213

5.2.2 Host reboot ............................................................................................................................................. 30

5.2.3 Serial reboot ........................................................................................................................................... 30

6. STANDBY MODE.................................................................................................................................. 31

6.1 Halt Mode ....................................................................................................................................................... 31

6.2 Stop Mode ...................................................................................................................................................... 31

7. MEMORY MAP...................................................................................................................................... 32

7.1 Instruction Memory ....................................................................................................................................... 32

7.1.1 Instruction memory map ......................................................................................................................... 32

7.1.2 Interrupt vector table............................................................................................................................... 33

7.2 Data Memory.................................................................................................................................................. 34

7.2.1 Data memory map .................................................................................................................................. 34

7.2.2 Internal peripherals ................................................................................................................................. 35

8. GENERAL-PURPOSE PORT AND INTERRUPT ............................................................................... 38

8.1 General-purpose Port Pins ........................................................................................................................... 38

8.2 Interrupt Pin ................................................................................................................................................... 38

9. INSTRUCTION ....................................................................................................................................... 39

9.1 Outline of Instruction .................................................................................................................................... 39

9.2 Instruction Set and Its Operation................................................................................................................. 40

10. ELECTRICAL SPECIFICATIONS....................................................................................................... 46

11. PACKAGE DRAWINGS...................................................................................................................... 69

12. RECOMMENDED SOLDERING CONDITIONS................................................................................. 71

12

Data Sheet U15203EJ3V0DS

µµµµ

PD77210, 77213

1. PIN FUNCTIONS

Because the pin numbers differ depending on the package, see the column for the package to be used in the

tables below.

1.1 Description of Pin Functions

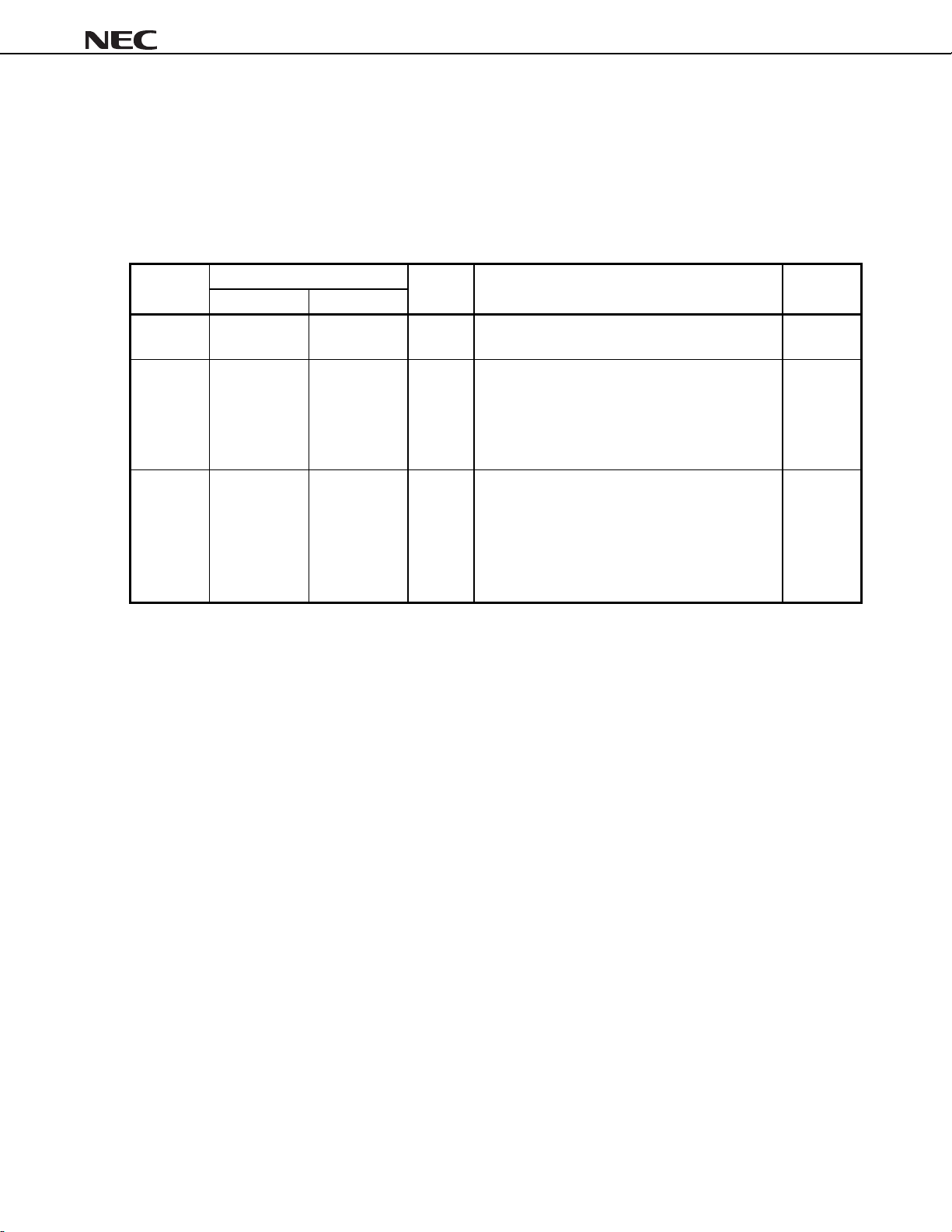

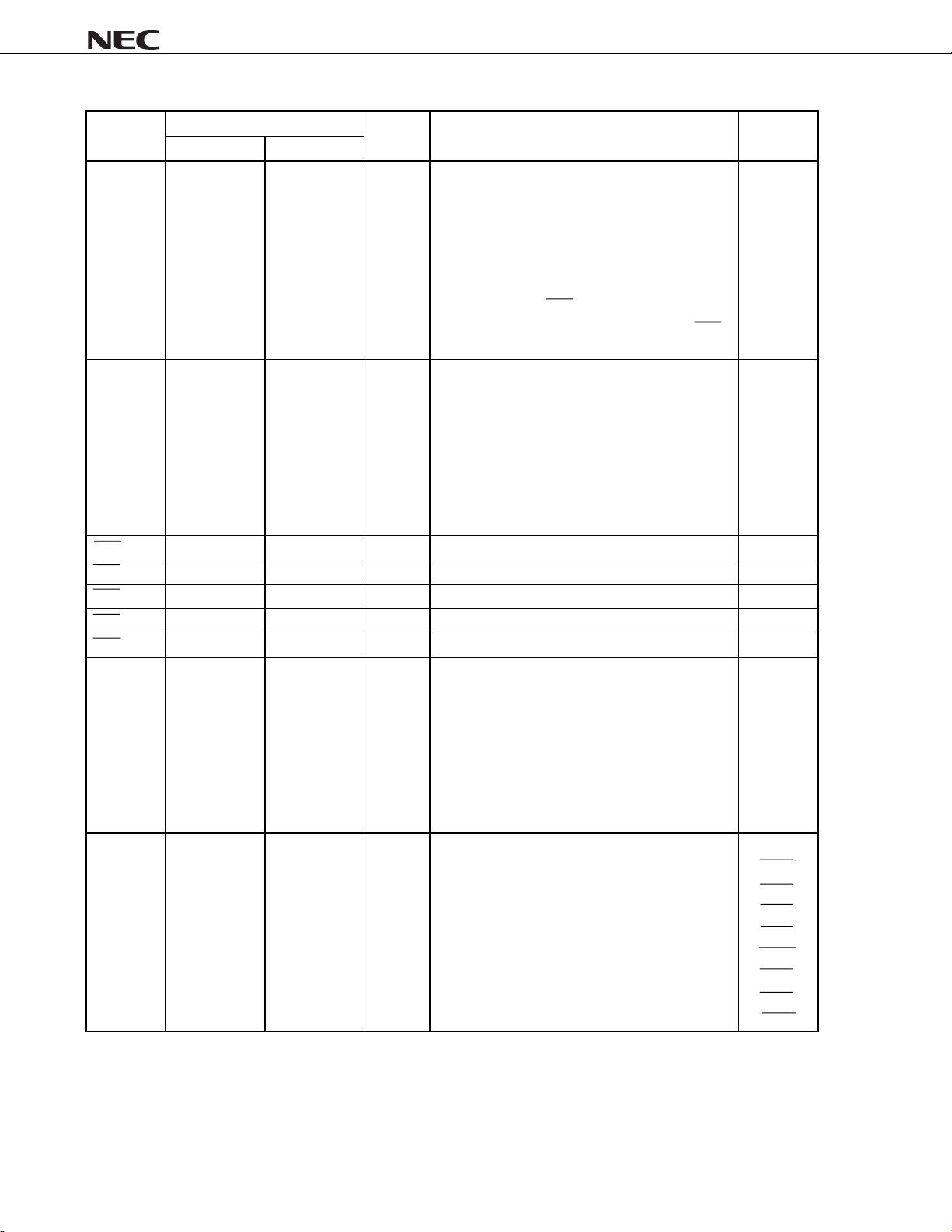

•••• Power supply pins

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

IV

DD

EV

DD

GND 1,9,19,22,24,

18,21,23,57,

88,123

8,26,37,47,59,

71,86,98,108,

110,121,133,

144

27,36,38,48,

58,60,72,73,

87,89,99,109,

122,124,134,

143

A7,A8,B7,H1,

J14, P7

A6,A11,C1,

C14,F1,F14,

J1,K14,M1,

M14,P6,P10,

P12

A5,C13,D4,D5,

D7,D8,D9,D10,

E4,E11,G4,

G11,H4,J11,

K11,L3,L4,L6,

L7,L9,L11

Remark Please supply voltage to the IV

I/O Function Alternate

− Power supply for DSP core (+1.5 V)

These pins supply power to the DSP core.

− Power supply for I/O (+3.3 V)

These pins supply power to the external interface

pins.

− Ground

These are ground pins.

DD

and EVDD pins simultaneously.

Pin

−

−

−

Data Sheet U15203EJ3V0DS

13

•••• Clock and system control pins

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

CLKIN 20 C6 Input Clock input

CLKOUT 25 B6 Output Internal system clock output

PLL0 to

PLL3

HALTS 13 C8 Output HALT mode status output

STOPS 11 A10 Output Stop mode status output

CSTOP 12 B10 Input Stop mode clear signal input

14 to 17 A9,B9,C7,B8 Input PLL multiple setting input

I/O Function Alternate

This pin inputs a clock to operate the

Family.

This pin outputs the internal system clock that is the

clock input from CLKIN and which is multiplied by the

PLL circuit.

These pins set a clock multiple of the PLL circuit.

• PLL3: PLL2: PLL1: PLL0

0000: x10 0001: x12 0010: x14

0011: x16 0100: x18 0101: x20

0110: x22 0111: x24 1000: x26

1001: x28 1010: x30 1011: x32

1100: x40 1101: x48 1110: x56

1111: x64

This pin is asserted active in halt mode and stop

mode.

This pin is asserted active in stop mode.

Stop mode is cleared when this pin is asserted

active.

µµµµ

PD77210, 77213

PD77210

µ

Pin

−

−

−

−

−

−

14

Data Sheet U15203EJ3V0DS

µµµµ

PD77210, 77213

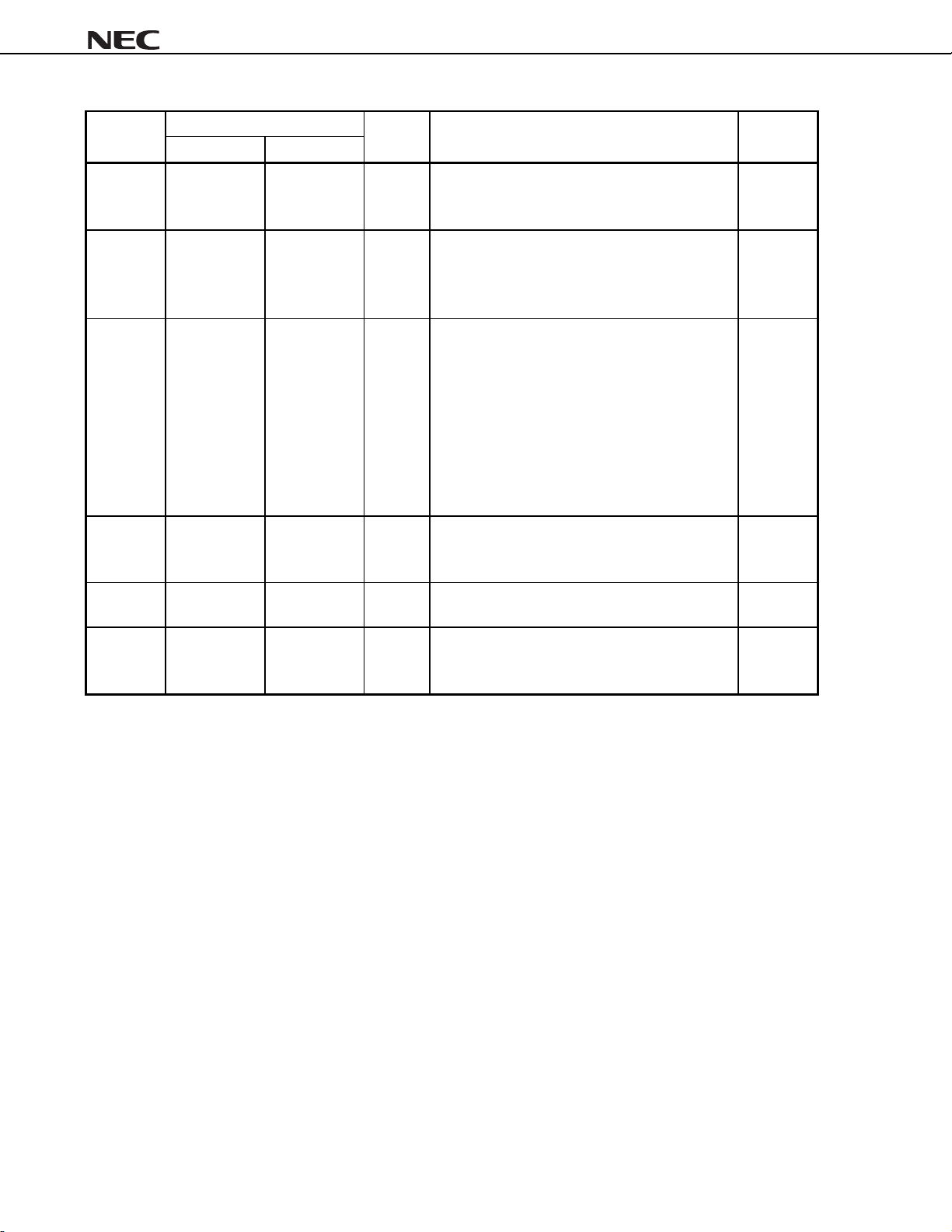

•••• Reset and interrupt pins

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

RESET 10 C9 Input Internal system reset signal input

INT00 28 C5 Input P0

INT01 32 C4 Input P4

INT02 39 C2 Input P8/HD8

INT03 43 D3 Input P12/HD12

INT10 29 D6 Input P1

INT11 33 A3 Input P5

INT12 40 C3 Input P9/HD9

INT13 44 E3 Input P13/HD13

INT20 30 A4 Input P2

INT21 34 B4 Input P6

INT22 41 D1 Input P10/HD10

INT23 45 E1 Input P14/HD14

INT30 31 B5 Input P3

INT31 35 B3 Input P7

INT32 42 D2 Input P11/HD11

INT33 46 E2 Input

I/O Function Alternate

Pin

−

This pin initializes the

Maskable external interrupt input

These pins input external interrupts.

PD77210 Family.

µ

P15/HD15

Data Sheet U15203EJ3V0DS

15

•••• External data memory interface

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

MA0 to

MA19

MD0 to

MD15

MWR 116 K12 Output

MRD 115 L13 Output

MHOLDAK 114 L14 Output Hold acknowledge signal

MHOLDRQ 113 L12 Input Hold request signal

MWAIT 117 K13 Input Wait signal input

MBSTB 118 J13 Output Bus strobe signal

Note

84, 85,

90 to 97,

100 to 107,

111, 112

119,120,

125 to 132,

135 to 140

M6,N6,N7,P8,

M7,M8,P9,N8,

L8,N9,M9,N10,

M10,P11,L10,

M11,N11,N12,

M13,M12

J12,H13,G13,

H14,H12,H11,

G14,F13,G12,

E13,F11,E14,

D13,F12,E12,

D14

I/O Function Alternate

Output

(3S)

I/O

(3S)

(3S)

(3S)

Address bus of external data memory

These pins output an address when the external data

memory is accessed.

16-bit data bus

These pins input/output data when the external data

memory is accessed.

Write output

This pin outputs a write strobe signal for the external

data memory.

Read output

This pin outputs a read strobe signal for the external

data memory.

This pin goes low when the external device is

granted use of the external data memory bus of the

PD77210 Family.

µ

The external device inputs a low level to this pin

when it uses the external data memory bus of the

PD77210 Family.

µ

This pin inserts wait cycles when the

Family accesses the external data memory.

• 0: Inserts wait cycles.

• 1: Does not insert wait cycles.

This pin goes low while the

the external data memory bus.

Note MA13 to MA19 pins of the µPD77213 are alternate function pins.

µµµµ

PD77210, 77213

PD77210

µ

PD77210 Family uses

µ

Pin

SDCLK,

SDCR,

SDDAT0,

SDMON

−

−

−

−

−

−

−

Remark Those pins marked “3S” in the above table enter the high-impedance state under the following

conditions:

MA0 to MA19, MRD, and MWR: When the bus is released (MHOLDAK = low level)

MD0 to MD15: When the external data memory is not accessed and when the bus is released

(MHOLDAK = low level)

16

Data Sheet U15203EJ3V0DS

µµµµ

PD77210, 77213

•••• Timer

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

TIMOUT 68 K3 Output Time out monitor

I/O Function Alternate

Pin

This pin is asserted active when the timer times out.

•••• Serial interface

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

ASCK/

BCLK

ASO 70 K4 Output

ASI 76 P3 Input Audio serial data input −

ASOEN/

LRCLK

ASIEN/

MCLK

TSCK 79 N4 Input Clock input for time division serial −

TSO 78 P4 Output

TSI 81 P5 Input Time-division serial data input −

TSORQ 82 M5 Output Time-division serial output request −

TSOEN 77 M4 Input Time-division serial output enable −

TSIEN 80 L5 Input Time-division serial input enable −

TSIAK 83 N5 Output Time-division serial input acknowledge −

74 M2 I/O Audio serial clock input/output

69 M3 I/O Audio serial output enable/left right clock input output

75 N3 Input Audio serial input enable/master clock input output

I/O Function Alternate

Pin

ASCK:Audio serial clock input

BCLK:Serial clock I/O

Audio serial data output −

(3S)

ASOEN:Audio serial output enable input

LRCLK:Left right clock I/O

ASIEN:Audio serial input enable input

MCLK:Master clock input (in master mode)

Time-division serial data output −

(3S)

Remark Those pins marked “3S” in the above table enter the high-impedance state when data transmission is

completed and when the hardware reset (RESET) signal is input.

−

−

−

−

Data Sheet U15203EJ3V0DS

17

µµµµ

PD77210, 77213

•••• Host interface

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

HA1 63 J3 Input Host address 1

HA0 62 K1 Input Host address 0

HCS 61 J2 Input Chip select input −

HRD 64 K2 Input Host read input −

HWR 66 J4 Input Host write input −

HRE 65 L2 Output Host read enable output −

HWE 67 L1 Output Host write enable output −

HD0 to

HD7

HD8 to

HD15

49 to 56 F4,F2,F3,G1,

G3,G2,H3,H2

39 to 46 C2,C3,D1,D2,

D3,E3,E1,E2

I/O Function Alternate

Pin

This pin specifies a register that is accessed by the

host interface pins (HD7 to HD0, or HD15 to HD0).

• 1: The host interface status register (HST) is

accessed.

• 0: The host transmit data register (HDT (out)) is

accessed for read (HRD = 0) and the host receive

data register (HDT (in)) is accessed for write (HWR

= 0).

This pin specifies a register that is accessed by HD7

to HD0 in 8-bit mode. This pin is invalid in 16-bit

mode.

• 1: Bits 15 to 8 of HST, HDT (in), and HDT (out) are

accessed.

• 0: Bits 7 to 0 of HST, HDT (in), and HDT (out)

are accessed.

I/O

(3S)

I/O

(3S)

8-bit host data bus

These pins constitute a host data bus in 8-bit host

mode. Access to 16-bit data for input/output is

controlled by the HA0 pin, and the data is accessed

two times such that it is divided into two blocks of 8-

bit data.

In 16-bit mode, the lower 8 bits of the data are

input/output.

Host data bus

These pins constitute a host data bus in 16-bit host

mode. They input/output 16-bit data with HD0 to

HD7.

P8 to P15/

INT02,

INT12,

INT22,

INT32,

INT03,

INT13,

INT23,

INT33

Remark Those pins marked “3S” in the above table enter the high-impedance state while the host interface is not

being accessed.

−

−

−

18

Data Sheet U15203EJ3V0DS

µµµµ

PD77210, 77213

•••• I/O port

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

P0 28 C5 I/O INT00

P1 29 D6 I/O INT10

P2 30 A4 I/O INT20

P3 31 B5 I/O INT30

P4 32 C4 I/O INT01

P5 33 A3 I/O INT11

P6 34 B4 I/O INT21

P7 35 B3 I/O INT31

P8 39 C2 I/O INT02/HD8

P9 40 C3 I/O INT12/HD9

P10 41 D1 I/O INT22/HD10

P11 42 D2 I/O INT32/HD11

P12 43 D3 I/O INT03/HD12

P13 44 E3 I/O INT13/HD13

P14 45 E1 I/O INT23/HD14

P15 46 E2 I/O

I/O Function Alternate

Pin

General-purpose I/O port

INT33/HD15

•••• Debugging interface

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

TDO 141 C12 Output

TICE 142 D12 Output −

TCK 2 B12 Input −

TDI 3 C11 Input −

TMS 4 D11 Input −

TRST 5 A12 Input

I/O Function Alternate

Pin

For debugging

(3S)

This interface pins are used when a debugger is

used.

Remark Those pins marked “3S” in the above table enter the high-impedance state while the debugging interface

is not being accessed.

−

−

Data Sheet U15203EJ3V0DS

19

µµµµ

PD77210, 77213

••••SD card interface (

SDCLK 112 M12 Output SD card clock output

SDCR 111 M13 I/O

SDDAT0 104 L10 I/O

SDMON 103 P11 Output SD card interface access monitor

Reserved 105 to 107 M11, N11, N12 − Reserved for future function expansion.

µµµµ

PD77213 only)

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

I/O Function Alternate

Pin

MA19

• Leave this pin open.

(3S)

(3S)

SD cord command/response

Input: Response

Output: Command

• Leave pull-up.

SD card data input/output

Input: Read data

Output: Write data

• Leave pull-up.

This pin outputs a high level when the SD card

interface is being accessed.

1: SD card interface being accessed

0: SD card interface not being accessed

This pin becomes high impedance when the SD card

interface is being used.

MA18

MA14

MA13

MA15 to

MA17

Remark Those pins marked “3S” in the above table enter the high-impedance state when the SD card interface is

not being accessed.

•••• Others

Pin No.Pin Name

144-pin LQFP 161-pin FBGA

I.C. 6, 7 B11, C10 − Internally connected.

NC − A1,A2,A13,

A14,B1,B2,

B13,B14,E5,

N1,N2,N13,

N14,P1,P2,

P13,P14

I/O Function Alternate

Leave these pins open.

− No connection.

Leave these pins open.

Caution If any signal is input to these pins or if these pins are read, the correct operation of the

Family is not guaranteed.

Pin

−

−

µµµµ

PD77210

20

Data Sheet U15203EJ3V0DS

µµµµ

PD77210, 77213

1.2 Connection of Unused Pins

1.2.1 Connection of functional pins

Connect the unused pins as shown in the table below.

Pin Name I/O Recommended Connection

STOPS, HALTS Output Leave open.

CSTOP Input Connect to GND via a pull-down resistor.

CLKOUT Output Leave open.

P0 to P15 I/O Connect to EVDD via a pull-up resistor or to GND via a pull-down resistor.

HD0 to HD7

HA0, HA1 Input Connect to EVDD via a pull-up resistor or to GND via a pull-down resistor.

HCS, HRD, HWR Input Connect to EV

HRE, HWE Output Leave open.

TIMOUT Output Leave open.

ASCK, TSCK Input

ASI, TSI Input

ASIEN, TSIEN Input

ASOEN, TSOEN,

LRCLK

ASO, TSO Output

TSORQ Output

TSIAK Output

MA0 to MA19 Output Leave open.

MD0 to MD15

MRD, MWR Output Leave open.

MHOLDRQ Input Connect to EVDD via a pull-up resistor.

MBSTB, MHOLDAK Output Leave open.

MWAIT Input Connect to EVDD via a pull-up resistor.

TCK Input Connect to GND via a pull-down resistor.

TDO, TICE Output Leave open.

TMS, TDI Input Leave open (this pin is internally pulled up).

TRST Input Leave open (this pin is internally pulled down).

Note 1

Note 2

I/O Connect to EVDD via a pull-up resistor or to GND via a pull-down resistor.

via a pull-up resistor.

DD

Connect to EVDD

Connect to GND via a pull-down resistor.

Input

Leave open.

I/O Connect to EVDD via a pull-up resistor or to GND via a pull-down resistor.

via a pull-up resistor or to GND via a pull-down resistor.

Notes 1. These pins may left opened if the HCS, HRD,and HWR are fixed to the high level.

However, connect these pins as recommended in the HALT and STOP modes when the power

consumption must be lowered.

2. These pins may leave opened if the external data memory is not accessed in the program.

However, connect these pins as recommended in the HALT and STOP modes when the power

consumption must be lowered.

Caution Unused alternate-function pins should be handled in accordance with the processing specified

for the pin function of the initial setting.

Data Sheet U15203EJ3V0DS

21

1.2.2 Connection of non-functional pin

Pin name I/O Recommended Connection

I.C. − Leave open.

NC − Leave open.

µµµµ

PD77210, 77213

22

Data Sheet U15203EJ3V0DS

2. FUNCTIONAL OUTLINE

2.1 Program Control Unit

µµµµ

PD77210, 77213

This unit controls the execution of

interrupts, clock, and standby mode.

2.1.1 CPU control

A three-stage pipeline architecture is employed so that all instructions, except branch instructions and some

others, can be executed with one system clock.

2.1.2 Interrupt control

The interrupt control circuit services the interrupt requests input to the interrupt controller by an external pin

(INTmn) or internal peripherals (such as the serial interface, host interface, timer, and DMA controller). The interrupt

of each interrupt source can be individually enabled or disabled. In addition, multiple interrupts are also supported.

2.1.3 Loop control stack

A loop function without any hardware overhead is realized. A 4-level loop stack is provided to support multiple

loops.

2.1.4 PC stack

A 15-level PC stack that stacks the program counter supports multiple interrupts/subroutine calls.

2.1.5 Clock control

A PLL and a divider are internally provided as a clock generator so that an externally input clock is multiplied or

divided and supplied as the operating clock to the µPD77210 Family. The multiple of the PLL can be set by using

external pins (PLL0 to PLL3) within a range of ×10 to 64. The division ratio can be set by using a register in a range

of ÷1 to 16.

The clock control register (CLKC) controls the power (ON/OFF) to the PLL, selects a clock source, controls the

output divider, and controls the output of the CLKOUT pin.

Two types of standby modes are available so that the power consumption can be reduced when the µPD77210

Family is standing by.

PD77210 Family by executing instructions and controlling branching, loop,

µ

•HALT mode: Current consumption falls to several mA upon execution of the HALT instruction.

This mode is released by an interrupt or hardware reset.

•STOP mode:Current consumption falls to hundreds of

This mode is released by hardware reset or inputting a signal to CSTOP pin.

Note When the PLL is stopped

Data Sheet U15203EJ3V0DS

Note

A

upon execution of the STOP instruction.

µ

23

Loading...

Loading...