DATA SHEET

MOS INTEGRATED CIRCUIT

PPPP

PD70F3017A, 70F3017AY

V850/SA1

TM

32-/16-BIT SINGLE-CHIP MICROCONTROLLER

The PPD70F3017A, 70F3017AY are products with on-chip flash memory. Because the devices can be

programmed by the user on-board, they are ideal for the evaluation stages of system development, small-scale

production of a variety of products, and rapid development of new products.

The V850/SA1 provides a high-level cost performance ideal for applications ranging from low-power camcorders

and other AV equipment to portable telephone equipment such as cellular phones and personal handyphone

systems (PHS).

Detailed function descriptions are provided in the following user's manuals. Be sure to read them before

designing.

V850/SA1 User's Manual Hardware: U12768E

V850 Family

FEATURES

Number of instructions: 74

{

Minimum instruction execution time:

{

59 ns (@ 17 MHz operation with main system

XX

clock (f

50 ns (@ 20 MHz operation with main system

clock (f

30.5

clock (f

General-purpose registers: 32 bits u 32 registers

{

Instruction set:

{

Signed multiplication, saturation operations, 32-bit

shift instructions, bit manipulation instructions,

load/store instructions

Memory space:

{

16 MB linear address space

Memory block division function: 2 MB per block

External bus interface: 16-bit data bus

{

Address bus: Separate output enabled

Internal memory

{

Flash memory: 256 KB

RAM: 8 KB

))

XX

))

s (@ 32.768 kHz operation with subsystem

P

XT

))

TM

User's Manual Architecture: U10243E

Interrupts and exceptions

{

External: 8, internal: 23, exceptions: 1

I/O lines Total: 85

{

Timer/counters

{

16-bit timer: 2 channels

8-bit timer: 4 channels

Watch timer: 1 channel

{

Watchdog timer: 1 channel

{

Serial interface (SIO)

{

Asynchronous serial interface (UART)

Clocked serial interface (CSI)

2

C bus interface (PPD70F3017AY)

I

A/D converter: 12 channels

{

DMA controller: 3 channels

{

RTP: 8 bits u 1 channel or 4 bits u 2 channels

{

Power-saving functions: HALT/IDLE/STOP modes

{

Packages: 100-pin plastic LQFP (14 u 14 mm)

{

121-pin plastic FBGA (12 u 12 mm)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Document No. U14527EJ2V0DS00 (2nd edition)

Date Published August 2000 J CP(K)

Printed in Japan

The mark shows major revised points.

©

2000

APPLICATIONS

Low-power portable devices

{

Cellular phones, PHSs, and camcorders

ORDERING INFORMATION

Part Number Package Internal ROM

PD70F3017AGC-8EU

P

PD70F3017AF1-EA6

P

PD70F3017AYGC-8EU

P

PD70F3017AYF1-EA6

P

100-pin plastic LQFP (fine-pitch) (14 u 14 mm)

121-pin plastic FBGA (12 u 12 mm)

100-pin plastic LQFP (fine-pitch) (14 u 14 mm)

121-pin plastic FBGA (12 u 12 mm)

PPPP

PD70F3017A, 70F3017AY

256 KB (Flash memory)

256 KB (Flash memory)

256 KB (Flash memory)

256 KB (Flash memory)

2

Data Sheet U14527EJ2V0DS00

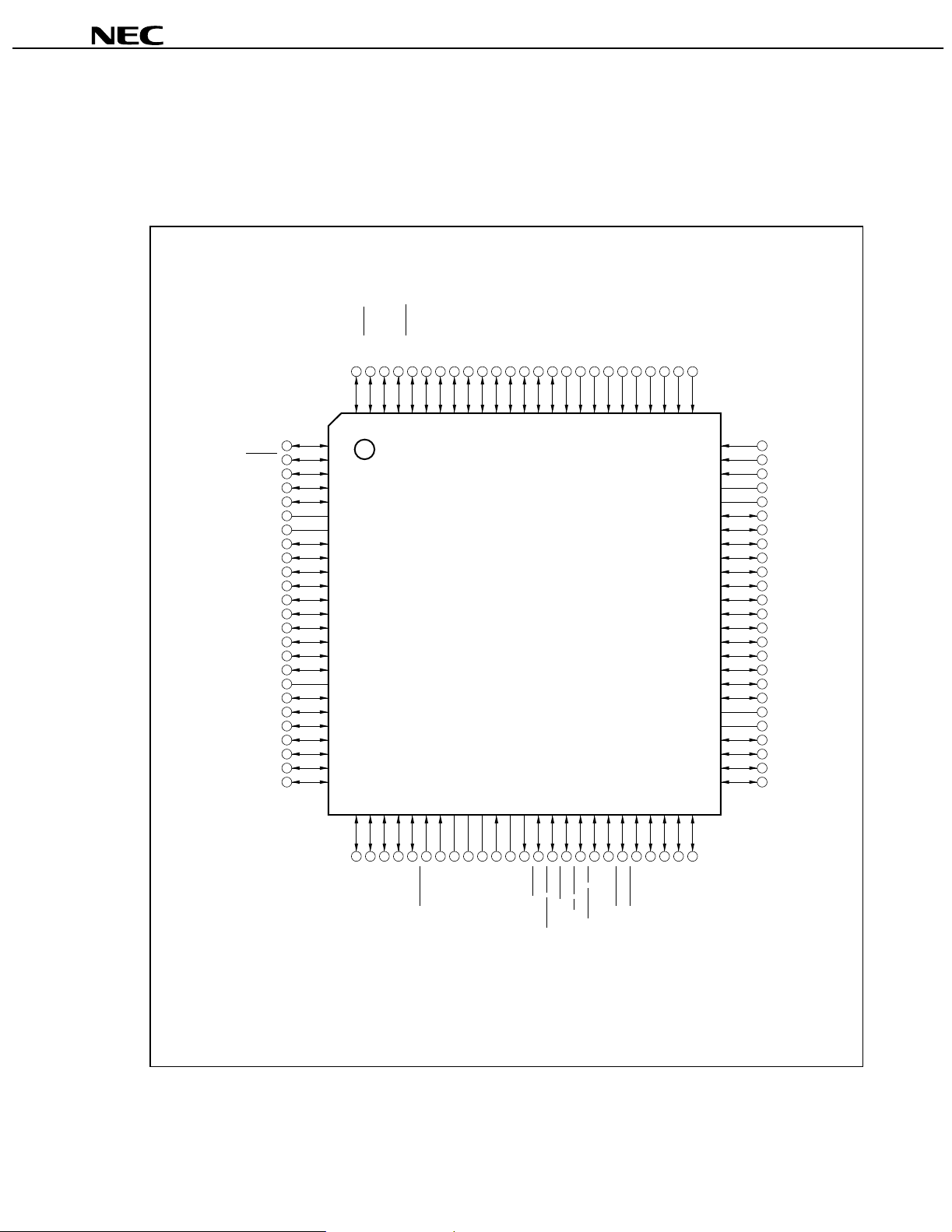

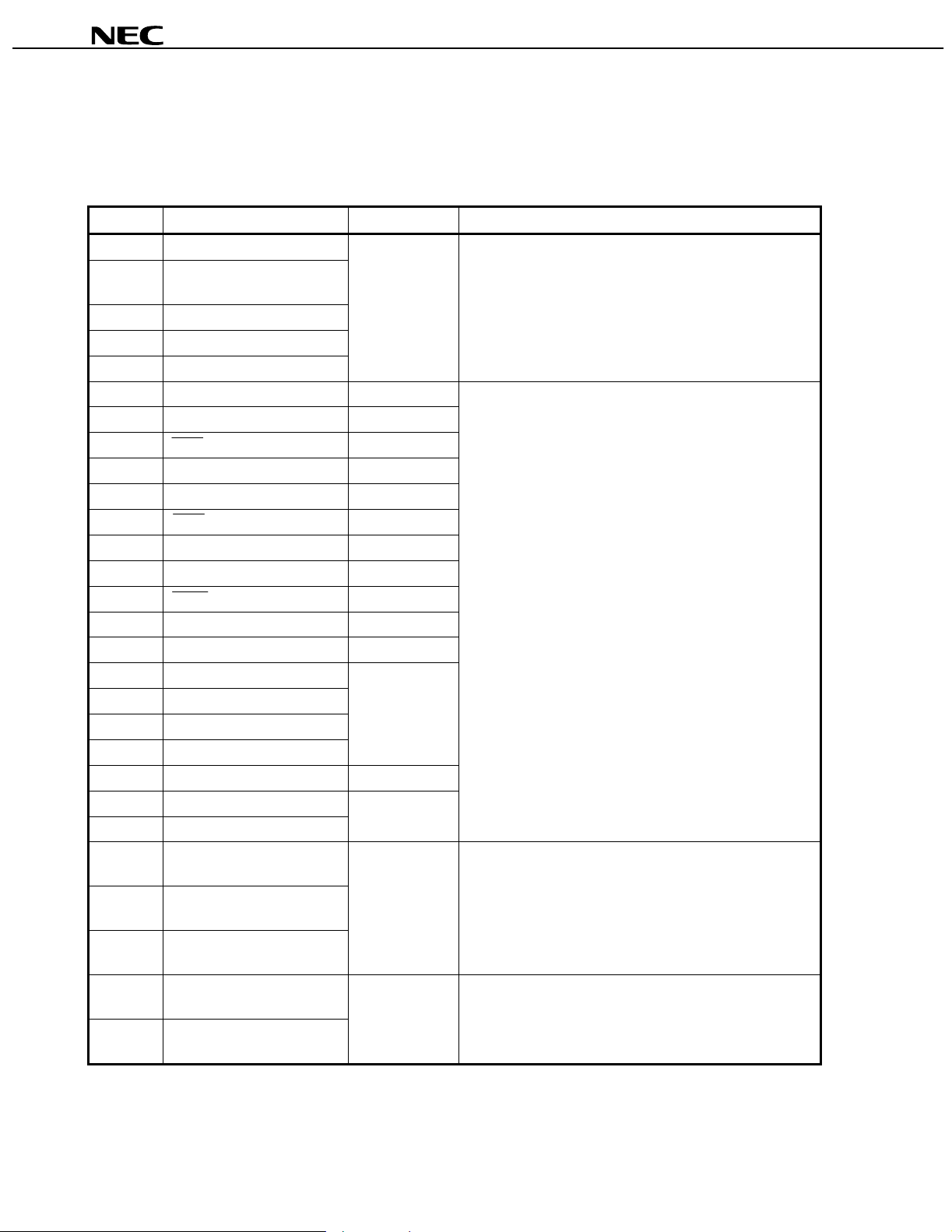

PIN CONFIGURATION

100-pin plastic LQFP (fine-pitch) (14 u 14 mm)

PD70F3017AGC-8EU

P

PD70F3017AYGC-8EU

P

P20/SI2

P15/SCK1/ASCK0

P14/SO1/TXD0

Note 2

Note 2

P07/INTP6

P11/SO0

P10/SI0/SDA

P13/SI1/RXD0

P12/SCK0/SCL

PPPP

P06/INTP5/RTPTRG

P05/INTP4/ADTRG

P04/INTP3

P03/INTP2

P02/INTP1

P01/INTP0

P00/NMI

P83/ANI11

PD70F3017A, 70F3017AY

P82/ANI10

P81/ANI9

P80/ANI8

P77/ANI7

P76/ANI6

P75/ANI5

P74/ANI4

P73/ANI3

P72/ANI2

P21/SO2

P22/SCK2

P23/RXD1

P24/TXD1

P25/ASCK1

V

V

P26/TI2/TO2

P27/TI3/TO3

P30/TI00

P31/TI01

P32/TI10

P33/TI11

P34/TO0/A13

P35/TO1/A14

P36/TI4/TO4/A15

P37/TI5/TO5

Note 1

V

PP

P100/RTP0/A5

P101/RTP1/A6

P102/RTP2/A7

P103/RTP3/A8

P104/RTP4/A9

P105/RTP5/A10

P106/RTP6/A11

9998979695949392919089888786858483828180797877

100

1

2

3

4

5

DD

SS

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

P71/ANI1

P70/ANI0

REF

AV

AV

SS

AV

DD

P65/A21

P64/A20

P63/A19

P62/A18

P61/A17

P60/A16

P57/AD15

P56/AD14

P55/AD13

P54/AD12

P53/AD11

P52/AD10

P51/AD9

P50/AD8

BV

SS

BV

DD

P47/AD7

P46/AD6

P45/AD5

P44/AD4

26272829303132333435363738394041424344454647484950

SS

DD

X2

X1

V

V

XT2

P111/A2

P112/A3

P113/A4

RESET

P114/XT1

CLKOUT

P91/UBEN

P120/WAIT

P90/LBEN/WRL

P40/AD0

P94/ASTB

P95/HLDAK

P96/HLDRQ

P93/DSTB/RD

P92/R/W/WRH

P41/AD1

P42/AD2

P43/AD3

P110/A1

P107/RTP7/A12

Notes 1.

PP

Connect the V

Applies to the PPD70F3017AY only.

2.

pin to VSS in the normal operating mode.

Data Sheet U14527EJ2V0DS00

3

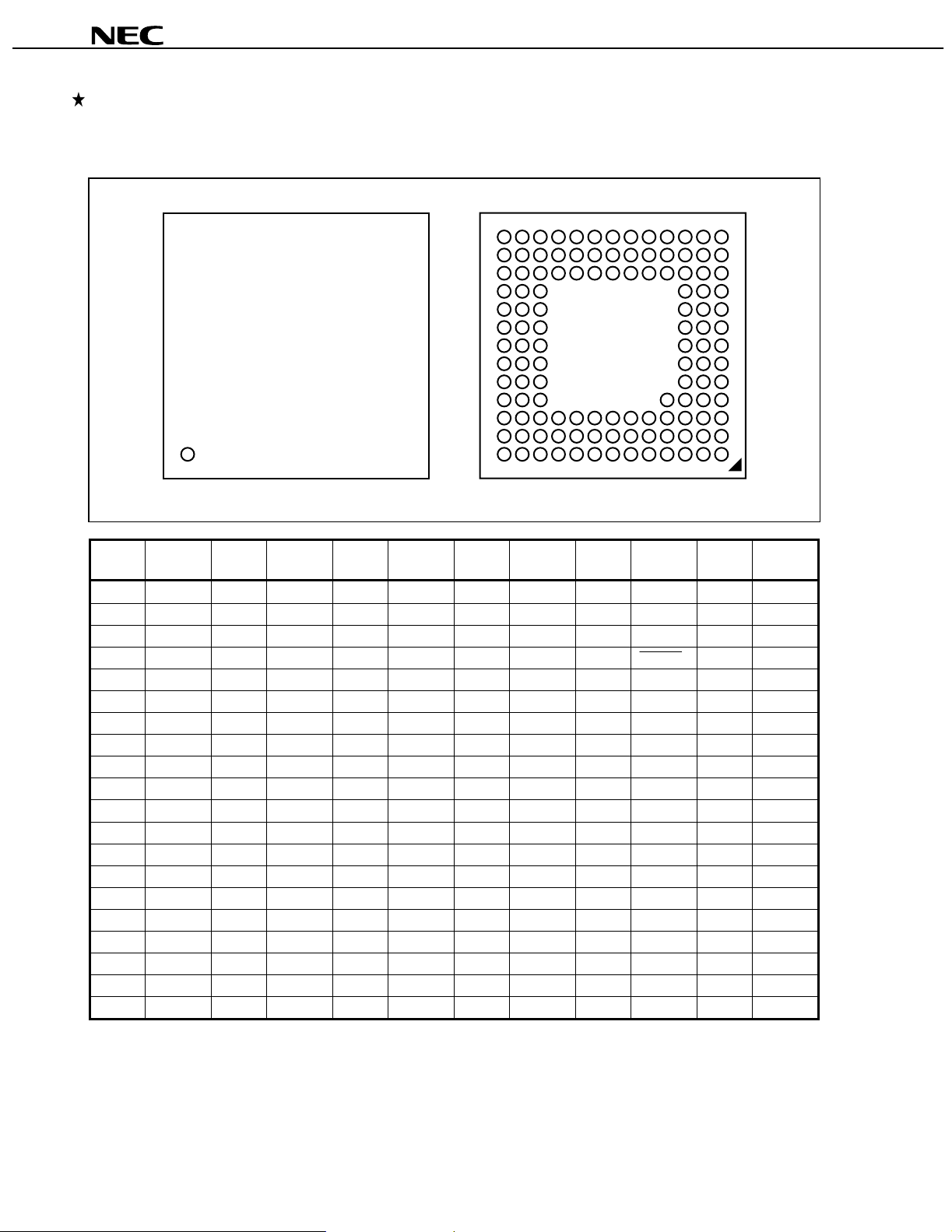

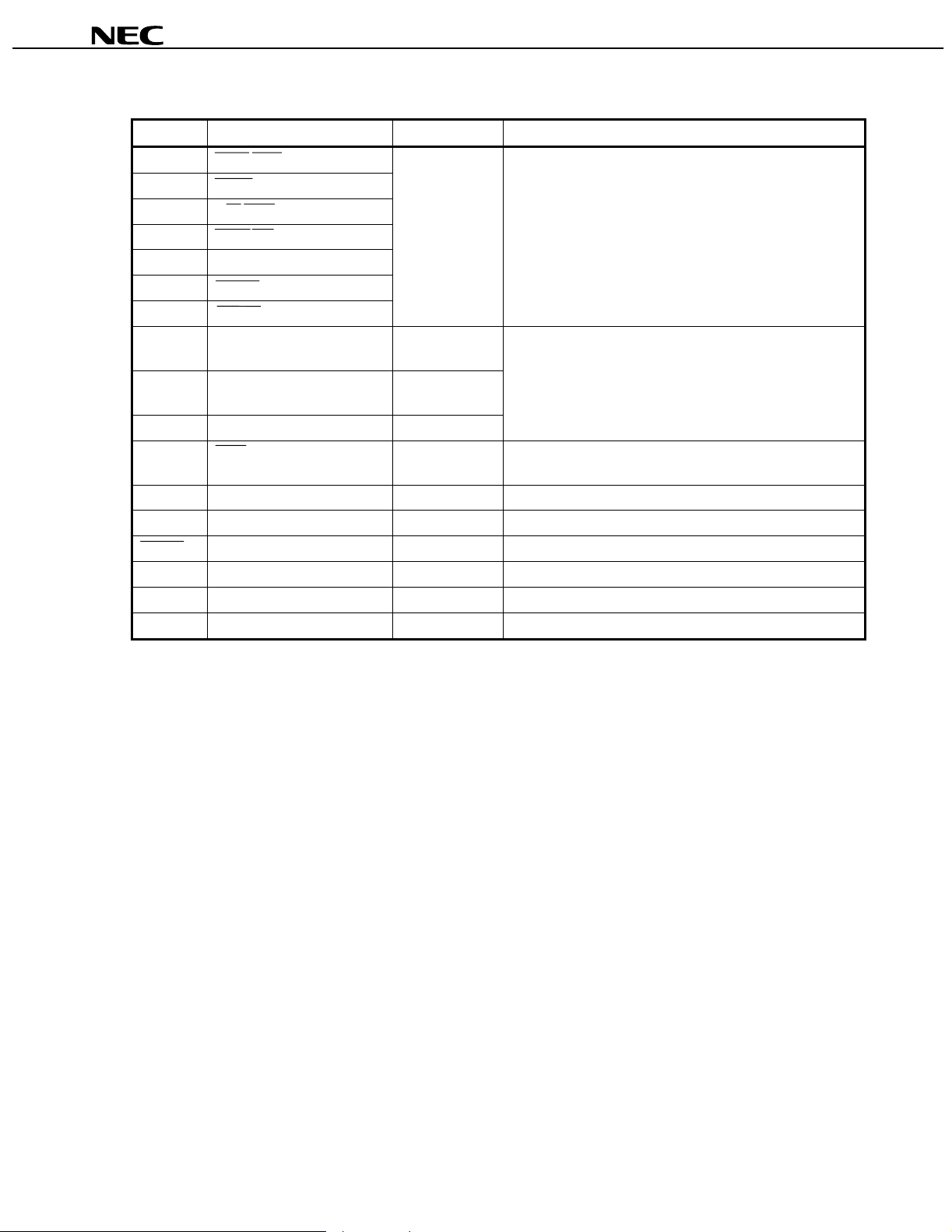

121-pin plastic FBGA (12 u 12 mm)

PD70F3017AF1-EA6

P

PD70F3017AYF1-EA6

P

Top View Bottom View

13

12

11

10

PPPP

PD70F3017A, 70F3017AY

9

8

7

6

5

4

3

2

1

NMLKJHGFEDCBAABCDEFGHJKLMN

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

A1 P20 B8 P83 D2 V

A2 P15 B9 P80 D3 V

A3 V

A4 P13 B11 AV

A5 P11 B12 AV

SS

B10 P75 D11 AV

SS

SS

D12 AV

D13 AV

Pin Name

DD

SS

DD

DD

DD

Pin

Number

Pin Name

G11 P60 K13 BV

G12 P56 L1 P104 M8 V

G13 P57 L2 P105 M9 P92

H1 P34 L3 RESET M10 P95

H2 P37 L4 V

Pin

Number

A6 P06 B13 P71 E1 P25 H3 P35 L5 V

A7 P03 C1 P22 E2 V

DD

H11 P55 L6 X2 M13 P44

Pin Name

DD

SS

Pin

Number

DD

M7 V

Pin Name

SS

SS

M11 P41

M12 P45

A8 P00 C2 P23 E3 P30 H12 P53 L7 P90 N1 P107

A9 P81 C3 V

SS

E11 AV

A10 P76 C4 P24 E12 P64 J1

A11 P73 C5 P07 E13 P65 J2

A12 P72 C6 P04 F1 P26 J3 P100 L11 BV

A13 AV

SS

C7 P01 F2 P27 J11 P52 L12 BV

B1 P21 C8 P82 F3 P33 J12 P50 L13 BV

DD

H13 P54 L8 P120 N2 P110

Note

PP

V

Note

PP

V

L9 P93 N3 P112

L10 P96 N4 V

SS

SS

SS

N5 XT1

N6 V

N7 V

DD

SS

SS

B2 P14 C9 P77 F11 P63 J13 P51 M1 P106 N8 CLKOUT

B3 V

B4 P12 C11 AV

B5 P10 C12 P70 G1 P31 K3 P103 M4 V

B6 P05 C13 AV

B7 P02 D1 V

Note

SS

C10 P74 F12 P61 K1 P101 M2 P111 N9 P91

Connect the V

SS

REF

DD

PP

pin to VSS in the normal operating mode.

F13 P62 K2 P102 M3 P113 N10 P94

G2 P32 K11 P46 M5 XT2 N12 P42

G3 P36 K12 P47 M6 X1 N13 P43

DD

N11 P40

Remarks 1.

4

Alternate function names are omitted. The alternate functions are identical to the 100-pin plastic

LQFP.

SS

Connect the D4 pin directly to V

2.

.

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3017AY

PIN IDENTIFICATION

A1 to A21: Address Bus P100 to P107: Port 10

AD0 to AD15: Address/Data Bus P110 to P114: Port 11

ADTRG: AD Trigger Input P120: Port 12

ANI0 to ANI11: Analog Input RD: Read

ASCK0, ASCK1: Asynchronous Serial Clock RESET: Reset

ASTB: Address Strobe RTP0 to RTP7: Real-Time Port

AVDD: Analog V

REF

AV

: Analog Reference Voltage R/W: Read/Write Status

AVSS: Analog V

BVDD: Power Supply for Bus Interface SCK0 to SCK2: Serial Clock

BVSS: Ground for Bus Interface SCL

CLKOUT: Clock Output SDA

DSTB: Data Strobe SI0 to SI2: Serial Input

HLDAK: Hold Acknowledge SO0 to SO2: Serial Output

HLDRQ: Hold Request TI00, TI01, TI10, : Timer Input

INTP0 to INTP6: Interrupt Request From Peripherals TI11, TI2 to TI5

LBEN: Lower Byte Enable TO0 to TO5: Timer Output

NMI: Non-maskable Interrupt Request TXD0,TXD1: Transmit Data

P00 to P07: Port 0 UBEN: Upper Byte Enable

P10 to P15: Port 1 VDD: Power Supply

P20 to P27: Port 2 VPP: Programming Power Supply

P30 to P37: Port 3 VSS: Ground

P40 to P47: Port 4 WAIT: Wait

P50 to P57: Port 5 WRH: Write Strobe High Level Data

P60 to P65: Port 6 WRL: Write Strobe Low Level Data

P70 to P77: Port 7 X1, X2: Crystal for Main System Clock

P80 to P83: Port 8 XT1, XT2: Crystal for Subsystem Clock

P90 to P96: Port 9

DD

SS

RTPTRG: RTP Trigger

RXD0, RXD1: Receive Data

Note

: Serial Clock

Note

: Serial Data

Note

Applies to the PPD70F3017AY only.

Data Sheet U14527EJ2V0DS00

5

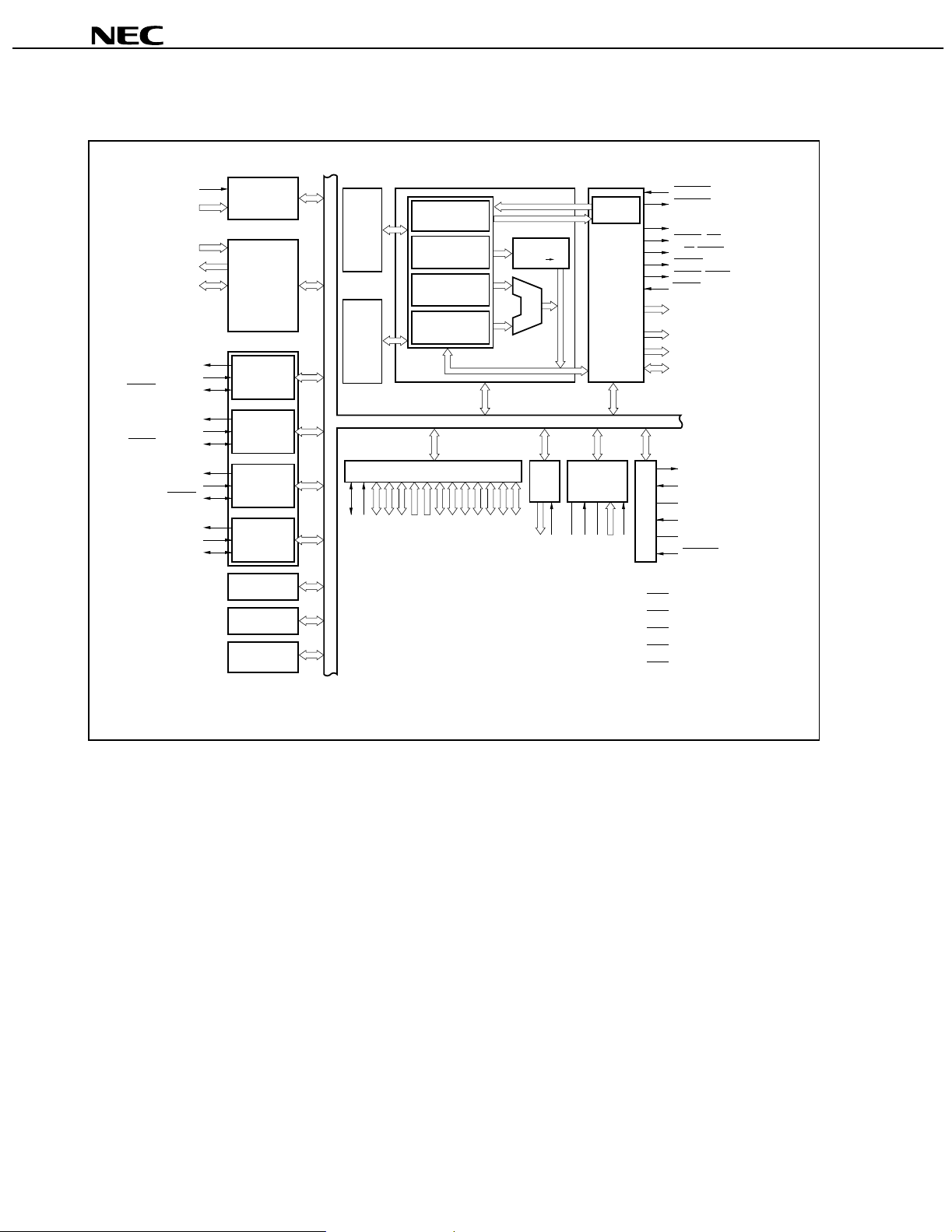

INTERNAL BLOCK DIAGRAM

PPPP

PD70F3017A, 70F3017AY

NMI

INTP0 to INTP6

TI00, TI01,

TI10, TI11

TO0, TO1

TI2/TO2

TI3/TO3

TI4/TO4

TI5/TO5

SO0

Note

SI0/SDA

SCK0/SCL

Note

SO1/TXD0

SI1/RXD0

SCK1/ASCK0

SO2

SI2

SCK2

TXD1

RXD1

ASCK1

INTC

Timer/counters

16-bit timer:

TM0, TM1

8-bit timer:

TM2 to TM5

SIO

Note

CSI0/I2C

CSI1/UART0

CSI2

UART1

DMAC: 3 ch

Watch timer

Watchdog

timer

Flash

memory

256 KB

RAM

8 KB

P120

P114

barrel shifter

System

registers

General-purpose

registers

32 bits x 32

Port

P90 to P96

P80 to P83

P110 to P113

P70 to P77

P100 to P107

PC

32-bit

P60 to P65

P50 to P57

P40 to P47

CPU

P30 to P37

P20 to P27

P10 to P15

Multiplier

16 x 16 32

ALU

RTP

P00 to P07

RTPTRG

RTP0 to RTP7

Instruction

queue

BCU

A/D

converter

SS

DD

REF

AV

AV

AV

HLDRQ (P96)

HLDAK (P95)

ASTB (P94)

DSTB/RD (P93)

R/W/WRH (P92)

UBEN (P91)

LBEN/WRL (P90)

WAIT

A1 to A12

(P100 to P107, P110 to P113)

A13 to A15 (P34 to P36)

A16 to A21 (P60 to P65)

AD0 to AD15

(P40 to P47, P50 to P57)

CG

ADTRG

ANI0 to ANI11

V

V

BV

BV

V

CLKOUT

X1

X2

XT1 (P114)

XT2

RESET

DD

SS

DD

SS

PP

Note

Applies to the

PD70F3017AY only.

P

6

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

CONTENTS

1. PIN FUNCTIONS ..................................................................................................................................8

1.1 Port Pins.....................................................................................................................................................8

1.2 Non-Port Pins...........................................................................................................................................11

1.3 Pin I/O Circuits and Recommended Connection of Unused Pins........................................................14

2. ELECTRICAL SPECIFICATIONS......................................................................................................18

3. PACKAGE DRAWINGS .....................................................................................................................43

4. RECOMMENDED SOLDERING CONDITIONS................................................................................45

Data Sheet U14527EJ2V0DS00

7

PPPP

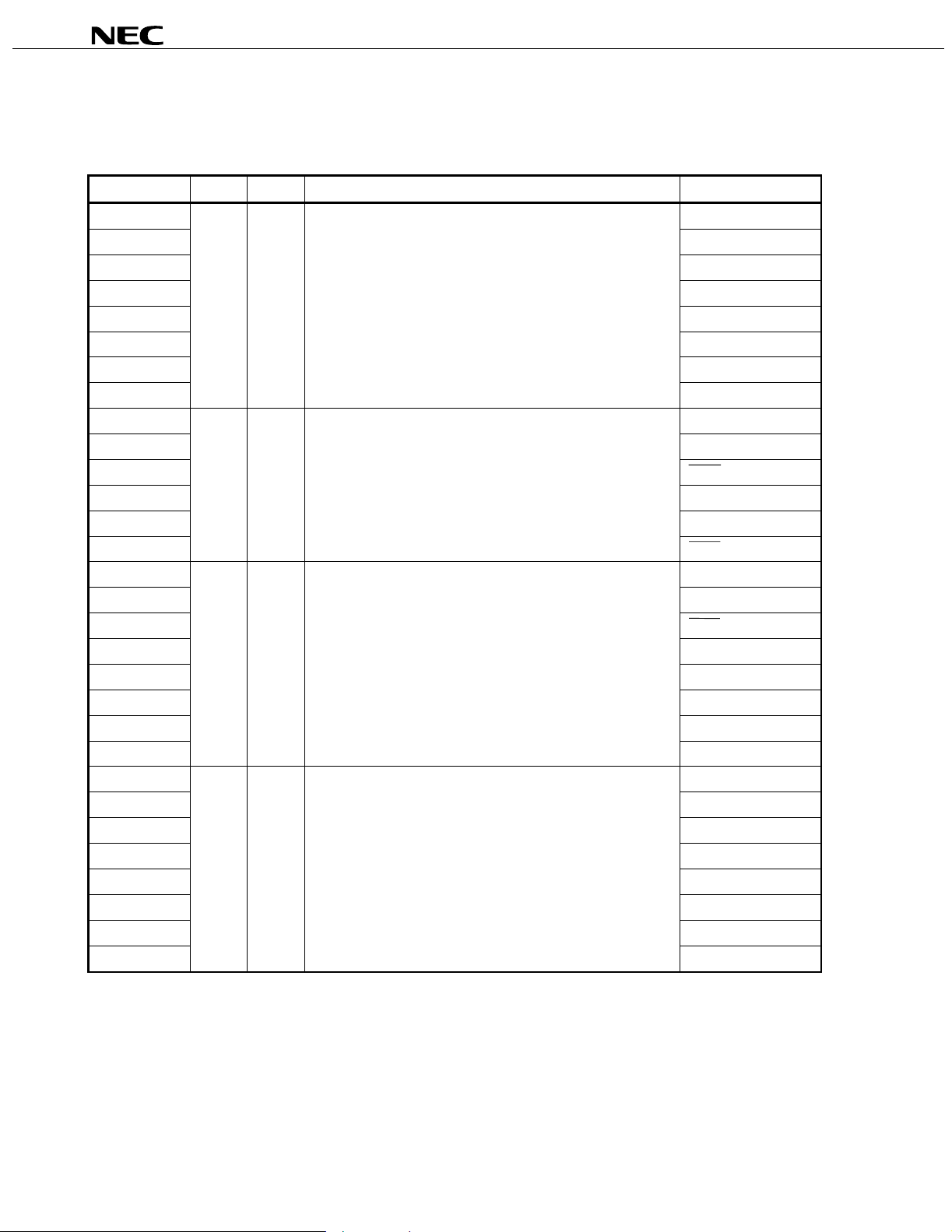

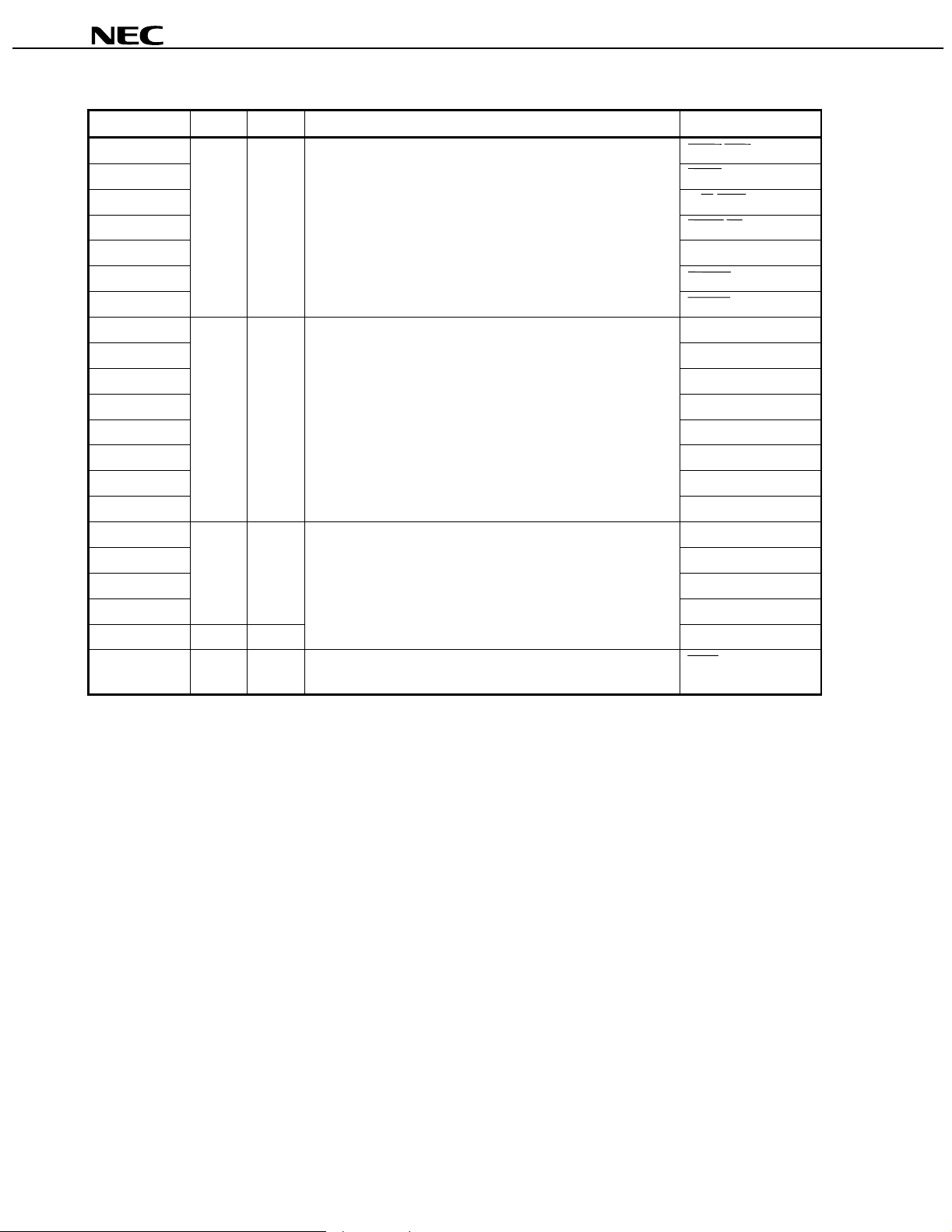

PD70F3017A, 70F3017AY

1. PIN FUNCTIONS

1.1Port Pins

Pin Name I/O PULL Function Alternate Function

(1/3)

P00 NMI

P01 INTP0

P02 INTP1

P03 INTP2

P04 INTP3

P05 INTP4/ADTRG

P06 INTP5/RTPTRG

P07

P10

P11 SO0

P12

P13 SI1/RXD0

P14 SO1/TXD0

P15

P20 SI2

P21 SO2

P22 SCK2

P23 RXD1

P24 TXD1

P25 ASCK1

P26 TI2/TO2

P27

P30 TI00

P31 TI01

P32 TI10

P33 TI11

P34 TO0/A13

P35 TO1/A14

P36 TI4/TO4/A15

P37

I/O Yes Port 0

8-bit I/O port

Input/output can be specified in 1-bi t uni ts.

I/O Yes Port 1

6-bit I/O port

Input/output can be specified in 1-bi t uni ts.

I/O Yes Port 2

8-bit I/O port

Input/output can be specified in 1-bi t uni ts.

I/O Yes Port 3

8-bit I/O port

Input/output can be specified in 1-bi t uni ts.

INTP6

SI0/SDA

SCK0/SCL

SCK1/ASCK0

TI3/TO3

TI5/TO5

Note

Note

Note

Remark

8

Applies to the

PD70F3017AY only.

P

PULL: On-chip pull-up resistor

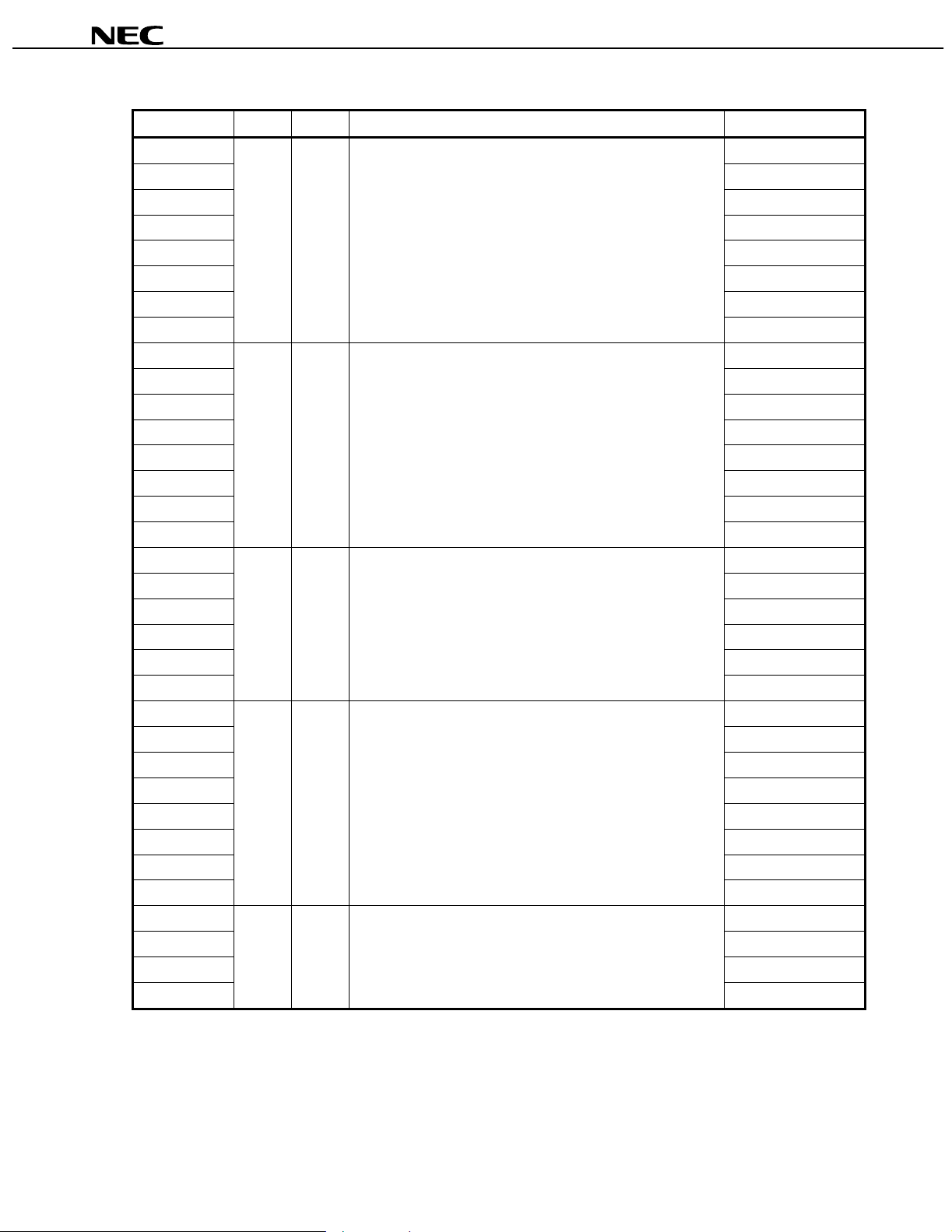

Data Sheet U14527EJ2V0DS00

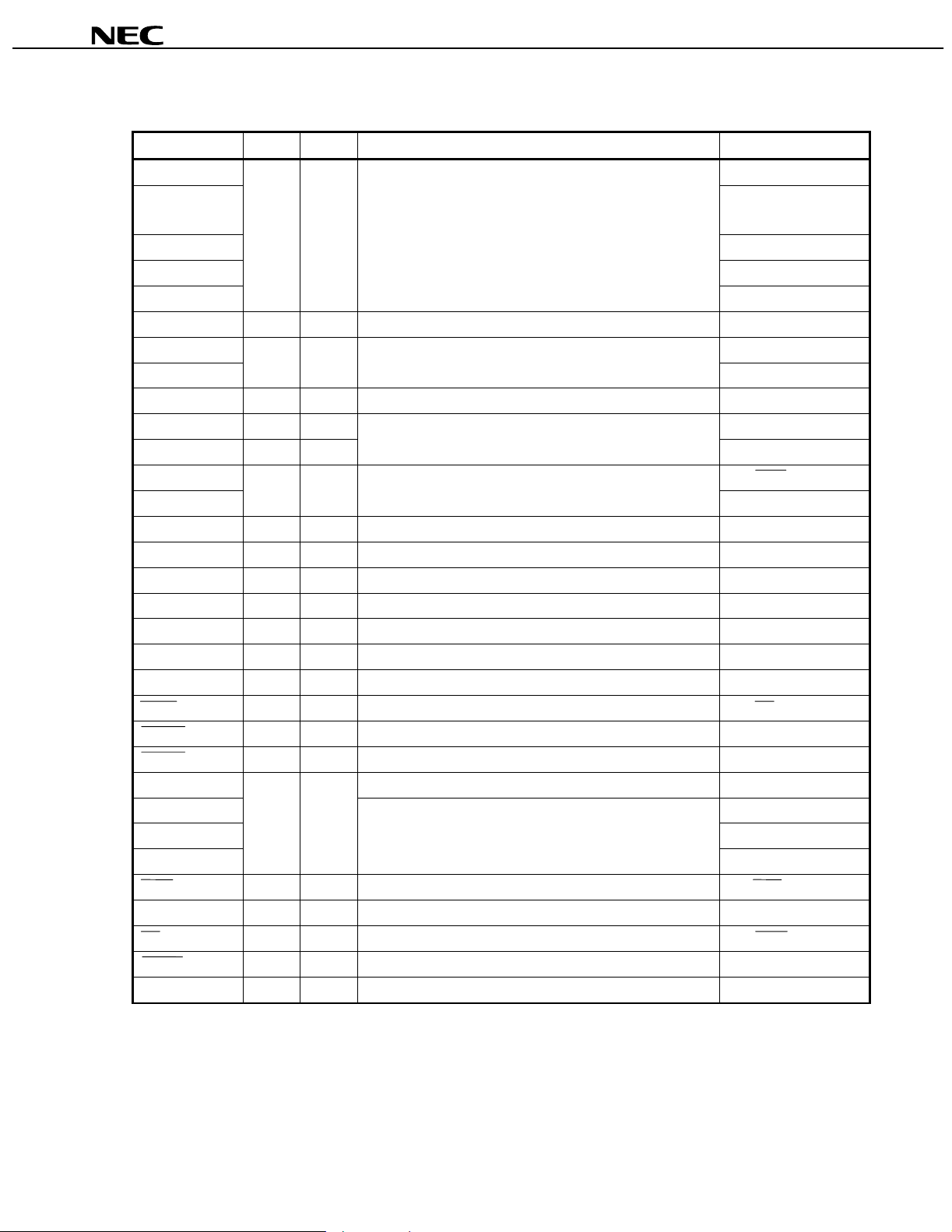

PPPP

PD70F3017A, 70F3017AY

Pin Name I/O PULL Function Alternate Function

(2/3)

P40 AD0

P41 AD1

P42 AD2

P43 AD3

P44 AD4

P45 AD5

P46 AD6

P47

P50 AD8

P51 AD9

P52 AD10

P53 AD11

P54 AD12

P55 AD13

P56 AD14

P57

P60 A16

P61 A17

P62 A18

P63 A19

P64 A20

P65

P70 ANI0

P71 ANI1

P72 ANI2

P73 ANI3

P74 ANI4

P75 ANI5

P76 ANI6

P77

P80 ANI8

P81 ANI9

P82 ANI10

P83

I/O No Port 4

8-bit I/O port

Input/output can be spec i f i ed i n 1-bi t units.

AD7

I/O No Port 5

8-bit I/O port

Input/output can be spec i f i ed i n 1-bi t units.

AD15

I/O No Port 6

6-bit I/O port

Input/output can be spec i f i ed i n 1-bi t units.

A21

Input No Port 7

8-bit input port

ANI7

Input No Port 8

4-bit input port

ANI11

Remark

PULL: On-chip pull-up resistor

Data Sheet U14527EJ2V0DS00

9

PPPP

PD70F3017A, 70F3017AY

Pin Name I/O PULL Function Alternate Function

(3/3)

P90 LBEN/WRL

P91 UBEN

P92 R/W/WRH

P93 DSTB/RD

P94 ASTB

P95 HLDAK

P96

P100 RTP0/A5

P101 RTP1/A6

P102 RTP2/A7

P103 RTP3/A8

P104 RTP4/A9

P105 RTP5/A10

P106 RTP6/A11

P107

P110 A1

P111 A2

P112 A3

P113

P114 Input No

P120 I/O No Port 12

I/O No Port 9

7-bit I/O port

Input/output can be spec i f i ed i n 1-bi t units.

I/O Yes Port 10

8-bit I/O port

Input/output can be spec i f i ed i n 1-bi t units.

I/O Yes

Port 11

5-bit I/O port

Input/output can be spec i f i ed i n 1-bi t units.

P114 is fixed as input onl y.

1-bit I/O port

HLDRQ

RTP7/A12

A4

XT1

WAIT

Remark

PULL: On-chip pull-up resistor

10

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3017AY

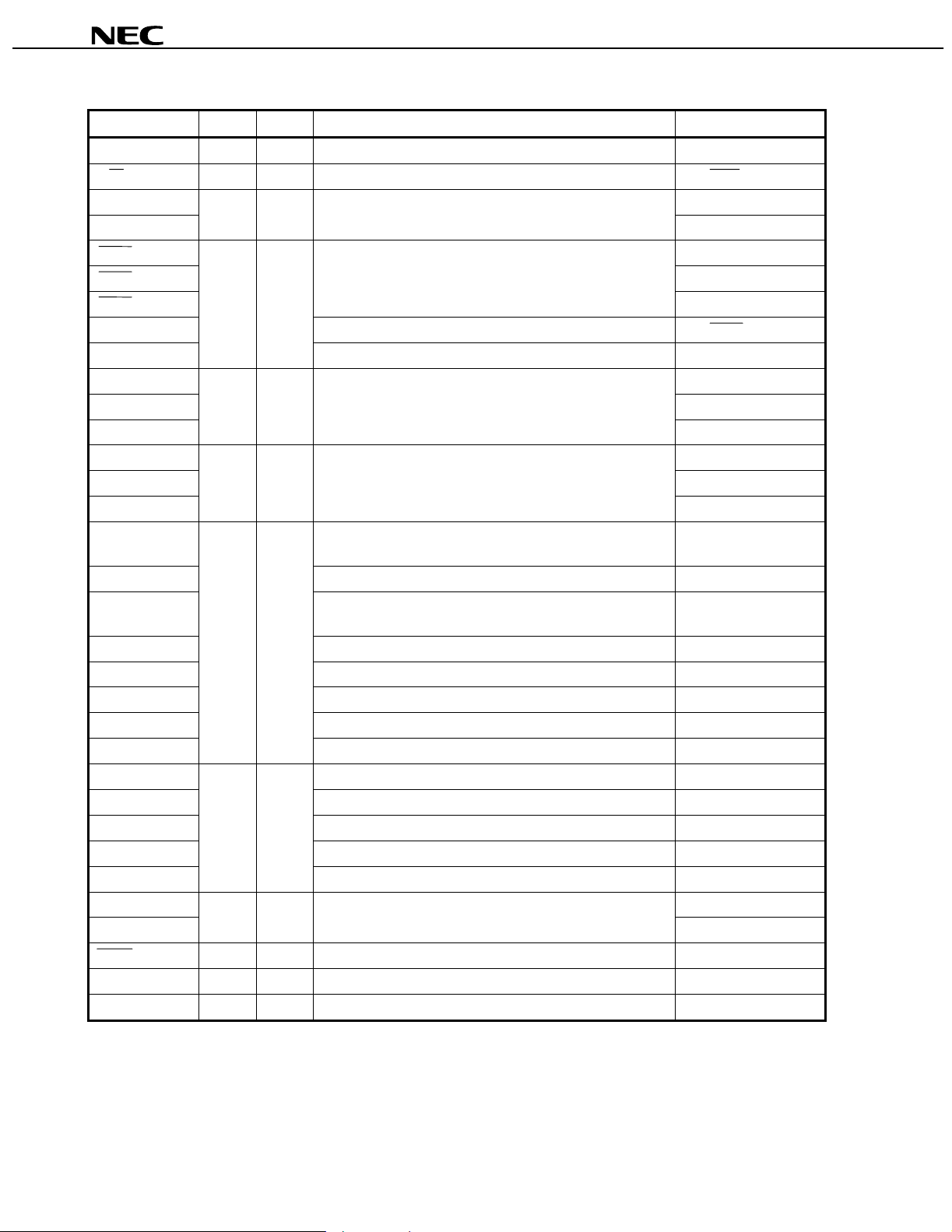

1.2 Non-Port Pins

Pin Name I/O PULL Function Alternate Function

(1/3)

A1 to A4 P110 to P113

A5 to A12

A13 P34/TO0

A14 P35/TI1

A15

A16 to A21 Output No High-order address bus used for ex ternal memory expansion P60 to P65

AD0 to AD7 P40 to P47

AD8 to AD15

ADTRG Input Yes A/ D c onverter external trigger input P05/INTP4

ANI0 to ANI7 Input No P70 to P77

ANI8 to ANI11 Input No

ASCK0 P15/SCK1

ASCK1

ASTB Output No E x ternal address strobe signal output P94

DD

AV

REF

AV

SS

AV

DD

BV

SS

BV

CLKOUT Output

DSTB Output No External data strobe signal output P93/RD

HLDAK Output No Bus hol d acknowledge output P95

HLDRQ Input No Bus hold request input P96

INTP0 to INTP3 External interrupt request i nput (anal og noi se elimination) P01 to P 04

INTP4 P05/ADTRG

INTP5 P06/RTPTRG

INTP6

LBEN Output No External data bus's low-order byte enable signal output P90/WRL

NMI Input Yes Non-maskable interrupt request i nput P00

RD Output No Read strobe signal output P93/DSTB

RESET Input

RTP0 to RTP7 Output Yes Real-time output port P100/A5 to P107/A12

Output Yes Low-order address bus us ed for external memory expans i on

I/O No 16-bi t multiplexed address/dat a bus used for external memory

expansion

Analog input to A/D converter

Input Y es Seri al clock input for UART0 and UART1

ðð

Input

ðð

ðð

ðð

Input Y es

Positive power supply for A/D converter

Reference voltage input for A / D converter

ð

Ground potential for A/D conv ert er

Positive power supply for bus interface

Ground potential for bus interface

Internal system clock output

ð

External interrupt request i nput (di gi tal noise elimination)

System reset input

ð

P100/RTP0 to

P107/RTP7

P36/TI4/TO4

P50 to P57

P80 to P83

P25

ð

ð

ð

ð

ð

ð

P07

ð

Remark

PULL: On-chip pull-up resistor

Data Sheet U14527EJ2V0DS00

11

PPPP

PD70F3017A, 70F3017AY

Pin Name I/O PULL Function Alternate Function

RTPTRG Input Y es RTP ex t ernal t ri gger i nput P06/INTP5

R/W Output No External read/wri te status output P92/WRH

RXD0 P13/SI1

RXD1

SCK0 P12

SCK1 P15/ASCK0

SCK2

SCL I2C serial clock I/O (PPD70F3017AY only) P12/SCK0

SDA

SI0 P10

SI1 P13/RXD0

SI2

SO0 P11

SO1 P14/TXD0

SO2

TI00 External c apture trigger input and external count clock input

TI01 External capt ure trigger input for TM0 P31

TI10 External c apture trigger input and external count clock input

TI11 External capt ure trigger input for TM1 P33

TI2 External count clock i nput for TM2 P26/TO2

TI3 External count clock i nput for TM3 P27/TO3

TI4 External count clock i nput for TM4 P36/TO4/A15

TI5

TO0, TO1 Pulse signal output for TM0, TM1 P34/A13, P35/ A14

TO2 Pulse signal output for TM2 P26/TI2

TO3 Pulse signal output for TM3 P27/TI3

TO4 Pulse signal output for TM4 P36/TI4/A15

TO5

TXD0 P 14/SO1

TXD1

UBEN Output No High-order by t e enabl e signal output for external dat a bus P91

DD

V

SS

V

Input Y es Seri al receive data input for UART0 and UART1

I/O Yes

Input Yes Serial receive data input (3-wi re type) for CSI0 to CSI2

Output Yes Serial trans m i t data output (3-wire type) for CSI0 to CSI2

Input Yes

Output Yes

Output Yes Serial trans m i t data output for UART0 and UART1

ðð

ðð

Serial clock I/O (3-wire type) for CSI0 to CSI2

I2C serial transmit/rec ei ve data I/O (PPD70F3017AY only) P10/SI0

for TM0

for TM1

External count clock i nput for TM5 P37/TO5

Pulse signal output for TM5 P37/TI5

Positive power supply pi n

GND potential

P23

P22

P20

P21

P30

P32

P24

ð

ð

(2/3)

12

Remark

PULL: On-chip pull-up resistor

Data Sheet U14527EJ2V0DS00

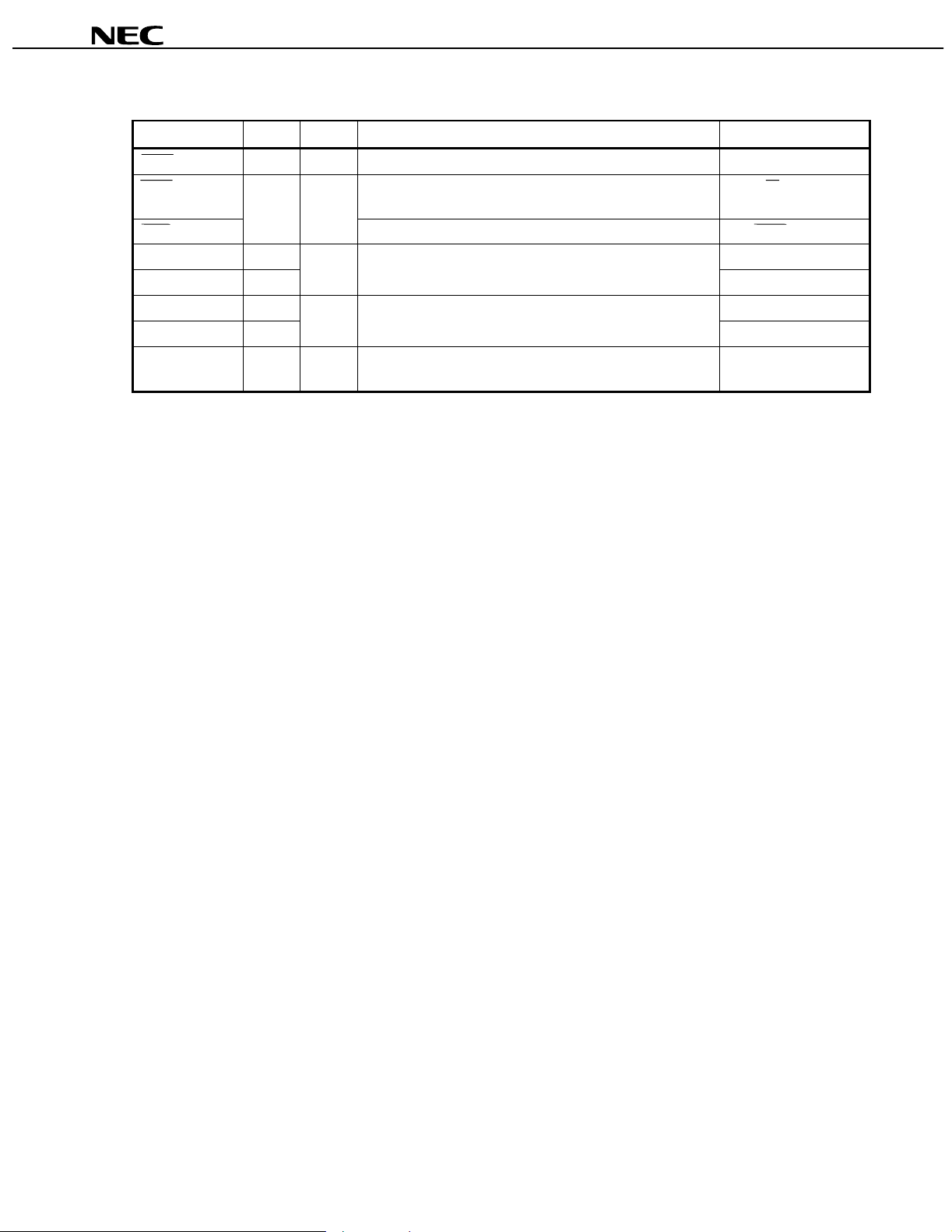

µµµµ

PD70F3017A, 70F3017AY

Pin Name I/O PULL Function Alternate Function

WAIT Input No Control signal input for inserting wait in bus cycle P120

WRH High-order byte write strobe signal output for external data

WRL

X1 Input

X2

XT1 Input P114

XT2

PP

V

Output No

No Resonator connection for main system clock

−

No Resonator connection for subsystem clock

−

−−

bus

Low-order byte write strobe signal output for external data bus P90/LBEN

Pin to which high voltage is applied during program

write/verify

P92/R/W

−

−

−

−

(3/3)

Remark

PULL: On-chip pull-up resistor

Data Sheet U14527EJ2V0DS00

13

PPPP

PD70F3017A, 70F3017AY

1.3 Pin I/O Circuits and Recommended Connection of Unused Pins

The input/output circuit type of each pin and recommended connection of unused pins are shown in Table 1-1. For

the input/output schematic circuit diagram of each type, refer to Figure 1-1.

Table 1-1. Types of Pin I/O Circuits (1/2)

Pin Alternate Function I/O Circuit Type Recommended Connection of Unused Pins

P00 NMI

P01 to

INTP0 to INTP3

8-A Input: Connect to V

P04

P05 INTP4/ADTRG

P06 INTP5/RTPTRG

P07 INTP6

P10

SI0/SDA

Note

10-A

P11 SO0 26

P12

SCK0/SCL

Note

10-A

P13 SI1/RXD0 8-A

P14 SO1/TXD0 26

P15 SCK1/ASCK0 10-A

P20 SI2 8-A

P21 SO2 26

P22 SCK2 10-A

P23 RXD1 8-A

P24 TXD1 5-A

P25 ASCK1

8-A

P26, P27 TI2/TO2, TI3/TO3

P30, P31 TI00, TI 01

P32, P33 TI10, TI 11

P34, P35 TO0/A13, TO1/A14 5-A

P36 TI4/TO4/A15

8-A

P37 TI5/TO5

P40 to

AD0 to AD7

5 Input: Connect to BV

P47

P50 to

AD8 to AD15

P57

P60 to

A16 to A21

P65

P70 to

ANI0 to ANI7

9 Connect to AV

P77

P80 to

ANI8 to ANI11

P83

Output: Leave open

Input: Connect to V

Output: Leave open

Output: Leave open

SS

or AV

SS

DD

DD

DD

or V

or BV

SS

SS

14

Note

Applies to the

PD70F3017AY only.

P

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3017AY

Table 1-1. Types of Pin I/O Circuits (2/2)

Pin Alternate Function I/O Circuit Type Recommended Connection of Unused Pins

DD

P90 LBEN/WRL

P91 UBEN

5 Input: Connect to BV

Output: Leave open

P92 R/W/WRH

P93 DSTB/RD

P94 ASTB

P95 HLDAK

P96 HLDRQ

P100 to

P107

P110 to

RTP0/A5 to RTP7/A12 26

A1 to A4 5-A

Input: Connect to V

Output: Leave open

DD

P113

P114 XT1 16

P120 WAIT 5 Input : Connect to BVDD or BV

Output: Leave open

REF

AV

CLKOUT

RESET

X2

XT2

PP

V

ðð

ð

ð

4 Leave open

2

ðð

ð

16 Leave open

Connect to AV

Leave open (when external clock i s i nput to X1 pin)

– – Connect to V

SS

SS

or BV

or V

SS

SS

SS

ð

Data Sheet U14527EJ2V0DS00

15

PPPP

Figure 1-1. Pin Input/Output Circuits (1/2)

PD70F3017A, 70F3017AY

Type 2

IN

Schmitt-triggered input with hysteresis characteristics

Type 4

V

DD

Data

P-ch

OUT

Output

disable

N-ch

Push-pull output that can be set for high-impedance output

(both P-ch and N-ch off)

Type 5-A

Pullup

enable

Data

Output

disable

Input

enable

Type 8-A

Pullup

enable

Data

Output

disable

V

V

DD

P-ch

N-ch

DD

P-ch

N-ch

V

DD

P-ch

IN/OUT

V

DD

P-ch

IN/OUT

Type 5

Data

Output

disable

Input

enable

V

DD

P-ch

N-ch

IN/OUT

Type 9

IN

P-ch

N-ch

Comparator

+

–

V

REF

(threshold voltage)

Input enable

16

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3017AY

Figure 1-1. Pin Input/Output Circuits (2/2)

Type 10-A Type 26

Pullup

enable

DD

V

Data

Open drain

Output disable

Type 16

Feedback cut-off

P-ch

P-ch

N-ch

V

DD

P-ch

Pullup

enable

Data

IN/OUT

Open drain

Output

disable

V

DD

P-ch

N-ch

V

DD

P-ch

IN/OUT

XT1 XT2

Data Sheet U14527EJ2V0DS00

17

2. ELECTRICAL SPECIFICATIONS

Absolute Maximum Ratings (TA = 25 °C, VSS = 0 V)

Parameter Symbol Conditions Ratings Unit

DD

AV

BV

AV

BV

V

DD

DD

SS

SS

Note 1

I1

V

Note 2

I2

V

I3

V

IAN

REF

OL

PP

V

K

X1, XT1, VDD = 2.7 to 3.6 V

(AV

Note 3

REF

AV

Per pin 4.0 mA

Total for P00 to P07, P10 to P15, P20 to

P25

Total for P26, P27, P30 to P37, P100 to

P107, P110 to P113

Total for P40 to P47, P90 to P96, P120,

CLKOUT

Total for P50 to P57, P60 to P65 25 mA

OH

Per pin –4.0 mA

Total for P00 to P07, P10 to P15, P20 to

P25

Total for P26, P27, P30 to P37, P100 to

P107, P110 to P113

Total for P40 to P47, P90 to P96, P120,

CLKOUT

Total for P50 to P57, P60 to P65 –25 mA

, V

Note 1

O1

V

, BV

Note 2

O2

V

A

Normal o perating mode –40 to +85

Flash memory programming mode 10 to 4 0

stg

Supply voltage

Input voltage

Clock input voltage V

Analog input voltage V

Analog reference input voltage A V

Output current, low I

Output current, high I

Storage temperature T

PPPP

PD70F3017A, 70F3 017AY

–0.5 to +4.6 V

–0.5 to +4.6 V

–0.5 to +4.6 V

–0.5 to +0.5 V

–0.5 to +0.5 V

–0.5 to V

–0.5 to BV

DD

DD

–0.5 to +8.5 V

–0.5 to V

DD

) –0.5 to AVDD + 0.5

DD

–0.5 to AVDD + 0.5

25 mA

25 mA

25 mA

–25 mA

–25 mA

–25 mA

DD

= 2.7 to 3.6 V –0.5 to VDD + 0.5

DD

= 2.7 to 3.6 V –0.5 to BVDD + 0.5

–40 to +125

+ 0.5

+ 0.5

+ 1.0

Note 4

Note 4

Note 4

Note 4

Note 4

Note 4

Note 4

V

V

V

V

V

VOutput voltage

V

COperating ambient temperature T

q

C

q

C

q

Notes 1.

18

Ports 0, 1, 2, 3, 10, 11, 12, RESET, and their alternate-function pins.

Ports 4, 5, 6, 9, CLKOUT, and their alternate-function pins.

2.

Ports 7, 8, and their alternate-function pins.

3.

Be sure not to exceed the absolute maximum ratings (MAX. value) of each supply voltage.

4.

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

Cautions 1. Do not directly connect the output (or I/O) pins of IC products to each other, or to VDD, VCC,

and GND. Open-drain pins or open-connector pins, however, can be directly connected to

each other. Direct connection of the output pins between an IC product and an external

circuit is possible, if the output pins can be set to the high-impedance state and the output

timing of the external circuit is designed to avoid output conflict.

2. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for

any parameter. That is, the absolute maximum ratings are rated values at which the product

is on the verge of suffering physical damage, and therefore the product must be used under

conditions that ensure that the absolute maximum ratings are not exceeded.

The ratings and conditions indicated for DC characteristics and AC characteristics represent

the quality assurance range during normal operation.

A

Capacitance (T

= 25 °C, VDD = VSS = 0 V)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input capacitance C

I/O capacitance C

Output capacitance C

I

fC = 1 MHz

Unmeasured pins returned to 0 V

IO

O

15 pF

15 pF

15 pF

Operating Conditions

Internal Operation Clock Frequency (I) Supply Voltage (VDD) Operating Ambient Temperature (TA)

2 MHz d fXX d 17 MHz 2.7 to 3.6 V –40 to +85 °C

2 MHz d fXX d 20 MHz 3.0 to 3.6 V –40 to +85 °C

fXT = 32.768 kHz 2.7 to 3.6 V –40 to +85 °C

Data Sheet U14527EJ2V0DS00

19

Recommended Oscillator

A

(1) Main system clock oscillator (T

= –40 to +85 °C)

(a) Connection of ceramic resonator or crystal resonator

X1 X2

Parameter Symbol Conditions MIN. TYP. MAX. Unit

µµµµ

PD70F3017A, 70F3 017AY

XX

VDD = 2.7 to 3.6 V 2 17 MHzOscillation frequency f

VDD = 3.0 to 3.6 V 2 20 MHz

Upon reset release 219/f

Upon STOP mode release

The TYP value differs depending on the setting of the oscillation stabilization time select register (OSTS).

Note

XX

Note

Caution Ensure that the duty of oscillation waveform is between 45% and 55%.

Remarks 1.

Connect the oscillator as close as possible to the X1 and X2 pins.

Do not route the wiring near broken lines.

2.

Sufficiently evaluate the matching between the oscillator and resonator.

3.

(b) External clock input

X1 X2

Open

High-speed CMOS inverter

External clock

sOscillation stabil ization time

s

Cautions 1. Connect the high-speed CMOS inverter as close as possible to the X1 pin.

2. Sufficiently evaluate the matching between the

PD70F3017A, 70F3017AY and the high-

µµµµ

speed CMOS inverter.

20

Data Sheet U14527EJ2V0DS00

(2) Subsystem clock oscillator (TA = –40 to +85 °C)

(a) Connection of crystal resonator

XT1 XT2

Parameter Symbol Conditions MIN. TYP. MAX. Unit

PPPP

PD70F3017A, 70F3 017AY

Oscillation frequency f

Oscillation stabil ization time 10 s

Remarks 1.

(b) External clock input

Cautions 1. Connect the high-speed CMOS inverter as close as possible to the XT2 pin.

Connect the oscillator as close as possible to the XT1 and XT2 pins.

Do not route the wiring near broken lines.

2.

Sufficiently evaluate the matching between the oscillator and resonator.

3.

2. Sufficiently evaluate the matching between the

speed CMOS inverter.

XT

XT1 XT2

32 32.768 35 kHz

High-speed CMOS inverter

PD70F3017A, 70F3017AY and the high-

PPPP

Data Sheet U14527EJ2V0DS00

21

DC Characteristics

PPPP

PD70F3017A, 70F3 017AY

(1) Operating Conditions (T

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input voltage, high

Input voltage, low

Output voltage, low

Output leakage current, high I

Output leakage current, low I

Supply current

Note 5

A

= –40 to +85 °C, VDD = AV

IH1

V

Pins other than below 0. 7V

Note 1

IH2

V

Note 2

IH3

V

IH4

V

X1, XT1 (P114), XT2 0.8V

IL1

V

Pins other than below V

Note 1

IL2

V

Note 2

IL3

V

IL4

V

X1, XT1 (P114), XT2 V

Note 3

OH1

V

Note 4

OH2

V

Note 3

OL1

V

Note 4

OL2

V

(Except pins P10

and P12)

OL3

P10, P12 IOL = 3 mA 0.4 V

V

LIH

VI = VDD = AVDD =

DD

BV

LIL

VI = 0 V

LOH

VO = VDD = AVDD = BV

LOL

VO = 0 V –5

DD1

I

Normal operation

DD2

I

HALT mode fXX = 17 MHz

DD3

I

IDLE mode

DD4

STOP mode (subsystem oscillator, watch

I

timer operating)

DD

OH

I

OH

I

OL

I

OL

I

DD

= BV

= 2.7 to 3.6 V, VSS = AVSS = BVSS = 0 V) (1/2)

0.7AV

0.75V

AV

V

= –3 mA 0.8V

= –1 mA 0.8V

DD

DD

DD

DD

SS

SS

SS

SS

DD

DD

DD

V

AV

DD

V

DD

V

0.3V

0.3AV

0.2V

0.2V

DD

DD

DD

DD

DD

= 1.6 mA 0.4 V

= 1.6 mA 0.4 V

5

X1, XT1, XT2 20

–5

X1, XT1, XT2 –20

DD

XX

= 17 MHz

f

30 60 mA

5

All peripheral

functions operating

10 25 mA

All peripheral

functions operating

XX

= 17 MHz

f

48mA

Watch timer

operating

10 100

V

V

V

V

V

V

V

V

VOutput voltage, high

V

AInput leakage current, high I

P

A

P

AInput leakage current, low I

P

A

P

A

P

A

P

A

P

22

STOP mode (subsystem oscillator

SS

stopped (XT1 = V

Data Sheet U14527EJ2V0DS00

))

2 100

A

P

PPPP

PD70F3017A, 70F3 017AY

(1) Operating Conditions (TA = –40 to +85 °C, VDD = AV

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Supply current

Pull-up resistance R

Notes 1.

Note 5

DD5

I

Subsystem clock normal operation mode

XT

= 32.768 kHz (main system clock

f

stopped)

DD6

I

Subsystem clock IDLE mode

XT

= 32.768 kHz (main system clock

f

stopped, watch timer operating)

L

VIN = 0 V 10 30 100 k

P70 to P77, P80 to P83, and their alternate-function pins.

P00 to P07, P10, P12, P13, P15, P20, P22, P23, P25 to P27, P30 to P33, P36, P37, RESET, and their

2.

alternate-function pins.

CLKOUT, P40 to P47, P50 to P57, P60 to P65, P90 to P96, P120, and their alternate-function pins.

3.

P00 to P07, P10 to P15, P20 to P27, P30 to P37, P100 to P107, P110 to P113, and their alternate-

4.

function pins.

DD

The TYP value of V

5.

is 3.3 V. The current consumed by the output buffer is not included.

DD

= BV

DD

= 2.7 to 3.6 V, VSS = AVSS = BVSS = 0 V) (2/2)

250 600

130 360

A

P

A

P

:

Data Sheet U14527EJ2V0DS00

23

PPPP

PD70F3017A, 70F3 017AY

(2) Operating Conditions (TA = –40 to +85 °C, VDD = AVDD = BVDD = 3.0 to 3.6 V, VSS = AVSS = BVSS = 0 V) (1/2)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Input voltage, high

Input voltage, low

Output voltage, low

Output leakage current, high I

Output leakage current, low I

Supply current

Note 5

IH1

V

Pins other than below 0. 7V

Note 1

IH2

V

Note 2

IH3

V

IH4

V

X1, XT1 (P114), XT2 0.8V

IL1

V

Pins other than below V

Note 1

IL2

V

Note 2

IL3

V

IL4

V

X1, X2, XT1 (P114), XT2 V

Note 3

OH1

V

Note 4

OH2

V

Note 3

OL1

V

Note 4

OL2

V

OH

= –3 mA 0.8V

I

OH

= –1 mA 0.8V

I

OL

= 1.6 mA 0.4 V

I

OL

= 1.6 mA 0.4 V

I

(Except pins P10

and P12)

OL3

P10, P12 IOL = 3 mA 0.4 V

V

LIH

VI = VDD = AVDD =

DD

BV

LIL

VI = 0 V

X1, XT1, XT2 20

X1, XT1, XT2 –20

LOH

LOL

DD1

I

DD

VO = V

VO = 0 V –5

Normal operation f

XX

= 20 MHz All

peripheral functions

operating

DD2

I

HALT mode

XX

= 20 MHz All

f

peripheral functions

operating

DD3

I

IDLE mode fXX = 20 MHz Watch

timer operating

DD4

I

STOP mode (subsystem oscillator, watch

timer operating)

STOP mode (subsystem oscillator

SS

stopped (XT1 = V

))

0.7AV

0.75V

SS

AV

SS

V

SS

DD

DD

DD

DD

SS

DD

DD

DD

V

AV

DD

V

DD

V

0.3V

0.3AV

0.2V

0.2V

5

V

DD

V

V

V

DD

V

DD

V

DD

V

DD

V

VOutput voltage, high

V

P

P

–5

P

P

5

P

P

32 64 mA

11 26 mA

4.5 9 mA

10 100

2 100

P

P

AInput leakage current, high I

A

AInput leakage current, low I

A

A

A

A

A

24

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

(2) Operating Conditions (TA = –40 to +85 °C, VDD = AVDD = BVDD = 3.0 to 3.6 V, VSS = AVSS = BVSS = 0 V) (2/2)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Supply current

Pull-up resistance R

Note 5

DD5

I

Subsystem clock normal operation mode

XT

= 32.768 kHz (main system clock

f

stopped)

DD6

I

Subsystem clock IDLE mode

XT

= 32.768 kHz (main system clock

f

stopped, watch timer operating)

L

VIN = 0 V 10 30 100 k

250 600

130 360

P

P

A

A

:

Notes 1.

P70 to P77, P80 to P83, and their alternate-function pins.

P00 to P07, P10, P12, P13, P15, P20, P22, P23, P25 to P27, P30 to P33, P36, P37, RESET and their

2.

alternate-function pins.

CLKOUT, P40 to P47, P50 to P57, P60 to P65, P90 to P96, P120, and their alternate-function pins.

3.

P00 to P07, P10 to P15, P20 to P27, P30 to P37, P100 to P107, P110 to P113, and their alternate-

4.

function pins.

DD

The TYP value of V

5.

is 3.3 V. The current consumed by the output buffer is not included.

Data Sheet U14527EJ2V0DS00

25

Data Retention Characteristics (TA = –40 to +85 °C)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

PPPP

PD70F3017A, 70F3 017AY

Data retention voltage V

Data retention current I

Supply voltage rise time t

Supply voltage fall time t

Supply voltage hold time

(from STOP mode setting)

STOP release signal input time t

Data retention high-level input voltage V

Data retention low-level input voltage V

Remarks 1.

TYP. values are reference values for when T

n = 1 to 4

2.

Setting STOP mode

V

DD

DDDR

DDDR

RVD

FVD

HVD

t

DREL

IHDR

ILDR

t

STOP mode 1.8 3.6 V

DDDR

V

[V] 2 100

200

200

0ms

0ms

All input ports V

IHn

All input ports 0 V

A

= 25 °C.

t

HVD

FVD

V

DDDR

t

RVD

t

DREL

V

DDDR

ILn

A

P

s

P

s

P

V

V

RESET

V

(input)

NMI, INTP0 to INTP3

(input)

IHDR

V

IHDR

NMI, INTP0 to INTP3 (input)

(when STOP mode is released

at rising edge)

V

ILDR

Caution Shifting to STOP mode and restoring from STOP mode must be performed at VDD = 2.7 V min.

(fXX = 17 MHz) and VDD = 3.0 V min. (fXX = 20 MHz), respectively.

26

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

AC Characteristics

AC Test Input Waveforms

(1) P11, P14, P21, P24, P34, P35, P100 to P107, P110 to P113, and their alternate-function pins

V

DD

0.7V

DD

0.7V

DD

Point of measurement

0.3V

0 V

DD

0.3V

DD

(2) P70 to P77, P80 to P83, and their alternate-function pins

AV

DD

0 V

0.7AV

0.3AV

DD

0.7AV

DD

Point of measurement

DD

0.3AV

DD

(3) P00 to P07, P10, P12, P13, P15, P20, P22, P23, P25 to P27, P30 to P33, P36, P37, RESET, and their

alternate-function pins

V

DD

0.75V

DD

0.75V

DD

Point of measurement

0.2V

0 V

DD

0.2V

DD

(4) X1, XT1 (P114), XT2

V

DD

0.8V

DD

0.8V

DD

Point of measurement

0.2V

0 V

DD

0.2V

DD

AC Test Output Measurement Points

0.8V

DD

Point of measurement

0.4 V

0.8V

0.4 V

DD

Data Sheet U14527EJ2V0DS00

27

PPPP

PD70F3017A, 70F3 017AY

Load conditions

DUT

(Device under test)

Caution If the load capacitance exceeds 50 pF due to the circuit configuration, bring the load capacitance

of the device to 50 pF or less by inserting a buffer or by some other means.

L

= 50 pF

C

28

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

Clock Timing

A

(1) Operating Conditions (T

= –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load

capacitance: CL = 50 pF)

Parameter S ym bol Conditions MIN. M AX . Unit

CYX

X1 input cycle 58.8 ns

XT1 input cycle

X1 input high-level width 26.4 ns

XT1 input high-level width

X1 input low-level width 26.4 ns

XT1 input low-level width

X1 input rise time t

X1 input fall time t

CLKOUT output cycle t

CLKOUT high-level width t

CLKOUT low-level width t

CLKOUT rise time t

CLKOUT fall time t

CYK

Remarks 1.

T = t

Ensure that the duty is between 45% and 55%.

2.

t

<1>

28.5

WXH

t

<2>

12.8

WXL

t

<3>

12.8

XR

<4>

XF

<5> 0.5 (t

CYK

<6> 58.8 ns 31.2 Ps

WKH

<7> 0.4t

WKL

<8> 0.4t

KR

<9> 10 ns

KF

<10> 10 ns

CYK

CYK

0.5 (t

WXH

t

WXH

t

– 10 ns

– 10 ns

– t

– t

CYX

CYX

WXL

WXL

–

)

–

)

P

P

P

ns

ns

s

s

s

A

(2) Operating Conditions (T

= –40 to +85 °C, VDD = BVDD = 3.0 to 3.6 V, VSS = BVSS = 0 V, Output pin load

capacitance: CL = 50 pF)

Parameter S ym bol Conditions MIN. M AX . Unit

CYX

X1 input cycle 50.0 ns

XT1 input cycle

X1 input high-level width 22.5 ns

XT1 input high-level width

X1 input low-level width 22.5 ns

XT1 input low-level width

X1 input rise time t

X1 input fall time t

CLKOUT output cycle t

CLKOUT high-level width t

CLKOUT low-level width t

CLKOUT rise time t

CLKOUT fall time t

CYK

Remarks 1.

T = t

Ensure that the duty is between 45% and 55%.

2.

t

<1>

28.5

WXH

t

<2>

12.8

WXL

t

<3>

12.8

XR

<4> 0.5 (t

WXH

t

XF

<5>

CYK

<6> 50.0 ns 31.2 Ps

WKH

<7> 0.4t

WKL

<8> 0.4t

KR

<9> 10 ns

KF

<10> 10 ns

CYK

CYK

0.5 (t

WXH

t

– 10 ns

– 10 ns

– t

– t

CYX

CYX

WXL

WXL

–

)

–

)

P

P

P

ns

ns

s

s

s

Data Sheet U14527EJ2V0DS00

29

Clock Timing

<1>

PPPP

PD70F3017A, 70F3 017AY

<2>

X1, XT1 (input)

<4> <5>

CLKOUT (output)

(1) Timing of pins other than CLKOUT, ports 4, 5, 6, and 9

A

= –40 to +85

(T

Parameter Symbol Conditions MIN. MAX. Unit

Output rise time t

Output fall time t

C, VDD = BVDD = 2.7 to 3.6 V, VSS = BV

qqqq

OR

<11> 20 ns

OF

<12> 20 ns

<3>

<6>

<7>

<9> <10>

SS

0 V, Output pin load capacitance: CL = 50 pF)

=

<8>

(2) Timing of pins other than CLKOUT, ports 4, 5, 6, and 9

(TA = –40 to +85

Parameter Symbol Conditions MIN. MAX. Unit

Output rise time t

Output fall time t

Output signal

C, VDD = BVDD = 3.0 to 3.6 V, VSS = BV

qqqq

OR

<11> 20 ns

OF

<12> 20 ns

0.8VDD

0.4 V 0.4 V

<12> <11>

SS

0 V, Output pin load capacitance: CL = 50 pF)

=

0.8V

DD

30

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

Bus Timing (CLKOUT Asynchronous)

A

= –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load capacitance: CL = 50 pF)

(T

Parameter Symbol Conditions MIN. MAX. Unit

Address setup time (to ASTBp)t

Address hold time (from ASTBp)t

Address float from DSTB

p

Data input setup time from address t

Data input setup time from DSTB

Delay time from ASTBp to DSTB

p

p

Data input hold time (from DSTBn)t

Address output time from DSTB

Delay time from DSTBn to ASTB

Delay time from DSTBn to ASTB

n

n

p

DSTB low-level width t

ASTB high-level width t

Data output time from DSTB

p

Data output setup time (to DSTBn)t

Data output hold time (from DSTBn)t

HLDRQ high-level width t

HLDAK low-level width t

Bus output delay time from HLDAK

n

Delay time from HLDRQp to HLDAK

Delay time from HLDRQn to HLDAK

SAST

<13> 0.5T – 15 ns

HSTA

<14> 0.5T – 15 ns

FDA

t

<15> 2 ns

SAID

<16> (2 + n)T – 25 ns

SDID

t

<17> (1 + n)T – 25 ns

DSTD

t

t

t

t

SAWT1

t

SAWT2

t

HAWT1

t

HAWT2

t

SSTWT1

t

SSTWT2

t

HSTWT1

t

HSTWT2

t

t

DHQHA1

t

p

DHQHA2

t

n

<18> 0.5T – 15 ns

HDID

<19> 0 ns

DDA

t

<20> (1 + i)T – 15 ns

DDST1

<21> 0.5T – 15 ns

DDST2

<22> (1.5 + i)T – 15 ns

WDL

<23> (1 + n)T – 15 ns

WSTH

<24> T – 15 ns

DDOD

<25> 15 ns

SODD

<26> (1 + n)T – 20 ns

HDOD

<27> T – 15 ns

<28> n t 1 1.5T – 25 nsWAIT setup time (to address)

<29> n t 1 (1.5 + n)T – 25 ns

<30> n t 1 (0. 5 + n)T nsWAIT hold time (from address)

<31> n t 1 (1. 5 + n)T ns

<32> n t 1 T – 25 nsWAIT setup time (to ASTBp)

<33> n t 1 (1 + n)T – 25 ns

<34> n t 1nTnsWAIT hold time (from ASTBp)

<35> n t 1 (1 + n)T ns

WHQH

<36> T + 10 ns

WHAL

<37> T – 15 ns

DHAC

<38> 0 ns

<39> (2n + 7.5)T + 25 ns

<40> 0.5T 1.5T + 25 ns

Remarks 1.

CPU

CPU

(f

T = 1/f

n: Number of wait clocks inserted in the bus cycle.

2.

: CPU operation clock frequency)

The sampling timing changes when a programmable wait is inserted.

i: Number of idle states inserted after the read cycle (0 or 1).

3.

The values in the above specifications are values for when clocks with a 5:5 duty ratio are input from

4.

X1.

Data Sheet U14527EJ2V0DS00

31

PPPP

PD70F3017A, 70F3 017AY

Bus Timing (CLKOUT Synchronous)

A

= –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load capacitance: CL = 50 pF)

(T

Parameter Symbol Conditions MIN. MAX. Unit

Delay time from CLKOUTn to address t

Delay time from CLKOUTn to address

DKA

<41> 0 19 ns

FKA

t

<42> –12 7 ns

float

Delay time from CLKOUTp to ASTB t

Delay time from CLKOUTn to DSTB t

Data input setup time (to CLKOUTn)t

Data input hold time (from CLKOUTn)t

Data output delay time from CLKOUT

WAIT setup time (to CLKOUTp)t

WAIT hold time (from CLKOUTp)t

HLDRQ setup time (to CLKOUTp)t

HLDRQ hold time (from CLKOUTp)t

Delay time from CLKOUTn to bus float t

Delay time from CLKOUTn to HLDAK t

Remark

The values in the above specifications are values for when clocks with a 5:5 duty ratio are input from X1.

DKST

<43> –12 7 ns

DKD

<44> –5 14 ns

SIDK

<45> 15 ns

HKID

<46> 5 ns

DKOD

t

n

<47> 19 ns

SWTK

<48> 15 ns

HKWT

<49> 5 ns

SHQK

<50> 15 ns

HKHQ

<51> 5 ns

DKF

<52> 19 ns

DKHA

<53> 19 ns

32

Data Sheet U14527EJ2V0DS00

Read Cycle (CLKOUT Synchronous/Asynchronous, 1 Wait)

T1 T2 TW T3

CLKOUT (output)

<41>

A16 to A21 (output),

A1 to A15 (output), Note

<16>

<42>

PPPP

PD70F3017A, 70F3 017AY

<45> <46>

AD0 to AD15 (I/O)

ASTB (output)

DSTB (output),

RD (output)

WAIT (input)

<13>

<24>

Address

<43>

<28>

<30>

<29>

<31>

Hi-Z

<14>

<44> <21>

<18>

<32> <48>

<15>

<17>

<49> <48> <49>

<34>

<33>

<35>

<23>

Data

<44>

<43>

<19>

<20>

<22>

Note R/W (output), UBEN (output), LBEN (output)

Remark WRL and WRH are high level.

Data Sheet U14527EJ2V0DS00

33

Write Cycle (CLKOUT Synchronous/Asynchronous, 1 Wait)

T1 T2 TW T3

CLKOUT (output)

<41>

A16 to A21 (output),

A1 to A15 (output), Note

<47>

PPPP

PD70F3017A, 70F3 017AY

AD0 to AD15 (I/O)

ASTB (output)

DSTB (output),

WRL (output),

WRH (output)

WAIT (input)

<13>

<24>

<43>

<28>

<30>

<29>

<31>

<14>

<44>

<32> <48>

<34>

<33>

<35>

<25>

<49> <48> <49>

<26>

<23>

DataAddress

<43>

<21>

<44>

<27><18>

34

Note R/W (output), UBEN (output), LBEN (output)

Remark RD is high level.

Data Sheet U14527EJ2V0DS00

Bus Hold

CLKOUT (output)

PPPP

PD70F3017A, 70F3 017AY

TH TH TH TI

HLDRQ (input)

HLDAK (output)

A16 to A19 (output), Note

A1 to A15 (output)

AD0 to AD15 (I/O)

<50> <51>

<50>

<36>

<53>

<39> <40>

<52>

Hi-Z

Data

Hi-Z

<53>

<38><37>

ASTB (output)

DSTB (output), RD (output),

WRL (output), WRH (output)

Remark R/W (output), UBEN (output), LBEN (output)

Hi-Z

Hi-Z

Data Sheet U14527EJ2V0DS00

35

PPPP

PD70F3017A, 70F3 017AY

Reset/Interrupt Timing

A

= –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load capacitance: CL = 50 pF)

(T

Parameter Symbol Conditions MIN. MAX. Unit

RESET high-level width t

RESET low-level width t

NMI high-level width t

NMI low-level width t

WRSH

<54> 500 ns

WRSL

<55> 500 ns

WNIH

<56> 500 ns

WNIL

<57> 500 ns

WITH

<58>

n = 0 to 3 (analog noise

500 nsINTPn high-level width t

elimination)

n = 4 to 6 (digital noise

3T + 20 ns

elimination)

Remark

Reset

Interrupt

T = 1/f

RESET (input)

WITL

<59>

n = 0 to 3 (analog noise

500 nsINTPn low-level width t

elimination)

n = 4 to 6 (digital noise

3T + 20 ns

elimination)

XX

<54> <55>

<56> <57>

36

NMI (input)

<58> <59>

INTPn (input)

Remark n = 0 to 6

Data Sheet U14527EJ2V0DS00

µµµµ

PD70F3017A, 70F3 017AY

TIn Input Timing

A

= –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load capacitance: CL = 50 pF)

(T

Parameter Symbol Conditions MIN. MAX. Unit

Note

sam

2T

2T

sam

+ 20

+ 20

Note

TIn0, TIn1 high-level width n = 0, 1

TIn high-level width

TIn0, TIn1 low-level width n = 0, 1

TIn low-level width

sam

(count clock cycle) can be selected as follows by setting the PRMn2 to PRMn0 bits of prescaler mode

T

Note

t

t

TIHn

TILn

<60>

n = 2 to 5 3T + 20 ns

<61>

n = 2 to 5 3T + 20 ns

register n, n1 (PRMn, PRMn1).

sam

When n = 0 (TM0): T

When n = 1 (TM1): T

However, when the TIn0 valid edge is selected as the count clock cycle, T

XX

Remark

T= 1/f

= 2T, 4T, 16T, 64T, 256T or 1/INTWTI cycle

sam

= 2T, 4T, 16T, 32T, 128T, or 256T cycle

sam

= 2T.

ns

ns

Tln

Remark n = 00, 01, 10, 11, 2 to 5

<60> <61>

Data Sheet U14527EJ2V0DS00

37

CSI Timing

A

(1) Master mode (T

= –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load capacitance:

CL = 50 pF)

Parameter Symbol Conditions MIN. MAX. Unit

KH1

KCY1

, t

SIK1

KSI1

KSO1

<62> 400 ns

KL1

<63> 140 ns

<64> 50 ns

<65> 50 ns

<66> 60 ns

SCKn cycle time t

SCKn high-/low-level width t

SIn setup time (to SCKnn)t

SIn hold time (from SCKnn)t

Delay time from SCKnp to SOn output t

PPPP

PD70F3017A, 70F3 017AY

Remark

(2) Slave mode (T

n = 0 to 2

A

= –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load capacitance:

CL = 50 pF)

Parameter Symbol Conditions MIN. MAX. Unit

KH2

KCY2

, t

SIK2

KSI2

KSO2

<62> 400 ns

KL2

<63> 140 ns

<64> 50 ns

<65> 50 ns

<66> 60 ns

<63> <63>

SCKn cycle time t

SCKn high-/low-level width t

SIn setup time (to SCKnn)t

SIn hold time (from SCKnn)t

Delay time from SCKnp to SOn output t

Remark

n = 0 to 2

SCKn (I/O)

<62>

<64>

<65>

38

SIn (input)

SOn (output)

Remark n = 0 to 2

Input data

<66>

Output data

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

UART Timing (TA = –40 to +85 °C, VDD = BVDD = 2.7 to 3.6 V, VSS = BVSS = 0 V, Output pin load capacitance:

CL = 50 pF)

Parameter Symbol Conditions MIN. MAX. Unit

ASCKn cycle time t

ASCKn high-level width t

ASCKn low-level width t

Remark

n = 0 or 1

ASCKn (input)

Remark n = 0 or 1

KCY13

<67> 200 ns

KH13

<68> 80 ns

KL13

<69> 80 ns

<67>

<68> <69>

Data Sheet U14527EJ2V0DS00

39

PPPP

PD70F3017A, 70F3 017AY

I2C Bus Mode (

A

= –40 to +85 °C, VDD = 2.7 to 3.6 V, VSS = 0 V)

(T

SCL clock frequency f

Bus-free time (between

PD70F3017AY only)

PPPP

CLK

BUF

t

<70> 4.7 – 1.3 –

stop/start conditions)

Hold time

SCL clock low-level width t

SCL clock high-level width t

Setup time for start/restart

Note 1

HD:STA

t

LOW

HIGH

SU:STA

t

<71> 4.0 – 0.6 –

<72> 4.7 – 1.3 –

<73> 4.0 – 0.6 –

<74> 4.7 – 0.6 –

condition

HD:DAT

t

<75>

time

CBUS

compatible

master

2

C mode

I

Data setup time t

SDA and SCL signal rise

SU:DAT

R

t

<76> 250 –

<77> – 1,000

time

SDA and SCL signal fall

F

t

<78> – 300

time

Stop condition setup time t

Capacitance load of each

SU:STO

<79> 4.0 – 0.6 –

Cb – 400 – 400 pF

bus line

Normal Mode High-Speed ModeParameter Symbol

Unit

MIN. MAX. MIN. MAX.

0 100 0 400 kHz

P

P

P

P

P

5.0–––

0

Note 2

–

Note 2

0

Note 4

100

20 + 0.1Cb

20 + 0.1Cb

Note 5

Note 5

Note 3

0.9

–ns

300 ns

300 ns

P

P

P

s

s

s

s

s

sData hold

s

s

Notes 1.

Remark

At the start condition, the first clock pulse is generated after the hold time.

The system requires a minimum of 300 ns hold time internally for the SDA signal in order to occupy the

2.

undefined area at the falling edge of SCL.

LOW

If the system does not extend the SCL signal low hold time (t

3.

HD:DAT

(t

) needs to be satisfied.

The high-speed mode I

4.

2

C bus can be used in the normal-mode I2C bus system. In this case, set the

), only the maximum data hold time

high-speed mode I2C bus so that it meets the following conditions.

If the system does not extend the SCL signal's low state hold time:

x

SU:DAT

t 250 ns

t

If the system extends the SCL signal's low state hold time:

x

Transmit the following data bit to the SDA line prior to the SCL line release (t

2

250 = 1,250 ns: Normal mode I

Cb: Total capacitance of one bus line (unit: pF)

5.

C bus specification).

The maximum operating frequency of the

PD70F3017AY is 17 MHz.

P

Rmax.

+ t

SU:DAT

= 1,000 +

40

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

I2C Bus Mode (

PD70F3017AY only)

PPPP

SCL (I/O)

<78>

<71>

SDA (I/O)

<70>

Stop

condition

Start

condition

A/D Converter

A

= –40 to +85 °C, VDD = AVDD = AV

(T

CL = 50 pF)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

<72>

<73

<77>

<75>

<77> <78>

<76>

<74>

<71> <79>

Restart

condition

REF

= 2.7 to 3.6 V, VSS = AVSS = 0 V, Output pin load capacitance:

Stop

condition

Resolution 10 10 10 bit

Overall error

Conversion time t

Zero-scale error

Full-scale error

Integral linearity error

Differential linearity error

Analog reference voltage AV

Analog input voltage V

REF

AV

Power supply current AI

Notes 1.

Remark

Note 1

CONV

Note 1

Note 1

Note 2

Note 2

REF

AV

IAN

current AI

REF

DD

Excluding quantization error (r0.05% FSR).

Excluding quantization error (r0.5 LSB)

2.

LSB: Least Significant Bit

REF = AVDD

0.8 %FSR

r

5 100

0.4 %FSR

r

0.4 %FSR

r

4LSB

r

4LSB

r

2.7 3.6 V

AV

SS

AV

REF

360 500

13mA

P

P

FSR: Full Scale Range

s

V

A

Data Sheet U14527EJ2V0DS00

41

Flash Memory Programming Mode

Write/erase characteristics (TA = 10 to 40

Parameter Symbol Conditions MIN. TYP. MAX. Unit

C, VDD = 3.0 to 3.6 V)

qqqq

PPPP

PD70F3017A, 70F3 017AY

Unit erase time t

Total erase time t

Number of rewrites

Note

I

I

I

I

V

V

DDW

PPW

DDE

PPE

ER

ERT

PP0

PP1

When VPP = V

When VPP = V

During normal operation 0 0.2V

In flash memory programming mode 7.5 7.8 8.1 V

PP1

PP1

VDD pin 67 mAWrite current

VPP pin 100 mA

VDD pin 67 mAErase current

VPP pin 200 mA

0.2 0.2 0.2 s

20 s

20 Times

DD

VVPP supply voltage

Operating frequency 2 20 MHz

Write/erase is regarded as one cycle.

Note

Operations of the

PD70F3017A and 70F3017AY are unpredictable if flash memory is rewritten more than

P

20 times.

42

Data Sheet U14527EJ2V0DS00

3. PACKAGE DRAWINGS

100-PIN PLASTIC LQFP (FINE PITCH) (14x14)

A

B

75 51

76

µµµµ

PD70F3017A, 70F3 017AY

50

detail of lead end

S

C D

Q

R

100

1

25

F

G

H

M

I

P

SN

L

NOTE

Each lead centerline is located within 0.08 mm of

its true position (T.P.) at maximum material condition.

26

J

K

S

M

ITEM MILLIMETERS

A

16.00±0.20

B

14.00±0.20

C 14.00±0.20

D

16.00±0.20

F 1.00

G

1.00

H 0.22

I 0.08

J

K

L

M 0.17

N

P

Q

R3°

S 1.60 MAX.

S100GC-50-8EU, 8EA-2

+0.05

−0.04

0.50 (T.P.)

1.00±0.20

0.50±0.20

+0.03

−0.07

0.08

1.40±0.05

0.10±0.05

+7°

−3°

Data Sheet U14527EJ2V0DS00

43

121-PIN PLASTIC FBGA (12x12)

µµµµ

PD70F3017A, 70F3 017AY

INDEX MARK

Sey

E

Sy1

φ

b

A2

M

φ

SwB

D

A

A1

SxAB

SwA

S

ZD

ZE

A

NMLKJHGFEDCBA

B

13

12

11

10

9

8

7

6

5

4

3

2

1

ITEM MILLIMETERS

12.00±0.10

D

E 12.00±0.10

w 0.20

A

1.48±0.10

A1

0.35±0.06

A2

1.13

e 0.80

b 0.50

x

y

y1

ZD

ZE

+0.05

−0.10

0.08

0.10

0.20

1.20

1.20

P121F1-80-EA6

44

Data Sheet U14527EJ2V0DS00

µµµµ

PD70F3017A, 70F3 017AY

4. RECOMMENDED SOLDERING CONDITIONS

The µPD70F3017A and 70F3017AY should be soldered and mounted under the following recommended

conditions.

For the details of the recommended soldering conditions, refer to the document

Technology Manual (C10535E).

For soldering methods and conditions other than those recommended below, contact your sales representative.

Table 4-1. Surface Mounting Type Soldering Conditions

Semiconductor Device Mounting

PD70F3017AGC-8EU: 100-pin plastic LQFP (fine-pitch) (14

(1)

µµµµ

PD70F3017AYGC-8EU: 100-pin plastic LQFP (fine-pitch) (14

µµµµ

Soldering Method Soldering Condit i ons Recommended

Infrared reflow Package peak temperature: 235 °C, Time: 30 seconds max. (at 210 °C or higher),

Count: Two times or less

Exposure limit: 7 days

VPS Package peak temperature: 215 °C, Time: 40 seconds max. (at 200 °C or higher),

Count: Two times or less

Exposure limit: 7 days

Partial heating Pin temperature: 300 °C max., Time: 3 seconds max. (per pin row) –

After opening the dry pack, store it at 25 °C or less and 65% RH or less for the allowable storage period.

Note

Note

(after that, prebake at 125 °C for 10 hours)

Note

(after that, prebake at 125 °C for 10 hours)

14 mm)

××××

14 mm)

××××

Condition

Symbol

IR35-107-2

VP15-107-2

Caution Do not use different soldering methods together (except for partial heating).

PD70F3017AF1-EA6: 121-pin plastic FBGA (12

(2)

µµµµ

PD70F3017AYF1-EA6: 121-pin plastic FBGA (12

µµµµ

Soldering Method Soldering Condit i ons

12 mm)

××××

12 mm)

××××

Recommended

Condition

Symbol

Infrared reflow Package peak temperature: 235 °C, Time: 30 seconds max. (at 210 °C or higher),

Count: Two times or less

Exposure limit: 7 days

Partial heating Pin temperature: 300 °C max., Time: 3 seconds max. (per pin row) –

After opening the dry pack, store it at 25 °C or less and 65% RH or less for the allowable storage period.

Note

Note

(after that, prebake at 125 °C for 10 hours)

Data Sheet U14527EJ2V0DS00

IR35-107-2

45

PPPP

PD70F3017A, 70F3 017AY

NOTES FOR CMOS DEVICES

1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and

ultimately degrade the device operation. Steps must be taken to stop generation of static electricity

as much as possible, and quickly dissipate it once, when it has occurred. Environmental control

must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using

insulators that easily build static electricity. Semiconductor devices must be stored and transported

in an anti-static container, static shielding bag or conductive material. All test and measurement

tools including work bench and floor should be grounded. The operator should be grounded using

wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need

to be taken for PW boards with semiconductor devices on it.

2 HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided

to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence

causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels

of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused

DD

pin should be connected to V

being an output pin. All handling related to the unused pins must be judged device by device and

related specifications governing the devices.

or GND with a resistor, if it is considered to have a possibility of

3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS

does not define the initial operation status of the device. Immediately after the power source is

turned ON, the devices with reset function have not yet been initialized. Hence, power-on does

not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the

reset signal is received. Reset operation must be executed immediately after power-on for devices

having reset function.

Caution The

PD70F3017AY contains an I2C bus interface circuit.

PPPP

Purchase of NEC I

these components in an I2C system, provided that the system conforms to the I2C Standard

Specification as defined by Philips.

2

C components conveys a license under the Philips I2C Patent Rights to use

46

Data Sheet U14527EJ2V0DS00

PPPP

PD70F3017A, 70F3 017AY

Regional Information

Some information contained in this document may vary from country to country. Before using any NEC

product in your application, pIease contact the NEC office in your country to obtain a list of authorized

representatives and distributors. They will verify:

•

Device availability

•

Ordering information

•

Product release schedule

•

Availability of related technical literature

•

Development environment specifications (for example, specifications for third-party tools and

components, host computers, power plugs, AC supply voltages, and so forth)

•

Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary

from country to country.

NEC Electronics Inc. (U.S.)

Santa Clara, California

Tel: 408-588-6000

800-366-9782

Fax: 408-588-6130

800-729-9288

NEC Electronics (Germany) GmbH

Duesseldorf, Germany

Tel: 0211-65 03 02

Fax: 0211-65 03 490

NEC Electronics (UK) Ltd.

Milton Keynes, UK

Tel: 01908-691-133

Fax: 01908-670-290

NEC Electronics Italiana s.r.l.

Milano, Italy

Tel: 02-66 75 41

Fax: 02-66 75 42 99

NEC Electronics (Germany) GmbH

Benelux Office

Eindhoven, The Netherlands

Tel: 040-2445845

Fax: 040-2444580

NEC Electronics (France) S.A.

Velizy-Villacoublay, France

Tel: 01-30-67 58 00

Fax: 01-30-67 58 99

NEC Electronics (France) S.A.

Madrid Office

Madrid, Spain

Tel: 91-504-2787

Fax: 91-504-2860

NEC Electronics (Germany) GmbH

Scandinavia Office

Taeby, Sweden

Tel: 08-63 80 820

Fax: 08-63 80 388

NEC Electronics Hong Kong Ltd.

Hong Kong

Tel: 2886-9318

Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd.

Seoul Branch

Seoul, Korea

Tel: 02-528-0303

Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd.

United Square, Singapore

Tel: 65-253-8311

Fax: 65-250-3583

NEC Electronics Taiwan Ltd.

Taipei, Taiwan

Tel: 02-2719-2377

Fax: 02-2719-5951

NEC do Brasil S.A.

Electron Devices Division

Guarulhos-SP Brasil

Tel: 55-11-6462-6810

Fax: 55-11-6462-6829

Data Sheet U14527EJ2V0DS00

J00.7

47

PPPP

PD70F3017A, 70F3017AY

Reference document Electrical Characteristics for Microcomputer (IEI-601)

Note

Note This document number is that of the Japanese version.

Related document

PD703014A, 703014AY, 703015A, 703015AY, 703017A, 703017AY Data Sheet (U14526E)

P

V850 Family and V850/SA1 are trademarks of NEC Corporation.

•

The information in this document is current as of August, 2000. The information is subject to

change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or

data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all

products and/or types are available in every country. Please check with an NEC sales representative

for availability and additional information.

•

No part of this document may be copied or reproduced in any form or by any means without prior

written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

•

NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of

third parties by or arising from the use of NEC semiconductor products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC or others.

•

Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of customer's equipment shall be done under the full

responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third

parties arising from the use of these circuits, software and information.

•

While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

•

NEC semiconductor products are classified into the following three quality grades:

"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products

developed based on a customer-designated "quality assurance program" for a specific application. The

recommended applications of a semiconductor product depend on its quality grade, as indicated below.

Customers must check the quality grade of each semiconductor product before using it in a particular

application.

"Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio

and visual equipment, home electronic appliances, machine tools, personal electronic equipment

and industrial robots

"Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster

systems, anti-crime systems, safety equipment and medical equipment (not specifically designed

for life support)

"Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life

support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's

data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not

intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness

to support a given application.

(Note)

(1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for

NEC (as defined above).

M8E 00. 4

Loading...

Loading...