NEC UPD4990AG Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD4990A

SERIAL I/O CALENDAR & CLOCK

CMOS LSI

The µPD4990A is a CMOS LSI developed to input/output calendar & clock data serially to/from the micro computer.

The crystal frequency is 32.768 kHz and the data items included are time, minute, second, year, month, day, and

week.

FEATURES

Built-in counters for time (hour, minute, and second) and date (year, month, day, and week)

•

Leap years are adjusted automatically.

•

Data is represented in BCD notation (except months in hexadecimal notation) and input/output serially.

•

Commands can be set by inputting serial data.

•

Selective timing pulses (TPs) are 64 Hz, 256 Hz, 2 048 Hz, and 4 096 Hz and selective output intervals are 1, 10,

•

30, and 60 seconds.

ORDERING INFORMATION

PART No. PACKAGE

µ

PD4990AC 14-pin plastic DIP (300 mil)

µ

PD4990AG 16-pin plastic SOP (300 mil)

CONNECTION DIAGRAM (Top View)

114

C

2

C

1

C

0

STB

CS

DATA IN

GND

(V

SS

)

213

312

411

510

69

7

PD4990AC

µ

V

X

X

OUT ENBL

TP

DATA OUT

CLK

8

DD

TAL

TAL

(+)

C

2

C

1

C

0

NC

STB

CS

DATA IN

GND

(V

SS

)

NC: NO CONNECTION

116

215

314

413

512

611

7

89

PD4990AG

µ

10

DD

(+)

V

X

TAL

X

TAL

NC

OUT ENBL

TP

DATA OUT

CLK

Document No. IC-1755 (1st edition)

Date Published March 1997 P

Printed in Japan

©

1989

µ

PD4990A

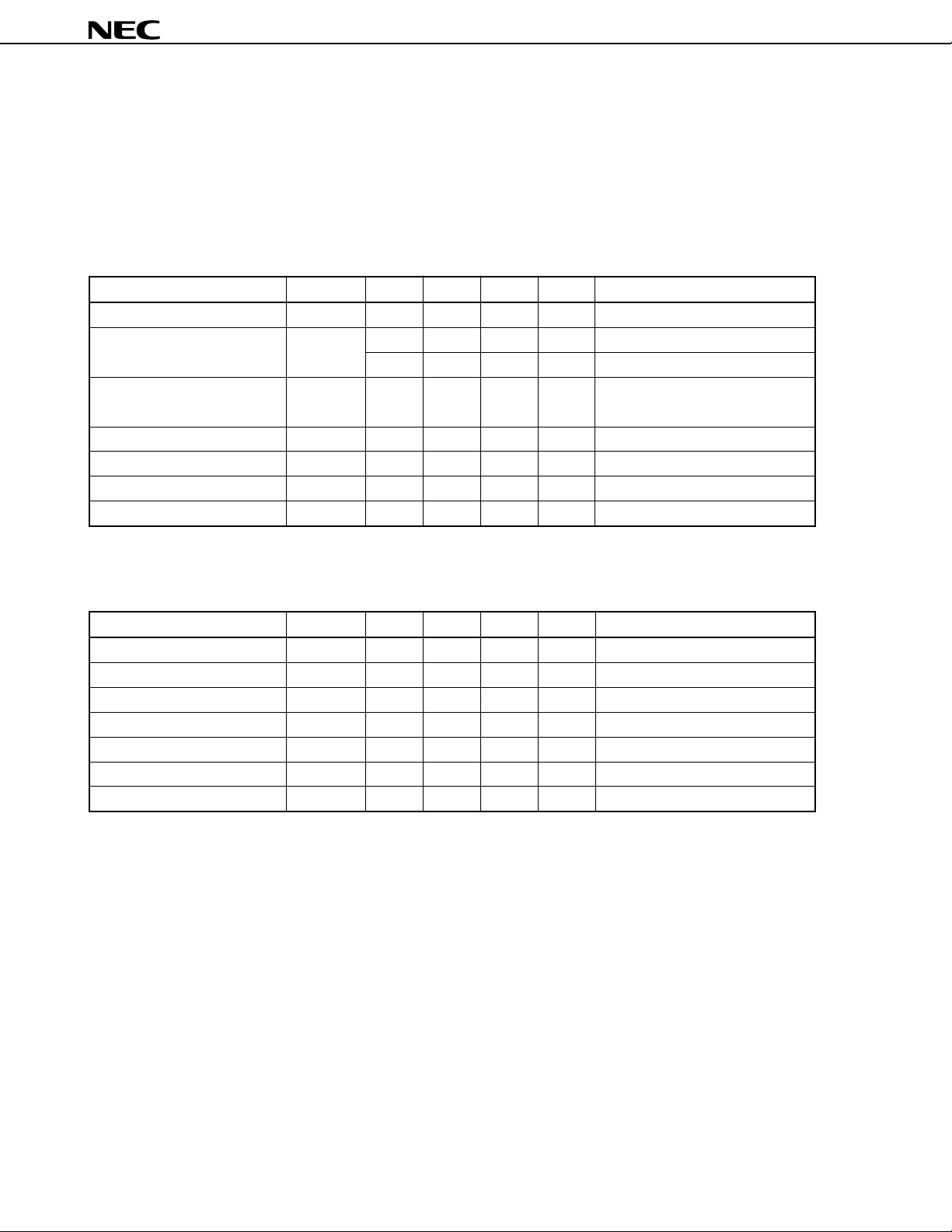

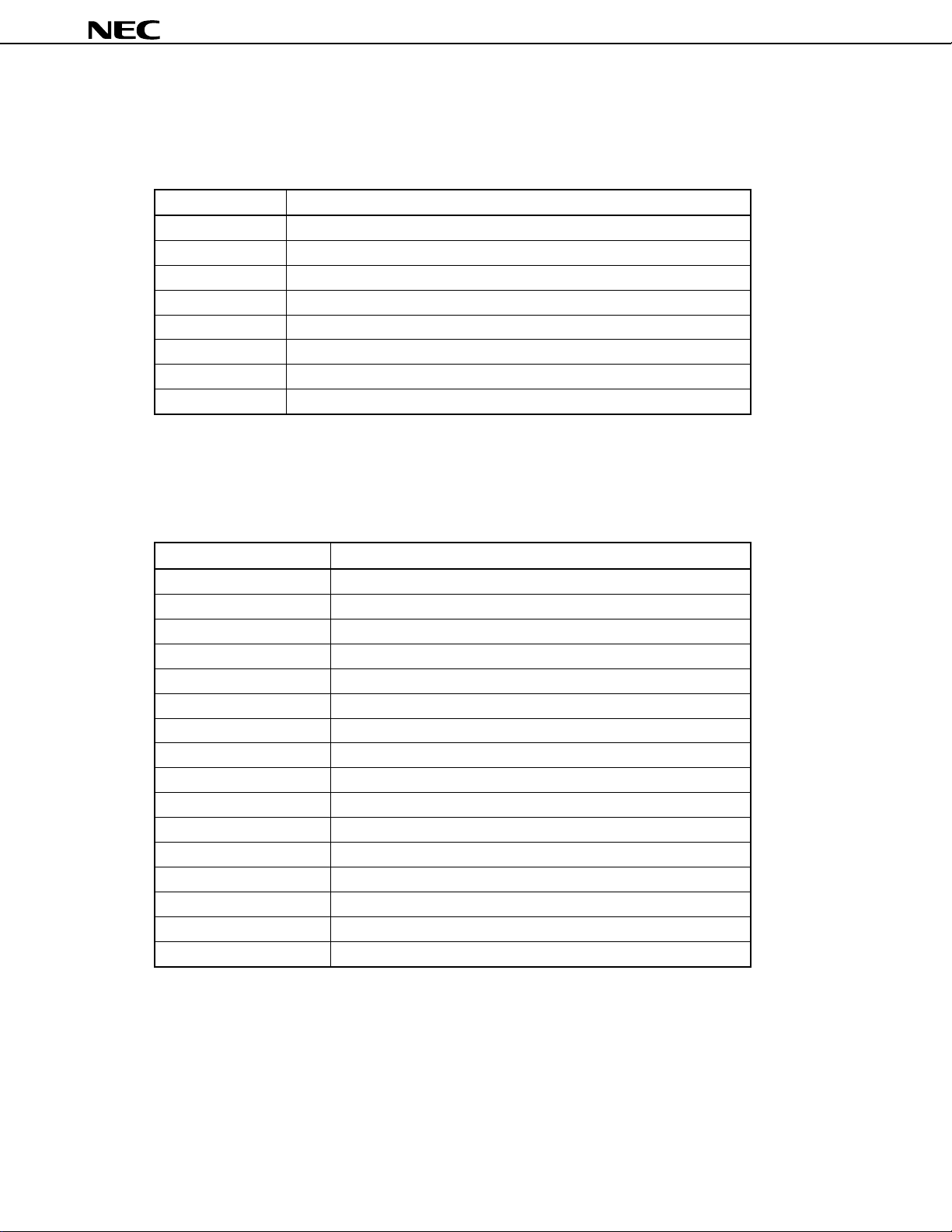

ABSOLUTE MAXIMUM RATINGS

Supply Voltage VDD − VSS −0.5 to 7.0 V

Input Voltage V

Operating Temperature Range T

Storage Temperature Range T

Output Terminal Voltage V

IN VSS −0.3 to VDD +0.3 V

opt −40 to +85 °C

stg −65 to +125 °C

OUT −0.5 to 7.0 V

ELECTRICAL CHARACTERISTICS (f = 32.768 kHz, CG = CD = 20 pF, CI = 20 kΩ, Ta = 25 °C)

CHARACTERISTIC SYMBOL MIN. TYP. MAX. UNIT TEST CONDITIONS

Operating Voltage VDD − VSS 2.00 5.50 V

Current Consumption IDD

Low Level Output Voltage V OL 0.4* V

CLK Input Frequency fCLK DC 500 kHz VDD − VSS = 2.0 V, Duty 50 %

Input Leakage Current IIN ±1

High Level Input Voltage VIH 0.7 VDD VDD V

Low Level Input Voltage VIL VSS 0.3 VDD V

820

100

µ

AVDD − VSS = 3.60 V

µ

AVDD − VSS = 5.50 V

VDD − VSS = 2.0 to 5.5 V

IOL = 500 µA

µ

AVDD − VSS = 5.50 V

* TP and DATA OUT are N-channel open drain output.

A.C. ELECTRICAL CHARACTERISTICS (f = 32.768 kHz, VDD − VSS = 2.0 V, Ta = 25 °C)

CHARACTERISTIC SYMBOL MIN. TYP. MAX. UNIT TEST CONDITIONS

C0 to 2, CS − STB Set-up Time tSU 1

STB Pulse Width tSTB 1

C0 to 2, CS − STB Hold Time tHLD 1

STB LATCH Delay Time td1 1**

CLK-DATA OUT Delay time td(c-o) 1

DATA IN Set-up Time tDSU 1

DATA IN Hold Time tDHLD 1

** Note: When a function mode is Time Read mode (other than Test mode), STB LATCH delay time is 20 µs MAX.

d2).

(t

µ

s

µ

s

µ

s

µ

s except Time Read mode

µ

sRL = 33 kΩ, CL = 15 pF

µ

s

µ

s

2

OE

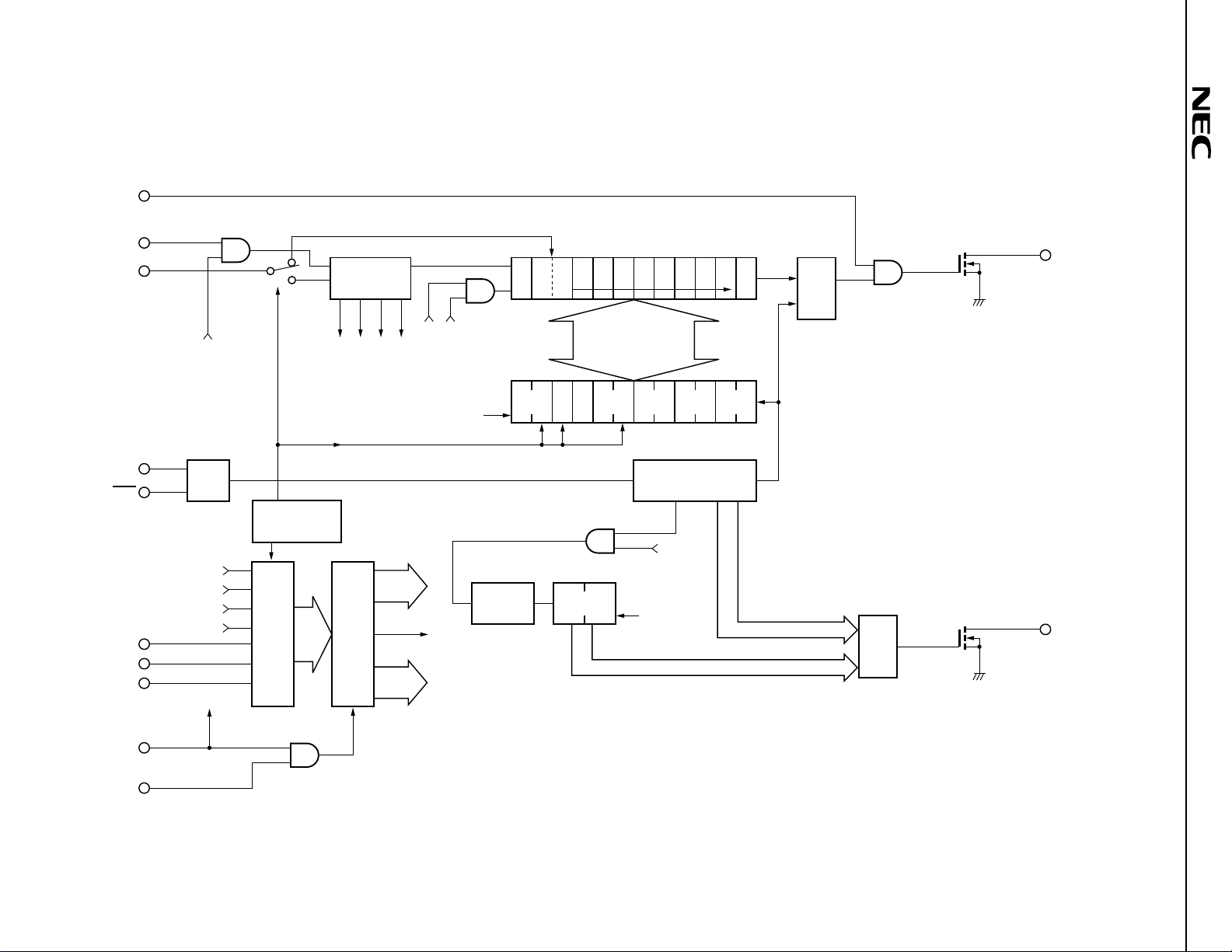

BLOCK DIAGRAM

CLK

DATA

IN

X

TAL

X

TAL

C

C

C

CS

STB

CLK

COMMAND

Register

48 Bit Shift Register

MPX

OPEN DRAIN

DATA

OUT

CLK RH

N-ch

CS

3'C2'C1'C0

'

PS

MON

-TH

D/W

HOUR MINYEAR DAY SEC

1 Hz

C

Time counter

15 Stage Binary Divider

15

OSC

1/2

Select signal

generator circuit

64 Hz

STOP

C3'

2

'

C

C

1

'

C

0

'

2

1

0

DATA SELECTOR

DECODER

TEST

1/2

1 Hz

6

SEC

RESET

TP

MPX

MPX

:

Multiplexer

PS

:

D/W

CS

TP

RH

Preset

:

Day of the Week

:

Chip Select

:

Timing Pulse

:

Register Hold

µ

PD4990A

3

FUNCTION SPECIFICATIONS

Crystal frequency (X tal osc.).

•

32.768 kHz

°

Data

•

Data types are: second, minute, day, week, month, and year.

Leap years, 31-day months, and months with 30 or less days are adjusted automatically.

A 24-hour system is used and last two digits of Gregorian year are indicated.

It is assumed that leap years are expressed by multiples of 4.

Data format

•

Data is represented in BCD notation. Only months are represented in hexadecimal notation.

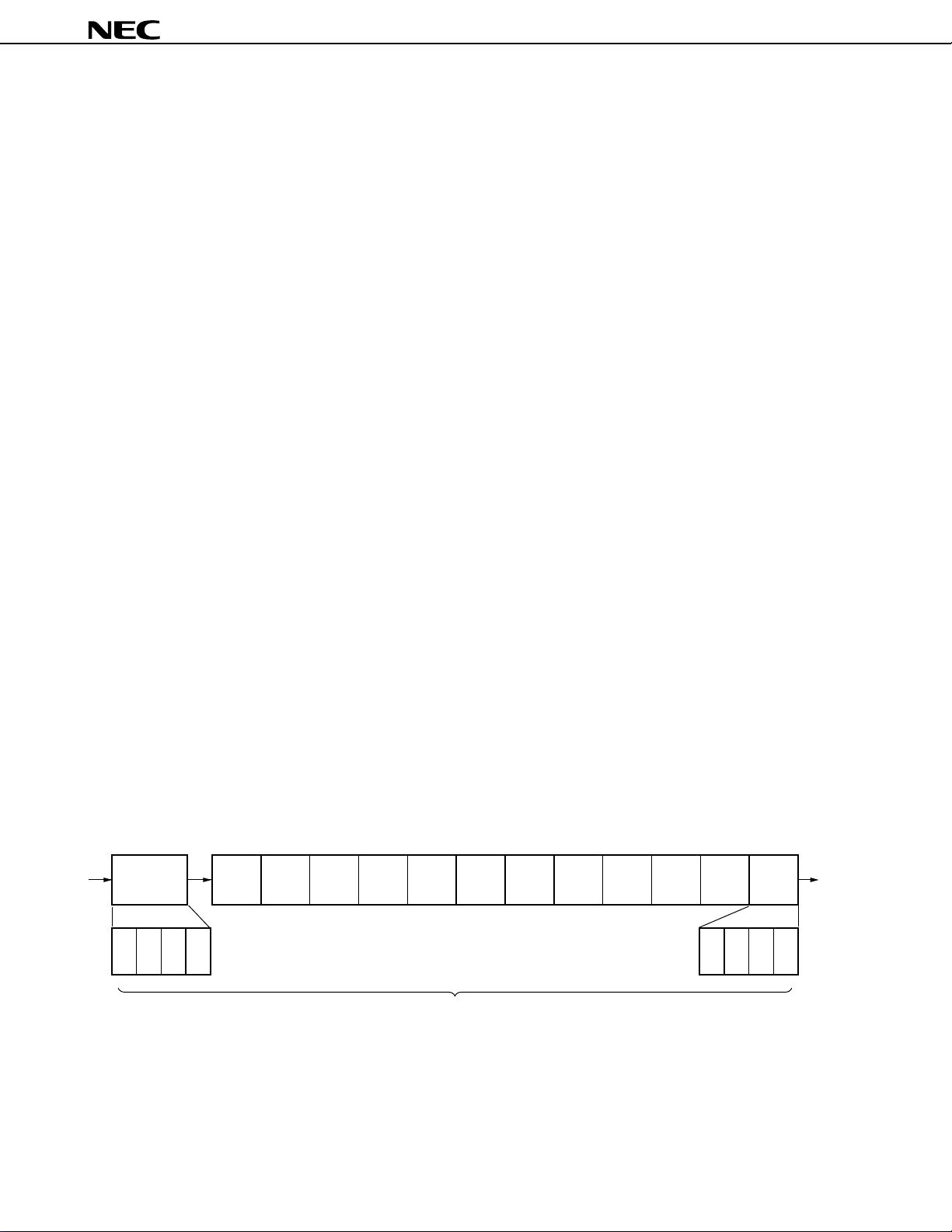

Data input-output and Clock

•

Data is input/output synchronously with reference to the external clocks input from the CLK pin using the serial

input/output system. (See Fig. 1.)

Timing pulse output

•

Three frequencies, 64 Hz, 256 Hz, and 2 048 Hz, can be set with C

Using serial data input command, selective timing pulses (TPs) are 64 Hz, 256 Hz, 2 048 Hz, and 4 096 Hz

and selective output intervals are 1, 10, 30, and 60 seconds.

0, C1 and C2 pins.

µ

PD4990A

Function mode selection

•

A function mode can be selected by the inputs from C

serial data input. (C

0 = C1 = C2 = VDD)

0, C1, and C2. Also a function mode can be selected through

Each command is latched with STB (strobe).

Chip select

•

Connecting the CS pin to the ground level inhibits CLK and STB inputs.

Data output inhibition

•

Connecting the OUT ENBL pin to the ground level sets the DATA OUT pin at high impedance.

Figure 1.

command

register

C

3

'

C2'C1'C0' D3D2D1D

Ten's of

* DATA of 52 Bit Shift Register appears on DATA OUT terminal from LSB of second.

year

Unit of

year

month

day of

the week

Ten's of

days

52 Bit Shift Register

Unit of

days

Ten's of

hours

Unit of

hours

Ten's of

minutes

Unit of

minutes

Ten's of

seconds

LSBMSB

Unit of

seconds

0

4

TERMINALS

Input terminals

•

DATA IN Data input of 40-/52-bit shift register

°

CLK Shift clock input of 40-/52-bit shift register

°

C0, C1, C2 Command input (3 bit)

°

STB Strobe input

°

CS Chip select input (Prohibits CLK & STB)

°

OUT ENBL Output control input (Makes the DATA OUT high impedance by inputting low level).

°

Output terminals (N-channel Open Drain)

•

DATA OUT Data output of 40-/52-bit shift register

°

TP Timing pulse output

°

Oscillation terminals

•

XTAL Oscillation inverter input (OSC IN)

°

XTAL Oscillation inverter output (OSC OUT)

°

Power supply terminals

•

VDD Plus power supply

°

GND (VSS) Common line

°

µ

PD4990A

5

COMMAND SPECIFICATIONS

Commands input from C0, C1, and C2 pins (1 ...H, 0 ...L)

°

Shift register 40 bit (The year function is ineffective.)

µ

(Operates as the existing

C2 C1 C0 FUNCTION

0 0 0 Register Hold DATA OUT = 1 Hz

0 0 1 Register Shift DATA OUT = [LSB] = 0 or 1

0 1 0 Time Set & Counter Hold DATA OUT = [LSB] = 0 or 1

0 1 1 Time Read DATA OUT = 1 Hz

1 0 0 TP = 64 Hz

1 0 1 TP = 256 Hz

1 1 0 TP = 2 048 Hz

1 1 1 Serial command transfer mode

* The test mode is cancelled by [C2, C1, C0] = [0, 0, 0] to [1, 1, 0].

Serial data commands

°

2, C1, C0] = [1, 1, 1] at all time.

Set [C

Shift register 52 bit (The year function is effective.)

PD1990AC in other than test mode)

µ

PD4990A

C3'C2'C1'C0' FUNCTION

0 0 0 0 Register Hold DATA OUT = 1 Hz

0 0 0 1 Register Shift DATA OUT = [LSB] = 0 or 1

0 0 1 0 Time Set & Counter Hold DATA OUT = [LSB] = 0 or 1

0 0 1 1 Time Read DATA OUT = 1 Hz

0 1 0 0 TP = 64 Hz

0 1 0 1 TP = 256 Hz

0 1 1 0 TP = 2 048 Hz

0 1 1 1 TP = 4 096 Hz

1 0 0 0 TP = 1 s interval set (counter reset & start)

1 0 0 1 TP = 10 s interval set (counter reset & start)

1 0 1 0 TP = 30 s interval set (counter reset & start)

1 0 1 1 TP = 60 s interval set (counter reset & start)

1 1 0 0 Interval Output Flag Reset

1 1 0 1 Interval Timer Clock Run

1 1 1 0 Interval Timer Clock Stop

1 1 1 1 TEST MODE SET

When serial data commands are used, C0, C1, and C2 pins should be connected VDD pin.

6

Loading...

Loading...