NEC MC-4516CB646EF-A80, MC-4516CB646PF-A10, MC-4516CB646PF-A80, MC-4516CB646EF-A10 Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

MC-4516CB646

16M-WORD BY 64-BIT SYNCHRONOUS DYNAMIC RAM MODULE

UNBUFFERED TYPE

Description

The MC-4516CB646 is a 16,777,216 words by 64 bits synchronous dynamic RAM module on which 8 pieces of

128M SDRAM: µPD45128841 are assembled.

This module provides high density and large quantities of memory in a small space without utilizing the surfacemounting technology on the printed circuit board.

Decoupling capacitors are mounted on power supply line for noise reduction.

Features

• 16,777,216 words by 64 bits organization

• Clock frequency and access time from CLK

Part number /CAS latency Clock frequency Access time from CLK

(MAX.) (MAX.)

MC-4516CB646EF-A80 CL = 3 125 MHz 6 ns

CL = 2 100 MHz 6 ns

MC-4516CB646EF-A10 CL = 3 100 MHz 6 ns

CL = 2 77 MHz 7 ns

MC-4516CB646PF-A80 CL = 3 125 MHz 6 ns

★

CL = 2 100 MHz 6 ns

MC-4516CB646PF-A10 CL = 3 100 MHz 6 ns

★

CL = 2 77 MHz 7 ns

• Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

• Pulsed interface

• Possible to assert random column address in every cycle

• Quad internal banks controlled by BA0 and BA1 (Bank Select)

• Programmable burst-length (1, 2, 4, 8 and full page)

• Programmable wrap sequence (sequential / interleave)

• Programmable /CAS latency (2, 3)

• Automatic precharge and controlled precharge

• CBR (Auto) refresh and self refresh

• All DQs have 10 Ω ±10 % of series resistor

• Single 3.3 V ± 0.3 V power supply

• LVTTL compatible

• 4,096 refresh cycles/64 ms

• Burst termination by Burst Stop command and Precharge command

• 168-pin dual in-line memory module (Pin pitch = 1.27 mm)

• Unbuffered type

• Serial PD

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M14334EJ2V0DS00 (2nd edition)

Date Published January 2000 NS CP(K)

Printed in Japan

The mark

••••

shows major revised points.

©

1999

Ordering Information

MC-4516CB646

Part number Clock frequency

MHz (MAX.)

MC-4516CB646EF-A80 125 MHz 168-pin Dual In-line Memory Module 8 pieces of µPD45128841G5 (Rev. E)

MC-4516CB646EF-A10 100 MHz (Socket Type) (10.16 m m (400) TSOP (II))

MC-4516CB646PF-A80 125 MHz Edge connector : Gold plated 8 pieces of µPD45128841G5 (Rev. P)

★

★

MC-4516CB646PF-A10 100 MHz 34.93 mm height (10.16 mm (400) TSOP (II))

Package Mounted devices

2

Data Sheet M14334EJ2V0DS00

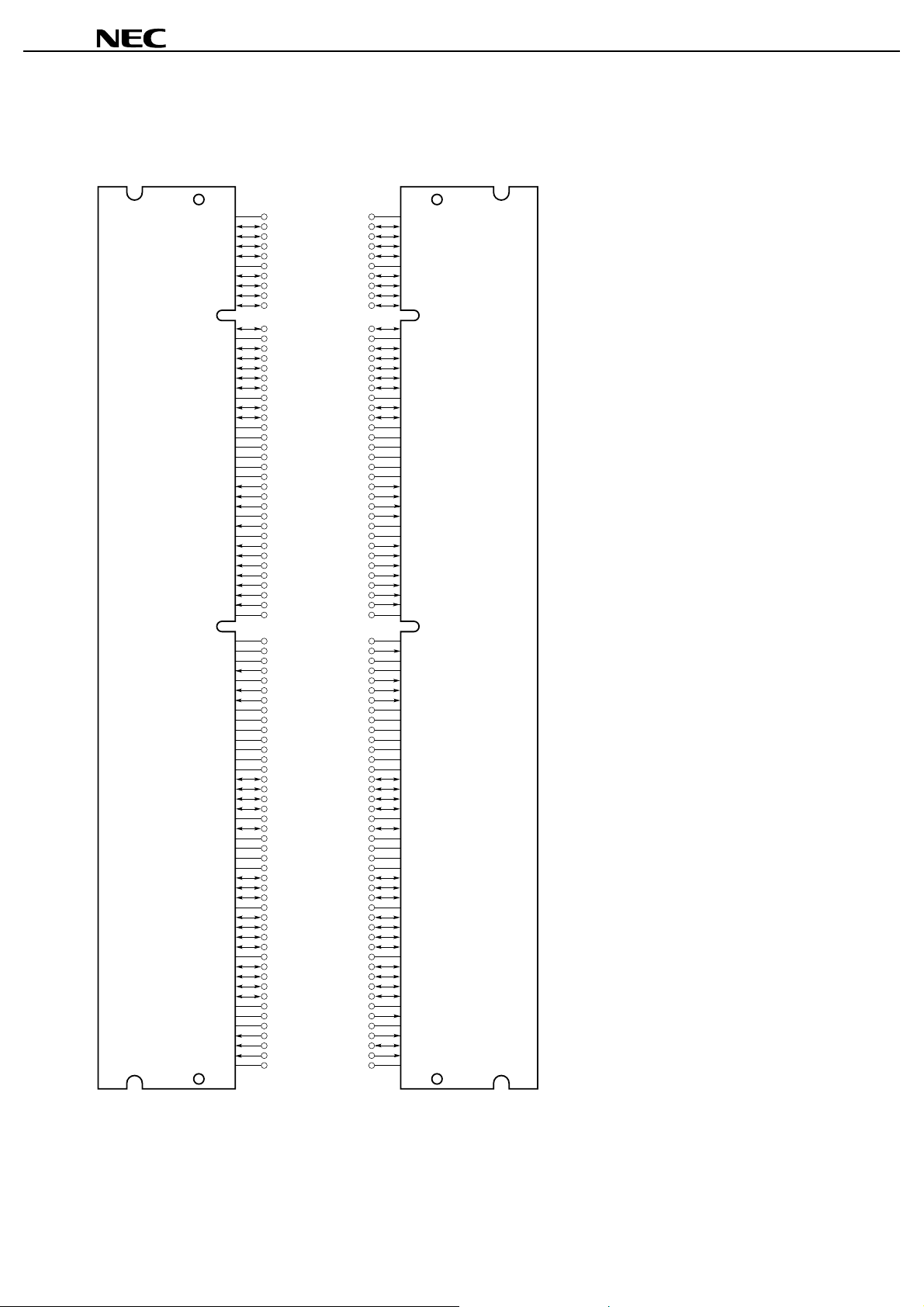

Pin Configuration

★

168-pin Dual In-line Memory Module Socket Type (Edge connector: Gold plated)

MC-4516CB646

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

SS

V

DQ32

DQ33

DQ34

DQ35

Vcc

DQ36

DQ37

DQ38

DQ39

DQ40

V

SS

DQ41

DQ42

DQ43

DQ44

DQ45

Vcc

DQ46

DQ47

NC

NC

V

SS

NC

NC

Vcc

/CAS

DQMB4

DQMB5

NC

/RAS

V

SS

A1

A3

A5

A7

A9

BA0

(A13)

A11

Vcc

CLK1

NC

V

SS

CKE0

NC

DQMB6

DQMB7

NC

Vcc

NC

NC

NC

NC

V

SS

DQ48

DQ49

DQ50

DQ51

Vcc

DQ52

NC

NC

NC

V

SS

DQ53

DQ54

DQ55

SS

V

DQ56

DQ57

DQ58

DQ59

Vcc

DQ60

DQ61

DQ62

DQ63

V

SS

CLK3

NC

SA0

SA1

SA2

Vcc

DQMB0

DQMB1

BA1

DQMB2

DQMB3

V

DQ0

DQ1

DQ2

DQ3

Vcc

DQ4

DQ5

DQ6

DQ7

DQ8

V

DQ9

DQ10

DQ11

DQ12

DQ13

Vcc

DQ14

DQ15

NC

NC

V

NC

NC

Vcc

/WE

/CS0

NC

V

A10

(A12)

Vcc

Vcc

CLK0

V

NC

/CS2

NC

Vcc

NC

NC

NC

NC

V

DQ16

DQ17

DQ18

DQ19

Vcc

DQ20

NC

NC

NC

V

DQ21

DQ22

DQ23

V

DQ24

DQ25

DQ26

DQ27

Vcc

DQ28

DQ29

DQ30

DQ31

V

CLK2

NC

WP

SDA

SCL

Vcc

SS

SS

SS

SS

A0

A2

A4

A6

A8

SS

SS

SS

SS

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

/xxx indica tes active low signal.

A0 - A11 : Address Inputs

[Row: A0 - A11, Column: A0 - A9]

BA0

(A13), BA1 (A12) : SDRAM Bank Select

DQ0 - DQ63 : Data Inputs/Outputs

CLK0 - CLK3 : Clock Input

CKE0 : Clock Enable Input

/CS0, /CS2 : Chip Select Input

/RAS : Row Address Strobe

/CAS : Column Address Strobe

/WE : Write Enable

DQMB0

-

DQMB7 : DQ Mask Enable

SA0 - SA2 : Address Input for EEPROM

SDA : Serial Data I/O for PD

SCL : Clock Input for PD

CC

V

SS

V

: Power Supply

: Ground

WP : Write Protect

NC : No Connection

Data Sheet M14334EJ2V0DS00

3

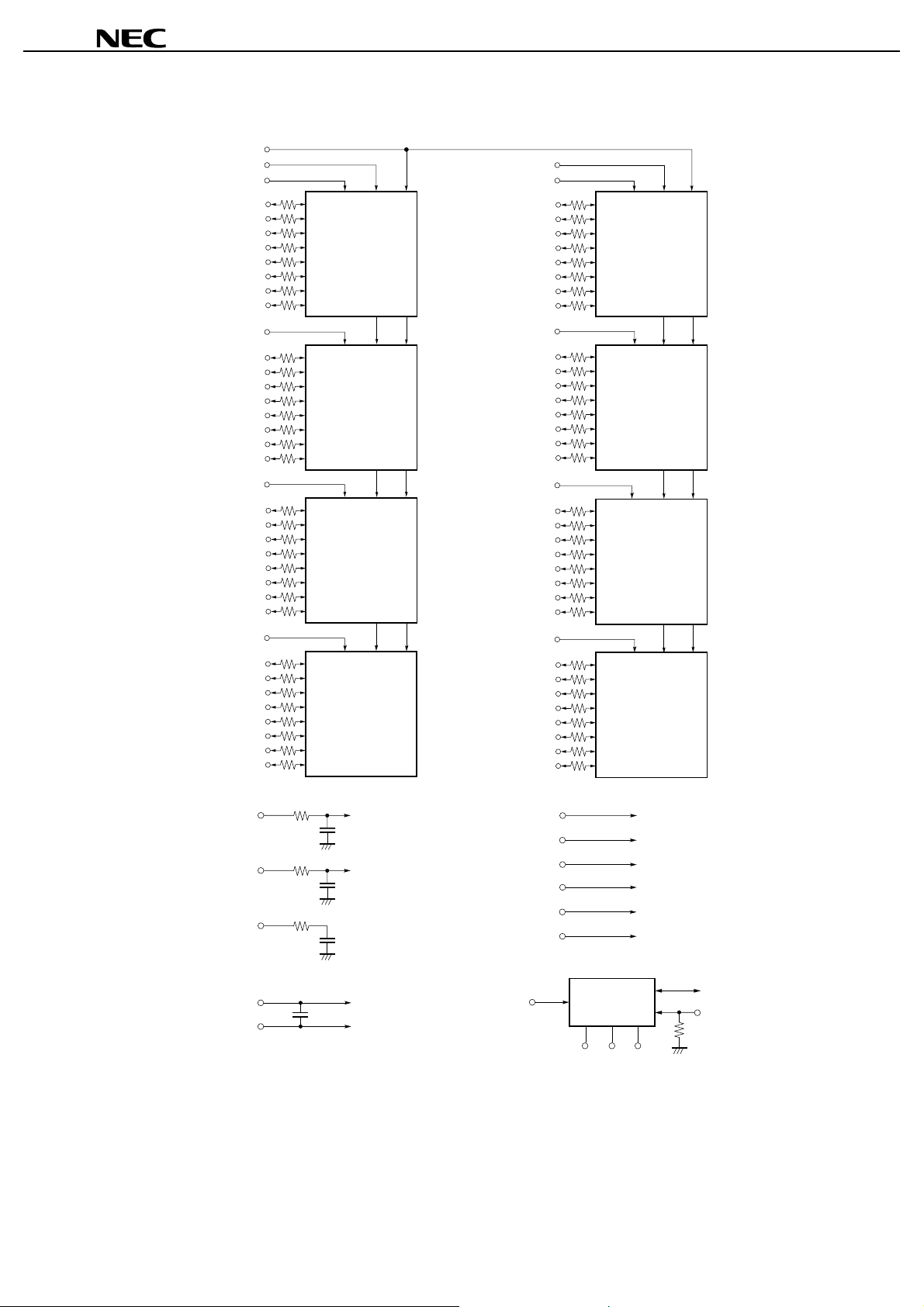

Block Diagram

/WE

/CS0

DQMB0

DQ 0

DQ 1

DQ 2

DQ 3

DQ 4

DQ 5

DQ 6

DQ 7

DQ 7

DQ 6

DQ 5

DQ 4

DQ 3

DQ 2

DQ 1

DQ 0

DQM

MC-4516CB646

/CS2

DQMB2

/WE

/CS

D0

DQ 16

DQ 17

DQ 18

DQ 19

DQ 20

DQ 21

DQ 22

DQ 23

DQMD2/CS /WE

DQ 7

DQ 6

DQ 5

DQ 4

DQ 3

DQ 2

DQ 1

DQ 0

DQMB1

DQ 8

DQ 9

DQ 10

DQ 11

DQ 12

DQ 13

DQ 14

DQ 15

DQMB4

DQ 32

DQ 33

DQ 34

DQ 35

DQ 36

DQ 37

DQ 38

DQ 39

DQMB5

DQ 40

DQ 41

DQ 42

DQ 43

DQ 44

DQ 45

DQ 46

DQ 47

DQ 7

DQ 6

DQ 5

DQ 4

DQ 3

DQ 2

DQ 1

DQ 0

DQ 4

DQ 7

DQ 6

DQ 5

DQ 3

DQ 2

DQ 1

DQ 0

DQ 5

DQ 7

DQ 6

DQ 4

DQ 3

DQ 2

DQ 1

DQ 0

DQM

/CS

D1

DQM /CS

D4

DQM

/CS

D5

/WE

/WE

/WE

DQMB3

DQ 24

DQ 25

DQ 26

DQ 27

DQ 28

DQ 29

DQ 30

DQ 31

DQMB6

DQ 48

DQ 49

DQ 50

DQ 51

DQ 52

DQ 53

DQ 54

DQ 55

DQMB7

DQ 56

DQ 57

DQ 58

DQ 59

DQ 60

DQ 61

DQ 62

DQ 63

DQ 4

DQ 7

DQ 6

DQ 5

DQ 3

DQ 2

DQ 1

DQ 0

DQ 7

DQ 6

DQ 5

DQ 4

DQ 3

DQ 2

DQ 1

DQ 0

DQ 7

DQ 6

DQ 5

DQ 4

DQ 3

DQ 2

DQ 1

DQ 0

DQM

DQM

DQM

/WE

/CS

D3

/WE

/CS

D6

/CS

/WE

D7

Remarks 1.

4

CLK0

CLK2

CLK1, CLK3

V

V

CC

SS

CLK : D0, D1, D4, D5

3.3 pF

CLK : D2, D3, D6, D7

3.3 pF

10 pF

D0 - D7

C

D0 - D7

The value of all resistors is 10 Ω except WP.

2.

D0 - D7:

µ

PD45128841 (4M words × 8 bits × 4 banks)

Data Sheet M14334EJ2V0DS00

A0 - A11

SCL

BA0

BA1

/RAS

/CAS

CKE0

SERIAL PD

A0

SA1 SA2

SA0

A1 A2

A0 - A11 : D0 - D7

A13 : D0 - D7

A12 : D0 - D7

/RAS : D0 - D7

/CAS : D0 - D7

CKE : D0 - D7

SDA

WP

47 kΩ

MC-4516CB646

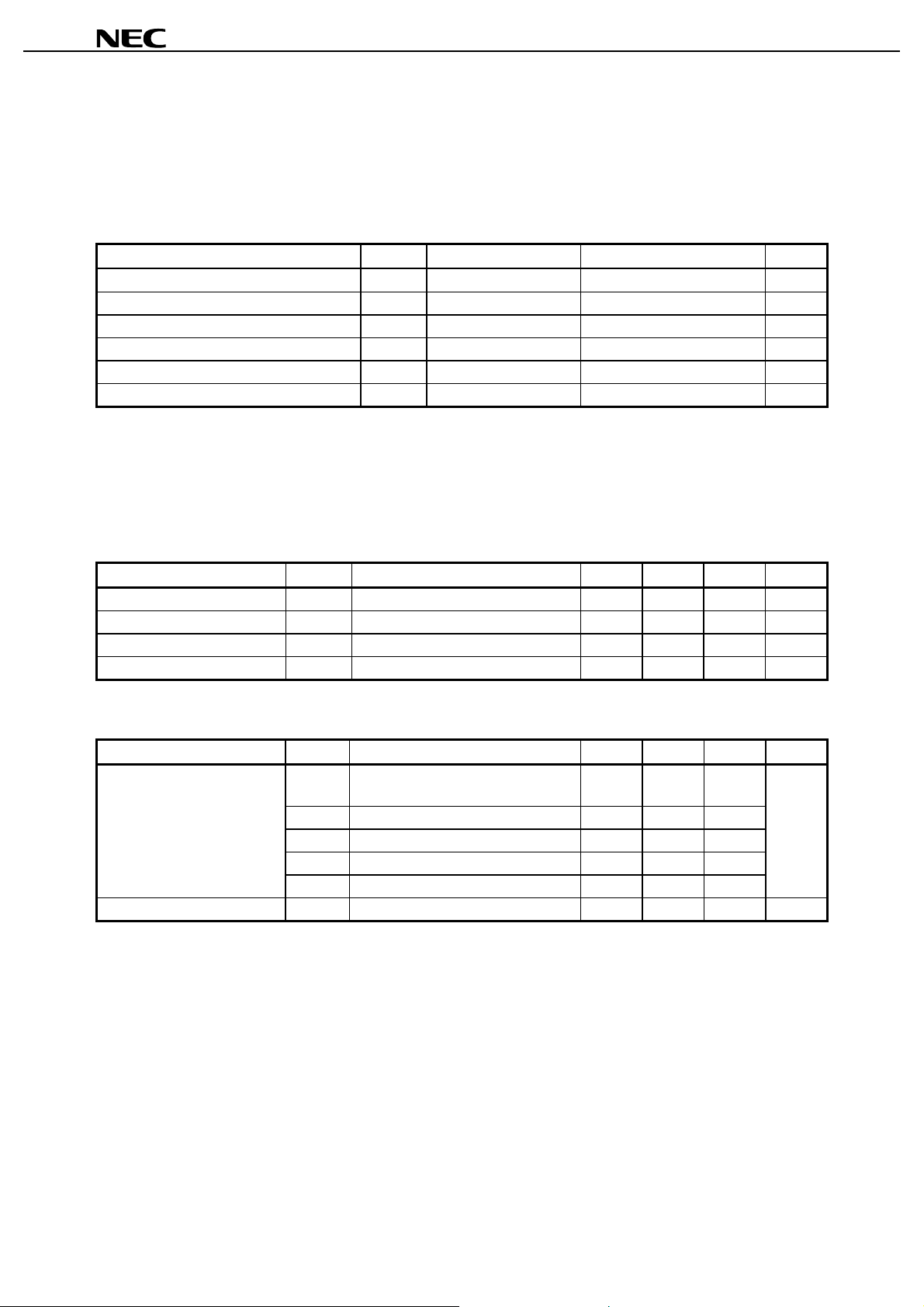

Electrical Specifications

• All voltages are referenced to VSS (GND).

µ

• After power up, wait more than 100

device operation is achieved.

Absolute Maximum Ratings

Parameter Symbol Condition Rating Unit

Voltage on power supply pin relative to GND V

Voltage on input pin relative to GND V

Short circuit output c urrent I

Power dissipation P

Operating ambient tem perature T

Storage temperature T

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause

permanent damage. The device is not meant to be operated under conditions outside the limits

described in the operational section of this specification. Exposure to Absolute Maximum Rating

conditions for extended periods may affect device reliability.

s and then, execute power on sequence and CBR (Auto) refresh before proper

CC

T

O

D

A

stg

–0.5 to +4.6 V

–0.5 to +4.6 V

50 mA

8W

0 to +70

–55 to +125

C

°

C

°

Recommended Operating Conditions

Parameter Symbol Condition MIN. TYP. MAX. Unit

Supply voltage V

High level input voltage V

Low level input voltage V

Operating ambient tem perature T

Capacitance (TA = 25

C, f = 1 MHz)

°°°°

Parameter Symbol Test condition MIN. TYP. MAX. Unit

Input capacitance C

Data input/output capaci t ance C

CC

IH

IL

A

I1

I2

C

I3

C

I4

C

I5

C

I/O

3.0 3.3 3.6 V

2.0 VCC + 0.3 V

0.3 +0.8 V

−

A0 - A11, BA0(A13), BA1(A12), /RAS,

070

38 62 pF

°

/CAS, /WE

CLK0, CLK2 24 40

CKE0 32 52

/CS0, /CS2 17 29

DQMB0 - DQMB7 7 13

DQ0 - DQ63 7 13 pF

C

Data Sheet M14334EJ2V0DS00

5

Loading...

Loading...