NEC Enterprise Server

NEC Express5800/1000 Series

NEC Express580 0 /1000 Technology Guide Vo l.1

Powered by t h e D u a l - C o r e I n tel® Itanium® Processor

NEC Express5800/1000 Series

Reliability and Perfor m ance th rough

3

the f usion of the N EC “A

” chipset and

the Dual-Core I ntel

®

It aniu m® processor

1320Xf/1160Xf 1080Rf

In t o day’s fas t-pac e d b u s iness en v ironm e n t, all e n terpris e s , f rom th e w orld’s larg e s t

com p a nies to t h e small e s t d epend on I T. E nter p r i se resou r c e plann i n g ( E R P ) , custo m e r

re l a tions h ip manag e m e nt ( CRM ) , a nd busin e s s inte l ligenc e ( BI ) a l l r e quir e t h at tra n s a c tion s

are q u ickly pr o c e s sed and th a t the res u l ting d a t a i s reli a b le as to m e e t t he requ i rement s o f the

rap i d ly chan g i ng busi n e s s e nvi r o nment . T h e n eed for hi g her perform a n c e and bette r r eliab i lity

is g r owing e x ponent i ally in e n terpri s e I T platfo r m s.

Pe o p le no lon g e r c onsid e r m a infr a m e syste m s a nd vec t o r superc o m pute r s a s o p e n ente r p r ise

IT p l a t forms. H o wev e r if one we r e able to h ave s u p e rcomp u ter perform a n c e and main f rame

re l i abili t y f or the co s t o f an open se r ve r i n a datac e n ter, many m a y recon s i d er.

Next generation enterprise IT platform

NEC Enterprise Server

Express5800/1000 series

Le veragi n g N EC’s ve c t or supe r c o mpute r a n d mainf r a me tech n o logy, Expre s s 5 8 0 0 /10 0 0 s e r ies

is d e s i gned to m e e t the re q u i remen t o f today ’s m i s sion cr i t ical ent e r prises .

Wit h t he new D u a l - C ore In t el

th i r d genera t ion chi p s et “A

com p r omise d t o reali z e mainf r a m e - class re l i abili t y a n d superc o m pute r-cla s s p e r f o rmance .

®

Itanium® pro c e s s or 900 0 series a n d t he NEC d e s i gned

3

”, fro m c h ipset , b o ard to s y stem - l evel d e s ign, NE C h as nev e r

Expr e s s 5 80 0 /10 0 0 s e r ies is th e p e r f e ct IT pla t f o r m for th e m o st deman d i ng mis s i o n criti c a l

enterprises.

Supercomputer-class Performance

• High processing power by the Dual-Core Intel® Itanium® processor:

Dual-Core, massive L3 cache and EPIC (Explicitly Parallel Instruction Computing) architecture

• Very Large Cache (VLC) Architecture:

High-speed / low latency Intra-Cell cache-to-cache data transfer

• Dedicated Cache Coherency Interface (CCI):

High-speed / low latency Inter-Cell cache-to-cache data transfer

• Crossbar-less configuration (Available only on 1080Rf):

Improved data transfer latency through direct attached Cell configuration

Flexibility and Operability

• Resource virtualization through Floating IO:

Flexible resource management allows for robust server virtualization

• Multi-OS Support / Rich application lineup:

Supports Windows® and Linux operating systems

• Superior standard chassis configuration:

Small footprint and highly scalable IO

2

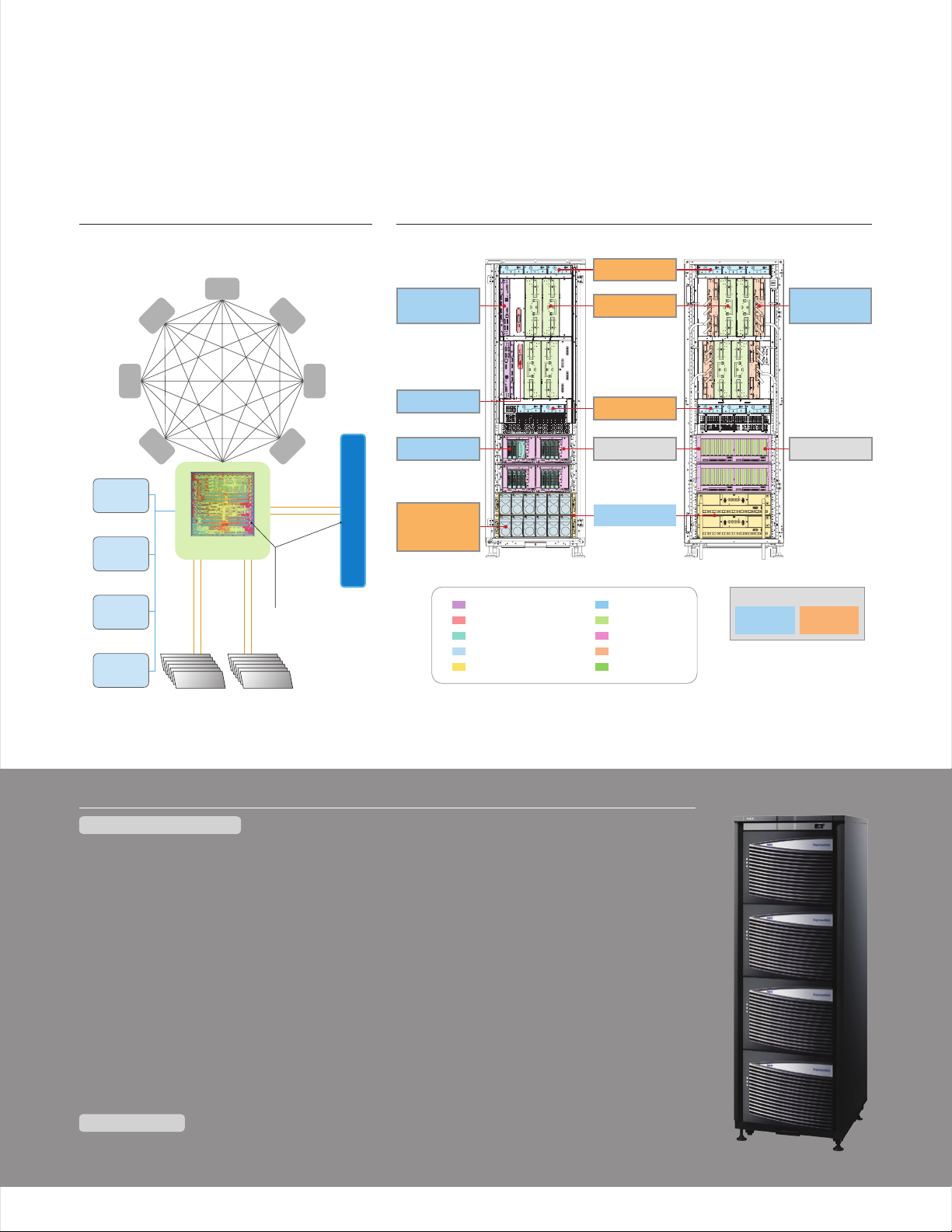

Increased inter-Cell data transfer speeds

Cell

Cell

Cell

Cell

Cell

Cell

Cell

High-speed crossb ar

Memory Memory

A3 Chipset

Processor

Processor

Processor

Processor

Cell Controller

Cache Coherenc y Inter face ( CCI)

Direct data transfer of large cache data

Internal Connections of the

n

Exp ress58 0 0/1000 Ser i es

System Hardware Layout of the Express5800/1000

n

Ser ies Server ( 1 320Xf)

Fan box

Service

Processor *

Clock card *

HDD Bay

Power

Distribution

Unit (PDU)

1

1

Service Processor

Clock card

HDD Bay

Power Distribution Unit

Power Bay

Ce ll ca rd

* R ed un da nt

configuration

available

Fan box

PCI box

* R ed un da nt

configuration

available

Power Bay

Fan box

Cell card

PCI box

Crossbar card

PCI slots

Crossbar

card

PCI slots

Hot Pluggable *

Fully

Redundant

*1 Redundancy is optional

*2 Ability to replace a failed component

without shutting down other partitions

2

N+1

Redundant

Mainframe-class RAS features

Reliability / Availability

• Dual-Core Intel® Itanium® processor:

Error handling of hardware and operating system through Machine Check Architecture (MCA)

• Memory mirroring:

• Partial Chipset degradation:

• Highly Available Center Plane:

no longer requires a system shutdown

• Complete modularization and redundancy:

continuous operation and serviceability

• Clock modularization, redundancy and 16 processor domain segmentation:

Minimizes downtime, and avoids multi partition shutdown due to clock failure

• Diagnostics of the error detection circuits:

• Enhanced error detection of the high-speed interconnect:

Intricate error handling through multi bit error detection and retransmission of error data

• Two independent power sources:

Serviceability

Autonomic reporting of logs with pinpoint prognosis of failed components allow for the realization of

•

mainframe-class platform serviceability

Continuous operation even in the event of a non-correctable error

Avoid multi-partition shutdowns resulting from chipset failures

System restoration after the replacement of a failed crossbar

Improvements in fault resilience,

Substantial strengthening of data integrity

Avoid system shutdown due to failures of the power distribution units

3

Supercomputer-class Performan c e

Improved Inter/Intra-Cell memory data transfer

Increased Memory Bandwidth

High-speed/low latency Intra-Cell cache-to-cache data transfer

Very Large Cache (VLC) Architecture

High-speed/low latency Inter-Cell cache-to-cache data transfer

Dedicated Cache Coherency Interface (CCI)

Improved data transfer latency between Cell/Cell and Cell/IO

Crossbar-less configuration

Conventional Superscalar

RISC Processor

Original Source Code Original Source Code

Some level of parallelization is achieved however,

it is not maximized nor efficient

Parallel processing with

EPIC architecture

In the EPIC architecture, parallelization is run at compile time,

allowing for maximum parallelization with minimal scheduling.

Hardware

Partial HW

Parallelization

Intel® Itanium®

processor

supported compiler

Compiler

Sequential

Machine Code

Intel® Itanium® processor

source is parallelized at

compile time

Efficient parallel processing

is made possible due to the

thorough parallelization.

Features for performance improvement

Dual-Core Intel® Itanium® pr ocess o r and high -speed

inter/intra Cell cache-to-cache data transfer

At the heart of the Express5800/1000 series server is the

64 -bi t Dua l-C ore I nte l

®

Itanium® processor, redesigned for

even faster processing of larger data sets.

Th e sys te m has b een e qui pped wi th th e NEC d esi gn ed ch ips et,

3

“A

”, in order to improve performance by utilizing, to its full

ex ten t, th e mas siv e 24M B of ca che m emo ry th at ha s bee n bui lt

into the Dual-Core Intel

®

Itanium® processor

Techn olo gie s to in creas e cac he- to- cac he da ta tr ans fer, s uch

as the VLC architecture and CCI, have been implemented

to m axi miz e the p erf orm anc e for e nte rpr ise m iss ion c rit ica l

[1080Rf]

computing.

High processing power of the Dual-Co re I ntel® Itanium® processor

Du a l-Core, massi ve L3 cach e and EPIC ( E xplici tly Para llel Ins t ructio n Comput ing) architec t ure

The Dual-Core Intel® Itanium® pr oc e ss o r is In tel ’s first p rod uct ion

in t he It ani um

on one processor and also the first member of the Intel

processor family to include Hyper-Threading Technology, which

pr ov i de s f ou r t im e s the n umb er of a ppl ica tio n threa ds pr ovi ded b y

earlier single-core implementations.

With a maximum of 24MB of On-Die L3 cache, the Dual-Core Intel

Itanium

®

pr oc e ss o r fam ily w ith t wo co mpl ete 6 4-b it co re s

®

pr oc e ss o r exc els a t hig h vol ume d ata t ran sac tio ns.

®

Itanium®

®

[1320Xf]

[1160Xf]

EPIC architecture provides a variety of advanced implementations

of parallelism, predication, and speculation, resulting in superior

In str uct ion -Le vel P ara lle lis m (IL P) to h elp a ddr ess t he cu rrent

and future requirements of high-end enterprise and technical

workloads.

4

Loading...

Loading...