NEC 2SK3324 Datasheet

DATA SHEET

MOS FIELD EFFECT TRANSISTOR

SWITCHING

N-CHANNEL POWER MOS FET

INDUSTRIAL USE

2SK3324

DESCRIPTION

The 2SK3324 is N-Channel MOS FET device that features a

Low gate charge and excellent switching characteristics, and

Designed for high voltage applications such as switching

power supply, AC adapter.

FEATURES

• Low gate charge :

QG = 32 nC TYP. (VDD = 450 V, VGS = 10 V, ID = 6.0 A)

• Gate voltage rating : ±30 V

• Low on-state resistance :

DS(on)

R

= 2.8 Ω MAX. (VGS = 10 V, ID = 3.0 A)

• Avalanche capability ratings

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)

Drain to Source Voltage V

Gate to Source Voltage V

Drain Current (DC) I

Drain Current (Pulse)

Total Power Dissipation (T

Total Power Dissipation (T

Note1

C

= 25°C) P

A

= 25°C) P

Storage Temperature T

Single Avalanche Current

Single Avalanche Energy

Note2

Note2

DSS

GSS(AC)

D(DC)

D(pulse)

I

stg

AS

I

AS

E

T

T

–55 to + 150 °C

ORDERING INFORMATION

PART NUMBER PACKAGE

2SK3324

900 V

±30 V

±6 A

±18 A

120 W

3.0 W

6.0 A

21.6 mJ

TO-3P

(TO-3P)

Notes 1.

Document No. D14203EJ2V0DS00 (2nd edition)

Date Published January 2000 NS CP(K)

Printed in Japan

PW ≤ 10

2.

Starting T

µ

s, Duty cycle ≤ 1 %

ch

= 25 °C, VDD = 150 V, RG = 25 Ω, VGS = 20 V → 0 V

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

The mark

••••

shows major revised points.

©

1999

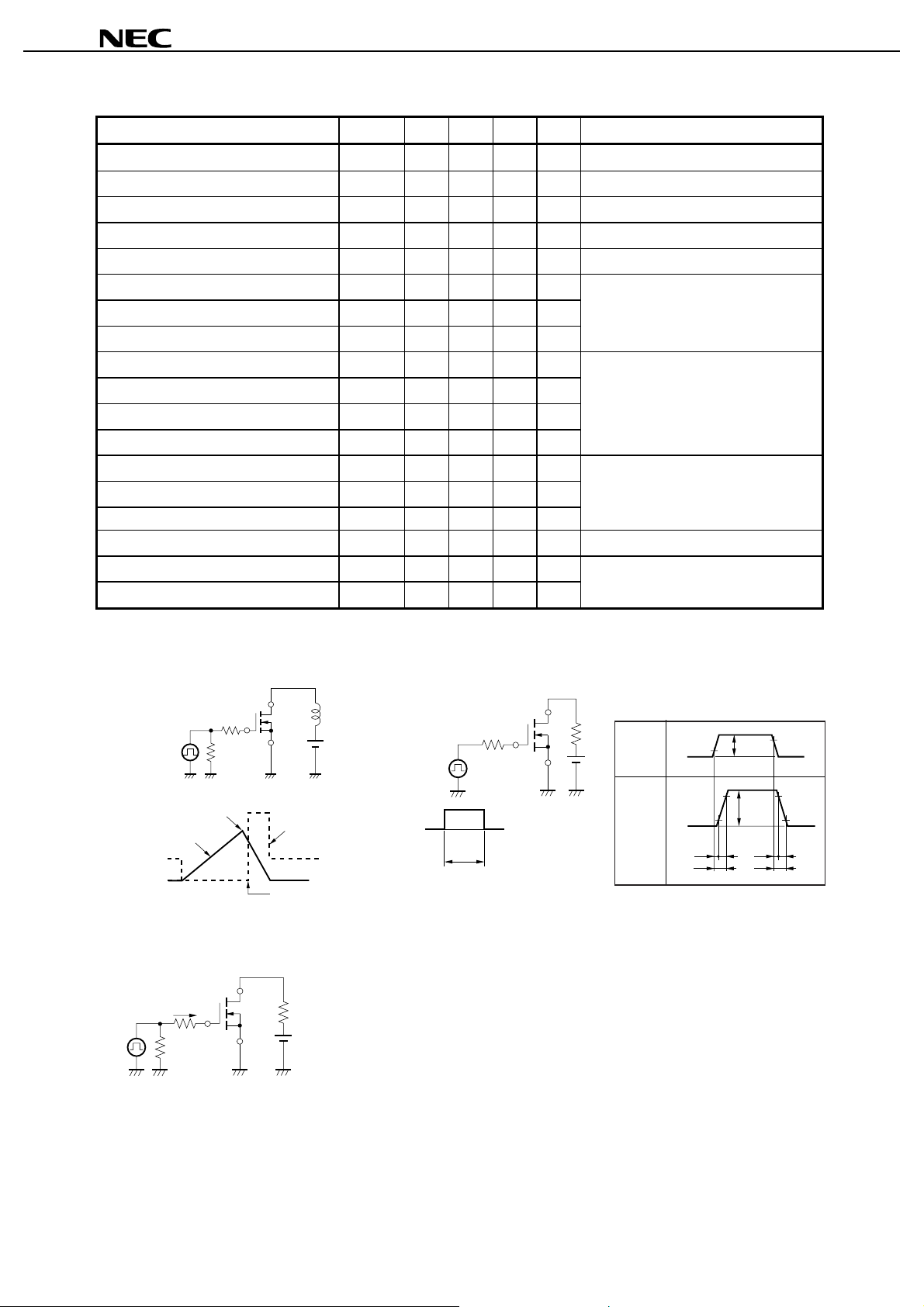

ELECTRICAL CHARACTERISTICS (TA = 25 °C)

CHARACTERISTICS SYMBOL MIN. TYP. MAX. UNIT TEST CONDITIONS

2SK3324

Drain Leakage Current I

Gate to Source Leakage Current I

Gate to Source Cut-off Voltage V

Forward Transfer Admittance | yfs | 2.5 3.3 S VDS = 20 V, ID = 3.0 A

••••

Drain to Source On-state Resi stance R

••••

Input Capacitance C

Output Capacitance C

Reverse Transfer Capacitance C

Turn-on Delay Time t

Rise Time t

Turn-off Delay Time t

Fall Time t

Total Gate Charge Q

Gate to Source Charge Q

Gate to Drain Charge Q

Body Diode Forward Voltage V

Reverse Recovery Time t

Reverse Recovery Charge Q

DSS

GSS

GS(off)

DS(on)

iss

oss

rss

d(on)

r

d(off)

f

G

GS

GD

F(S-D)

rr

rr

100

AVDS = 900 V, VGS = 0 V

µ

±100 nA VGS = ±30 V, VDS = 0 V

2.5 3.5 V VDS = 10 V, ID = 1.0 mA

2.5 2.8

1000 pF

200 pF

42 pF

17 ns

38 ns

57 ns

33 ns

32 nC

5nC

20 nC

VGS = 10 V, ID = 3.0 A

Ω

DS

V

= 10 V,

GS

= 0 V,

V

f = 1 MHz

DD

V

= 150 V,

D

= 3.0 A,

I

GS(on)

= 10 V,

V

G

= 10

R

DD

V

= 450 V,

GS

= 10 V,

V

D

= 6.0 A

I

0.9 V IF = 6.0 A, VGS = 0 V

1.9

9.0

F

s

= 6.0 A, VGS = 0 V,

I

µ

di/dt = 50 A/

C

µ

Ω,

RL = 10

s

µ

Ω

TEST CIRCUIT 1 AVALANCHE CAPABILITY

D.U.T.

L

V

DD

PG

RG = 25 Ω

50 Ω

VGS = 20 → 0 V

BV

DSS

I

AS

V

I

D

V

DD

DS

Starting T

ch

TEST CIRCUIT 3 GATE CHARGE

D.U.T.

PG.

IG = 2 mA

50 Ω

R

L

V

DD

TEST CIRCUIT 2 SWITCHING TIME

D.U.T.

L

R

G

PG.

GS

V

0

τ = 1 s

Duty Cycle ≤ 1 %

R

V

DD

τ

µ

GS

V

Wave Form

I

D

Wave Form

V

GS

10 %

0

90 %

I

D

10 %

0

t

d(on)

r

t

on

t

90 %

V

GS

(on)

90 %

I

D

10 %

t

d(off)

t

f

t

off

2

Data Sheet D14203EJ2V0DS00

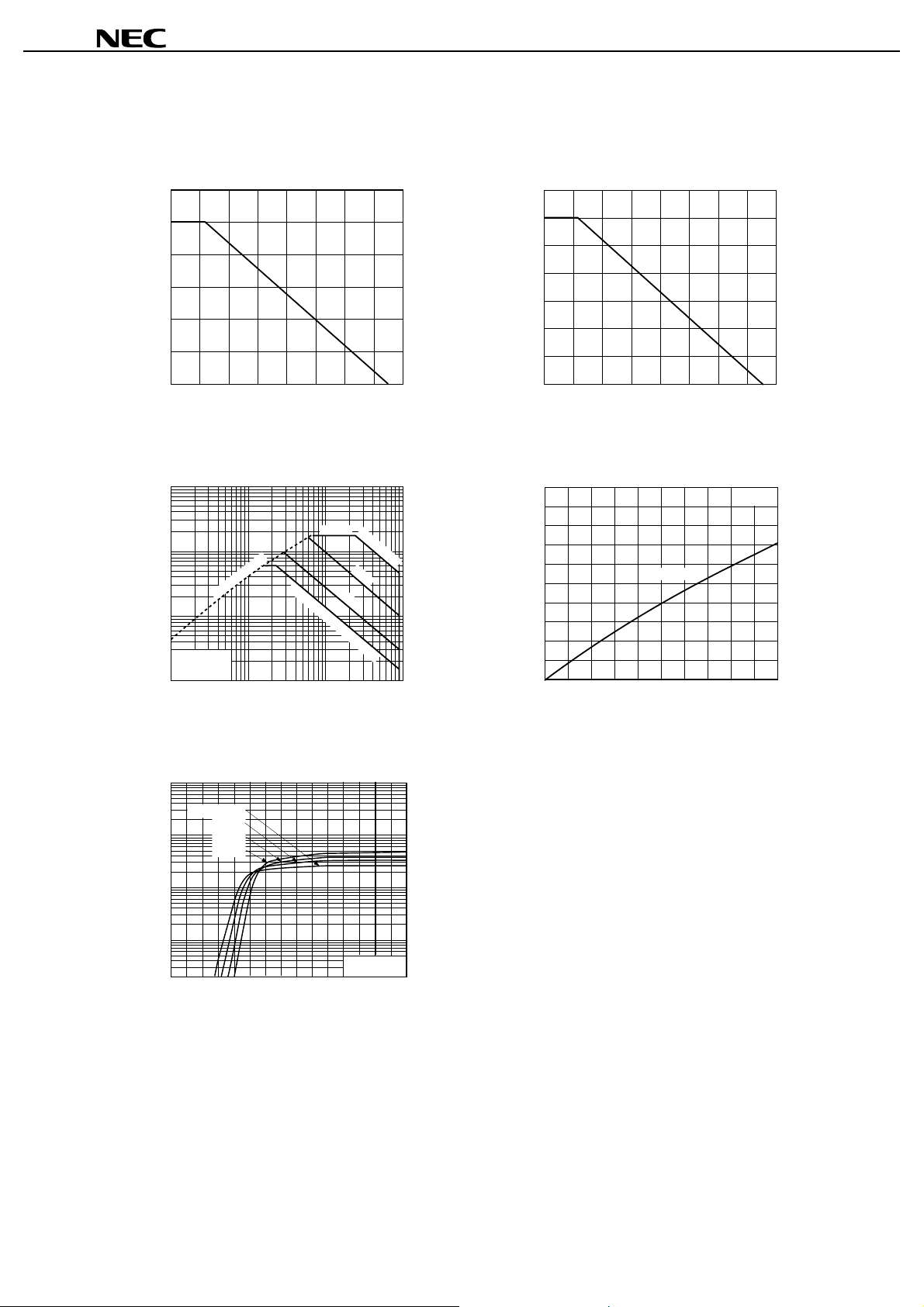

TYPICAL CHARACTERISTICS (TA = 25 °C)

2SK3324

DERATING FACTOR OF FORWARD BIAS

SAFE OPERATING AREA

100

80

60

40

20

dT - Percentage of Rated Power - %

0

20 40 60 80 100 120 140 160

C

- Case Temperature - °C

T

FORWARD BIAS SAFE OPERATING AREA

100

10

Limited

DS(on)

R

1

- Drain Current - A

D

I

TC = 25

˚C

Single Pulse

0.1

1 10 1000100

DS

- Drain to Source Voltage - V

V

Power Dissipation Limited

I

D(pulse)

TOTAL POWER DISSIPATION vs.

CASE TEMPERATURE

140

120

100

80

60

40

- Total Power Dissipation - W

T

20

P

0

20 40 60 80 100 120 140 160

C

- Case Temperature - °C

T

DRAIN CURRENT vs.

DRAIN TO SOURCE VOLTAGE

10

P

W

=100

µs

1

ms

10

ms

8

6

4

- Drain Current - A

D

I

2

0

4

DS

V

VGS =

10 V

8

12

- Drain to Source Voltage - V

Pulsed

16 20

FORWARD TRANSFER CHARACTERISTICS

100

TA = 125˚C

10

75˚C

25˚C

−25˚C

1

- Drain Current - A

D

I

0.1

0.01

01015

5

GS

- Gate to Source Voltage - V

V

Pulsed

Data Sheet D14203EJ2V0DS00

3

Loading...

Loading...