现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

LM1881

Video Sync Separator

LM1881 Video Sync Separator

May 2006

General Description

The LM1881 Video sync separator extracts timing information including composite and vertical sync, burst/back porch

timing, and odd/even field information from standard negative going sync NTSC, PAL* and SECAM video signals with

amplitude from 0.5V to 2V p-p. The integrated circuit is also

capable of providing sync separation for non-standard,

faster horizontal rate video signals. The vertical output is

produced on the rising edge of the first serration in the

vertical sync period. A default vertical output is produced

after a time delay if the rising edge mentioned above does

not occur within the externally set delay period, such as

might be the case for a non-standard video signal.

Connection Diagram

LM1881N

Features

n AC coupled composite input signal

>

n

10 kΩ input resistance

<

n

10 mA power supply drain current

n Composite sync and vertical outputs

n Odd/even field output

n Burst gate/back porch output

n Horizontal scan rates to 150 kHz

n Edge triggered vertical output

n Default triggered vertical output for non-standard video

signal (video games-home computers)

Order Number LM1881M or LM1881N (0˚C to +70˚C)

See NS Package Number M08A or N08E

*PAL in this datasheet refers to European broadcast TV standard “Phase Alternating Line”, and not to Programmable Array Logic.

© 2006 National Semiconductor Corporation DS009150 www.national.com

00915001

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

LM1881

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage 13.2V

Input Voltage 3 V

Output Sink Currents; Pins, 1, 3, 5 5 mA

6V

P-P(VCC

P-P(VCC

= 5V)

≥ 8V)

Storage Temperature Range −65˚C to +150˚C

ESD Susceptibility (Note 3) 2 kV

ESD Susceptibility (Note 4) 200 V

Soldering Information

Dual-In-Line Package (10 sec.) 260˚C

Small Outline Package

Vapor Phase (60 sec.) 215˚C

Infrared (15 sec.) 220˚C

Output Sink Current; Pin 7 2 mA

Package Dissipation (Note 2) 1100 mW

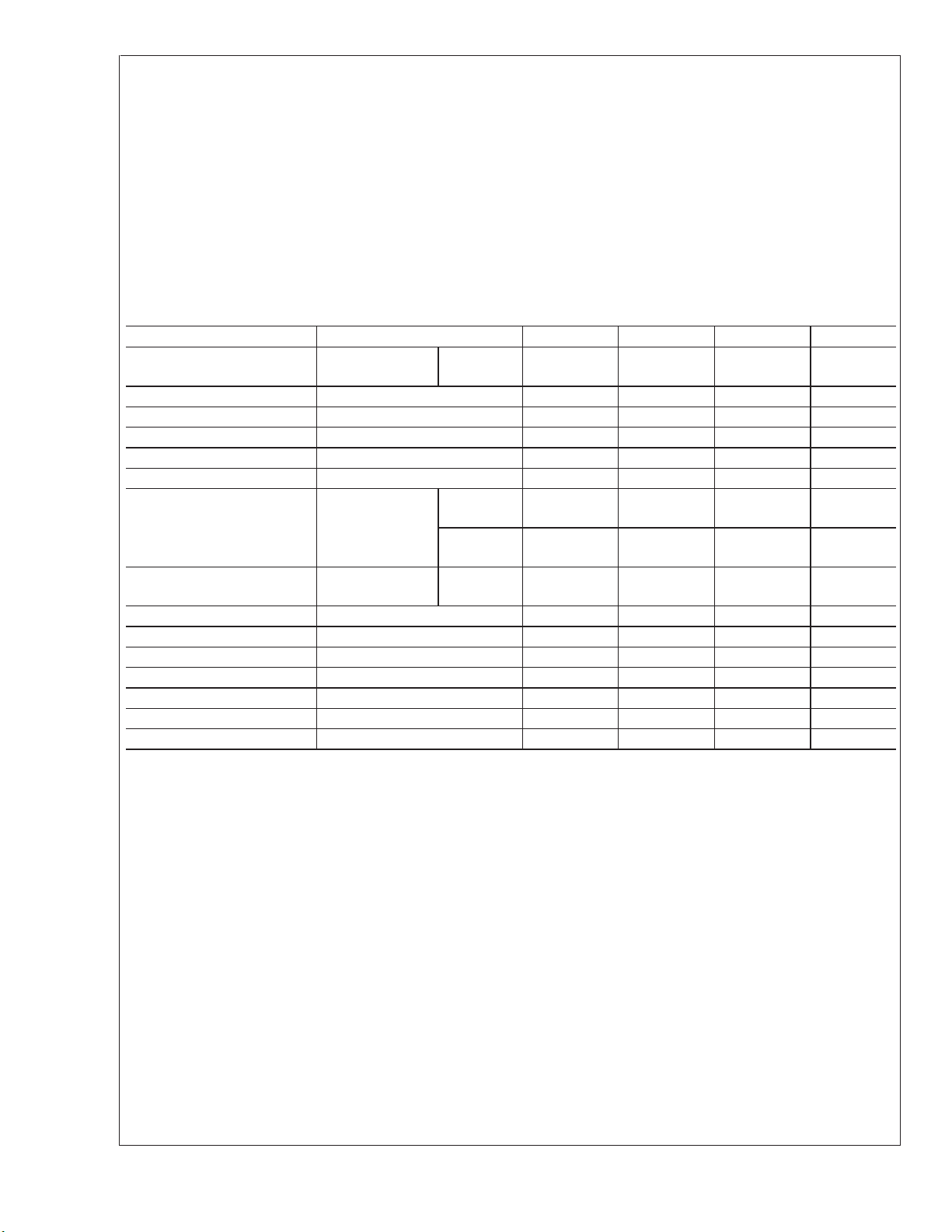

Electrical Characteristics LM1881

VCC= 5V; R

Parameter Conditions Min Typ (Note 5) Max Units

Supply Current Outputs at

DC Input Voltage Pin 2 1.3 1.5 1.8 V

Input Threshold Voltage (Note 6) 55 70 85 mV

Input Discharge Current Pin 2; V

Input Clamp Charge Current Pin 2; V

R

Pin Reference Voltage Pin 6; (Note 7) 1.10 1.22 1.35 V

SET

Composite Sync. & Vertical

Outputs

Burst Gate & Odd/Even

Outputs

Composite Sync. Output I

Vertical Sync. Output I

Burst Gate Output I

Odd/Even Output I

Vertical Sync Width 190 230 300 µs

Burst Gate Width 2.7 kΩ from Pin 5 to V

Vertical Default Time (Note 8) 32 65 90 µs

= 680 kΩ;TA= 0˚C to +70˚C by correlation with 100% electrical testing at TA=25˚C

SET

V

=5V

CC

Logic 1

= 2V 6 11 16 µA

IN

= 1V 0.2 0.8 mA

IN

I

=40µA;

OUT

Logic 1

I

= 1.6 mA

OUT

Logic 1

I

=40µA;

OUT

Logic 1

= −1.6 mA; Logic 0; Pin 1 0.2 0.8 V

OUT

= −1.6 mA; Logic 0; Pin 3 0.2 0.8 V

OUT

= −1.6 mA; Logic 0; Pin 5 0.2 0.8 V

OUT

= −1.6 mA; Logic 0; Pin 7 0.2 0.8 V

OUT

= 12V

V

CC

VCC=5V

= 12V

V

CC

VCC=5V

= 12V

V

CC

VCC=5V

= 12V

V

CC

CC

4.0

11.0

2.4

10.0

4.0

11.0

2.5 4 4.7 µs

5.2

5.5

4.5

3.6

4.5

10

12

mA

V

V

V

www.national.com 2

Electrical Characteristics LM1881 (Continued)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. For guaranteed specifications and test conditions, see the

Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed.

Note 2: For operation in ambient temperatures above 25˚C, the device must be derated based on a 150˚C maximum junction temperature and a package thermal

resistance of 110˚C/W, junction to ambient.

Note 3: ESD susceptibility test uses the “human body model, 100 pF discharged through a 1.5 kΩ resistor”.

Note 4: Machine Model, 220 pF – 240 pF discharged through all pins.

Note 5: Typicals are at T

Note 6: Relative difference between the input clamp voltage and the minimum input voltage which produces a horizontal output pulse.

Note 7: Careful attention should be made to prevent parasitic capacitance coupling from any output pin (Pins 1, 3, 5 and 7) to the R

Note 8: Delay time between the start of vertical sync (at input) and the vertical output pulse.

= 25˚C and represent the most likely parametric norm.

J

SET

pin (Pin 6).

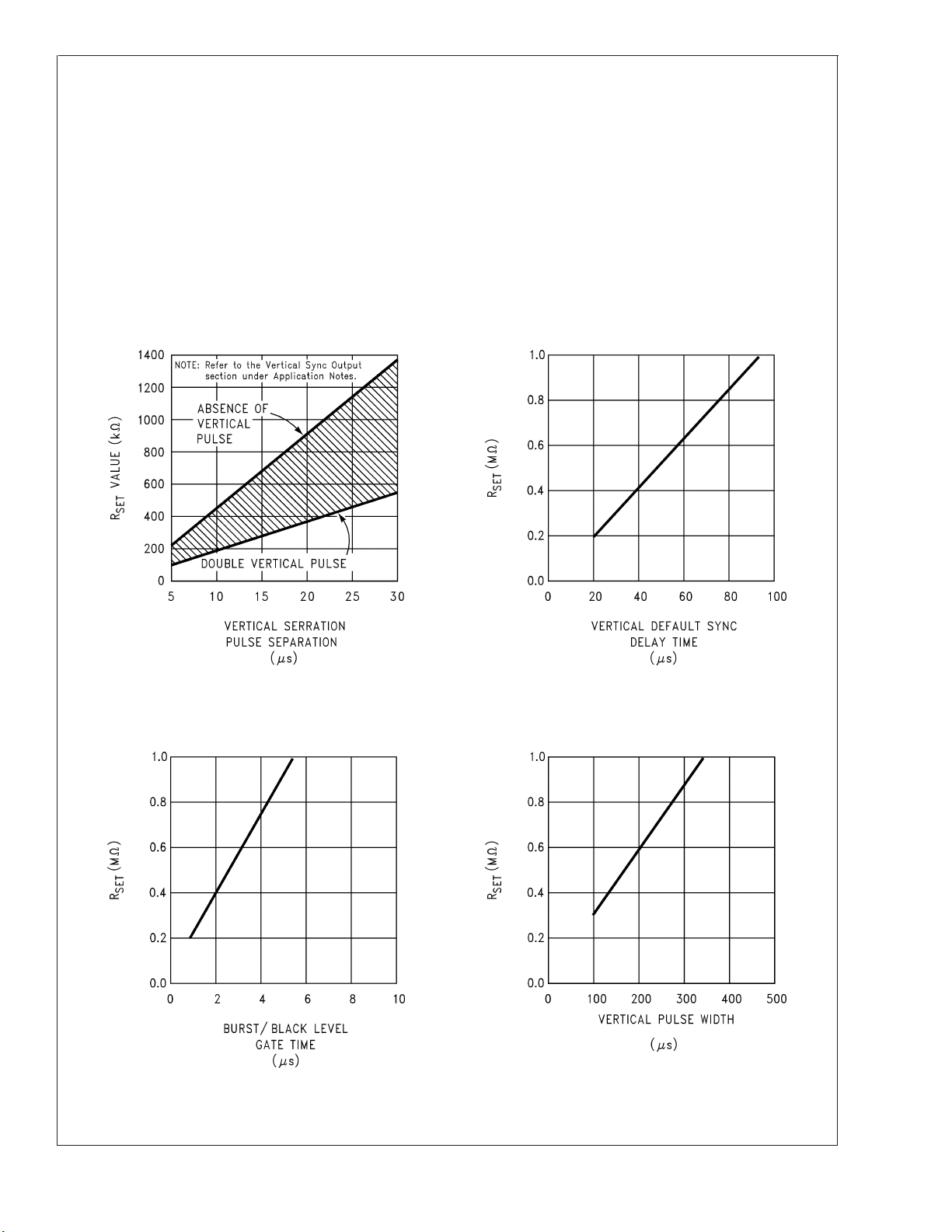

Typical Performance Characteristics

R

Value Selection

SET

vs Vertical Serration

Pulse Separation

Vertical Default

Sync Delay Time

vs R

SET

LM1881

Burst/Black Level

Gate Time vs R

SET

00915007 00915008

Vertical Pulse

Width vs R

00915009

SET

00915010

www.national.com3

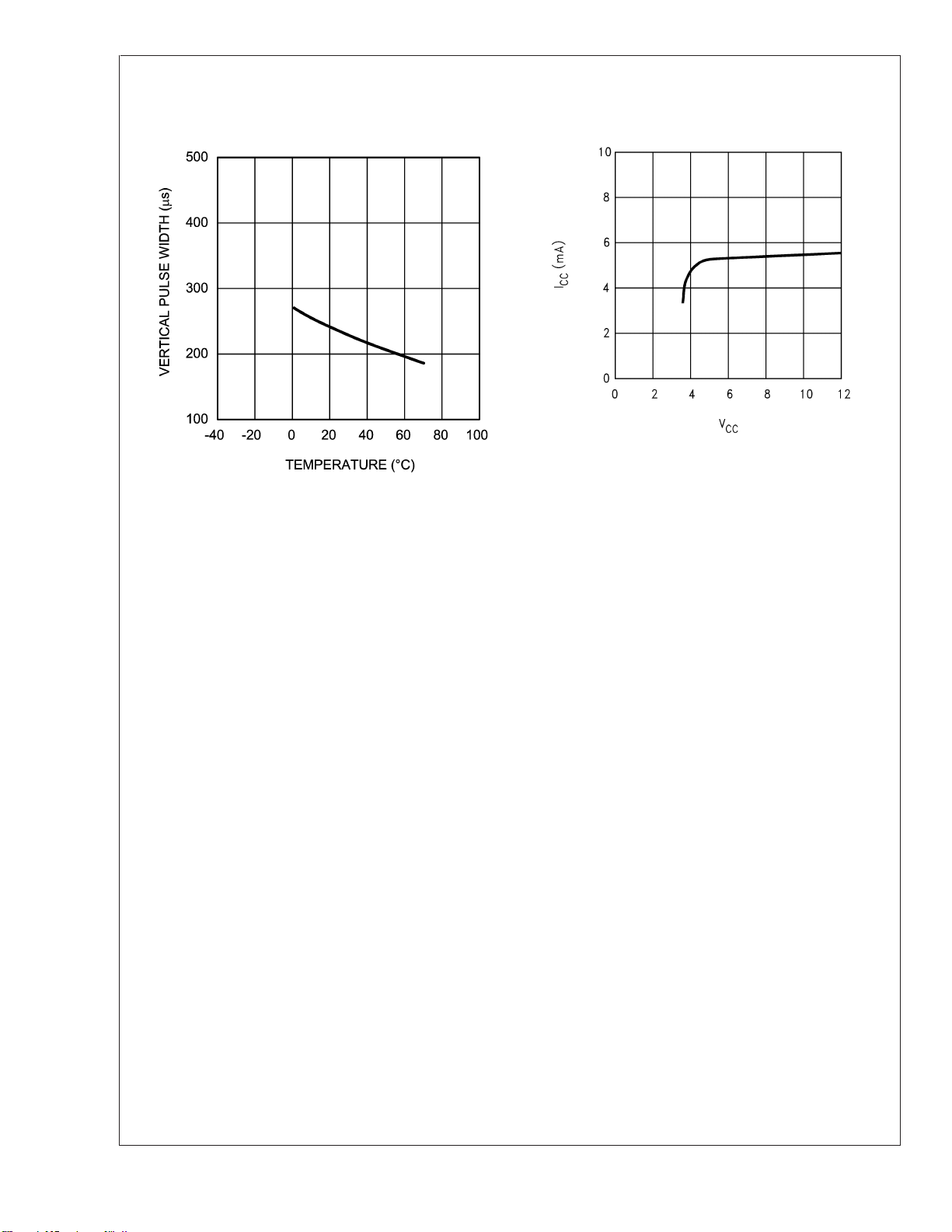

Typical Performance Characteristics (Continued)

LM1881

Vertical Pulse

Width vs Temperature

Application Notes

The LM1881 is designed to strip the synchronization signals

from composite video sources that are in, or similar to, the

N.T.S.C. format. Input signals with positive polarity video

(increasing signal voltage signifies increasing scene brightness) from 0.5V (p-p) to 2V (p-p) can be accommodated.

The LM1881 operates from a single supply voltage between

5V DC and 12V DC. The only required external components

besides a power supply decoupling capacitor at pin 8 and a

set current decoupling capacitor at pin 6, are the composite

input coupling capacitor at pin 2 and one resistor at pin 6 that

sets internal current levels. The resistor on pin 6 (i.e. R

allows the LM1881 to be adjusted for source signals with line

scan frequencies differing from 15.734 kHz. Four major sync

signals are available from the I/C; composite sync including

both horizontal and vertical scan timing information; a vertical sync pulse; a burst gate or back porch clamp pulse; and

an odd/even output. The odd/even output level identifies

which video field of an interlaced video source is present at

the input. The outputs from the LM1881 can be used to

gen-lock video camera/VTR signals with graphics sources,

provide identification of video fields for memory storage,

recover suppressed or contaminated sync signals, and provide timing references for the extraction of coded or uncoded

data on specific video scan lines.

To better understand the LM1881 timing information and the

type of signals that are used, refer to Figure 1(a-e) which

shows a portion of the composite video signal from the end

of one field through the beginning of the next field.

COMPOSITE SYNC OUTPUT

The composite sync output, Figure 1(b), is simply a reproduction of the signal waveform below the composite video

black level, with the video completely removed. This is obtained by clamping the video signal sync tips to 1.5V DC at

Pin 2 and using a comparator threshold set just above this

voltage to strip the sync signal, which is then buffered out to

Pin 1. The threshold separation from the clamped sync tip is

nominally 70 mV which means that for the minimum input

00915011

set

Supply Current vs

Supply Voltage

00915002

level of 0.5V (p-p), the clipping level is close to the halfway

point on the sync pulse amplitude (shown by the dashed line

on Figure 1(a). This threshold separation is independent of

the signal amplitude, therefore, for a 2V (p-p) input the

clipping level occurs at 11% of the sync pulse amplitude. The

charging current for the input coupling capacitor is 0.8 mA,

Normally the signal source for the LM1881 is assumed to be

clean and relatively noise-free, but some sources may have

excessive video peaking, causing high frequency video and

chroma components to extend below the black level reference. Some video discs keep the chroma burst pulse

)

present throughout the vertical blanking period so that the

burst actually appears on the sync tips for three line periods

instead of at black level. A clean composite sync signal can

be generated from these sources by filtering the input signal.

When the source impedance is low, typically 75Ω, a 620Ω

resistor in series with the source and a 510 pF capacitor to

ground will form a low pass filter with a corner frequency of

500 kHz. This bandwidth is more than sufficient to pass the

sync pulse portion of the waveform; however, any subcarrier

content in the signal will be attenuated by almost 18 dB,

effectively taking it below the comparator threshold. Filtering

will also help if the source is contaminated with thermal

noise. The output waveforms will become delayed from between 40 ns to as much as 200 ns due to this filter. This

much delay will not usually be significant but it does contribute to the sync delay produced by any additional signal

processing. Since the original video may also undergo processing, the need for time delay correction will depend on

the total system, not just the sync stripper.

VERTICAL SYNC OUTPUT

A vertical sync output is derived by internally integrating the

composite sync waveform (Figure 2). To understand the

generation of the vertical sync pulse, refer to the lower left

hand section Figure 2. Note that there are two comparators

in the section. One comparator has an internally generated

voltage reference called V

going to one of its inputs. The

1

other comparator has an internally generated voltage refer-

www.national.com 4

Loading...

Loading...