National Semiconductor DS90CR215, DS90CR216 Technical data

查询DS90CR216供应商

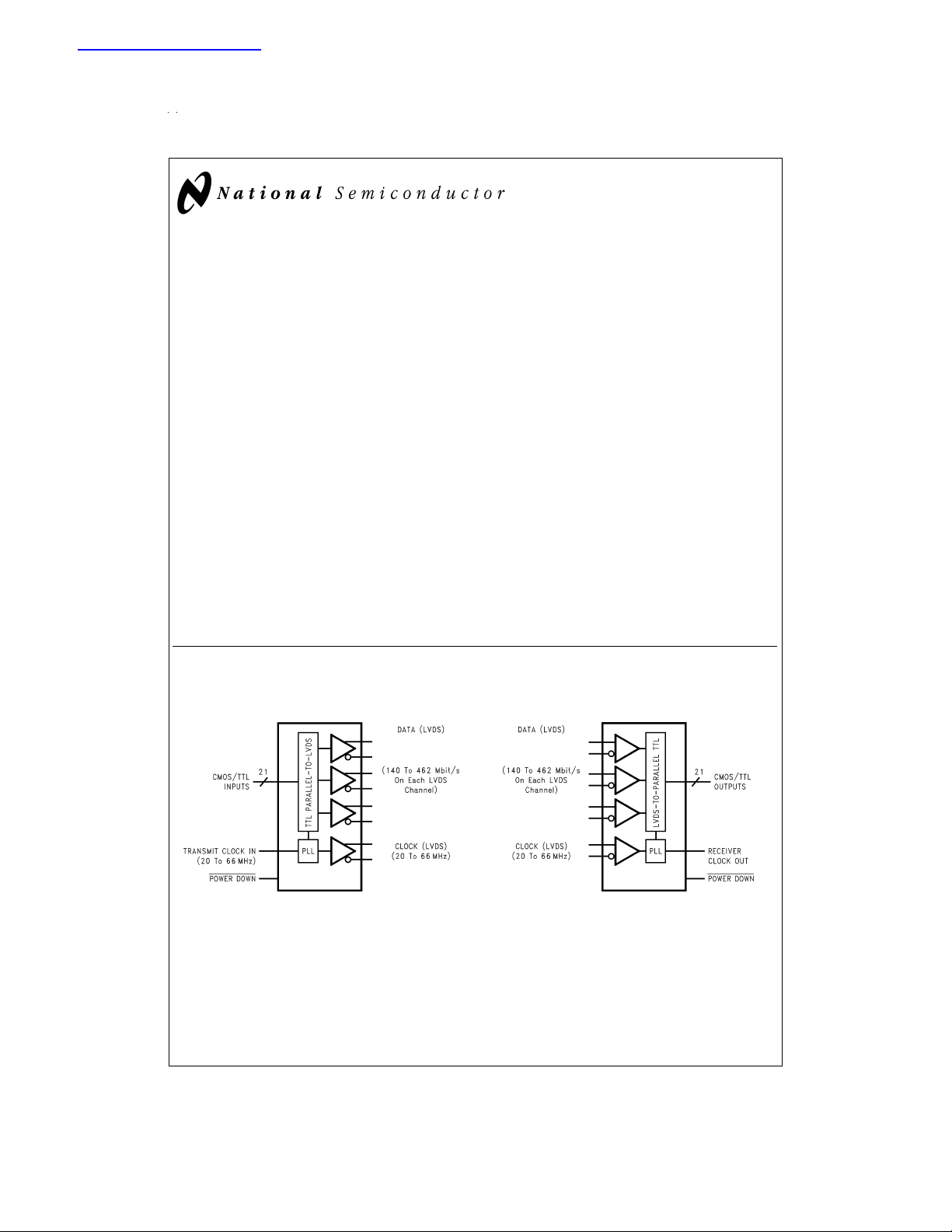

DS90CR215/DS90CR216

+3.3V Rising Edge Data Strobe LVDS 21-Bit Channel

Link - 66 MHz

General Description

The DS90CR215 transmitter converts 21 bits of CMOS/TTL

data into three LVDS (Low Voltage Differential Signaling)

data streams.Aphase-locked transmit clockis transmitted in

parallel with thedata streams over a fourth LVDS link.Every

cycle of the transmit clock 21 bits of input data are sampled

and transmitted. The DS90CR216 receiver converts the

LVDS data streams back into 21 bits of CMOS/TTL data. At

a transmitclock frequencyof 66 MHz,21 bitsof TTLdata are

transmitted at a rate of 462 Mbps per LVDS data channel.

Using a 66 MHz clock, the data throughput is 1.386 Gbit/s

(173 Mbytes/s).

The multiplexing of the data lines provides a substantial

cable reduction. Long distance parallel single-ended buses

typically require a ground wire per active signal (and have

very limitednoise rejectioncapability). Thus,for a21-bit wide

data and one clock, up to 44 conductors are required. With

the Channel Link chipset as few as 9 conductors (3 data

pairs, 1 clock pair and a minimum of one ground) are

needed. This provides a 80%reduction in required cable

width, which provides a system cost savings, reduces connector physicalsize and cost,and reduces shieldingrequirements due to the cables’ smaller form factor.

March 1999

The 21 CMOS/TTL inputs can support a variety of signal

combinations. For example, five 4-bit nibbles plus 1 control,

or two 9-bit (byte + parity) and 3 control.

Features

n Single +3.3V supply

n Chipset (Tx + Rx) power consumption

n Power-down mode (

n Up to 173 Megabytes/sec bandwidth

n Up to 1.386 Gbps data throughput

n Narrow bus reduces cable size

n 290 mV swing LVDS devices for low EMI

n +1V common mode range (around +1.2V)

n PLL requires no external components

n Low profile 48-lead TSSOP package

n Rising edge data strobe

n Compatible with TIA/EIA-644 LVDS standard

n ESD Rating

n Operating Temperature: −40˚C to +85˚C

>

7kV

<

0.5 mW total)

<

250 mW (typ)

DS90CR215/DS90CR216 +3.3V Rising Edge Data Strobe LVDS 21-Bit Channel Link-66 MHz

Block Diagrams

DS90CR215

DS012909-1

Order Number DS90CR215MTD

See NS Package Number MTD48

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

© 1999 National Semiconductor Corporation DS012909 www.national.com

Order Number DS90CR216MTD

See NS Package Number MTD48

DS90CR216

DS012909-27

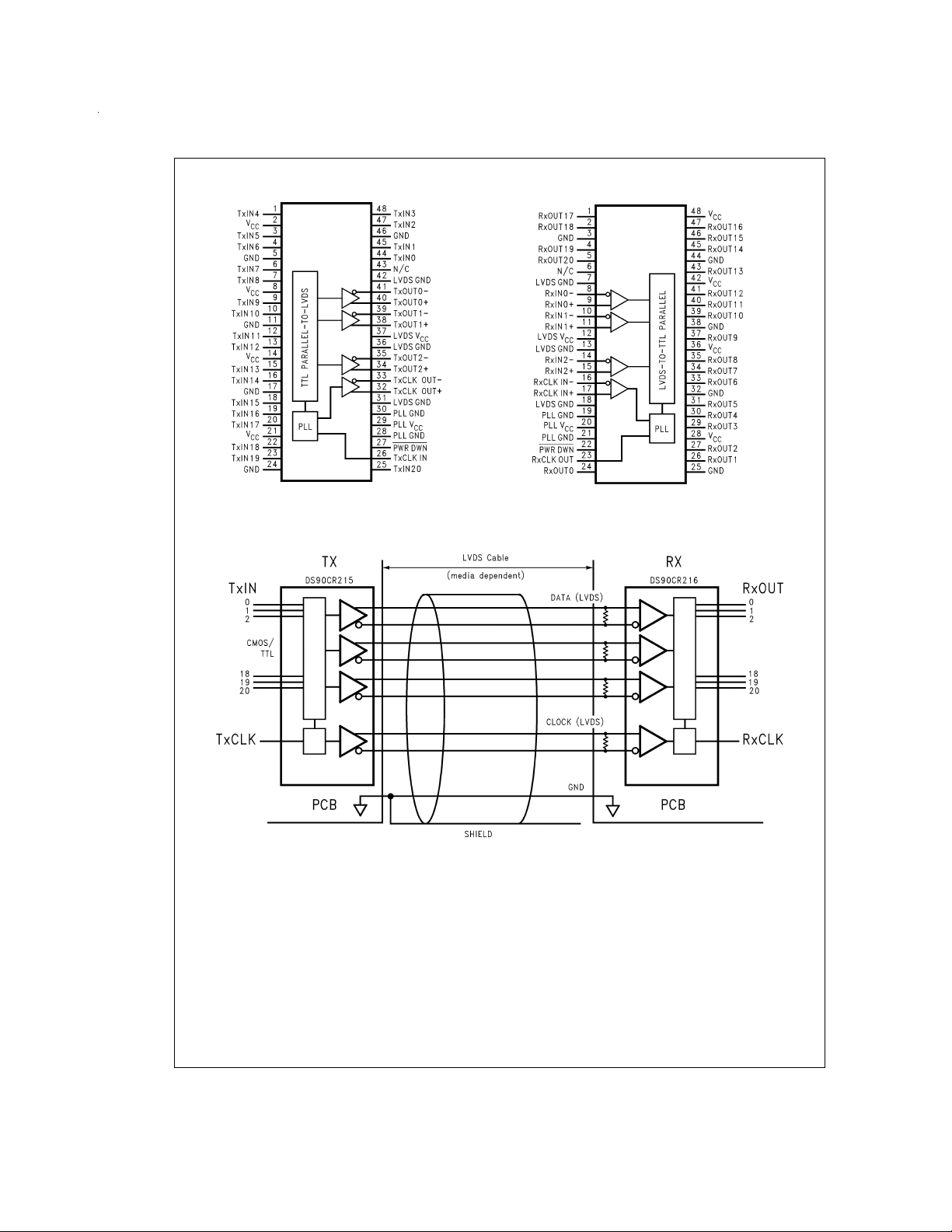

Pin Diagrams

DS90CR215

Typical Application

DS012909-21

DS012909-22

DS90CR216

DS012909-23

www.national.com 2

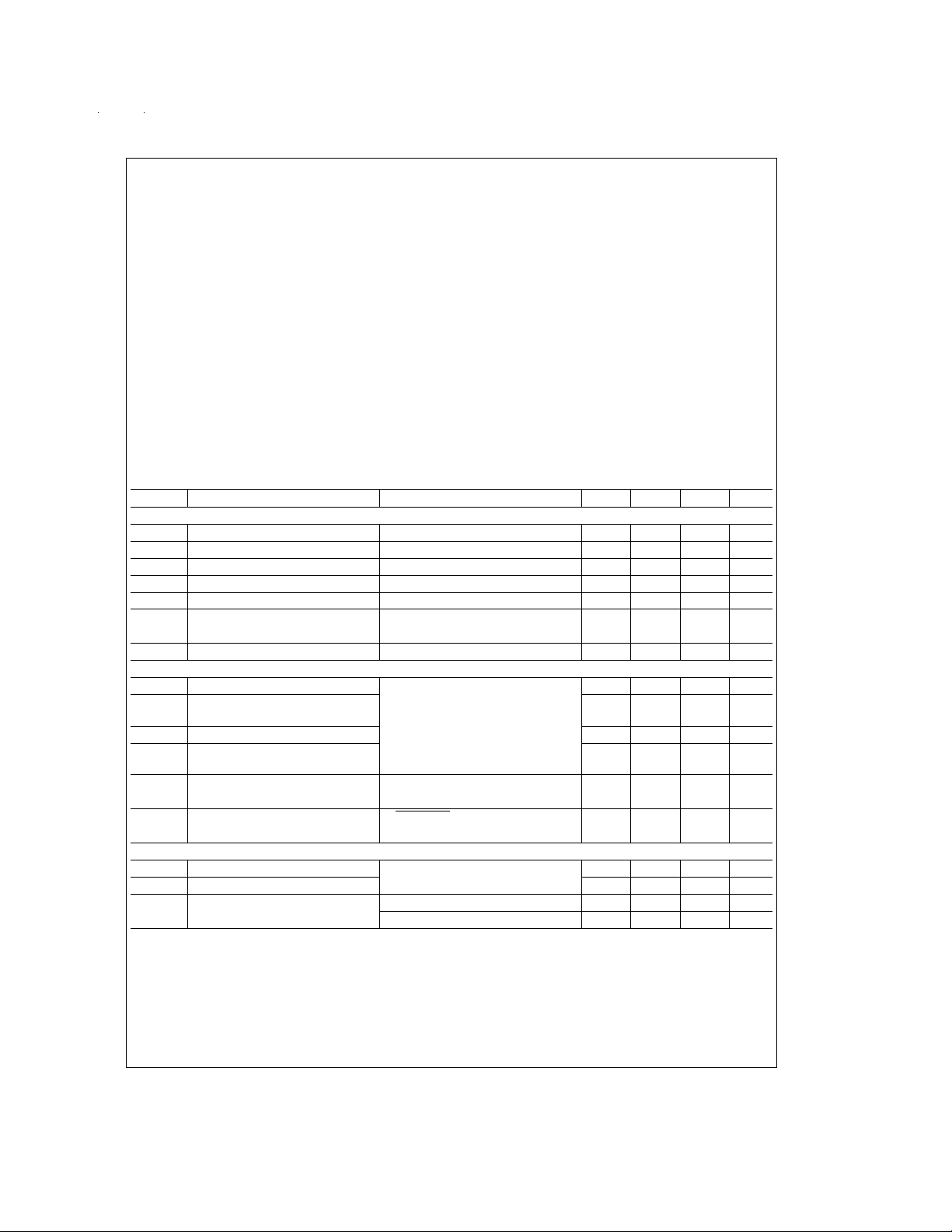

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contactthe National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CMOS/TTL Input Voltage −0.3V to (V

CMOS/TTL Output Voltage −0.3V to (V

LVDS Receiver Input Voltage −0.3V to (V

LVDS Driver Output Voltage −0.3V to (V

LVDS Output Short

Circuit Duration Continuous

Junction Temperature +150˚C

Storage Temperature Range −65˚C to +150˚C

Lead Temperature

(Soldering, 4 sec.) +260˚C

Maximum Package Power Dissipation

MTD48 (TSSOP) Package:

) −0.3V to +4V

CC

@

CC

CC

CC

CC

+25˚C

+ 0.3V)

+ 0.3V)

+ 0.3V)

+ 0.3V)

DS90CR215 1.98 W

DS90CR216 1.89 W

Package Derating

DS90CR215 16 mW/˚C above +25˚C

DS90CR216 15 mW/˚C above +25˚C

ESD Rating

(HBM, 1.5 kΩ, 100 pF)

>

Recommended Operating

Conditions

Supply Voltage (V

) 3.0 3.3 3.6 V

CC

Operating Free Air

Temperature (T

) −40 +25 +85 ˚C

A

Receiver Input Range 0 2.4 V

Supply Noise Voltage (V

Min Nom Max Units

) 100 mV

CC

7kV

Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified

Symbol Parameter Conditions Min Typ Max Units

CMOS/TTL DC SPECIFICATIONS

V

IH

V

IL

V

OH

V

OL

V

CL

I

IN

I

OS

LVDS DRIVER DC SPECIFICATIONS

V

OD

∆V

V

OS

∆V

I

OS

I

OZ

LVDS RECEIVER DC SPECIFICATIONS

V

TH

V

TL

I

IN

High Level Input Voltage 2.0 V

Low Level Input Voltage GND 0.8 V

High Level Output Voltage IOH= −0.4 mA 2.7 3.3 V

Low Level Output Voltage IOL= 2 mA 0.06 0.3 V

Input Clamp Voltage ICL= −18 mA −0.79 −1.5 V

Input Current VIN=VCC, GND,

±

5.1

2.5V or 0.4V

Output Short Circuit Current V

= 0V -60 −120 mA

OUT

Differential Output Voltage RL= 100Ω 250 290 450 mV

Change in VODbetween

OD

Complimentary Output States

Offset Voltage (Note 4) 1.125 1.25 1.375 V

Change in VOSbetween

OS

Complimentary Output States

Output Short Circuit Current V

Output TRI-STATE®Current PWR DWN = 0V,

= 0V, −3.5 −5 mA

OUT

R

= 100Ω

L

±

V

=0VorV

OUT

CC

Differential Input High Threshold VCM= +1.2V +100 mV

Differential Input Low Threshold −100 mV

Input Current VIN= +2.4V, VCC= 3.6V

V

= 0V, VCC= 3.6V

IN

1

CC

±

10 µA

35 mV

35 mV

±

10 µA

±

10 µA

±

10 µA

PP

V

www.national.com3

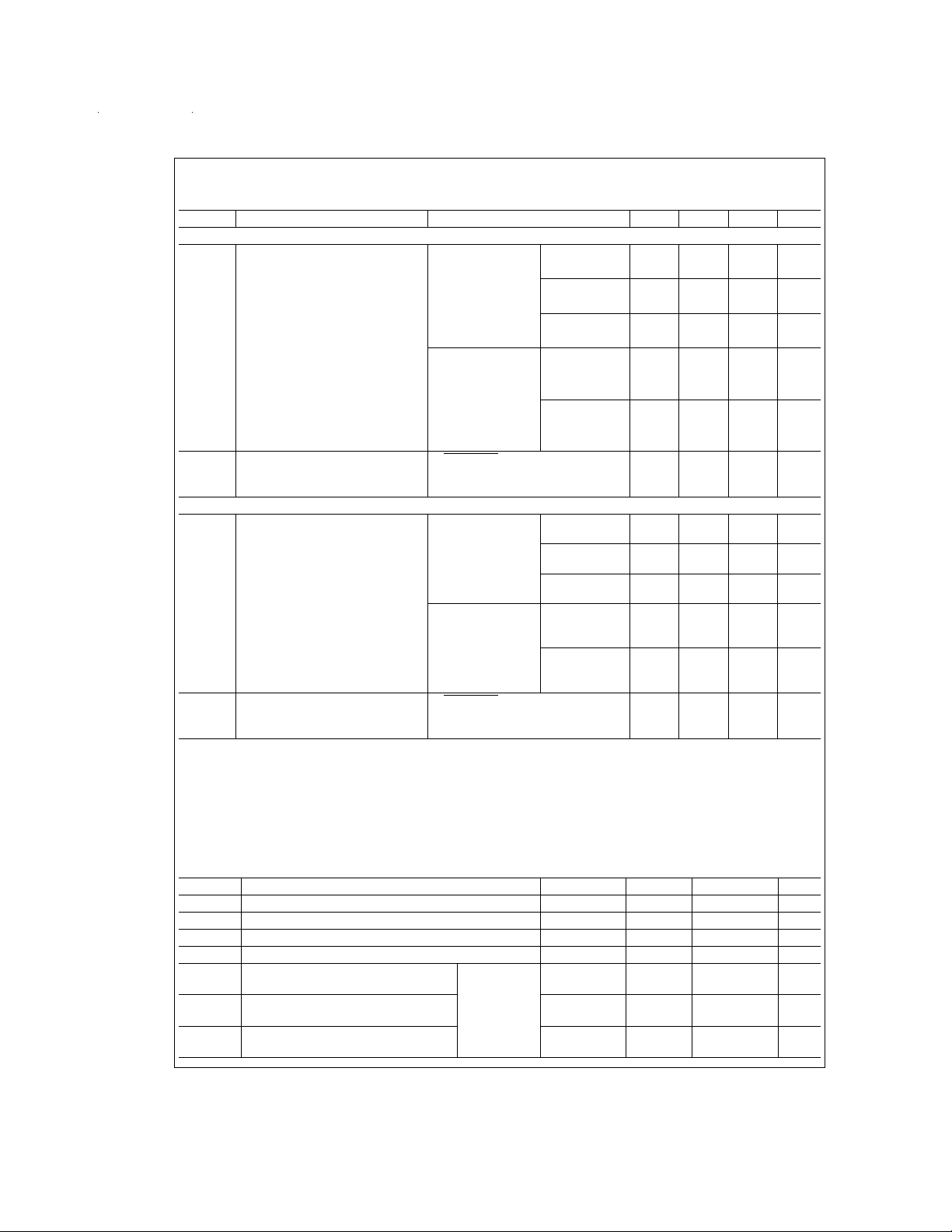

Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified

Symbol Parameter Conditions Min Typ Max Units

TRANSMITTER SUPPLY CURRENT

I

CCTW

I

CCTZ

RECEIVER SUPPLY CURRENT

I

CCRW

I

CCRZ

Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device

should be operated at these limits. The tables of “Electrical Characteristics” specify conditions for device operation.

Note 2: Typical values are given for V

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages arereferenced toground unlessotherwise speci-

fied (except V

Note 4: V

Transmitter Supply Current

Worst Case (with Loads)

Transmitter Supply Current

Power Down

Receiver Supply Current Worst

Case

Receiver Supply Current Power

Down

CC

and ∆VOD).

OD

previously referred as VCM.

OS

= 3.3V and TA= +25˚C.

RL= 100Ω,

= 5 pF,

C

L

Worst Case

Pattern

Figures 1, 2

(

= −10˚C to

T

A

+70˚C

= 100Ω,

R

L

= 5 pF,

C

L

Worst Case

Pattern

Figures 1, 2

(

= −40˚C to

T

A

+85˚C

),

),

f = 32.5 MHz 31 45 mA

f = 37.5 MHz 32 50 mA

f = 66 MHz 37 55 mA

f = 40 MHz 38 51 mA

f = 66 MHz 42 55 mA

PWR DWN = Low

Driver Outputs in TRI-STATE

under Powerdown Mode

CL= 8 pF,

f = 32.5 MHz 49 65 mA

Worst Case

Pattern

Figures 1, 3

(

= −10˚C to

T

A

+70˚C

= 8 pF,

C

L

Worst Case

),

f = 37.5 MHz 53 70 mA

f = 66 MHz 78 105 mA

f = 40 MHz 55 82 mA

Pattern

Figures 1, 3

(

T

A

+85˚C

= −40˚C to

),

f = 66 MHz 78 105 mA

PWR DWN = Low

Receiver Outputs Stay Low during

Powerdown Mode

10 55 µA

10 55 µA

Transmitter Switching Characteristics

Over recommended operating supply and −40˚C to +85˚C ranges unless otherwise specified

Symbol Parameter Min Typ Max Units

Figure 2

LLHT LVDS Low-to-High Transition Time (

LHLT LVDS High-to-Low Transition Time (

TCIT TxCLK IN Transition Time (

Figure 4

TCCS TxOUT Channel-to-Channel Skew (

TPPos0 Transmitter Output Pulse Position for

Bit0 (Note 7) (

Figure 16

)

TPPos1 Transmitter Output Pulse Position for

Bit1

TPPos2 Transmitter Output Pulse Position for

Bit2

www.national.com 4

) 0.5 1.5 ns

Figure 2

) 0.5 1.5 ns

)5ns

Figure 5

) 250 ps

f = 40 MHz −0.4 0 0.4 ns

3.1 3.3 4.0 ns

6.5 6.8 7.6 ns

Transmitter Switching Characteristics (Continued)

Over recommended operating supply and −40˚C to +85˚C ranges unless otherwise specified

Symbol Parameter Min Typ Max Units

TPPos3 Transmitter Output Pulse Position for

TPPos4 Transmitter Output Pulse Position for

TPPos5 Transmitter Output Pulse Position for

TPPos6 Transmitter Output Pulse Position for

TPPos0 Transmitter Output Pulse Position for

TPPos1 Transmitter Output Pulse Position for

TPPos2 Transmitter Output Pulse Position for

TPPos3 Transmitter Output Pulse Position for

TPPos4 Transmitter Output Pulse Position for

TPPos5 Transmitter Output Pulse Position for

TPPos6 Transmitter Output Pulse Position for

TCIP TxCLK IN Period (

TCIH TxCLK IN High Time (

TCIL TxCLK IN Low Time (

TSTC TxIN Setup to TxCLK IN (

THTC TxIN Hold to TxCLK IN (

TCCD TxCLK IN to TxCLK OUT Delay

TPLLS Transmitter Phase Lock Loop Set (

TPDD Transmitter Powerdown Delay (

Bit3

Bit4

Bit5

Bit6

Bit0 (Note 6) (

Bit1

Bit2

Bit3

Bit4

Bit5

Bit6

Figure 8

)

(

Figure 16

Figure 6

)

) 15 T 50 ns

Figure 6

) 0.35T 0.5T 0.65T ns

Figure 6

) 0.35T 0.5T 0.65T ns

Figure 6

) 2.5 ns

Figure 6

)0 ns

@

Figure 14

f = 66 MHz −0.4 0 0.3 ns

25˚C,VCC=3.3V

Figure 10

)10ms

) 100 ns

10.2 10.4 11.0 ns

13.7 13.9 14.6 ns

17.3 17.6 18.2 ns

21.0 21.2 21.8 ns

1.8 2.2 2.5 ns

4.0 4.4 4.7 ns

6.2 6.6 6.9 ns

8.4 8.8 9.1 ns

10.6 11.0 11.3 ns

12.8 13.2 13.5 ns

3 3.7 5.5 ns

Receiver Switching Characteristics

Over recommended operating supply and −40˚C to +85˚C ranges unless otherwise specified

Symbol Parameter Min Typ Max Units

Figure 3

CLHT CMOS/TTL Low-to-High Transition Time (

CHLT CMOS/TTL High-to-Low Transition Time (

RSPos0 Receiver Input Strobe Position for Bit 0 (Note 7)(

RSPos1 Receiver Input Strobe Position for Bit 1 4.5 5.0 5.8 ns

RSPos2 Receiver Input Strobe Position for Bit 2 8.1 8.5 9.15 ns

RSPos3 Receiver Input Strobe Position for Bit 3 11.6 11.9 12.6 ns

RSPos4 Receiver Input Strobe Position for Bit 4 15.1 15.6 16.3 ns

RSPos5 Receiver Input Strobe Position for Bit 5 18.8 19.2 19.9 ns

RSPos6 Receiver Input Strobe Position for Bit 6 22.5 22.9 23.6 ns

) 2.2 5.0 ns

Figure 3

) 2.2 5.0 ns

Figure 17

) f = 40 MHz 1.0 1.4 2.15 ns

www.national.com5