查询DS90CP04供应商

DS90CP04 4 × 4、低消費電力、2.5Gb/s、LVDS デジタル・クロスポイント・ス イッチ

2004 年 1 月

converted to nat2000 and removed application division saying TBD

Converted to nat2000 DTD

correct pkg added, format errors corrected (JFG)

new datasheet to be created by RRD)

ds200287

11800

23900

33020

20010301

DS90CP04

4 ×4、低消費電力、2.5Gb/s、LV DS デジタル・クロスポイ ント・スイッチ

DS90CP04

4 × 4、低消費電力、2.5Gb/s、LV DS デジタル・クロスポイント・スイッチ

概要

DS90CP04 は 4 ×4 のデジタル・ クロスポイント・スイ ッチ です 。効

率よく基 板レイアウ トが行えるよ うに入 力 端 子と出力 端 子をパッ

ケージの対向両辺に配置しています。低電圧差動信号(LVDS)

技術を採用し、低消費電力と高速動作の両立を実現していま

す。デー タ・パスは、ノイズを抑えるために入力か ら 出力まです

べて差動回路で構成されています。ノン・ブロッキング・アーキテ

クチャ方式により、 任 意 の入 力ビットから任 意の 出 力ビット ( 単出

力または複数の出力 ) への接続が可能で す。スイッチ・マトリッ

クスとして 4 組の差動 4:1 マルチプレ クサを内蔵しています。 各

マルチプレクサには 4 入力系統がすべて接続されており、任意の

出力チャネルから任意の 1 入力系統を出力できます。DS90CP04

の各出力ペア は 、それぞれが独立して最高 2.5Gbit/s で動作しま

す。

MODE 端子によって、制御が 容 易なシリアル制御インタフェース、

または構成 選 択ポー トを切り替えられ ます。シリア ル制御 インタ

フ ェース を用いる と、全出力に対する新規のスイッチ構成情報を

単一のロード・コマン ドによ って一度に更新で きます。 直接構成

ポートを使用する と、SEL0/1 端子の論理レベルでデコードされた

情報にもとづき、出力の構成を直接変更できます。

特長

■ 2.5Gbps の完全差動データ・パス

■ノン・ブロッキン グ・アーキテ クチ ャ

■ 任意の入力からのブロー ドキャス ト

■ 対向両辺に配置された端子配置

■ 大規模スイッチ・アレイへ の 拡 張が 可 能

■ LVDS/BLVDS/LVPECL/2.5V-CML 入力レベルに対応

■ TRI-STATE LVDS 出力

■読み出し可能なシリアル制御イ ンタフェース

■ 2 段階のレジス タ書き込み

■+2.5V 単一電源

■ 低消費電力、2.5Gb/s で575mW (typ)

■リードレス LLP-32 パッケージ ( 本体サイズ6 ×6mm)

■アドバンス トCMOS プロ セス技術で製造

updated limits (LMS)

changed datasheet title in pid source to match document title

Removed preliminary. Removed old CP44 pin names and replaced with updated CP04 pin names. Removed TBD from jitter note in AC table.

removed incorrect artwork, included correct order numbers, and changed all references from Vss to GND. No limit changes (LMS)

removed duplicate colspec from thead in table 3

DS90CP04

機能ブロ ッ ク図

© National Semiconductor Corporation DS200287-07-JP

20021023

1

機能ブロ ッ ク図 ( つづき)

DS90CP04

www.national.com/JPN/

2

ピン配置図

DS90CP04

Order Number DS90CP04TLQ, DS90CP04TLQX (Tape and Reel)

See NS Package Number LQA32A

3

www.national.com/JPN/

端子説明

端子名 端子番号 入出力、タイプ 説明

各マルチプレク サに共通の差動入力

DS90CP04

IN1 +

IN1 −

IN2 +

IN2 −

IN3 +

IN3 −

IN4 +

IN4 −

差動スイッチ出 力

OUT1 +

OUT1 −

OUT2 +

OUT2 −

OUT3 +

OUT3 −

OUT4 +

OUT4 −

デジタル制 御インタフェース

SCLK 6 I, LVCMOS SI から入力されるプログラミング・データをラッチする制御クロックです 。 SCLK は

SI / SEL1 7 I, LVCMOS スイ ッチ構成を指定するプログラミング・データ入 力です 。 データは SCLK の立ち上がり

SEL0 5 I, LVCMOS スイ ッチ構成を指定するプログラミング・データです。

CSO

RSO

CSCLK

RSCLK

LOAD 22 I, LVCMOS LOAD 信号が HIGH のと きSCLK をLOW から HIGHに遷移させる と、デバイスは

MODE 23 I, LVCMOS MODE が LOW のと きSCLK 入力はアクティブとなり、バッ ファされた SCLK 信号が

POWER

V

DD

GND 4, 20, 21,

16

15

14

13

12

11

10

9

25

26

27

28

29

30

31

32

18

2

19

3

1, 8, 17, 24 I, Power V

DAP

I, LVDS 反転および非反転差動入力

I, LVDS 反転および非反転差動入力

I, LVDS 反転および非反転差動入力

I, LVDS 反転および非反転差動入力

O, LVDS 反転および非反転差動出力。IN1 ±、IN2 ±、IN3 ±、IN4±の任意の差動ペアを

O, LVDS 反転および非反転差動出力。IN1 ±、IN2 ±、IN3 ±、IN4±の任意の差動ペアを

O, LVDS 反転および非反転差動出力。IN1 ±、IN2 ±、IN3 ±、IN4±の任意の差動ペアを

O, LVDS 反転および非反転差動出力。IN1 ±、IN2 ±、IN3 ±、IN4±の任意の差動ペアを

O, LVCMOS MODE がLOW のとき、シリアル・チェーンの次段のデバイ スに向けて、コントロール・

O, LVCMOS MODE がLOW のとき、これら端 子からは制 御クロ ックSCLK をバ ッファしたクロック信

I, Power LVDSとCMOS 回 路 のグラウンド基準です。LLP-32 パ ッ ケージの下面には DAP があ

OUT1 ±か ら出力可能

OUT2 ±か ら出力可能

OUT3 ±か ら出力可能

OUT4 ±か ら出力可能

0MHz から 100MHz に対 応しています。 デバイ スにアクセスするときのみ、SCLK にク

ロック・パルス列を与えて ください。 プログラ ミング完了後は、高速差動データ・パスに

対す るノイズ 混 入を防ぐため、 SCLK は論理 LOW に保持し てください。

クロックで内 部バッファ・ レジスタ にラ ッチされます。

デー タ が CSO(RSO) からシフ ト出力されま す。 CSO(RSO) から出力されるコントロール・

デー タは SI に入力されたデータと同じですが、デバイスのコラ ム ( ロー )・ア ドレスは内

部で 1 ずつ減算されて、チェーンの次段のデバイスに伝達されます。CSO(RO) は

SCLK の立ち上がりエッ ジに同期して出力されます。

号が出 力されます。 カスケー ド接続 した シ リアル制御バスで、CSCLK(RSCLK) はシ リ

アル・チ ェー ンの次段のデバイ ス に対する ク ロックとして使用 し ます。

ロー ド・レジス タに書き込まれているプロ グラ ミング・データを構成レジス タに転送しま す 。

このタ イミングで全出力端子は新規のスイッチ 構 成に 切り替 わります。 LOAD 信号は1

SCLK サイ クルのみ HIGH にしてください。 LOAD 信号をHIGH のま ま保持する と構

成レジスタへの転 送が繰り返し発生します。

CSCLK/RSCLK 端子から出力されます。MODE が HIGH のと き、SCLK 信号はレジ

スタ回 路と内 部 ステート・マシンか ら切り 離さ れま す。 MODE が LOW にな る まで内部レ

ジスタ側から見た場合、負論理状態になっています。

は2.5V ±5%です。 4 個以上の低ESR 0.01μF のバイパス・コン デ ン サをVDDと

DD

GND 間に接続してください 。

り金属コンタ クト が露出してい ま す。DAP はデバイ スの主と なるグ ラウ ン ドにな ります 。 最

適な AC および熱性能を得るため、4 個以上のビアでグラウンド層に接続 してください。

www.national.com/JPN/

4

シリアル ・インタフェース真 理値表

LOAD MODE SCLK 生じる動作

00LHSI端子の現在のレベルが入力シフト・レジスタにクロック転送されます。

0 1 LH SCLK 入力を内部レジスタ およ び 内部ステー ト ・マシ ン入力から切り 離し ま す。 MODE が

再び LOW になる まで RSCLKとCSCLK には LOW が出力されます。下記の「構成選

択真理値表」を参照してください。

LH 0 X 最後の有効フ レームから OUT1 〜OUT4 構成情報をロードします 。 ロード・レ ジスタ の内

容は構 成レジスタ に転送されます。 スイ ッチ構 成は SCLK 入力とは非同期に更新されま

す。

1 1 LH SCLK 入力を内部レジスタ およ び 内部ステー ト ・マシ ン入力から切り 離し ま す。 MODE が

再び LOW になる まで RSCLKとCSCLK には LOW が出力されます。下記の「構成選

択真理値表」を参照してください。

構成選択真理値表

MODE SEL1 SEL0 生じ る動作

0XXSEL0/1端子は構成選択モードでのみ機能します。以下を参照してください。

100分配 : IN1 - OUT1 OUT2 OUT3 OUT4

101分配 : IN2 - OUT1 OUT2 OUT3 OUT4

110冗長 : IN1 - OUT1 OUT2、IN3 - OUT3 OUT4

111対向接続 : IN1 - OUT1、IN2 - OUT2、IN3 - OUT3、IN4 - OUT4

DS90CP04

LH: LOW から HIGH への遷移 ( 立ち上が りエッジ )

X: ドン ト・ケア

5

www.national.com/JPN/

構成選択真理値表( つづき)

DS90CP04

www.national.com/JPN/

FIGURE 1. DS90CP04 Configuration Select Decode

6

絶対最大定格 (Note 1)

本データ シートには軍用・航空宇宙用の規格は記載されていません。

関連する電気的信頼性試験方法の規格を参照ください。

電源電圧 (V

CMOS/TTL 入力電圧 −0.3V 〜(V

) −0.3V 〜+ 3V

DD

+0.3V)

DD

LV DS レシーバ入力電圧 −0.3V 〜+ 3.3V

LV DS ドライバ出力 電 圧 − 0.3V 〜+ 3V

LV DS 出力短絡電流 40mA

最大接合部温度 +150 ℃

保存温度範囲 −65 ℃〜+ 150 ℃

リード温度 ( ハンダ付け 4 秒 ) +260 ℃

25 ℃でのパッケージ最大消費電力

LLP-32 3200 mW

ディ レーテ ィ ング 25 ℃以上で 38mW/ ℃

熱抵抗θ

JA

ESD 耐圧

人体モデル、1.5kΩ、100pF

LVDS 出力 >1.0kV

LVDS 入力 >1.5kV

その他の ピン >4.0kV

EIAJ、0Ω、200pF > 100V

推奨動作条件

最小値 代表値 最大値 単位

電源電圧 (V

レシーバ入力電圧 0.05 3.3 V

動作周囲温度 −40 25 85 ℃

接合部温度 110 ℃

– GND) 2.375 2.5 2.625 V

DD

電気的特性

特記のない限り、推奨動作条件の電源電圧と動作周囲温度を対象

Symbol Parameter Conditions Min

LVCMOS/LVTTL DC SPECIFICATIONS (SCLK, SI/SEL1, SEL0, LOAD, MODE , CSCLK, RSCLK, CSO, RSO)

V

V

I

IH

I

IL

C

C

V

V

V

IH

IL

IN1

OUT1

CL

OH

OL

High Level Input Voltage

Low Level Input Voltage

High Level Input Current V

Low Level Input Current V

IN=VDD=VDDMAX

IN=VSS

, V

DD=VDDMAX

Input Capacitance Any Digital Input Pin to V

Output Capacitance Any Digital Output Pin to V

Input Clamp Voltage I

High Level Output Voltage I

Low Level Output Voltage I

=− 18 mA

CL

=− 4.0 mA, VDD=V

OH

I

=− 100 μA, VDD=2.5V

OH

=4.0 mA, VDD=V

OL

I

=100 μA, VDD=2.5V

OL

DDMIN

SS

SS

DDMIN

1.7 V

GND 0.7 V

−10 +10 μA

−10 +10 μA

−1.5 − 0.8 V

1.9 V

2.4 V

LVDS INPUT DC SPECIFICATIONS (IN1 ±, IN2 ±, IN3 ±, IN4 ±)

V

V

V

V

C

I

TH

TL

ID

CMR

IN2

IN

Differential Input High Threshold

(Note 3)

Differential Input Low Threshold V

Differential Input Voltage V

Common Mode Voltage Range V

=0.05V or 1.2V or 2.45V,

V

CM

V

=2.5V

DD

=0.05V or 1.2V or 2.45V,

CM

V

=2.5V

DD

=2.5V, VCM=0.05V to 2.45V

DD

=100 mV, VDD=2.5V

ID

Input Capacitance IN + or IN− to V

Input Current V

=2.5V, VDD=V

IN

V

=0V, VDD=V

IN

SS

DDMAX

DDMAX

or 0V

or 0V

−50 0 mV

100 V

0.05 3.25 V

−10 +10 μA

−10 +10 μA

LVDS OUTPUT DC SPECIFICATIONS (OUT1 ±, OUT2 ±, OUT3 ±, OUT4 ±)

V

ΔV

V

ΔV

OD

OD

OS

OS

Differential Output Voltage

(Note 3)

Change in VOD between

Complementary States

Offset Voltage (Note 4)

Change in VOS between

Complementary States

=100Ω between OUT + and

R

L

OUT −Figure 2

250 400 475 mV

−35 35 mV

1.125 1.25 1.375 V

−35 35 mV

Typ

(Note 2)

3.5 pF

5.5 pF

050mV

3.5 pF

26.4 ℃/W

Max Units

DD

V

0.4 V

0.1 V

DD

mV

DS90CP04

7

www.national.com/JPN/

電気的特性( つづき)

特記のない限り、推奨動作条件の電源電圧と動作周囲温度を対象

Symbol Parameter Conditions Min

DS90CP04

LVDS OUTPUT DC SPECIFICATIONS (OUT1 ±, OUT2 ±, OUT3 ±, OUT4 ±)

I

OZ

I

OFF

I

OS

I

OSB

C

OUT2

SUPPLY CURRENT

I

CCD

I

CCZ

SWITCHING CHARACTERISTICS ─ LVDS OUTPUTS (Figures 3、5、6)

t

LHT

t

HLT

t

PLHD

t

PHLD

t

SKD1

t

SKCC

t

JIT

Output TRI-STATE Current TRI-STATE Output

Power Off Leakage Current V

Output Short Circuit Current, One

Complementary Output

Output Short Circuit Current, both

Complementary Outputs

V

OUT=VDD

DD

OUT + or OUT− Short to GND −15 − 40 mA

OUT + or OUT− Short to V

OUT + and OUT− Short to GND − 15 −30 mA

OUT + and OUT− Short to V

=0V, V

or V

SS

=2.5V or GND

OUT

DD

Output Capacitance OUT + or OUT − to GND when

TRI-STATE

Total Supply Current All inputs and outputs enabled,

terminated with differential load of

100Ω between OUT + and OUT −.

TRI-STATE Supply Current TRI-STATE All Outputs

Differential Low to High

Transition Time

Differential High to Low

Use an alternating 1 and 0 pattern

at 200 Mb/s, measure between

20% and 80% of V

OD

.

Transition Time

Differential Low to High

Propagation Delay

Differential High to Low

Use an alternating 1 and 0 pattern

at 200 Mb/s, measure at 50% V

between input to output.

Propagation Delay

Pulse Skew |t

PLHD–tPHLD

|

Output Channel to Channel Skew Difference in propagation delay

(t

PLHD

or t

) among all output

PHLD

channels in Broadcast mode (any

one input to all outputs).

Jitter (Note 5)

CM

OD

Typ

(Note 2)

Max Units

−10 +10 μA

−10 +10 μA

15 40 mA

15 30 mA

5.5 pF

220 300 mA

10 20 mA

100 135 160 ps

100 135 160 ps

500 750 1200 ps

500 750 1200 ps

030ps

0 50 100 ps

t

ON

t

OFF

t

SW

www.national.com/JPN/

Alternating 1 and 0 Pattern

750 MHz 1.6 2.5 psrms

1.25 GHz 1.6 2.5 psrms

K28.5 Pattern

1.5 Gb/s 10 40 psp-p

2.5 Gb/s 27 60 psp-p

23

PRBS 2

-1 Pattern

1.5 Gb/s 25 40 psp-p

2.5 Gb/s 40 70 psp-p

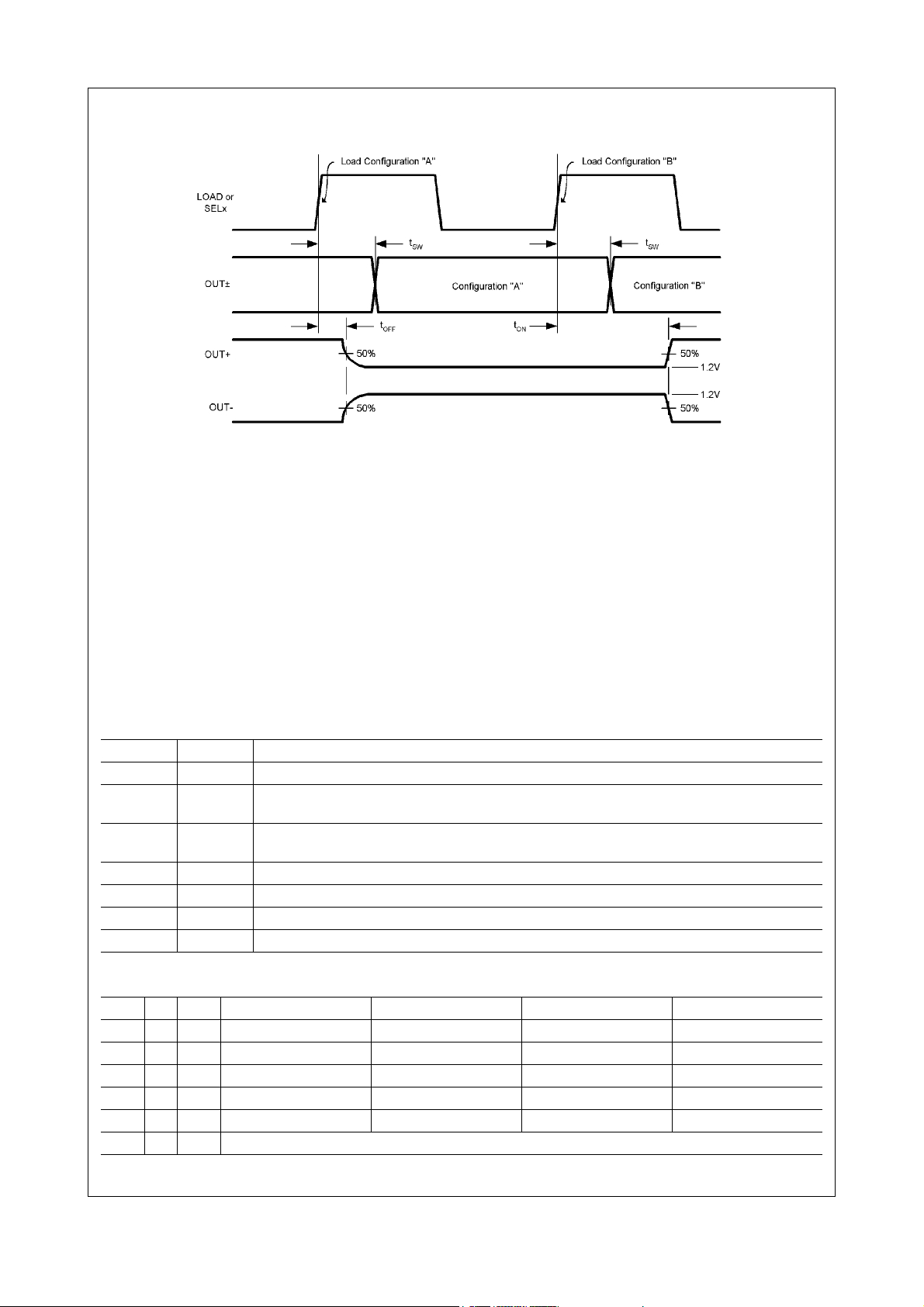

LVDS Output Enable Time Time from LOAD =LH or SELx to

OUT ± change from TRI-STATE to

active.

LVDS Output Disable Time Time from LOAD =LH or SELx to

OUT ± change from active to

TRI-STATE.

LVDS Switching Time Time from LOAD =LH to new

switch configuration effective for

OUT ±.

8

50 150 300 ns

35ns

50 150 ns

電気的特性( つづき)

特記のない限り、推奨動作条件の電源電圧と動作周囲温度を対象

Symbol Parameter Conditions Min

SWITCHING CHARACTERISTICS ─ LVDS OUTPUTS (Figures 3, 5, 6)

t

SEL

SWITCHING CHARACTERISTICS ─ Serial control Interface (Figures 4, 8, 9)

F

SCLK

T

DCCLK

t

S

t

H

t

DSO

t

DSCLK

t

DSDIF

T

RISE

T

FAL L

SELx to OUT ± Configuration select to new data at

OUT ±.

SCLK Clock Frequency

CSCLK Duty Cycle

Input SCLK Duty Cycle set at 50%

RSCLK Duty Cycle

SI–SCLK or MODE–SCLK Setup

Time

SCLK–SI or SCLK–MODE Hold

Time

From SI or MODE Input Data to

SCLK Rising Edge

From SCLK Rising Edge to SI or

MODE Input Data

SCLK to RSO or CSO Delay From SCLK to RSO or CSO 1.5 4 ns

SCLK to RSCLK or CSCLK

From SCLK to RSCLK or CSCLK

Delay

|SCLK to RSCLK or CSCLK–

SCLK to RSO or CSO|

Logic Low to High Transition

Time

Logic High to Low Transition

Time

Propagation Delay Difference

between t

DSO

and t

DSCLK

20% to 80% at RSO, CSO, RSCLK,

or CSCLK

80% to 20% at RSO, CSO, RSCLK,

or CSCLK

DS90CP04

Typ

(Note 2)

50 150 ns

0 100 MHz

45 55 %

1.5 ns

1ns

4.0 8.5 ns

1.5 4.5 ns

1.5 ns

1.5 ns

Max Units

Note 1: 「絶対最大定格」とは、この値を超えるとデバイスの安全を保障できない制限値を意味します。デバイスがこの規格値で正常に動作することを意味 して

いるわけではありません。

Note 2: 代表値はV

Note 3: 差動出力電圧V

Note 4: 出力オフセット電圧 V

Note 5: 任意の入力から任意の1 つの差動 LVDS 出力に対する、規定のデ ータレー トとデータパターンで動 作している ときの仕様規定で、このとき残り の 3 チャネ

ルは試験対象チャネルとは非同期の 1.25Gb/s の K28.5 パターンで動 作させています。 ジッタは、製造 時に検 査 はなされません が 、 サンプルにもとづく 特

性を通して保証されています。ラン ダム・ジッタは 1,000 回分のヒストグラムのピーク・ツー・ピーク として測定さ れま す。 なお K28.5 パターンは、ビット・ス

トリーム 00 11111010 1100000101 の繰 り 返 しです。確定的ジ ッタ(DJ パターン ) は、サ ンプル回数 350 回のヒス トグラムの 平 均と して測定されています 。

総ジッタ(TJ) は、3,500 回分のヒストグラムで、ランダム・ジ ッタと同様にピーク・ツー・ ピークとして測 定されています。

=2.5V、TA=25 ℃で測定されています。代表値は参照を目的としており、製造時検査は行っていません。

DD

は|OUT +− OUT −| として定義されています。差動入力VIDは|IN +− IN −|として定義さ れています。

OD

は、LVDSシングル・エン ド出力の論理 HIGH 電圧と論理 LOW 電圧の平均として定 義されています。

OS

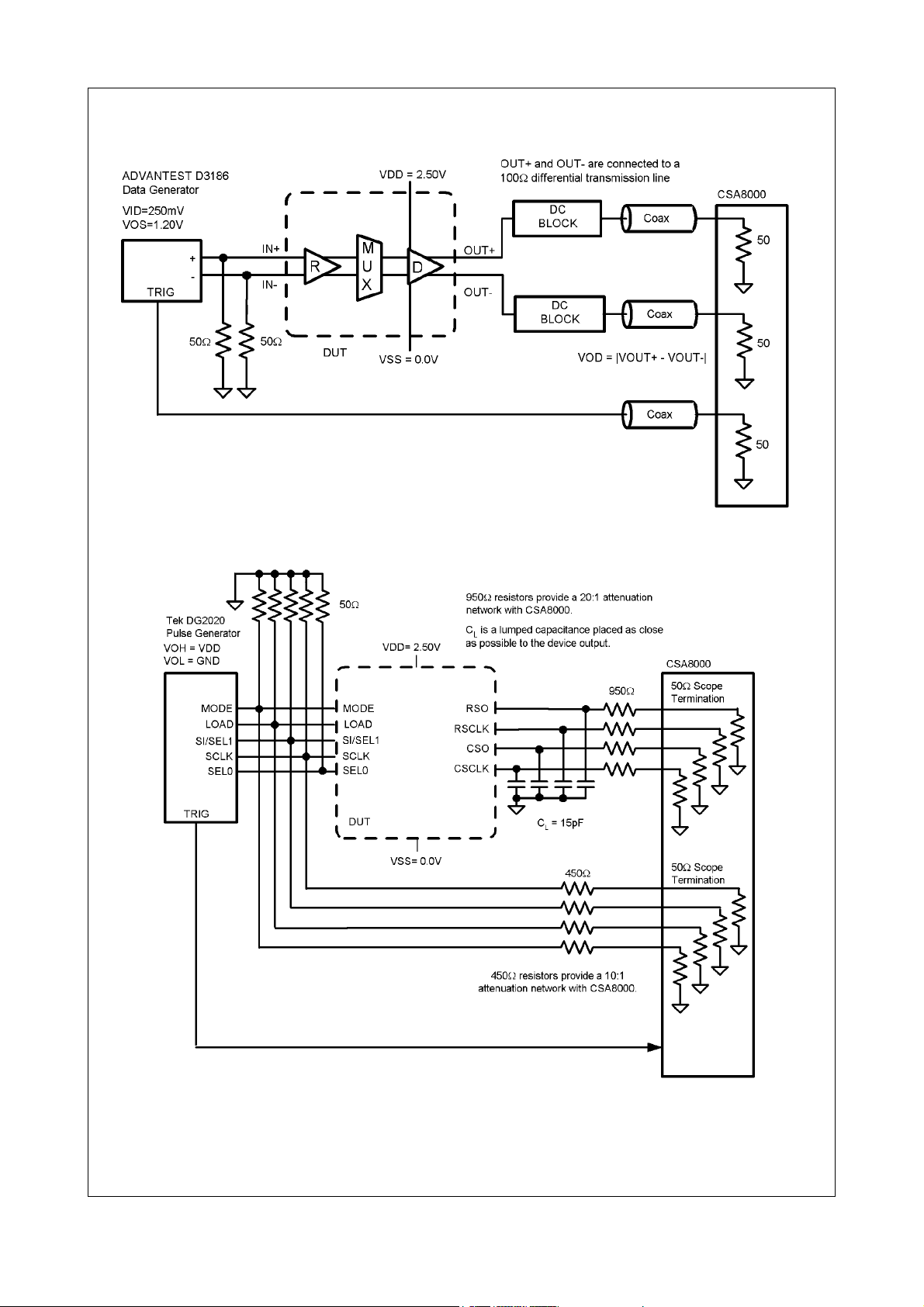

FIGURE 2. Differential Driver DC Test Circuit

9

www.national.com/JPN/

電気的特性( つづき)

DS90CP04

FIGURE 3. Differential Driver AC Test Circuit

www.national.com/JPN/

FIGURE 4. LVCMOS Driver AC Test Circuit (Note 6)

10

電気的特性( つづき)

Note 6: LVC M OS 入 力と出 力の AC 仕様は、Figure 4 に示される電力スプリッタではなく、入力減衰ネットワーク を使用しても検証および検査が可 能 です。

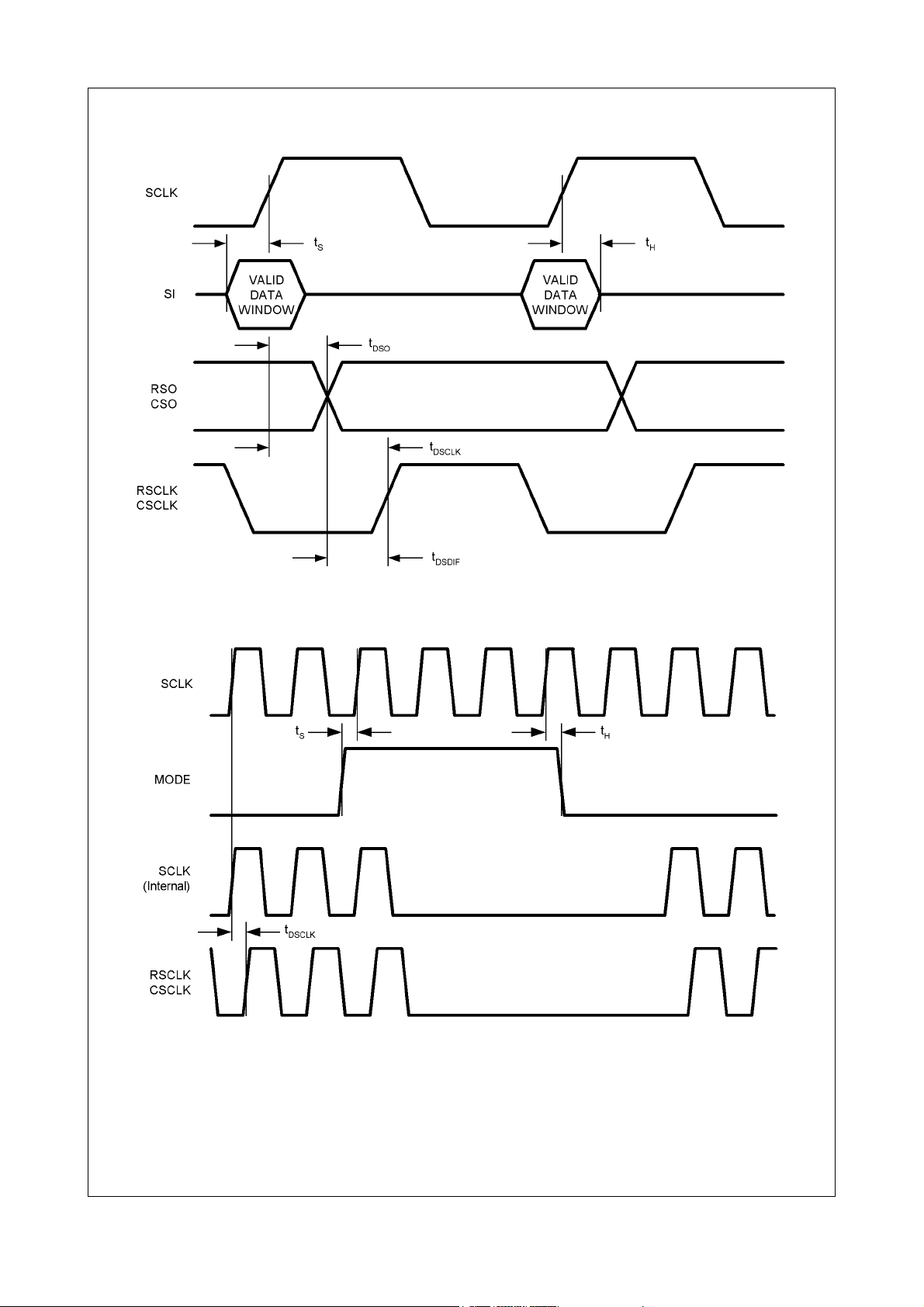

FIGURE 5. LVDS Signals

DS90CP04

FIGURE 6. LVDS Output Transition Time

FIGURE 7. LVDS Output Propagation Delay

11

www.national.com/JPN/

電気的特性( つづき)

DS90CP04

FIGURE 8. Serial Interface Propagation Delay and Input Timing Waveforms

www.national.com/JPN/

FIGURE 9. Serial Interface ─ MODE Timing and Functionality

12

電気的特性( つづき)

機能説明

DS90CP04

FIGURE 10. Configuration and Output Enable/Disable Timing

シリアル ・インタフェースによるプログラミング

シリアル・ク ロック SCLK とシリアル入力データライン SI で構成 さ

れる単純なシ リアル・ インタフェースを介して、内 部マルチプレクサ

に構成をプログラムできます。シリ アル・イ ンタフェースは、大規模

スイ ッチ・アレイに容 易に拡 張 できるよう に 設 計され ています。

DS90CP04 で構成したマトリックス ・アレイ の次 段のロー・デバイ

スは、 バッファされたシリアル ・ インタフェース出力 (RSCLK、RSO)

を使って接続します。 同様に、マトリックス・アレイの 次 段のコラ

ム・デバイスは、バッ ファ されたシリアル・イ ンタ フェース出 力

(CSCLK、CSO) を使っ て接続 し ま す。こ の フィードスルー される

RSCLKとRSO、CSCLKとCSO の各バッファ信号を使用する方

式に より、 ユーザー は単一のバス (SCLK とSI) でマトリックス内の

すべてのデバイス を プログラ ム でき ます

スイ ッチの構 成をプログラムするには、デバイスに 30 ビットの制 御

ワー ドを与えます。 最 初の 6 ビットでスタート・フレームが SI へシ

フトインされます。有効スタート・フ レーム には、構成ロードの 1FH

と、構成読み出しの 1EH の 2 種類があります。 スター ト・フレー

ムに続いて、アク セスするデバイスのロー・ア ドレスとコラム・ア ド

レス、さ らに 4 チャネル分のス イ ッチ 構 成 データが送られます 。

Table 1. 30-Bit Control Wordおよび Table 2. Switch Configuration

Data に制御 ワードのビ ット定義を示します。D29 がSI にシ フトイン

される先頭ビ ットです 。

TABLE 1. 30-Bit Control Word

ビッ トビット長 説明

D29–D24 6 制御ワード同期用のスタート・ フレームです。 (01 1111'b =LOAD)

D23–D18 6 アク セスするデバイ スのロ ー・アドレスを 指 定します。 シリアル・イ ンタフェースは最 大 64 個のロー ・デバイ

スをアクセスできます。

D17–D12 6 アクセスするデバイスのコラ ム・ア ドレスを指 定します 。 シリアル・イ ンタフェースは最 大 64 個のコラム・ デ

バイスをアクセスでき ます。

D11–D9 3 出力 1 用のスイッチ構 成を指 定します 。 Table 2. Switch Configuration Dataを参照し て ください。

D8–D6 3 出力 2 用のスイッチ 構 成を指 定します 。 Table 2. Switch Configuration Dataを参照 してく ださい。

D5–D3 3 出力 3 用のスイッチ 構 成を指 定します 。 Table 2. Switch Configuration Dataを参照 してく ださい。

D2–D0 3 出力 4 用のスイッチ 構 成を指 定します 。 Table 2. Switch Configuration Dataを参照 してく ださい。

TABLE 2. Switch Configuration Data

MSB LSB OUT1 ±に対する接続 OUT2 ±に対す る 接続 OUT3 ±に対する 接続 OUT4 ± に対する 接続

000出力1 はTRI-STATE

001IN1± IN1 ± IN1 ± IN1 ±

010IN2± IN2 ± IN2 ± IN2 ±

011IN3± IN3 ± IN3 ± IN3 ±

100IN4± IN4 ± IN4 ± IN4 ±

101無効。

出力 2 はTRI-STATE 出力3 はTRI-STATE 出力 4 はTRI-STATE

13

www.national.com/JPN/

機能説明( つづき)

TABLE 2. Switch Configuration Data ( つづき)

MSB LSB OUT1 ±に対する接続 OUT2 ±に対す る 接続 OUT3 ±に対する 接続 OUT4 ± に対する 接続

110これら無効の組み合わせは同期の喪失を招きます。

DS90CP04

111

ローおよびコ ラム・ア ドレッシング

デバ イスを N ×Nアレイで構成した場合、左上のデバイスがロー・

アドレス、コラム・ア ドレスともゼロに割り当て られます。 右 側に続

くデバイスがコラム・ア ドレス 1 から N、対して下側に続くデバイス

がロー ・ アドレス 1 から N となります。システムのシリ アル制御イン

タフェース (SCLK とSI) は、ロー・ア ド レス、コラ ム・ア ドレスとも

にゼロ のデバ イスに接続し ま す。シリ アル制御インタフェースから、

アクセスしたいデバイ スのロー・ ア ドレスとコラム・アドレスを含む 制

御ワードがシ フト・インされます。 制 御 データがデバイスに与えられ

ると、次のローおよ びコラム・デバイ スに送られる前に、制御ワー

ド内のアドレスは内部で1 だけ減算さ れま す。ロー ・アドレスが 1

だけ減 算された制 御 データがコラム ・イ ンタ フェース (CSO と

CSCLK) から送出され、コラ ム・ア ドレスが 1 だけ減算さ れた制

御データがロー・イ ンタフェース (RSO とRSCLK) からシフ ト・アウ

トされます。プログラ ミングの対 象となるデバイスに制 御ワードが到

達した時点では、ロー・アドレス とコラム・ア ドレスはともにゼロと

なっています。

アレイ内の 各デ バイスは、 常に 開 始フレームの 受 信をチェックして

います (D29 〜24 =01 1111'b または 01 1110'b)。適正な開始 フ

レーム・ストリングを検出し、かつ続くロー・アドレスとコラム・ア ド

レスがともにゼロであった場 合、そ の デバイスは 30 ビット制 御ワー

ドのスイッチ構成データをロー ド・レジス タに格 納します。

アレイ内の 各デ バイスは、シリアル・イ ンタフェースを介して順にプ

ログラムされます。アレイ全 体 のプログラ ミ ングが完了したら、

LOAD 端子にHIGH パル スを与え て、各デバ イス の ロ ード・レジ

スタの 内 容を構 成レジスタに 転 送します 。LOAD パル スの発行は、

制御ワードの最終ビットがロー ド・レジスタ に格 納されるまで待たな

ければなりません。 この タイミングが保証 さ れる のはプ ロ グ ラムが完

了した 2 クロック後です。

アレイのプログラムでは、内部シフト・レジスタ で生じる追 加の SCLK

サイ クルを 考 慮しなければなりません。次段に与える制御データが

RSO とCSO に現れるまでのレイテンシは、立ち上がりエッ ジ 7 ク

ロック(SCLK) 分です 。アレイ内の目的とするデバイスに 制 御ワー

ドを届けるためには、設計者は正しいクロック数を与える必要があ

ります。 4 デバイスをシリアル・チェーン接続した場 合の制御ワー

ドの例を Table 3. Example to Program a 4 Device Arrayに示し ま

TABLE 3. Example to Program a 4 Device Array

す (OUT1 =IN1、OUT2 =IN2、OUT16 =IN16)。このアレイ

のプロ グラ ムには、シリアル・チェー ンを介して目的とするデバイス

に届け るため に、4 組の 30 ビット制御ワードが必要です。ア レ イ

全体を 120 クロック・ サイクルでプログラミングするには、チェーン

の最後にあるデバイスからプログラミングをしていくことが 重 要 で

す。続くプログ ラ ミング・データによって、最初 のデータはチェーン

を通 して正し いデバイスに向かっ て押し込まれてい きます。

スイ ッチ構成の読 み出し

DS90CP04 に読み出し用の開始 フレーム (01 1110'b) を送ると読

み出 し モードにな ります。読み出し開始フ レームを受信する と構成

レジスタ情報はシフ ト ・レジス タに転 送され、制御ワー ドの OUT1

〜OUT4 のビット・セグメントの 読 み出し値が RSOとCSO の両方

から出力されます。デバイスから読み出されたデー タは、デフォル

ト・ア ドレス (11 1111'b) が1ずつ内部で減算さ れなが ら 次段のデ

バイ スを順に通って送られます。ロー最後尾にあるデバイスの

RSO には、読み出しデバイスを始点とする「相対的」なコラム・

アドレス が現れるため、送出デバ イスのコラム位置を求められま

す。同様に、コ ラ ム最後尾にあ るデバイスの CSO には、送出デ

バイ スの相対ロー・ア ドレスが 現 れます 。 チャネル構 成 情 報 が挿

入 された読み出し制御ワードの送出後、デバイ スは自動的に書き

込みモ ードに戻り、SI から入力される新規の制御ワードを待ちま

す。

Table 4. A Read-Back Example from a 4 Device Array に、4 ×4

デバ イス・ アレイ の先頭のローに ある 4 個のデバイスから構成レジ

スタを読み出す例を示します。す でに述べたように、アレイ読 み 出

しの完了に も 、 内部シ フト・レジスタのレイテンシ分を充当するだけ

の追加 SCLK サイ クルが 必 要 です 。 4 組分の 30 ビットの構成レ

ジス タをシフ ト・アウ トするには、4 ×30 SCLKクロック・サイ クルに

加え、デバイス・レイテンシ分と してデバイ ス 1 個あたり 7 SCLK

サイ クルが 必 要 で、合 計 SCLK 数は 148 になります 。シリ アル化

された読み出しデ ータは、ロー最後尾のデバイスRSOからRSCLK

に同期 して出力されます。 4 組分の構 成データの読み出しをシフ

ト・インしたあ と は、SI をLOW にしておくことを推奨 し ま す。

ロー・

フレーム

D29:D24

01 1111 00 0000 00 0011 001 010 011 100 30 0, 3

01 1111 00 0000 00 0010 001 010 011 100 30 0, 2

01 1111 00 0000 00 0001 001 010 011 100 30 0, 1

01 1111 00 0000 00 0000 001 010 011 100 30 0, 0

プロ グラミン グ工程のア レ イ・レ イテン シ を最小にする ため、システムの SI 入力から最も遠いデバイスの

すべて のチャネル情報がロード・ レジスタ に到達してからすべてのスイッチが構成可能になるまでに

www.national.com/JPN/

アドレス

D23:D18

コラム・

アドレス

D17:D12

構成情報からシフト・インして く ださい。

2 クロック・ サイクルの遅 延が 必 要 です 。

OUT1

D11:D9

OUT2

D8:D6

14

OUT3

D5:D3

OUT4

D2:D0

SCLK

サイ クル数

2

制御ワードのア

レイ内アクセス

先デバ イス

ロー、コラム

機能説明( つづき)

DS90CP04

TABLE 4. A Read-Back Example from a 4 Device Array

ロー・

フレーム

D29:D24

01 1110 00 0000 11 1111 000 000 000 000 30

01 1110 00 0000 11 1110 000 000 000 000 30

01 1110 00 0000 11 1101 000 000 000 000 30

01 1110 00 0000 11 1100 001 010 011 100 30

Note 7: 書き込みと読み出しのプログラ ミング 例は、Figure 11に示される16× 16 ア レイ構成に基づいています 。別のアレイ構成ではプログ ラミング順は異なります。

アドレス

D23:D18

最小プログラミング・レイテンシとなるスイッチ拡張

プロ グラミング・デー タは、ロー方向は RSOとRSCLK を通っ て、

コラム方向は CSOとCSCLK を通 っ て伝え ら れ ま す。 すべてのデ

バイ スの LOAD 端子は電気的に共通に接続し、同一信号で駆

コラム・

アドレス

D17:D12

OUT1

D11:D9

OUT2

D8:D6

OUT3

D5:D3

動します。 LOAD の信号品質に影響を与えないよう、アレイ内の

スタブ 長 が 極 端 に 長くならないように配 線して ください。 大 規模ク

ロスポイ ント・アプリケーションの場合、LOAD 信号は各ローまた

は各カラムごとに分 配 することを推奨します。

OUT4

D2:D0

SCLK

サイ クル数

説明

Read-Back

(R,C) =0, 3

Read-Back

(R,C) =0, 2

Read-Back

(R,C) =0, 1

Read-Back

(R,C) =0, 0

FIGURE 11.

15

www.national.com/JPN/

プログラミ ングの例

構成書き込み

30ビット制御ワー ド : [ 書き込み フレーム ][ ロー・ア ドレス ][ コラ ム・ア ドレス ][OUT1][OUT2][OUT3][OUT4]

DS90CP04

アレイ書き込み :

[01 1111] [0][1] [1][1][1][1] //* アレイ位 置 1、ブロードキャス トIN1 *//

[01 1111] [0][0] [2][2][4][4] //* アレイ位 置 0、IN2 をOUT1とOUT2 に接続、IN4をOUT3とOUT4 に接続 *//

LOAD =H、SCLK =LH

デバイス0 書き込みプログラ ミング・シーケンス

SCLK 数イベントの説明

6 デバイス0 (R =0、C =0) は第 1 の制御ワードの「書 き込み」フレームを検出しま す。

18 デバイス0 (R =0、C =0) は第 1 制御ワードのア ドレスがロー= 1、コラ ム= 0 である こ とを識別し ま す。 第 1 の制御

ワー ドから ロー・アドレスが 1 だけ減算 さ れ ( ロー・ア ドレス= 0) RSO に送ら れます。

36 デバイス0 (R =0、C =0) は第 2 の制御ワード の「書き込み」フレ ームを検出し ます。

48 デバイス0 (R =0、C=0) は第 2 の制御ワードがロー = 0、コラム= 0 である こ とを識別します。これは有効な構成書き

込み アドレスのため、デバ イス 0 は構成情報の受信を待ちます。

60 デバイス0 (R =0、C =0) は構成情報を受信しLOAD を待ちます。

デバイス1 書き込みプログラ ミング・シーケンス

SCLK 数イベントの説明

13 デバイス1 (R =1、C =0) は第 1 の制御ワード の「書き込み」フレ ームを検出し ます。

25 デバイス1 (R =1、C =0) は第 2 の制御ワードのア ドレスがロー= 0、コラ ム= 0 である こ とを識別します。これは 有効

な構成書き 込み アドレス のため、デバイス 1 は構成情報の受信を待ちます。

37 デバイス1 (R =1、C =0) は構成情報を受信しLOAD を待ちます。

43 デバイス1 (R =1、C =0) は第 2 の制御ワード の「書き込み」フレ ームを検出し ます。

55 デバイス1 (R =1、C =0) は第 2 の制御ワードのア ドレスがロー= 3F、コラム= 0 である こ とを識別します。 第 2 の制

御ワードから ロー・アドレスが 1 だけ減算され ( ロー・ア ドレス= 3E) RSO に送られます。

構成読み出し

30ビット制御ワー ド : [ 読み出しフレーム][ ロー・ア ドレス ][ コラ ム・ア ドレス ][OUT1][OUT2][OUT3][OUT4]

アレイ書き込み :

[01 1110] [1][0] [0][0][0][0] //*アレイ位 置 1、構成情報の読み出し*//

[01 1110] [0][0] [0][0][0][0] //*アレイ位 置 0、構成情報の読み出し*//

www.national.com/JPN/

16

プログラミ ングの例 ( つづき)

デバイス0 読み出しプ ログ ラミン グ・シーケンス

DS90CP04

SCLK 数イベントの説明

6 デバイス0 (R =0、C=0) は第 1 の制御ワード の「読み出 し」フレ ー ムを検出します。

18 デバイス0 (R =0、C =0) は第 1 制御ワードのア ドレスがロー= 1、コラム= 0 である こ とを識別します。 第 1 の制御

ワー ドから ロー・アドレスが 1 だけ減算さ れ ( ロー・ア ドレス= 0) RSO に送ら れます。

36 デバイス0 (R =0、C =0) は第 2 の制御ワード の「書き込み」フレームを検出しま す。

48 デバイス0 (R =0、C =0) は第 2 の制御ワードがロー = 0、コラム = 0 であ る こ とを識別します。これは有効な構成書

き込みア ドレス のため、デバイス0 は構成情報の送信を準備します。最後の制御ワードか らロ ー・アドレスが 1 だけ減

算され ( ロー・ア ドレス= 3F) RSO に送ら れます。

60 デバイス0 (R =0、C =0) は構成情報を送信します。

74 アレイ出力 ( デバイス1 のRSO) から構成情報の送出が終わります。

デバイス1 読み出しプ ログ ラミン グ・シーケンス

SCLK 数イベントの説明

13 デバイス1 (R =1、C =0) は第 1 の制御ワードの「読み出し」フレームを検出 します。

25 デバイス1 (R =1、C =0) は第 1 制御ワードのア ドレスがロー= 0、コラム= 0 である こ とを識別します。これは有効な

構成書き込みアドレスのため、デバ イス 1 は構成情報の送信を準備します。第 1 の制御 ワードから ロー・ ア ドレスが 1

だけ減算さ れ ( ロー・ア ドレス= 3F) RSO に送 られ ます。

37 デバイス1 (R =1、C =0) は構成情報をアレイ出力 ( デバ イス1 の RSO) から送出します。

17

www.national.com/JPN/

外形寸法図 単位はmillimeters

LLP, Plastic, QUAD,

Order Number DS90CP04TLQ, DS90CP04TLQX (Tape and Reel)

NS Package Number LQA032A

生命維持装置への使用について

DS90CP04 4 × 4、低消費電力、2.5Gb/s、LV DS デジタル・クロスポイ ント・スイッチ

弊社の製品はナショナル セミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品とし

て使用することはできません。

1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使

用されることを意図されたもの、または (b) 生命を維持ある

いは支持するものをいい、ラベルにより表示される使用法に

従って適切に使用された場合に、これの不具合が使用者に身

体的障害を与えると予想されるものをいいます。

2. 重要な部品とは、生命維持にかかわる装置またはシステム内

のすべての部品をいい、これの不具合が生命維持用の装置ま

たはシステムの不具合の原因となりそれらの安全性や機能

に影響を及ぼすことが予想されるものをいいます。

ナショナル セミコンダクター ジャパン株式会社

本社/〒 135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300

技術資料(日本語 / 英語)はホームページより入手可能です。

www.national.com/JPN/

その他のお問い合わせはフリーダイヤルをご利用下さい。

フリーダイヤル

0120-666-116

本資料に掲載されているすべての回路の使用に起因する第三者の特許権その他の権利侵害に関して、弊社ではその責を負いません。

また掲載内容は予告無く変更されることがありますのでご了承ください。

Loading...

Loading...