Page 1

SERVICE

SERVICE MANUAL

4

4

MMK-702U

DM802

Page 2

CONTENTS

1. PRECAUTIONS -----------------------------------------------------------------------------------------------------------------------2

1-1 SAFETY PRECAUTIONS------------------------------------------------------------------------------------------------------------2

1-2 SERVICING PRECAUTIONS--------------------------------------------------------------------------------------------------------3

1-2-1 General Serving Precautions------------------------------------------------------------------------------------------------3

1-2-2 Insulation Checking Procedure ---------------------------------------------------------------------------------------------4

1-3 ESD PRECAUTIONS ---------------------------------------------------------------------------------------------------------------4

2. REFERENCE INFORMATION ----------------------------------------------------------------------------------------------------5

2-1 COMPONENT DESCRIPTIONS-----------------------------------------------------------------------------------------------------5

2-1-1 DVD SONY HM-313PUH----------------------------------------------------------------------------------------------------5

2-1-2 DVD Processor Chip MTK1389D ------------------------------------------------------------------------------------------7

2-1-3 Serial EEPROM, 2K (256 x 8) (24C02) or 16 K (2048 x 8) (24C16)------------------------------------------------ 19

2-1-4: --------------------------------------------------- 20

Boot Sector Flash Memory 1M X 8 Bit / 512K X 16 Bit A29L800

2-1-5 2 Banks x 512K x 16 Bit Synchronous DRAM HY57V161610E ----------------------------------------------------- 24

3. PRODUCT SPECIFICATIONS --------------------------------------------------------------------------------------------------28

4. UPGRADING SYSTEM AND CHANGING THE REGION CODE------------------------------------------------------ 29

5. OPERATING INSTRUCTION---------------------------------------------------------------------------------------------------- 30

MAINTENANCE & TROUBLESHOOTING--------------------------------------------------------------------------------------------- 30

6.Problems and Solutions

7.TROUBLESHOOTING ------------------------------------------------------------------------------------------------------------- 32

8.RESOLVE DIAGRAM ------------------------------------------------------------------------------------------------------------- 33

9. BLOCK DIAGRAM ----------------------------------------------------------------------------------------------------------------- 34

10. CIRCUIT DIAGRAMS------------------------------------------------------------------------------------------------------------- 35

11. WIRING DIAGRAM:-------------------------------------------------------------------------------------------------------------- 49

----------------------------------------------------------------------------------------------------

31

- 1 -

Page 3

1. PRECAUTIONS

1-1 Safety Precautions

1) Before returning an instrument to the customer,

always make a safety check of the entire instrument,

including, but not limited to, the following items:

(1) Be sure that no built-in protective devices are

defective or have been defeated during servicing.

(1) Protective shields are provided to protect both

the technician and the customer. Correctly replace

all missing protective shields, including any

remove for servicing convenience.

(2) When reinstalling the chassis and/or other

assembly in the cabinet, be sure to put back in

place all protective devices, including, but not

limited to, nonmetallic control knobs, insulating

fish papers, adjustment and compartment

covers/shields, and isolation resistor/capacitor

networks. Do not operate this instrument or permit

it to be operated without all protective devices

correctly installed and functioning.

(2) Be sure that there are no cabinet opening through

which adults or children might be able to insert

their fingers and contact a hazardous voltage.

Such openings include, but are not limited to,

excessively wide cabinet ventilation slots, and an

improperly fitted and/or incorrectly secured

cabinet back cover.

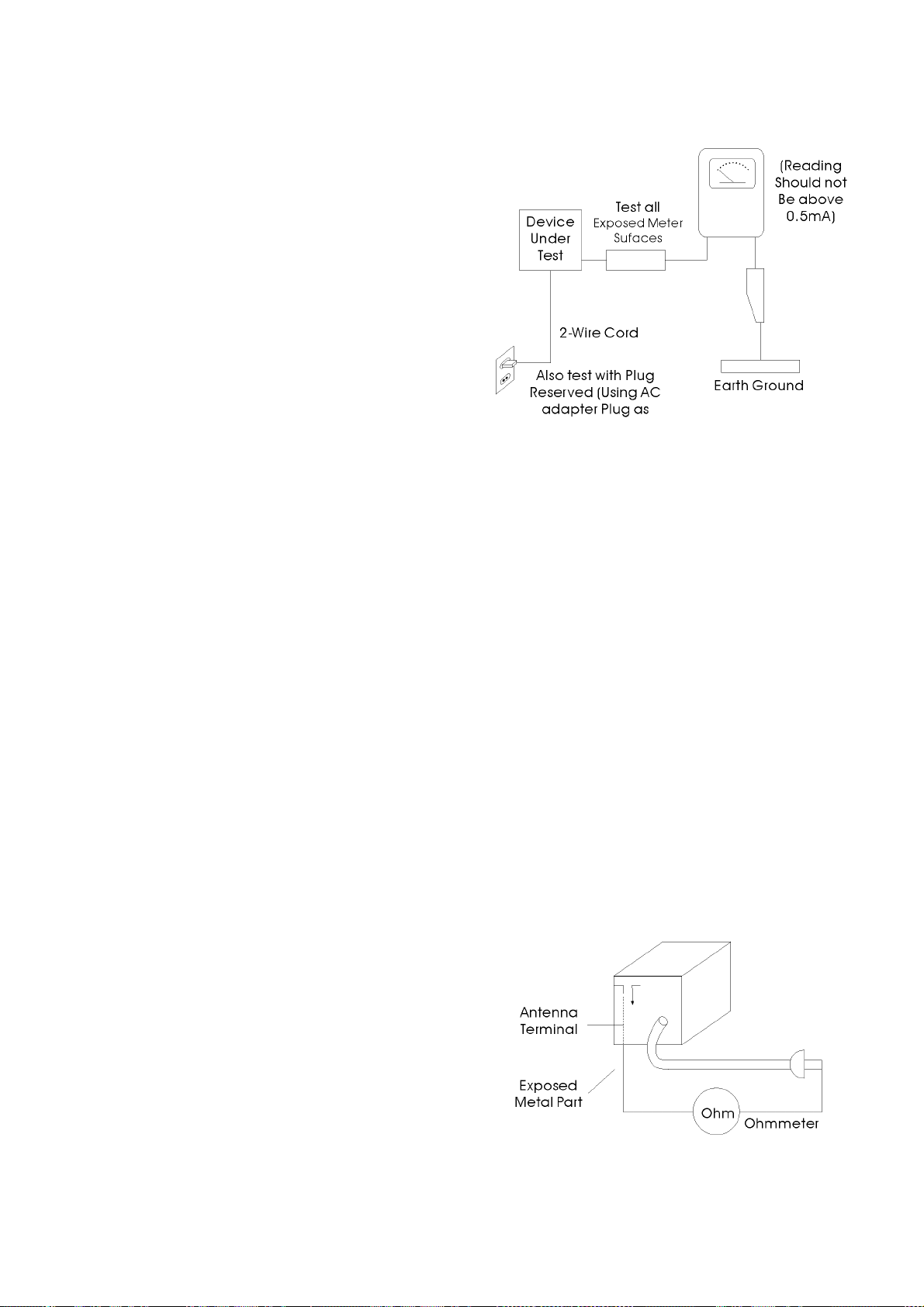

(3) Leakage Current Hot Check-With the instrument

completely reassembled, plug the AC line cord

directly into a 120V AC outlet. (Do not use an

isolation transformer during this test.) Use a

leakage current tester or a metering system that

complies with American National Standards

institute (ANSI) C101.1 Leakage.

Current for Appliances and underwriters

Laboratories (UL) 1270 (40.7). With the

instrument’s AC switch first in the ON position and

then in the OFF position, measure from a known

earth ground (metal water pipe, conduit, etc.) to all

exposed metal parts of the instrument (antennas,

handle brackets, metal cabinets, screwheads,

metallic overlays, control shafts, etc.), especially

and exposed metal parts that offer an electrical

return path to the chassis.

Any current measured must not exceed 0.5mA.

Reverse the instrument power cord plug in the

outlet and repeat the test.

AC Leakage Test

Any measurements not within the limits specified

herein indicate a potential shock hazard that must

be eliminated before returning the instrument to

the customer.

(4) Insulation Resistance Test Cold Check-(1) Unplug

the power supply cord and connect a jumper wore

between the two prongs of the plug. (2) Turn on

the power switch of the instrument. (3) Measure

the resistance with an ohmmeter between the

jumpered AC plug and all exposed metallic

cabinet parts on the instrument, such as

screwheads, antenna, control shafts, handle

brackets, etc. When an exposed metallic part has

a return path to the chassis, the reading should be

between 1 and 5.2 megohm. When there is no

return path to the chassis, the reading must be

infinite. If the reading is not within the limits

specified, there is the possibility of a shock hazard,

and the instrument must be re-pared and

rechecked before it is returned to the customer.

Insulation Resistance Test

- 2 -

Page 4

2) Read and comply with all caution and safety related

notes non or inside the cabinet, or on the chassis.

3) Design Alteration Warning-Do not alter of add to the

mechanical or electrical design of this instrument.

Design alterations and additions, including but not

limited to, circuit modifications and the addition of

items such as auxiliary audio output connections,

might alter the safety characteristics of this

instrument and create a hazard to the user. Any

design alterations or additions will make you, the

service, responsible for personal injury or property

damage resulting there from.

4) Observe original lead dress. Take extra care to

assure correct lead dress in the following areas:

(1) near sharp edges, (2) near thermally hot parts

(be sure that leads and components do not touch

thermally hot parts), (3) the AC supply, (4) high

voltage, and (5) antenna wiring. Always inspect in

all areas for pinched, out-of-place, or frayed wiring.

Do not change spacing between a component and

the printed-circuit board, Check the AC power

cord for damage.

5) Components, parts, and/or wiring that appear to

have overheated or that are otherwise damaged

should be replaced with components, parts and/or

wiring that meet original specifications.

Additionally determine the cause of overheating

and/or damage and, if necessary, take corrective

action to remove and potential safety hazard.

6) Product Safety Notice-Some electrical and

mechanical parts have special safety-related

characteristics which are often not evident from

visual inspection, nor can the protection they give

necessarily be obtained by replacing them with

components rated for higher voltage, wattage, etc.

Parts that have special safety characteristics are

identified by shading, an (

schematics and parts lists. Use of a substitute

replacement that does not have the same safety

characteristics as the recommended replacement

part might created shock, fire and/or other

hazards. Product safety is under review

continuously and new instructions are issued

whenever appropriate.

) or a ( ) on

1-2 Servicing Precautions

CAUTION: Before servicing Instruments covered by

this service manual and its supplements, read and

follow the Safety Precautions section of this manual.

Note: If unforeseen circument create conflict between

the following servicing precautions and any of the

safety precautions, always follow the safety

precautions. Remember; Safety First

1-2-1 General Serving Precautions

(1) a. Always unplug the instrument’s AC power cord

from the AC power source before (1) removing or

reinstalling any component, circuit board, module

or any other instrument assembly. (2)

disconnecting any instrument electrical plug or

other electrical connection. (3) connecting a test

substitute in parallel with an electrolytic capacitor

in the instrument.

b. Do not defeat any plug/socket B+ voltage

interlocks with which instruments covered by this

service manual might be equipped.

c. Do not apply AC power to this instrument and/or

any of its electrical assemblies unless all

solid-state device heat sinks are correctly

installed.

d. Always connect a test instrument’s ground lead

to the instrument chassis ground before

connecting the test instrument positive lead.

Always remove the test instrument ground lead

last.

Note: Refer to the Safety Precautions section

ground lead last.

(2) The service precautions are indicated or printed on

the cabinet, chassis or components. When

servicing, follow the printed or indicated service

precautions and service materials.

(3) The components used in the unit have a specified

flame resistance and dielectric strength.

When replacing components, use components

which have the same ratings, by (

in the circuit diagram are important for safety or

for the characteristics of the unit. Always replace

them with the exact replacement components.

(4) An insulation tube or tape is sometimes used and

some components are raised above the printed

wiring board for safety. The internal wiring is

sometimes clamped to prevent contact with

heating components. Install such elements as

they were.

(5) After servicing, always check that the removed

screws, components, and wiring have been

installed correctly and that the portion around the

serviced part has not been damaged and so on.

Further, check the insulation between the blades

of the attachment plus and accessible conductive

parts.

) or by ( )

- 3 -

Page 5

1-2-2 Insulation Checking Procedure

Disconnect the attachment plug from the AC outlet and

turn the power ON. Connect the insulation resistance

meter (500V) to the blades of the attachment plug. The

insulation resistance between each blade of the

1-3 ESD Precautions

attachment plug and accessible conductive parts (see

note) should be more than 1 Megohm.

Note: Accessible conductive parts include metal

panels, input terminals, earphone jacks, etc.

Electrostatically Sensitive Devices (ESD)

Some semiconductor (solid static electricity) devices

can be damaged easily by static electricity.

Such compo9nents commonly are called

Electrostatically Sensitive Devices (ESD). Examples of

typical ESD devices are integrated circuits and some

field-effect transistors and semiconductor chip

components. The following techniques of component

damage caused by static electricity.

(1) immediately before handling any semiconductor

components or semiconductor-equipped assembly,

drain off any electrostatic charge on your body by

touching a known earth ground. Alternatively,

obtain and wear a commercially available

discharging wrist strap device, which should be

removed for potential shock reasons prior to

applying power to the unit under test.

(2) after removing an electrical assembly equipped

with ESD devices, place the assembly on a

conductive surface such as aluminum foil, to

prevent electrostatic charge buildup or exposure

of the assembly.

(3) Use only a grounded-tip soldering iron to solder or

unsolder ESD device.

(4) Use only an anti-static solder removal devices.

Some solder removal devices not classified as

“anti-static” can generate electrical charges

sufficient to damage ESD devices.

(5) Do not use freon-propelled chemicals. These can

generate electrical charges sufficient to damage

ESD devices.

(6) Do not remove a replacement ESD device from its

protective package until immediately before you

are ready to install it. (Most replacement ES

devices are packaged with leads electrically

shorted together by conductive foam, aluminum

foil or comparable conductive materials).

(7) Immediately before removing the protective

materials from the leads of a replacement ES

device touch the protective material to the chassis

or circuit assembly into which the device will be

installed.

CAUTION: Be sure no power is applied to the chassis

or circuit, and observe all other safety precautions.

(8) Minimize bodily motions when handling

unpackaged replacement ESD devices.

(Otherwise harmless motion such as the brushing

together of your clothes fabric or the lifting of your

foot from a carpeted floor can generate static

electricity sufficient to damage an ESD device).

- 4 -

Page 6

2. Reference Information

2-1 Component Descripti

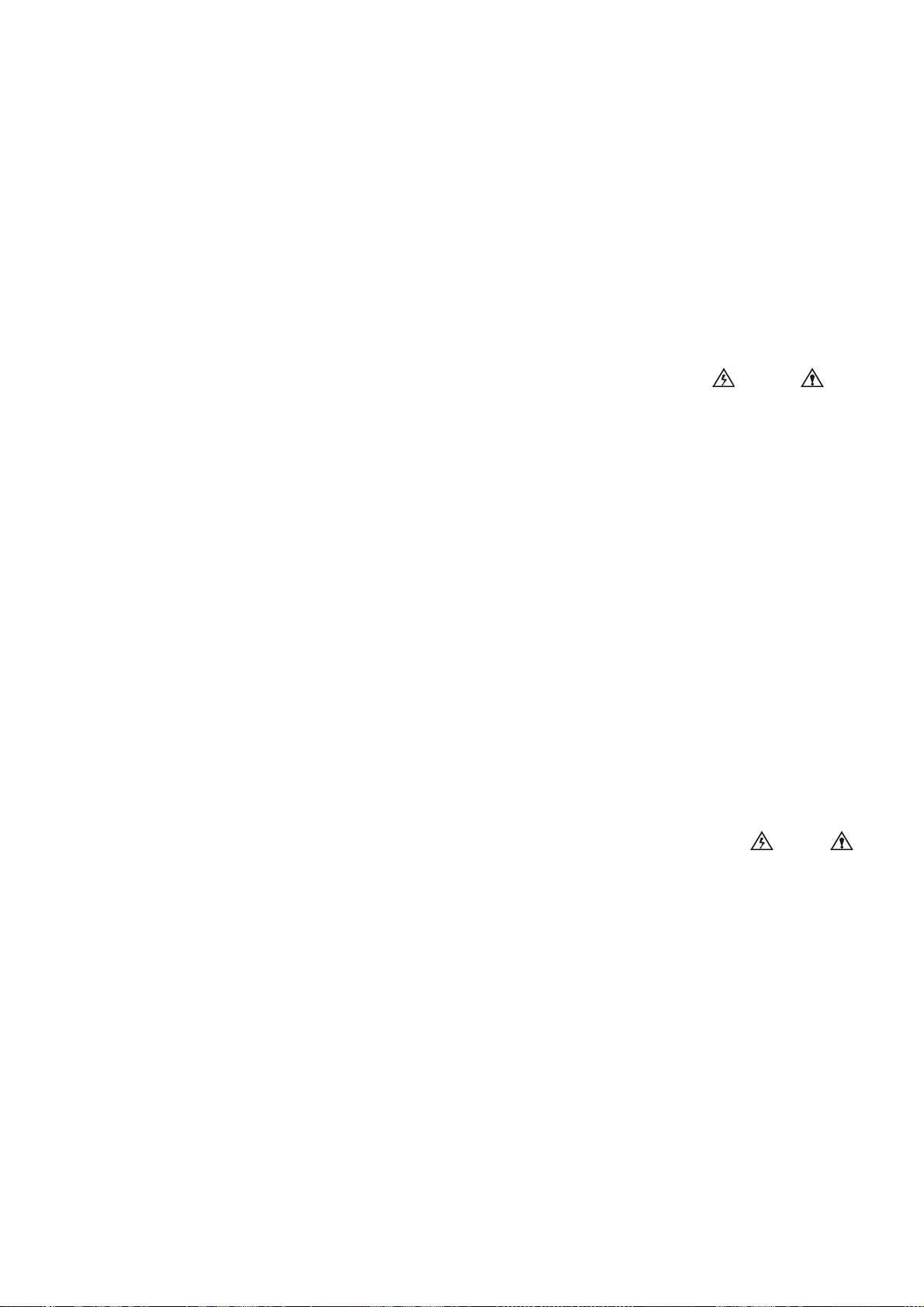

2-1-1 DVD

Conn

SONY HM 313-

ector Pin Definition

PUH

ons

-5-

Page 7

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

1 Applications

This present specifications are applied to IC MT1389L.

2 Type

MT1389L

3 Usage

Single Chip IC for DVD Player

4 Structure

0.16um CMOS process, Silicon material, Monolithic IC, 128pin LQFP, 3.3/1.8 Dual operation voltages.

1

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 8

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

5 Function

5-1 General Description

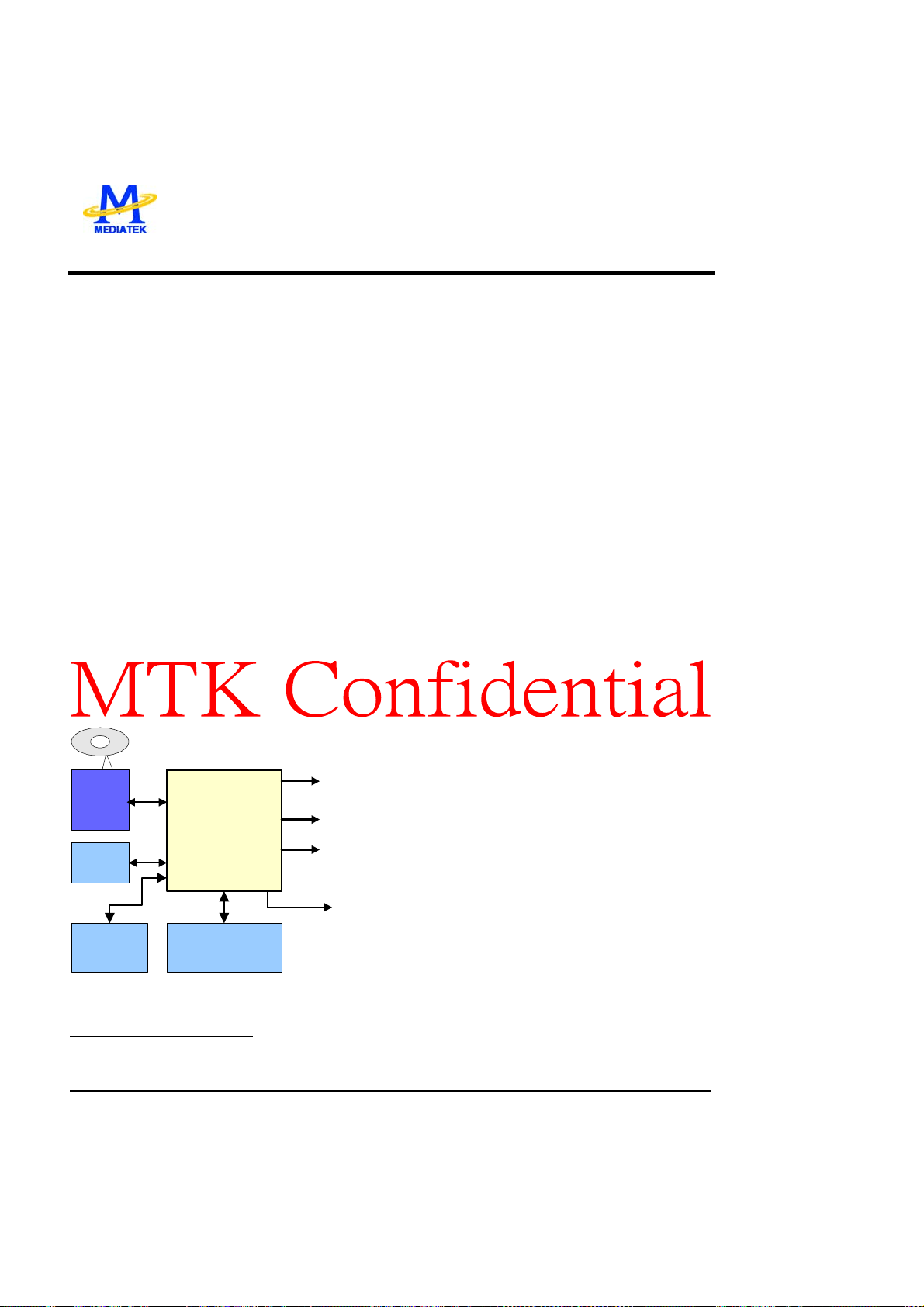

MediaTek MT1389L is a cost-effective DVD system-on-chip (SOC) which incorporates advanced features like

MPEG-4 video decoder, high quality TV encoder and state-of-art de-interlace processing. The MT1389L enables

consumer electronics manufacturers to build high quality, USB2.0, MS/SD/MMC reader, feature-rich DVD players,

portable DVD players or any other home entertainment audio/video devices.

World-Leading Technology: Based on MediaTek’s world-leading DVD player SOC architecture, the

MT1389L is the New generation of the DVD player SOC. It integrates the MediaTek 3

RF amplifier and the Servo/MPEG AV decoder.

Rich Feature for High Valued Product: To enrich the feature of DVD player, the MT1389 equips a

simplified MPEG-4 advanced simple profile (ASP) video decoder to fully support the DivX

makes the MT1389-based DVD player be capable of playback MPEG-4 content which become more and more

popular.

Incredible Audio/Video Quality: The progressive scan of the MT1389L utilized advanced motion-adaptive

de-interlace algorithm to achieve the best movie/video playback. It also supports a 3:2 pull down algorithm to give

the best film effect. The 108MHz/12-bit video DAC provides users a whole new viewing experience. Built-in 6ch

audio DACs and 2ch audio ADCs could give the variable function solutions.

High Performance Memory Storage Device: As the core of Portable DVD players need more capability to

support current multimedia contents. The MT1389L provides the interface for the 3-in-1 card reader, which

supports Memory-Stick, Secure Digital Memory Card, and MultiMediaCard, to connect with the mainstream digital

camera FLASH cards. For the USB application, we adopt USB2.0 High speed specification to reach rich-contents

transference. USB 2.0 High speed will support for high-speed devices. USB 2.0 High Speed is suitable for

high-performance devices such as high-density storage devices. In addition, USB 2.0 High Speed supports old

USB 1.0/1.1 software and peripherals, offering impressive and even better compatibility to customers

rd

generation front-end digital

1

Home Theater profile. It

Key Features

DVD

PUH

Module

FLASH

MT1389L

Desktop

CVBS, Y/C,

Component

SDPIF

Analog

Audio

Output

USB 2.0

High Speed

Front-panel

Remote

DRAM

DVD Player System Diagram Using MT1389L

1

DivX is a trademark of DivXNetworks

2

USB High Speed : 480Mbit/sec. USB Full Speed : 12Mbit/sec.

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

2

RF/Servo/MPEG Integration

DivX Home Theater Level MPEG4 ASP Video decoder

Support Nero-Digital

Support DivX Ultra

High Performance Audio Processor

Progressive Scan

108MHz/12-bit, 4 CH TV Encoder

Internal 6CH Audio DAC

Internal 2CH Audio ADC

USB2.0 High Speed (Host/Device)

3-in-1 MS/SD/MMC reader

Applications

Standard DVD Players

Page 9

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

5-2 Key Features

RF/Servo/MPEG Integration

Embedded 6ch Audio DAC

Embedded 2ch Audio ADC for Karaoke

High Performance Audio Processor

High Performance Progressive Video Processor

Support Nero-Digital

Support DivX Ultra

High Quality 108MHz/12-bit, 4 CH TV Encoder

USB 2.0 High-Speed

5-3 Applications

MT1389L

Standard DVD Players

DVD Players Home Theater Application

Portable DVD Players

TV/DVD Combo Systems

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

3

Page 10

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

5-4 General Feature lists

Super Integration DVD player single chip

High performance analog RF amplifier

Servo controller and data channel processing

MPEG-1/MPEG-2/JPEG video

Dolby AC-3/DTS Decoder

Unified memory architecture

Versatile video scaling & quality enhancement

OSD & Sub-picture

Built-in clock generator

Built-in high quality TV encoder

Built-in progressive video processor

Audio effect post-processor

Built-in 5.1-ch Audio DAC

Built-in 2-ch Audio ADC for Karaoke

USB 2.0 High-Speed

MS/SD/MMC 3-in-1 card reader

Speed Performance on Servo/Channel

Decoding

DVD-ROM up to 4XS

CD-ROM up to 24XS

Channel Data Processor

Digital data slicer for small jitter capability

Built-in high performance data PLL for channel

data demodulation

EFM/EFM+ data demodulation

Enhanced channel data frame sync protection

& DVD-ROM sector sync protection

Servo Control and Spindle Motor Control

Programmable frequency error gain and phase

error gain of spindle PLL to control spindle

motor on CLV and CAV mode

Built-in ADCs and DACs for digital servo

control

Provide 2 general PWM

Tray control can be PWM output or digital

output

Embedded Micro controller

Built-in 8032 micro controller

Built-in internal 373 and 8-bit programmable

lower address port

1024-bytes on-chip RAM

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Up to 2M bytes FLASH-programming interface

Supports 5/3.3-Volt. FLASH interface

Supports power-down mode

Supports additional serial port

DVD-ROM/CD-ROM Decoding Logic

High-speed ECC logic capable of correcting

one error per each P-codeword or Q-codeword

Automatic sector Mode and Form detection

Automatic sector Header verification

Decoder Error Notification Interrupt that signals

various decoder errors

Provide error correction acceleration

Buffer Memory Controller

Supports 16Mb/32Mb/64Mb SDRAM

Supports 16-bit SDRAM data bus

Provides the self-refresh mode SDRAM

Block-based se ct or addressing

Video Decode

Decodes MPEG1 video and MPEG2 main level,

main profile video (720/480 and 720x576)

Decodes MPEG-4 Advanced Simple Profile

Support DivX 3.11/4.x/5.x Home Theater

Profile

Support Nero-Digital

Support DivX Ultra

Smooth digest view function with I, P and B

picture decoding

Baseline, extended-sequential and progressive

JPEG image decoding

Support CD-G titles

Video/OSD/SPU/HLI Processor

Arbitrary ratio vertical/horizontal scaling of

video, from 0.25X to 256X

65535/256/16/4/2-color bitmap format OSD,

256/16 color RLC format OSD

Automatic scrolling of OSD image

Audio Effect Processing

Dolby Digit al (AC- 3)/EX decoding

DTS/DTS-ES decoding

MPEG-1 layer 1/layer 2 audio decoding

4

MT1389L

Page 11

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

High Definition Compatible Digital (HDCD)

Windows Media Audio (WMA)

Dolby ProLogic II

Concurrent multi-channel and downmix out

IEC 60958/61937 output

- PCM / bit stream / mute mode

- Custom IEC latency up to 2 frames

Pink noise and white noise generator

Karaoke functions

- Microphone echo

- Microphone tone control

- Vocal mute/vocal assistant

- Key shift up to +/- 8 keys

- Chorus/Flanger/Harmony/Reverb

Channel equalizer

3D surround processing include virtual

surround and speaker separation

TV Encoder

Four 108MHz/12bit DACs

Support NTSC, PAL-BDGHINM, PAL-60

Support 525p, 625p progressive TV format

Automatically turn off unconnected channels

Support PC monitor (VGA)

Support Macrovision 7.1 L1, Macrovision 525P

and 625P

CGMS-A/WSS

Closed Caption

Progressive Scan Video

Automatic detect film or video source

3:2 pull down source detection

Advanced Motion adaptive de-interlace

Minimum external memory requirement

External Interface

USB2.0 High Speed (Host/Device)

Memory-Stick, Secure Digital Memory Card, and

MultiMediaCard Interface

Outline

128-pin LQFP package

3.3/1.8-Volt. Dual operating voltages

5

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 12

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

Dolby License

Supply of this Implementation of Dolby technology does not convey a license nor imply a right

under any patent, or any other industrial or intellectual property right of Dolby Laboratories, to

use this Implementation in any finished end-user or ready-to-use final product. It is hereby

notified that a license for such use is required from Dolby Laboratories.

6

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 13

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

5-5 Pin Definitions

Abbreviations:

y SR: Slew Rate

y PU: Pull Up

y PD: Pull Down

y SMT: Schmitt Trigger

y 4mA~16mA: Output buffer driving strength.

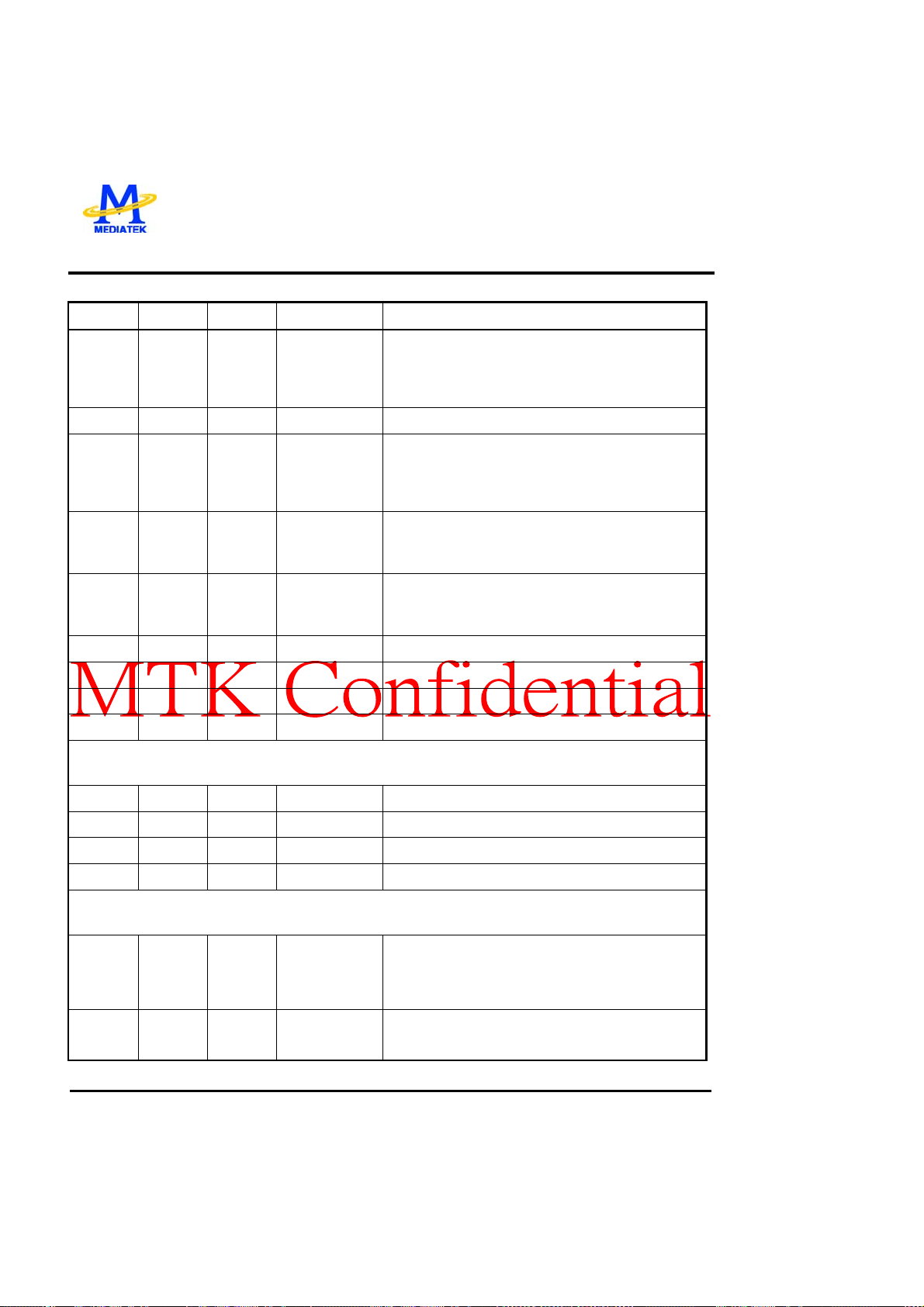

Pin Main Alt. Type Description

Analog Interface (66)

125

126

127

128

1

2

3

4

5

6

7

8

9 XTALI Input

10 XTALO Output

11

12

13

14

15

RFIP Analog Input AC coupled DVD RF signal input RFIP

RFIN OPOUT Analog Input AC coupled DVD RF signal input RFIN

RFG OPINP Analog Input Main beam, RF AC input path

RFH OPINN Analog Input Main beam, RF AC input path

RFA Analog Input RF main beam input A

RFB Analog Input RF main beam input B

RFC Analog Input RF main beam input C

RFD Analog Input RF main beam input D

RFE Analog Input RF sub beam input E

RFF Analog Input RF sub beam input E

AVDD18_2 Analog power Analog 1.8V power

AVDD33_1 Analog Power Analog 3.3V power

27MHz crys tal input

27MHz crystal output

AGND33 Analog Ground Analog Ground

V20

V14

REXT Analog Input

MDI1 Analog Input Laser power monitor input

Analog output Reference voltage 2.0V

Analog output Reference voltage 1.4V

Current reference input. It generates reference current for

RF path. Connect an external 15K resistor to this pin and

AVSS

7

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 14

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

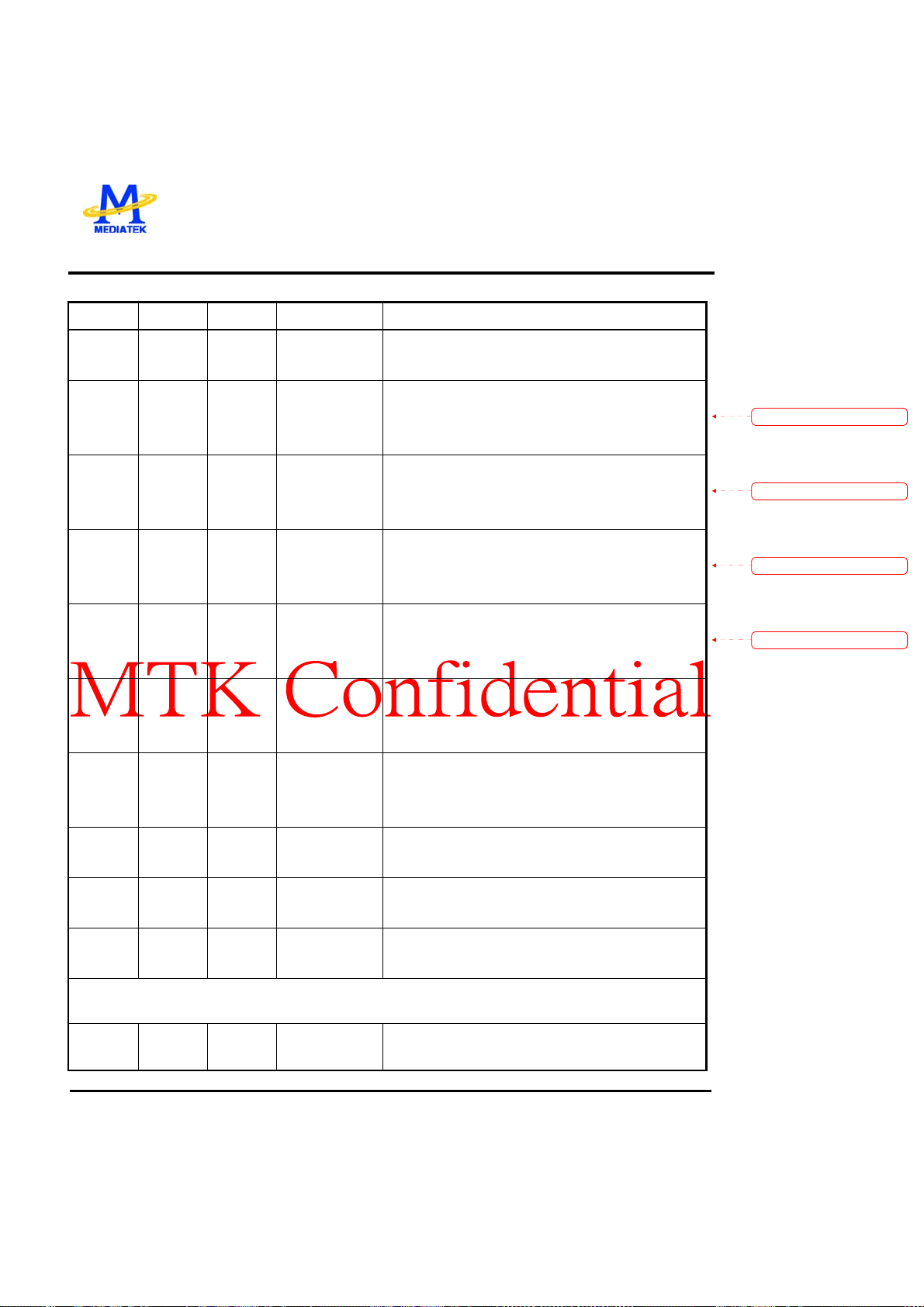

Pin Main Alt. Type Description

16 MDI2 Analog Input Laser power monitor input

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

95 DACVDDC Power

96 VREF Analog

97 FS Analog

98 DACVSSC Ground

99 CVBS

100 DACVDDB Power

101 DACVDDA Power

102 Y/G

103 B/CB/PB

LDO1 Analog Output Laser driver output

LDO2 Analog Output Laser driver output

AVDD33_2 Analog Power Analog 3.3V power

DMO Ana log Outp ut Disk motor control output. PWM output

FMO Analog Output Feed motor control. PWM output

TRAY_OPEN

TRAY_CLOSE

TRO

FOO

FG

USB_DP

USB_DM

VDD33_USB

VSS33_USB

PAD_VRT

VDD18_USB

Analog Output Tray PWM output/Tray open output

Analog Output

GPIO2

Analog Output

Analog Output

Analog

Analog Inout USB port DPLUS analog pin

Analog Inout USB port DMINUS analog pin

USB Power USB Power pin 3.3V

USB Ground USB ground pin

Analog Inout USB generating reference current

USB Power USB Power pin 1.8V

Analog

Analog

Analog

Tray PWM output/Tray close output

Tracking servo output. PDM output of tracking servo

compensator

Focus servo output. PDM output of focus servo

compensator

1) Motor Hall sensor input

2) GPIO

3.3V power pin for video DAC circuitry

Bandgap reference voltage

Full scale adjustment (suggest to use 560 ohm)

Ground pin for video DAC circuitry

Analog composite output

3.3V power pin for video DAC circuitry

3.3V power pin for video DAC circuitry

Green, Y, SY, or CVBS

Blue, CB/PB, or SC

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

8

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 15

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Main Alt. Type Description

104 R/CR/PR

105 AADVSS Ground

106 AKIN2 Analog

107 ADVCM Analog

108 AKIN1 Analog

109 AADVDD Power

110 APLLVDD3 Power

111 APLLCAP Analog InOut

112 ADACVSS2 Ground

113 ADACVSS1 Ground

114 ARF / LFE GPIO Analog Output

115 ARS GPIO Analog Output

Analog Red, CR/PR, CVBS, or SY

Ground pin for 2ch audio ADC circuitry

1) Audio ADC input 2

2) MS_CLK set B

3) MCDATA

4) Audio Mute

5) HSYN/VSYN output

6) C5

7) GPIO

1) 2ch audio ADC reference voltageC

2) C6

3) GPIO

1) Audio ADC input 1

2) MS_D0 set B

3) Audio Mute

4) HSYN/VSYN output

5) C7

6) GPIO

3.3V power pin for 2ch audio ADC circuitry

3.3V Power pin for audio clock circuitry

APLL external capacitance connection

Ground pin for audio DAC circuitry

Ground pin for audio DAC circuitry

1) Audio DAC sub-woofer channel output

2) While internal audio DAC not used:

a. ACLK

b. GPIO

1) Audio DAC right Surround channel output

2) While internal audio DAC not used:

a. ABCK

b. GPIO

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

9

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 16

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

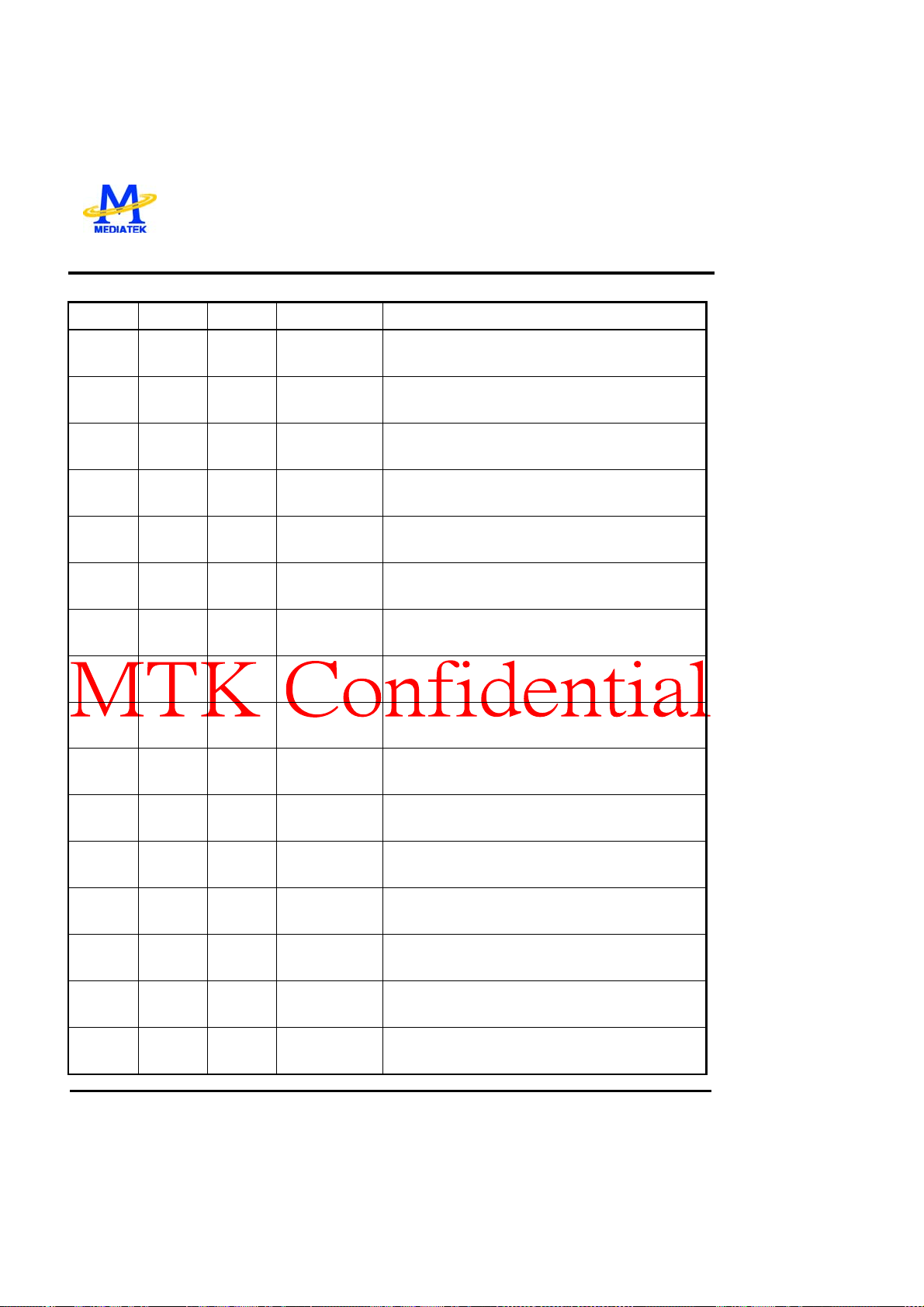

Pin Main Alt. Type Description

1) Audio DAC right channel output

116 AR GPIO Analog Output

117 AVCM Analog

118 AL GPIO Analog Output

119 ALS GPIO Analog Output

ALF /CENTER

120

121 ADACVDD1 Analog Power

122 ADACVDD2 Analog Power

123 AVDD18_1 Analog Power

124 AGND18 Analog Ground

GPIO Analog Output

2) While internal audio DAC not used:

a. SDATA2

b. GPIO

c. RXD2

Audio DAC reference voltage

1) Audio DAC left channel output

2) While internal audio DAC not used:

a. SDATA1

b. GPIO

c. RXD1

1) Audio DAC left Surround channel output

2) While internal audio DAC not used:

a. ALRCK

b. GPIO

1) Audio DAC center channel output

2) While internal audio DAC not used:

a. ASDATA0

b. GPIO

3.3V power pin for audio DAC circuitry

3.3V power pin for audio DAC circuitry

Analog 1.8V power

Analog Ground

General Power/Ground (7)

54, 90 DVDD18 Power

79 DVSS18 Ground

50, 68,84 DVDD33 Power

60 DVSS Ground

Micro Controller , Flash Interface and GPIO(12)

InOut

33 GPIO3 INT#

34 GPIO4

8mA, SR

PD, SMT

InOut

4mA, PD

1.8V power pin for internal digital circuitry

1.8V Ground pin for internal digital circuitry

3.3V power pin for internal digital circuitry

3.3V Ground pin for internal digital circuitry

1) General purpose IO 3

2) Microcontroller external interrupt 1

General purpose IO 4

10

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 17

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

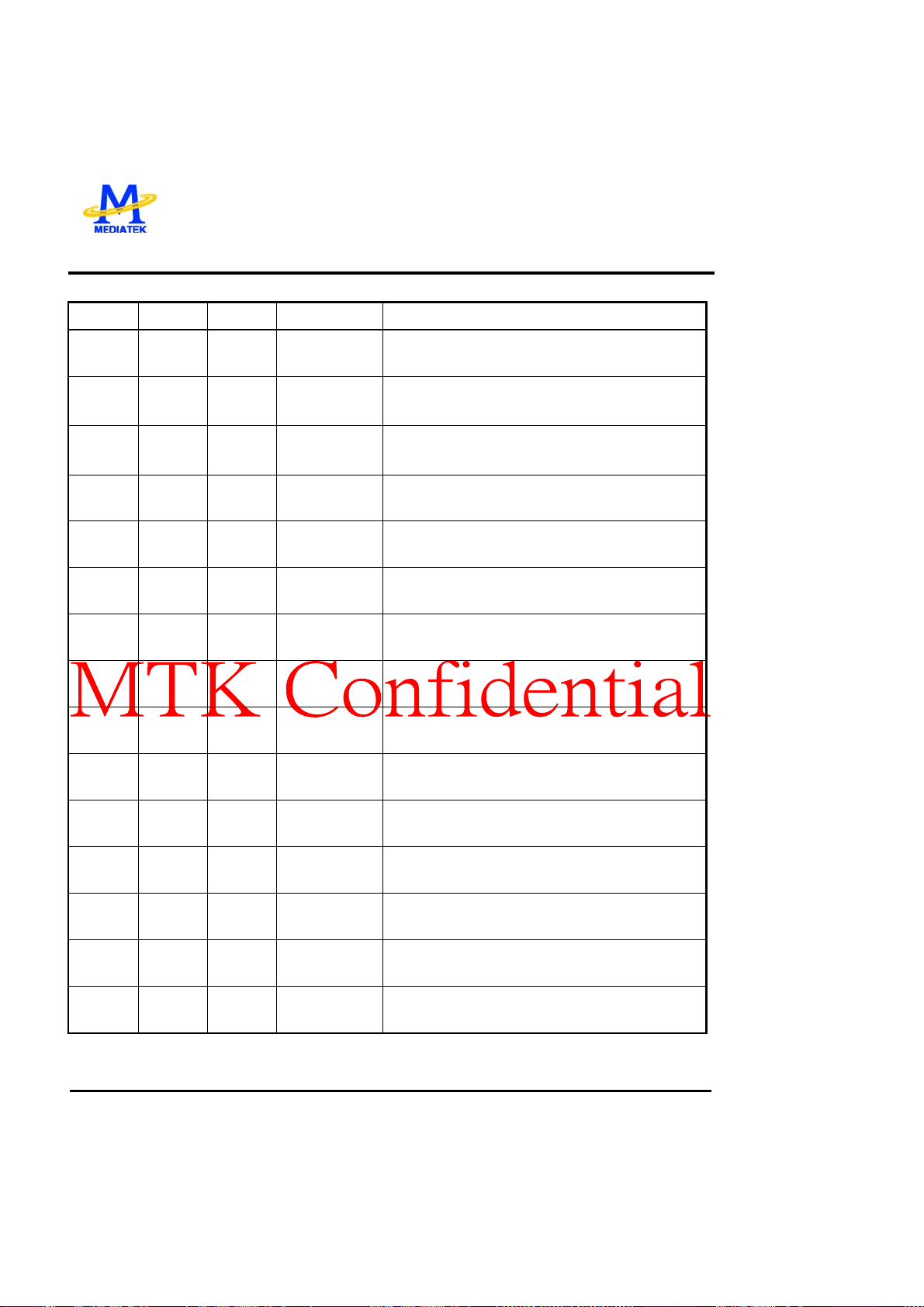

Pin Main Alt. Type Description

35 GPIO6

36 SF_CS_

37 SF_DO

38 SF_DI

39 SF_CK

40 UP1_6 SCL

41 UP1_7 SDA

42 ICE

43 PRST#

44 IR

InOut

4mA, PD

InOut

8mA, SR

PU, SMT

InOut

8mA, SR

PD, SMT

InOut

8mA, SR

PU, SMT

InOut

8mA, SR

PD, SMT

InOut

4mA, SR

PU, SMT

InOut

4mA, SR

PU, SMT

Input

PD, SMT

Input

PU, SMT

Input

SMT

General purpose IO 6

Serial Flash Chip Select

Serial Flash Dout

Serial Flash Din

Serial Flash Clock

1) Microcontroller port 1-6

2

C clock pin

2) I

1) Microcontroller port 1-7

2

2) I

C data pin

Microcontroller ICE mode enable

Power on reset input, active low

IR control signal input

带格式的:

带格式的:

带格式的:

带格式的:

项目符号和编号

项目符号和编号

项目符号和编号

项目符号和编号

Dram Interface (37) (Sorted by position)

45 RD0

InOut,

4mA

DRAM data 0

11

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 18

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Main Alt. Type Description

46 RD1

47 RD2

48 RD3

49 RD4

51 RD5

52 RD6

53 RD7

55 DQM0

56 RD15

57 RD14

58 RD13

59 RD12

61 RD11

62 RD10

63 RD9

64 RD8

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA, PD

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

InOut

4mA

DRAM data 1

DRAM data 2

DRAM data 3

DRAM data 4

DRAM data 5

DRAM data 6

DRAM data 7

Data mask 0

DRAM data 15

DRAM data 14

DRAM data 13

DRAM data 12

DRAM data 11

DRAM data 10

DRAM data 9

DRAM data 8

12

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 19

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Main Alt. Type Description

65 DQM1

66 RCLK

67 RA11

69 RA9

70 RA8

71 RA7

72 RA6

73 RA5

74 RA4

75 RWE#

76 CAS#

77 RAS#

78 BA0

80 BA1

81 RA10

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

Output

4mA, PD

Output

4mA, PD

Output

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

Data mask 1

Dram clock

DRAM address bit 11

DRAM address 9

DRAM address 8

DRAM address 7

DRAM address 6

DRAM address 5

DRAM address 4

DRAM Write enable, active low

DRAM column address strobe, active low

DRAM row address strobe, active low

DRAM bank address 0

DRAM bank address 1

DRAM address 10

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

13

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 20

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Main Alt. Type Description

82 RA0

83 RA1

85 RA2

86 RA3

87 GPIO7 CKE

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

InOut

4mA, PD

DRAM address 0

DRAM address 1

DRAM address 2

DRAM address 3

1) GPIO 7

2) Dram Clock Enable

3) MS_CLK set A

4) Audio Mute

5) HSYN/VSYN input

6) C0

GPIO (6)

1) GPIO8

2) MS_BS set A

3) SD_CLK set A

88 GPIO8

89 GPIO9

InOut

4mA, PD

InOut

4mA, PU

4) ASDATA2

5) ACLK

6) Audio Mute

7) HSYN/VSYN input

8) C1

1) GPIO9

2) MS_D0 set A

3) SD_CMD set A

4) ASDATA1

5) ABCK

6) C2

7) RXD1

14

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 21

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Pin Main Alt. Type Description

1) GPIO10

2) SD_CLK set B

3) SD_D0 set A

91 GPIO10

92 GPIO11

93 SPDIF GPIO12

94 GPIO13

InOut

4mA, PD

InOut

4mA, PD

InOut

2mA, PD

InOut

4mA, PD

4) ASDATA0

5) ALRCK

6) HSYN/VSYN output

7) C3

8) TXD1

1) GPIO11

2) SD_CMD set B

3) MS_BS set B

4) Audio Mute

5) HSYN/VSYN output

6) C4

1) SPDIF output

2) GPIO12

1) GPIO13

2) SD_D0 set B

3) ALRCK

4) Audio Mute

5) YUVCLK

Note:

1. The Main column is the main function, Alt. means alternative function.

2. The multi-function GPIO pins are set to green characters.

15

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 22

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

5-6 Functional Block

DVD

PUH

Module

Motor

Drive

FLASH

ROM

DRAM

GPIO

IR/VFD

RF Amplifier

Servo IO

Spindle

Control

Memory

Controller

System

CPU

Debug

Servo

Processor

Audio

DSP

System

Parser

CPPM/CPRM

DRM

32-bit

RISC

Port

108MHz

TV Encoder

Video

Processor

Audio

Ouptut

Video DAC

interlacer

MPEG-1/2/4

JPEG

Video Decoder

6ch Audio DACs

De-

Internal

PCM output

Internal

Audio ADC

CVBS, Y/C

Component

Video

6ch Audio Analog

outputs

Audio

DAC

SDPIF

Audio Mic1

Audio Mic2

USB 2.0 High

Speed

controller

MS/SD/MMC

Card

Controller

USB 2.0 High

/ Full Speed

Device

MS/SD/MMC

Flash Card

16

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 23

V1.2

GPIO13

AudioAudioVid

DAC

ADC

DAC

_

DVDD18

INT RF

GPIO9

XTALI

GPIO8

XTALO

GPIO7 / CKE

V20

V14

REXT

USB

DVSS18

_

_

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

6 Pin Assignment

AKIN1 / GPIO21 / Audio_mute

AKIN2 / GPIO19 / Audio_mute

ALF / CENTER / GPIO

RFH / OPINN /

RFIN / OPOUT /

RFG / OPINP /

128

127

126

1 96 VREF

RFA

2 95 DACVDDC

RFB

3 94

RFC

4

RFD

5

RFE

6 91 GPIO10

RFF

7 90

2

AVDD18

AVDD33_1

AGND33

AVDD33_2

TRAY

TRAY

FG / GPIO2 26 71 RA7

USB_DP 27 70 RA8

USB_DM 28 69 RA9

VDD33_USB 29 68 DVDD33

VSS33_USB 30 67 RA11

PAD_VRT 31 66 RCLK

VDD18_USB 32 65 DQM1

8

9 88

10 87

11 86 RA3

12 85 RA2

13 84 DVDD33

14 83 RA1

15 82 RA0

MDI1

16 81 RA10

MDI2

17 80 BA1

LDO1

18

LDO2

19 78 BA0

20 77 RAS#

DMO

21 76 CAS#

FMO

22 75 RWE#

OPEN

23 74 RA4

CLOSE

24 73 RA5

TRO

25 72 RA6

FOO

33343536373839404142434445464748495051525354555657585960616263

GPIO3 / INT#

GPIO4

GPIO6

RFIP

125

SF_CS_

AGND18

124

SF_DO

AVDD18_1

123

SF_DI

ADACVDD2

122

SF_CK

ADACVDD1

121

UP1_6 / SCL

120

UP1_7 / SDA

ALS / GPIO

119

ICE

AL / GPIO1

118

PRST#IRRD0

ARF / LFE / GPIO

ARS / GPIO

ADACVSS1

115

114

ADACVSS2

113

112

APLLCAP

111

AR / GPIO0

AVCM

117

116

MT1389L

Desktop

RD1

RD2

RD3

RD4

DVDD33

APLLVDD

110

RD5

AADVDD

109

RD6

108

RD7

ADVCM / GPIO20 /

107

DVDD18

106

DQM0

AADVSS

R

105

104

RD15

RD14

B

103

RD13

G

102

RD12

eo

DACVDDA

101

DVSS33

DACVDDB

100

RD11

DACVSSC

CVBS

FS

999897

93 SPDIF / GPIO12

92 GPIO11

89

79

64

RD10

RD9

RD8

17

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 24

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

7 Absolute Maximum Ratin gs

Symbol Parameters Value Unit

VDD3 3.3V Supply voltage -0.3 to 3.6 V

VDD2 1.8V Supply voltage -0.3 to 2.1 V

VDDA Analog Supply voltage -0.3 to 3.6 V

VIN(3.3V) Input Voltage (3.3V IO) -0.3 to 3.63 V

VIN(5V-tolerance) Input Voltage (5V-tolerance IO) -0.3 to 5.5 V

V

Output Voltage -0.3 to VDD3+0.3 V

OUT

T

Storage Temperature -45 to 150

STG

o

C

8 Recommend Operation Condition

Symbol Parameters Min Typ Max Unit

TOP Operating Temperature 0 70 oC

TJ Junction Operation Temp. 0 25 115 oC

VDD3 3.3V Supply voltage 3.0 3.3 3.6 V

VDD2 1.8V Supply voltage 1.7 1.8 2.0 V

VDDA Analog Supply voltage 3.0 3.3 3.6 V

VIH (1.8V) Input voltage high (1.8V IO) 1.05 - - V

VIL (1.8V) Input voltage low (1.8V IO) - - 0.69 V

VIH (3.3V) Input voltage high (3.3V IO) 2.0 - - V

VIL (3.3V) Input voltage low (3.3V IO) - - 0.8 V

IIH High level input current 10 UA

IIL Low level input current -10 UA

PD Power dissipation 1.5 W

P

Power down mode 0.1 W

DOWN

fclk Input frequency of clock 27 MHz

18

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 25

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

9 Electrical Characteristi cs

9-1 DC Characteristics

Symbol Parameters Min Typ Max Unit

VOH (1.8V)

VOL (1.8V)

VOH (3.3V)

VOL (3.3V)

Output voltage high (1.8V IO)

Output voltage low (1.8V IO)

Output voltage high (3.3V IO)

Output voltage low (3.3V IO)

(*IOH = 2 ~ 16mA)

(*IOL = 2 ~ 16mA)

(*IOH = 2 ~ 16mA)

(*IOL = 2 ~ 16mA)

Rpu Pull-up Resistance 40 75 190

Rpd Pull-down Resistance 40 75 190

FOO

Offset voltage between FOO zero output and V

OFF

TRO

Offset voltage between TRO zero output and V

OFF

DMO

Offset voltage between DMO zero output and V

OFF

-50 0 50 mV

REF

-40 0 40 mV

REF

-30 0 30 mV

REF

Note * : The driving current of some IO pad are programmable according to the different application and

environment . All setting will be defined according to the F/W progress and test result.

Built-in Audio- DAC Characteristics

9-2

Note *: All parameters is measured on MediaTek’s DVD player reference DVD board, the actual performance depends on

different PCB desig n.

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

Output swing level:

V

out

Digital i/p level =0 dBFS , ADACVDD =3.3V

= 1.0 * ADACVDD / 3.3)

(V

out

Ro Output impedance @ 1kHz 50 100

RL_

Minimum resister load 5 K

min

CL_

Maximum capacitor load 20 PF

max

S/(THD+N)

S/(THD+N) @ 0 dBFS;

= 1kHz; Fs = 48kHz, A-weighted

f

in

DR Dynamic Range 88 dBr(A)

SNR Signal to noise ratio; A-weighted 95 dBr(A)

Channel

Separation

Close-talk of Left and Right Channel 85 dB

9-3 Built-in Video-DAC Specifications

Input Codes for Video Application:

NTSC NTSC w/setup 525_I 525_I w/setup 525_P

WHITE (235) Programable, Programable, Programable, Programable, Programable,

19

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

1.22 - - V

- - 0.4 V

2.4 - - V

- - 0.4 V

KΩ

KΩ

0.9 1.0 1.1 V

P

90 dBr(A)

带格式的:

带格式的:

项目符号和编号

项目符号和编号

Page 26

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Current setting:

3297

Current setting:

3297

Current setting:

3297

Current setting:

3297

Current setting:

3290

BLACK (16) 960 1120 960 1120 1008

PEDESTAL 960 960 960 960 1008

SYNC TIP 64 64 64 64 64

525_P w/s PAL 625_I 625_P RGB

WHITE (235) ---

Programable,

Current setting:

3290

Programable,

Current setting:

3290

Programable,

Current setting:

3290

Programable,

Current setting:

2282

BLACK (16) --- 1008 1008 1008 0

PEDESTAL --- 1008 1008 1008 -

SYNC TIP --- 64 64 64 -

9-4 Video Output Voltage Level:

High Impedance Mode:

I

(max) = 19.4152 / R

OUT

(max) = R

V

OUT

= D

V

OUT

/ 4095 * V

IN

LOAD

, R

REF

* I

(max) = 1.3237 V, R

OUT

(max) = D

OUT

= 2.2 KOhm

REF

* R

IN

LOAD

= 150 Ohm

LOAD

* 0.0047412 / R

REF

Low Impedance Mode:

I

(max) = 19.4152 / R

OUT

(max) = R

V

OUT

= D

V

OUT

/ 4095 * V

IN

LOAD

, R

REF

* I

(max) = 1.3 V, R

OUT

(max) = D

OUT

= 560 Ohm

REF

* R

IN

= 37.5 Ohm ( 75 Ohm || 75 Ohm )

LOAD

* 0.0047412 / R

LOAD

REF

9-5 Video DAC DC Electrical Characteristics

(Operating Free-Air Temperature, AVDD 3.3V, DVDD = 3.3V).

Analog Output MIN TYP MAX UNIT

Full Scale Output Current CVBS/Y/C/R/G/B (low impedance mode) 33.6 34.6 34.9 mA

Full Scale Output Current CVBS/Y/C/R/G/B (high impedance mode) 8.40 8.65 8.73 mA

LSB current CVBS/Y/C/R/G/B (low impedance mode) 32.8 33.8 34.1 uA

LSB current CVBS/Y/C/R/G/B (high impedance mode) 8.20 8.45 8.52 uA

DAC-to-DAC Mis-Matching -- 1.28 -- %

Output Compliance 0 -- 1.35 V

带格式的:

项目符号和编号

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

20

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 27

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

DAC Output Delay -- 1.5 10 ns

DAC Rise/Fall Time -- 2.1 5

Voltage Reference

Reference Voltage Output 1.27 V

Reference Input Current 2.267 MA

Static Performance

DAC Resolution 12 Bits

DNL Differential Non-Linearity +/-0.2 */-0.25 +/-0.3 LSB

INL Integral Non-Linearity +/-0.35 */-0.4 +/-0.49 LSB

Dynamic Performance

Differential Gain 0.8 1.5 %

Differential Phase 0.6 1.5 ∘

S/N Ratio 70 dB

Power Supply

Supply Voltage 3.0 3.3 3.6 V

RF specification

9-6

带格式的:

项目符号和编号

Item Designator Conditions Min Typ Max Unit

3.3V POWER 3.00 3.30 3.60 Volts

Power Down Mode

Reference Voltage V20 Force current =0A 1.85 1.99 2.15 Volts

Reference Voltage VREFO Force current =0A 1.25 1.39 1.55 Volts

Reference Voltage V2REFO Force current =0A 2.65 2.78 2.95 Volts

MDI1

APC1(CD)

APC2(DVD)

LDO1 0Ah=00 ;APC1 off 3.00 3.28 V

MDI1→LDO1

MDI2

Enable power down 10 27 50 mA

Chip Reset 90 151 200 mA

0Ah=10 ;APC1 on

MDI1=180mV

0Ah=10; APC1 on 212 254 295 V/V

0Bh=10 ;APC2 on

MDI2=180mV

166 184 202 mV

166 184 202 mV

21

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 28

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Designator Conditions Min Typ Max Unit

LDO2 0Bh=00 ;APC2 off 3.00 3.28 V

Focusing Error Ga in

Focusing Error Frequency

Response

Focusing Error Commo n

Mode Gain

Focusing Error H/L Gain

Focusing Error off set

Adjustment step

Focusing Error THD

Central Servo Gain

Central Servo Frequency

Response

Central Servo Common

Mode Gain

MDI2→LDO2

MA → FEO

MA → FEO

MA → FEO

MB → FEO

MA → FEO

Input Floating

Measure FEO

MA → FEO

MA → CSO

MA → CSO

MA → CSO

MB → CSO

0Bh=10; APC2 on

High gain

05h=30; low gain

With 10KHz Sin Input

05h=7C; low gain

With 10KHz, 300KHz Sin Input

R=G(10kHz)-G(300Khz)

05h=3F; low gain

With 10KHz Sin Input

Toggle 05h bit5 : FELG

With 10KHz Sin Input

Toggle 4Dh : FEOS[6:0] 65 103 140 mV

05h=7C; low gain

With 10KHz Sin Input

06h=F0; low gain

With 10KHz Sin Input

06h=FF; low gain

With 10KHz, 300KHz Sin Input

R=G(10kHz)-G(300Khz)

06h=F0; low gain

With 10KHz Sin Input

210 265 298 V/V

7.5 10.3 11.5 dB

16 23.9 dB

-34 -20 dB

2.75 2.99 3.25 V/V

30 54 dB

12.5 14.1 15.5 dB

14 21.4 dB

-30 -10 dB

Central Servo H/L Gain

Central Servo offset

Adjustment step

MA → CSO

Input Floating

Measure CSO

Toggle 06h bit5 : CSOLG

With 10KHz Sin Input

Toggle 4Eh : CSOOS[6:0] 65 108 140 mV

2.75 2.97 3.25 V/V

22

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 29

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Designator Conditions Min Typ Max Unit

Central Servo THD

Tracking Error Gain

Tracking Error Frequency

Response

Tracking Error Common

Mode Gain

Tracking Error H/L Gain

Tracking Error offset

Adjustment step

Tracking Error THD

RFL Gain

RFL Frequency Response

RFL H/L Gain I

RFL H/L Gain II

RFL offset Adjustment

step

RFL THD

MA → CSO

MA → TEO

MA → TEO

MA → TEO

MB → TEO

MA → TEO

Input Floating

Measure TEO

MA → TEO

MA → LVL

MA → LVL

MA → LVL

SA → LVL

Input Floating

Measure LVL

MA → LVL

06h=F0; low gain

With 10KHz Sin Input

07h=70; low gain

With 10KHz Sin Input

07h=70; low gain

With 10KHz, 300KHz Sin Input

R=G(10kHz)-G(300Khz)

07h=7F; low gain

With 10KHz Sin Input

Toggle 07h bit6, 5

With 10KHz Sin Input

Toggle 4Fh : TEOS[6:0] 65 110 140 mV

07h=7F; low gain

With 10KHz Sin Input

08h=60; low gain

With 10KHz Sin Input

08h=7F; low gain

With 10KHz, 300KHz Sin Input

R=G(10kHz)-G(300Khz)

Toggle 09h bit1 : LVLATN

With 10KHz Sin Input

Toggle 09h bit2 : SBADHG

With 10KHz Sin Input

Toggle 50h : LVLOS[6:0] 65 113 140 mV

08h=7F; low gain

With 10KHz Sin Input

30 53 dB

13 15 17 dB

16 24.2 dB

-22 -10 dB

4 5.8 8 V/V

30 42 dB

-6.5 -4.6 -3.5 dB

14 22.7 dB

0.3 0.52 0.7 V/V

2.5 2.77 3.1 V/V

30 44 dB

23

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 30

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Micro Controller Interface

9-7

Parameter Symbol Min. Max. Units

Oscillator Frequency 1/Tf 0 23.3 MHz

ALE Pulse Width T0 1.5Tf-5 ns

ALE Low to Valid Instruction T1 2.5Tf-20 ns

ALE Low to PSEN Low T5 0.5Tf-5 ns

Address Valid to ALE Low T2 0.5Tf-5 ns

Address Hold After ALE Low T9 0.5Tf-5 ns

PSEN Pulse Width T3 2.0Tf-5 ns

PSEN Low to Valid Instruction T4 2.0Tf-20 ns

Input Instruction Hold Aft e r PSE N high T8 0 ns

Input Instruction Float After PSEN high T6 1.0Tf-5 ns

Port 0 Address to Valid Instruction T10 3.0Tf-20 ns

Port 2 Address to Valid Instruction T11 3.5Tf-20 ns

PSEN Low to Address Float T7 0 ns

带格式的:

项目符号和编号

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

24

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 31

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

t0 t1

MT1389L

ALE

PSEN

Port 0

Port 2

Program Memory Read Cycle Timing Diagram

Digital Video Output Interface

9-8

Parameter Symbol Min Typ Max Units

Oscillator Frequency 1/T1 27 MHz

YUV digital output delay T2 15 ns

HSYNC Rising delay T3 15 ns

VSYNC Rising delay T4 15 ns

HSYNC Falling delay T5 20 ns

VSYNC Falling delay T6 20 ns

t2

t3

t4

t5

t7

t9

ADR[7:0] Ins t. ADR[7:0]

t10

t11

ADR[15:8]

t6

t8

带格式的:

项目符号和编号

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

25

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 32

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

t1

XTALI

YUV[7:0]

t2

YUV[7:0]

t3

t5

YUV[7:0]

HSYNC

t

6

VSYNC

t

4

Digital Video Output Interface Timing Diagram

SPDIF I/O Interface

9-9

带格式的:

项目符号和编号

Parameter Symbol Min Typ Max Units

BCK negative edge to ASDATA valid T1 1.0 3.0 ns

ASDATA/LRCK input setup T2 3.0 ns

ASDATA/LRCK input hold T3 1.2 ns

BCK

1

t

ASDATA/LRCK

ASDATA/LRCK

SPLIN_BCK

ASDATA/LRCK

(input)

t2

ASDATA/LRCK

t3

ASDATA/LRCK

SPDIF Input/Output Timing Diagram

DRAM Interface

9-10

带格式的:

项目符号和编号

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

26

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 33

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

0 1 2 3 4 5 6 7 8 9 1 0 1 1 1 2 1 3 1 4 15 1 6 1 7 18 1 9 2 0 2 1 2 2 2 3 2 4 25

CLK

CS

RAS

tRCD

tR A S

tR P

CAS

WE

tS H

ADR

BA

AP

DQ

tS S

BS BS BS BS

Ra

Ca CbRa

Qa Db

Rb

BS

Rb

DQM

tW R

CKE

R o w A c tive R e ad W rite P re c h ar g e R o w A c tiv e

Parameter Symbol

CLK cycle time

CAS latency = 3 7.5 7.5 8

tCC

CAS latency = 2

SDRAM input setup time tSS 1.5 1.75 2 ns

SDRAM input hold time tSH 1 1 1 ns

Active to Precharge command period tRAS 42 100K 49 100K 48 100K ns

Precharge to Active command period tRP 18 20 20 ns

Active to read/write command delay tRCD 18 20 20 ns

Write recovery time

CL = 3 6 7 8

tWR

CL = 2

-6 -7 -8

Min Max Min Max Min Max

8

10

10

10

10

10

Units

- ns

ns

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

27

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 34

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

FREQUENCY vs. AC PARAMETER RELATIONSHIP TABLE

-6T

(Unit: number of clock)

Frequency

133MHz (7.5ns) 3 6 3 3 1

125MHz (8ns) 2 6 3 3 1

100MHz (10ns) 2 5 2 2 1

-7T

133MHz (7.5ns) 3 7 3 3 1

125MHz (8ns) 3 6 3 3 1

100MHz (10ns) 2 5 2 2 1

-7.5T

(Unit: number of clock)

Frequency

(Unit: number of clock)

Frequency

CAS

Latency

CAS

Latency

CAS

Latency

tRAS tRP tRCD tWR

42ns 18ns 18ns 6ns/10ns

tRAS tRP tRCD tWR

49ns 20ns 20ns 7ns/10ns

tRAS tRP tRCD tWR

45ns 20ns 20ns 7.5ns/10ns

133MHz (7.5ns) 3 6 3 3 1

125MHz (8ns) 3 6 3 3 1

100MHz (10ns) 2 5 2 2 1

-8T

125MHz (8ns) 3 6 3 3 1

100MHz (10ns) 3 5 2 2 1

(Unit: number of clock)

Frequency

CAS

Latency

tRAS tRP tRCD tWR

48ns 20ns 20ns 8ns/10ns

28

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 35

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

10 Marking on Devices

Date Code (Year+Week)

MediaTek Logo

MTK Production Code

MT1389 FE

YYWW- LXXL

LLLLL

Lot No.

Product Name

Lead Free Product

11 Package Description

11-1 Package Outline Dimension

The bend lead are controlled under the criteria 0.075mm (2.5mil).

29

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

带格式的:

项目符号和编号

Page 36

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

30

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 37

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

11-2 Weight of the chip

0.65g

Material and Finish of Lead Terminals

11-3

For Normal Package, (Materials of terminal is Sn(85%) and Pb (15%)and thickness is 300~600u inch.

For Lead-free Package, (Materials of terminal is Sn(98%) and Bi (2%)and thickness is 300~600u inch,

similar as SnPb.

Package Material

11-4

Lead frame: Cu

Epoxy: 1033BF

Molding compound: G700

带格式的:

带格式的:

带格式的:

项目符号和编号

项目符号和编号

项目符号和编号

12 Packing Description

Package Pin / Ball count EA / Tray Tray / Box Full Box Q’ty Box / Carton Full carton Q’ty

LQFP 128 90 10 900 6 5400

Tray Description

12-1

40ea/ Hard Tray (150oC resistance).

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

31

带格式的:

带格式的:

项目符号和编号

项目符号和编号

Page 38

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

32

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 39

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Desiccants

12-2

Size: 110*120 mm.

Weight: 66g

Aluminum Foil Bag

12-3

Size: 250*500 mm.

Thickness: 0.12 +/- 0.005 mm.

8

Surface impedance: 10

-1012 Ohm/SQ

Box Description

12-4

Material: 3 Layer B corrugated paper.

Strength: 1176000 PA.

Box size: 355(L)*157(W)*90.5(H) mm.

Printing: Black (words, warning, index)

带格式的:

带格式的:

带格式的:

项目符号和编号

项目符号和编号

项目符号和编号

Side Plank

12-5

Material: 5 Layer AB corrugated paper

Strength: 1793400 PA.

Size: 405(L)*237(W) mm.

Fixture: 3 pieces of EPE (recyclable material).

Thickness: 20 mm.

Carton Description

12-6

Material: 5 Layer AB corrugated paper.

Strength: 1793400 PA.

Carton size: 558(L)*428(W)*264(H) mm.

Printing: Black (words, warning, index)

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

33

带格式的:

带格式的:

项目符号和编号

项目符号和编号

Page 40

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

12-7 Packing Flow

Pin No. 1

direction

40pcs per tray

Empty tray

10 tray

带格式的:

项目符号和编号

Label is on top of the

Aluminum foil bag.

Aluminum foil bag

34

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 41

V1.2

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT1389L

Air cap

Box with the Aluminum foil bag

6 box per carton

Side plank

Label is on top

of the BOX.

Fill with empty box if the

quantity is less than 6 box

35

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 42

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

13 Solder-Reflow Condition

13-1 Reflow Condition

MTK can guarantee 3 times IR reflow base on the reflow curve.

Average ramp-up rate (217

Preheat : 150~200

o

C、60~180 seconds

Temperature maintained above 217

o

Time within 5

C of actual peak temperature : 20 ~ 40 sec.

Peak temperature : 250+0/-5

o

Ramp-down rate : 6

o

Time 25

C to peak temperature : 8 minutes max.

C /sec. max.

Cycle interval : 5 minus

o

217

C

o

C to peak) : 3 oC /sec. max.

o

C : 60~150 seconds

o

C

Slope: Max. 3

o

(217

C to peak)

o

C /sec

Peak: 250+0/-5

o

C

Ramp down rate :

o

Max. 6

C /sec.

带格式的:

项目符号和编号

Preheat: 150~200

o

C

20~40 sec.

60 ~ 180 sec. 60 ~150sec

o

25

C

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

36

or disclosed in whole or in part without prior written permission of MediaTek Inc

Time (sec)

Page 43

V1.2

MT1389L

Desktop DVD Player SOC

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

13-2 Pre-process and Heat Treatment

Procedure: (MRT L3)

[Package opening] Æ [Baking] Æ [Humidification] Æ [Reflow]

A. Conditions between each step of procedure

o

Be lift for duration of 2 hours or longer at temperature of 30

C or lower and a humidity of 60% R.H.

or lower.

o

B. Baking 125

C. Humidification: 30

C, 24 hours.

o

C, 60% R.H., 192 Hours

D. Reflow: 3 x 260oC

14 Manual Solder Condition

The specimen should be in the as-delivered condition. Set the soldering iron at a temperature of 300 +/- 10 oC

(at the iron bit). Place the iron and flux-cored solder in parallel with each and every terminal/lead on the back

of the board for a duration which does not exceed 5 seconds without applying any mechanical stress on the

component body.

o

It can also be applied under 350 +/- 10

condition.

C at the iron bit within 3 seconds, please treat it carefully under such

带格式的:

带格式的:

项目符号和编号

项目符号和编号

The chip can’t do DIP soldering.

37

All information contained herein is the exclusive property of MediaTek Inc. and shall not be distributed, reproduced

or disclosed in whole or in part without prior written permission of MediaTek Inc

Page 44

2-1-3 Serial EEPROM, 2K (256 x 8) (24C02) or 16 K (2048 x 8) (24C16)

24C02 is used for DVD player while 24C16 is for DVD receiver. The capacity is the only difference between

two kinds of serial EEPROM. Both of them use same package and have same pin configuration.

* Features

z Low-Voltage and Standard-Voltage Operation

-5.0 (V CC = 4.5V to 5.5V)

-2.7 (V CC = 2.7V to 5.5V)

-2.5 (V CC = 2.5V to 5.5V)

-1.8 (V CC = 1.8V to 5.5V)

z Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K), 1024 x 8 (8K) or 2048 x 8 (16K)

z 2-Wire Serial Interface

z Schmitt Trigger, Filtered Inputs for Noise Suppression

z Bi-directional Data Transfer Protocol

z 100 kHz (1.8v, 2.5V, 2.7V) and 400 kHz (5V) Compatibility

z Write Protect Pin for Hardware Data Protection

z 8-Byte Page (1K, 2K), 16-Byte Page (4K, 8K, 16K) Write Modes

z Partial Page Writes Are Allowed

z Self-Timed Write Cycle (10 ms max)

z High Reliability

- Endurance: 1 Million Write Cycles

- Data Retention: 100 Years

-

- ESD Protection: >3000V

z Automotive Grade and Extended Temperature Devices Available

z 8-Pin and 14-Pin JEDEC SOIC, 8-Pin PDIP, 8-Pin MSOP, and 8-Pin TSSOP Packages

* Pin Configurations

* Pin Description

Pin Name Function

A0-A2 Address Inputs

SDA Serial Data

SCL Serial Clock input

WP Write Protect

NC No Connect

- 19 -

Page 45

2-1-4:

Boot Sector Flash Memory

A29L800 Series

1M X 8 Bit / 512K X 16 Bit CMOS 3.0 Volt-only,

Features

n Single power supply operation

- Full voltage range: 2.7 to 3.6 volt read and write

operations for battery-powered applications

n Access times:

- 70/90 (max.)

n Current:

- 9 mA typical active read current

- 20 mA typical program/erase current

- 200 nA typical CMOS standby

- 200 nA Automatic Sleep Mode current

n Flexible sector architecture

- 16 Kbyte/ 8 KbyteX2/ 32 Kbyte/ 64 KbyteX15 sectors

- 8 Kword/ 4 KwordX2/ 16 Kword/ 32 KwordX15 sectors

- Any combination of sectors can be erased

- Supports full chip erase

- Sector protection:

A hardware method of protecting sectors to prevent

any inadvertent program or erase operations within

that sector. Temporary Sector Unprotect feature

allows code changes in previously locked sectors

n Extended operating temperature range: -45°C ~ +85°C

for -U series

n Unlock Bypass Program Command

- Reduces overall programming time when issuing

multiple program command sequence

n Top or bottom boot block configurations available

n Embedded Algorithms

- Embedded Erase algorithm will automatically erase

the entire chip or any combination of designated

sectors and verify the erased sectors

- Embedded Program algorithm automatically writes

and verifies data at specified addresses

n Typical 100,000 program/erase cycles per sector

n 20-year data retention at 125°C

n Compatible with JEDEC-standards

- Pinout and software compatible with single-power-

n

n Ready /

- Provides a hardware method of detecting completion

n Erase Suspend/Erase Resume

n Hardware reset pin (

n Package options

- Reliable operation for the life of the system

supply Flash memory standard

- Superior inadvertent write protection

Polling and toggle bits

Data

- Provides a software method of detecting completion

of program or erase operations

pin (RY / BY)

BUSY

of program or erase operations (not available on 44pin SOP)

- Suspends a sector erase operation to read data from,

or program data to, a non-erasing sector, then

resumes the erase operation

RESET

- Hardware method to reset the device to reading array

data

- 44-pin SOP or 48-pin TSOP (I) or 48-ball TFBGA

)

-20-

Page 46

General Description

The A29L800 is an 8Mbit, 3.0 volt-only Flash memory

organized as 1,048,576 bytes of 8 bits or 524,288 words of

16 bits each. The 8 bits of data appear on I/O0 - I/O7; the 16

bits of data appear on I/O0~I/O15. The A29L800 is offered in

48-ball TFBGA, 44-pin SOP and 48-Pin TSOP packages.

This device is designed to be programmed in-system with the

standard system 3.0 volt VCC supply. Additional 12.0 volt

VPP is not required for in-system write or erase operations.

However, the A29L800 can also be programmed in standard

EPROM programmers.

The A29L800 has the first toggle bit, I/O6, which indicates

whether an Embedded Program or Erase is in progress, or it

is in the Erase Suspend. Besides the I/O6 toggle bit, the

A29L800 has a second toggle bit, I/O2, to indicate whether

the addressed sector is being selected for erase. The

A29L800 also offers the ability to program in the Erase

Suspend mode. The standard A29L800 offers access times

of 70 and 90ns, allowing high-speed microprocessors to

operate without wait states. To eliminate bus contention the

device has separate chip enable (CE), write enable (WE)

and output enable (OE) controls.

The device requires only a single 3.0 volt power supply for

both read and write functions. Internally generated and

regulated voltages are provided for the program and erase

operations.

The A29L800 is entirely software command set compatible

with the JEDEC single-power-supply Flash standard.

Commands are written to the command register using

standard microprocessor write timings. Register contents

serve as input to an internal state-machine that controls the

erase and programming circuitry. Write cycles also internally

latch addresses and data needed for the programming and

erase operations. Reading data out of the device is similar to

reading from other Flash or EPROM devices.

Device programming occurs by writing the proper program

command sequence. This initiates the Embedded Program

algorithm - an internal algorithm that automatically times the

program pulse widths and verifies proper program margin.

Device erasure occurs by executing the proper erase

command sequence. This initiates the Embedded Erase

algorithm - an internal algorithm that automatically

preprograms the array (if it is not already programmed)

before executing the erase operation. During erase, the

device automatically times the erase pulse widths and

verifies proper erase margin. The Unlock Bypass mode

facilitates faster programming times by requiring only two

write cycles to program data instead of four.

The host system can detect whether a program or erase

operation is complete by observing the RY / BY pin, or by

reading the I/O7 (

After a program or erase cycle has been completed, the

device is ready to read array data or accept another

command.

The sector erase architecture allows memory sectors to be

erased and reprogrammed without affecting the data

contents of other sectors. The A29L800 is fully erased when

shipped from the factory.

The hardware sector protection feature disables operations

for both program and erase in any combination of the

sectors of memory. This can be achieved via programming

equipment.

The Erase Suspend/Erase Resume feature enables the user

to put erase on hold for any period of time to read data from,

or program data to, any other sector that is not selected for

erasure. True background erase can thus be achieved.

The hardware

progress and resets the internal state machine to reading

array data. The

circuitry. A system reset would thus also reset the device,

enabling the system microprocessor to read the boot-up

firmware from the Flash memory.

The device offers two power-saving features. When

addresses have been stable for a specified amount of time,

the device enters the automatic sleep mode. The system can

also place the device into the standby mode. Power

consumption is greatly reduced in both these modes.

Polling) and I/O6 (toggle) status bits.

Data

RESET

RESET

pin terminates any operation in

pin may be tied to the system reset

-21-

Page 47