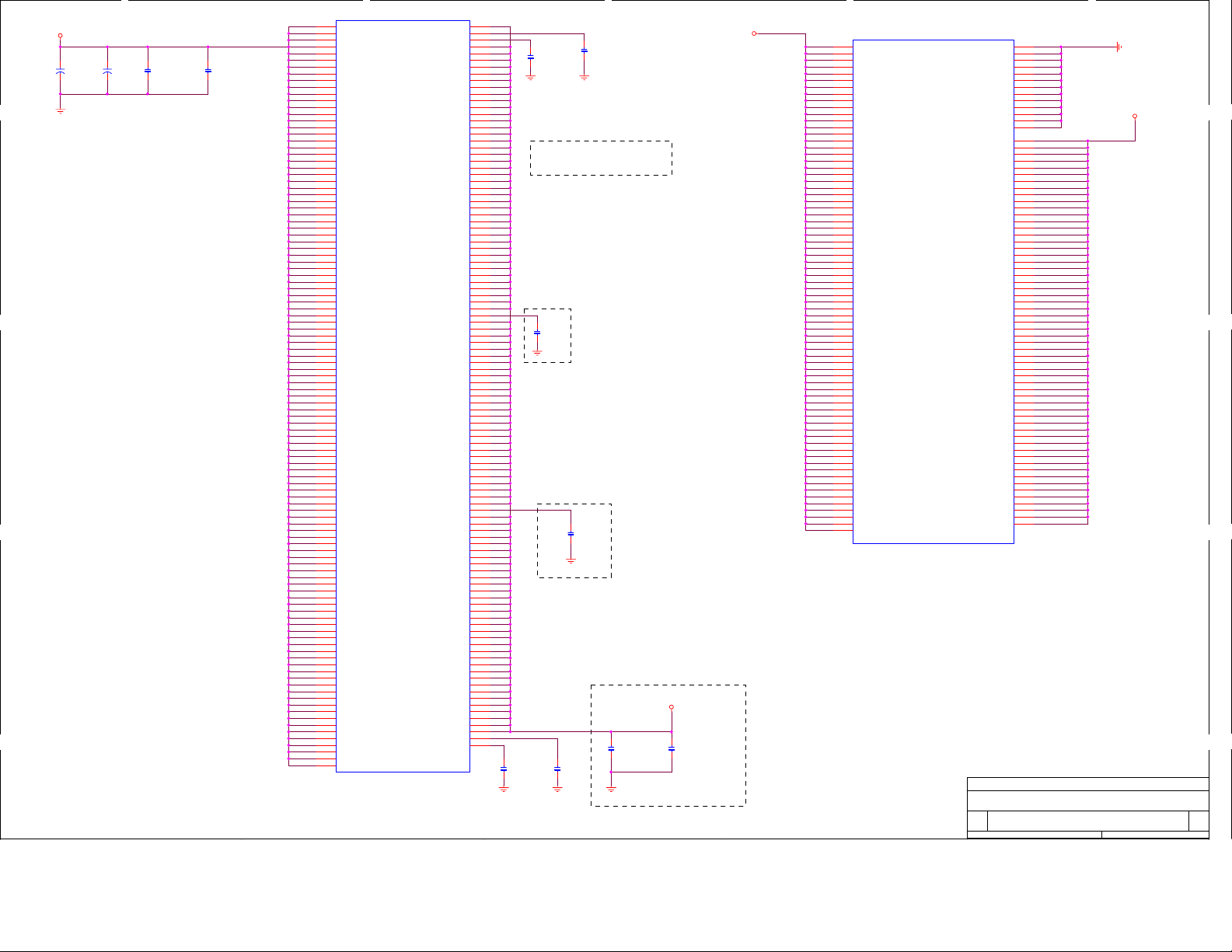

Page 1

1

Cover Sheet

Block Diagram

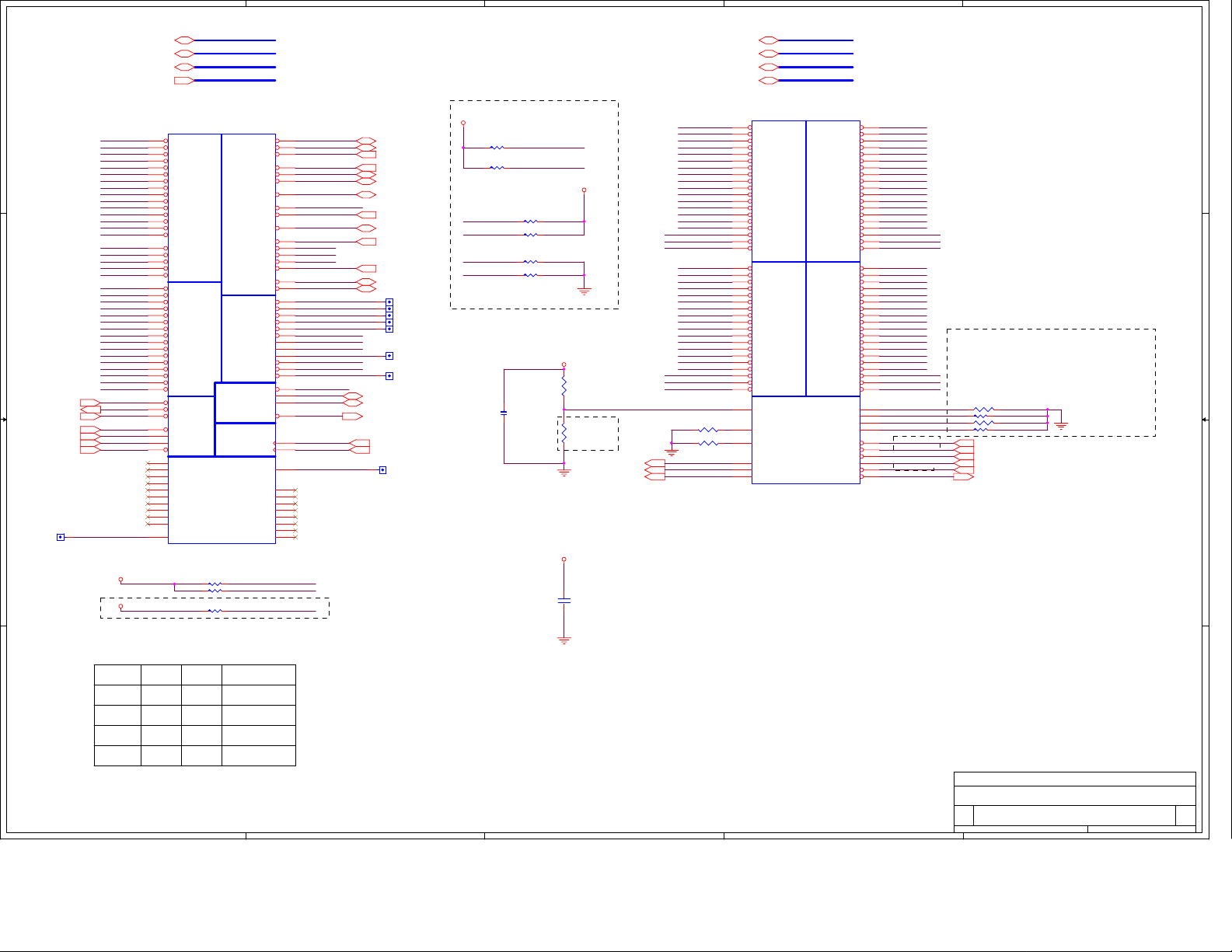

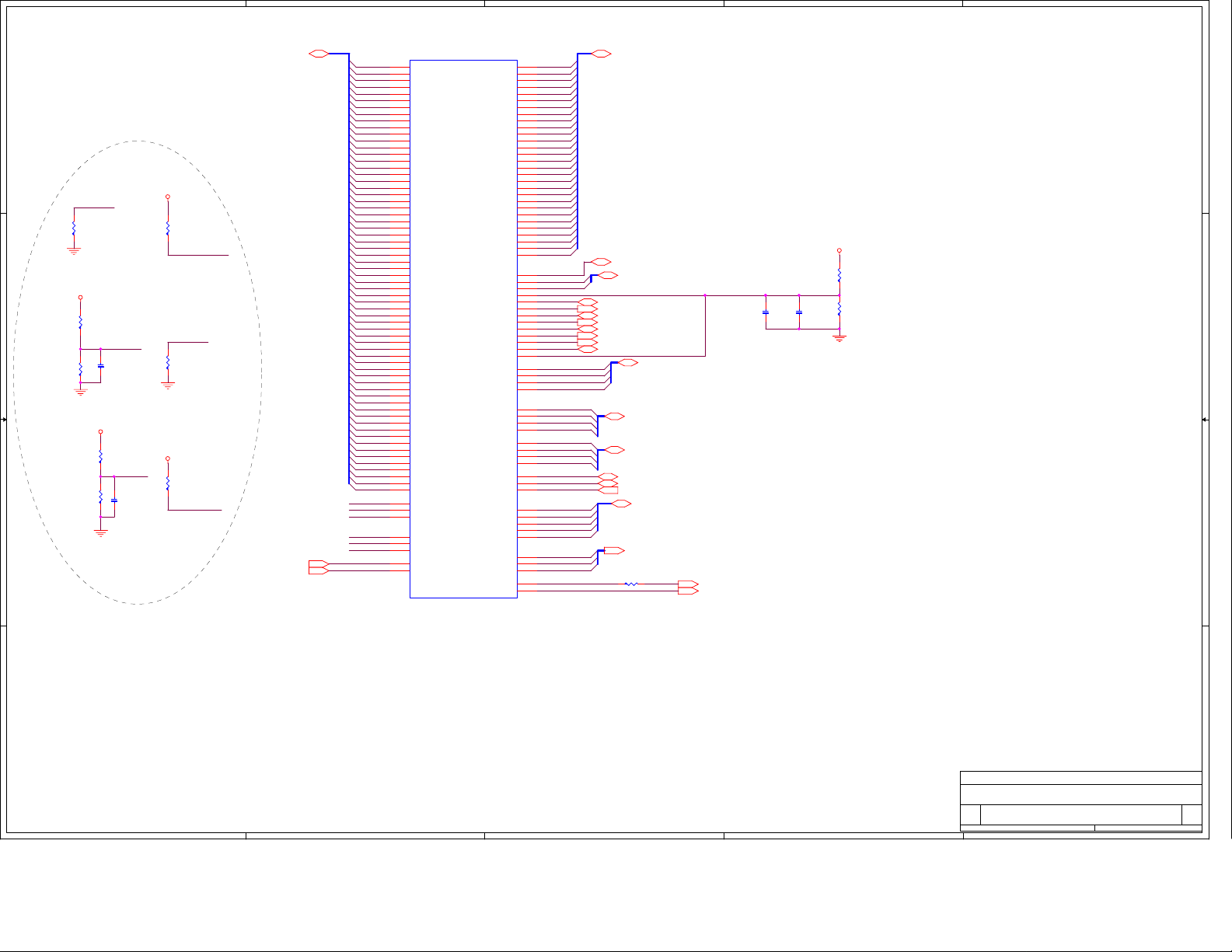

Intel Yonah CPU

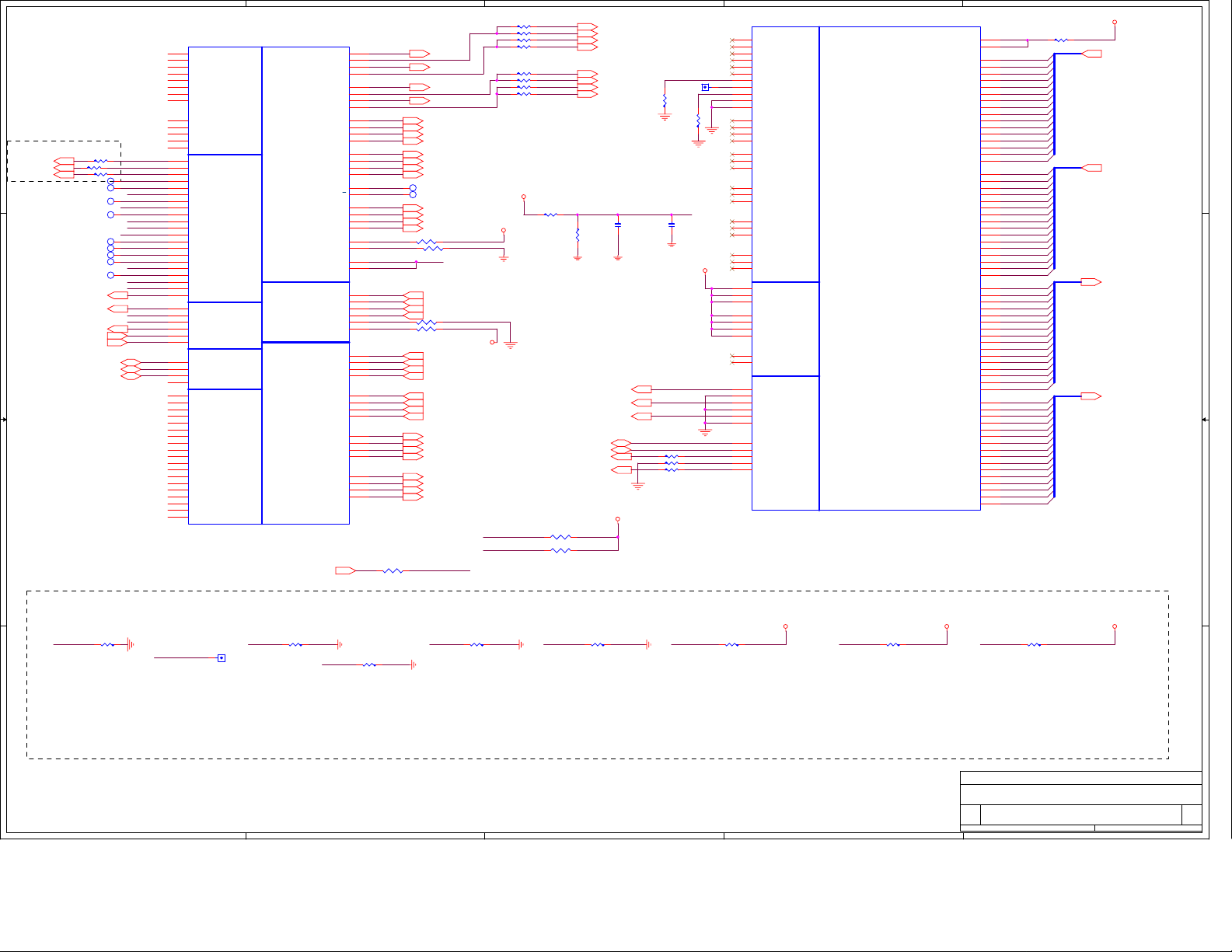

Intel 945GT

Intel ICH7M-DH - PCI & DMI & CPU & IRQ

Intel ICH7M-DH - LPC & ATA & USB & GPIO & POWER

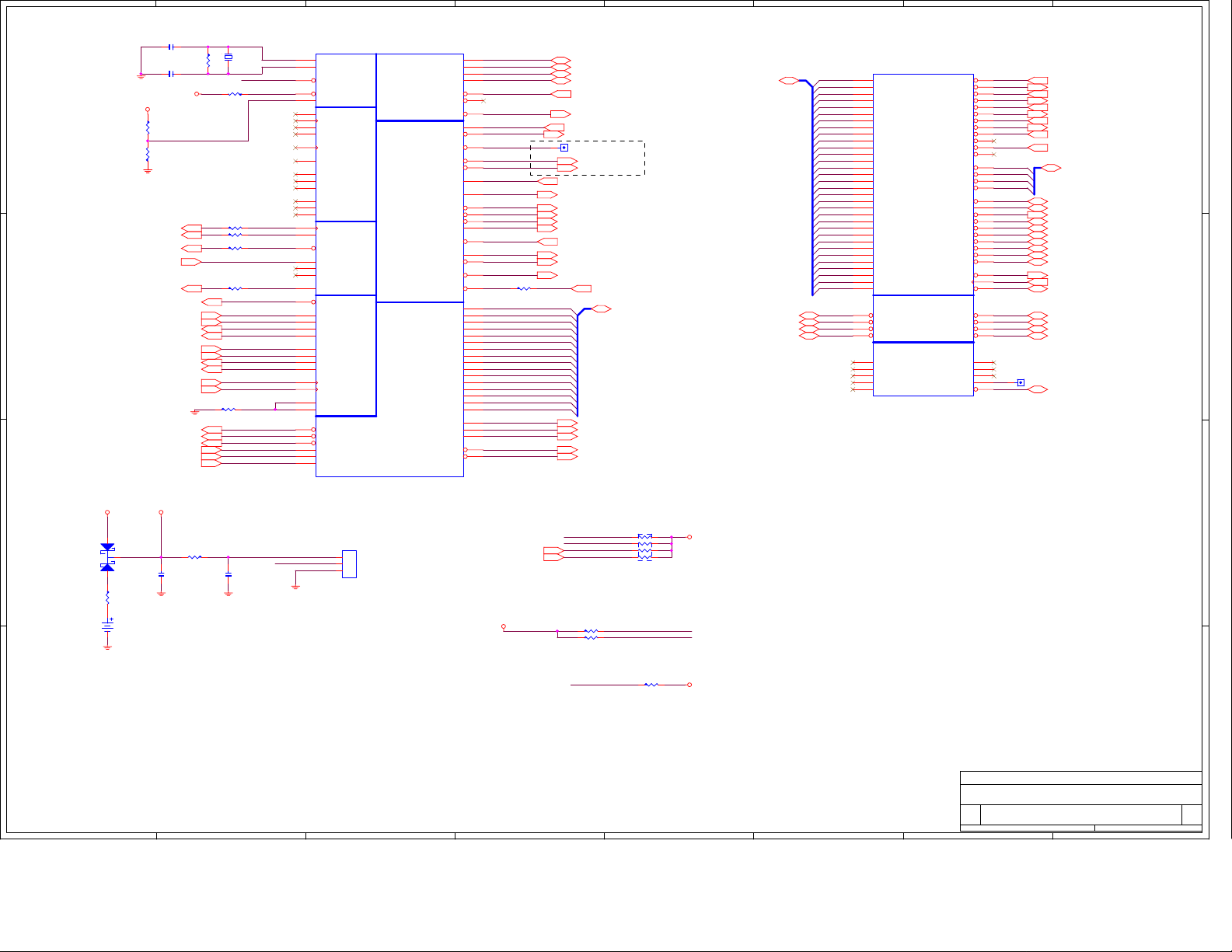

LPC I/O - W83627EHG

Azalia ALC880 17

LAN -- INTEL 82573E

SATA2 - SIL 3132

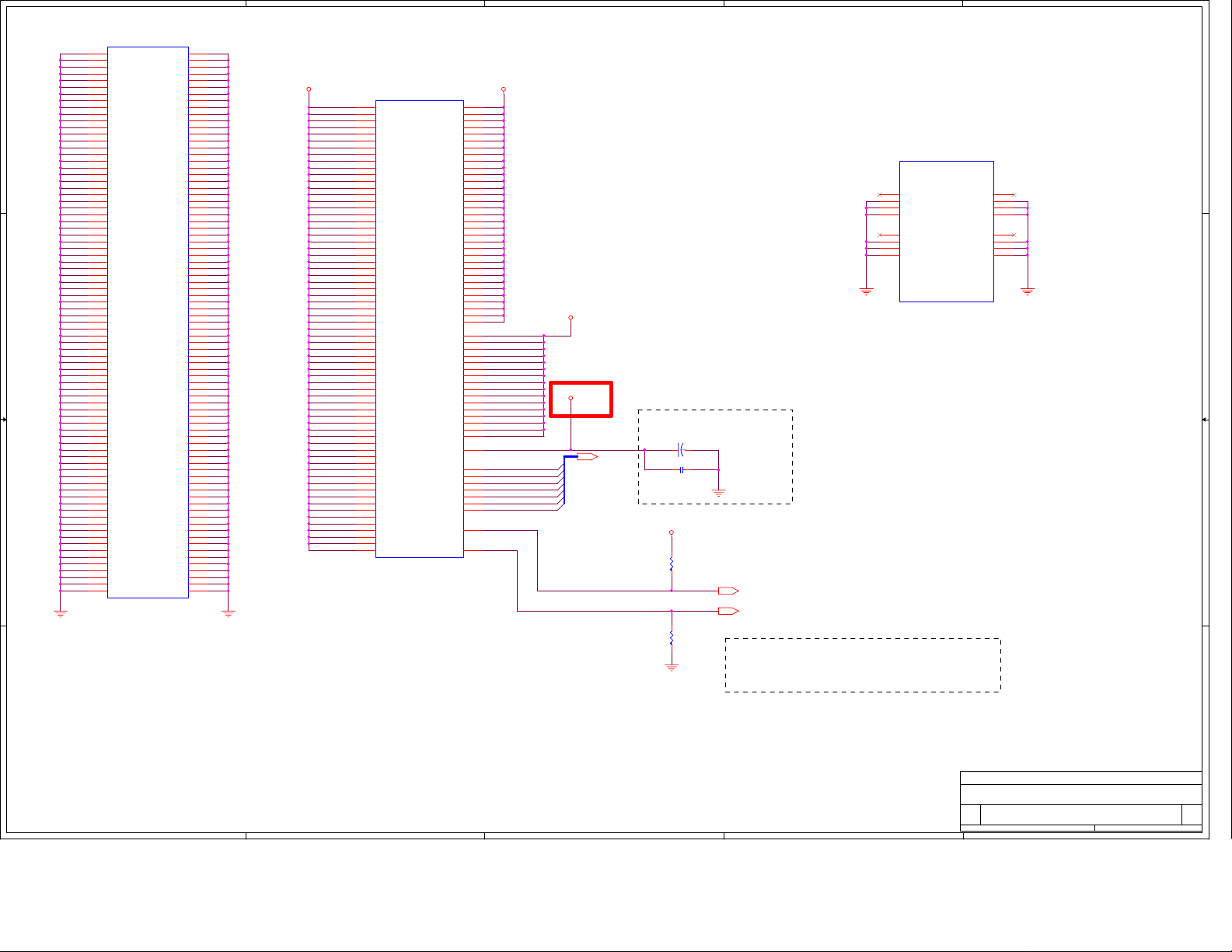

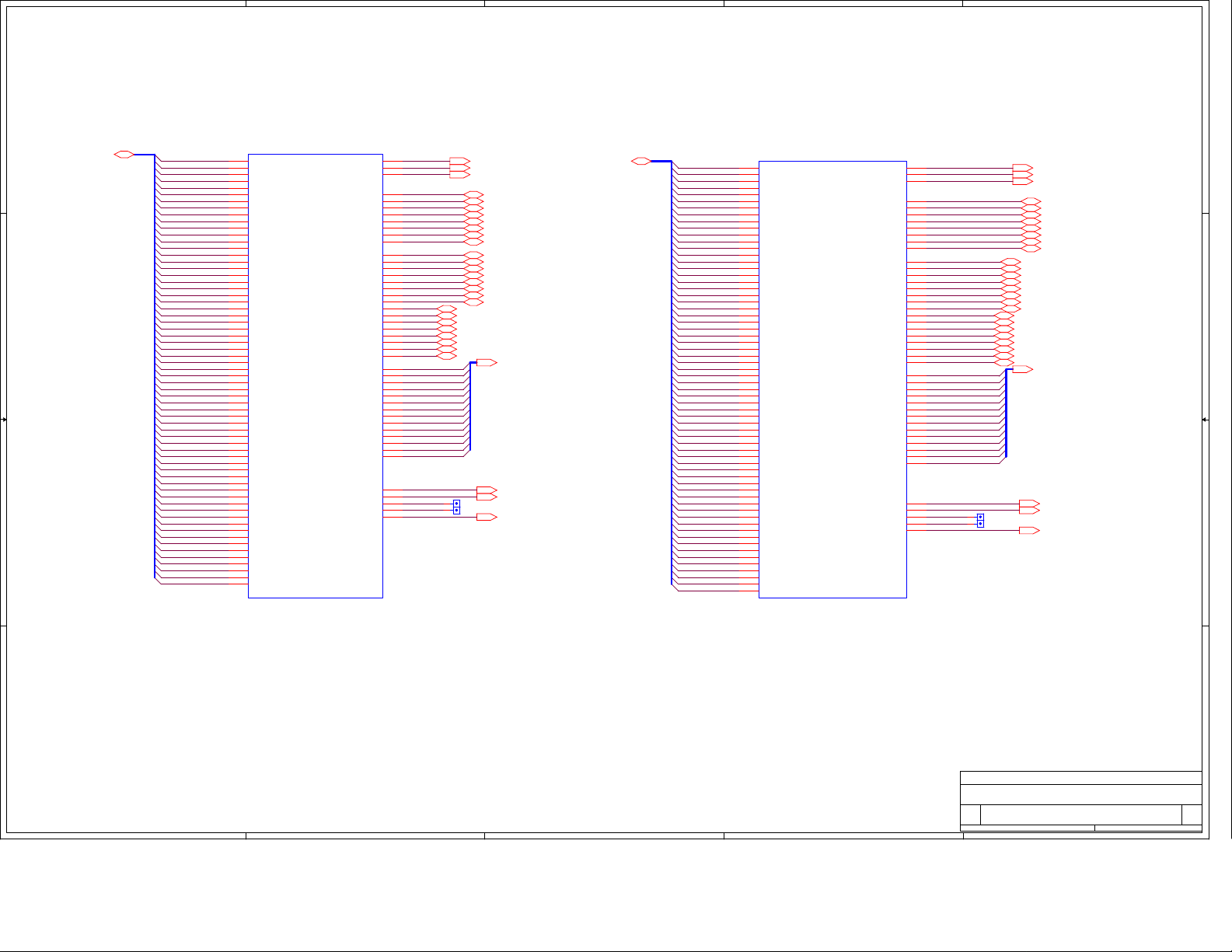

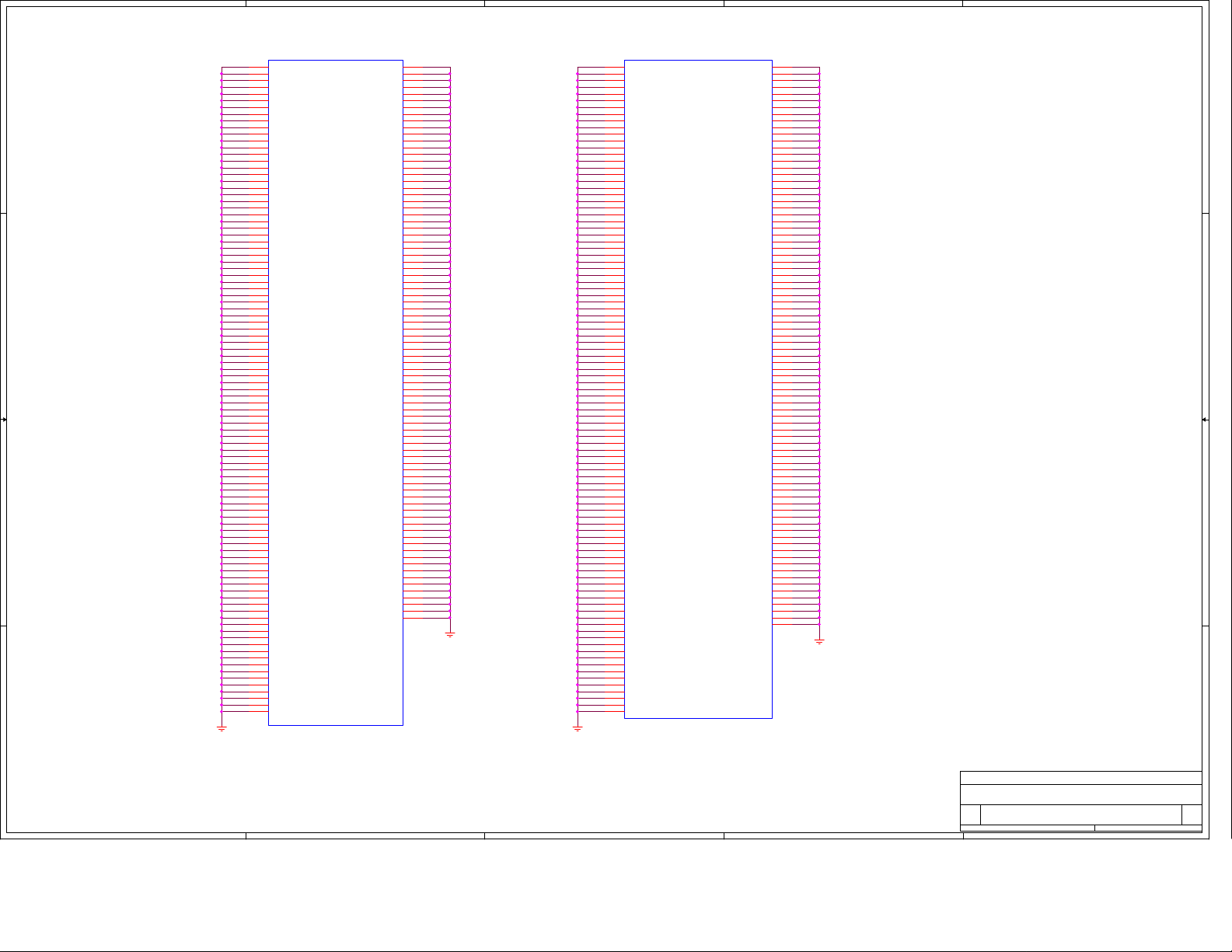

DDR2 System Memory 1 & 2

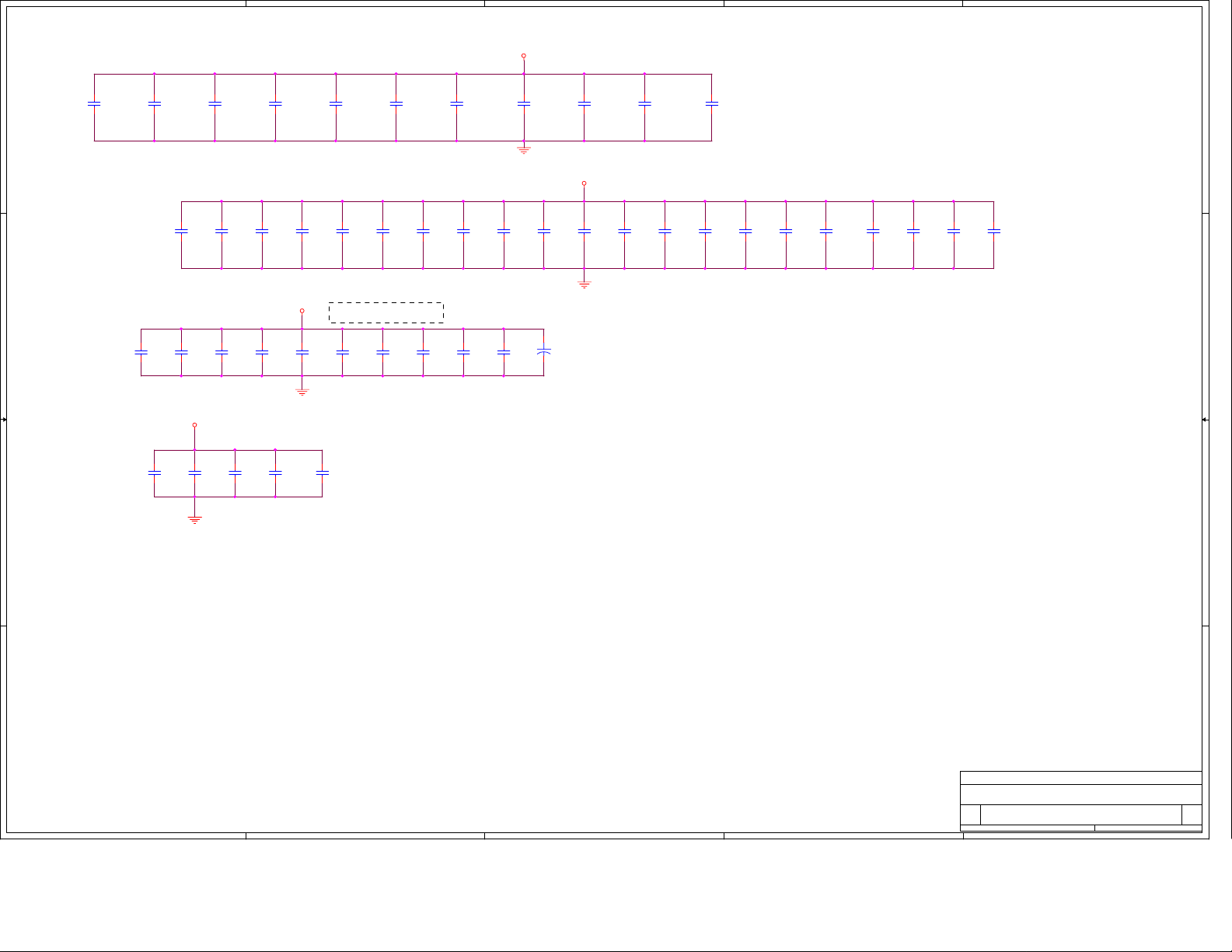

DDR Termination Resistors

1

2

3-5

6-11

12

13-14

15Clock -ICS954129 & FWH

16

18

19

20

21

MS-9631

CPU:

Intel Yonah/Merom Processor

System Chipset:

Intel 945 GT - GMCH (North Bridge)

Intel ICH7M-DH (South Bridge)

On Board Chipset:

Clock Generator - ICS954129

LAN -- INTEL 82573E

LPC Super I/O -- W83627EHG

Version 1.0

01/18/2006

Azalia ALC880

A A

TPM 22

PCI Slot / PCI EXPRESS X16 Slot

USB Connectors

23-24

25

VIA-6307 IEEE1394 Controller

SIL-3132 SATA2 Controller

BIOS -- FWH EEPROM

TPM -- Infineon SLD9635

2623ATX , VGA Connetcors & Front Panel

CH7307 & DVI CONNECTOR

MS-7 ACPI Controller & MS-6 Plus

27

28

Main Memory:

DDR 2 * 2 (Max 4GB)

FAN, SATA & IDE CONNECTORS

IEEE 1394 CONTROLLER

CPU Power

GPIO & JUMPER SETTTING

MANUAL PAR T S

Power MAP

CLOCK MAP

POWER SEQUENCE/SMBUS MAP 36

29

30

31

32

33

34

35

Expansion Slots:

PCI EXPRESS X16 SLOT

Mini PCI type III *1

PCI2.3 SLOT * 1

V-core PWM:

IMVP-6 Controller: ISL6262

System power PWM:

MS-7 & MS-6 +

1

Title

Size Document Number Rev

Custom

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

Cover Sheet

MS-9631

of

137Monday, February 13, 2006

1.0

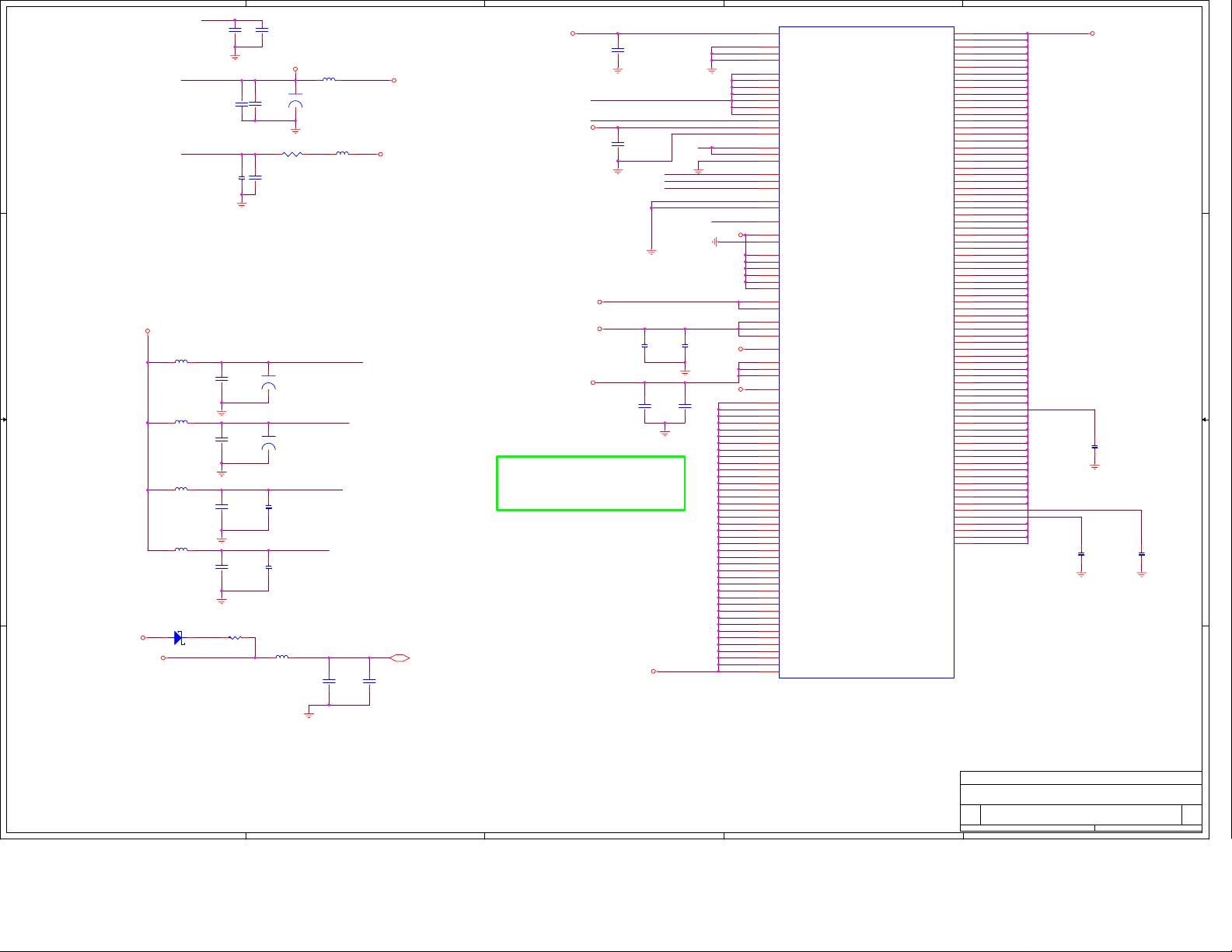

Page 2

IMVP-6

ISL 6262

Intel Yonah Processor

PCI EXPRESS X 16

533/667MHz

Block Diagram

FSB

CH7307

DVI-I

IDE Primary

SATA 3~4

USB Port 0~7

Azalia

ALC880

SDVO

CRT

UltraDMA

33/66/100

SATA

USB

AC97

300 MB/s

945GT

Calistoga

DMI

2GB/s

ICH7M-DH

TPM

2 DDR II

64bit DDR

400/533/667MHz

DIMM

Modules

Type III

Mini-PCI

PCI Slot x 1

PCI bus PCI BUS

IEEE-1394

VT6307

PCI-E x1

PCI-E x1

LPC Bus

33MHz@16.5MB/s

SATA 2

SIL 3132

SATA II

300 MB/s

LAN Intel

82573E

SATA II 1~2

LPC SIO

Winbond

83627EHG

Flash

Title

Size Document Number Rev

Custom

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

Block Diagram

MS-9631

237Monday, February 13, 2006

of

1.0

Page 3

5

4

3

2

1

HREQ#[0..4]

HREQ#[0..4]6

HA#[3..31]6

HASTB#[0..1]6

RS#[0..2]6

D D

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HASTB#0

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HA#17

HA#18

HA#19

HA#20

C C

H_A20M#12

H_FERR#12

H_IGNNE#12

H_STPCLK#12

H_INTR12

H_NMI12

ICH_H_SMI#12

B B

TP7

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HASTB#1

IN

OUT

IN

H_STPCLK#

IN

IN

IN

IN

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

BI

HA#[3..31]

BI

HASTB#[0..1]

BI

RS#[0..2]

IN

U9A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

RSVD[11]

Yonah_Skt_0

ADDR GROUP 0 ADDR GROUP 1

RESERVED

PLACE AT CPU END OF ROUTE

R218 X_56_0402

R150 56R_0402

R235 X_54.9R1%0402

DEFER#

CONTROL

RESET#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

XDP/ITP SIGNALS

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

THERM

BCLK[0]

BCLK[1]

H

CLK

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

ADS#

BNR#

BPRI#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

H_CPURST#

H_PROCHOT#

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

H_PWRGD

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR#0

H_IERR#

H_INIT#

H_LOCK#

RS#0

RS#1

RS#2

H_TRDY#

H_HIT#

H_HITM#

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#3

H_BPM#4

H_BPM#5

H_PROCHOT#

TRMTRIP#

CK_H_CPU

CK_H_CPU#

BI

BI

IN

IN

BI

BI

BI

IN

BI

IN

IN

BI

BI

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST#

BI

CPU_TMPA 16

BI

THERMDC 16

OUT

TRMTRIP# 7,12

IN

CK_H_CPU 15

IN

CK_H_CPU# 15

Yonah 478pin socket

(keyed)

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BR#0 6

H_INIT# 12

H_LOCK# 6

H_CPURST# 6

H_TRDY# 6

H_HIT# 6

H_HITM# 6

TP17

TP19

TP24

TP16

TP23

TP18

TP9

TP8

V_FSB_VTT

R154 56_0402

R211 54.9R1%0402

H_TMS

H_TDI

H_TCK

H_TRST#

H_IERR#

H_BPM#5

R205 54.9R1%0402

R238 54.9R1%0402

R214 54.9R1%0402

R220 54.9R1%0402

V_FSB_VTT

C137

0.1u_0603

R134

2K_1%_0603

V_FSB_VTT

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

V_FSB_VTT

R135

1K_1%_0603

Don't need CAP. (Design Guide P.90)

CPU_GTLREF

0.5" max

length

BSEL07,15

BSEL17,15

BSEL27,15

C139

4.7U10V_0805

HD#9

HD#11

HD#12 HD#44

HD#13

HD#14

HD#15

HDSTBN#0

HDSTBP#0

DBI#0 DBI#2

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HDSTBN#1

HDSTBP#1

DBI#1

1K_0603

R132

R131 51R

OUT

OUT

OUT

HD#[0..63]6

HDSTBP#[0..3]6

HDSTBN#[0..3]6

DBI#[0..3]6

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

H23

G22

J26

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

AD26

C26

D25

B22

B23

C21

BI

BI

BI

BI

U9B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

Yonah_Skt_0

HD#[0..63]

HDSTBP#[0..3]

HDSTBN#[0..3]

DBI#[0..3]

DATA GRP0 DATA GRP1

MISC

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP2DATA GRP3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42HD#10

HD#43

HD#45

HD#46

HD#47

HDSTBN#2

HDSTBP#2

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBN#3

HDSTBP#3

DBI#3

HCOMP0

HCOMP1

HCOMP2

HCOMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGD

H_SLP#

0.5" max length

25 MIL AWAY FROM HIGH

SPEED SIGNAL

HCOMP0,2==>18MIL(27.4ohm)

HCOMP1,3==>5MIL(55ohm)

R133 27.4_1%_0603

R136 54.9_1%_0402

R236 27.4_1%_0603

R237 54.9_1%_0402

IN

H_DPRSTP# 12,31

IN

H_DPSLP# 12

IN

H_DPWR# 6

IN

H_PWRGD 12

IN

H_SLP# 6

OUT

PSI# 31

BSEL[2] BSEL[1] BSEL[0] BC LK

LLL

LL

A A

L

L

5

H

HH

RESERVED

H

133MHZ

L

RESERVED

166MHZ

Title

Size Document Number Rev

Custom

4

3

2

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

Yonah - Host bus

MS-9631

1

1.0

of

337Monday, February 13, 2006

Page 4

5

U9D

A4

VSS1

A8

VSS2

A11

VSS3

A14

VSS4

A16

VSS5

A19

VSS6

A23

VSS7

A26

VSS8

B6

VSS9

D D

C C

B B

B11

B13

B16

B19

B21

B24

C11

C14

C16

C19

C22

C25

D11

D13

D16

D19

D23

D26

E11

E14

E16

E19

E21

E24

F11

F13

F16

F19

F22

F25

G23

G26

H21

H24

J22

J25

K23

K26

L21

L24

M22

M25

N23

N26

B8

C5

C8

C2

D1

D4

D8

E3

E6

E8

F5

F8

F2

G4

G1

H3

H6

J2

J5

K1

K4

L3

L6

M2

M5

N1

N4

P3

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

Yonah_Skt_0

GND

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

VCORE VCORE

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

4

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

U9C

VCC[1]

VCC[2]

VCC[3]

VCC[4]

VCC[5]

VCC[6]

VCC[7]

VCC[8]

VCC[9]

VCC[10]

VCC[11]

VCC[12]

VCC[13]

VCC[14]

VCC[15]

VCC[16]

VCC[17]

VCC[18]

VCC[19]

VCC[20]

VCC[21]

VCC[22]

VCC[23]

VCC[24]

VCC[25]

VCC[26]

VCC[27]

VCC[28]

VCC[29]

VCC[30]

VCC[31]

VCC[32]

VCC[33]

VCC[34]

VCC[35]

VCC[36]

VCC[37]

VCC[38]

VCC[39]

VCC[40]

VCC[41]

VCC[42]

VCC[43]

VCC[44]

VCC[45]

VCC[46]

VCC[47]

VCC[48]

VCC[49]

VCC[50]

VCC[51]

VCC[52]

VCC[53]

VCC[54]

VCC[55]

VCC[56]

VCC[57]

VCC[58]

VCC[59]

VCC[60]

VCC[61]

VCC[62]

VCC[63]

VCC[64]

VCC[65]

VCC[66]

VCC[67]

Yonah_Skt_0

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

POWER

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[1]

VCCP[2]

VCCP[3]

VCCP[4]

VCCP[5]

VCCP[6]

VCCP[7]

VCCP[8]

VCCP[9]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

Internal PLL super filter

B26

VID0

AD6

VID1

AF5

VID2

AE5

VID3

AF4

VID4

AE3

VID5

AF2

VID6

AE2

AF7

AE7

V_FSB_VTT

V_1P5_CORE

OUT

3

0.01uf and 10uf near B26

C145 10U10V_0805

VID[0..6] 31

C1460.01U25V_0402

VCORE

R190

100_1%_0402

R192

100_1%_0402

2

U9E

X1

H1

XX1

GND

XX2

GND

HEAT

XX3

GND

SINK

X2

H2

GND

XX5

GND

XX6

GND

XX7

GND

Yonah_Skt_0

OUT

VCCSENSE_2 31

OUT

VSSSENSE_2 31

LAYOUT NOTE:

Route VCCSENSE and VSSSENSE traces at

27.4Ohm(18mil) with 7 mil spacing.

Place PU and PD within 1 inch of CPU.

GND

GND

GND

GND

GND

GND

1

Modify X1,X2,X3,X4 to NC

X3

XX9

XX10

XX11

X4

XX13

XX14

XX15

2005.11.3

H3

H4

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

Yonah - Power / GND

Custom

MS-9631

1.0

of

437Monday, February 13, 2006

1

Page 5

5

4

3

2

1

VCORE

C223

D D

22UF/6.3V_0805

C231

22UF/6.3V_0805

C197

22UF/6.3V_0805

C600

22UF/6.3V_0805-BOT

C214

22UF/6.3V_0805

C606

22UF/6.3V_0805-BOT

C219

22UF/6.3V_0805

C190

22UF/6.3V_0805

C601

22UF/6.3V_0805-BOT

C597

22UF/6.3V_0805-BOT

C193

22UF/6.3V_0805

VCORE

C607

C206

22UF/6.3V_0805

22UF/6.3V_0805-BOT

C182

22UF/6.3V_0805

C218

22UF/6.3V_0805

V_FSB_VTT

C C

C609

C595

C610

0.1u_0603-BOT

0.1u_0603-BOT

C176

C596

0.1u_0402

0.1u_0603-BOT

0.1u_0603-BOT

C604

C605

22UF/6.3V_0805-BOT

22UF/6.3V_0805-BOT

close to cpu socket

C608

C593

0.1u_0603-BOT

0.1u_0603-BOT

C212

C594

22UF/6.3V_0805

0.1u_0603-BOT

C598

C179

C599

22UF/6.3V_0805-BOT

C236

0.1u_0402

22UF/6.3V_0805-BOT

0.1u_0402

C191

22UF/6.3V_0805

C201

+

X_100U/2V

C603

C194

22UF/6.3V_0805

C181

22UF/6.3V_0805

C232

22UF/6.3V_0805

C207

22UF/6.3V_0805

C224

22UF/6.3V_0805

C198

22UF/6.3V_0805

C237

22UF/6.3V_0805

C227

22UF/6.3V_0805

C175

22UF/6.3V_0805

C168

22UF/6.3V_0805

22UF/6.3V_0805-BOT

V_FSB_VTT

C233

C178

C235

C234

0.1u_0402

B B

0.1u_0402

0.1u_0402

C177

0.1u_0402

0.1u_0402

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

Yonah- Decoupling

Custom

MS-9631

1.0

of

537Monday, February 13, 2006

1

Page 6

5

4

3

2

1

HD#[0..63]3

D D

HYSWING

C238

0.1u_0402

0.5" max

length

V_FSB_VTT

R206

54.9_1%_0402

HYRCOMP

R183

24.9R1%_0402

V_FSB_VTT

R188

54.9_1%_0402

HXSCOMP

HYSCOMP

HXRCOMP

R200

24.9R1%_0402

V_FSB_VTT

C C

100_1%_0402

B B

R208

R187

221_1%_0402

R186

100_1%_0402

R209

221_1%_0402

HXSWING

0.1u_0402

V_FSB_VTT

C254

BI

IN

CK_H_MCH15

IN

CK_H_MCH#15

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

CK_H_MCH

CK_H_MCH#

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

AA10

AB11

AC11

AD10

W11

AG2

AG1

K11

T10

U11

T11

W9

W7

W6

AB7

AA9

W4

W3

W5

Y10

AB8

W2

AA4

AA7

AA2

AA6

AA1

AB4

AC9

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD4

AC8

W1

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

G4

T3

U7

U9

T1

T8

T4

U5

T9

T5

Y3

Y7

Y8

E1

E2

E4

Y1

U1

U11A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

945GT

H9

H_A#_3

C9

H_A#_4

E11

H_A#_5

G11

H_A#_6

F11

H_A#_7

G12

H_A#_8

F9

H_A#_9

H11

H_A#_10

J12

H_A#_11

G14

H_A#_12

D9

H_A#_13

J14

H_A#_14

H13

H_A#_15

J15

H_A#_16

F14

H_A#_17

D12

H_A#_18

A11

H_A#_19

C11

H_A#_20

A12

H_A#_21

A13

H_A#_22

E13

H_A#_23

G13

H_A#_24

F12

H_A#_25

B12

H_A#_26

B14

H_A#_27

C12

H_A#_28

A14

H_A#_29

C14

H_A#_30

D14

H_A#_31

E8

H_ADS#

B9

H_ADSTB#_0

C13

H_ADSTB#_1

J13

H_AVREF

C6

H_BNR#

F6

H_BPRI#

C7

H_BREQ#0

B7

H_CPURST#

A7

H_DBSY#

C3

H_DEFER#

J9

H_DPWR#

H8

H_DRDY#

H_DVREF

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_CPUSLP#

H_TRDY#

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

HOST

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

H_ADS#

HASTB#0

HASTB#1

H_BNR#

H_BPRI#

H_BR#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

DBI#0

DBI#1

DBI#2

DBI#3

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

H_HIT#

H_HITM#

H_LOCK#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

RS#0

RS#1

RS#2

HCPUSLP#_GMCH

H_TRDY#

BI

BI

BI

BI

H_BNR# 3

OUT

H_BPRI# 3

BI

H_BR#0 3

OUT

H_CPURST# 3

BI

H_DBSY# 3

OUT

H_DEFER# 3

OUT

H_DPWR# 3

BI

H_DRDY# 3

BI

BI

IN

OUT

R217 0R_0603

HA#[3..31] 3

H_ADS# 3

HASTB#[0..1] 3

BI

BI

HDSTBN#[0..3] 3

BI

HDSTBP#[0..3] 3

H_HIT# 3

H_HITM# 3

H_LOCK# 3

BI

HREQ#[0..4] 3

RS#[0..2] 3

DBI#[0..3] 3

OUT

OUT

C268

0.1u_0402

Place C275 to bottom side.

2006.1.18

H_SLP# 3

H_TRDY# 3

as close as to

GMCH J13 pin

HVREF

C275

0.1u_0603-BOT

V_FSB_VTT

R247

100_1%_0402

R244

200_1%_0402

No MSI PN

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

GMCH1- Host

Custom

MS-9631

1.0

of

637Monday, February 13, 2006

1

Page 7

A

U11B

T32

RSVD_1

R32

RSVD_2

F3

RSVD_3

F7

RSVD_4

AG11

RSVD_5

AF11

RSVD_6

H7

RSVD_7

J19

AH33

AH34

BA41

BA40

BA39

AY41

AW41

AW1

A41

A35

A34

D28

D27

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

J25

K27

J26

G28

F25

H26

G6

H28

H27

K28

H32

D1

C41

C1

BA3

BA2

BA1

B41

B2

AY1

A40

A4

A39

A3

RSVD_8

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

ICH_SYNC#

CLK_REQ#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

945GT

4 4

TP27

TP21

TP29

TP22

TP26

OUT

OUT

OUT

IN

IN

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

BM_BUSY#

PM_EXTTS#0

PM_EXTTS#1

BI

BI

BI

R253 10KR0402

OUT

BSEL03,15

R252 10KR0402

OUT

BSEL13,15

R251 10KR0402

OUT

BSEL23,15

3 3

2 2

TP25

TP28

TP20

TP30

CFG2023

BM_BUSY#13

TRMTRIP#3,12

PWRGD13,28

DEV_RST#15,16,22,28

SDVO_CTRL_CLK23,27

SDVO_CTRL_DATA23,27

MCH_ICH_SYNC#12

RSVD CFG

SM_OCDCOMP_0

SM_OCDCOMP_1

DDR MUXING

PM

D_REFSSCLKIN#

D_REFSSCLKIN

MISC

NC

DMI CLK

DPRSLPVR13,31

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

D_REFCLKIN#

D_REFCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

G_CLKIN

B

AY35

P_DDR1_A1

AR1

AW7

P_DDR1_B1

AW40

AW35

N_DDR1_A1

AT1

AY7

N_DDR1_B1

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

AL20

AF10

BA13

BA12

AY20

AU21

M_RCOMPN

AV9

M_RCOMPP

AT9

945GMDDR_VREF

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

OUT

P_DDR0_A 20

OUT

P_DDR0_B 20

OUT

N_DDR0_A 20

OUT

N_DDR0_B 20

OUT

SCKE_A0 20,21

OUT

SCKE_A1 20,21

OUT

SCKE_B0 20,21

OUT

SCKE_B1 20,21

OUT

SCS_A#0 20,21

OUT

SCS_A#1 20,21

OUT

SCS_B#0 20,21

OUT

SCS_B#1 20,21

TP14

TP15

OUT

ODT_A0 20,21

OUT

ODT_A1 20,21

OUT

ODT_B0 20,21

OUT

ODT_B1 20,21

IN

CK_PE_100M_MCH# 15

IN

CK_PE_100M_MCH 15

IN

CK_96M_DREF# 15

IN

CK_96M_DREF 15

0R_0402R223

0R_0402R222

IN

DMIRXN0 13

IN

DMIRXN1 13

IN

DMIRXN2 13

IN

DMIRXN3 13

IN

DMIRXP0 13

IN

DMIRXP1 13

IN

DMIRXP2 13

IN

DMIRXP3 13

OUT

DMITXN0 13

OUT

DMITXN1 13

OUT

DMITXN2 13

OUT

DMITXN3 13

OUT

DMITXP0 13

OUT

DMITXP1 13

OUT

DMITXP2 13

OUT

DMITXP3 13

PM_EXTTS#1

0R_0402R227

80.6R1%_0603R127

80.6R1%_0603R128

V_1P5_CORE

R158 10R0402

R157 10R0402

R140 10R0402

R129 10R0402

R155 10R0402

R156 10R0402

R141 10R0402

R130 10R0402

VCC_DDR2

R162 1KR1%_0603

VCC_DDR2

Without LVDS

PM_EXTTS#0

R246 10K_0402

PM_EXTTS#1

R228 10K_0402

C

OUT

P_DDR1_A 20

OUT

P_DDR2_A 20

OUT

P_DDR1_B 20

OUT

P_DDR2_B 20

OUT

N_DDR1_A 20

OUT

N_DDR2_A 20

OUT

N_DDR1_B 20

OUT

N_DDR2_B 20

945GMDDR_VREF

C171

R161

VCC3

BI

BI

OUT

OUT

0.1u_0603

OUT

OUT

OUT

MCH_DDC_CLK

MCH_DDC_DATA

1KR1%_0603

VGA_BLUE26

VGA_GREEN26

VGA_RED26

MCH_DDC_CLK26

MCH_DDC_DATA26

HSYNC26

VSYNC26

TP31

R489

1.5KR0402

R224

100KR0402

C169

0.1u_0603

V_1P5_CORE

VGA_BLUE

VGA_GREEN

VGA_RED

R232 39R_0402

R488 255R1%_0603-BOT

R233 39R_0402

D32

J30

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

J20

B16

B18

B19

K30

J29

E23

D23

C22

B22

A21

B21

C26

C25

G23

J22

H23

U11C

L_BKLTCTL

L_BKLTEN

L_CTLACLK

L_CTLB_DATA

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

TV_DCONSEL0

TV_DCONSEL1

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

945GT

D

SDVO_TVCLKIN# / EXP_A_RXN_0

SDVO_INT# / EXP_A_RXN_1

SDVO_FLDSTALL# / EXP_A_RXN_2

LVDS TV VGA

SDVO_TVCLKIN / EXP_A_RXP_0

SDVO_INT / EXP_A_RXP_1

SDVO_FLDSTALL / EXP_A_RXP_2

SDVOB_RED# / EXP_A_TXN_0

SDVOB_GREEN# / EXP_A_TXN_1

SDVOB_BLUE# / EXP_A_TXN_2

SDVOC_RED# / SDVOB_ALPHA# / EXP_A_TXN_4

SDVOB_CLKN / EXP_A_TXN_3

SDVOC_GREEN# / EXP_A_TXN_5

SDVOC_BLUE# / EXP_A_TXN_6

SDVOC_CLKN / EXP_A_TXN_7

PCI-EXPRESS GRAPHICS

SDVOB_RED / EXP_A_TXP_0

SDVOB_GREEN / EXP_A_TXP_1

SDVOB_BLUE / EXP_A_TXP_2

SDVOB_CLKP / EXP_A_TXP_3

SDVOC_RED / SDVOB_ALPHA / EXP_A_TXP_4

SDVOC_GREEN / EXP_A_TXP_5

SDVOC_BLUE / EXP_A_TXP_6

SDVOC_CLKP / EXP_A_TXP_7

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

GRCOMP

D40

D38

EXP_A_RXN_0

F34

EXP_A_RXN_1

G38

EXP_A_RXN_2

H34

EXP_A_RXN_3

J38

EXP_A_RXN_4

L34

EXP_A_RXN_5

M38

EXP_A_RXN_6

N34

EXP_A_RXN_7

P38

EXP_A_RXN_8

R34

EXP_A_RXN_9

T38

EXP_A_RXN_10

V34

EXP_A_RXN_11

W38

EXP_A_RXN_12

Y34

EXP_A_RXN_13

AA38

EXP_A_RXN_14

AB34

EXP_A_RXN_15

AC38

EXP_A_RXP_0

D34

EXP_A_RXP_1

F38

EXP_A_RXP_2

G34

EXP_A_RXP_3

H38

EXP_A_RXP_4

J34

EXP_A_RXP_5

L38

EXP_A_RXP_6

M34

EXP_A_RXP_7

N38

EXP_A_RXP_8

P34

EXP_A_RXP_9

R38

EXP_A_RXP_10

T34

EXP_A_RXP_11

V38

EXP_A_RXP_12

W34

EXP_A_RXP_13

Y38

EXP_A_RXP_14

AA34

EXP_A_RXP_15

AB38

EXP_A_TXN_0

F36

EXP_A_TXN_1

G40

EXP_A_TXN_2

H36

EXP_A_TXN_3

J40

EXP_A_TXN_4

L36

EXP_A_TXN_5

M40

EXP_A_TXN_6

N36

EXP_A_TXN_7

P40

EXP_A_TXN_8

R36

EXP_A_TXN_9

T40

EXP_A_TXN_10

V36

EXP_A_TXN_11

W40

EXP_A_TXN_12

Y36

EXP_A_TXN_13

AA40

EXP_A_TXN_14

AB36

EXP_A_TXN_15

AC40

EXP_A_TXP_0

D36

EXP_A_TXP_1

F40

EXP_A_TXP_2

G36

EXP_A_TXP_3

H40

EXP_A_TXP_4

J36

EXP_A_TXP_5

L40

EXP_A_TXP_6

M36

EXP_A_TXP_7

N40

EXP_A_TXP_8

P36

EXP_A_TXP_9

R40

EXP_A_TXP_10

T36

EXP_A_TXP_11

V40

EXP_A_TXP_12

W36

EXP_A_TXP_13

Y40

EXP_A_TXP_14

AA36

EXP_A_TXP_15

AB40

E

R234 24.9R1%_0603

IN

IN

OUT

OUT

VCC3G_PCIE

EXP_A_RXN_[0..15] 23,27

EXP_A_RXP_[0..15] 23,27

EXP_A_TXN_[0..15] 23,27

EXP_A_TXP_[0..15] 23,27

NB strapping

R239

CFG5 CFG19

X_2.2K_0402

HIGH

CFG5 DMI Width

LOW=DMI x 2

1 1

HIGH=DMI x 4

CFG7 CPU STRAP

LOW=REVERSED

HIGH=MOBILE CPU

A

CFG[3:17] Internal Pull up CFG[18:20] Internal Pull down

CFG7

R242 2.2K_0402

TP1

CFG10

R241 X_2.2K_0402

LOWHIGH

CFG9 PCIE

Graphics

LOW=REVERSE LAN

HIGH=NORMAL

CFG10 HOST PLL

VCO SELECT

LOW=REVERSED

HIGH=MOBILITY

B

R250 X_2.2K_0402

CFG11 PSB 4X

CLK ENABLE

LOW=4X ENABLE

HIGH=8X

CFG16CFG9 CFG11

R240 X_2.2K_0402

HIGHLOW

CFG16 FSB Dynamic

ODT LOW=Dynamic ODT

Disabled

HIGH=Dynamic ODT

Enabled

C

CFG18

R231 2.2K_0402

HIGH

CFG18 VCC Select

LOW=1.05V

HIGH=1.5V

R229 X_2.2K_0402

LOWHIGH

CFG19 DMI LANE

REVERSAL LOW=Normal

HIGH=LANES REVRSED

D

VCC3VCC3VCC3

CFG20

R230 X_2.2K_0402

LOW

CFG20 SDVO/PCIe concurrent

LOW=Only SDVO or PCIE x 1 is

operational

HIGH=SDVO and PCIE x 1 are

operating simultaneously via

the PEG port

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

GMCH2-PCIE/DMI/CRT

Custom

MS-9631

of

737Monday, February 13, 2006

E

1.0

Page 8

A

4 4

B

C

D

E

DATA_A[63:0]20

3 3

2 2

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AW2

U11D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

AK9

SA_DQ40

AN7

SA_DQ41

AK8

SA_DQ42

AK7

SA_DQ43

AP9

SA_DQ44

AN9

SA_DQ45

AT5

SA_DQ46

AL5

SA_DQ47

AY2

SA_DQ48

SA_DQ49

AP1

SA_DQ50

AN2

SA_DQ51

AV2

SA_DQ52

AT3

SA_DQ53

AN1

SA_DQ54

AL2

SA_DQ55

AG7

SA_DQ56

AF9

SA_DQ57

AG4

SA_DQ58

AF6

SA_DQ59

AG9

SA_DQ60

AH6

SA_DQ61

AF4

SA_DQ62

AF8

SA_DQ63

945GT

DDR SYSTEM MEMORY A

SA_RCVEMIN#

SA_RCVENOUT#

SA_BS_0

SA_BS_1

SA_BS_2

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_CAS#

SA_RAS#

SA_WE#

AU12

AV14

BA20

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AY13

AW14

AK23

AK24

AY14

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

SBS_A0 20,21

SBS_A1 20,21

SBS_A2 20,21

DQS_A#0 20

DQS_A#1 20

DQS_A#2 20

DQS_A#3 20

DQS_A#4 20

DQS_A#5 20

DQS_A#6 20

DQS_A#7 20

TP11

TP13

DQM_A0 20

DQM_A1 20

DQM_A2 20

DQM_A3 20

DQM_A4 20

DQM_A5 20

DQM_A6 20

DQM_A7 20

DQS_A0 20

DQS_A1 20

DQS_A2 20

DQS_A3 20

DQS_A4 20

DQS_A5 20

DQS_A6 20

DQS_A7 20

MAA_A[0..13] 20,21

CAS_A# 20,21

RAS_A# 20,21

WE_A# 20,21

DATA_B[63:0]20

DATA_B0

DATA_B1

DATA_B2

DATA_B3

DATA_B4

DATA_B5

DATA_B6

DATA_B7

DATA_B8

DATA_B9

DATA_B10

DATA_B11

DATA_B12

DATA_B13

DATA_B14

DATA_B15

DATA_B16

DATA_B17

DATA_B18

DATA_B19

DATA_B20

DATA_B21

DATA_B22

DATA_B23

DATA_B24

DATA_B25

DATA_B26

DATA_B27

DATA_B28

DATA_B29

DATA_B30

DATA_B31

DATA_B32

DATA_B33

DATA_B34

DATA_B35

DATA_B36

DATA_B37

DATA_B38

DATA_B39

DATA_B40

DATA_B41

DATA_B42

DATA_B43

DATA_B44

DATA_B45

DATA_B46

DATA_B47

DATA_B48

DATA_B49

DATA_B50

DATA_B51

DATA_B52

DATA_B53

DATA_B54

DATA_B55

DATA_B56

DATA_B57

DATA_B58

DATA_B59

DATA_B60

DATA_B61

DATA_B62

DATA_B63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

AW4

AY10

AW5

U11E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

AJ9

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

AJ8

SB_DQ47

SB_DQ48

SB_DQ49

BA4

SB_DQ50

SB_DQ51

SB_DQ52

AY9

SB_DQ53

SB_DQ54

AY5

SB_DQ55

AV4

SB_DQ56

AR5

SB_DQ57

AK4

SB_DQ58

AK3

SB_DQ59

AT4

SB_DQ60

AK5

SB_DQ61

AJ5

SB_DQ62

AJ3

SB_DQ63

945GT

DDR SYSTEM MEMORY B

SB_RCVENIN#

SB_RCVENOUT#

SB_BS_0

SB_BS_1

SB_BS_2

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_CAS#

SB_RAS#

SB_WE#

AT24

AV23

AY28

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AR24

AU23

AK16

AK18

AR27

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5MAA_A6

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

TP12

TP10

SBS_B0 20,21

SBS_B1 20,21

SBS_B2 20,21

DQS_B0 20

DQS_B1 20

DQS_B2 20

DQS_B3 20

DQS_B4 20

DQS_B5 20

DQS_B6 20

DQS_B7 20

DQS_B#0 20

DQS_B#1 20

DQS_B#2 20

DQS_B#3 20

DQS_B#4 20

DQS_B#5 20

DQS_B#6 20

DQS_B#7 20

MAA_B[0..13] 20,21

CAS_B# 20,21

RAS_B# 20,21

WE_B# 20,21

DQM_B0 20

DQM_B1 20

DQM_B2 20

DQM_B3 20

DQM_B4 20

DQM_B5 20

DQM_B6 20

DQM_B7 20

1 1

Title

Size Document Number Rev

A

B

C

D

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

GMCH3-MEM

Custom

MS-9631

1.0

of

837Monday, February 13, 2006

E

Page 9

5

AA33

AA32

AA31

AA30

AA29

AB28

AA28

AB23

AA23

AC22

AB22

AC21

AA21

AC20

AB20

AB19

AA19

EC30

1000u_6.3V

V_1P5_CORE

+

12

1000u_6.3V

EC29

+

12

C281

10UF/10V_0805

5500mA

0.22UF/10V

D D

C C

B B

A A

5

4

U11F

VCC_0

W33

VCC_1

P33

VCC_2

N33

VCC_3

L33

VCC_4

J33

VCC_5

VCC_6

Y32

VCC_7

W32

VCC_8

V32

VCC_9

P32

VCC_10

N32

VCC_11

M32

VCC_12

L32

VCC_13

J32

VCC_14

VCC_15

W31

VCC_16

V31

VCC_17

T31

VCC_18

R31

VCC_19

P31

VCC_20

N31

VCC_21

M31

VCC_22

VCC_23

Y30

VCC_24

W30

VCC_25

V30

VCC_26

U30

VCC_27

T30

VCC_28

R30

VCC_29

P30

VCC_30

N30

VCC_31

M30

VCC_32

L30

VCC_33

VCC_34

Y29

VCC_35

W29

VCC_36

V29

VCC_37

U29

VCC_38

R29

VCC_39

P29

VCC_40

M29

VCC_41

L29

VCC_42

VCC_43

VCC_44

Y28

VCC_45

V28

VCC_46

U28

VCC_47

T28

VCC_48

R28

VCC_49

P28

VCC_50

N28

VCC_51

M28

VCC_52

L28

VCC_53

P27

VCC_54

N27

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC

VCC_SM_100

VCC_SM_101

VCC_SM_102

VCC_SM_103

VCC_SM_104

VCC_SM_105

VCC_SM_106

VCC_SM_107

M27

L27

P26

N26

L26

N25

M25

L25

P24

N24

M24

Y23

P23

N23

M23

L23

Y22

W22

P22

N22

M22

L22

W21

N21

M21

L21

Y20

W20

P20

N20

M20

L20

Y19

N19

M19

L19

N18

M18

L18

P17

N17

M17

N16

M16

L16

945GT

VCC_SM_0

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_SM_37

VCC_SM_38

VCC_SM_39

VCC_SM_40

VCC_SM_41

VCC_SM_42

VCC_SM_43

VCC_SM_44

VCC_SM_45

VCC_SM_46

VCC_SM_47

VCC_SM_48

VCC_SM_49

VCC_SM_50

VCC_SM_51

VCC_SM_52

VCC_SM_53

VCC_SM_54

VCC_SM_55

VCC_SM_56

VCC_SM_57

VCC_SM_58

VCC_SM_59

VCC_SM_60

VCC_SM_61

VCC_SM_62

VCC_SM_63

VCC_SM_64

VCC_SM_65

VCC_SM_66

VCC_SM_67

VCC_SM_68

VCC_SM_69

VCC_SM_70

VCC_SM_71

VCC_SM_72

VCC_SM_73

VCC_SM_74

VCC_SM_75

VCC_SM_76

VCC_SM_77

VCC_SM_78

VCC_SM_79

VCC_SM_80

VCC_SM_81

VCC_SM_82

VCC_SM_83

VCC_SM_84

VCC_SM_85

VCC_SM_86

VCC_SM_87

VCC_SM_88

VCC_SM_89

VCC_SM_90

VCC_SM_91

VCC_SM_92

VCC_SM_93

VCC_SM_94

VCC_SM_95

VCC_SM_96

VCC_SM_97

VCC_SM_98

VCC_SM_99

AU41

AT41

AM41

AU40

BA34

AY34

AW34

AV34

AU34

AT34

AR34

BA30

AY30

AW30

AV30

AU30

AT30

AR30

AP30

AN30

AM30

AM29

AL29

AK29

AJ29

AH29

AJ28

AH28

AJ27

AH27

BA26

AY26

AW26

AV26

AU26

AT26

AR26

AJ26

AH26

AJ25

AH25

AJ24

AH24

BA23

AJ23

BA22

AY22

AW22

AV22

AU22

AT22

AR22

AP22

AK22

AJ22

AK21

AK20

BA19

AY19

AW19

AV19

AU19

AT19

AR19

AP19

AK19

AJ19

AJ18

AJ17

AH17

AJ16

AH16

BA15

AY15

AW15

AV15

AU15

AT15

AR15

AJ15

AJ14

AJ13

AH13

AK12

AJ12

AH12

AG12

AK11

BA8

AY8

AW8

AV8

AT8

AR8

AP8

BA6

AY6

AW6

AV6

AT6

AR6

AP6

AN6

AL6

AK6

AJ6

AV1

AJ1

C162

0.47UFC277

Remove C777 & C778 ->

VCC_DDR2 to GND -1025

C140

0.47UF

C186

0.47UF

4

C150

0.47UF

C143

0.47UF

3

C158

0.47UF

C142

10UF/10V_0805

Place close to GMCH

3

VCC_DDR2

V_1P5_CORE

C141

10UF/10V_0805

AD27

AC27

AB27

AA27

W27

AD26

AC26

AB26

AA26

W26

AD25

AC25

AB25

AA25

W25

AD24

AC24

AB24

AA24

W24

AD23

AD22

AD21

AD20

AD19

AD18

AC18

AB18

AA18

W18

U27

T27

R27

Y26

V26

U26

T26

R26

Y25

V25

U25

T25

R25

Y24

V24

U24

T24

R24

V23

U23

T23

R23

V22

U22

T22

R22

V21

U21

T21

R21

V20

U20

T20

R20

V19

U19

T19

Y18

V18

U18

T18

2

Y27

V27

2

U11G

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

945GT

NCTF

1

VSS_NCTF

AE27

VSS_NCTF0

AE26

VSS_NCTF1

AE25

VSS_NCTF2

AE24

VSS_NCTF3

AE23

VSS_NCTF4

AE22

VSS_NCTF5

AE21

VSS_NCTF6

AE20

VSS_NCTF7

AE19

VSS_NCTF8

AE18

VSS_NCTF9

AC17

VSS_NCTF10

Y17

VSS_NCTF11

U17

VSS_NCTF12

VCCAUX_NCTF0

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VCCAUX_NCTF39

VCCAUX_NCTF40

VCCAUX_NCTF41

VCCAUX_NCTF42

VCCAUX_NCTF43

VCCAUX_NCTF44

VCCAUX_NCTF45

VCCAUX_NCTF46

VCCAUX_NCTF47

VCCAUX_NCTF48

VCCAUX_NCTF49

VCCAUX_NCTF50

VCCAUX_NCTF51

VCCAUX_NCTF52

VCCAUX_NCTF53

VCCAUX_NCTF54

VCCAUX_NCTF55

VCCAUX_NCTF56

VCCAUX_NCTF57

Title

GMCH-POWER1

Size Document Number Rev

Custom

Date: Sheet of

VCCAUX_NCTF

AG27

AF27

AG26

AF26

AG25

AF25

AG24

AF24

AG23

AF23

AG22

AF22

AG21

AF21

AG20

AF20

AG19

AF19

R19

AG18

AF18

R18

AG17

AF17

AE17

AD17

AB17

AA17

W17

V17

T17

R17

AG16

AF16

AE16

AD16

AC16

AB16

AA16

Y16

W16

V16

U16

T16

R16

AG15

AF15

AE15

AD15

AC15

AB15

AA15

Y15

W15

V15

U15

T15

R15

MS-9631 1.0

V_1P5_CORE

937Monday, February 13, 2006

1

Page 10

A

4 4

3 3

2 2

V_1P5_CORE

V_FSB_VTT

V_2P5_MCH

VCC3G_PCIE

C189

0.1u_0402

VCC3G_PCIE

C188

10U10V_0805

VCCA_3GPLL

C602

0.1u_0603-BOT

L19 10U100mA_0805

C287

0.1u_0402

L17 10U100mA_0805

C272

0.1u_0402

L15 120L500m_350_0402

C215

0.1u_0402

L14 120L500m_350_0402

C204

0.1u_0402

D12

A C

RAS40WS

R261 10R_0603

C195

0.1u_0402

VCC3G_PCIE

C180

10U10V_0805

R176

1_1%_0603

C199

10U10V_0805

12

EC31

470u2.5V_POS

12

EC28

470u2.5V_POS

C216

22UF/6.3V_0805

VCCA_MPLL

C202

22UF/6.3V_0805

L18

180L1500m_90_0603

L12 91N1.5_1210-LF

12

EC14

220u_POS

L13 1U25m_0603

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_CRTDAC

C276

0.1u_0402

B

V_1P5_CORE

C274

0.022U16V_0402

V_1P5_CORE

BI

VCCA_CRTDAC 26

C

V_2P5_MCH

C273

0.1u_0402

VCC3G_PCIE

VCCA_3GPLL

V_2P5_MCH

C264

0.1u_0402

V_1P5_CORE

V_1P5_CORE

VCC3

Modify TV Disable Circuit.

All TV power signals connect to 1.5V.

945GM Design Guide page 188.

2005.11.3

V_1P5_CORE

C269

0.1u_0402

C270

0.1u_0402

VCCA_DPLLB

VCCA_HPLL

V_1P5_CORE

C611

V_1P5_CORE

10U10V_0805-BOT

V_1P5_CORE

C612

10U10V_0805-BOT

70mA

VCCA_CRTDAC

VCCA_DPLLA

VCCA_MPLL

AJ41

AB41

AC33

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

AH15

AH14

AG14

AF14

AE14

AF13

AE13

AF12

AE12

AD12

H22

C30

B30

A30

Y41

V41

R41

N41

L41

G41

H41

F21

E21

G21

B26

C39

AF1

A38

B39

AF2

H20

G20

E19

F19

C20

D20

E20

F20

AH1

AH2

A28

B28

C28

D21

A23

B23

B25

H19

P19

P16

P15

Y14

U11H

VCCSYNC

VCC_TXLVDS0

VCC_TXLVDS1

VCC_TXLVDS2

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_LVDS

VSSA_LVDS

VCCA_MPLL

VCCA_TVBG

VSSA_TVBG

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_HMPLL0

VCCD_HMPLL1

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCD_TVDAC

VCC_HV0

VCC_HV1

VCC_HV2

VCC_QTVDAC

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VCCAUX29

VCCAUX30

VCCAUX31

VCCAUX32

VCCAUX33

VCCAUX34

VCCAUX35

VCCAUX36

VCCAUX37

VCCAUX38

VCCAUX39

VCCAUX40

945GT

D

POWER

VTT_0

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_30

VTT_31

VTT_32

VTT_33

VTT_34

VTT_35

VTT_36

VTT_37

VTT_38

VTT_39

VTT_40

VTT_41

VTT_42

VTT_43

VTT_44

VTT_45

VTT_46

VTT_47

VTT_48

VTT_49

VTT_50

VTT_51

VTT_52

VTT_53

VTT_54

VTT_55

VTT_56

VTT_57

VTT_58

VTT_59

VTT_60

VTT_61

VTT_62

VTT_63

VTT_64

VTT_65

VTT_66

VTT_67

VTT_68

VTT_69

VTT_70

VTT_71

VTT_72

VTT_73

VTT_74

VTT_75

VTT_76

AC14

AB14

W14

V14

T14

R14

P14

N14

M14

L14

AD13

AC13

AB13

AA13

Y13

W13

V13

U13

T13

R13

N13

M13

L13

AB12

AA12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

L12

R11

P11

N11

M11

R10

P10

N10

M10

P9

N9

M9

R8

P8

N8

M8

P7

N7

M7

R6

P6

M6

A6

R5

P5

N5

M5

P4

N4

M4

R3

P3

N3

M3

R2

P2

M2

D2

AB1

R1

P1

N1

M1

E

C222

0.47UF

V_FSB_VTT

C271

0.47UF

C261

0.22UF/10V

1 1

Title

Size Document Number Rev

A

B

C

D

Date: Sheet

MICRO-STAR INt'L CO. , LTD.

GMCH4 - Power 2

Custom

MS-9631

1.0

of

10 37Monday, February 13, 2006

E

Page 11

A

B

C

D

E

U11I

AC41

VSS_0

AA41

VSS_1

W41

VSS_2

T41

VSS_3

P41

VSS_4

M41

VSS_5

J41

VSS_6

4 4

3 3

2 2

1 1

AV40

AP40

AN40

AK40

AJ40

AH40

AG40

AF40

AE40

AY39

AW39

AV39

AR39

AN39

AJ39

AC39

AB39

AA39

AT38

AM38

AH38

AG38

AF38

AE38

AK37

AH37

AB37

AA37

AY36

AW36

AN36

AH36

AG36

AF36

AE36

AC36

BA35

AV35

AR35

AH35

AB35

AA35

AN34

F41

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

B40

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

Y39

VSS_27

W39

VSS_28

V39

VSS_29

T39

VSS_30

R39

VSS_31

P39

VSS_32

N39

VSS_33

M39

VSS_34

L39

VSS_35

J39

VSS_36

H39

VSS_37

G39

VSS_38

F39

VSS_39

D39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

C38

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

Y37

VSS_52

W37

VSS_53

V37

VSS_54

T37

VSS_55

R37

VSS_56

P37

VSS_57

N37

VSS_58

M37

VSS_59

L37

VSS_60

J37

VSS_61

H37

VSS_62

G37

VSS_63

F37

VSS_64

D37

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

C36

VSS_74

B36

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

Y35

VSS_82

W35

VSS_83

V35

VSS_84

T35

VSS_85

R35

VSS_86

P35

VSS_87

N35

VSS_88

M35

VSS_89

L35

VSS_90

J35

VSS_91

H35

VSS_92

G35

VSS_93

F35

VSS_94

D35

VSS_95

VSS_96

945GT

VSS

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

AK34

AG34

AF34

AE34

AC34

C34

AW33

AV33

AR33

AE33

AB33

Y33

V33

T33

R33

M33

H33

G33

F33

D33

B33

AH32

AG32

AF32

AE32

AC32

AB32

G32

B32

AY31

AV31

AN31

AJ31

AG31

AB31

Y31

AB30

E30

AT29

AN29

AB29

T29

N29

K29

G29

E29

C29

B29

A29

BA28

AW28

AU28

AP28

AM28

AD28

AC28

W28

J28

E28

AP27

AM27

AK27

J27

G27

F27

C27

B27

AN26

M26

K26

F26

D26

AK25

P25

K25

H25

E25

D25

A25

BA24

AU24

AL24

AW23

AT23

AN23

AM23

AH23

AC23

W23

AA22

BA21

AV21

AR21

AN21

AL21

AB21

AW20

AR20

AM20

AA20

AN19

AC19

W19

AH18

AY17

AR17

AP17

AM17

AK17

AV16

AN16

AL16

AN15

AM15

AK15

M15

BA14

AT14

AK14

AD14

AA14

AV13

AR13

AN13

AM13

AL13

AG13

AY12

AC12

AD11

AA11

AV10

U11J

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

K23

VSS_186

J23

VSS_187

F23

VSS_188

C23

VSS_189

VSS_190

K22

VSS_191

G22

VSS_192

F22

VSS_193

E22

VSS_194

D22

VSS_195

A22

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

Y21

VSS_203

P21

VSS_204

K21

VSS_205

J21

VSS_206

H21

VSS_207

C21

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

K20

VSS_213

B20

VSS_214

A20

VSS_215

VSS_216

VSS_217

VSS_218

K19

VSS_219

G19

VSS_220

C19

VSS_221

VSS_222

P18

VSS_223

H18

VSS_224

D18

VSS_225

A18

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

J16

VSS_235

F16

VSS_236

C16

VSS_237

VSS_238

VSS_239

VSS_240

N15

VSS_241

VSS_242

L15

VSS_243

B15

VSS_244

A15

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

U14

VSS_251

K14

VSS_252

H14

VSS_253

E14

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

P13

VSS_261

F13

VSS_262

D13

VSS_263

B13

VSS_264

VSS_265

VSS_266

K12

VSS_267

H12

VSS_268

E12

VSS_269

VSS_270

VSS_271

Y11

VSS_272

J11

VSS_273

D11

VSS_274

B11

VSS_275

VSS_276

945GT

VSS

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

AP10

AL10

AJ10

AG10

AC10

W10

U10

BA9

AW9

AR9

AH9

AB9

Y9

R9

G9

E9

A9

AG8

AD8

AA8

U8

K8

C8

BA7

AV7

AP7

AL7

AJ7

AH7

AF7

AC7

R7

G7

D7

AG6

AD6

AB6