A B C

D

REVISIONS

1

2

3

SUB=NP Always no-pop

BOM options

1 = Adds 1U Parts

2 = Adds 2U Parts

5 = STMicro TPM (ROW)

6 = Winbond TPM (ST TPM is base/pop 0)

7 = Plug In Module TPM (ROW-PIM)

8 = Development/Debug (ST parts)

9 = Development/Debug (non-ST parts)

BOM Instructions

In order to build a proper BOM, you must run a combo build

Parts without subs appear on all builds (i.e., Build 0 is not needed)

BRINGUP/UT/PT

2U: 2,5,8,9

1U: 1,5,8,9

SYSTEM TEST

2U: 2,5,8

1U: 1,5,8

PRODUCTION

2U: 2,5 (Must be in Combined Build Field)

1U: 1,5 (Must be in Combined Build Field)

Bluefish Thidwick

PWA: KP259

ASSY: DU071

PWB: YN967

SCH: NT247

THIDWICK PLANAR

1U DPNs2U DPNs

PWA: FN855

ASSY: UU671

PWB: PK460

SCH: RR154

P15_JR_DT17255: remove change build5 to STMicro TPM

P15_JR_DT17120: New build option for onboard TPM

Bluefish/Thidwick 8 Layers Stackup

SolderMask: 0.5 mils, ER = 3.7

Layer 1: TOP, 2.1 mils, 1.5 oz

Prepreg: 4 mils, ER = 4

Layer 2: GND, 1.3 mils, 1.0 oz

Core: 4 mils, ER = 4

Layer 3: INNER1, 1.3 mils, 1.0 oz

Prepreg: 20 mils, ER = 4.3

Layer 4: VCC, 2.6 mils, 2.0 oz

Core: 10 mils, ER = 4

Layer 5: VC2, 2.6 mils, 2.0 oz

Prepreg: 20 mils, ER = 4.3

Layer 6: INNER2, 1.3 mils, 1.0 oz

Core: 4 mils, ER = 4

Layer 7: GD2, 1.3 mils, 1.0 oz

Prepreg: 4 mils, ER = 4

Layer 8: BOTTOM, 2.1 mils, 1.5 oz

SolderMask: 0.5 mils, ER = 3.7

REV

X00 Initial Prototype Release

X01 Unit Test (UT) Release

Layout Issue, schematics same as X01X02

X03 Product Test (PT) Release

X04

X05

Product Test (PT) Release with Memory Route Updates

System Test (ST1) Release

DESCRIPTIONECO DATE

TABLE OF CONTENTS

Page 1.

Page 2-10.

Page 11.

Page 12-18.

Page 19-28.

Page 29-35.

Page 36-45.

Page 46.

Page 47.

Page 48-49

Page 50.

Page 51-61.

Page 62-71.

Page 72.

Page 73.

Page 74.

Page 75.

Page 76.

Page 77-80.

Page 81-84.

Page 85.

Page 86-87.

Page 88.

Page 89.

Page 90.

Page 91.

Page 92.

Page 93.

Page 94-97. CPLD

Page 98.

Page 99.

Page 100.

Page 101.

Page 102-110.

Page 111.

Page 112.

Page 113.

Page 114.

Page 115.

Page 116-118.

Page 119-121.

Page 122.

Page 123.

Page 124.

Page 125-126.

Page 127-128.

Page 129.

Page 130.

Page 131.

Page 132.

Page 133. VR: ICH9 1.05V

Page 134.

Page 135.

Page 136. VR: System 1.2V AUX and 1.8V AUX

Page 137.

Page 138.

Page 139.

Page 140.

Page 141. VR: Voltage Margining

Page 142.

Page 143.

Page 144.

Page 145.

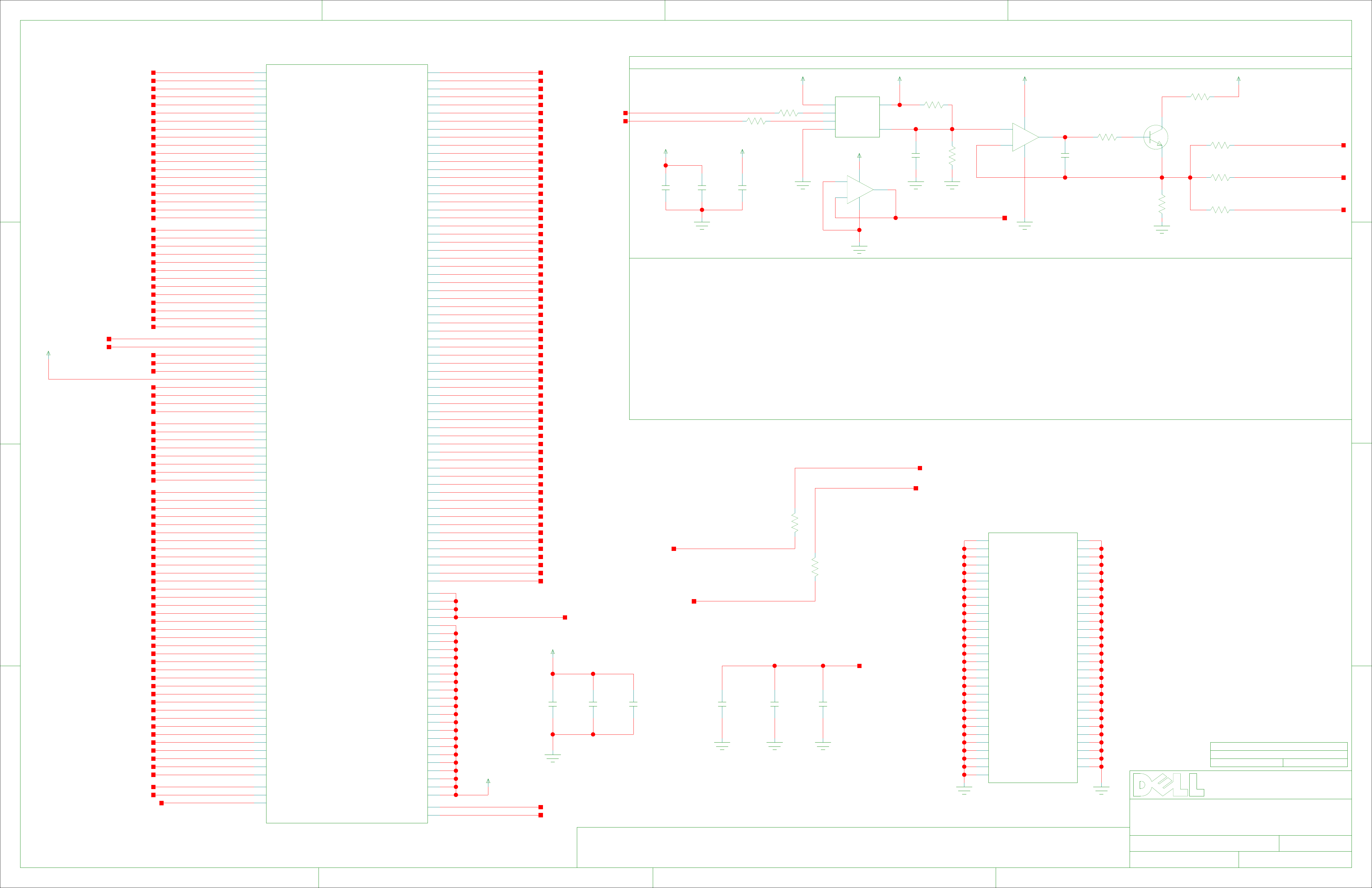

TOC

BLOCK DIAGRAMS

CPU TOC

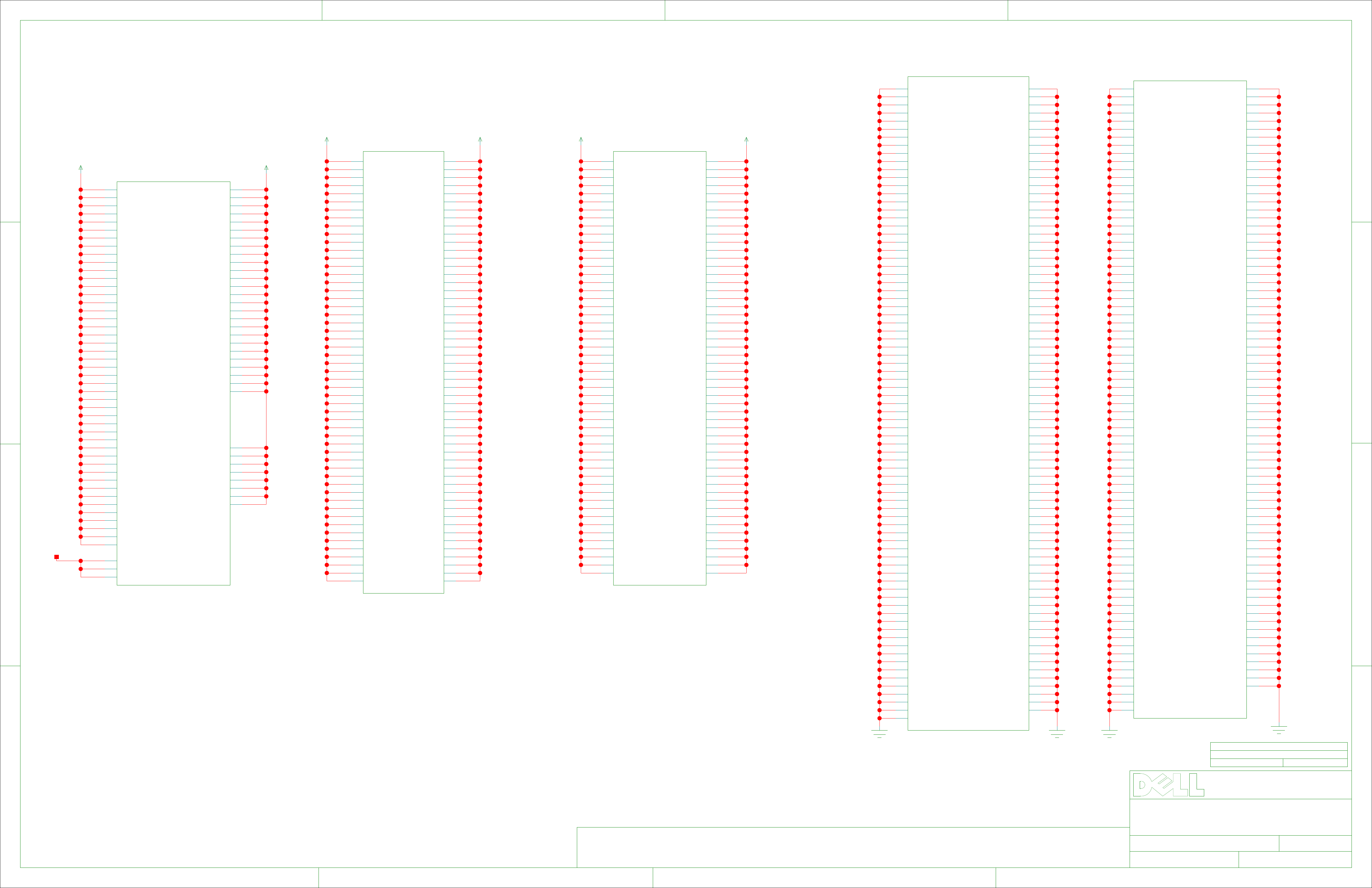

CPU 1

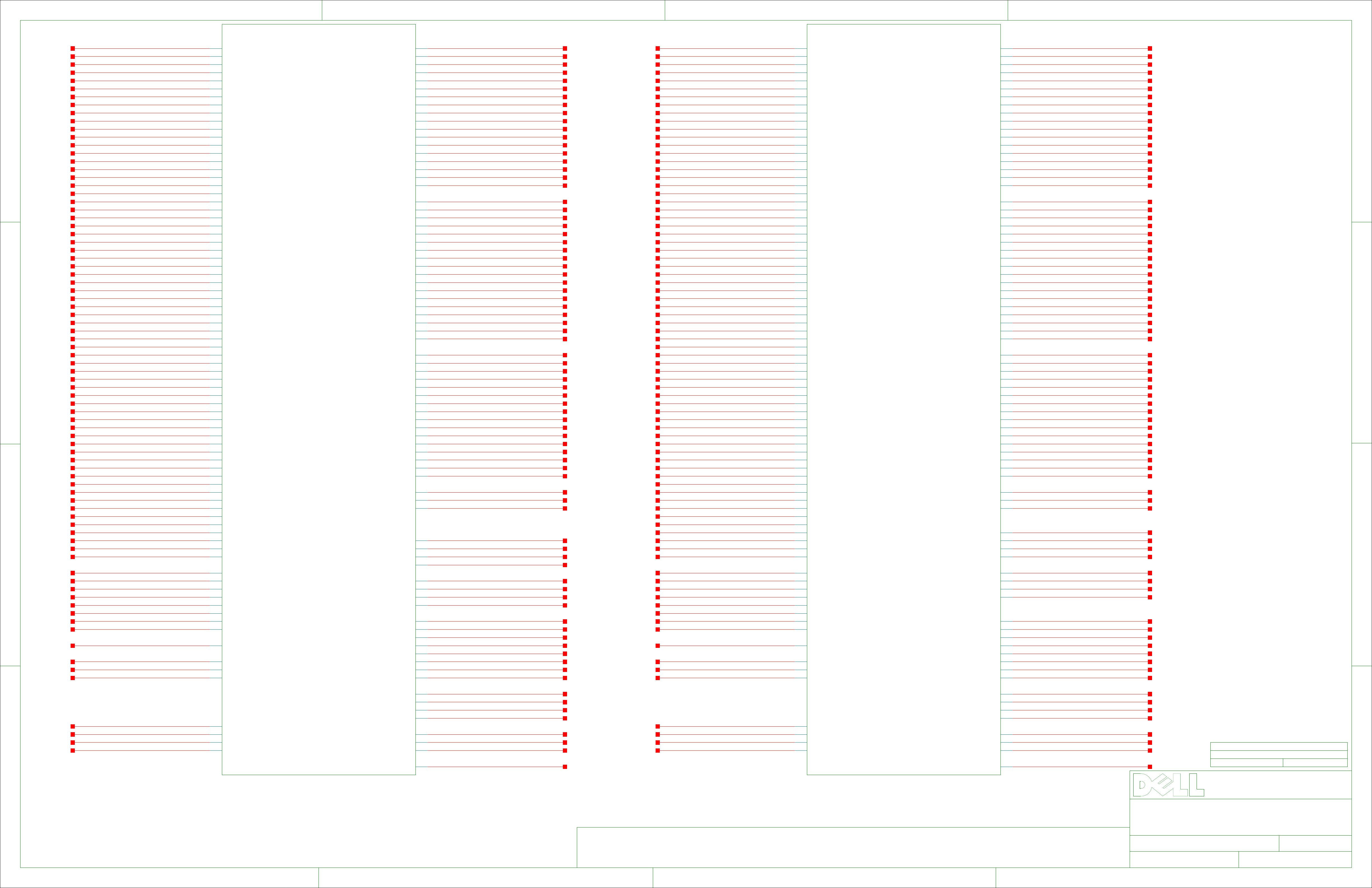

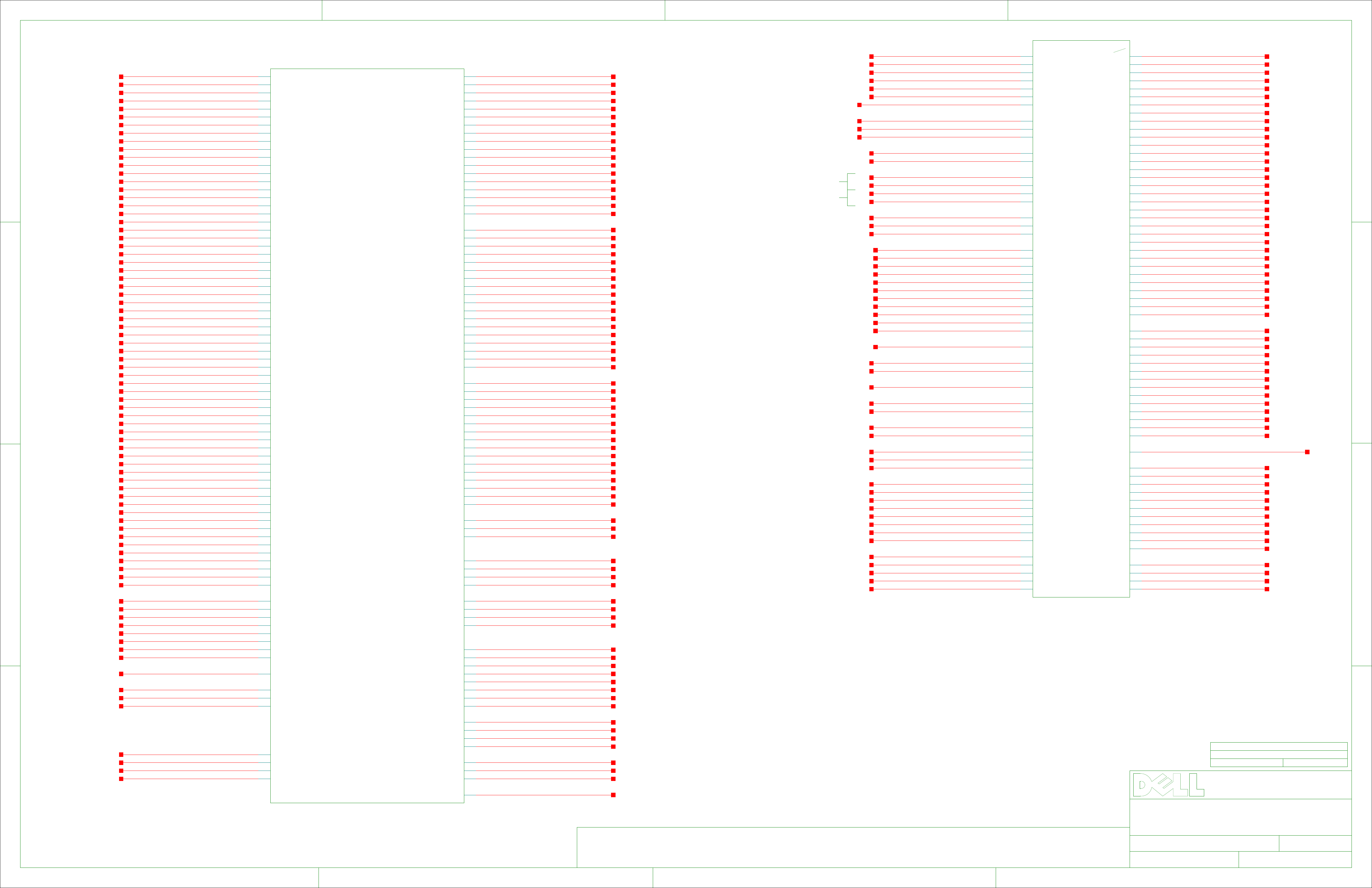

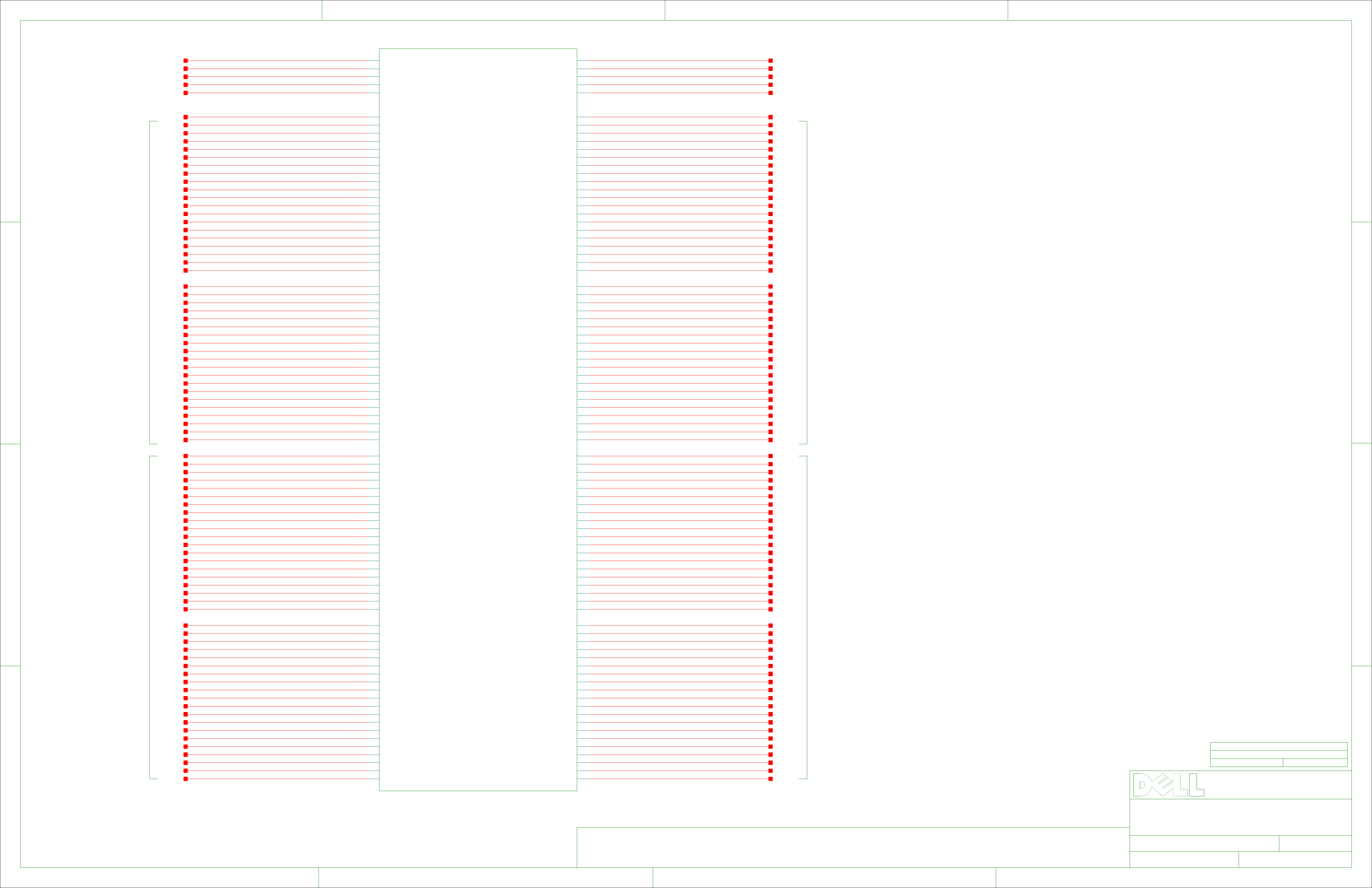

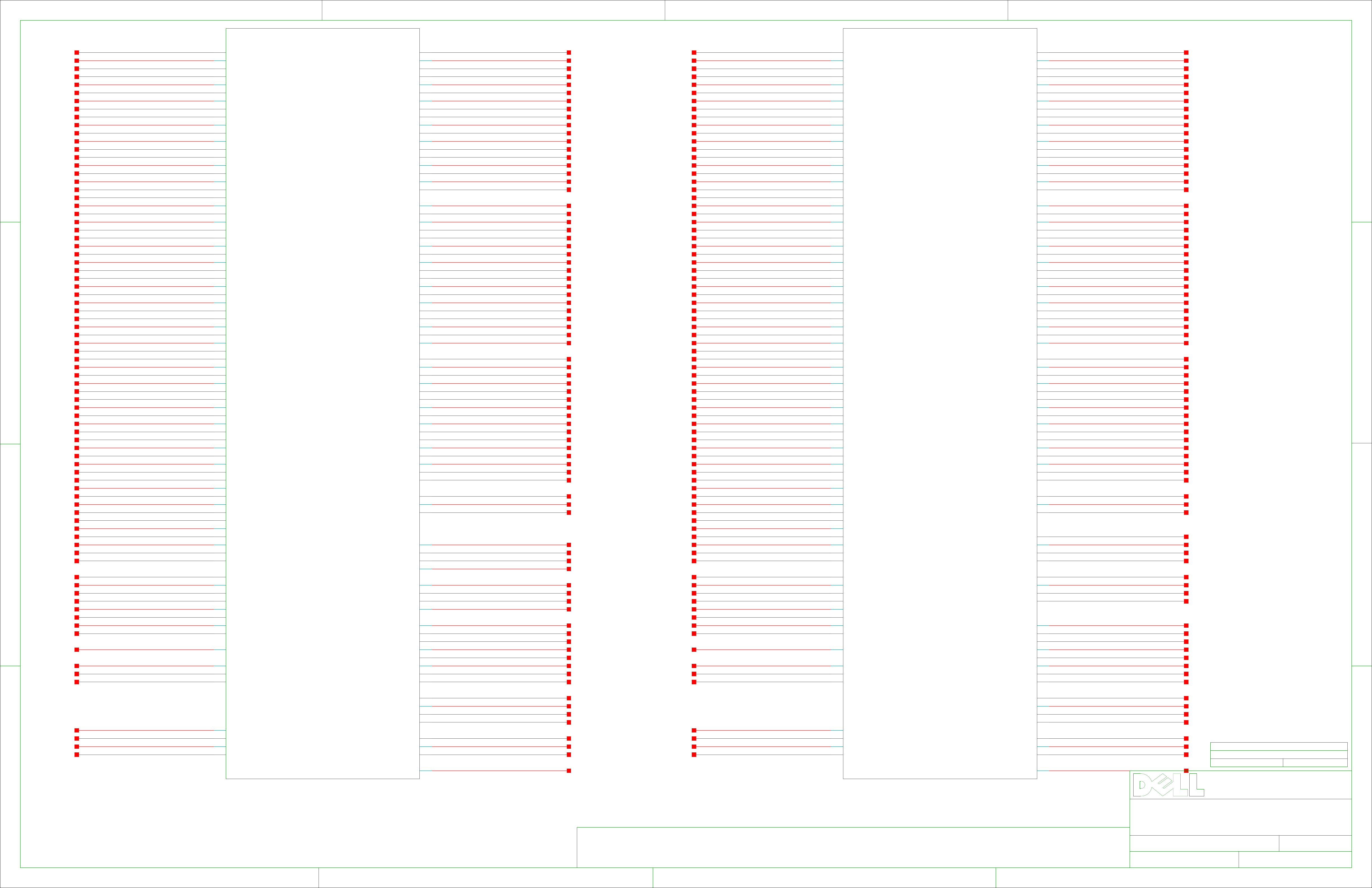

CPU 1 DIMMs (6)

CPU 2

CPU 2 DIMMs (6)

CPU XDP

Clock Generator: CK410B+

Clock Buffer: DB1200

Clock Buffer: CK-MNG

Tylersburg IOH

ICH9

PCIE Wake

Super I/O

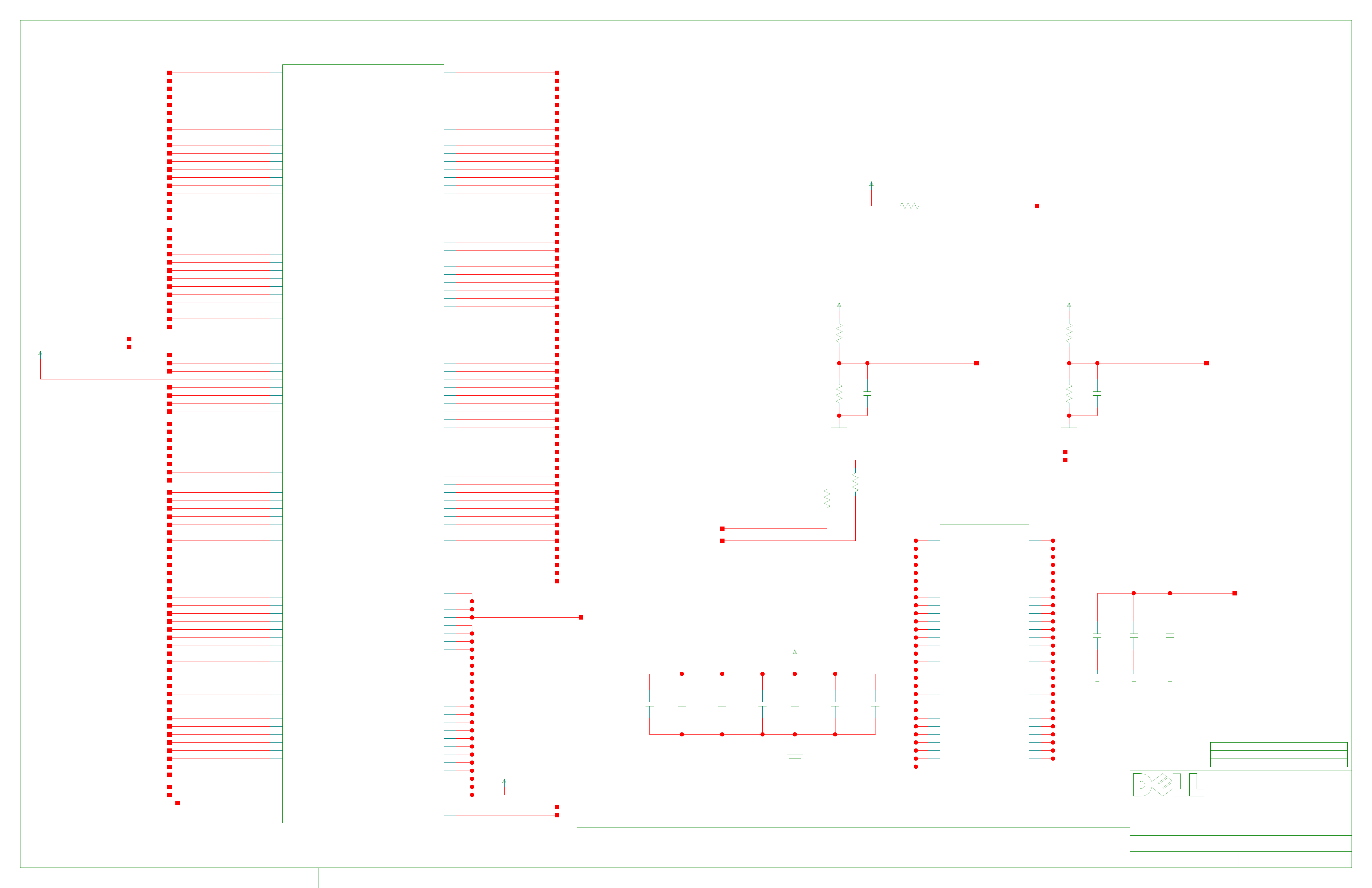

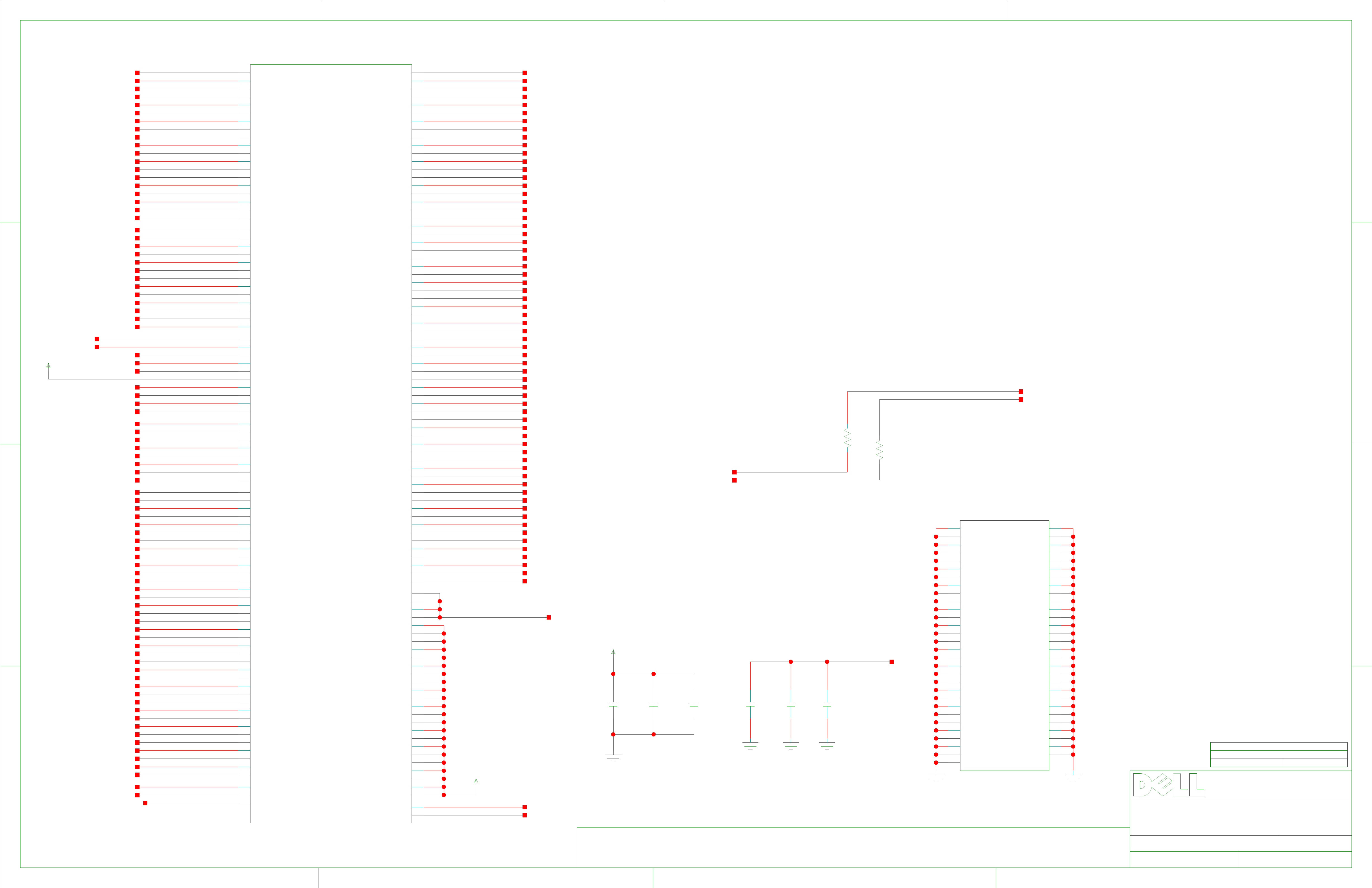

TPM and Jumpers

Firmware Hub

Coin Cell Battery

LOM1 Broadcom 5709C

LOM2 Broadcom 5709C

LOM 1&2 Shared Circuitry

Risers (Left, Center)

Control Panel and Backplane Connectors

SATA Connectors

USB Connectors and Buttons

COM port

PCIe Midbus

Debug

Intrusion Detect and Power Good

Rear ID, Cyclops

Fan Connectors and Tach

iBMC TOC

iBMC

Video Riser

Video Redrive

Video Switch

Power Connectors

VR: CPU 1&2 1.8V

VR: CPU 1 VCore

VR: CPU 2 VCore

VR: CPU 1 Vtt

VR: CPU 2 Vtt

VR: Memory 1 & 2 Vtt 0.75V

VR: Memory 1 1.5V

VR: Memory 2 1.5V

VR: System 8V

VR: IOH 1.8V & 0.9V

VR: ICH9 5V AUX

VR: 3.3V AUX

VR: LOM 1.0V

VR: LOM 1.0V AUX

VR: System 5V

VR: System 3.3V

VR: System 1.5V

VR: System 1.1V

Ground Clips, Mounting Holes and Mechanical Adds

Impedance Coupons

PAUX LED & Voltage Props

Spare Parts

APPROVED

1

2

3

4

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

THIDWICK

UNIQUE PAGE

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY

OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN

WHOLE OR IN PART AND MUST BE RETURNED TO DELL INC.

UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE

OF THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED

FOR SUCH USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE

LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

11G Team

11G Team

TJ Thompson

Mark Reinke

04/11/2008

04/11/2008

04/11/2008

04/11/2008

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

SCHEM,PLN,SV,R610

DWG NO.

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

INC.

ROUND ROCK,TEXAS

RR154

DATE

SHEET

4

REV.

X05

1 OF 14511/6/2008

DCBA

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

SCHEM,PLN,SV,R610

RR154

DCBA

4

ROUND ROCK,TEXAS

REV.

X05

SHEET

2 OF 14511/6/2008

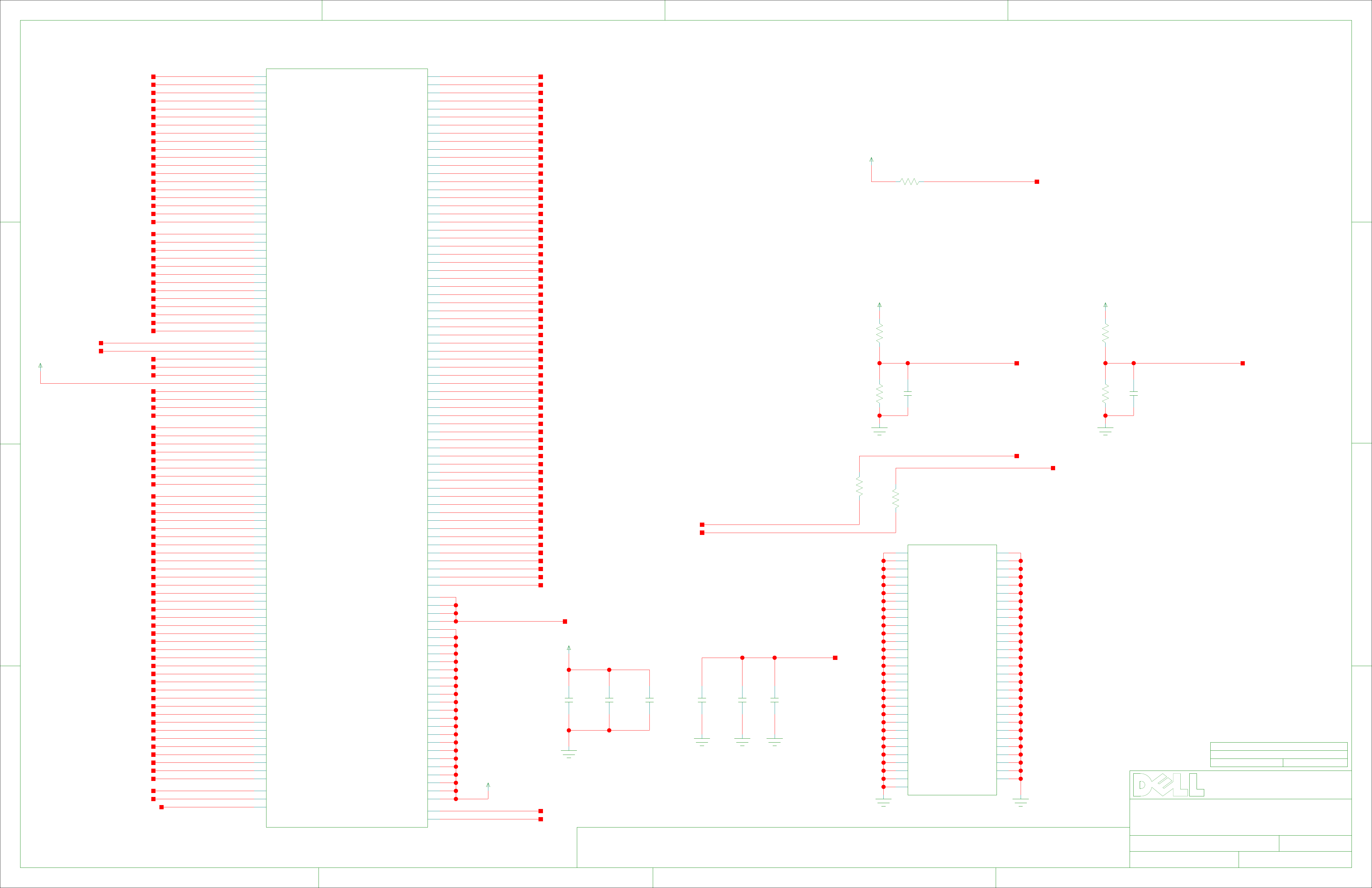

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

SCHEM,PLN,SV,R610

RR154

DCBA

4

ROUND ROCK,TEXAS

REV.

X05

SHEET

3 OF 14511/6/2008

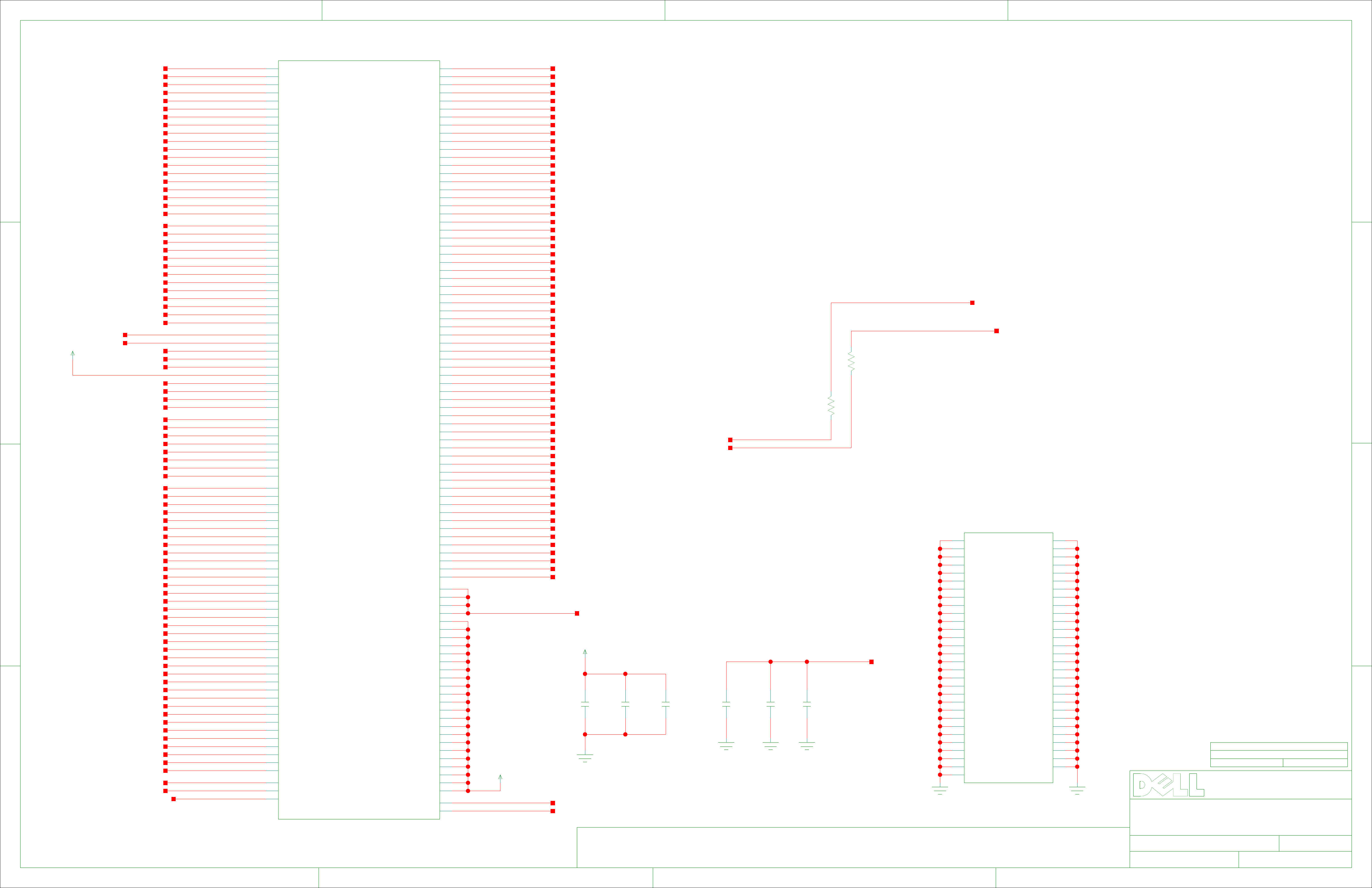

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,PLN,SV,R610

REV.

RR154

SHEET

11/6/2008 4 OF 145

DCBA

4

X05

A B C

I2C Bluefish Address Table & Segments

D

1

1

2

2

3

3

Location of these docs: R:\Schematic_Projects\PowerEdge\11G\Bluefish\System_Documentation\Block_Diagrams\I2C

P21_DTnone_BT: Updated I2C Table

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,PLN,SV,R610

REV.

RR154

SHEET

11/6/2008 5 OF 145

DCBA

4

X05

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,PLN,SV,R610

REV.

RR154

SHEET

11/6/2008 6 OF 145

DCBA

4

X05

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,PLN,SV,R610

REV.

RR154

SHEET

11/6/2008 7 OF 145

DCBA

4

X05

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

SCHEM,PLN,SV,R610

RR154

DCBA

4

ROUND ROCK,TEXAS

REV.

X05

SHEET

8 OF 14511/6/2008

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,PLN,SV,R610

REV.

RR154

SHEET

11/6/2008 9 OF 145

DCBA

4

X05

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,PLN,SV,R610

REV.

RR154

SHEET

X05

11/6/2008 10 OF 145

DCBA

4

A B C

D

1

1

2

2

3

3

4

P22_JLP_added chart

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM,PLN,SV,R610

REV.

RR154

SHEET

X05

11/6/2008 11 OF 145

DCBA

4

A B C

J_CPU1

D

1

CSI_CK_CPU1_IOH_DN

51

CSI_CK_CPU1_IOH_DP

51

CSI_CK_IOH_CPU1_DN

51

CSI_CK_IOH_CPU1_DP

51

MOD_CPU_CSI_CPU1_COMP_0

16

CSI_CPU1_IOH_19_DP

51

CSI_CPU1_IOH_18_DN

51

CSI_CPU1_IOH_17_DP

51

CSI_CPU1_IOH_16_DN

51

CSI_CPU1_IOH_15_DP

51

CSI_CPU1_IOH_14_DN

51

CSI_CPU1_IOH_13_DN

51

CSI_CPU1_IOH_12_DN

51

CSI_CPU1_IOH_11_DN

51

CSI_CPU1_IOH_10_DN

51

CSI_CPU1_IOH_09_DN

51

CSI_CPU1_IOH_08_DP

51

CSI_CPU1_IOH_07_DP

51

CSI_CPU1_IOH_06_DN

51

CSI_CPU1_IOH_05_DP

51

CSI_CPU1_IOH_04_DP

51

CSI_CPU1_IOH_03_DP

51

CSI_CPU1_IOH_02_DP

51

CSI_CPU1_IOH_01_DP

51

CSI_CPU1_IOH_00_DN

51

AG42

CSI0_CLKTX_DP

AF42

CSI0_CLKTX_DN

AR41

CSI0_CLKRX_DP

AR42

CSI0_CLKRX_DN

AL43

CSI0_COMP

AE40

CSI0_DTX_DP_19

AD38

CSI0_DTX_DP_18

AB39

CSI0_DTX_DP_17

AC39

CSI0_DTX_DP_16

AC41

CSI0_DTX_DP_15

AD40

CSI0_DTX_DP_14

AC43

CSI0_DTX_DP_13

AD42

CSI0_DTX_DP_12

AE42

CSI0_DTX_DP_11

AF43

CSI0_DTX_DP_10

AG40

CSI0_DTX_DP_9

AJ43

CSI0_DTX_DP_8

AK42

CSI0_DTX_DP_7

AH41

CSI0_DTX_DP_6

AK40

CSI0_DTX_DP_5

AH40

CSI0_DTX_DP_4

AJ38

CSI0_DTX_DP_3

AK37

CSI0_DTX_DP_2

AF39

CSI0_DTX_DP_1

AG38

CSI0_DTX_DP_0

CSI1_CLKTX_DP

CSI1_CLKTX_DN

CSI1_CLKRX_DP

CSI1_CLKRX_DN

CSI1_COMP

CSI1_DTX_DP_19

CSI1_DTX_DP_18

CSI1_DTX_DP_17

CSI1_DTX_DP_16

CSI1_DTX_DP_15

CSI1_DTX_DP_14

CSI1_DTX_DP_13

CSI1_DTX_DP_12

CSI1_DTX_DP_11

CSI1_DTX_DP_10

CSI1_DTX_DP_9

CSI1_DTX_DP_8

CSI1_DTX_DP_7

CSI1_DTX_DP_6

CSI1_DTX_DP_5

CSI1_DTX_DP_4

CSI1_DTX_DP_3

CSI1_DTX_DP_2

CSI1_DTX_DP_1

CSI1_DTX_DP_0

AF6

AE6

AT6

AR6

AL6

AC8

AD5

AD6

AB6

AC4

AE3

AC3

AD2

AE1

AF2

AH2

AH3

AK1

AJ3

AG7

AJ4

AK6

AH6

AJ8

AG8

CSI_CK_CPU1_CPU2_DP

CSI_CK_CPU1_CPU2_DN

CSI_CK_CPU2_CPU1_DP

CSI_CK_CPU2_CPU1_DN

MOD_CPU_CSI_CPU1_COMP_1

CSI_CPU1_CPU2_19_DP

CSI_CPU1_CPU2_18_DP

CSI_CPU1_CPU2_17_DP

CSI_CPU1_CPU2_16_DP

CSI_CPU1_CPU2_15_DP

CSI_CPU1_CPU2_14_DP

CSI_CPU1_CPU2_13_DP

CSI_CPU1_CPU2_12_DP

CSI_CPU1_CPU2_11_DP

CSI_CPU1_CPU2_10_DP

CSI_CPU1_CPU2_09_DP

CSI_CPU1_CPU2_08_DP

CSI_CPU1_CPU2_07_DP

CSI_CPU1_CPU2_06_DP

CSI_CPU1_CPU2_05_DP

CSI_CPU1_CPU2_04_DP

CSI_CPU1_CPU2_03_DP

CSI_CPU1_CPU2_02_DP

CSI_CPU1_CPU2_01_DP

CSI_CPU1_CPU2_00_DP

29

29

29

29

16

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

1

To CPU2

Port 1 Port 1

2

Port 0

CSI_CPU1_IOH_19_DN

51

CSI_CPU1_IOH_18_DP

51

CSI_CPU1_IOH_17_DN

51

CSI_CPU1_IOH_16_DP

51

CSI_CPU1_IOH_15_DN

51

CSI_CPU1_IOH_14_DP

51

CSI_CPU1_IOH_13_DP

51

CSI_CPU1_IOH_12_DP

51

CSI_CPU1_IOH_11_DP

51

CSI_CPU1_IOH_10_DP

51

CSI_CPU1_IOH_09_DP

51

CSI_CPU1_IOH_08_DN

51

CSI_CPU1_IOH_07_DN

51

CSI_CPU1_IOH_06_DP

51

CSI_CPU1_IOH_05_DN

51

CSI_CPU1_IOH_04_DN

51

CSI_CPU1_IOH_03_DN

51

CSI_CPU1_IOH_02_DN

51

CSI_CPU1_IOH_01_DN

51

CSI_CPU1_IOH_00_DP

51

AF40

CSI0_DTX_DN_19

AE38

CSI0_DTX_DN_18

AB38

CSI0_DTX_DN_17

AC38

CSI0_DTX_DN_16

AC40

CSI0_DTX_DN_15

AD39

CSI0_DTX_DN_14

AB43

CSI0_DTX_DN_13

AC42

CSI0_DTX_DN_12

AE41

CSI0_DTX_DN_11

AE43

CSI0_DTX_DN_10

AG41

CSI0_DTX_DN_9

AH43

CSI0_DTX_DN_8

AJ42

CSI0_DTX_DN_7

AH42

CSI0_DTX_DN_6

AK41

CSI0_DTX_DN_5

AJ40

CSI0_DTX_DN_4

AJ39

CSI0_DTX_DN_3

AK38

CSI0_DTX_DN_2

AG39

CSI0_DTX_DN_1

AH38

CSI0_DTX_DN_0

CSI1_DTX_DN_19

CSI1_DTX_DN_18

CSI1_DTX_DN_17

CSI1_DTX_DN_16

CSI1_DTX_DN_15

CSI1_DTX_DN_14

CSI1_DTX_DN_13

CSI1_DTX_DN_12

CSI1_DTX_DN_11

CSI1_DTX_DN_10

CSI1_DTX_DN_9

CSI1_DTX_DN_8

CSI1_DTX_DN_7

CSI1_DTX_DN_6

CSI1_DTX_DN_5

CSI1_DTX_DN_4

CSI1_DTX_DN_3

CSI1_DTX_DN_2

CSI1_DTX_DN_1

CSI1_DTX_DN_0

AD8

AE5

AD7

AC6

AD4

AE4

AB3

AD3

AD1

AF3

AG2

AH4

AJ1

AJ2

AG6

AK4

AK5

AJ6

AJ7

AH8

CSI_CPU1_CPU2_19_DN

CSI_CPU1_CPU2_18_DN

CSI_CPU1_CPU2_17_DN

CSI_CPU1_CPU2_16_DN

CSI_CPU1_CPU2_15_DN

CSI_CPU1_CPU2_14_DN

CSI_CPU1_CPU2_13_DN

CSI_CPU1_CPU2_12_DN

CSI_CPU1_CPU2_11_DN

CSI_CPU1_CPU2_10_DN

CSI_CPU1_CPU2_09_DN

CSI_CPU1_CPU2_08_DN

CSI_CPU1_CPU2_07_DN

CSI_CPU1_CPU2_06_DN

CSI_CPU1_CPU2_05_DN

CSI_CPU1_CPU2_04_DN

CSI_CPU1_CPU2_03_DN

CSI_CPU1_CPU2_02_DN

CSI_CPU1_CPU2_01_DN

CSI_CPU1_CPU2_00_DN

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

2

3

CSI_IOH_CPU1_19_DN

51

CSI_IOH_CPU1_18_DN

51

CSI_IOH_CPU1_17_DN

51

CSI_IOH_CPU1_16_DN

51

CSI_IOH_CPU1_15_DN

51

CSI_IOH_CPU1_14_DP

51

CSI_IOH_CPU1_13_DP

51

CSI_IOH_CPU1_12_DN

51

CSI_IOH_CPU1_11_DN

51

CSI_IOH_CPU1_10_DP

51

CSI_IOH_CPU1_09_DN

51

CSI_IOH_CPU1_08_DN

51

CSI_IOH_CPU1_07_DN

51

CSI_IOH_CPU1_06_DN

51

CSI_IOH_CPU1_05_DN

51

CSI_IOH_CPU1_04_DN

51

CSI_IOH_CPU1_03_DN

51

CSI_IOH_CPU1_02_DN

51

CSI_IOH_CPU1_01_DP

51

CSI_IOH_CPU1_00_DN

51

AP38

CSI0_DRX_DP_19

AN39

CSI0_DRX_DP_18

AP41

CSI0_DRX_DP_17

AM42

CSI0_DRX_DP_16

AN40

CSI0_DRX_DP_15

AN43

CSI0_DRX_DP_14

AP42

CSI0_DRX_DP_13

AT40

CSI0_DRX_DP_12

AT43

CSI0_DRX_DP_11

AU42

CSI0_DRX_DP_10

AU40

CSI0_DRX_DP_9

AW40

CSI0_DRX_DP_8

AU39

CSI0_DRX_DP_7

BA38

CSI0_DRX_DP_6

AW37

CSI0_DRX_DP_5

BA36

CSI0_DRX_DP_4

AW36

CSI0_DRX_DP_3

AV36

CSI0_DRX_DP_2

AU38

CSI0_DRX_DP_1

AT37

CSI0_DRX_DP_0

CSI1_DRX_DP_19

CSI1_DRX_DP_18

CSI1_DRX_DP_17

CSI1_DRX_DP_16

CSI1_DRX_DP_15

CSI1_DRX_DP_14

CSI1_DRX_DP_13

CSI1_DRX_DP_12

CSI1_DRX_DP_11

CSI1_DRX_DP_10

CSI1_DRX_DP_9

CSI1_DRX_DP_8

CSI1_DRX_DP_7

CSI1_DRX_DP_6

CSI1_DRX_DP_5

CSI1_DRX_DP_4

CSI1_DRX_DP_3

CSI1_DRX_DP_2

CSI1_DRX_DP_1

CSI1_DRX_DP_0

AM8

AM6

AN5

AM4

AP3

AM2

AN1

AP2

AR4

AT1

AT3

AU4

AW4

AU7

AY6

BA7

AV5

AY8

AV7

AU8

CSI_CPU2_CPU1_19_DP

CSI_CPU2_CPU1_18_DP

CSI_CPU2_CPU1_17_DP

CSI_CPU2_CPU1_16_DP

CSI_CPU2_CPU1_15_DP

CSI_CPU2_CPU1_14_DP

CSI_CPU2_CPU1_13_DP

CSI_CPU2_CPU1_12_DP

CSI_CPU2_CPU1_11_DP

CSI_CPU2_CPU1_10_DP

CSI_CPU2_CPU1_09_DP

CSI_CPU2_CPU1_08_DP

CSI_CPU2_CPU1_07_DP

CSI_CPU2_CPU1_06_DP

CSI_CPU2_CPU1_05_DP

CSI_CPU2_CPU1_04_DP

CSI_CPU2_CPU1_03_DP

CSI_CPU2_CPU1_02_DP

CSI_CPU2_CPU1_01_DP

CSI_CPU2_CPU1_00_DP

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

From CPU2

3

4

CSI_IOH_CPU1_19_DP

51

CSI_IOH_CPU1_18_DP

51

CSI_IOH_CPU1_17_DP

51

CSI_IOH_CPU1_16_DP

51

CSI_IOH_CPU1_15_DP

51

DEBUG: Mirror port default is port 0.

Port 0

From IOH To IOH

Note: P/N is intentionally swizzled for layout

CSI_IOH_CPU1_14_DN

51

CSI_IOH_CPU1_13_DN

51

CSI_IOH_CPU1_12_DP

51

CSI_IOH_CPU1_11_DP

51

CSI_IOH_CPU1_10_DN

51

CSI_IOH_CPU1_09_DP

51

CSI_IOH_CPU1_08_DP

51

CSI_IOH_CPU1_07_DP

51

CSI_IOH_CPU1_06_DP

51

CSI_IOH_CPU1_05_DP

51

CSI_IOH_CPU1_04_DP

51

CSI_IOH_CPU1_03_DP

51

CSI_IOH_CPU1_02_DP

51

CSI_IOH_CPU1_01_DN

51

CSI_IOH_CPU1_00_DP

51

ADD*_FN258_ILM

AR38

CSI0_DRX_DN_19

AP39

CSI0_DRX_DN_18

AP40

CSI0_DRX_DN_17

AM41

CSI0_DRX_DN_16

AM40

CSI0_DRX_DN_15

AM43

CSI0_DRX_DN_14

AN42

CSI0_DRX_DN_13

AR40

CSI0_DRX_DN_12

AR43

CSI0_DRX_DN_11

AT42

CSI0_DRX_DN_10

AU41

CSI0_DRX_DN_9

AV40

CSI0_DRX_DN_8

AT39

CSI0_DRX_DN_7

AY38

CSI0_DRX_DN_6

AW38

CSI0_DRX_DN_5

BA37

CSI0_DRX_DN_4

AY36

CSI0_DRX_DN_3

AV37

CSI0_DRX_DN_2

AV38

CSI0_DRX_DN_1

AU37

CSI0_DRX_DN_0

GAINESTOWN_WESTMERE REV 2.0

HETERO 1 OF 10

CSI1_DRX_DN_19

CSI1_DRX_DN_18

CSI1_DRX_DN_17

CSI1_DRX_DN_16

CSI1_DRX_DN_15

CSI1_DRX_DN_14

CSI1_DRX_DN_13

CSI1_DRX_DN_12

CSI1_DRX_DN_11

CSI1_DRX_DN_10

CSI1_DRX_DN_9

CSI1_DRX_DN_8

CSI1_DRX_DN_7

CSI1_DRX_DN_6

CSI1_DRX_DN_5

CSI1_DRX_DN_4

CSI1_DRX_DN_3

CSI1_DRX_DN_2

CSI1_DRX_DN_1

CSI1_DRX_DN_0

AL8

AM7

AN6

AN4

AP4

AM3

AM1

AN2

AR5

AR1

AT2

AU3

AW3

AU6

AY5

BA6

AW5

BA8

AW7

AV8

CSI_CPU2_CPU1_19_DN

CSI_CPU2_CPU1_18_DN

CSI_CPU2_CPU1_17_DN

CSI_CPU2_CPU1_16_DN

CSI_CPU2_CPU1_15_DN

CSI_CPU2_CPU1_14_DN

CSI_CPU2_CPU1_13_DN

CSI_CPU2_CPU1_12_DN

CSI_CPU2_CPU1_11_DN

CSI_CPU2_CPU1_10_DN

CSI_CPU2_CPU1_09_DN

CSI_CPU2_CPU1_08_DN

CSI_CPU2_CPU1_07_DN

CSI_CPU2_CPU1_06_DN

CSI_CPU2_CPU1_05_DN

CSI_CPU2_CPU1_04_DN

CSI_CPU2_CPU1_03_DN

CSI_CPU2_CPU1_02_DN

CSI_CPU2_CPU1_01_DN

CSI_CPU2_CPU1_00_DN

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

29

Note: P/N is intentionally swizzled for layout

MODULE:

DESC:

REV: OF

CPU1

INC.

TITLE

ROUND ROCK,TEXAS

CPU1

CPUS,CSI,XDP0,XDP1

SEC

4

ADD*_Y080J_ILM_COVER

ADD*_D994J_LABEL

P21_SCH_17608 added ilm cover and label

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

SCHEM,PLN,SV,R610

RR154

DCBA

REV.

X05

SHEET

12 OF 14511/6/2008

A B C

J_CPU1

J_CPU1

D

1

2

3

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

21

20

CPU1_M_CH0_DQ63

CPU1_M_CH0_DQ62

CPU1_M_CH0_DQ61

CPU1_M_CH0_DQ60

CPU1_M_CH0_DQ59

CPU1_M_CH0_DQ58

CPU1_M_CH0_DQ57

CPU1_M_CH0_DQ56

CPU1_M_CH0_DQ55

CPU1_M_CH0_DQ54

CPU1_M_CH0_DQ53

CPU1_M_CH0_DQ52

CPU1_M_CH0_DQ51

CPU1_M_CH0_DQ50

CPU1_M_CH0_DQ49

CPU1_M_CH0_DQ48

CPU1_M_CH0_DQ47

CPU1_M_CH0_DQ46

CPU1_M_CH0_DQ45

CPU1_M_CH0_DQ44

CPU1_M_CH0_DQ43

CPU1_M_CH0_DQ42

CPU1_M_CH0_DQ41

CPU1_M_CH0_DQ40

CPU1_M_CH0_DQ39

CPU1_M_CH0_DQ38

CPU1_M_CH0_DQ37

CPU1_M_CH0_DQ36

CPU1_M_CH0_DQ35

CPU1_M_CH0_DQ34

CPU1_M_CH0_DQ33

CPU1_M_CH0_DQ32

CPU1_M_CH0_DQ31

CPU1_M_CH0_DQ30

CPU1_M_CH0_DQ29

CPU1_M_CH0_DQ28

CPU1_M_CH0_DQ27

CPU1_M_CH0_DQ26

CPU1_M_CH0_DQ25

CPU1_M_CH0_DQ24

CPU1_M_CH0_DQ23

CPU1_M_CH0_DQ22

CPU1_M_CH0_DQ21

CPU1_M_CH0_DQ20

CPU1_M_CH0_DQ19

CPU1_M_CH0_DQ18

CPU1_M_CH0_DQ17

CPU1_M_CH0_DQ16

CPU1_M_CH0_DQ15

CPU1_M_CH0_DQ14

CPU1_M_CH0_DQ13

CPU1_M_CH0_DQ12

CPU1_M_CH0_DQ11

CPU1_M_CH0_DQ10

CPU1_M_CH0_DQ09

CPU1_M_CH0_DQ08

CPU1_M_CH0_DQ07

CPU1_M_CH0_DQ06

CPU1_M_CH0_DQ05

CPU1_M_CH0_DQ04

CPU1_M_CH0_DQ03

CPU1_M_CH0_DQ02

CPU1_M_CH0_DQ01

CPU1_M_CH0_DQ00

CPU1_M_CH0_ECC_7

CPU1_M_CH0_ECC_6

CPU1_M_CH0_ECC_5

CPU1_M_CH0_ECC_4

CPU1_M_CH0_ECC_3

CPU1_M_CH0_ECC_2

CPU1_M_CH0_ECC_1

CPU1_M_CH0_ECC_0

CPU1_M_CH0_MA_PAR

NC_SCR_CPU1_M_CH0_PERR_2_N

CPU1_M_CH0_PERR_1_N

CPU1_M_CH0_PERR_0_N

W4

DDR0_DQ_63

V4

DDR0_DQ_62

U3

DDR0_DQ_61

U1

DDR0_DQ_60

Y3

DDR0_DQ_59

Y2

DDR0_DQ_58

V1

DDR0_DQ_57

U4

DDR0_DQ_56

T3

DDR0_DQ_55

R4

DDR0_DQ_54

N3

DDR0_DQ_53

M3

DDR0_DQ_52

T2

DDR0_DQ_51

T1

DDR0_DQ_50

N2

DDR0_DQ_49

N1

DDR0_DQ_48

L2

DDR0_DQ_47

L3

DDR0_DQ_46

H3

DDR0_DQ_45

G1

DDR0_DQ_44

M1

DDR0_DQ_43

L1

DDR0_DQ_42

H1

DDR0_DQ_41

H2

DDR0_DQ_40

F2

DDR0_DQ_39

F3

DDR0_DQ_38

C6

DDR0_DQ_37

B6

DDR0_DQ_36

G3

DDR0_DQ_35

F1

DDR0_DQ_34

C4

DDR0_DQ_33

B5

DDR0_DQ_32

B38

DDR0_DQ_31

C38

DDR0_DQ_30

D42

DDR0_DQ_29

D41

DDR0_DQ_28

D37

DDR0_DQ_27

A38

DDR0_DQ_26

C41

DDR0_DQ_25

D40

DDR0_DQ_24

F42

DDR0_DQ_23

F43

DDR0_DQ_22

J41

DDR0_DQ_21

J42

DDR0_DQ_20

E43

DDR0_DQ_19

E42

DDR0_DQ_18

H43

DDR0_DQ_17

H41

DDR0_DQ_16

L42

DDR0_DQ_15

L43

DDR0_DQ_14

P41

DDR0_DQ_13

P42

DDR0_DQ_12

K43

DDR0_DQ_11

K42

DDR0_DQ_10

N43

DDR0_DQ_9

N41

DDR0_DQ_8

T42

DDR0_DQ_7

U41

DDR0_DQ_6

W42

DDR0_DQ_5

W40

DDR0_DQ_4

R42

DDR0_DQ_3

R43

DDR0_DQ_2

V41

DDR0_DQ_1

W41

DDR0_DQ_0

C34

DDR0_ECC_7

B34

DDR0_ECC_6

A37

DDR0_ECC_5

C37

DDR0_ECC_4

C33

DDR0_ECC_3

F32

DDR0_ECC_2

A36

DDR0_ECC_1

C36

DDR0_ECC_0

B20

DDR0_MA_PAR

A27

DDR0_PAR_ERR_N_2

B28

DDR0_PAR_ERR_N_1

D25

DDR0_PAR_ERR_N_0

DDR0_DQS_P_17

DDR0_DQS_P_16

DDR0_DQS_P_15

DDR0_DQS_P_14

DDR0_DQS_P_13

DDR0_DQS_P_12

DDR0_DQS_P_11

DDR0_DQS_P_10

DDR0_DQS_P_9

DDR0_DQS_P_8

DDR0_DQS_P_7

DDR0_DQS_P_6

DDR0_DQS_P_5

DDR0_DQS_P_4

DDR0_DQS_P_3

DDR0_DQS_P_2

DDR0_DQS_P_1

DDR0_DQS_P_0

DDR0_DQS_N_17

DDR0_DQS_N_16

DDR0_DQS_N_15

DDR0_DQS_N_14

DDR0_DQS_N_13

DDR0_DQS_N_12

DDR0_DQS_N_11

DDR0_DQS_N_10

DDR0_DQS_N_9

DDR0_DQS_N_8

DDR0_DQS_N_7

DDR0_DQS_N_6

DDR0_DQS_N_5

DDR0_DQS_N_4

DDR0_DQS_N_3

DDR0_DQS_N_2

DDR0_DQS_N_1

DDR0_DQS_N_0

DDR0_MA_15

DDR0_MA_14

DDR0_MA_13

DDR0_MA_12

DDR0_MA_11

DDR0_MA_10

DDR0_MA_9

DDR0_MA_8

DDR0_MA_7

DDR0_MA_6

DDR0_MA_5

DDR0_MA_4

DDR0_MA_3

DDR0_MA_2

DDR0_MA_1

DDR0_MA_0

DDR0_BA_2

DDR0_BA_1

DDR0_BA_0

DDR0_CLK_P_3

DDR0_CLK_P_2

DDR0_CLK_P_1

DDR0_CLK_P_0

DDR0_CLK_N_3

DDR0_CLK_N_2

DDR0_CLK_N_1

DDR0_CLK_N_0

DDR0_CS_N_7/DDR0_ODT_5

DDR0_CS_N_6/DDR0_ODT_4

DDR0_CS_N_5

DDR0_CS_N_4

DDR0_CS_N_3

DDR0_CS_N_2

DDR0_CS_N_1

DDR0_CS_N_0

B36

V2

P2

J2

D5

D39

H42

N42

V43

D34

W2

R2

K2

E3

B39

F41

L41

T43

B35

V3

P1

J1

D4

C39

G43

M43

V42

D35

W1

R3

K3

E4

B40

G41

M41

U43

B29

A28

A10

B26

A26

B19

C26

B25

A25

C24

B24

B23

D24

C23

B21

A20

C28

A16

B16

E20

F18

D19

J19

E19

E18

C19

K19

B8

C11

A7

B15

B9

C13

B10

G15

CPU1_M_CH0_DQS_17_DP

CPU1_M_CH0_DQS_16_DP

CPU1_M_CH0_DQS_15_DP

CPU1_M_CH0_DQS_14_DP

CPU1_M_CH0_DQS_13_DP

CPU1_M_CH0_DQS_12_DP

CPU1_M_CH0_DQS_11_DP

CPU1_M_CH0_DQS_10_DP

CPU1_M_CH0_DQS_09_DP

CPU1_M_CH0_DQS_08_DP

CPU1_M_CH0_DQS_07_DP

CPU1_M_CH0_DQS_06_DP

CPU1_M_CH0_DQS_05_DP

CPU1_M_CH0_DQS_04_DP

CPU1_M_CH0_DQS_03_DP

CPU1_M_CH0_DQS_02_DP

CPU1_M_CH0_DQS_01_DP

CPU1_M_CH0_DQS_00_DP

CPU1_M_CH0_DQS_17_DN

CPU1_M_CH0_DQS_16_DN

CPU1_M_CH0_DQS_15_DN

CPU1_M_CH0_DQS_14_DN

CPU1_M_CH0_DQS_13_DN

CPU1_M_CH0_DQS_12_DN

CPU1_M_CH0_DQS_11_DN

CPU1_M_CH0_DQS_10_DN

CPU1_M_CH0_DQS_09_DN

CPU1_M_CH0_DQS_08_DN

CPU1_M_CH0_DQS_07_DN

CPU1_M_CH0_DQS_06_DN

CPU1_M_CH0_DQS_05_DN

CPU1_M_CH0_DQS_04_DN

CPU1_M_CH0_DQS_03_DN

CPU1_M_CH0_DQS_02_DN

CPU1_M_CH0_DQS_01_DN

CPU1_M_CH0_DQS_00_DN

CPU1_M_CH0_MA_15

CPU1_M_CH0_MA_14

CPU1_M_CH0_MA_13

CPU1_M_CH0_MA_12

CPU1_M_CH0_MA_11

CPU1_M_CH0_MA_10

CPU1_M_CH0_MA_09

CPU1_M_CH0_MA_08

CPU1_M_CH0_MA_07

CPU1_M_CH0_MA_06

CPU1_M_CH0_MA_05

CPU1_M_CH0_MA_04

CPU1_M_CH0_MA_03

CPU1_M_CH0_MA_02

CPU1_M_CH0_MA_01

CPU1_M_CH0_MA_00

CPU1_M_CH0_BA_2

CPU1_M_CH0_BA_1

CPU1_M_CH0_BA_0

CPU1_M_CH0_CK_3_DP

CPU1_M_CH0_CK_2_DP

CPU1_M_CH0_CK_1_DP

CPU1_M_CH0_CK_0_DP

CPU1_M_CH0_CK_3_DN

CPU1_M_CH0_CK_2_DN

CPU1_M_CH0_CK_1_DN

CPU1_M_CH0_CK_0_DN

CPU1_M_CH0_CS_7_N

CPU1_M_CH0_CS_6_N

CPU1_M_CH0_CS_5_N

CPU1_M_CH0_CS_4_N

CPU1_M_CH0_CS_3_N

CPU1_M_CH0_CS_2_N

CPU1_M_CH0_CS_1_N

CPU1_M_CH0_CS_0_N

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

21

20

21

20

21

20

21

20

21

21

21

21

20

20

20

20

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

24

23

CPU1_M_CH1_DQ63

CPU1_M_CH1_DQ62

CPU1_M_CH1_DQ61

CPU1_M_CH1_DQ60

CPU1_M_CH1_DQ59

CPU1_M_CH1_DQ58

CPU1_M_CH1_DQ57

CPU1_M_CH1_DQ56

CPU1_M_CH1_DQ55

CPU1_M_CH1_DQ54

CPU1_M_CH1_DQ53

CPU1_M_CH1_DQ52

CPU1_M_CH1_DQ51

CPU1_M_CH1_DQ50

CPU1_M_CH1_DQ49

CPU1_M_CH1_DQ48

CPU1_M_CH1_DQ47

CPU1_M_CH1_DQ46

CPU1_M_CH1_DQ45

CPU1_M_CH1_DQ44

CPU1_M_CH1_DQ43

CPU1_M_CH1_DQ42

CPU1_M_CH1_DQ41

CPU1_M_CH1_DQ40

CPU1_M_CH1_DQ39

CPU1_M_CH1_DQ38

CPU1_M_CH1_DQ37

CPU1_M_CH1_DQ36

CPU1_M_CH1_DQ35

CPU1_M_CH1_DQ34

CPU1_M_CH1_DQ33

CPU1_M_CH1_DQ32

CPU1_M_CH1_DQ31

CPU1_M_CH1_DQ30

CPU1_M_CH1_DQ29

CPU1_M_CH1_DQ28

CPU1_M_CH1_DQ27

CPU1_M_CH1_DQ26

CPU1_M_CH1_DQ25

CPU1_M_CH1_DQ24

CPU1_M_CH1_DQ23

CPU1_M_CH1_DQ22

CPU1_M_CH1_DQ21

CPU1_M_CH1_DQ20

CPU1_M_CH1_DQ19

CPU1_M_CH1_DQ18

CPU1_M_CH1_DQ17

CPU1_M_CH1_DQ16

CPU1_M_CH1_DQ15

CPU1_M_CH1_DQ14

CPU1_M_CH1_DQ13

CPU1_M_CH1_DQ12

CPU1_M_CH1_DQ11

CPU1_M_CH1_DQ10

CPU1_M_CH1_DQ09

CPU1_M_CH1_DQ08

CPU1_M_CH1_DQ07

CPU1_M_CH1_DQ06

CPU1_M_CH1_DQ05

CPU1_M_CH1_DQ04

CPU1_M_CH1_DQ03

CPU1_M_CH1_DQ02

CPU1_M_CH1_DQ01

CPU1_M_CH1_DQ00

CPU1_M_CH1_ECC_7

CPU1_M_CH1_ECC_6

CPU1_M_CH1_ECC_5

CPU1_M_CH1_ECC_4

CPU1_M_CH1_ECC_3

CPU1_M_CH1_ECC_2

CPU1_M_CH1_ECC_1

CPU1_M_CH1_ECC_0

CPU1_M_CH1_MA_PAR

NC_SCR_CPU1_M_CH1_PERR_2_N

CPU1_M_CH1_PERR_1_N

CPU1_M_CH1_PERR_0_N

W9

DDR1_DQ_63

AA7

DDR1_DQ_62

W5

DDR1_DQ_61

V9

DDR1_DQ_60

W10

DDR1_DQ_59

Y10

DDR1_DQ_58

W7

DDR1_DQ_57

W6

DDR1_DQ_56

R7

DDR1_DQ_55

R8

DDR1_DQ_54

M6

DDR1_DQ_53

J4

DDR1_DQ_52

T5

DDR1_DQ_51

R5

DDR1_DQ_50

K5

DDR1_DQ_49

K4

DDR1_DQ_48

J5

DDR1_DQ_47

G5

DDR1_DQ_46

H9

DDR1_DQ_45

G9

DDR1_DQ_44

H4

DDR1_DQ_43

G4

DDR1_DQ_42

J6

DDR1_DQ_41

H8

DDR1_DQ_40

F6

DDR1_DQ_39

D6

DDR1_DQ_38

G8

DDR1_DQ_37

F10

DDR1_DQ_36

F5

DDR1_DQ_35

E5

DDR1_DQ_34

E8

DDR1_DQ_33

E9

DDR1_DQ_32

K30

DDR1_DQ_31

L32

DDR1_DQ_30

H34

DDR1_DQ_29

J34

DDR1_DQ_28

J32

DDR1_DQ_27

K32

DDR1_DQ_26

L33

DDR1_DQ_25

H33

DDR1_DQ_24

H36

DDR1_DQ_23

J36

DDR1_DQ_22

M36

DDR1_DQ_21

N34

DDR1_DQ_20

J35

DDR1_DQ_19

K35

DDR1_DQ_18

M34

DDR1_DQ_17

M35

DDR1_DQ_16

N38

DDR1_DQ_15

N37

DDR1_DQ_14

R35

DDR1_DQ_13

R34

DDR1_DQ_12

N39

DDR1_DQ_11

P39

DDR1_DQ_10

P35

DDR1_DQ_9

P34

DDR1_DQ_8

Y39

DDR1_DQ_7

Y40

DDR1_DQ_6

AB36

DDR1_DQ_5

AA35

DDR1_DQ_4

Y34

DDR1_DQ_3

Y35

DDR1_DQ_2

AA36

DDR1_DQ_1

AA37

DDR1_DQ_0

G35

DDR1_ECC_7

E34

DDR1_ECC_6

F37

DDR1_ECC_5

E37

DDR1_ECC_4

G36

DDR1_ECC_3

E33

DDR1_ECC_2

F36

DDR1_ECC_1

D36

DDR1_ECC_0

D20

DDR1_MA_PAR

F25

DDR1_PAR_ERR_N_2

E25

DDR1_PAR_ERR_N_1

C22

DDR1_PAR_ERR_N_0

DDR1_DQS_P_17

DDR1_DQS_P_16

DDR1_DQS_P_15

DDR1_DQS_P_14

DDR1_DQS_P_13

DDR1_DQS_P_12

DDR1_DQS_P_11

DDR1_DQS_P_10

DDR1_DQS_P_9

DDR1_DQS_P_8

DDR1_DQS_P_7

DDR1_DQS_P_6

DDR1_DQS_P_5

DDR1_DQS_P_4

DDR1_DQS_P_3

DDR1_DQS_P_2

DDR1_DQS_P_1

DDR1_DQS_P_0

DDR1_DQS_N_17

DDR1_DQS_N_16

DDR1_DQS_N_15

DDR1_DQS_N_14

DDR1_DQS_N_13

DDR1_DQS_N_12

DDR1_DQS_N_11

DDR1_DQS_N_10

DDR1_DQS_N_9

DDR1_DQS_N_8

DDR1_DQS_N_7

DDR1_DQS_N_6

DDR1_DQS_N_5

DDR1_DQS_N_4

DDR1_DQS_N_3

DDR1_DQS_N_2

DDR1_DQS_N_1

DDR1_DQS_N_0

DDR1_MA_15

DDR1_MA_14

DDR1_MA_13

DDR1_MA_12

DDR1_MA_11

DDR1_MA_10

DDR1_MA_9

DDR1_MA_8

DDR1_MA_7

DDR1_MA_6

DDR1_MA_5

DDR1_MA_4

DDR1_MA_3

DDR1_MA_2

DDR1_MA_1

DDR1_MA_0

DDR1_BA_2

DDR1_BA_1

DDR1_BA_0

DDR1_CLK_P_3

DDR1_CLK_P_2

DDR1_CLK_P_1

DDR1_CLK_P_0

DDR1_CLK_N_3

DDR1_CLK_N_2

DDR1_CLK_N_1

DDR1_CLK_N_0

DDR1_CS_N_7/DDR1_ODT_5

DDR1_CS_N_6/DDR1_ODT_4

DDR1_CS_N_5

DDR1_CS_N_4

DDR1_CS_N_3

DDR1_CS_N_2

DDR1_CS_N_1

DDR1_CS_N_0

F35

Y4

M5

H7

F8

K34

L37

P36

AA40

G33

Y8

L6

H6

E7

L30

L35

R38

Y38

E35

Y5

M4

J7

F7

K33

K37

P37

AA41

G34

Y9

L5

G6

D7

L31

L36

R37

Y37

F26

H26

B14

E24

E23

H14

G24

E22

D22

J27

F22

K28

L28

J17

J16

J14

H27

K13

C18

H18

K18

G19

C21

H19

L18

G20

D21

E12

C14

E10

C17

E13

E15

A8

D12

CPU1_M_CH1_DQS_17_DP

CPU1_M_CH1_DQS_16_DP

CPU1_M_CH1_DQS_15_DP

CPU1_M_CH1_DQS_14_DP

CPU1_M_CH1_DQS_13_DP

CPU1_M_CH1_DQS_12_DP

CPU1_M_CH1_DQS_11_DP

CPU1_M_CH1_DQS_10_DP

CPU1_M_CH1_DQS_09_DP

CPU1_M_CH1_DQS_08_DP

CPU1_M_CH1_DQS_07_DP

CPU1_M_CH1_DQS_06_DP

CPU1_M_CH1_DQS_05_DP

CPU1_M_CH1_DQS_04_DP

CPU1_M_CH1_DQS_03_DP

CPU1_M_CH1_DQS_02_DP

CPU1_M_CH1_DQS_01_DP

CPU1_M_CH1_DQS_00_DP

CPU1_M_CH1_DQS_17_DN

CPU1_M_CH1_DQS_16_DN

CPU1_M_CH1_DQS_15_DN

CPU1_M_CH1_DQS_14_DN

CPU1_M_CH1_DQS_13_DN

CPU1_M_CH1_DQS_12_DN

CPU1_M_CH1_DQS_11_DN

CPU1_M_CH1_DQS_10_DN

CPU1_M_CH1_DQS_09_DN

CPU1_M_CH1_DQS_08_DN

CPU1_M_CH1_DQS_07_DN

CPU1_M_CH1_DQS_06_DN

CPU1_M_CH1_DQS_05_DN

CPU1_M_CH1_DQS_04_DN

CPU1_M_CH1_DQS_03_DN

CPU1_M_CH1_DQS_02_DN

CPU1_M_CH1_DQS_01_DN

CPU1_M_CH1_DQS_00_DN

CPU1_M_CH1_MA_15

CPU1_M_CH1_MA_14

CPU1_M_CH1_MA_13

CPU1_M_CH1_MA_12

CPU1_M_CH1_MA_11

CPU1_M_CH1_MA_10

CPU1_M_CH1_MA_09

CPU1_M_CH1_MA_08

CPU1_M_CH1_MA_07

CPU1_M_CH1_MA_06

CPU1_M_CH1_MA_05

CPU1_M_CH1_MA_04

CPU1_M_CH1_MA_03

CPU1_M_CH1_MA_02

CPU1_M_CH1_MA_01

CPU1_M_CH1_MA_00

CPU1_M_CH1_BA_2

CPU1_M_CH1_BA_1

CPU1_M_CH1_BA_0

CPU1_M_CH1_CK_3_DP

CPU1_M_CH1_CK_2_DP

CPU1_M_CH1_CK_1_DP

CPU1_M_CH1_CK_0_DP

CPU1_M_CH1_CK_3_DN

CPU1_M_CH1_CK_2_DN

CPU1_M_CH1_CK_1_DN

CPU1_M_CH1_CK_0_DN

CPU1_M_CH1_CS_7_N

CPU1_M_CH1_CS_6_N

CPU1_M_CH1_CS_5_N

CPU1_M_CH1_CS_4_N

CPU1_M_CH1_CS_3_N

CPU1_M_CH1_CS_2_N

CPU1_M_CH1_CS_1_N

CPU1_M_CH1_CS_0_N

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

23,24

24

23

24

23

24

23

24

23

24

24

24

24

23

23

23

23

1

2

3

4

CPU1_M_CH0_ODT_3

21

CPU1_M_CH0_ODT_2

21

CPU1_M_CH0_ODT_1

20

CPU1_M_CH0_ODT_0

20

C7

DDR0_ODT_3

B11

DDR0_ODT_2

C9

DDR0_ODT_1

F12

DDR0_ODT_0

GAINESTOWN_WESTMERE REV 2.0

HETERO 2 OF 10

DDR0_CKE_3

DDR0_CKE_2

DDR0_CKE_1

DDR0_CKE_0

DDR0_WE_N

DDR0_RAS_N

DDR0_CAS_N

DDR0_RESET_N

B31

B30

A30

C29

B13

A15

C12

D32

CPU1_M_CH0_CKE_3

CPU1_M_CH0_CKE_2

CPU1_M_CH0_CKE_1

CPU1_M_CH0_CKE_0

CPU1_M_CH0_WE_N

CPU1_M_CH0_RAS_N

CPU1_M_CH0_CAS_N

CPU1_M_CH0_RST_N

21

20

21

20

CPU1_M_CH1_ODT_3

24

20,21

20,21

20,21

20,21

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

CPU1_M_CH1_ODT_2

24

CPU1_M_CH1_ODT_1

23

CPU1_M_CH1_ODT_0

23

F11

DDR1_ODT_3

D14

DDR1_ODT_2

C8

DDR1_ODT_1

D11

DDR1_ODT_0

GAINESTOWN_WESTMERE REV 2.0

HETERO 3 OF 10

DDR1_CKE_3

DDR1_CKE_2

DDR1_CKE_1

DDR1_CKE_0

DDR1_WE_N

DDR1_RAS_N

DDR1_CAS_N

DDR1_RESET_N

C27

D27

E27

H28

G13

G14

E14

D29

CPU1_M_CH1_CKE_3

CPU1_M_CH1_CKE_2

CPU1_M_CH1_CKE_1

CPU1_M_CH1_CKE_0

CPU1_M_CH1_WE_N

CPU1_M_CH1_RAS_N

CPU1_M_CH1_CAS_N

CPU1_M_CH1_RST_N

TITLE

CPU1

DWG NO.

DATE

24

23

24

23

23,24

23,24

23,24

MODULE:

DESC:

23,24

REV: OF

INC.

SCHEM,PLN,SV,R610

RR154

CPU1

CPUS,CSI,XDP0,XDP1

SEC

4

ROUND ROCK,TEXAS

REV.

X05

SHEET

13 OF 14511/6/2008

DCBA

1

2

3

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

27

26

A B C

J_CPU1

CPU1_M_CH2_DQ63

CPU1_M_CH2_DQ62

CPU1_M_CH2_DQ61

CPU1_M_CH2_DQ60

CPU1_M_CH2_DQ59

CPU1_M_CH2_DQ58

CPU1_M_CH2_DQ57

CPU1_M_CH2_DQ56

CPU1_M_CH2_DQ55

CPU1_M_CH2_DQ54

CPU1_M_CH2_DQ53

CPU1_M_CH2_DQ52

CPU1_M_CH2_DQ51

CPU1_M_CH2_DQ50

CPU1_M_CH2_DQ49

CPU1_M_CH2_DQ48

CPU1_M_CH2_DQ47

CPU1_M_CH2_DQ46

CPU1_M_CH2_DQ45

CPU1_M_CH2_DQ44

CPU1_M_CH2_DQ43

CPU1_M_CH2_DQ42

CPU1_M_CH2_DQ41

CPU1_M_CH2_DQ40

CPU1_M_CH2_DQ39

CPU1_M_CH2_DQ38

CPU1_M_CH2_DQ37

CPU1_M_CH2_DQ36

CPU1_M_CH2_DQ35

CPU1_M_CH2_DQ34

CPU1_M_CH2_DQ33

CPU1_M_CH2_DQ32

CPU1_M_CH2_DQ31

CPU1_M_CH2_DQ30

CPU1_M_CH2_DQ29

CPU1_M_CH2_DQ28

CPU1_M_CH2_DQ27

CPU1_M_CH2_DQ26

CPU1_M_CH2_DQ25

CPU1_M_CH2_DQ24

CPU1_M_CH2_DQ23

CPU1_M_CH2_DQ22

CPU1_M_CH2_DQ21

CPU1_M_CH2_DQ20

CPU1_M_CH2_DQ19

CPU1_M_CH2_DQ18

CPU1_M_CH2_DQ17

CPU1_M_CH2_DQ16

CPU1_M_CH2_DQ15

CPU1_M_CH2_DQ14

CPU1_M_CH2_DQ13

CPU1_M_CH2_DQ12

CPU1_M_CH2_DQ11

CPU1_M_CH2_DQ10

CPU1_M_CH2_DQ09

CPU1_M_CH2_DQ08

CPU1_M_CH2_DQ07

CPU1_M_CH2_DQ06

CPU1_M_CH2_DQ05

CPU1_M_CH2_DQ04

CPU1_M_CH2_DQ03

CPU1_M_CH2_DQ02

CPU1_M_CH2_DQ01

CPU1_M_CH2_DQ00

CPU1_M_CH2_ECC_7

CPU1_M_CH2_ECC_6

CPU1_M_CH2_ECC_5

CPU1_M_CH2_ECC_4

CPU1_M_CH2_ECC_3

CPU1_M_CH2_ECC_2

CPU1_M_CH2_ECC_1

CPU1_M_CH2_ECC_0

CPU1_M_CH2_MA_PAR

NC_SCR_CPU1_M_CH2_PERR_2_N

CPU1_M_CH2_PERR_1_N

CPU1_M_CH2_PERR_0_N

U9

DDR2_DQ_63

V8

DDR2_DQ_62

T7

DDR2_DQ_61

T6

DDR2_DQ_60

U10

DDR2_DQ_59

T10

DDR2_DQ_58

U6

DDR2_DQ_57

U5

DDR2_DQ_56

R9

DDR2_DQ_55

R10

DDR2_DQ_54

N7

DDR2_DQ_53

N8

DDR2_DQ_52

P10

DDR2_DQ_51

P9

DDR2_DQ_50

N6

DDR2_DQ_49

P7

DDR2_DQ_48

M8

DDR2_DQ_47

L8

DDR2_DQ_46

M10

DDR2_DQ_45

L11

DDR2_DQ_44

N9

DDR2_DQ_43

M9

DDR2_DQ_42

K10

DDR2_DQ_41

L10

DDR2_DQ_40

L12

DDR2_DQ_39

H12

DDR2_DQ_38

G10

DDR2_DQ_37

G11

DDR2_DQ_36

L13

DDR2_DQ_35

H13

DDR2_DQ_34

J12

DDR2_DQ_33

K12

DDR2_DQ_32

E38

DDR2_DQ_31

F38

DDR2_DQ_30

G39

DDR2_DQ_29

H39

DDR2_DQ_28

H37

DDR2_DQ_27

J37

DDR2_DQ_26

F40

DDR2_DQ_25

G40

DDR2_DQ_24

K38

DDR2_DQ_23

L40

DDR2_DQ_22

N36

DDR2_DQ_21

P40

DDR2_DQ_20

J39

DDR2_DQ_19

J40

DDR2_DQ_18

M40

DDR2_DQ_17

M39

DDR2_DQ_16

R40

DDR2_DQ_15

T41

DDR2_DQ_14

V39

DDR2_DQ_13

W39

DDR2_DQ_12

T36

DDR2_DQ_11

R39

DDR2_DQ_10

U39

DDR2_DQ_9

U38

DDR2_DQ_8

V38

DDR2_DQ_7

V37

DDR2_DQ_6

V34

DDR2_DQ_5

U34

DDR2_DQ_4

U36

DDR2_DQ_3

V36

DDR2_DQ_2

W35

DDR2_DQ_1

W34

DDR2_DQ_0

F30

DDR2_ECC_7

F31

DDR2_ECC_6

J30

DDR2_ECC_5

J31

DDR2_ECC_4

E30

DDR2_ECC_3

E29

DDR2_ECC_2

F33

DDR2_ECC_1

H32

DDR2_ECC_0

B18

DDR2_MA_PAR

F23

DDR2_PAR_ERR_N_2

J25

DDR2_PAR_ERR_N_1

F21

DDR2_PAR_ERR_N_0

DDR2_DQS_P_17

DDR2_DQS_P_16

DDR2_DQS_P_15

DDR2_DQS_P_14

DDR2_DQS_P_13

DDR2_DQS_P_12

DDR2_DQS_P_11

DDR2_DQS_P_10

DDR2_DQS_P_9

DDR2_DQS_P_8

DDR2_DQS_P_7

DDR2_DQS_P_6

DDR2_DQS_P_5

DDR2_DQS_P_4

DDR2_DQS_P_3

DDR2_DQS_P_2

DDR2_DQS_P_1

DDR2_DQS_P_0

DDR2_DQS_N_17

DDR2_DQS_N_16

DDR2_DQS_N_15

DDR2_DQS_N_14

DDR2_DQS_N_13

DDR2_DQS_N_12

DDR2_DQS_N_11

DDR2_DQS_N_10

DDR2_DQS_N_9

DDR2_DQS_N_8

DDR2_DQS_N_7

DDR2_DQS_N_6

DDR2_DQS_N_5

DDR2_DQS_N_4

DDR2_DQS_N_3

DDR2_DQS_N_2

DDR2_DQS_N_1

DDR2_DQS_N_0

DDR2_MA_15

DDR2_MA_14

DDR2_MA_13

DDR2_MA_12

DDR2_MA_11

DDR2_MA_10

DDR2_MA_9

DDR2_MA_8

DDR2_MA_7

DDR2_MA_6

DDR2_MA_5

DDR2_MA_4

DDR2_MA_3

DDR2_MA_2

DDR2_MA_1

DDR2_MA_0

DDR2_BA_2

DDR2_BA_1

DDR2_BA_0

DDR2_CLK_P_3

DDR2_CLK_P_2

DDR2_CLK_P_1

DDR2_CLK_P_0

DDR2_CLK_N_3

DDR2_CLK_N_2

DDR2_CLK_N_1

DDR2_CLK_N_0

DDR2_CS_N_7/DDR2_ODT_5

DDR2_CS_N_6/DDR2_ODT_4

DDR2_CS_N_5

DDR2_CS_N_4

DDR2_CS_N_3

DDR2_CS_N_2

DDR2_CS_N_1

DDR2_CS_N_0

H31

V6

N4

K9

H11

H38

M38

U40

U35

G29

U8

P6

L7

J10

E39

K40

T37

W37

G31

V7

P4

K8

J11

G38

L38

T40

T35

G30

T8

P5

K7

J9

E40

K39

T38

W36

G25

H24

F15

G23

H23

H17

H22

L25

J24

K22

K23

F20

J20

G18

K17

A18

L26

F17

A17

L22

H21

L20

J22

L21

G21

K20

J21

J15

L17

D9

E17

H16

D16

K14

G16

CPU1_M_CH2_DQS_17_DP

CPU1_M_CH2_DQS_16_DP

CPU1_M_CH2_DQS_15_DP

CPU1_M_CH2_DQS_14_DP

CPU1_M_CH2_DQS_13_DP

CPU1_M_CH2_DQS_12_DP

CPU1_M_CH2_DQS_11_DP

CPU1_M_CH2_DQS_10_DP

CPU1_M_CH2_DQS_09_DP

CPU1_M_CH2_DQS_08_DP

CPU1_M_CH2_DQS_07_DP

CPU1_M_CH2_DQS_06_DP

CPU1_M_CH2_DQS_05_DP

CPU1_M_CH2_DQS_04_DP

CPU1_M_CH2_DQS_03_DP

CPU1_M_CH2_DQS_02_DP

CPU1_M_CH2_DQS_01_DP

CPU1_M_CH2_DQS_00_DP

CPU1_M_CH2_DQS_17_DN

CPU1_M_CH2_DQS_16_DN

CPU1_M_CH2_DQS_15_DN

CPU1_M_CH2_DQS_14_DN

CPU1_M_CH2_DQS_13_DN

CPU1_M_CH2_DQS_12_DN

CPU1_M_CH2_DQS_11_DN

CPU1_M_CH2_DQS_10_DN

CPU1_M_CH2_DQS_09_DN

CPU1_M_CH2_DQS_08_DN

CPU1_M_CH2_DQS_07_DN

CPU1_M_CH2_DQS_06_DN

CPU1_M_CH2_DQS_05_DN

CPU1_M_CH2_DQS_04_DN

CPU1_M_CH2_DQS_03_DN

CPU1_M_CH2_DQS_02_DN

CPU1_M_CH2_DQS_01_DN

CPU1_M_CH2_DQS_00_DN

CPU1_M_CH2_MA_15

CPU1_M_CH2_MA_14

CPU1_M_CH2_MA_13

CPU1_M_CH2_MA_12

CPU1_M_CH2_MA_11

CPU1_M_CH2_MA_10

CPU1_M_CH2_MA_09

CPU1_M_CH2_MA_08

CPU1_M_CH2_MA_07

CPU1_M_CH2_MA_06

CPU1_M_CH2_MA_05

CPU1_M_CH2_MA_04

CPU1_M_CH2_MA_03

CPU1_M_CH2_MA_02

CPU1_M_CH2_MA_01

CPU1_M_CH2_MA_00

CPU1_M_CH2_BA_2

CPU1_M_CH2_BA_1

CPU1_M_CH2_BA_0

CPU1_M_CH2_CK_3_DP

CPU1_M_CH2_CK_2_DP

CPU1_M_CH2_CK_1_DP

CPU1_M_CH2_CK_0_DP

CPU1_M_CH2_CK_3_DN

CPU1_M_CH2_CK_2_DN

CPU1_M_CH2_CK_1_DN

CPU1_M_CH2_CK_0_DN

CPU1_M_CH2_CS_7_N

CPU1_M_CH2_CS_6_N

CPU1_M_CH2_CS_5_N

CPU1_M_CH2_CS_4_N

CPU1_M_CH2_CS_3_N

CPU1_M_CH2_CS_2_N

CPU1_M_CH2_CS_1_N

CPU1_M_CH2_CS_0_N

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

26,27

27

26

27

26

27

26

27

26

27

27

27

27

26

26

26

26

IN to CPU

OUT to XDP

DBR not used with XDP

16,31,33,46,52

16,94

16,94

16

16,94

94,95

16

16

16

16

31,33

16

47

47

46

46

16

16,94

16,94

16,116

16

16

116

17

17

122

122

46

46

46

46

46

46

46

46

46

46

31,46

31,46

31,46

46

46

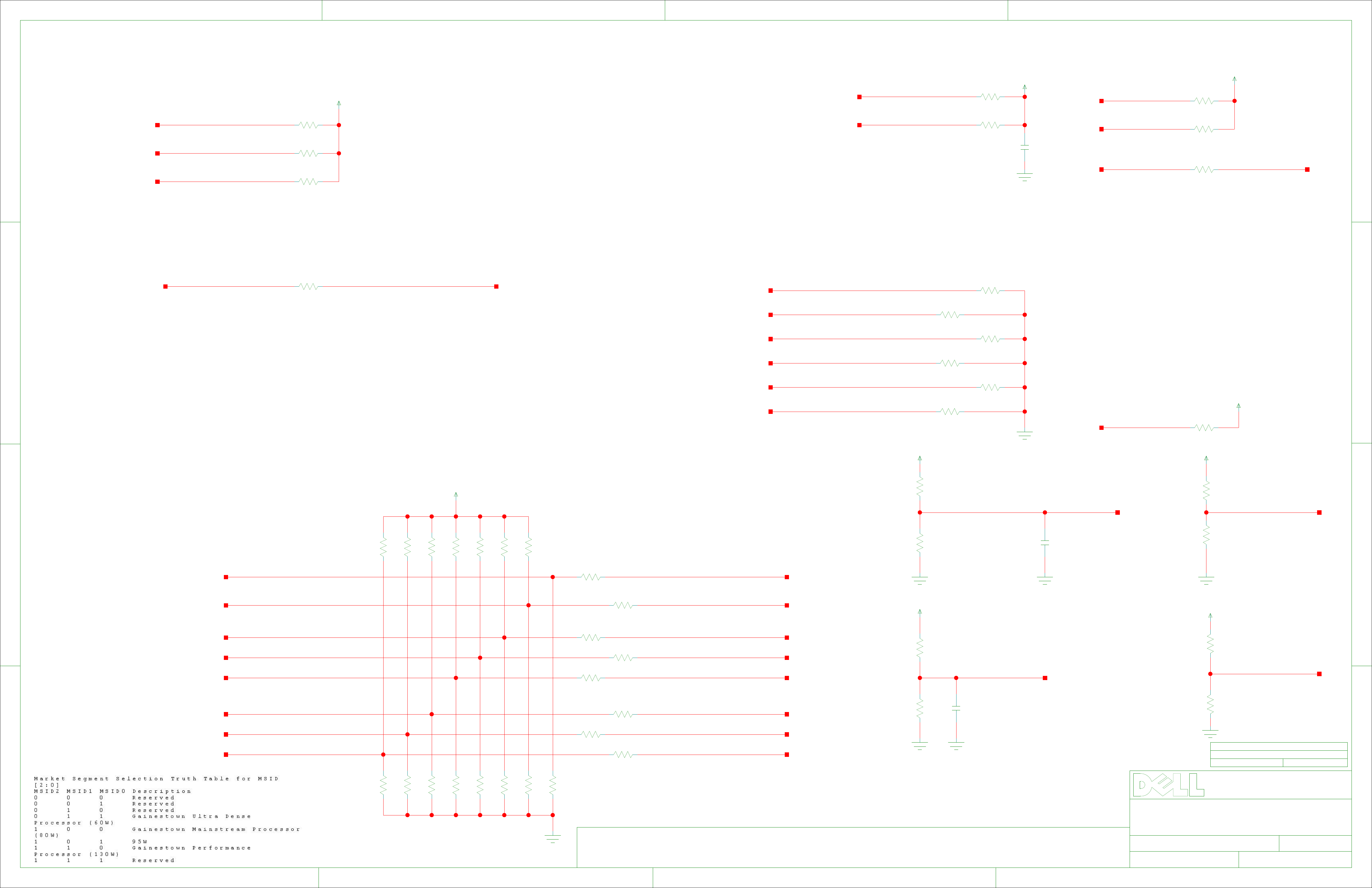

CPU_RST_N

CPU1_CAT_ERR_N

CPU1_THERMTRIP_N

CPU1_PROCHOT_N

CPU1_PRES_N

CPU1_CPLD_EVENT_N

MOD_CPU_CPU1_COMP_SOUTH_0

MOD_CPU_CPU1_M_DDR_COMP_2

MOD_CPU_CPU1_M_DDR_COMP_1

MOD_CPU_CPU1_M_DDR_COMP_0

PECI_CPU

MOD_CPU_PECI_CPU1_ID_N

CK_133M_CPU1_DP

CK_133M_CPU1_DN

MOD_CPU_CK_133M_CPU1_ITP_DP

MOD_CPU_CK_133M_CPU1_ITP_DN

MOD_CPU_VCORE_CPU1_GTL_PG

MEM_CPU1_GTL_PG

VTT_CPU1_GTL_PG

MOD_CPU_VCORE_CPU1_VID_7

16

MOD_CPU_VCORE_CPU1_VID_6

16

MOD_CPU_VCORE_CPU1_VID_5

16

MOD_CPU_VCORE_CPU1_VID_4

16

MOD_CPU_VCORE_CPU1_VID_3

16

VCORE_CPU1_VID_2

16

VCORE_CPU1_VID_1

16

VCORE_CPU1_VID_0

16

VTT_CPU1_VID_2

122

VTT_CPU1_VID_1

122

VTT_CPU1_VID_0

122

MOD_CPU_CPU1_PSI_N

MOD_CPU_CPU1_DDR3_VREF

MOD_CPU_CPU1_GTL_VREF

CPU1_ISENSE

MOD_CPU_VCORE_CPU1_SENSE_P

MOD_CPU_VCORE_CPU1_SENSE_N

VTT_CPU1_SENSE_P

VTT_CPU1_SENSE_N

TP_MOD_CPU_DBR_CPU1_N

MOD_CPU_XDP_CPU1_PRDY_N

MOD_CPU_XDP_CPU1_PREQ_N

MOD_CPU_XDP_CPU1_BPM_7_N

MOD_CPU_XDP_CPU1_BPM_6_N

MOD_CPU_XDP_CPU1_BPM_5_N

MOD_CPU_XDP_CPU1_BPM_4_N

MOD_CPU_XDP_CPU1_BPM_3_N

MOD_CPU_XDP_CPU1_BPM_2_N

MOD_CPU_XDP_CPU1_BPM_1_N

MOD_CPU_XDP_CPU1_BPM_0_N

MOD_CPU_JTAG_CPU_TRST_N

MOD_CPU_JTAG_CPU_TCK

MOD_CPU_JTAG_CPU_TMS

MOD_CPU_JTAG_CPU1_TDI

MOD_CPU_JTAG_CPU1_TDO

AL39

RESET_N

AC37

CAT_ERR_N

AG37

THERMTRIP_N

AG35

PROCHOT_N

AG36

SKTOCC_N

AB5

DDR_THERM_N

AB41

COMP0

AC1

DDR_COMP_2

Y7

DDR_COMP_1

AA8

DDR_COMP_0

AH36

PECI

AK35

PECI_ID_N/ODT

AJ35

BCLK_DP

AH35

BCLK_DN

AA5

BCLK_ITP_DP

AA4

BCLK_ITP_DN

AR7

VCCPWRGOOD

AA6

VDDPWRGOOD

AB35

VTTPWRGOOD

AN8

VID_7

AP8

VID_6

AP9

VID5_CSC_2

AN10

VID4_CSC_1

AM10

VID3_CSC_0

AN9

VID2_MSID_2

AL9

VID1_MSID_1

AL10

VID0_MSID_0

AV6

VTT_VID_4

AF7

VTT_VID_3

AV3

VTT_VID_2

AP7

PSI_N

L23

DDR_VREF

AJ37

GTLREF

AK8

ISENSE

AR9

VCC_SENSE

AR8

VSS_SENSE

AE36

VTTD_SENSE

AE37

VSS_SENSE_VTTD

AF10

DBR_N

B41

PRDY_N

C42

PREQ_N

E2

BPM_N_7

D2

BPM_N_6

C3

BPM_N_5

D1

BPM_N_4

B4

BPM_N_3

C2

BPM_N_2

A5

BPM_N_1

B3

BPM_N_0

AH9

TRST_N

AH10

TCK

AG10

TMS

AJ9

TDI

AJ10

TDO

GAINESTOWN_WESTMERE REV 2.0

J_CPU1

Ball L23 is DDR_VREF in Intel CRB

DDR_THERM2_N

TAPPWRGOOD

HETERO 5 OF 10

RSVD_66

RSVD_65

RSVD_64

RSVD_63

RSVD_62

RSVD_61

RSVD_60

RSVD_59

RSVD_58

RSVD_57

RSVD_56

RSVD_55

RSVD_54

RSVD_53

RSVD_52

RSVD_51

RSVD_50

RSVD_49

RSVD_48

RSVD_47

RSVD_46

RSVD_45

RSVD_44

RSVD_43

RSVD_42

RSVD_41

RSVD_40

RSVD_39

RSVD_38

RSVD_37

RSVD_36

RSVD_35

RSVD_34

RSVD_32

RSVD_31

RSVD_30

RSVD_29

RSVD_28

RSVD_27

RSVD_26

RSVD_25

RSVD_24

RSVD_23

RSVD_22

RSVD_21

RSVD_20

RSVD_19

RSVD_15

RSVD_14

RSVD_12

RSVD_11

RSVD_10

RSVD_9

RSVD_8

RSVD_7

RSVD_6

RSVD_5

RSVD_3

RSVD_2

RSVD_1

RSVD_0

D

B33

F27

K25

K27

D30

K29

J29

G28

H29

E28

F28

A31

C32

C31

D31

AL3

AL38

AG1

AF1

AK7

AT5

AT4

V11

U11

A40

AL4

AL5

AL41

AL40

K24

AK36

K15

L15

AU2

BA40

AY40

AW41

AY41

AW42

AV43

AV42

AV1

AY3

AW2

AV2

AY4

BA4

AF4

NOTE: not implementing THERM2 method for Westmere, using PECI interface

AG4

AG5

AH5

AK2

AM36

AM38

AN36

AN38

AR36

AR37

AT36

AV35

AW39

AY35

AY39

NC_J_CPU1_B33

NC_J_CPU1_F27

NC_J_CPU1_K25

NC_J_CPU1_K27

NC_J_CPU1_D30

NC_J_CPU1_K29

NC_J_CPU1_J29

NC_J_CPU1_G28

NC_J_CPU1_H29

NC_J_CPU1_E28

NC_J_CPU1_F28

NC_J_CPU1_A31

NC_J_CPU1_C32

NC_J_CPU1_C31

NC_J_CPU1_D31

NC_J_CPU1_AL3

NC_J_CPU1_AL38

NC_J_CPU1_AG1

NC_J_CPU1_AF1

NC_J_CPU1_AK7

NC_J_CPU1_AT5

NC_J_CPU1_AT4

NC_J_CPU1_V11

NC_J_CPU1_U11

NC_J_CPU1_A40

NC_J_CPU1_AL4

NC_J_CPU1_AL5

NC_J_CPU1_AL41

NC_J_CPU1_AL40

NC_J_CPU1_K24

NC_J_CPU1_AK36

NC_J_CPU1_K15

NC_J_CPU1_L15

NC_J_CPU1_AU2

NC_J_CPU1_BA40

NC_J_CPU1_AY40

NC_J_CPU1_AW41

NC_J_CPU1_AY41

NC_J_CPU1_AW42

NC_J_CPU1_AV43

NC_J_CPU1_AV42

NC_J_CPU1_AV1

NC_J_CPU1_AY3

NC_J_CPU1_AW2

NC_J_CPU1_AV2

NC_J_CPU1_AY4

NC_J_CPU1_BA4

J_CPU1_TESTHI_AF4

NC_J_CPU1_AG4

NC_J_CPU1_AG5

CPU_TAPPWRGOOD

NC_J_CPU1_AK2

NC_J_CPU1_AM36

NC_J_CPU1_AM38

NC_J_CPU1_AN36

NC_J_CPU1_AN38

NC_J_CPU1_AR36

NC_J_CPU1_AR37

NC_J_CPU1_AT36

NC_J_CPU1_AV35

NC_J_CPU1_AW39

NC_J_CPU1_AY35

NC_J_CPU1_AY39

1

2

16

31,46

3

4

27

27

26

26

CPU1_M_CH2_ODT_3

CPU1_M_CH2_ODT_2

CPU1_M_CH2_ODT_1

CPU1_M_CH2_ODT_0

D10

DDR2_ODT_3

D15

DDR2_ODT_2

F13

DDR2_ODT_1

L16

DDR2_ODT_0

GAINESTOWN_WESTMERE REV 2.0

HETERO 4 OF 10

DDR2_CKE_3

DDR2_CKE_2

DDR2_CKE_1

DDR2_CKE_0

DDR2_WE_N

DDR2_RAS_N

DDR2_CAS_N

DDR2_RESET_N

L27

D26

G26

J26

C16

D17

F16

E32

CPU1_M_CH2_CKE_3

CPU1_M_CH2_CKE_2

CPU1_M_CH2_CKE_1

CPU1_M_CH2_CKE_0

CPU1_M_CH2_WE_N

CPU1_M_CH2_RAS_N

CPU1_M_CH2_CAS_N

CPU1_M_CH2_RST_N

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

27

26

27

26

26,27

26,27

26,27

26,27

CPU1

TITLE

DWG NO.

DATE

MODULE:

DESC:

REV: OF

INC.

SCHEM,PLN,SV,R610

RR154

CPU1

CPUS,CSI,XDP0,XDP1

SEC

4

ROUND ROCK,TEXAS

REV.

X05

SHEET

14 OF 14511/6/2008

DCBA

A B C

D

CPU1

1

2

3

+MEM_CPU1

A14

A19

A24

A29

A9

B12

B17

B22

B27

B32

B7

C10

C15

C20

C25

C30

D13

D18

D23

D28

E11

E16

E21

E26

E31

F14

F19

F24

G17

G22

G27

H15

H20

H25

J18

J23

J28

K16

K21

K26

L14

L19

L24

M17

V_1V8_CPU1

18,115,141,144

NET_PHYSICAL_TYPE=PWR_PNG

M27

U33

V33

W33

VDDQ_44

VDDQ_43

VDDQ_42

VDDQ_41

VDDQ_40

VDDQ_39

VDDQ_38

VDDQ_37

VDDQ_36

VDDQ_35

VDDQ_34

VDDQ_33

VDDQ_32

VDDQ_31

VDDQ_30

VDDQ_29

VDDQ_28

VDDQ_27

VDDQ_26

VDDQ_25

VDDQ_24

VDDQ_23

VDDQ_22

VDDQ_21

VDDQ_20

VDDQ_19

VDDQ_18

VDDQ_17

VDDQ_16

VDDQ_15

VDDQ_14

VDDQ_13

VDDQ_12

VDDQ_11

VDDQ_10

VDDQ_9

VDDQ_8

VDDQ_7

VDDQ_6

VDDQ_5

VDDQ_4

VDDQ_3

VDDQ_2

VDDQ_1

VDDQ_0

VCCPLL_2

VCCPLL_1

VCCPLL_0

GAINESTOWN_WESTMERE REV 2.0

J_CPU1

HETERO 6 OF 10

VTTD_25

VTTD_24

VTTD_23

VTTD_22

VTTD_21

VTTD_20

VTTD_19

VTTD_18

VTTD_17

VTTD_16

VTTD_15

VTTD_14

VTTD_13

VTTD_12

VTTD_11

VTTD_10

VTTD_9

VTTD_8

VTTD_7

VTTD_6

VTTD_5

VTTD_4

VTTD_3

VTTD_2

VTTD_1

VTTD_0

VTTA_7

VTTA_6

VTTA_5

VTTA_4

VTTA_3

VTTA_2

VTTA_1

VTTA_0

AF37

AA10

AA11

AA33

AB10

AB11

AB33

AB34

AB8

AB9

AC10

AC11

AC33

AC34

AC35

AD34

AD35

AD36

AD9

AE34

AE35

AE8

AE9

AF36

AF8

AF9

AG34

AF34

AF33

AF11

AE33

AE11

AE10

AD10

+VTT_CPU1

J_CPU1

AH11

VCC_209

AH33

VCC_208

AJ11

VCC_207

AJ33

VCC_206

AK11

VCC_205

AK12

VCC_204

AK13

VCC_203

AK15

VCC_202

AK16

VCC_201

AK18

VCC_200

AK19

VCC_199

AK21

VCC_198

AK24

VCC_197

AK25

VCC_196

AK27

VCC_195

AK28

VCC_194

AK30

VCC_193

AK31

VCC_192

AK33

VCC_191

AL12

VCC_190

AL13

VCC_189

AL15

VCC_188

AL16

VCC_187

AL18

VCC_186

AL19

VCC_185

AL21

VCC_184

AL24

VCC_183

AL25

VCC_182

AL27

VCC_181

AL28

VCC_180

AL30

VCC_179

AL31

VCC_178

AL33

VCC_177

AL34

VCC_176

AM12

VCC_175

AM13

VCC_174

AM15

VCC_173

AM16

VCC_172

AM18

VCC_171

AM19

VCC_170

AM21

VCC_169

AM24

VCC_168

AM25

VCC_167

AM27

VCC_166

AM28

VCC_165

AM30

VCC_164

AM31

VCC_163

AM33

VCC_162

AM34

VCC_161

AN12

VCC_160

AN13

VCC_159

AN15

VCC_158

AN16

VCC_157

GAINESTOWN_WESTMERE REV 2.0

HETERO 7 OF 10

VCC_156

VCC_155

VCC_154

VCC_153

VCC_152

VCC_151

VCC_150

VCC_149

VCC_148

VCC_147

VCC_146

VCC_145

VCC_144

VCC_143

VCC_142

VCC_141

VCC_140

VCC_139

VCC_138

VCC_137

VCC_136

VCC_135

VCC_134

VCC_133

VCC_132

VCC_131

VCC_130

VCC_129

VCC_128

VCC_127

VCC_126

VCC_125

VCC_124

VCC_123

VCC_122

VCC_121

VCC_120

VCC_119

VCC_118

VCC_117

VCC_116

VCC_115

VCC_114

VCC_113

VCC_112

VCC_111

VCC_110

VCC_109

VCC_108

VCC_107

VCC_106

VCC_105

VCC_104

AN18

AN19

AN21

AN24

AN25

AN27

AN28

AN30

AN31

AN33

AN34

AP12

AP13

AP15

AP16

AP18

AP19

AP21

AP24

AP25

AP27

AP28

AP30

AP31

AP33

AP34

AR10

AR12

AR13

AR15

AR16

AR18

AR19

AR21

AR24

AR25

AR27

AR28

AR30

AR31

AR33

AR34

AT10

AT12

AT13

AT15

AT16

AT18

AT19

AT21

AT24

AT25

AT27

J_CPU1

Y6

VSS_309

Y41

VSS_308

Y36

VSS_307

Y33

VSS_306

Y11

VSS_305

Y1

+VCORE_CPU1 +VCORE_CPU1+VCORE_CPU1 +VCORE_CPU1

J_CPU1

AT28

AT30

AT31

AT33

AT34

AT9

AU10

AU12

AU13

AU15

AU16

AU18

AU19

AU21

AU24

AU25

AU27

AU28

AU30

AU31

AU33

AU34

AU9

AV10

AV12

AV13

AV15

AV16

AV18

AV19

AV21

AV24

AV25

AV27

AV28

AV30

AV31

AV33

AV34

AV9

AW10

AW12

AW13

AW15

AW16

AW18

AW19

AW21

AW24

AW25

AW27

AW28

VCC_103

VCC_102

VCC_101

VCC_100

VCC_99

VCC_98

VCC_97

VCC_96

VCC_95

VCC_94

VCC_93

VCC_92

VCC_91

VCC_90

VCC_89

VCC_88

VCC_87

VCC_86

VCC_85

VCC_84

VCC_83

VCC_82

VCC_81

VCC_80

VCC_79

VCC_78

VCC_77

VCC_76

VCC_75

VCC_74

VCC_73

VCC_72

VCC_71

VCC_70

VCC_69

VCC_68

VCC_67

VCC_66

VCC_65

VCC_64

VCC_63

VCC_62

VCC_61

VCC_60

VCC_59

VCC_58

VCC_57

VCC_56

VCC_55

VCC_54

VCC_53

VCC_52

GAINESTOWN_WESTMERE REV 2.0

HETERO 8 OF 10

VCC_51

VCC_50

VCC_49

VCC_48

VCC_47

VCC_46

VCC_45

VCC_44

VCC_43

VCC_42

VCC_41

VCC_40

VCC_39

VCC_38

VCC_37

VCC_36

VCC_35

VCC_34

VCC_33

VCC_32

VCC_31

VCC_30

VCC_29

VCC_28

VCC_27

VCC_26

VCC_25

VCC_24

VCC_23

VCC_22

VCC_21

VCC_20

VCC_19

VCC_18

VCC_17

VCC_16

VCC_15

VCC_14

VCC_13

VCC_12

VCC_11

VCC_10

VCC_9

VCC_8

VCC_7

VCC_6

VCC_5

VCC_4

VCC_3

VCC_2

VCC_1

VCC_0

AW30

AW31

AW33

AW34

AW9

AY10

AY12

AY13

AY15

AY16

AY18

AY19

AY21

AY24

AY25

AY27

AY28

AY30

AY31

AY33

AY34

AY9

BA10

BA12

BA13

BA15

BA16

BA18

BA19

BA24

BA25

BA27

BA28

BA30

BA9

M11

M13

M15

M19

M21

M23

M25

M29

M31

M33

N11

N33

R11

R33

T11

T33

W11

W8

W43

W38

W3

V5

V40

V35

V10

U7

U42

U37

U2

T9

T4

T39

T34

R6

R41

R36

R1

P8

P43

P38

P33

P3

P11

N5

N40

N35

N10

M7

M42

M37

M32

M30

M28

M26

M24

M22

M20

M2

M18

M16

M14

M12

L9

L4

L39

L34

L29

K6

K41

K36

K31

K11

K1

J8

J43

J38

J33

J3

J13

H5

H40

H35

H30

H10

G7

G42

G37

G32

G2

G12

VSS_304

VSS_303

VSS_302

VSS_301

VSS_300

VSS_299

VSS_298

VSS_297

VSS_296

VSS_295

VSS_294

VSS_293

VSS_292

VSS_291

VSS_290

VSS_289

VSS_288

VSS_287

VSS_286

VSS_285

VSS_284

VSS_283

VSS_282

VSS_281

VSS_280

VSS_279

VSS_278

VSS_277

VSS_276

VSS_275

VSS_274

VSS_273

VSS_272

VSS_271

VSS_270

VSS_269

VSS_268

VSS_267

VSS_266

VSS_265

VSS_264

VSS_263

VSS_262

VSS_261

VSS_260

VSS_259

VSS_258

VSS_257

VSS_256

VSS_255

VSS_254

VSS_253

VSS_252

VSS_251

VSS_250

VSS_249

VSS_248

VSS_247

VSS_246

VSS_245

VSS_244

VSS_243

VSS_242

VSS_241

VSS_240

VSS_239

VSS_238

VSS_237

VSS_236

VSS_235

VSS_234