MSI MS-91A2 91A2 0a_0112001

5

D D

4

3

2

1

MS-91A2

CPU:

Intel Pentium 4, Pentium D, Core2 Duo, Wolfdale, Kentsfield

Version: 0A

and Yorkfield processors in LGA775 Package.

Main Chipset:

North Bridge

South Bridge

C C

:

Intel Bigby /V

:

Intel ICH9

On Board Device:

:

CLOCK Gen

LPC Super I/O

:

LAN

Intel_82575

IDE Controller

Cypress_CY505YC64DT+Cypress_CY23S05SXC-1H

:

Winbond_W83627EHG

:

JMB368

PCIE Switch:PLX 8525

Main Memory:

Unbuffered Dual-channel DDR-II 667 or 800 MHz * 2 with ECC and non-ECC

B B

Expansion Slots:

PCI X4 SLOT *2 (X4 Signal for Golden Finger)

Mini PCI SLOT * 1

PWM:

A A

5

Intersil ISL6322CRZ+ICS9DB104BFLF

4

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

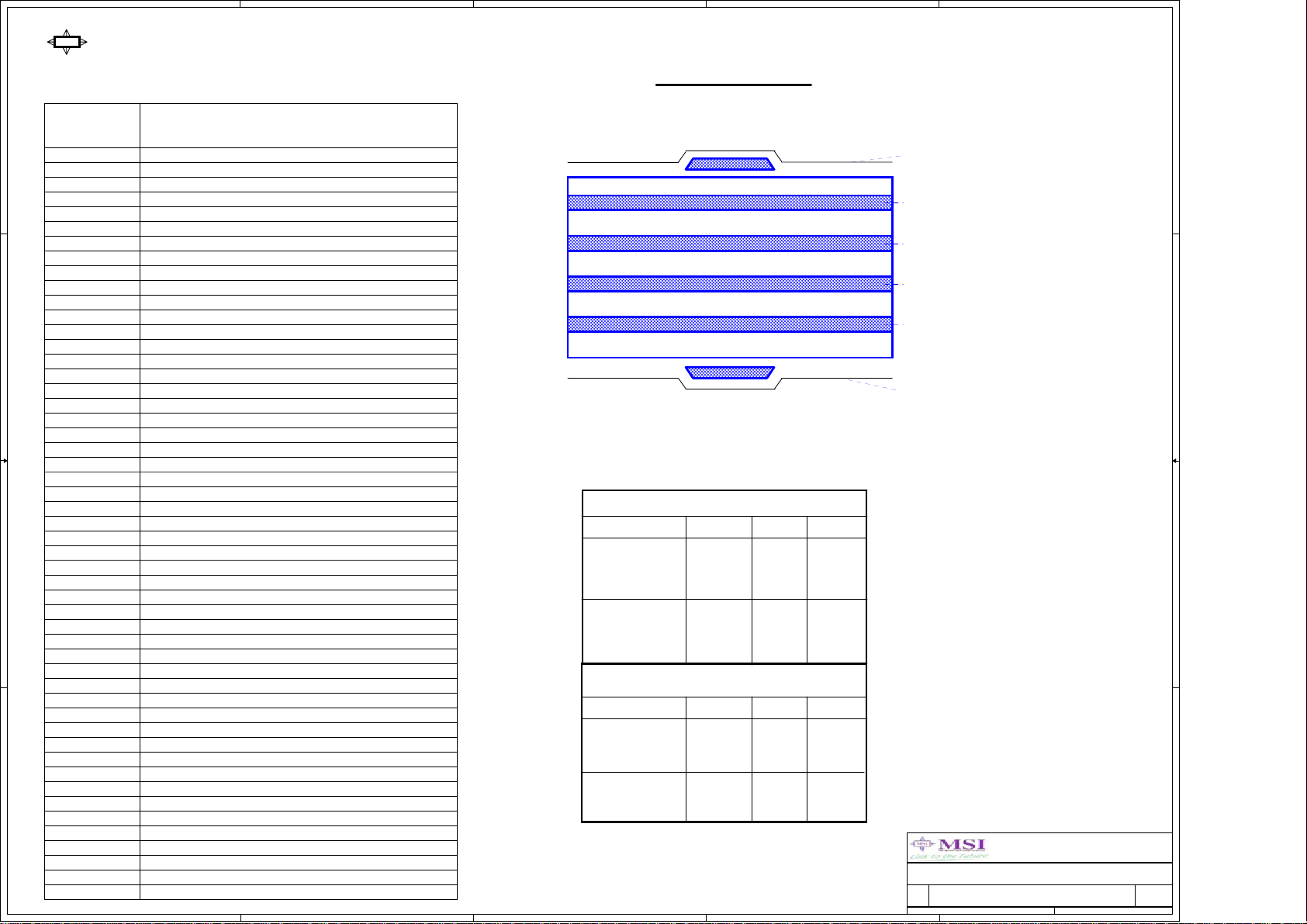

Cover Sheet

Cover Sheet

Cover Sheet

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

161Wednesday, November 14, 2007

of

161Wednesday, November 14, 2007

of

161Wednesday, November 14, 2007

5

MSI

MS-91A2 Rev0A

4

3

2

1

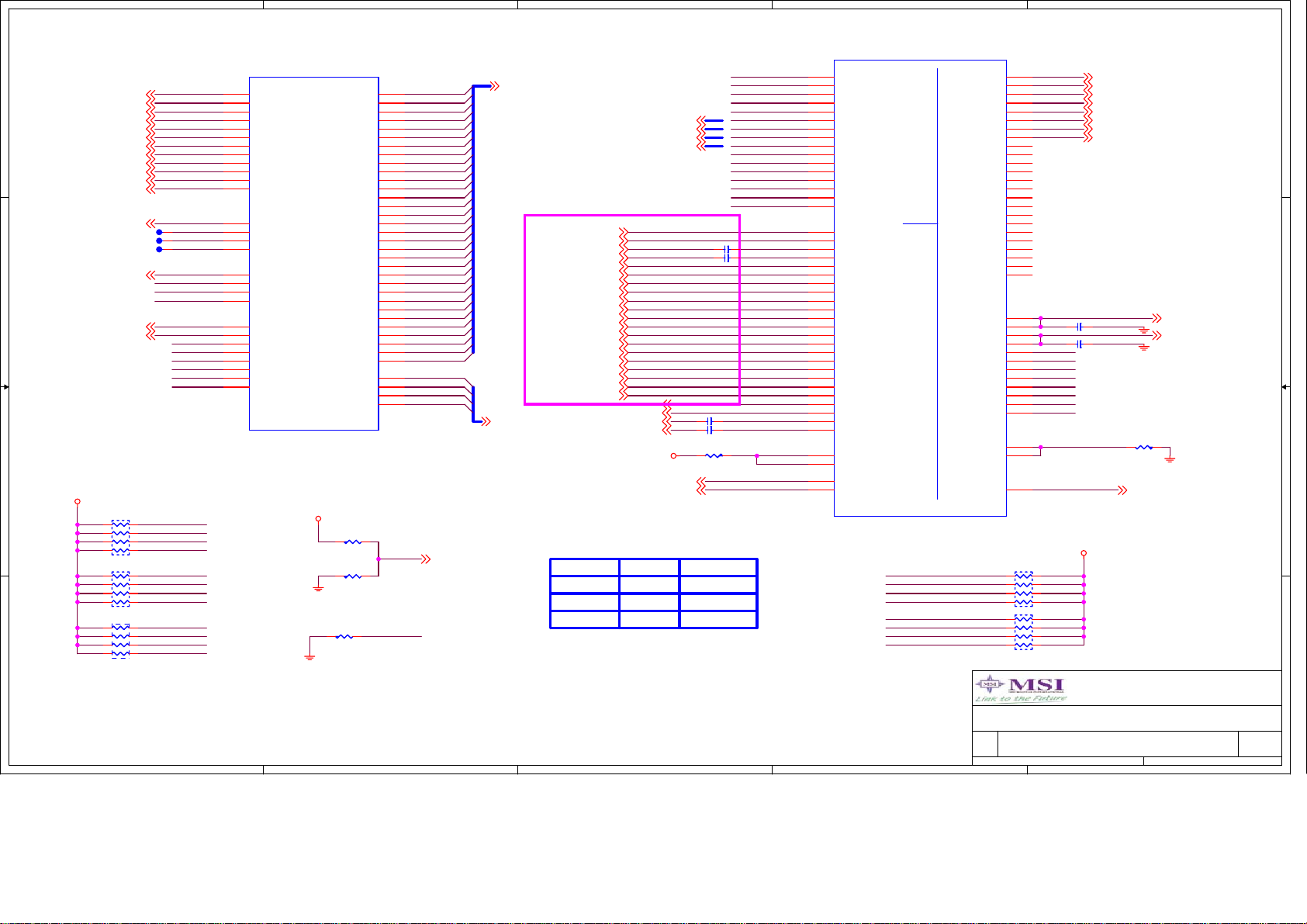

BB-P/V + ICH9 Schematics

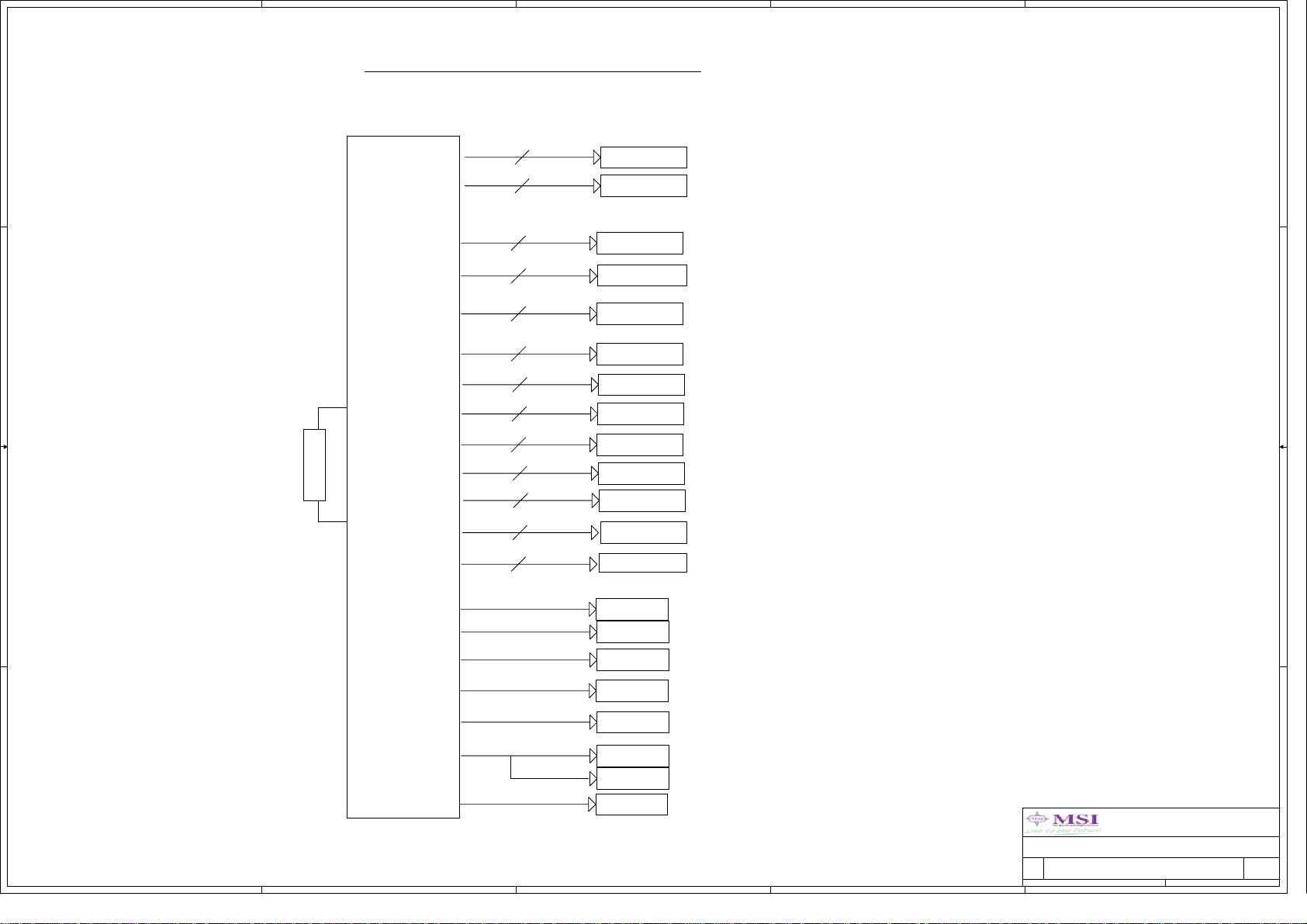

Table of Contents

D D

Page

01

02

03

04

05

06

07

08

10

11

12

C C

14

15

16

17

18

19

20

21

22

23

24

25

26

27~28

29~31

B B

32~34

35~37

38

39

40

41

42

43

44

45

46

47

48~50

51

52

53

A A

54

55

56

57

58

59

60 Revision & History

5

Title

Cover / Table of Contents

Table of Contents

System Block Diagram

Power map

Power on diagram

CLOCK BLOCK DIAGRAM

SMBus rounting

GPIO Setting / PCI Routing

CPU_LGA775_Signal09

CPU_LGA775_Power

CPU_LGA775_GND

MCH_Bigby_PCIE & DMI

MCH_Bigby_FSB13

MCH_Bigby_DDR2

MCH_Bigby_Miscellaneous

MCH_Bigby_Power

MCH_Bigby_Ground

ICH9_PCIE & USB & DMI & PCI

ICH9_Host & SATA & MSIC

ICH9_Power, GND

DDR2 Channel A

DDR2 Channel B

DDR2_Termination&Decoupling

PLX_PEX8525AA STN0

PLX_PEX8525AA STN1

PLX_PEX8252AA PWR/STRAP

PEX8525AA_Power-1.0V

LAN_82575 I with Bypass Function

LAN_82575 II with Bypass Function

LAN_82575 III with SFP Function

LAN Power-1.8V/1.0V

BYPASS CONTROL

LAN_82566DM IV

GOLDEN_FINGER

Mini PCI

Clock generator_CY505YC64C

Super IO_Winbond 83627DHG

COM port & KBMS

USB&SATA

JMB368 to IDE/ CF

XGI Z7 VGA

Power Connector&Front Panel

Power Sequence&DUAL power

Power Reset & SMBus

VRD11_ISL6322

MCH Core Power & DDR2 Power

ICH Core Power & FSB_VTT

FAN

GPIO BUFFER

Manual & Option parts

Solder Mask

L1

L2

L3

L4

L5

L6

Solder Mask

Target Actual Line Space

50ohms

95ohms-diff

Target Actual Line Space

50ohms

95ohms-diff

4

3

Board Stack-up

62+8/-5mils

PREPREG 2.7mils

CORE 4mils

PREPREG 40mils

CORE 4mils

PREPREG 2.7mils

Outer Impedances

48.60

93.18

Inner Impedances

49.78

93.54

4.0

4.0

5.0 N/A

4.0

N/A

8.0

8.0

2

0.65mils Solder Mask

1.5 oz. (1.9mils) Cu plus plating

1 oz. (1.2mils) Cu GND Plane

1 oz. (1.2mils) Cu INT3 Plane

1 oz. (1.2mils) Cu Power Plane

1 oz. (1.2mils) Cu Power Plane

1.5 oz. (1.9mils) Cu plus plating

0.65mils Solder Mask

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Table of Contents

Table of Contents

Table of Contents

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

261Wednesday, November 14, 2007

261Wednesday, November 14, 2007

261Wednesday, November 14, 2007

5

4

3

2

1

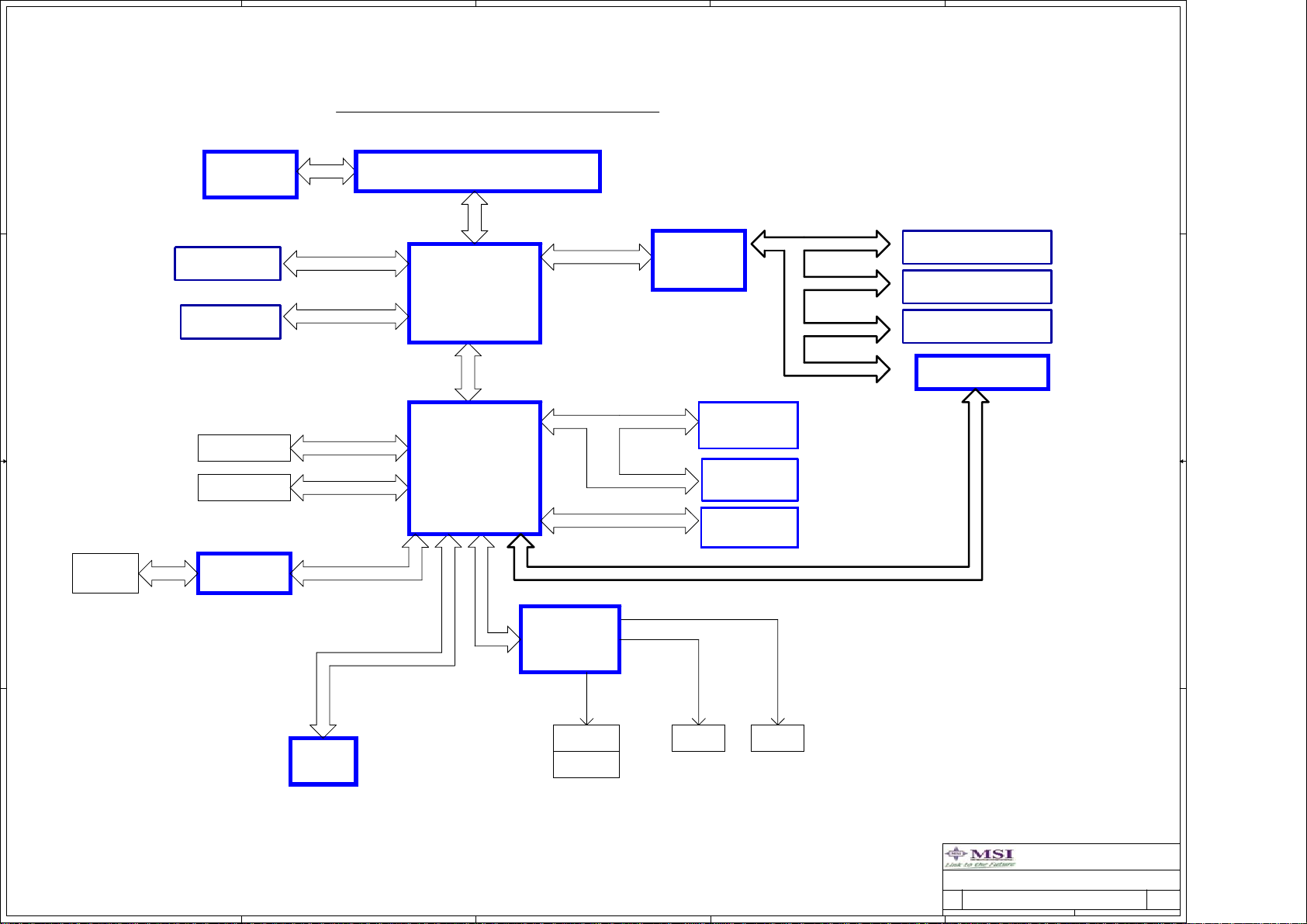

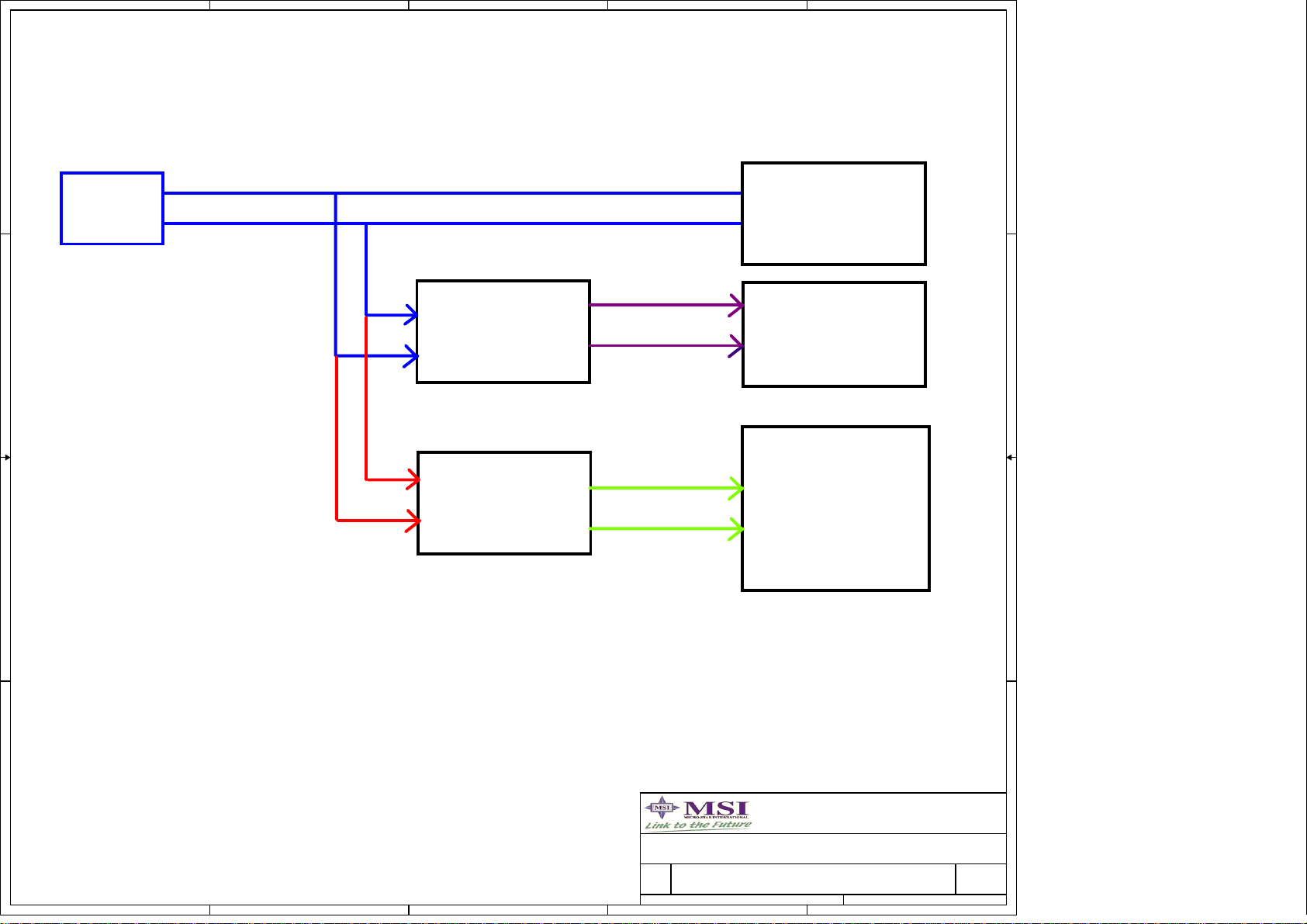

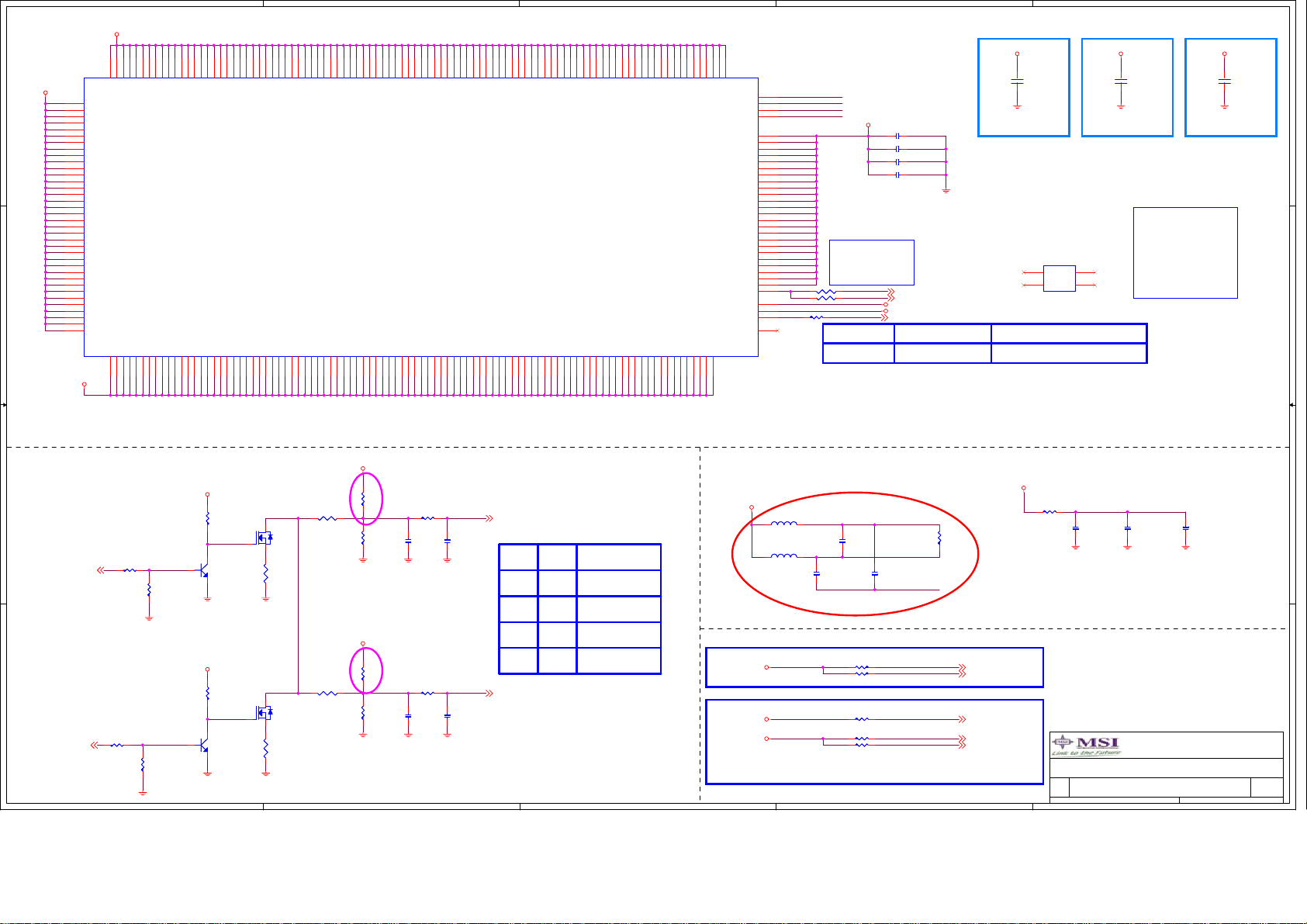

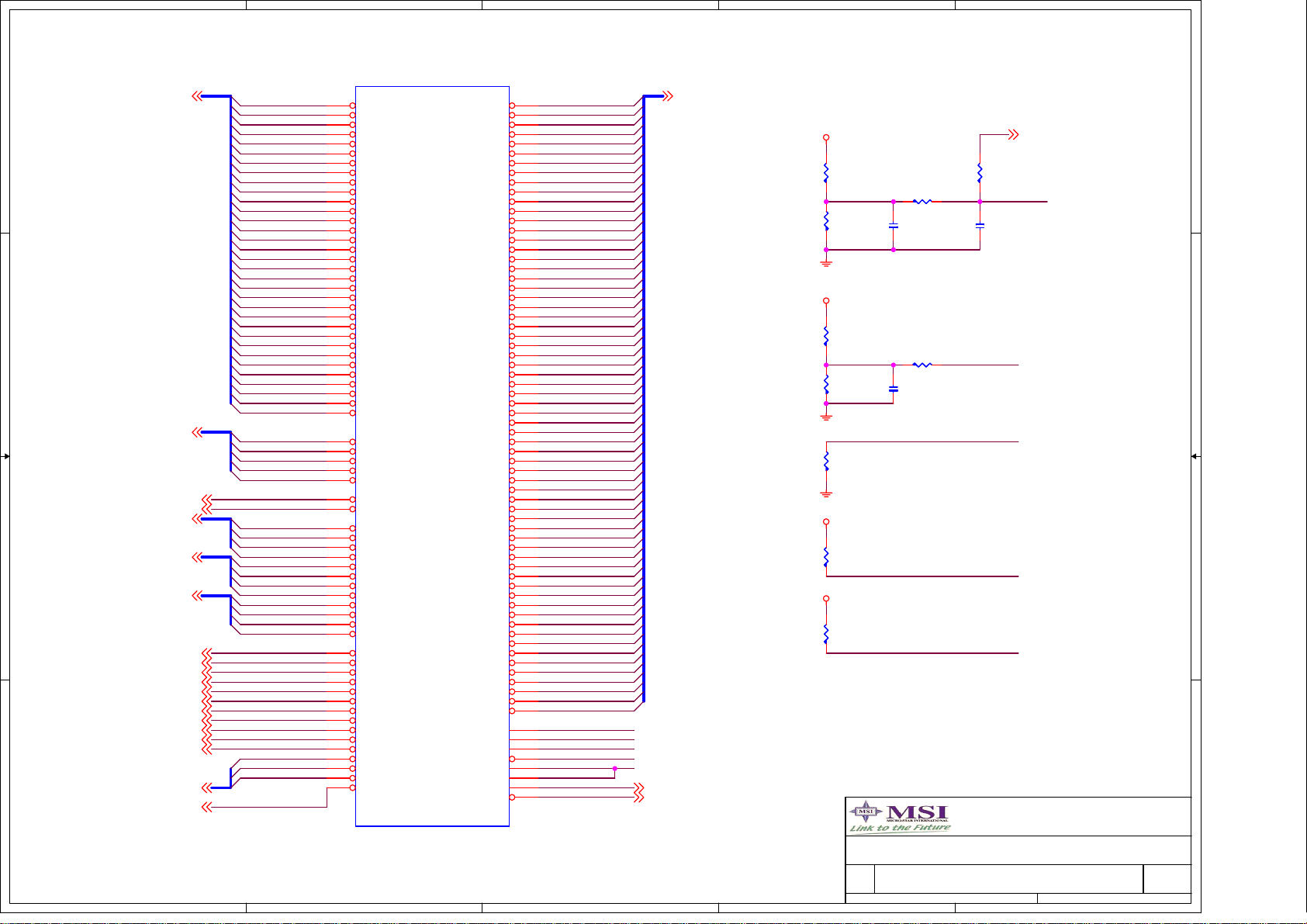

MS-91A2 SYSTEM BLOCK DIAGRAM

D D

VRD 11

ISL6322

Intel LGA775 Processor

4-Phase PWM

FSB

FSB 800/1066/1333

DDR2 x2

DIMM Modules

DDR2 x2

DIMM Modules

C C

SATA 0~3

DDRII Channel0

Unbuffered ECC

DDR2 667/800

DDRII Channel1

Unbuffered ECC

DDR2 667/800

SATA

MCH

Bigby /V=>Default

DMI

ICH

ICH9

PORT #0,1 FRONT

PORT #2,3 Internal

USB Port 0~3

USB 2.0

PCI Express X 8

PCIE_1

PCI 33MHz BUS

PCI 33MHz BUS

GLCI & LCI

PLX-8525

PCI Express X4

PCI Express X4

PCI Express X4

Mini PCI SLOT

XGI VGA

Volari Z7 GPU

LAN

PCI Express X4

82571EB RJ45 2 Ports

82571EB RJ45 2 Ports

82571EB SPF 2 Ports

2X PCI EXPRESS X 4

(Golden Finger)

Bypass F/C

Bypass F/C

82566DM

LPC Bus & SMBus

B B

IDE/CF

JMB368

PCI Express X 1

SPI

PCI Express X4

Super IO

W83627EHG

Keyboard

Serial

Serial

SPI

Flash ROM

A A

5

4

Mouse

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Block Diagram

Block Diagram

Block Diagram

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

361Wednesday, November 14, 2007

of

361Wednesday, November 14, 2007

of

361Wednesday, November 14, 2007

5

4

3

2

1

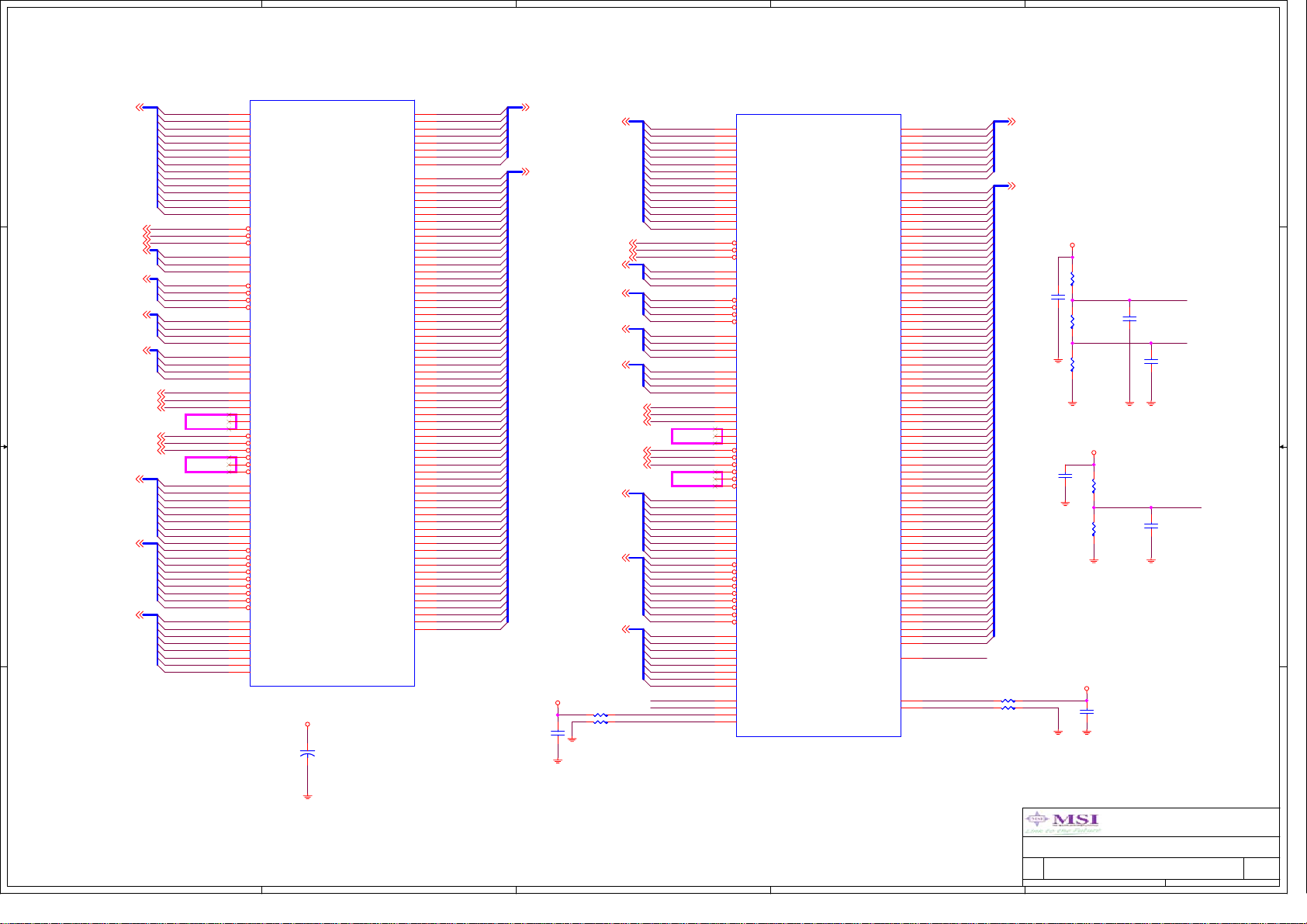

+1.5VCORE

1.5V

1.88A

REG

P2V5_VGA

1.88A

REG

1.5V

REG

+1.2V_FSBVTT

9A

D D

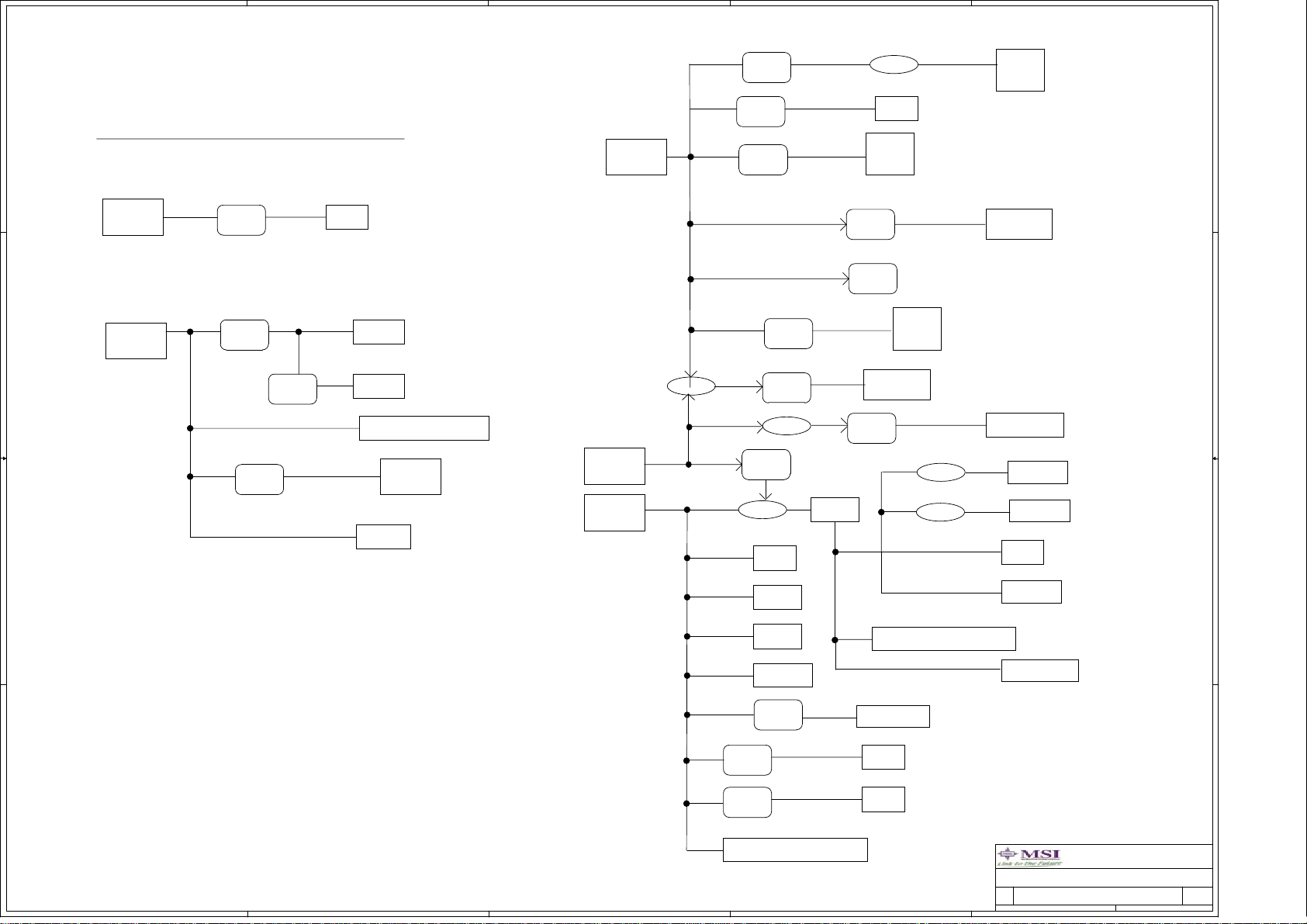

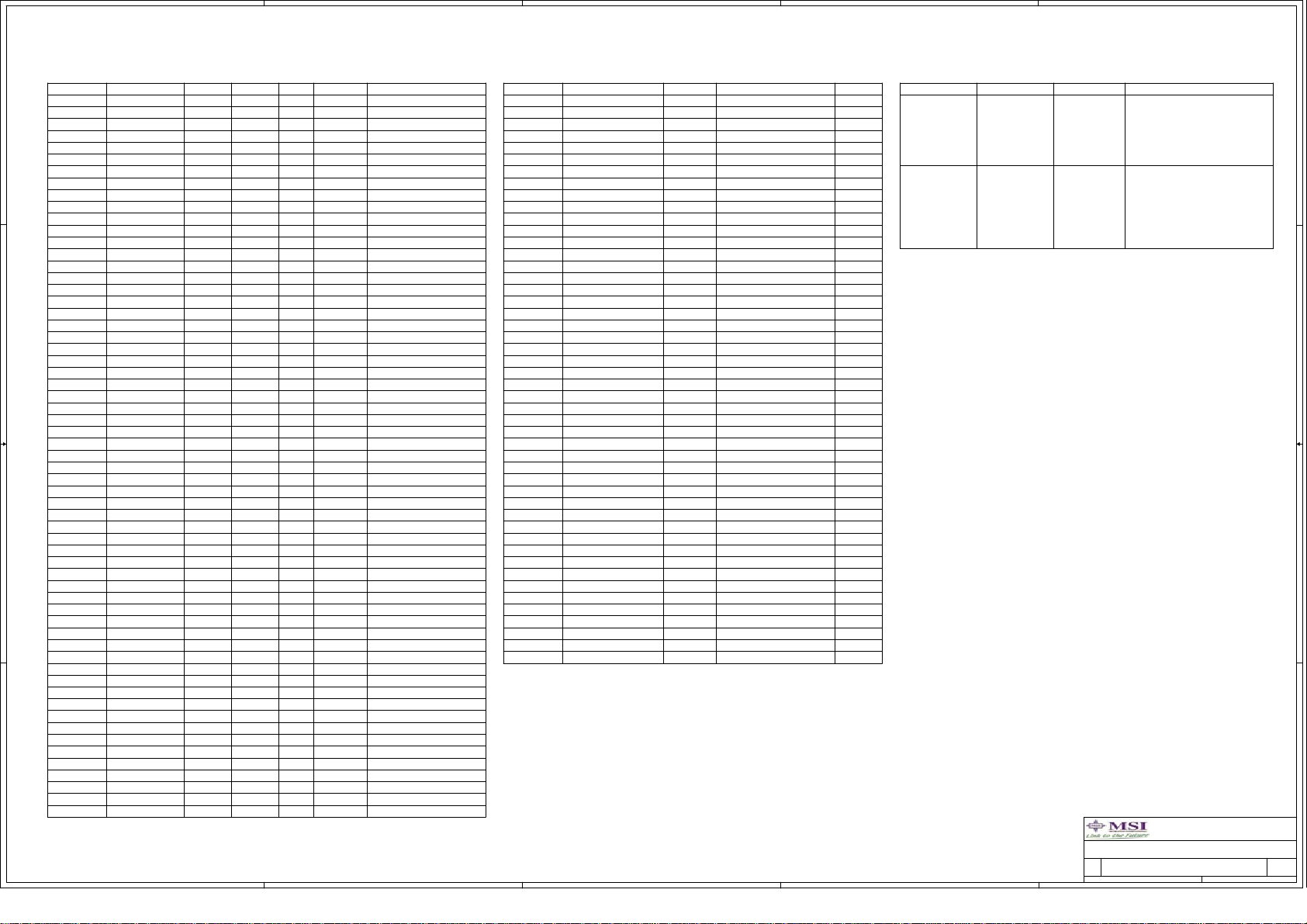

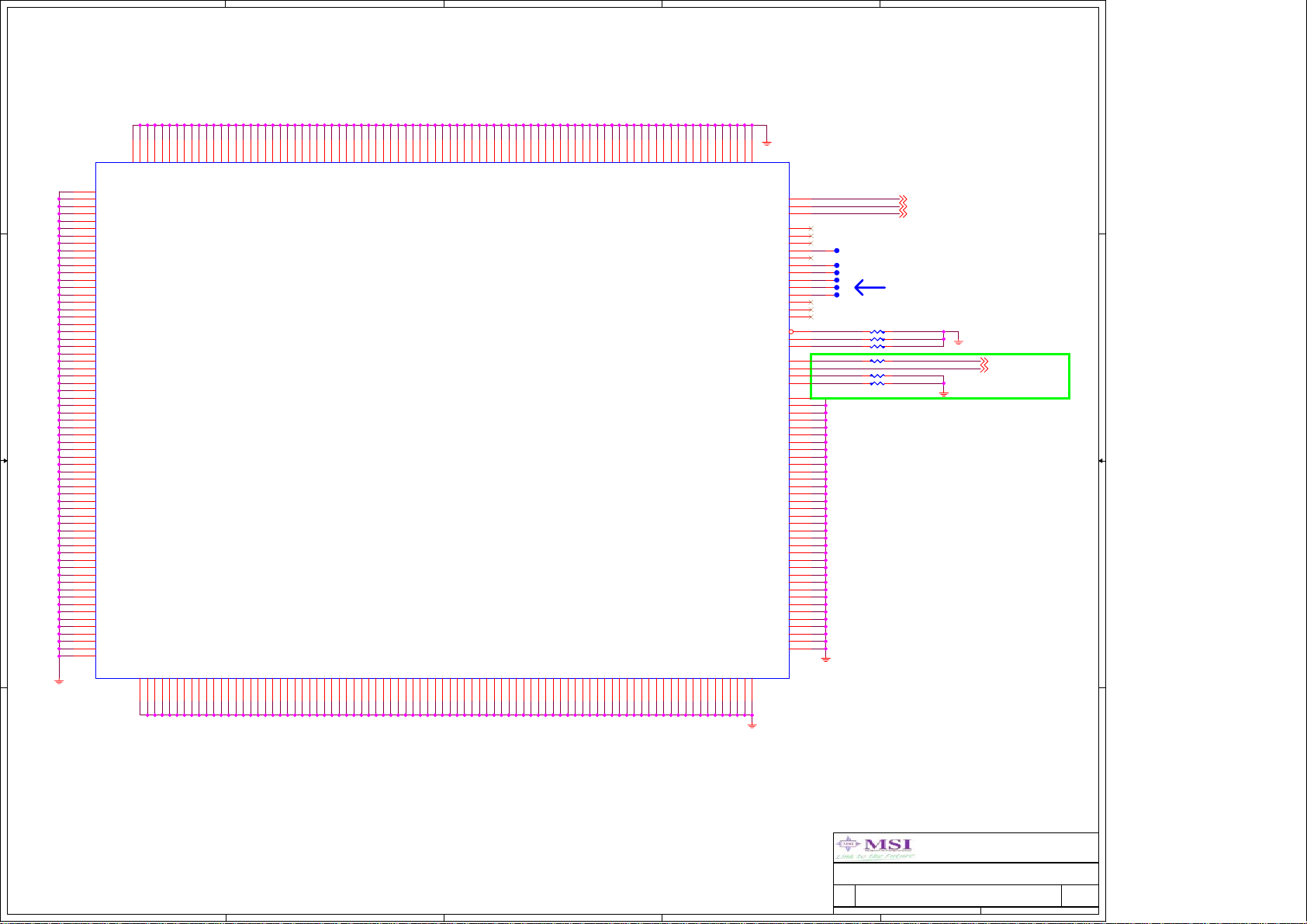

MS-91A2POWER DELIEVERY DIAGRAM

+5V

+12V

16.7A

VRM1

CPU

3A

2.1A

SWITCH

25A

1.25V

REG

2A

+5VDUAL

+1.25VCORE

SWITCH

3.33A

C C

+12V

1.8V

REG

+1.8VCC_DDR2

DIMM

U23 VTT_DDR2

3.3A

Golden Finger (2X PCIE 4X)

+3VSB

1.27A

3.3VSB

REG

SWITCH

ICH9

+3.3VDUAL

3.54A

1.25V

REG

+1.25

MCH

DIMM

+5VSB

+3.3V

1.15A * 4

B B

SYSFAN1~4

1.0

REG

Mini PCI

REG

+3.3V_CL

SWITCH

VGA2.5V

MCH

ICH9

CPU

USB X 4 PORT

KB/MS

CLK GEN.

+1.05VCORE

VDD10

MCH

ICH9

VLAN_18 & VLAN_10

SWITCH

SWITCH

PEX8525AA

LAN 82575 I II III1.0V&1.8V

Lan_V_1P8

Lan_V_1P0

ICH9

LAN 82566DM

LAN 82566DM

ICH9

LAN 82566DM

Super IO

XGI Z7 VGA

VTT_PEX

1.5V

REG

DVDD_2.0

REG

A A

REG

P1V8_VGA

Golden Finger (2X PCIE 4X)

LAN 82575 I II III

PEX8525AA

JMB3682.0V

VGA1.8V

Golden Finger (2X PCIE 4X)

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Power map

Power map

Power map

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

461Wednesday, November 14, 2007

461Wednesday, November 14, 2007

461Wednesday, November 14, 2007

This board doesn't support ACPI S3 state

5

4

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

3

2

Date: Sheet of

5

4

3

2

1

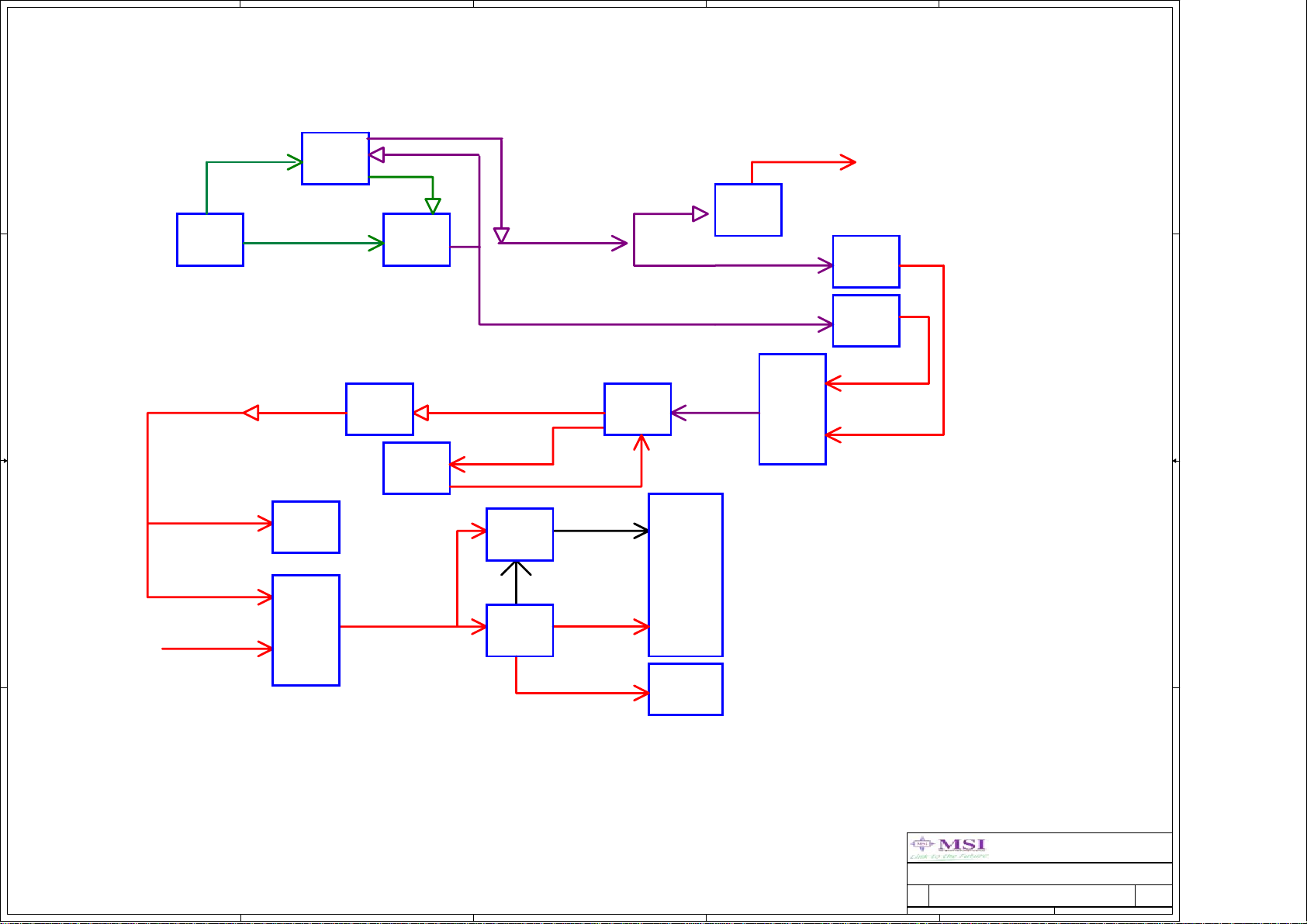

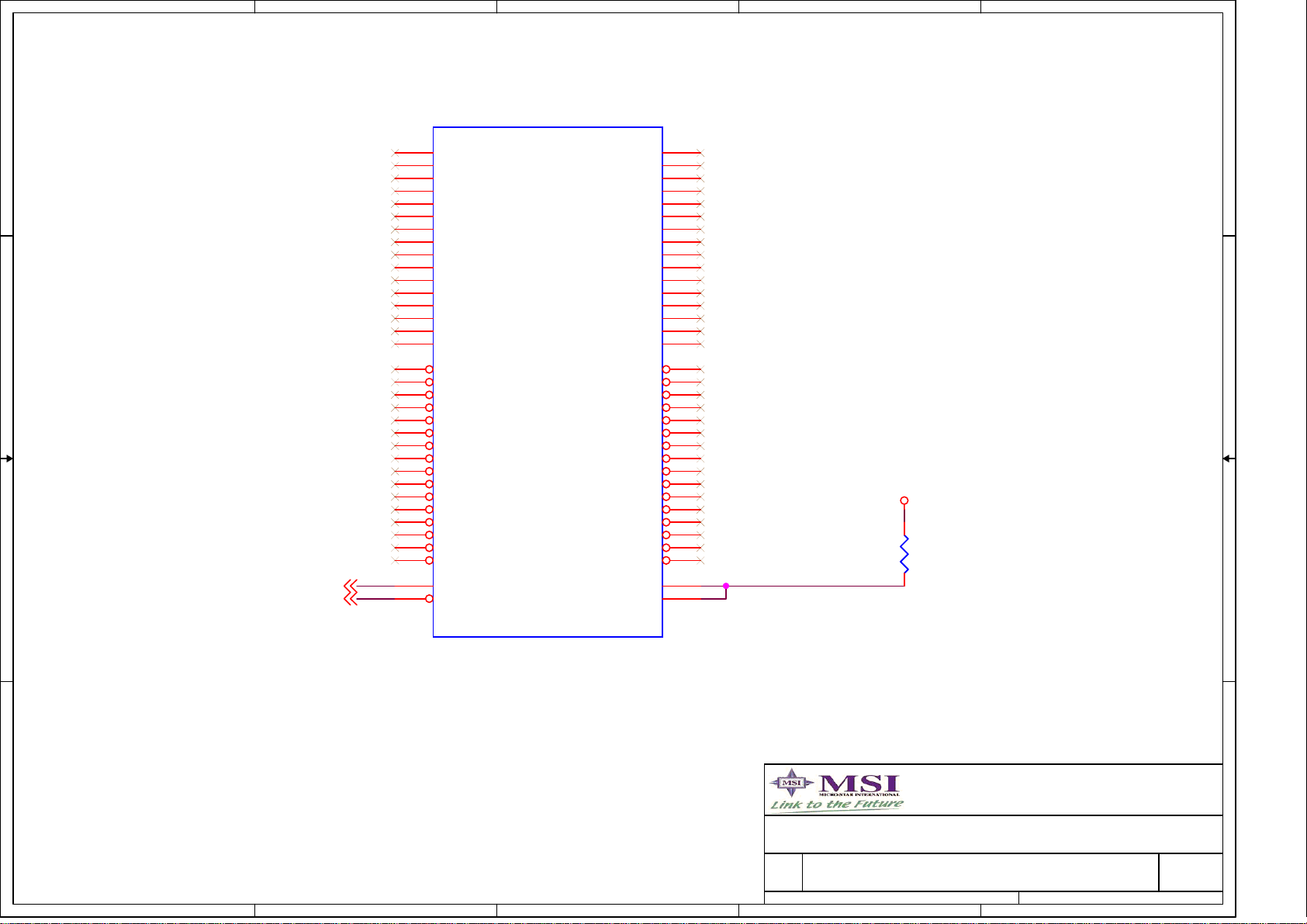

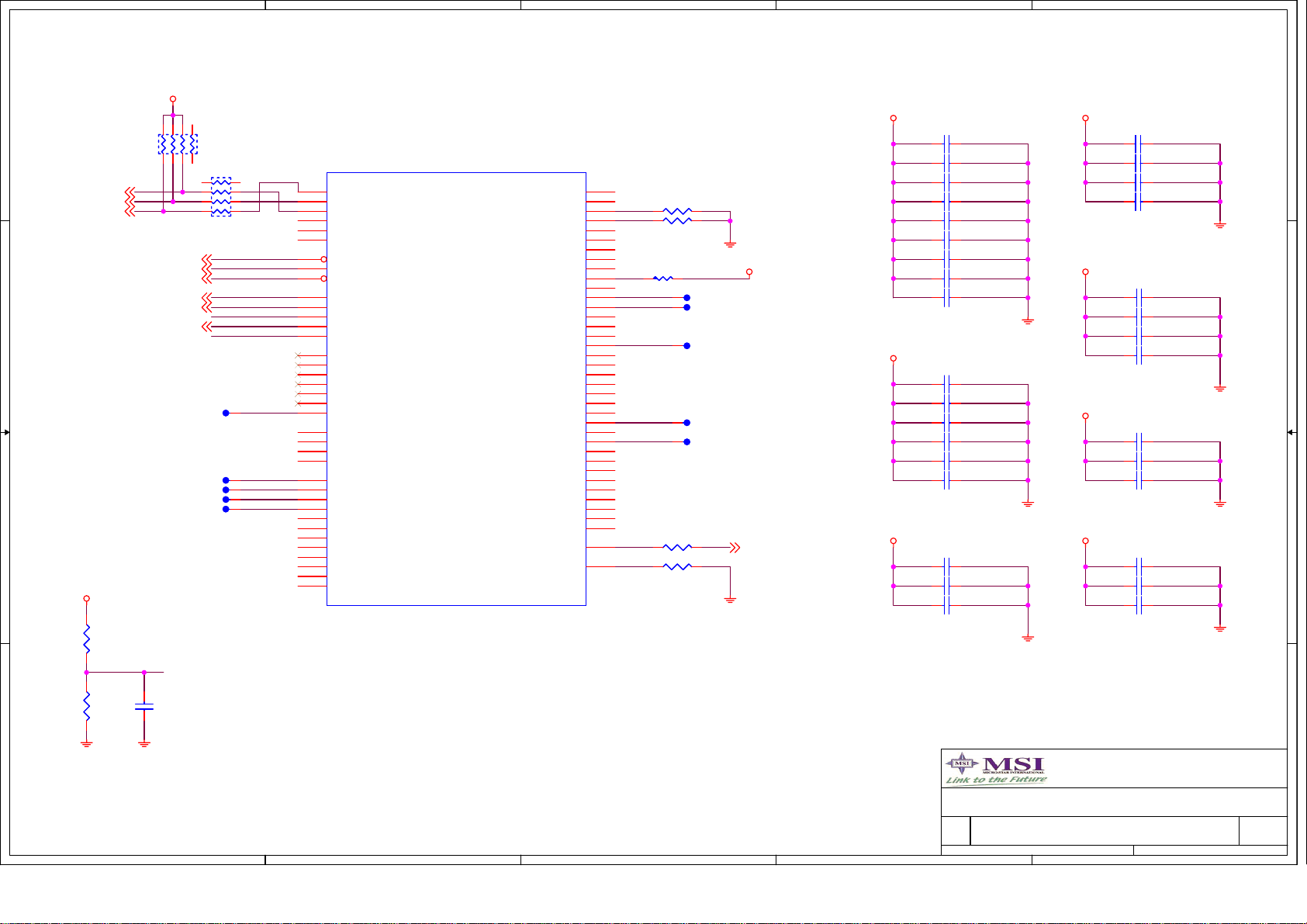

D D

1

SIO_PSIN#

Super

I\O

SIO_PSON#

SLP_S3#

SIO_PSOUT#

4

3

ATX_POWER_OK

2

Power

Front

panel

1

PWRBTN_FP#

ICH9

POWER_SUPPLY_ON#

supply

EN_CHIP_VCORE

U8

U11

SLP_S4#

C C

VRM_POWER_GOOD

CPU

VRM

CPU

ICH9

B B

FSB_VTT_GDCPU_VCORE_GD

FSB_VTT_OK

MCH

U18B

VTT_SEL

FSB_CPURST#

EN_FSB_VTT

CPU

AND

Gate

PLT_RESET_MCH#

U29

DDR2_VCC_GD

CHIP_VCORE_GD

ATX_POWER_OK

AND

Gate

ALL_POWER_GOOD

ICH9

CPU_PWRGD

CK_PWRGD

Clock

generator

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Power on diagram

Power on diagram

Power on diagram

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

561Wednesday, November 14, 2007

561Wednesday, November 14, 2007

561Wednesday, November 14, 2007

5

4

3

2

1

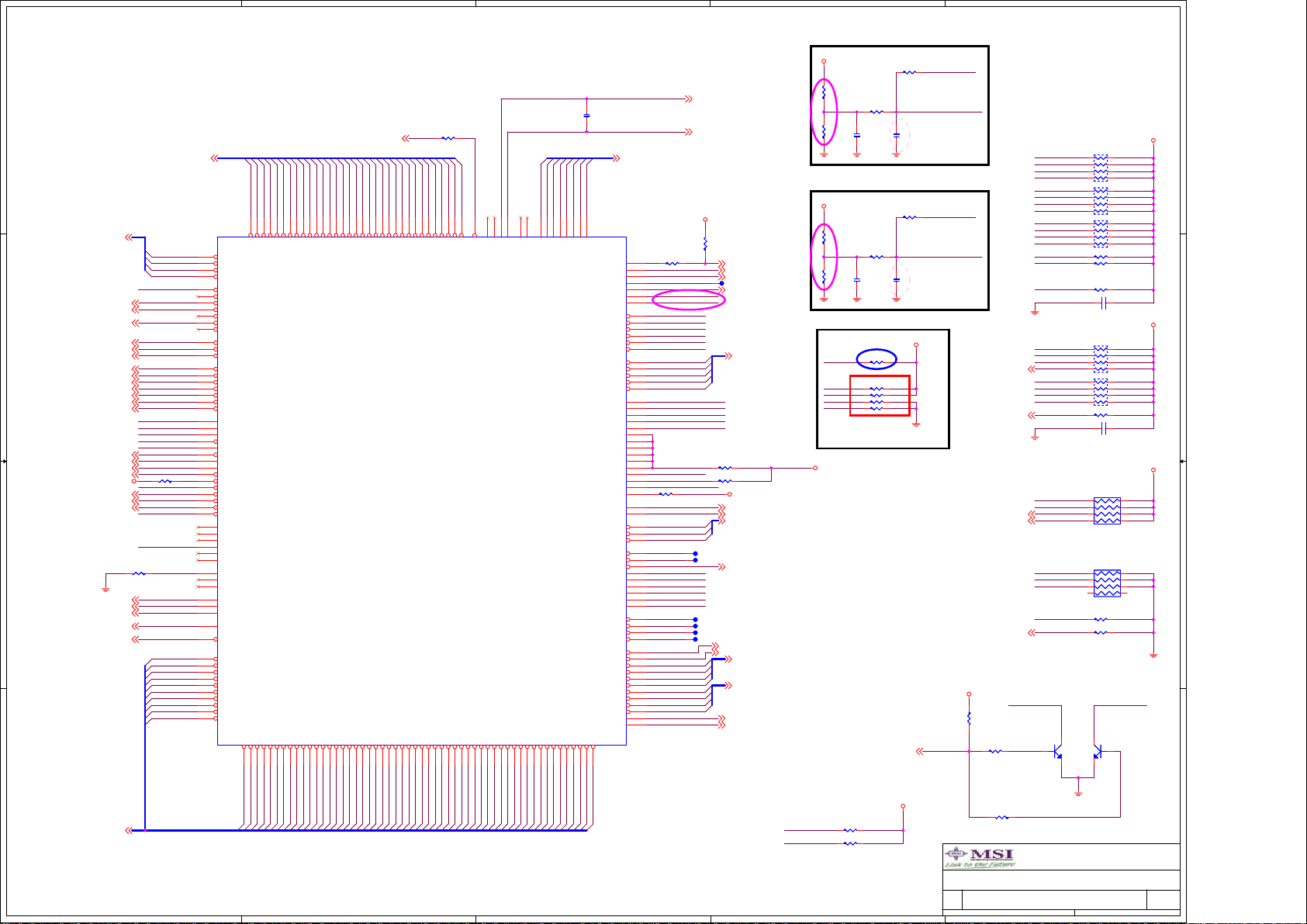

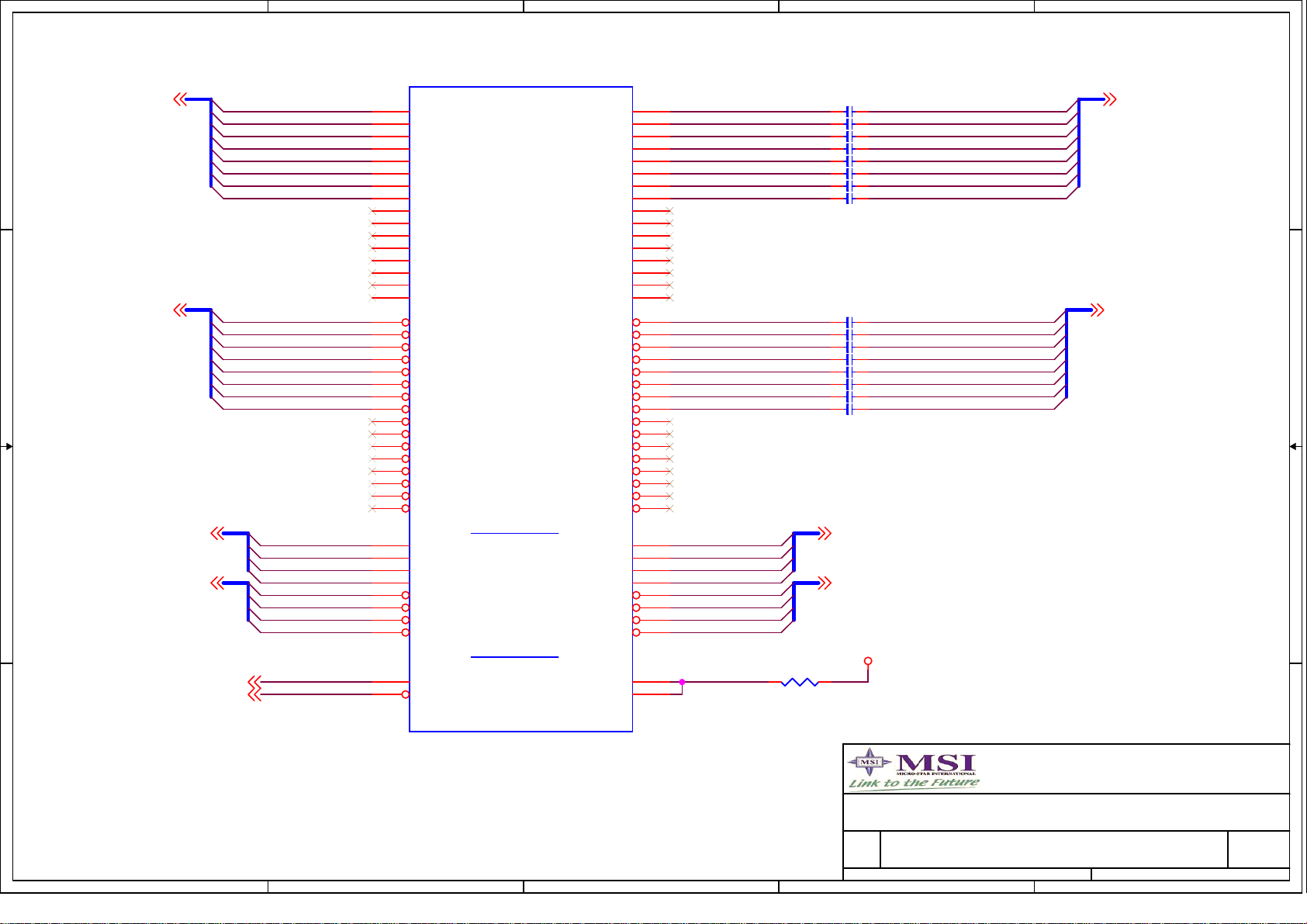

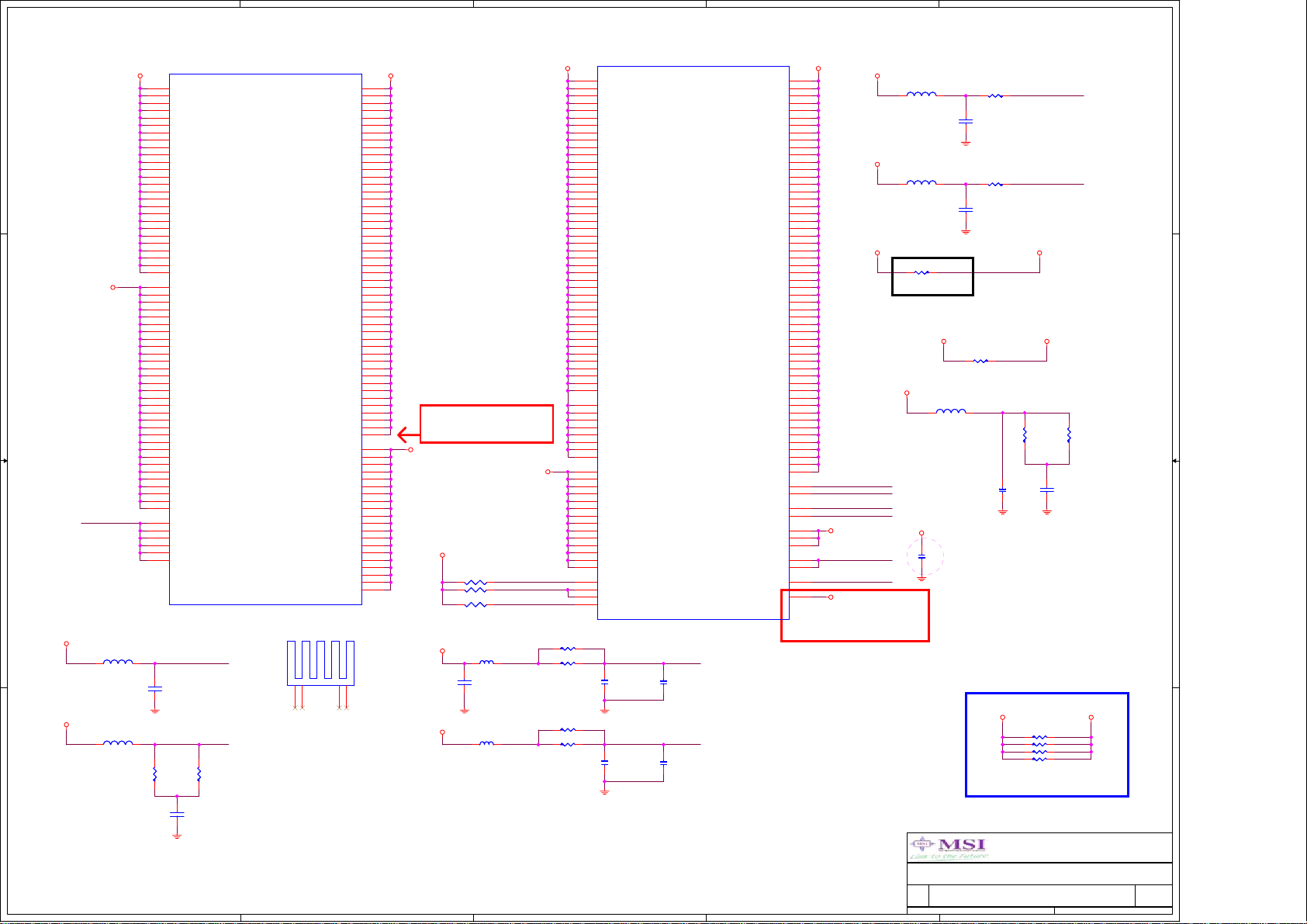

MS-91A2 CLOCK BLOCK DIAGRAM

D D

CY505YC64DT

CPU0

CPU1

53/54

50/51

CK_FSB_CPU_P/N

2

CK_FSB_MCH_P/N

2

CPU

MCH

SRC8

13/14

SRC0

17/18

SRC1

21/22

SRC2

C C

14.318MHZ

Crystal

B B

SRC3

SRC4

SRC6

SRC9

SRC10

SRC11

SRC5

SRC7

24/25

27/28

40/41

30/31

34/35

32/33

37/38

43/44

CK_PCIE_MCH1_P/N

2

CK_ICH_PCIE_P/N

2

CK_SATA_ICH_P/N

2

CK_PCIE_ICH_P/N

2

CK_PCIE_SLOT_P/N

2

CK_PCIE_LAN3_P/N

2

CK_PCIE_LAN1_P/N

2

CK_PCIE_MCH2_P/N

2

CK_1PORT_S1_DP/N

2

REFCLK_PLX_P/N

2

CK_PCIE_LAN2_P/N

2

MCH-PCIE1

CK_ICH_PCIE

ICH9-SATA

ICH-PCIE

PCIE-SLOT

LAN3-82575

LAN1-82575

MCH-PCIE2

JMB-IDE

PLX

LAN2-82575

CK_PCI_SLOT1

1

PCI_0

CPLD_33MHZ_CLK

3

PCI_1

PCI_3

PCI_4

PCI_5

USB_48

A A

REF0

5

4

CK_PCI_VGA

3

CK_PCI_SIO

6

CK_PCI_ICH

7

10

CK_REF14MHZ_ICH

62

CK_USB_48MHZ

CK_SIO_48MHZ

MiniPCI

Bypass Control

VGA

LPC

ICH-PCI

USB

Super I/O

ICH

3

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

CLOCK BLOCK DIAGRAM

CLOCK BLOCK DIAGRAM

CLOCK BLOCK DIAGRAM

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

661Wednesday, November 14, 2007

of

661Wednesday, November 14, 2007

of

661Wednesday, November 14, 2007

5

D D

4

3

2

1

Super IO==>2D

GPIO

ICH9

ICH_SDA1

ICH_SCL1

GOLDEN FINGER

GOLDEN FINGER

C C

PCA9515

PLX_8525

LAN_82575

VRM

Clock generator

PCA9515

DIMM A1==>A0

B B

DIMM B1==>A4

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

MICRO-START INT'L CO.,LTD.

SMBus rounting

SMBus rounting

SMBus rounting

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

2

of

761Wednesday, November 14, 2007

of

761Wednesday, November 14, 2007

of

761Wednesday, November 14, 2007

1

5

4

3

2

1

ICH9 GPIO setting

GPIO

GPIO[0]

D D

C C

B B

A A

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[4]

GPIO[5]

GPIO[6]

GPIO[7]

GPIO[8]

GPIO[9]

GPIO[10] 3.3V

GPIO[11]

GPIO[12]

GPIO[13]

GPIO[14]

GPIO[15]

GPIO[16]

GPIO[17]

GPIO[18]

GPIO[19]

GPIO[20]

GPIO[21]

GPIO[22]

GPIO[23]

GPIO[24]

GPIO[25]

GPIO[26]

GPIO[27]

GPIO[28]

GPIO[29]

GPIO[30]

GPIO[31]

GPIO[32]

GPIO[33]

GPIO[34]

GPIO[35]

GPIO[36]

GPIO[37]

GPIO[38]

GPIO[39]

GPIO[40]

GPIO[41]

GPIO[42]

GPIO[43]

GPIO[44]

GPIO[45]

GPIO[46]

GPIO[47]

GPIO[48]

GPIO[49]

GPIO[50]

GPIO[51]

GPIO[52]

GPIO[53]

GPIO[54]

GPIO[55]

GPIO[56]

GPIO[57]

GPIO[58]

GPIO[59]

GPIO[60]

Alt Func Tol

PMSYNC#

TACH1

PIRQ[E]#

PIRQ[F]#

PIRQ[G]#

PIRQ[H]#

TACH[2]

TACH[3]

unmuxed

WOL_EN

CLGPIO1

SMBALERT#

unmuxed

unmuxed

CLGPIO2

STP_PCI#

unmuxed

TACH0

unmuxed

SATA1GP

unmuxed

SATA0GP

SCLOCK

LDRQ1#

MEM_LED

STP_CPU#

S4_STATE#

QRT_STATE0

QRT_STATE1

OC5#

OC6#

OC7#

unmuxed

unmuxed

unmuxed

SATACLKREQ#

SATA2GP

SATA3GP

SLOAD

SDATAOUT0

OC[1]#

OC[2]#

OC[3]#

OC[4]#

OC[8]#

OC[9]#

OC[10]#

OC[11]#

SDATAOUT1

unmuxed

REQ1#

GNT1#

REQ2#

GNT2#

REQ3#

GNT3#

unmuxed

CLGPIO5

SPI_CS1#

OC[0]#

LINKALERT#

5

I/O/NC

I/O

I/O

I/OD

I/OD

I/OD

I/OD

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O 3.3V

I/O

I/O

I/O

I/O Core

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Power

Core

Core

Core

Core

Core

Core

Core

Core

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Core

Core

Core

Core

Core

Core

Core

Core

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Core

Core

Core

Core

Core

Core

Core

Core

Resume

Resume

Resume 3.3V

Resume

Resume

Resume

Resume

Resume

Core

Core

Core

Core

Core

Core

Core

Resume

Resume

Resume

Resume

Resume

3.3V

3.3V

5V

5V

5V

5V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

5V

3.3V

5V

3.3V

5V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

Default

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

Native

GPI

Native

GPO

GPI

GPI

Native

GPO

GPI

GPO

GPI

GPO

GPI

GPI

Native

GPO

Native

Native

GPO

GPO

Native

Native

Native

GPO

GPO

GPO

GPO

GPI

GPI

GPI

GPI

Native

Native

Native

Native

Native

Native

Native

Native

GPI

GPO

Native

Native

Native

Native

Native

Native

GPI

GPI

GPI

Native

Native

Signal Name

unused

unused

PCI_PIRQ#4

PCI_PIRQ#5

PCI_PIRQ#6

PCI_PIRQ#7

unused

unused

unused

WOL_ONLY

unused

SMBUS_ICH_ALERT#

EXTSMI#

SIO_PME#

BOOT_BLOCK

unused

unused

unused

unused

SATA1GP_PU

unused

SATA0GP_PU

SATA_LED_CLK

LPC_DRQ_1#

unused

unused

unused

unused

CPU_GTLREF_GP28

OC#5

OC#6

OC#7

SPI_WP#

SPI_HOLD_GPO#

unused

CPU_GTLREF_GP35

SATA2GP_PU

SATA3GP_PU

SATA_LED_LOAD

SATA_LED_OUT0

OC#0_1

OC#2_3

OC#2_3

OC#4

OC#8

OC#9

OC#10

OC#11

SATA_LED_OUT1

DMI_STRAP

PCI_REQ#1

PCI_GNT#1

PCI_REQ#2

unused

PCI_REQ#3

unused

ICH_GP56_PU

ICH_GP57_PU

SPI_CS1#

OC#0_1

LINK_ALERT#

4

Super IO GPIO setting

GPIO Alt Func Power Signal Name

GPIO[20]

GPIO[21]

GPIO[22]

GPIO[23]

GPIO[24]

GPIO[25]

GPIO[26]

GPIO[27]

GPIO[30]

GPIO[31]

GPIO[32]

GPIO[33]

GPIO[34]

GPIO[35]

GPIO[36]

GPIO[37]

GPIO[40]

GPIO[41]

GPIO[42]

GPIO[43]

GPIO[44]

GPIO[45]

GPIO[46]

GPIO[47]

GPIO[50]

GPIO[51]

GPIO[52]

GPIO[53]

GPIO[54]

GPIO[55]

GPIO[56]

GPIO[57]

GPIO[60]

GPIO[61]

GPIO[62]

GPIO[63]

GPIO[64]

GPIO[65]

GPIO[66]

GPIO[67]

GPIO[10]

GPIO[11]

GPIO[12]

GPIO[13]

GPIO[14]

GPIO[15]

GPIO[16]

GPIO[17]

CPUFANOUT1/MSO

CPUFANIN1/MSI

SCE#

SCK

MDAT

MCLK

KDAT

KCLK

unmuxed

unmuxed

RSTOUT2#/SCL

RSTOUT3#/SDA

RSTOUT4#

unmuxed

unmuxed

unmuxed

RIB#

DCDB#

SOUTB/IRTX

SINB/IRRX

DTRB#

RTSB#

DSRB#

CTSB#

EN_VRM10/WDTO#

RSMRST#

SUSB#

PSON#

PWROK

SUSLED

PSIN

PSOUT#

RIA#

DCDA#

SOUTA/PENKBC

SINA

DTRA#/PENROM

RTSA#/HEFRAS

DSRA#

CTSA#

GPSA1

GPSB1

GPX1

GPX2

GPY2

GPY1

GPSB2

GPSA2

3

Core

Core

Core

Core

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Core

Core

Core

Core

Core

Core

Core

Core

Resume

Resume

Resume

Resume

Resume

Resume

Resume

Resume

SYSTEM_FAN2_PWM

SYSTEM_FAN2_TACH

unused

unused

MSDATA

MSCLK

KBDATA

KBCLK

PCIE16GPIO2

PCIE16GPIO1

SMBUS_CLK

SMBUS_DATA

LAN1_DIS_N

EN_BYPASS1#

PCIE16GPIO4

PCIE16GPIO3

RIB#

DCDB#

SOUTB

SINB

DTRB#

RTSB#

DSRB#

CTSB#

WDTO#

RSMRST#

SLP_S3# Intput

SIO_PSON#

RELAY1_CON Output

EN_WDTO_RST#

SIO_PSIN#

SIO_PSOUT#

RIA#

DCDA#

SOUTA

SINA

DTRA#

RTSA#

DSRA#

CTSA#

unused

PCIE_SLOT1_PRE#

PCIE16GPIO5

PCIE16GPIO6

unused

FAN_TYPE

PCIE16GPIO7

PCIE16GPIO8

I/O

Output

Input

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Input

Output

Output

Output

Output

Output

Output

Output

MiniPCI rounting

Device

MIniPCI slot

XGI Z7

2

Interrupt ID select REQ&GNT

PCI_PIRQ#0

PCI_PIRQ#1

PCI_PIRQ#0 PCI_AD17

PCI_AD16

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

PCI_REQ#0 & PCI_GNT#0

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

GPIO Setting / PCI Routing

GPIO Setting / PCI Routing

GPIO Setting / PCI Routing

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

861Wednesday, November 14, 2007

861Wednesday, November 14, 2007

861Wednesday, November 14, 2007

5

4

3

2

1

VTT_OUT_LEFT

VCC_SENSE

C362

C362

10u_1206

VID2

VID3

VID1

VID4

VID5

AM5

AL4

AK4

AL6

AM3

AL5

VID6

VID5

VID4

VID3

VID2

FC5/CPU_GTLREF2

RSVD/CPU_GTLREF3

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

10u_1206

VID0

AM2

VID1

VID0

VID_SELECT

GTLREF0

GTLREF1

GTLREF_SEL

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

B4

ZIF-SOCK775-15u-in

ZIF-SOCK775-15u-in

VSS_SENSE

VID[0:7] 54

AN7

CPU_GTLREF0

H1

CPU_GTLREF1

H2

GTLREF_SEL

H29

E24

CPU_GTLREF2

F2

CPU_GTLREF3

G10

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

FSB_REQ#4

J6

FSB_REQ#3

K6

FSB_REQ#2

M6

FSB_REQ#1

J5

FSB_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_BPMB#2

G4

H_BPMB#3

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

R303 X_62R_0402R303 X_62R_0402

G6

G28

F28

FSB_RS#_2

A3

FSB_RS#_1

F5

FSB_RS#_0

B3

TEST-U3

U3

TEST-U2

U2

F3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

TEST-J17

J17

TEST-H16

H16

TEST-H15

H15

TEST-J16

J16

AD5

R6

FSB_DSTBP#_3

C17

FSB_DSTBP#_2

G19

FSB_DSTBP#_1

E12

FSB_DSTBP#_0

B9

FSB_DSTBN#_3

A16

FSB_DSTBN#_2

G20

FSB_DSTBN#_1

G12

FSB_DSTBN#_0

C8

L1

K1

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

D D

FSB_ADD[3:35]14

FSB_ADD28

FSB_ADD30

FSB_ADD29

FSB_ADD32

FSB_ADD34

FSB_ADD33

FSB_ADD31

FSB_ADD27

FSB_ADD26

FSB_ADD35

AJ6

AJ5

AH5

CPU1A

A8

G11

D19

C20

AB2

AB3

R3

M3

AD3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AD1

AF1

AC1

AG1

AE1

G5

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

AH2

N5

AE6

C9

D16

A20

Y1

V2

AA2

G29

H30

G30

N1

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

CPU1A

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

PECI

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

A35#

A34#

A33#

D53#

D52#

D51#

D50#

A14

C14

C15

FSB_DINV#_[0:3]14

FSB_DINV#_0

FSB_DINV#_1

FSB_DINV#_2

FSB_DINV#_3

CPU_IERR#

CPU_FERR#10,20

CPU_STPCLK#20

CPU_INIT#20

Kentsfield

FSB_DBSY#14

FSB_DRDY#14

FSB_TRDY#14

FSB_ADS#14

FSB_LOCK#14

FSB_BNR#14

FSB_HIT#14

FSB_HITM#14

FSB_BPRI#14

FSB_DEFER#14

PECI_ICH20

THERMDA44

THERMDC44

CPU_THERMTRIP#10,20

CPU_IGNNE#20

ICH_CPU_SMI#20

A20M#20

FSB_SEL016,43

FSB_SEL116,43

FSB_SEL216,43

CPU_PWRGD10,20

FSB_CPURST#10,14

+3.3VDUAL

R343 X_51R_0402R343 X_51R_0402

TDI

TDO

TMS

TRST#

TCK

R399 X_4.7K_0402R399 X_4.7K_0402

PROCHOT#

H_TESTHI13

H_BPMB#1

FSB_SEL0

FSB_SEL1

FSB_SEL2

FSB_DATA63

FSB_DATA62

FSB_DATA61

FSB_DATA60

FSB_DATA59

FSB_DATA58

FSB_DATA57

FSB_DATA56

FSB_DATA55

FSB_DATA54

C C

B B

FSB_ADD25

AH4

AG5

AG4

AG6

AF4

AF5

AB4

A32#

A31#

A30#

A29#

A28#

A27#

A26#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

F21

E22

D17

D20

D22

G22

G21

RSTBTN_FP#20,51

FSB_ADD16

FSB_ADD18

FSB_ADD17

FSB_ADD15

FSB_ADD20

FSB_ADD22

FSB_ADD21

FSB_ADD24

FSB_ADD23

FSB_ADD19

AC5

AB5

AA5

AD6

AA4

AB6

A25#

A24#

A23#

A22#

A21#

A20#Y4A19#Y6A18#W6A17#

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

F20

F18

F17

E21

E19

E18

E16

E15

G17

G18

R352 X_0R_0402R352 X_0R_0402

VID7

FSB_ADD12

FSB_ADD14

FSB_ADD13

FSB_ADD11

FSB_ADD4

FSB_ADD6

FSB_ADD5

FSB_ADD8

FSB_ADD10

FSB_ADD9

FSB_ADD7

FSB_ADD3

AC2

L5

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

F15

F14

F12

F11

E13

D13

G16

G15

G14

G13

D22#

D21#

E10

D10

AN4

AN3

DBR#

VCC_SENSE

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

D11

VSS_SENSE

VID6

AM7

AJ3

AK3

AN6

AN5

ITP_CLK1

ITP_CLK0

RSVD/VID7

VSS_MB_REGULATION

VCC_MB_REGULATION

D14#

D13#

D12#D8D11#

D10#

D9#

D8#

B12

B10

A11

A10

C12

C11

96/10/01 Change

VCC_SENSE 54

VSS_SENSE 54

+1.2FSB_VTT

96/10/01 Change

R398

R398

680R_0402

680R_0402

T41T41

96/10/01 Change

R383 51_0402R383 51_0402

R384 51_0402R384 51_0402

FORCEPH

VTT_OUT_LEFT

CK_FSB_CPU_N 43

CK_FSB_CPU_P 43

FSB_RS#_[0:2] 14

T33T33

T32T32

T37T37

T35T35

T34T34

T36T36

FSB_ADSTB#_1 14

FSB_ADSTB#_0 14

CPU_NMI 20

CPU_INTR 20

VID_SELECT 54

CPU_GTLREF0 10

CPU_GTLREF1 10

CPU_MCH_GTLREF 14

FSB_REQ#[0:4] 14

FSB_BREQ0# 10,14

FSB_DSTBP#_[0:3] 14

FSB_DSTBN#_[0:3] 14

R284

R284

57.6RST_0402

57.6RST_0402

R282

R282

100RST_0402

100RST_0402

VTT_OUT_RIGHT

R354

R354

57.6RST_0402

57.6RST_0402

R351

R351

100RST_0402

100RST_0402

CLOSE TO XDP

TDO

TMS

TDI

TRST#

CLOSE TO CPU

PLACE ON TOP LAYER

VTT_OUT_RIGHT

R278 X_0R_0402R278 X_0R_0402

R283 10R_0402R283 10R_0402

C2941uC294

1u

R350 X_0R_0402R350 X_0R_0402

R348 10R_0402R348 10R_0402

C3171uC317

1u

R359 62R_0402R359 62R_0402

R349 62R_0402R349 62R_0402

R353 62R_0402R353 62R_0402

R355 62R_0402R355 62R_0402

R361 62R_0402R361 62R_0402

SIO_THERM#20,44

VTT_OUT_RIGHT

CPU_GTLREF0

CPU_GTLREF2

C297

C297

X_C220P50N2

X_C220P50N2

CLOSE TO CPU

CPU_GTLREF1

CPU_GTLREF3

C313

C313

X_C220P50N2

X_C220P50N2

CLOSE TO CPU

H_TESTHI1211

+3.3V

R386

R386

2K_0402

2K_0402

R390 130RST_0402R390 130RST_0402

1000 mils Maximum

VID7

RN43 8P4R-680RRN43 8P4R-680R

1

VID3

3

VID1

5

VID6

7

VID5

RN42 8P4R-680RRN42 8P4R-680R

1

VID4

3

VID2

5

VID0

7

H_BPM#0

RN41 8P4R-51RRN41 8P4R-51R

1

H_BPM#1

3

H_BPM#3

5

H_BPM#5

7

H_BPM#4

R357 51_0402R357 51_0402

H_BPM#2

R356 51_0402R356 51_0402R396 0R_0402R396 0R_0402

CPU_IERR#

R346 62R_0402R346 62R_0402

C329 1uC329 1u

H_BPMB#2

RN40 8P4R-51RRN40 8P4R-51R

1

H_TESTHI10

3

H_TESTHI11

5

7

H_BPMB#3

RN38 8P4R-51RRN38 8P4R-51R

1

H_TESTHI1

3

H_TESTHI13

5

H_BPMB#1TCK

7

H_COMP5

H_COMP4

H_COMP6

H_COMP7

H_COMP2

H_COMP3

H_COMP1

H_COMP0

B

Q45

Q45

E C

R294 51_0402R294 51_0402

C306 1uC306 1u

RN37 X_8P4R-49.9RSTRN37 X_8P4R-49.9RST

RN39

RN39

8P4R-49.9RST

8P4R-49.9RST

R273 49.9RST_0402R273 49.9RST_0402

R276 24.9RST_0402R276 24.9RST_0402

E C

H_BPMB#011

H_COMP611

H_COMP711

H_COMP811

FORCEPH PROCHOT#

N-MMBT3904

N-MMBT3904

VTT_OUT_RIGHT

2

4

6

8

2

4

6

8

2

4

6

8

VTT_OUT_LEFT

2

4

6

8

2

4

6

8

12

34

56

78

12

34

56

78

Q44

Q44

N-MMBT3904

N-MMBT3904

B

+1.2FSB_VTT

A A

FSB_DATA[0:63]14

5

FSB_DATA51

FSB_DATA52

FSB_DATA53

FSB_DATA49

FSB_DATA50

FSB_DATA43

FSB_DATA44

FSB_DATA47

FSB_DATA48

FSB_DATA45

FSB_DATA46

FSB_DATA42

FSB_DATA35

FSB_DATA36

FSB_DATA39

FSB_DATA40

FSB_DATA37

FSB_DATA38

FSB_DATA41

4

FSB_DATA27

FSB_DATA28

FSB_DATA31

FSB_DATA32

FSB_DATA29

FSB_DATA30

FSB_DATA26

FSB_DATA33

FSB_DATA34

FSB_DATA19

FSB_DATA20

FSB_DATA23

FSB_DATA24

FSB_DATA21

FSB_DATA22

FSB_DATA25

FSB_DATA17

FSB_DATA18

FSB_DATA11

FSB_DATA12

FSB_DATA15

FSB_DATA16

FSB_DATA13

FSB_DATA14

FSB_DATA3

FSB_DATA4

FSB_DATA0

FSB_DATA7

FSB_DATA8

FSB_DATA5

FSB_DATA6

FSB_DATA9

FSB_DATA10

FSB_DATA1

FSB_DATA2

FORCEPH

R391 130RST_0402R391 130RST_0402

PROCHOT#

R366 X_130RST_0402R366 X_130RST_0402

3

2

VTT_OUT_RIGHT

R385 130RST_0402R385 130RST_0402

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

CPU_LGA775_Signal

CPU_LGA775_Signal

CPU_LGA775_Signal

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

961Wednesday, November 14, 2007

of

961Wednesday, November 14, 2007

of

961Wednesday, November 14, 2007

5

CPU_VCORE

AF9

AF8

AG19

AG18

AG15

AG14

AG12

AG11

AF22

AF21

CPU1B

CPU_VCORE

D D

C C

CPU1B

AF19

VCC#AF19

AF18

VCC#AF18

AF15

VCC#AF15

AF14

VCC#AF14

AF12

VCC#AF12

AF11

VCC#AF11

AE9

VCC#AE9

AE23

VCC#AE23

AE22

VCC#AE22

AE21

VCC#AE21

AE19

VCC#AE19

AE18

VCC#AE18

AE15

VCC#AE15

AE14

VCC#AE14

AE12

VCC#AE12

AE11

VCC#AE11

AD8

VCC#AD8

AD30

VCC#AD30

AD29

VCC#AD29

AD28

VCC#AD28

AD27

VCC#AD27

AD26

VCC#AD26

AD25

VCC#AD25

AD24

VCC#AD24

AD23

VCC#AD23

AC8

VCC#AC8

AC30

VCC#AC30

AC29

VCC#AC29

AC28

VCC#AC28

AC27

VCC#AC27

AC26

VCC#AC26

AC25

VCC#AC25

AC24

VCC#AC24

AC23

VCC#AC23

AB8

VCC#AB8

AA8

VCC#AA8

CPU_VCORE

VCC#AF9

VCC#AF8

VCC#AF22

VCC#AF21

VCC#Y30

VCC#Y8

Y8

Y29

Y30

VCC#AG19

VCC#AG18

VCC#AG15

VCC#AG14

VCC#AG12

VCC#AG11

VCC#W8W8VCC#Y23

VCC#Y24

VCC#Y25

VCC#Y26

VCC#Y27

VCC#Y28

VCC#Y29

Y23

Y24

Y25

Y26

Y27

Y28

AG21

W30

AG30

AG29

AG28

AG27

AG26

AG25

AG22

VCC#AG25

VCC#AG22

VCC#AG21

VCC#W28

VCC#W29

VCC#W30

W28

W29

AH11

AG9

AG8

VCC#AG9

VCC#AG8

VCC#AH11

VCC#AG30

VCC#AG29

VCC#AG28

VCC#AG27

VCC#AG26

VCC#U30

VCC#U8U8VCC#V8V8VCC#W23

VCC#W24

VCC#W25

VCC#W26

VCC#W27

U30

W23

W24

W25

W26

W27

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

VCC#AH25

VCC#AH22

VCC#AH21

VCC#AH19

VCC#AH18

VCC#AH15

VCC#AH14

VCC#AH12

VCC#T8T8VCC#U23

VCC#U24

VCC#U25

VCC#U26

VCC#U27

VCC#U28

VCC#U29

U23

U24

U25

U26

U27

U28

U29

AJ11

AH27

AH26

AH28

AH29

AH30

AH8

AH9

VCC#AH8

VCC#AH9

VCC#AH27

VCC#AH26

VCC#AH28

VCC#AH29

VCC#AH30

VCC#T24

VCC#T25

VCC#T26

VCC#T27

VCC#T28

VCC#T29

VCC#T30

T23

T24

T25

T26

T27

T28

T29

T30

4

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

VCC#AJ8

VCC#AJ11

VCC#AJ12

VCC#AJ14

VCC#AJ15

VCC#N8N8VCC#P8P8VCC#R8R8VCC#T23

N30

VCC#AJ9

VCC#AJ18

VCC#AJ19

VCC#AJ21

VCC#AJ22

VCC#AJ25

VCC#AJ26

VCC#AK11

VCC#AK12

VCC#AK14

VCC#M29

VCC#M30

VCC#M8M8VCC#N23

VCC#N24

VCC#N25

VCC#N26

VCC#N27

VCC#N28

VCC#N29

VCC#N30

N23

N24

N25

N26

N27

N28

N29

M28

M29

M30

VCC#AK15

VCC#M28

VCC#AK8

VCC#AK9

VCC#AL11

VCC#AL12

VCC#AL14

VCC#AK25

VCC#AK26

VCC#AL15

VCC#K26

VCC#K27

VCC#K28

VCC#K29

VCC#K30

VCC#K8K8VCC#L8L8VCC#M23

K26

K27

K28

K29

K30

VCC#AK18

VCC#AK19

VCC#AK21

VCC#AK22

VCC#M24

VCC#M25

VCC#M26

VCC#M27

M23

M24

M25

M26

M27

AL30

AL8

AL9

AM11

AM12

VCC#AL8

VCC#AL18

VCC#AL19

VCC#K24

VCC#K25

K23

K24

K25

VCC#AL9

VCC#AL21

VCC#AL22

VCC#AL25

VCC#AL26

VCC#AL29

VCC#AL30

VCC#AM11

VCC#AM12

VCC#J24

VCC#J25

VCC#J26

VCC#J27

VCC#J28

VCC#J29

VCC#J30

VCC#J8J8VCC#J9J9VCC#K23

J24

J25

J26

J27

J28

J29

J30

3

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

VCC#AN11

VCC#AN9

AN8

AN9

VCC#AN12

VCC#AN14

VCC#AN15

VCC#AN29

VCC#AN30

VCC#AN8

AN26

AN29

AN30

AN22

VCCA

VSSA

VCC#AN18

VCC#AN19

VCC#AN21

VCC#AN22

VCCPLL

VCC-IOPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD#F29

VCC#AN25

VCC#AN26

ZIF-SOCK775-15u-in

ZIF-SOCK775-15u-in

AN25

A23

B23

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

PV_CPU_VCCA

GND_CPU_VSSA

PV_CPU_VCCPLL

PV_CPU_VCCIOPLL

R397 X_0R_0402R397 X_0R_0402

R400 0R_0402R400 0R_0402

R367 0R_0402R367 0R_0402

+1.2FSB_VTT

CAPS FOR FSB GENERIC

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VTT_SEL = L

VTT_SEL = H

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

VCC#AM8

VCC#AM14

VCC#AM15

VCC#AM18

VCC#AM19

VCC#J20

VCC#J21

VCC#J22

VCC#J23

J19

J20

J21

J22

J23

VCC#AM9

VCC#AM21

VCC#AM22

VCC#AM25

VCC#AM26

VCC#AM29

VCC#AM30

VCC#J10

VCC#J11

VCC#J12

VCC#J13

VCC#J14

VCC#J15

VCC#J18

VCC#J19

J10

J11

J12

J13

J14

J15

J18

2

C333 0.1uC333 0.1u

C335 0.1uC335 0.1u

C330 C4.7U16X51206C330 C4.7U16X51206

C341 C4.7U16X51206C341 C4.7U16X51206

FSB_VTT_OK 56

CPU_VCORE_GD 52,54

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL 56

+1.2FSB_VTT=1.1V

+1.2FSB_VTT=1.2V

CPU_VCORE

CI3

CI3

0.1u_0402

0.1u_0402

HS2

HS2

1

3

2

4

CPU_HEATSINK

CPU_HEATSINK

cloase to CPU1

for EMI

3

4

cloase to CPU1

for EMI

1

2

For FSB1333, Quad-Core processor

For normal processors.

CPU_VCORE

CI4

CI4

0.1u_0402

0.1u_0402

BACKPLATE1

BACKPLATE1

CPU_BACKPLATE

CPU_BACKPLATE

1

cloase to CPU1

for EMI

CPU_VCORE

CI5

CI5

0.1u_0402

0.1u_0402

Variable GTLREF Circuit for Intel Bigby Chipset Boards

with Future Quad Core Processor FSB Speeds

==>See 2007_WW03_MoW

B B

CPU_GTLREF_GP2820

A A

CPU_GTLREF_GP3520

R295 1K_0402R295 1K_0402

R296 1K_0402R296 1K_0402

5

R299

R299

100K_0402

100K_0402

R292

R292

100K_0402

100K_0402

+5VSB

R291

R291

1K_0402

1K_0402

Q39

Q39

B

N-MMBT3904

N-MMBT3904

E C

+5VSB

R302

R302

1K_0402

1K_0402

Q40

Q40

B

N-MMBT3904

N-MMBT3904

E C

DS

Q38

Q38

G

2N7002

2N7002

R285

R285

1.3KRST_0402

1.3KRST_0402

DS

Q41

Q41

G

2N7002

2N7002

R304

R304

576RST

576RST

+1.2FSB_VTT

R288 X_0R_0402R288 X_0R_0402

+1.2FSB_VTT

R340 0R_0402R340 0R_0402

96/10/02 Change

R289

R289

57.6RST_0402

57.6RST_0402

R298 10RST_0402R298 10RST_0402

C3031uC303

R290

R290

1u

100RST_0402

100RST_0402

96/10/02 Change

R316

R316

57.6RST_0402

57.6RST_0402

R347 10RST_0402R347 10RST_0402

R344

R344

C3121uC312

100RST_0402

100RST_0402

1u

4

C305

C305

C220P50N2

C220P50N2

C314

C314

C220P50N2

C220P50N2

CPU_GTLREF0 9

GP28

0

1

0

1

CPU_GTLREF1 9

GP35

0

0

1

1

Ratio set

0.67

default

0.65

0.63

0.615

Place componots as close as possible to CPU socket

Trace width to caps must be no smaller that 12 mils

+1.2FSB_VTT

FB4 600L350M_450FB4 600L350M_450

FB5 600L350M_450FB5 600L350M_450

+1.2FSB_VTT

VTT_OUT_RIGHT

VTT_OUT_LEFT

3

C318

C318

C22U6.3X50805

C22U6.3X50805

PLACE AT CPU END OF ROUTE

AND

CLOSE TO CPU

PV_CPU_VCCIOPLL

C3231uC323

1u

PV_CPU_VCCA

C3201uC320

1u

GND_CPU_VSSA

CLOSE TO ICH9

R132 62R_0402R132 62R_0402

R113 62R_0402R113 62R_0402

R388 62R_0402R388 62R_0402

R297 X_100RST_0402R297 X_100RST_0402

R281 62R_0402R281 62R_0402

R3640RR364

0R

2

+1.5VCORE

Place within 500 mils of CPU socket

CPU_THERMTRIP# 9,20

CPU_FERR# 9,20

FSB_CPURST# 9,14

CPU_PWRGD 9,20

FSB_BREQ0# 9,14

R358 0R_0402R358 0R_0402

C324

C324

10000p

10000p

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

PV_CPU_VCCPLL

C319

C319

10u_0805

10u_0805

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

CPU_LGA775_Power

CPU_LGA775_Power

CPU_LGA775_Power

C326

C326

0.01u_0402

0.01u_0402

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

10 61Wednesday, November 14, 2007

10 61Wednesday, November 14, 2007

10 61Wednesday, November 14, 2007

of

5

D D

U7

CPU1C

CPU1C

V30

V29

V28

V27

V26

V25

W4

Y2

V6

V24

V3

R5

V23

T3

4

L30

L29

M1

L6

R30

R29

R28

R27

R26

R25

R24

R23

R2

P30

P29

P28

P27

P26

P25

P24

P4

P23

L3

N3

3

L28

L27

L26

L25

L24

L23

J7

H3

H6

H7

H8

H9

K2

K5

H22

H23

H24

H25

H26

H27

H28

H13

H14

H17

H18

H19

H20

H21

2

H10

H11

H12

F7

1

VSS#L7L7VSS#L6

VSS#Y7Y7VSS#Y5Y5VSS#Y2

VSS#V7V7VSS#V6

A12

VSS#A12

A15

VSS#A15

A18

VSS#A18

A2

VSS#A2

A21

VSS#A21

A6

VSS#A6

A9

VSS#A9

AA23

VSS#AA23

AA24

VSS#AA24

AA25

VSS#AA25

AA26

VSS#AA26

AA27

VSS#AA27

AA28

VSS#AA28

AA29

VSS#AA29

AA3

VSS#AA3

AA30

VSS#AA30

AA6

VSS#AA6

AA7

VSS#AA7

AB1

VSS#AB1

AB23

VSS#AB23

AB24

VSS#AB24

AB25

C C

B B

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF30

AC3

AC6

AC7

AD4

AD7

AE2

AE5

AE7

AF3

AF6

AF7

AB7

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

VSS#AE29

VSS#AE30

VSS#AE5

VSS#AE7

VSS#AF10

VSS#AF13

VSS#AF16

VSS#AF17

VSS#AF20

VSS#AF23

VSS#AF24

VSS#AF25

VSS#AF26

VSS#AF27

VSS#AF28

VSS#AF29

VSS#AF3

VSS#AF30

VSS#AF6

VSS#AF7

VSS#AG10

AG10

AG13

VSS#W7W7VSS#W4

VSS#AG13

VSS#AG16

VSS#AG17

AG16

AG17

AG20

VSS#V30

VSS#AG20

VSS#AG23

VSS#AG24

AG7

AG23

AG24

VSS#V3

VSS#V29

VSS#V28

VSS#AG7

VSS#AH1

VSS#AH10

AH1

AH10

AH13

VSS#V27

VSS#V26

VSS#V25

VSS#AH13

VSS#AH16

VSS#AH17

AH16

AH17

AH20

VSS#U7

VSS#V24

VSS#V23

VSS#AH20

VSS#AH23

VSS#AH24

AH3

AH23

AH24

VSS#T7T7VSS#T6T6VSS#T3

VSS#R7R7VSS#R5

VSS#AH3

VSS#AH6

VSS#AH7

VSS#AJ10

AH6

AH7

AJ10

AJ13

VSS#R30

VSS#R29

VSS#AJ13

VSS#AJ16

VSS#AJ17

AJ16

AJ17

VSS#R28

VSS#R27

VSS#AJ20

VSS#AJ23

AJ20

AJ23

AJ24

VSS#R26

VSS#R25

VSS#R24

VSS#AJ24

VSS#AJ27

VSS#AJ28

AJ27

AJ28

AJ29

VSS#P7P7VSS#P4

VSS#R2

VSS#R23

VSS#AJ29

VSS#AJ30

VSS#AJ4

AJ4

AJ7

AJ30

VSS#P30

VSS#P29

VSS#AJ7

VSS#AK10

VSS#AK13

AK10

AK13

VSS#P28

VSS#P27

VSS#P26

VSS#AK16

VSS#AK17

VSS#AK2

AK2

AK16

AK17

VSS#P25

VSS#P24

VSS#P23

VSS#AK20

VSS#AK23

VSS#AK24

AK20

AK23

AK24

VSS#N7N7VSS#N6N6VSS#N3

VSS#AK27

VSS#AK28

AK27

AK28

AK29

VSS#M7M7VSS#M1

VSS#AK29

VSS#AK30

VSS#AK5

AK5

AK7

AK30

VSS#L30

VSS#AK7

VSS#AL10

VSS#AL13

AL10

AL13

VSS#L3

VSS#L29

VSS#AL16

VSS#AL17

AL16

AL17

AL20

VSS#L28

VSS#L27

VSS#L26

VSS#AL20

VSS#AL23

VSS#AL24

AL23

AL24

AL27

VSS#L25

VSS#AL27

AL28

VSS#K7K7VSS#K5

VSS#L24

VSS#L23

VSS#AL28

VSS#AL7

VSS#AM1

AL7

AM1

VSS#K2

VSS#AM10

VSS#AM13

VSS#AM16

AM10

AM13

AM16

VSS#J4J4VSS#J7

VSS#H8

VSS#H9

VSS#AM17

VSS#AM20

VSS#AM23

AM17

AM20

AM23

VSS#H3

VSS#H6

VSS#H7

VSS#AM24

VSS#AM27

VSS#AM28

AM24

AM27

AM28

VSS#H27

VSS#H28

VSS#AM4

VSS#AN1

AN1

AM4

VSS#H25

VSS#H26

VSS#AN10

VSS#AN13

AN10

AN13

AN16

VSS#H22

VSS#H23

VSS#H24

VSS#AN16

VSS#AN17

VSS#AN2

AN2

AN17

AN20

VSS#H19

VSS#H20

VSS#H21

VSS#AN20

VSS#AN23

VSS#AN24

AN23

AN24

AN27

VSS#H14

VSS#H17

VSS#H18

VSS#AN27

VSS#AN28

VSS#B1B1VSS#B11

B11

AN28

VSS#H11

VSS#H12

VSS#H13

RSVD/COMP8

VSS#B14

VSS#B17

B14

B17

VSS#F7

VSS#H10

COMP6

COMP7

RSVD#AE4

RSVD#D1

RSVD#D14

RSVD#E5

RSVD#E6

RSVD#E7

RSVD#E23

RSVD#F23

RSVD

RSVD#J3

RSVD#N4

RSVD#P5

RSVD#AC4

IMPSEL#

MSID1

MSID0

FC28

FC27

FC26

FC23

VSS#F4

VSS#F22

VSS#F19

VSS#F16

VSS#F13

VSS#F10

VSS#E8

VSS#E28

VSS#E27

VSS#E26

VSS#E25

VSS#E20

VSS#E2

VSS#E17

VSS#E14

VSS#E11

VSS#D9

VSS#D6

VSS#D5

VSS#D3

VSS#D24

VSS#D21

VSS#D18

VSS#D15

VSS#D12

VSS#C7

VSS#C4

VSS#C24

VSS#C22

VSS#C19

VSS#C16

VSS#C13

VSS#C10

VSS#B8

VSS#B5

VSS#B20

VSS#B24

ZIF-SOCK775-15u-in

ZIF-SOCK775-15u-in

B20

B24

Y3

AE3

B13

AE4

D1

D14

E5

E6

E7

E23

F23

AL3

J3

N4

P5

AC4

F6

V1

W1

U1

G1

E29

A24

F4

F22

F19

F16

F13

F10

E8

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

T29T29

T30T30

T38T38

T39T39

T40T40

T31T31

R287 X_51R_0402R287 X_51R_0402

R339 X_51R_0402R339 X_51R_0402

R341 X_51R_0402R341 X_51R_0402

R338 0R_0402R338 0R_0402

R368 X_0R_0402R368 X_0R_0402

R365 X_1K_0402R365 X_1K_0402

H_COMP6 9

H_COMP7 9

H_COMP8 9

VRDSEL

H_TESTHI12

H_TESTHI12 9

H_BPMB#0 9

Kentsfield

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

CPU_LGA775_GND

CPU_LGA775_GND

CPU_LGA775_GND

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

of

11 61Wednesday, November 14, 2007

11 61Wednesday, November 14, 2007

11 61Wednesday, November 14, 2007

5

PCIE_A_RXP_[0:7]26

D D

PCIE_A_RXN_[0:7]26

C C

DMI_ICH_TXP_[0:3]19

B B

DMI_ICH_TXN_[0:3]19

PCIE_A_RXP_0

PCIE_A_RXP_1

PCIE_A_RXP_2

PCIE_A_RXP_3

PCIE_A_RXP_4

PCIE_A_RXP_5

PCIE_A_RXP_6

PCIE_A_RXP_7

PCIE_A_RXN_0

PCIE_A_RXN_1

PCIE_A_RXN_2

PCIE_A_RXN_3

PCIE_A_RXN_4

PCIE_A_RXN_5

PCIE_A_RXN_6

PCIE_A_RXN_7

DMI_ICH_TXP_0

DMI_ICH_TXP_1

DMI_ICH_TXP_2

DMI_ICH_TXP_3

DMI_ICH_TXN_0

DMI_ICH_TXN_1

DMI_ICH_TXN_2

DMI_ICH_TXN_3

A16

B13

H13

L13

N13

H12

K11

G10

E6

F7

D2

K7

M11

M7

K3

N8

B15

C14

G13

K13

M13

G12

L12

H10

D5

G6

C2

K8

L10

M8

N10

N5

T7

P4

V7

M4

T8

R5

V6

4

J2

MCH1A

MCH1A

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG_RXP_9

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG_RXN_7

PEG_RXN_8

PEG_RXN_9

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

PCIE

PCIE

DMI

DMI

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

D16

E15

E13

B11

D10

B9

D8

B7

C6

B3

F3

F5

H1

J5

L5

M1

E17

D14

D12

A12

E11

C10

E9

A8

C4

B4

D3

E4

G2

H4

K4

L2

R7

N2

R2

V10

R6

P3

T1

V11

3

PCIE_A_TXP_0C

PCIE_A_TXP_1C

PCIE_A_TXP_2C

PCIE_A_TXP_3C

PCIE_A_TXP_4C

PCIE_A_TXP_5C

PCIE_A_TXP_6C

PCIE_A_TXP_7C

PCIE_A_TXN_0C

PCIE_A_TXN_1C

PCIE_A_TXN_2C

PCIE_A_TXN_3C

PCIE_A_TXN_4C

PCIE_A_TXN_5C

PCIE_A_TXN_6C

PCIE_A_TXN_7C

DMI_ICH_RXP_0

DMI_ICH_RXP_1

DMI_ICH_RXP_2

DMI_ICH_RXP_3

DMI_ICH_RXN_0

DMI_ICH_RXN_1

DMI_ICH_RXN_2

DMI_ICH_RXN_3

2

C181 0.1u_0402C181 0.1u_0402

C176 0.1u_0402C176 0.1u_0402

C167 0.1u_0402C167 0.1u_0402

C159 0.1u_0402C159 0.1u_0402

C155 0.1u_0402C155 0.1u_0402

C151 0.1u_0402C151 0.1u_0402

C148 0.1u_0402C148 0.1u_0402

C144 0.1u_0402C144 0.1u_0402

C185 0.1u_0402C185 0.1u_0402

C168 0.1u_0402C168 0.1u_0402

C161 0.1u_0402C161 0.1u_0402

C160 0.1u_0402C160 0.1u_0402

C158 0.1u_0402C158 0.1u_0402

C152 0.1u_0402C152 0.1u_0402

C150 0.1u_0402C150 0.1u_0402

C147 0.1u_0402C147 0.1u_0402

DMI_ICH_RXP_[0:3] 19

DMI_ICH_RXN_[0:3] 19

+1.25V_PCIEXPRESS

PCIE_A_TXP_0

PCIE_A_TXP_1

PCIE_A_TXP_2

PCIE_A_TXP_3

PCIE_A_TXP_4

PCIE_A_TXP_5

PCIE_A_TXP_6

PCIE_A_TXP_7

PCIE_A_TXN_0

PCIE_A_TXN_1

PCIE_A_TXN_2

PCIE_A_TXN_3

PCIE_A_TXN_4

PCIE_A_TXN_5

PCIE_A_TXN_6

PCIE_A_TXN_7

1

PCIE_A_TXP_[0:7] 26

PCIE_A_TXN_[0:7] 26

CK_PCIE_MCH1_P43

CK_PCIE_MCH1_N43

A A

5

D19

D18

4

EXP_CLKINP

EXP_CLKINN

Bigby

Bigby

EXP_COMPO

EXP_COMPI

1 OF 9

1 OF 9

T10

R10

EXP_COMP

1000 mils Maximum

3

R167 24.9RSTR167 24.9RST

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

MCH_Bigby_PCIE & DMI

MCH_Bigby_PCIE & DMI

MCH_Bigby_PCIE & DMI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

12 61Wednesday, November 14, 2007

12 61Wednesday, November 14, 2007

12 61Wednesday, November 14, 2007

1

5

D D

C C

B B

CK_PCIE_MCH2_P43

CK_PCIE_MCH2_N43

4

MCH1I

MCH1I

W12

PEG2_RXP_0

AA10

PEG2_RXP_1

AA6

PEG2_RXP_2

AC13

PEG2_RXP_3

AC11

PEG2_RXP_4

AC6

PEG2_RXP_5

AE13

PEG2_RXP_6

AE10

PEG2_RXP_7

AE7

PEG2_RXP_8

AG12

PEG2_RXP_9

AH11

PEG2_RXP_10

AH7

PEG2_RXP_11

AK12

PEG2_RXP_12

AL11

PEG2_RXP_13

AL6

PEG2_RXP_14

AP10

PEG2_RXP_15

AA13

PEG2_RXN_0

AA11

PEG2_RXN_1

AA7

PEG2_RXN_2

AB12

PEG2_RXN_3

AC10

AC7

AD12

AE11

AE6

AH13

AH10

AH6

AK13

AL10

AL7

AP11

AE14

AD14

PEG2_RXN_4

PEG2_RXN_5

PEG2_RXN_6

PEG2_RXN_7

PEG2_RXN_8

PEG2_RXN_9

PEG2_RXN_10

PEG2_RXN_11

PEG2_RXN_12

PEG2_RXN_13

PEG2_RXN_14

PEG2_RXN_15

EXP2_CLKINP

EXP2_CLKINN

Bigby

Bigby

PCIE_2

PCIE_2

3

PEG2_TXP_0

PEG2_TXP_1

PEG2_TXP_2

PEG2_TXP_3

PEG2_TXP_4

PEG2_TXP_5

PEG2_TXP_6

PEG2_TXP_7

PEG2_TXP_8

PEG2_TXP_9

PEG2_TXP_10

PEG2_TXP_11

PEG2_TXP_12

PEG2_TXP_13

PEG2_TXP_14

PEG2_TXP_15

PEG2_TXN_0

PEG2_TXN_1

PEG2_TXN_2

PEG2_TXN_3

PEG2_TXN_4

PEG2_TXN_5

PEG2_TXN_6

PEG2_TXN_7

PEG2_TXN_8

PEG2_TXN_9

PEG2_TXN_10

PEG2_TXN_11

PEG2_TXN_12

PEG2_TXN_13

PEG2_TXN_14

PEG2_TXN_15

EXP2_COMPI

EXP2_COMPO

9 OF 9

9 OF 9

AB3

AD4

AE2

AF4

AG2

AH4

AJ2

AK4

AL2

AM4

AN2

AP4

AR2

AT4

AU2

AP7

AB1

AC4

AD3

AE5

AF1

AG5

AH3

AJ5

AK1

AL5

AM3

AN5

AP1

AR5

AT3

AP6

AN10

AN8

2

+1.25VCCR_PEG

R166

R166

24.9RST

24.9RST

EXP2_COMP

1000 mils Maximum

1

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MCH_Bigby_PCIE_II

MCH_Bigby_PCIE_II

MCH_Bigby_PCIE_II

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

13 61Wednesday, November 14, 2007

13 61Wednesday, November 14, 2007

2

13 61Wednesday, November 14, 2007

1

of

5

FSB_ADD[3:35]9

D D

C C

FSB_REQ#[0:4]9

FSB_ADSTB#_09

FSB_ADSTB#_19

FSB_DSTBP#_[0:3]9

B B

A A

FSB_DSTBN#_[0:3]9

FSB_DINV#_[0:3]9

FSB_ADS#9

FSB_TRDY#9

FSB_DRDY#9

FSB_DEFER#9

FSB_HITM#9

FSB_HIT#9

FSB_LOCK#9

FSB_BREQ0#9,10

FSB_BNR#9

FSB_BPRI#9

FSB_DBSY#9

FSB_RS#_[0:2]9

FSB_CPURST#9,10

5

FSB_ADD3

FSB_ADD4

FSB_ADD5

FSB_ADD6

FSB_ADD7

FSB_ADD8

FSB_ADD9

FSB_ADD10

FSB_ADD11

FSB_ADD12

FSB_ADD13

FSB_ADD14

FSB_ADD15

FSB_ADD16

FSB_ADD17

FSB_ADD18

FSB_ADD19

FSB_ADD20

FSB_ADD21

FSB_ADD22

FSB_ADD23

FSB_ADD24

FSB_ADD25

FSB_ADD26

FSB_ADD27

FSB_ADD28

FSB_ADD29

FSB_ADD30

FSB_ADD31

FSB_ADD32

FSB_ADD33

FSB_ADD34

FSB_ADD35

FSB_REQ#0

FSB_REQ#1

FSB_REQ#2

FSB_REQ#3

FSB_REQ#4

FSB_DSTBP#_0

FSB_DSTBP#_1

FSB_DSTBP#_2

FSB_DSTBP#_3

FSB_DSTBN#_0

FSB_DSTBN#_1

FSB_DSTBN#_2

FSB_DSTBN#_3

FSB_DINV#_0

FSB_DINV#_1

FSB_DINV#_2

FSB_DINV#_3

FSB_RS#_0

FSB_RS#_1

FSB_RS#_2

F43

M38

M36

K38

L40

N36

N40

R36

N39

N34

N38

R39

K42

R35

T40

T36

T34

T38

P43

W38

V38

V39

W34

V35

W33

V43

AB34

W36

AA33

AA35

AA40

AB35

AA38

C44

G40

L39

K36

H39

M40

V34

J44

H34

N25

C40

K43

G34

M25

D41

L41

E40

N28

B37

U44

W40

U41

T39

V42

R42

T45

W44

U42

H38

T42

R44

W41

R41

D35

4

MCH1B

MCH1B

FSB_AB_3

FSB_AB_4

FSB_AB_5

FSB_AB_6

FSB_AB_7

FSB_AB_8

FSB_AB_9

FSB_AB_10

FSB_AB_11

FSB_AB_12

FSB_AB_13

FSB_AB_14

FSB_AB_15

FSB_AB_16

FSB_AB_17

FSB_AB_18

FSB_AB_19

FSB_AB_20

FSB_AB_21

FSB_AB_22

FSB_AB_23

FSB_AB_24

FSB_AB_25

FSB_AB_26

FSB_AB_27

FSB_AB_28

FSB_AB_29

FSB_AB_30

FSB_AB_31

FSB_AB_32

FSB_AB_33

FSB_AB_34

FSB_AB_35

FSB_REQB_0

FSB_REQB_1

FSB_REQB_2

FSB_REQB_3

FSB_REQB_4

FSB_ADSTBB_0

FSB_ADSTBB_1

FSB_DSTBPB_0

FSB_DSTBPB_1

FSB_DSTBPB_2

FSB_DSTBPB_3

FSB_DSTBNB_0

FSB_DSTBNB_1

FSB_DSTBNB_2

FSB_DSTBNB_3

FSB_DINVB_0

FSB_DINVB_1

FSB_DINVB_2

FSB_DINVB_3

FSB_ADSB

FSB_TRDYB

FSB_DRDYB

FSB_DEFERB

FSB_HITMB

FSB_HITB

FSB_LOCKB

FSB_BREQ0B

FSB_BNRB

FSB_BPRIB

FSB_DBSYB

FSB_RSB_0

FSB_RSB_1

FSB_RSB_2

FSB_CPURSTB

Bigby

Bigby

4

2 OF 9

2 OF 9

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB

FSB

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_SCOMP

FSB_SCOMPB

FSB_DVREF

FSB_ACCVREF

HPL_CLKINP

HPL_CLKINN

P42

N41

N44

M42

N42

M45

L44

L42

J43

H42

J41

G42

H45

G44

F41

E42

F38

F39

B43

L36

G38

K35

G36

G35

K34

H33

F33

L34

N33

L33

N31

M31

F31

K31

H31

M30

L30

N30

G30

H30

K28

L28

N24

L25

L24

H24

K24

G24

F35

A38

E41

C42

D44

D43

D38

B42

B39

D39

C36

D36

C37

E37

B35

E35

A28

C26

D28

C28

E27

D27

P28

P30

FSB_DATA0

FSB_DATA1

FSB_DATA2

FSB_DATA3

FSB_DATA4

FSB_DATA5

FSB_DATA6

FSB_DATA7

FSB_DATA8

FSB_DATA9

FSB_DATA10

FSB_DATA11

FSB_DATA12

FSB_DATA13

FSB_DATA14

FSB_DATA15

FSB_DATA16

FSB_DATA17

FSB_DATA18

FSB_DATA19

FSB_DATA20

FSB_DATA21

FSB_DATA22

FSB_DATA23

FSB_DATA24

FSB_DATA25

FSB_DATA26

FSB_DATA27

FSB_DATA28

FSB_DATA29

FSB_DATA30

FSB_DATA31

FSB_DATA32

FSB_DATA33

FSB_DATA34

FSB_DATA35

FSB_DATA36

FSB_DATA37

FSB_DATA38

FSB_DATA39

FSB_DATA40

FSB_DATA41

FSB_DATA42

FSB_DATA43

FSB_DATA44

FSB_DATA45

FSB_DATA46

FSB_DATA47

FSB_DATA48

FSB_DATA49

FSB_DATA50

FSB_DATA51

FSB_DATA52

FSB_DATA53

FSB_DATA54

FSB_DATA55

FSB_DATA56

FSB_DATA57

FSB_DATA58

FSB_DATA59

FSB_DATA60

FSB_DATA61

FSB_DATA62

FSB_DATA63

FSB_SWING

FSB_RCOMP

FSB_SCOMP

FSB_SCOMP#

MCH_GTLREF

3

FSB_DATA[0:63] 9

CK_FSB_MCH_P 43

CK_FSB_MCH_N 43

3

2

*GTLREF VOLTAGE SHOULD BE

0.67*VTT=0.8V (At VTT=1.2V)

+1.2FSB_VTT

R242

R242

49.9RST_0402

49.9RST_0402

R233

R233

51RST_0402

R241

R241

100RST_0402

100RST_0402

+1.2FSB_VTT

R239

R239

301RST_0402

301RST_0402

R243

R243

100RST_0402

100RST_0402

R228

R228

16.5RST_0402

16.5RST_0402

+1.2FSB_VTT

R237

R237

49.9RST_0402

49.9RST_0402

+1.2FSB_VTT

R238

R238

49.9RST_0402

49.9RST_0402

2

500 mils Maximum

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

51RST_0402

C2221uC222

1u

R234

R234

C224

C224

0.1u

0.1u

750 mils Maximum

750 mils Maximum

FSB_SWING

51RST_0402

51RST_0402

FSB_RCOMP

FSB_SCOMP

FSB_SCOMP#

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

CPU_MCH_GTLREF 9

R240

R240

X_0R_0402

X_0R_0402

MCH_GTLREF

C216

C216

C220P50N2

C220P50N2

MCH_Bigby_FSB

MCH_Bigby_FSB

MCH_Bigby_FSB

MS-91A2 0A

MS-91A2 0A

MS-91A2 0A

1

14 61Wednesday, November 14, 2007

14 61Wednesday, November 14, 2007

14 61Wednesday, November 14, 2007

1

of

of

of

5

MCH1C

D D

C C

DDR_A_MA_[0:14]22,24

DDR_A_WE#22,24

DDR_A_CAS#22,24

DDR_A_RAS#22,24

DDR_A_BS_[0:2]22,24

DDR_A_CS#_[0:3]22,24

DDR_A_CKE_[0:3]22,24

DDR_A_ODT_[0:3]22,24

DDR_A_CK_022

DDR_A_CK_122

DDR_A_CK_222

96/9/20 change

DDR_A_CK#_022

DDR_A_CK#_122

DDR_A_CK#_222

DDR_A_MA_0

DDR_A_MA_1

DDR_A_MA_2

DDR_A_MA_3

DDR_A_MA_4

DDR_A_MA_5

DDR_A_MA_6

DDR_A_MA_7

DDR_A_MA_8

DDR_A_MA_9

DDR_A_MA_10

DDR_A_MA_11

DDR_A_MA_12

DDR_A_MA_13

DDR_A_MA_14

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CS#_0

DDR_A_CS#_1

DDR_A_CS#_2

DDR_A_CS#_3

DDR_A_CKE_0

DDR_A_CKE_1

DDR_A_CKE_2

DDR_A_CKE_3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_0

DDR_A_CK_1

DDR_A_CK_2

DDR_A_CK#_0

DDR_A_CK#_1

DDR_A_CK#_2

96/9/20 change

DDR_A_DQS_[0:8]22

DDR_A_DQS#_[0:8]22

B B

DDR_A_ECC_[0:7]22

A A

DDR_A_DQS_0

DDR_A_DQS_1

DDR_A_DQS_2

DDR_A_DQS_3

DDR_A_DQS_4

DDR_A_DQS_5

DDR_A_DQS_6

DDR_A_DQS_7

DDR_A_DQS_8

DDR_A_DQS#_0

DDR_A_DQS#_1

DDR_A_DQS#_2

DDR_A_DQS#_3

DDR_A_DQS#_4

DDR_A_DQS#_5

DDR_A_DQS#_6

DDR_A_DQS#_7

DDR_A_DQS#_8

DDR_A_ECC_0

DDR_A_ECC_1

DDR_A_ECC_2

DDR_A_ECC_3

DDR_A_ECC_4

DDR_A_ECC_5

DDR_A_ECC_6

DDR_A_ECC_7

BC36

BB31

BB30

BB29

BA29

BB28

BD29

AY27

BC28

BA27

BD37

BD27

BB27

BA42

BA25

BD39

BB41

BB38

BC37

BB36

BB26

BA40

BD42

BB39

AY43

BD25

AY24

BB25

BC24

BB43

AY41

BA41

AW44

AT33

AN28

AT34

AV31

AN27

AT35

AR33

AM28

AV35

AT31

AM27

AT36

BA11

BA15

AT21

AT43

AM43

AD43

AA42

AL38

BC6

AY11

AY15

AV21

AT42

AM42

AD42

AA44

AL36

AL33

AN35

AK38

AK35

AK33

AL34

AK34

AK39

BA6

MCH1C

DDR_A_MA_0

DDR_A_MA_1

DDR_A_MA_2

DDR_A_MA_3

DDR_A_MA_4

DDR_A_MA_5

DDR_A_MA_6

DDR_A_MA_7

DDR_A_MA_8

DDR_A_MA_9

DDR_A_MA_10

DDR_A_MA_11

DDR_A_MA_12

DDR_A_MA_13

DDR_A_MA_14

DDR_A_WEB

DDR_A_CASB

DDR_A_RASB

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CSB_0

DDR_A_CSB_1

DDR_A_CSB_2

DDR_A_CSB_3

DDR_A_CKE_0

DDR_A_CKE_1

DDR_A_CKE_2

DDR_A_CKE_3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_0

DDR_A_CK_1

DDR_A_CK_2

DDR_A_CK_3

DDR_A_CK_4

DDR_A_CK_5

DDR_A_CKB_0

DDR_A_CKB_1

DDR_A_CKB_2

DDR_A_CKB_3

DDR_A_CKB_4

DDR_A_CKB_5

DDR_A_DQS_0

DDR_A_DQS_1

DDR_A_DQS_2

DDR_A_DQS_3

DDR_A_DQS_4

DDR_A_DQS_5

DDR_A_DQS_6

DDR_A_DQS_7

DDR_A_DQS_8

DDR_A_DQSB_0

DDR_A_DQSB_1

DDR_A_DQSB_2

DDR_A_DQSB_3

DDR_A_DQSB_4

DDR_A_DQSB_5

DDR_A_DQSB_6

DDR_A_DQSB_7

DDR_A_DQSB_8

DDR_A_CB_0

DDR_A_CB_1

DDR_A_CB_2

DDR_A_CB_3

DDR_A_CB_4

DDR_A_CB_5

DDR_A_CB_6

DDR_A_CB_7

Bigby

Bigby

DDR_A

DDR_A

VCC_DDR2

EC19

EC19

470u_16V

470u_16V

Close to MCH

4

DDR_A_DM_0

DDR_A_DM_1

DDR_A_DM_2

DDR_A_DM_3

DDR_A_DM_4

DDR_A_DM_5

DDR_A_DM_6

DDR_A_DM_7

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

3 OF 9

3 OF 9

BB5

BC10

BC14

AP21

AU44

AN44

AE44

AB40

BC4

BD4

BB8

BE8

BD3

BB4

BD7

BB7

BD9

BB10

BB12

BE12

BA9

BC9

BD11

BB11

BD13

BB14

BB16

BE16

BA13

BB13

BD15

BB15

AN19

AY21

AN22

AT22

AV19

AW19

AN21

AW22

AV42

AU43

AR44

AR42

AW42

AU41

AR41

AR40

AN41

AN42

AL44

AL42

AP42

AP45

AL40

AL41

AE41

AE42

AC42

AC45

AF42

AF45

AD40

AC39

AB42

AB43

Y42

W42

AC40

AB39

AA41

Y45

DDR_A_DM_0

DDR_A_DM_1

DDR_A_DM_2

DDR_A_DM_3

DDR_A_DM_4

DDR_A_DM_5

DDR_A_DM_6

DDR_A_DM_7

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22