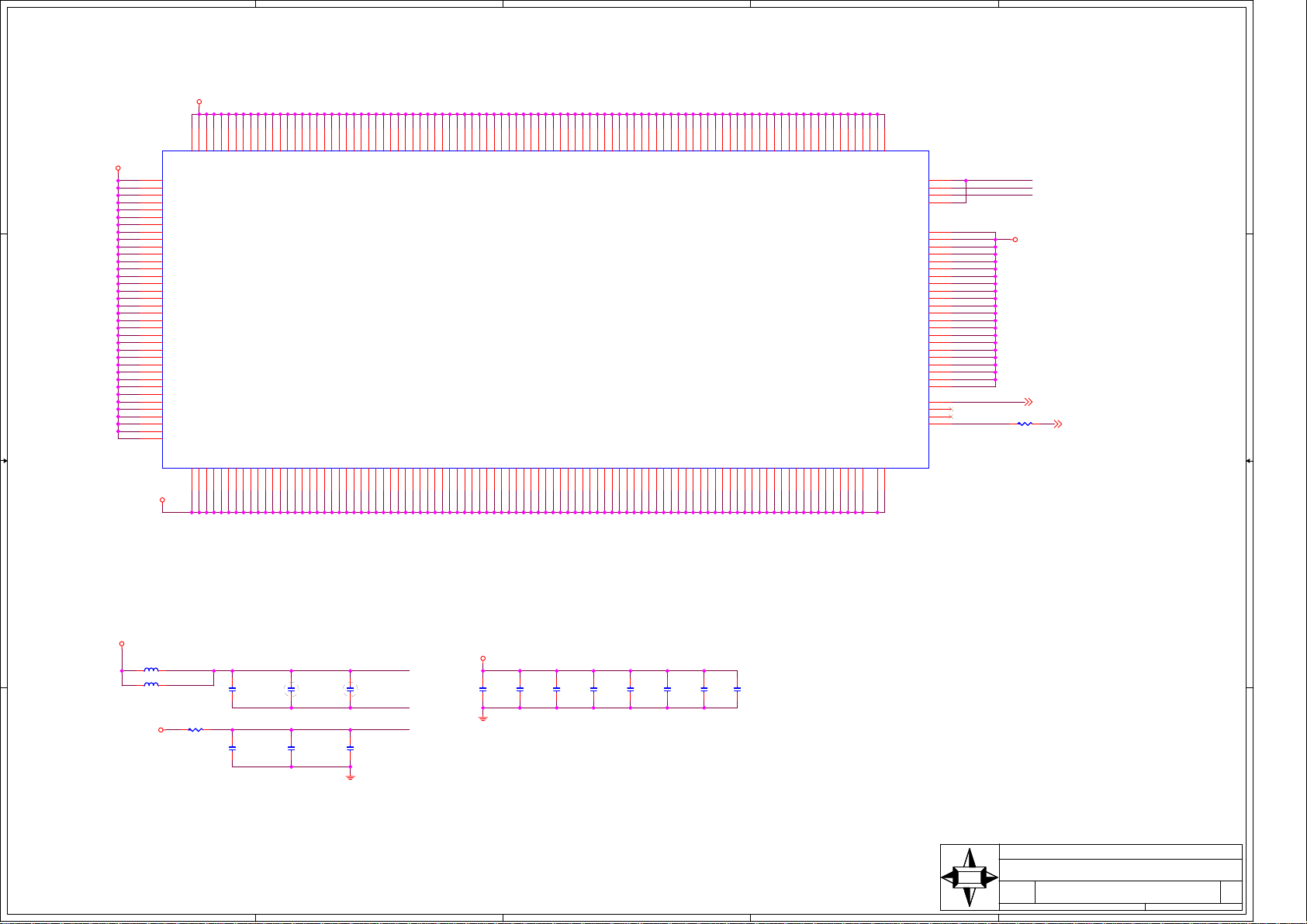

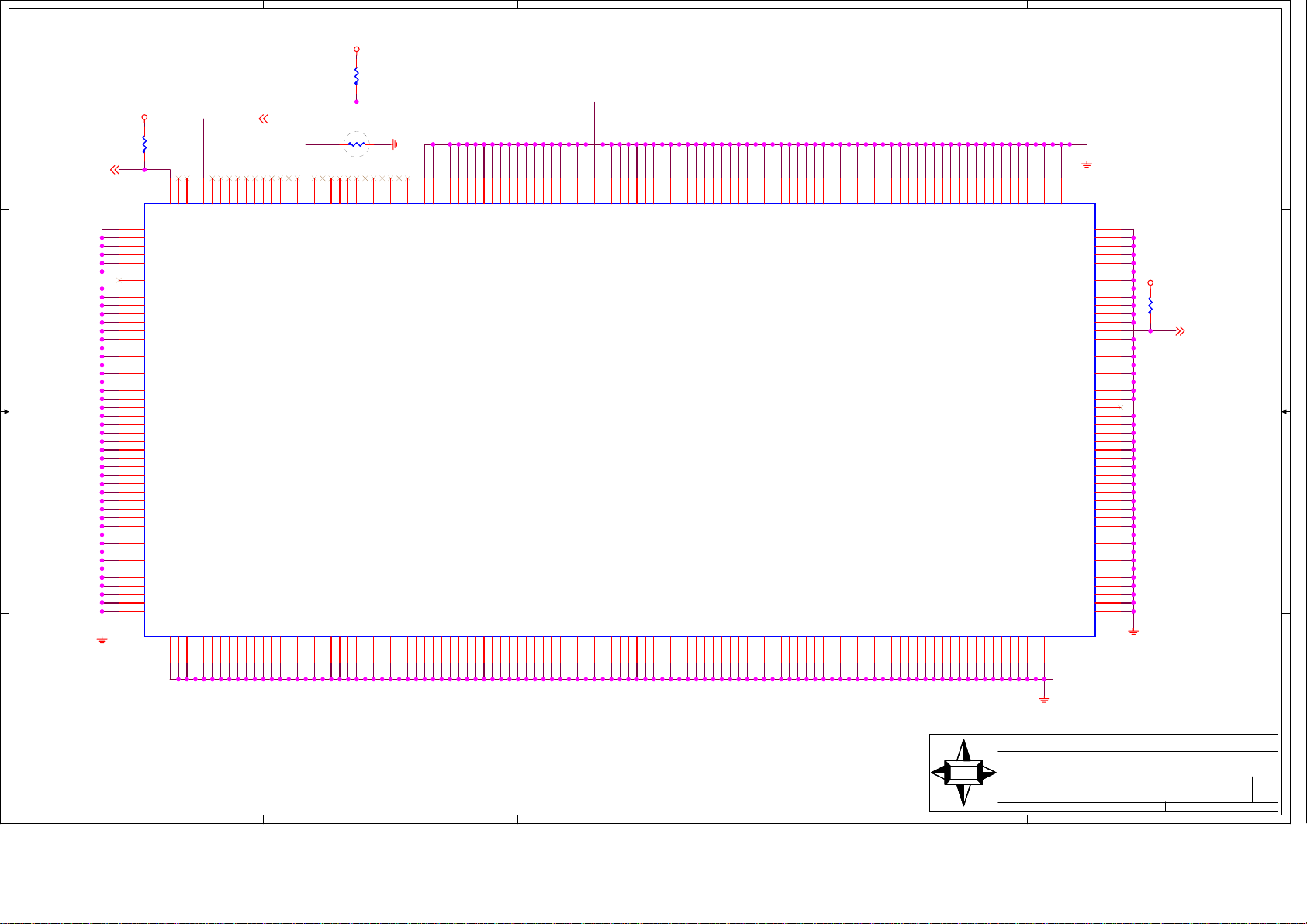

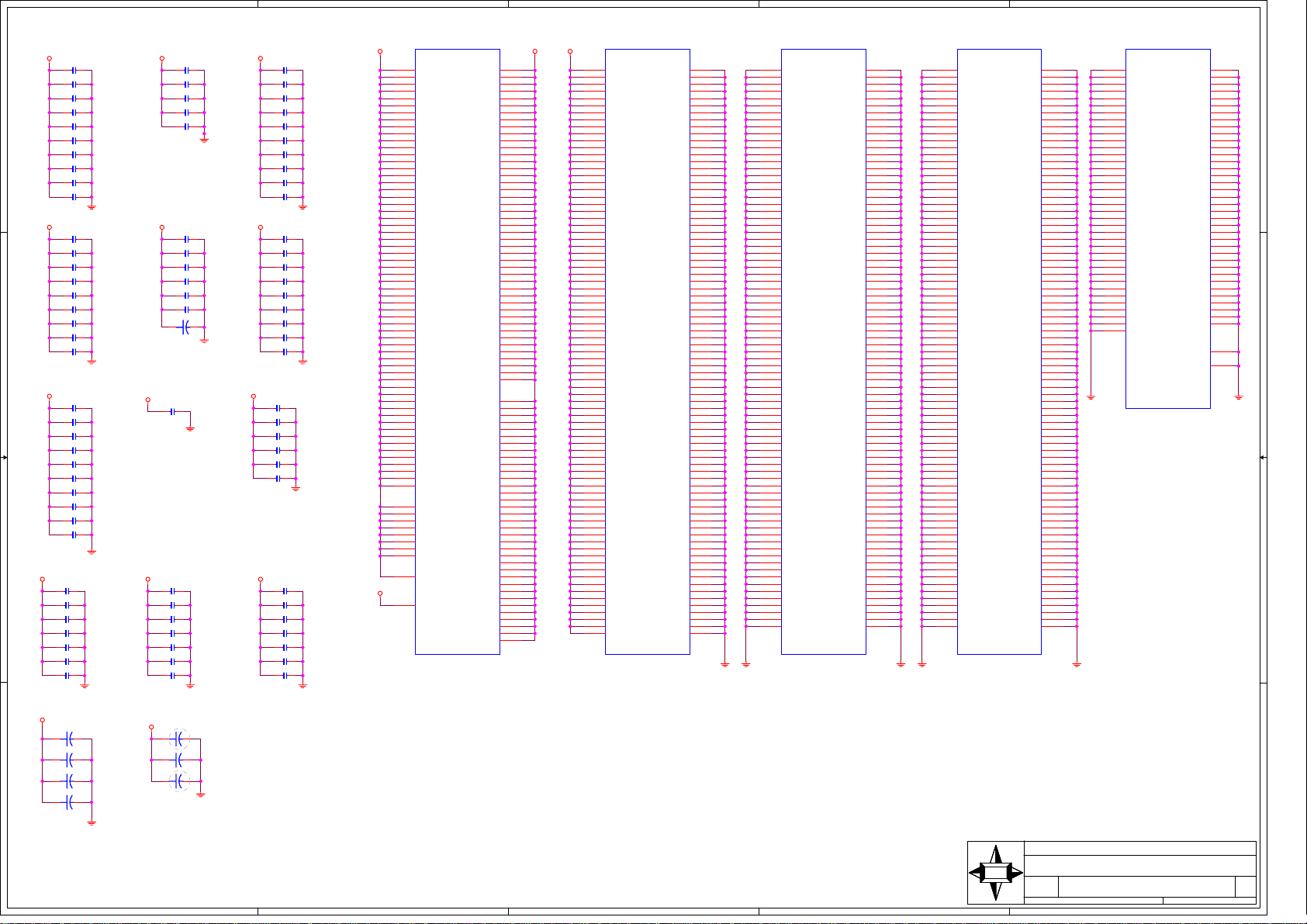

MSI MS-9196 Schematic 0a_0502

5

4

3

2

1

PAGE

01

02

03

D D

C C

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

TITLE

Cover / Table of Contents

System Block Diagram

System Voltage Table / Board Stackup

Power Delivery Block Diagram

System Clock Block Diagram

System Reset Block Diagram

System SMBus Block Diagram

XDP Block Diagram

CPU0 SIGNAL

CPU0 POWER / PECI

CPU0 GND

CPU1 SIGNAL

CPU1 POWER

CPU1 GND

5000P CPU

5000P FBD

5000P PCI-E

5000P POWER/GND

FB DIMM11~13

FB DIMM21~23

FB DIMM31~33

MSI

Version: 0.ASSI EEB (12"X13")

Intel 5000P + 632xESB Schematics

FB DIMM41~4322

23

24

25

26

27

28

29

30

31

32

33

34

B B

35

36

37

38

39~40

PCI-Express X8/X4 Slots

632xESB PCI / PCI-X

632xESB PCIE/ESI/LAN/USB/FRU

632xESB SATA/IDE/RTC/SMBUS

632xESB Power/GND

PCI / PCI-X SLOTs (PCI1/PCI2)

PCI Express X8 Slot and Thermtrip

GILGAL LAN

CLOCKGEN / CLOCK BUFFER

PILOT2 PCI-E/LPC/USB/DDR

PILOT2 BMC MODULES

PILOT2 UART & OSC

PILOT2 POWER

PILOT2 MSIC

PILOT2 LAN

FAN & HW MONITOR

CPU1 VRD

41~42 CPU2 VRD

43

44

45

46

POWER 1.8V

POWER 1.5V

POWER P_VTT

PLD / XDP

CPU BSEL47

48

49

50

51

52

A A

53

SYSTEM POWER / BIOS /TPM

POWER CONN & Front Panel

PECI

SGPIO CPLD

MISC

GPIO Maping

Reset and Pwr Good PLD Logic54

55

56

57

58

5

Power On/Off Sequence

System Reset Sequence

History

Reserved Page

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

4

3

2

Wednesday, May 02, 2007

MS-9196

COVER SHEET

COVER SHEET

COVER SHEET

1

Sheet of

Sheet of

Sheet of

158

158

158

00A

00A

00A

5

4

3

2

1

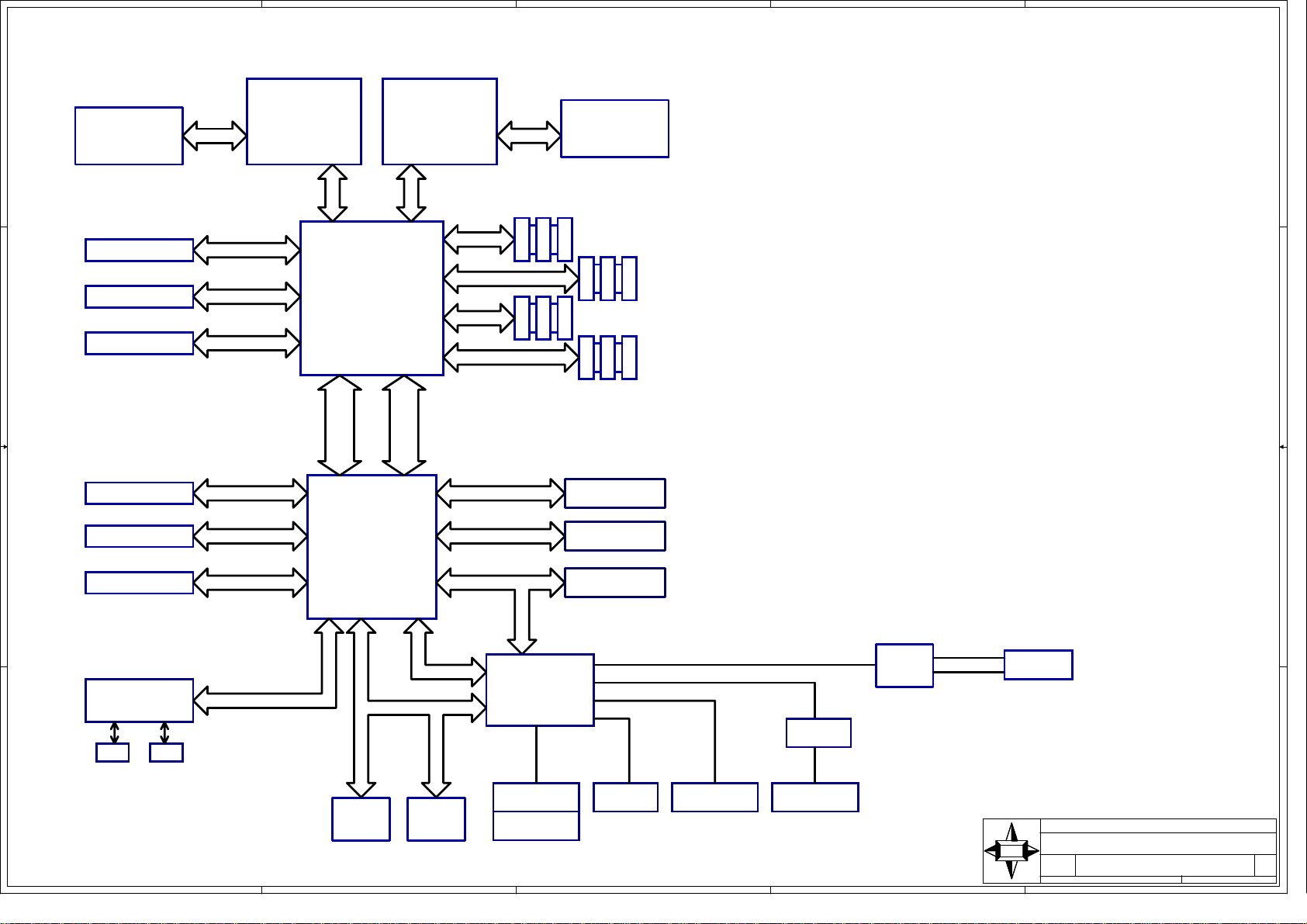

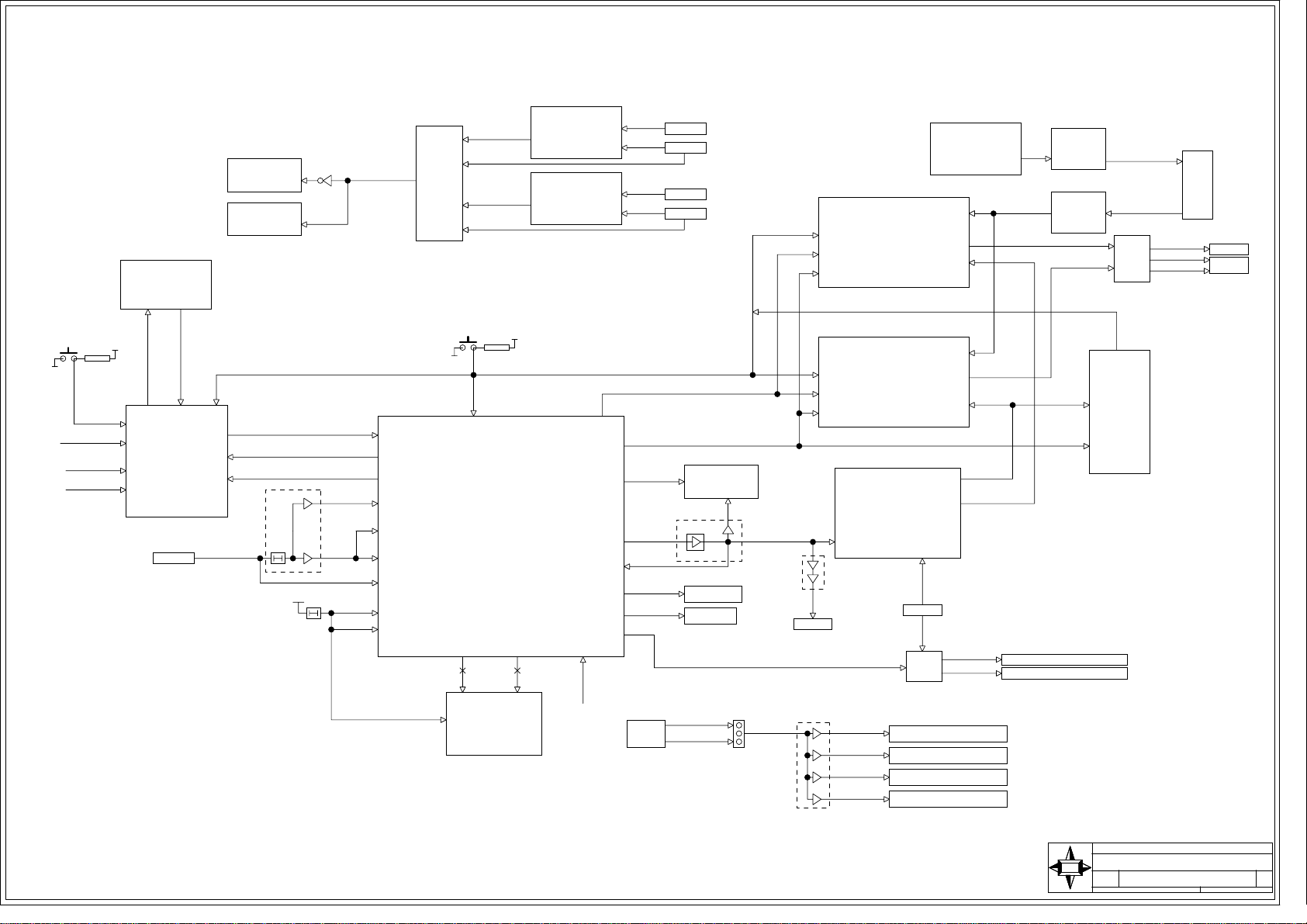

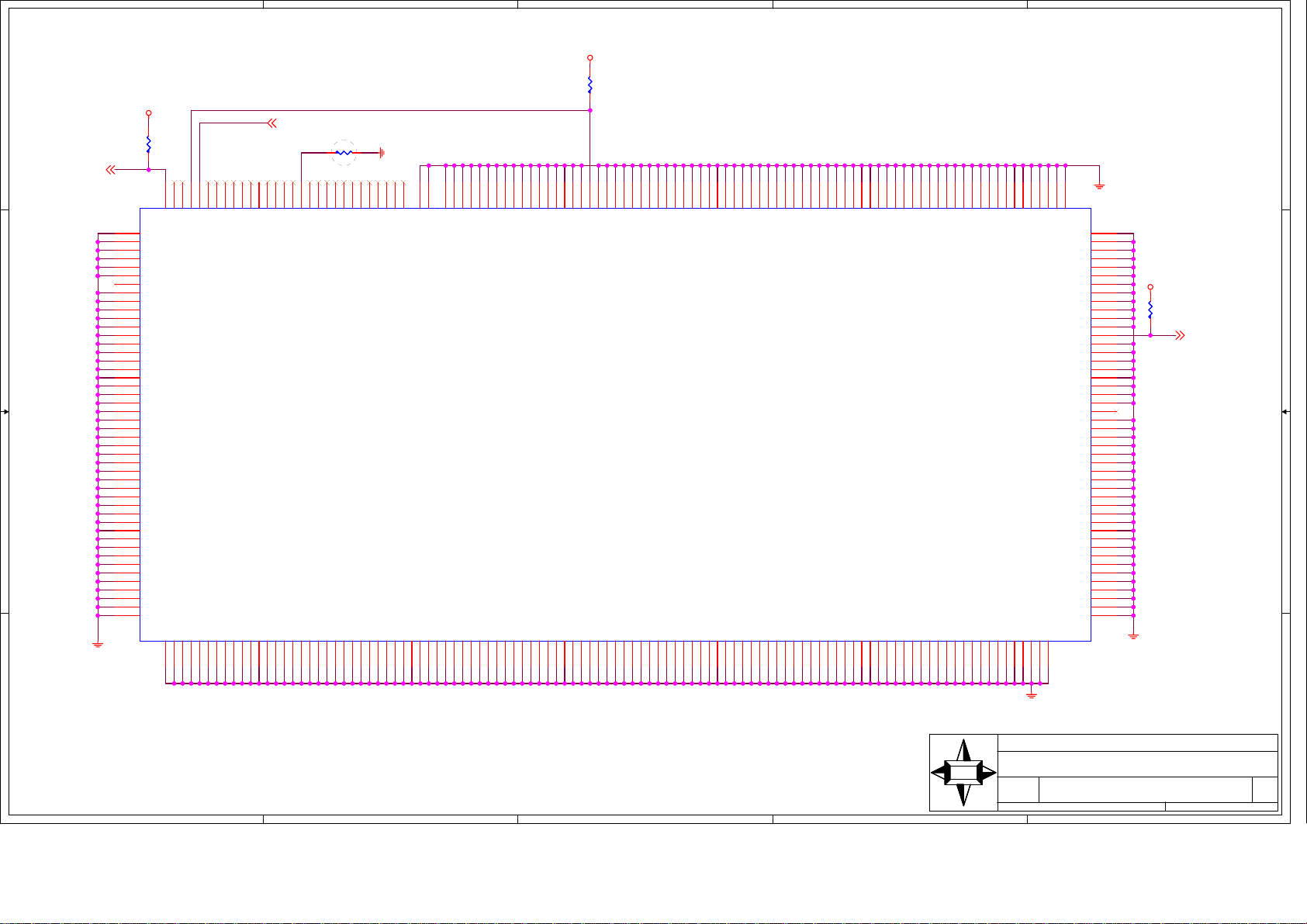

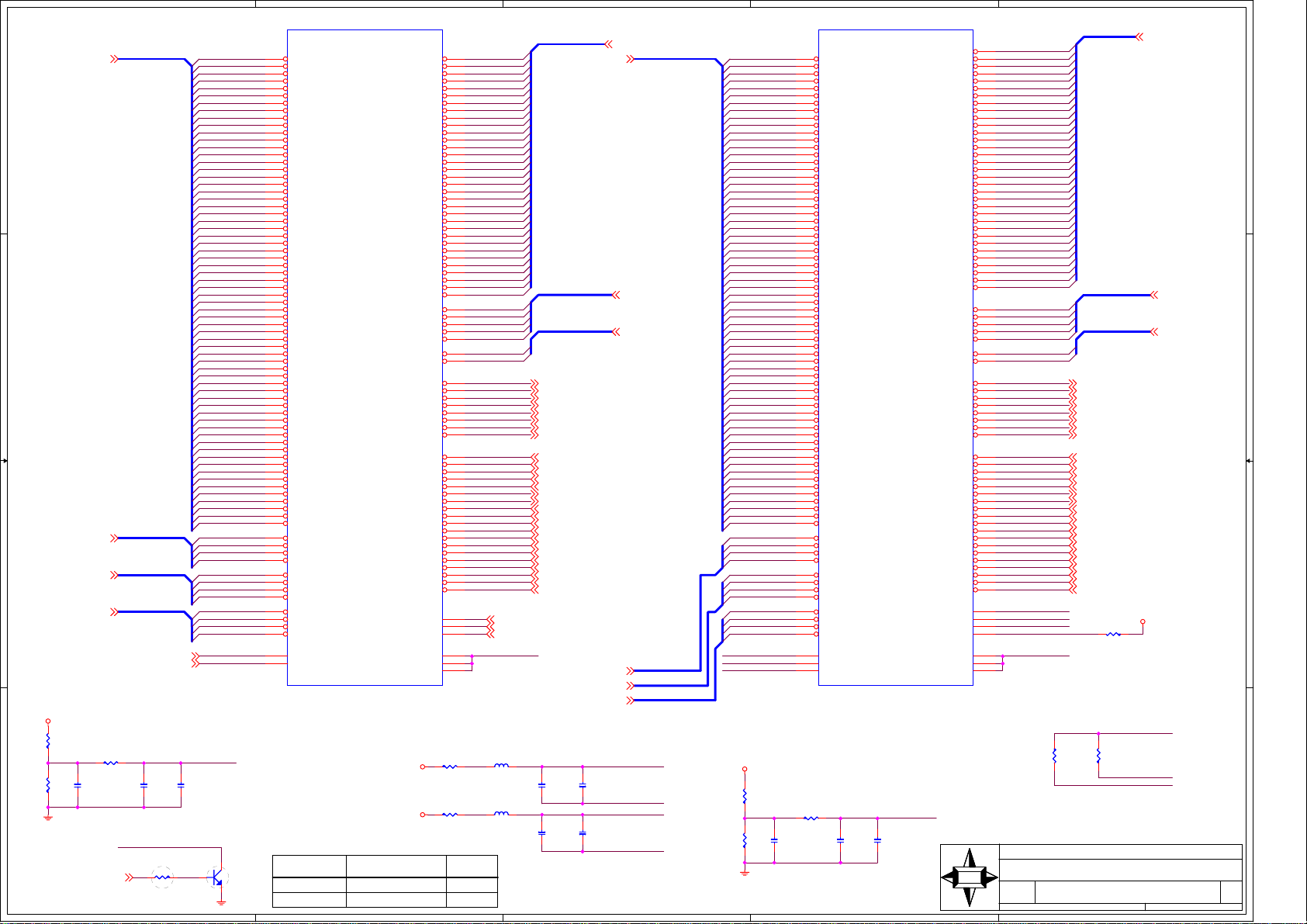

MS-9196 SYSTEM BLOCK DIAGRAM

CPU0 Intel

FC-LGA4 771

D D

VRD 11

VT1115M

5-Phase PWM

VRD VRD

Woodcrest/

Clovertown

FSB0

1066/1333MHz

Dempsey/

CPU1 Intel

FC-LGA4 771

Dempsey/

Woodcrest/

Clovertown

FSB1

1066/1333MHz

VRM 11

VT1115M

5-Phase PWM

Spec

* Dual LGA-771 CPU

* Intel 500P / 632XESB Chipset

* 8 Layer E-ATX Form Factor (12" X 13")

* 12 Fully-Buffered DIMM (4 Channel)

* USB 2.0 (Rear x2, Front x2, Internal x2)

* 4 PCI-E X 8 Slot

* 1 PCI-64 slot

FBD

PCI-E X8 SLOT PCI5

PCI-E X8 SLOT PCI4

C C

PCI-E X8 SLOT PCI6

For RAID Card

PCI-E X8 SLOT PCI3

PCI Express X8

BW = 4GB/s

PCI Express X4

BW = 2GB/s

PCI Express X4

BW = 2GB/s

PCI EXPRESS X8

BW = 4GB/s

5000P

PCIE X8 BUS

ESI X 4 BUS

FBD CH0

FBD CH1

FBD

FBD CH2

FBD CH3

Ultra DMA 66/100

FBD

FBD

ATA Primary

* 1 PCI-32 slot

* ServerEngines Pilot II

* Dual Giga-Lan Gilgal

* Serial ATA x4 + IDE x1

PCI-64 SLOT PCI2

B B

PCI-32 SLOT PCI1

GbE PHY (2ch)

Intel 82563EB

PCI-X 133

BW = 1.06MB/s

PCI-32

Gilgsl PHY BUS

632xESB

LPC Bus

PCI-E X1

SATA 3.0Gb/s

USB 2.0

USB X1

ServerEngines

PilotII

SATA 0~5

USB2.0 Port 0~5

Port #0,1 Front

Port #2,3 Rear

Port #4,5 Internal

SGPIO

cPLD

SGPIO1

SGPIO2

SGPIO Headers

PHY

RJ-45 RJ-45

A A

PS2 - KB Serial Port

FWH

5

TPM 1.2

4

PS2 - MS

VGA CONN

LAN Port

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

3

2

Wednesday, May 02, 2007

MS-9196

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

1

Sheet of

Sheet of

Sheet of

00A

00A

00A

258

258

258

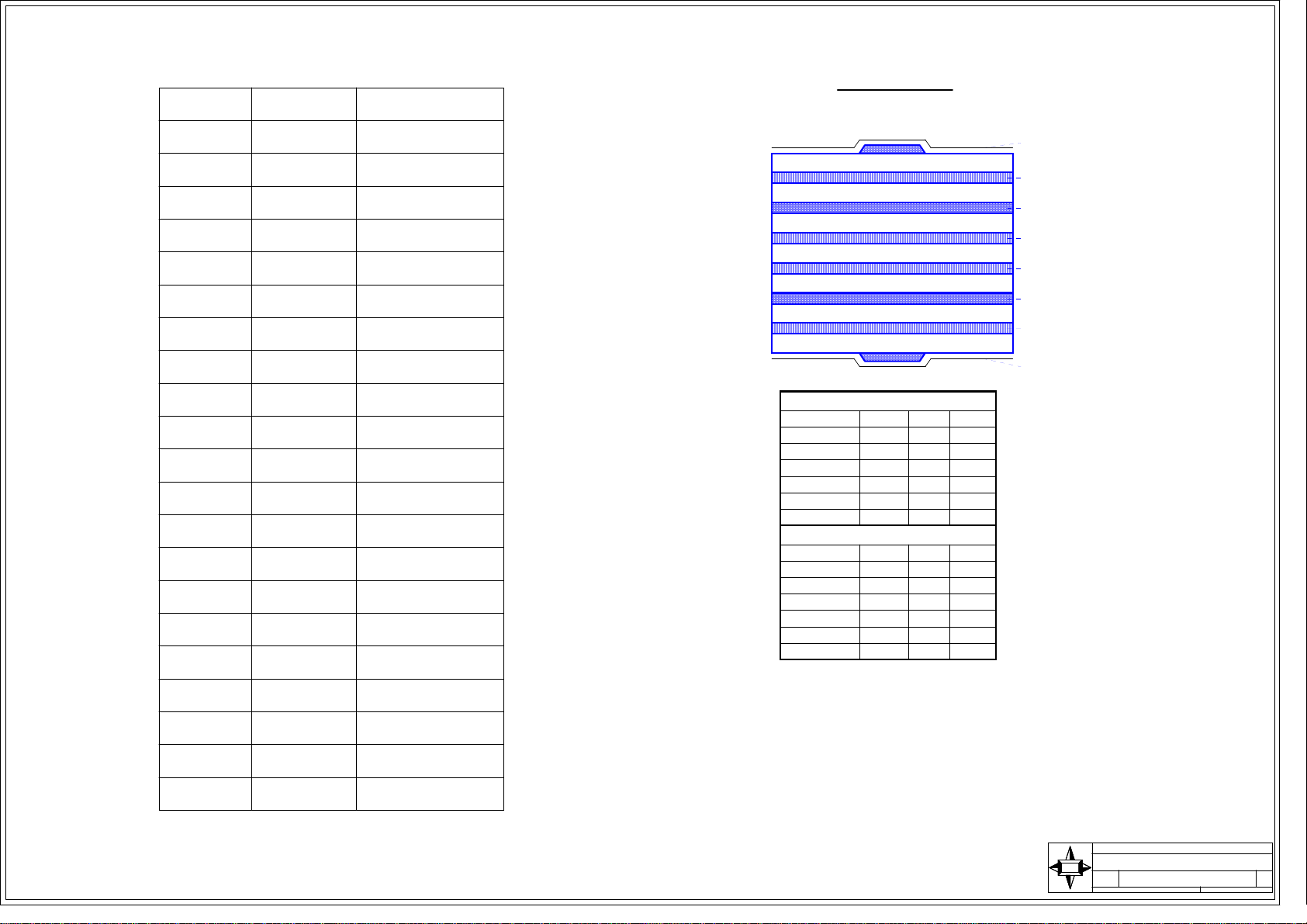

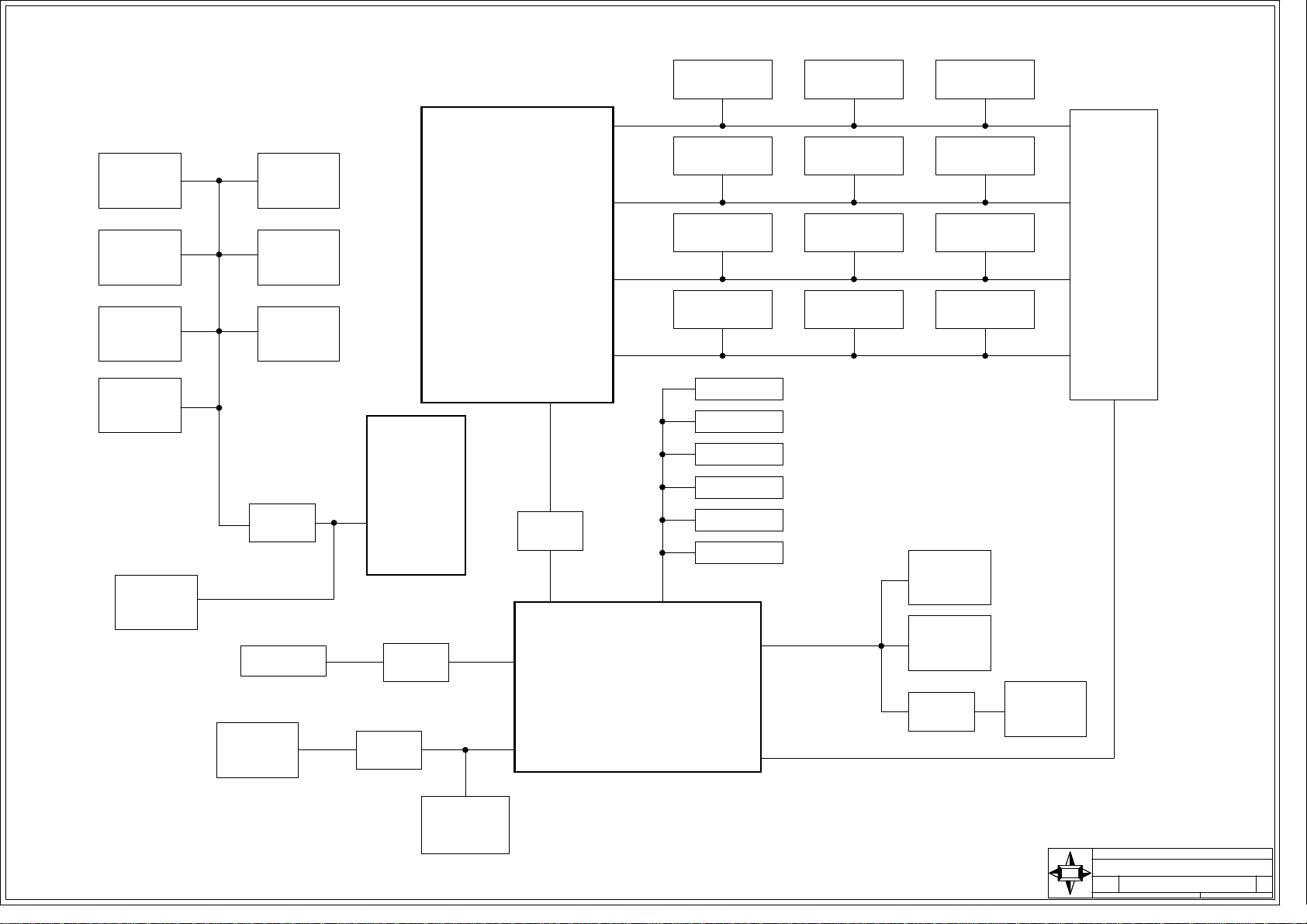

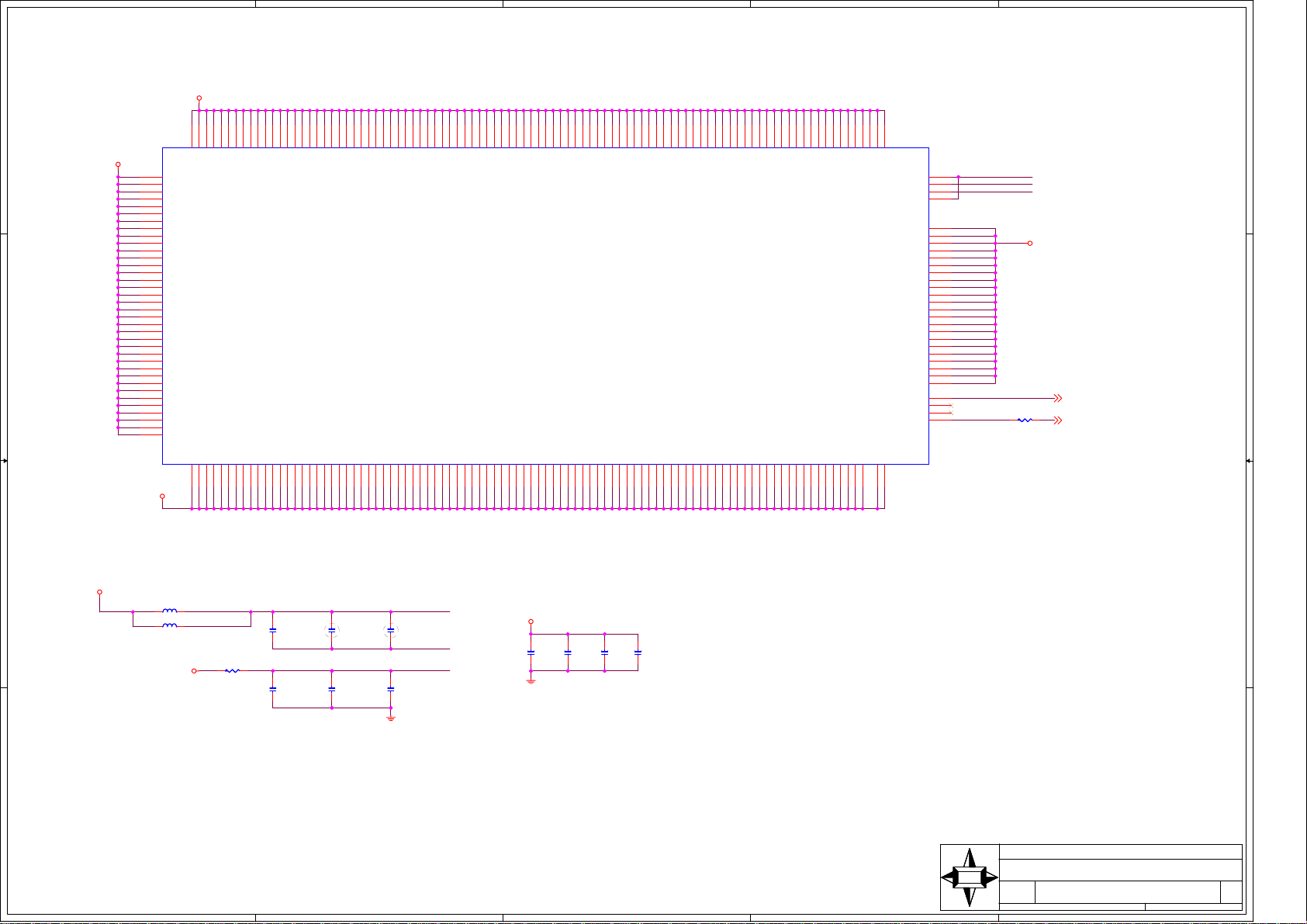

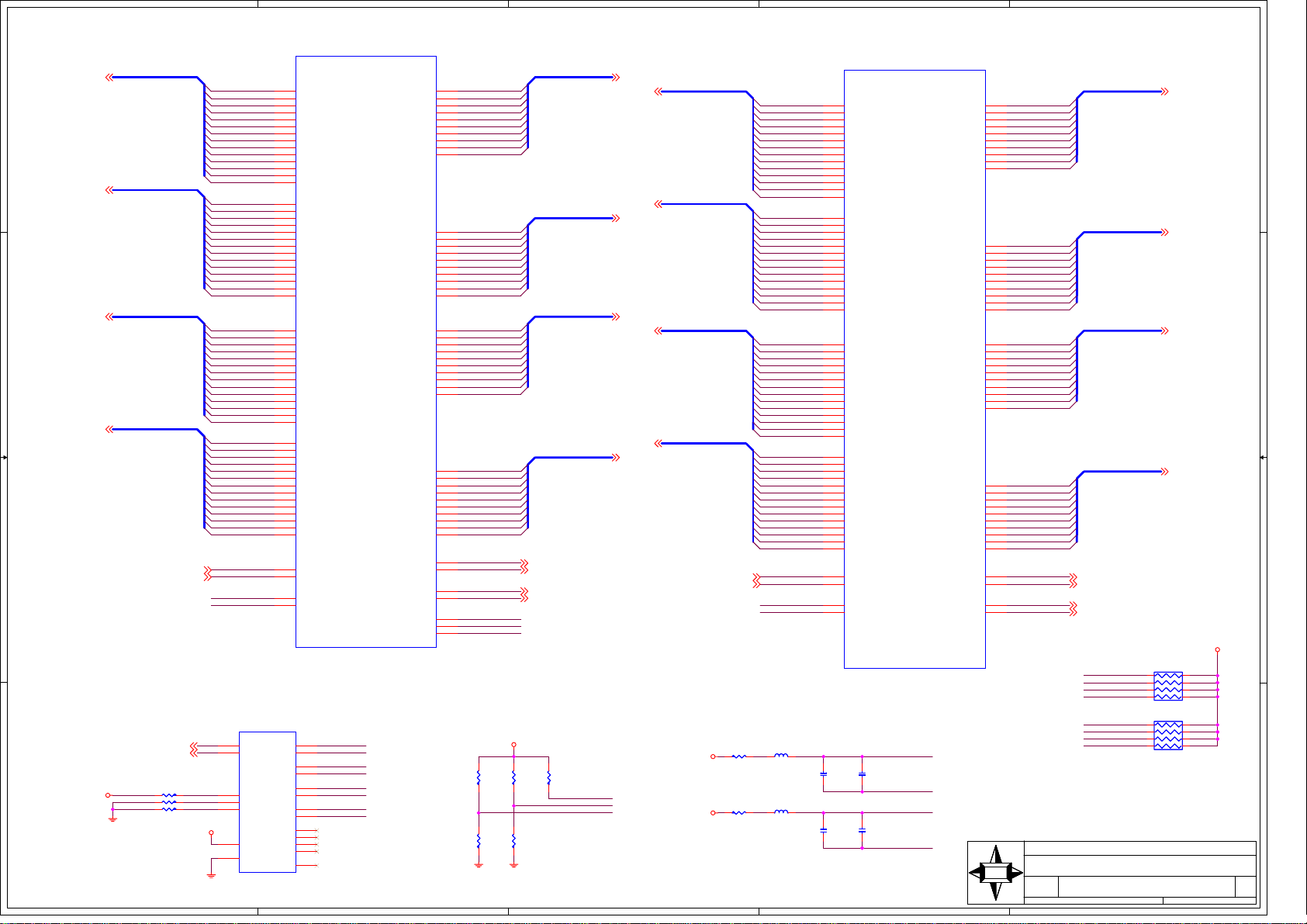

Voltage Table and Board Stackup

Voltage Level

Netname

Generated From

1

Board Stack-up

62+8/-5mils

+3.3V

+5V

+5V STBY

-12V

+12V1

+12V2

+12V3

+12V4 P12V4 AC

VID_CPU0 P12V1

VID_CPU1

A A

+1.2V

+1.5V

+1.5V AUX

+1.8V

+0.9V

+3.3V STBY

+3.3V AUX

P3V3

P5V

P5VSB

P-12V

P12V1

P12V2

P12V3

AC

AC

AC

AC

AC

AC

AC

VCORE0

VCORE1

P_VTT

P1V5

P1V5_AUX

P12V2

P5V

P12V4

P3V3_AUX

P1V8 P12V3

P0V9 P1V8

P3VSB

P5VSB

P3V3_AUX P3V3 / P3VSB

Solder Mask

L1

L2

L3

L4

L5

L6

L7

L8

Solder Mask

PREPREG 4mils

CORE 4mils

PREPREG 12mils

CORE 9.3mils

PREPREG 12mils

CORE 4mils

PREPREG 4mils

Outer Impedances

Target Actual Line Space

60ohms

55ohms

50ohms

100ohms-diff

90ohms-diff

85ohms-diff

59.76 4.0 N/A

54.96

50.80

100.50

88.58

85.48

Inner Impedances

Target Actual Line Space

50ohms

48ohms

100ohms-diff

90ohms-diff

85ohms-diff

50.80

48.66

97.82

89.08

84.86 5.0

N/A

5.0

N/A

6.0

6.0

4.0

5.0

5.0

6.0

6.0

4.5 N/A

N/A

5.0

9.0

4.0

5.0

8.0

6.5

0.65mils Solder Mask

1.5 oz. (1.8mils) Cu plus plating

1 oz. (1.3mils) Cu GND Plane

1 oz. (1.3mils) Cu INT3 Plane

1 oz. (1.3mils) Cu Power Plane

1 oz. (1.3mils) Cu Power Plane

1 oz. (1.3mils) Cu INT6 Plane

1 oz. (1.3mils) Cu GND Plane

1.5 oz. (1.8mils) Cu plus plating

0.65mils Solder Mask

+1.8V1 AUX

+1.2V1 AUX

+1.8V2 AUX

+1.2V2 AUX

P1V8LAN

P1V2LAN

P1V8AUX

P1V2AUX

P3V3_AUX

P3V3_AUX

P3V3_AUX

P3V3_AUX

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

1

Wednesday, May 02, 2007

MS-9196

Voltage Table and Board Stackup

Voltage Table and Board Stackup

Voltage Table and Board Stackup

Sheet of

Sheet of

Sheet of

00A

00A

00A

358

358

358

5

4

3

2

1

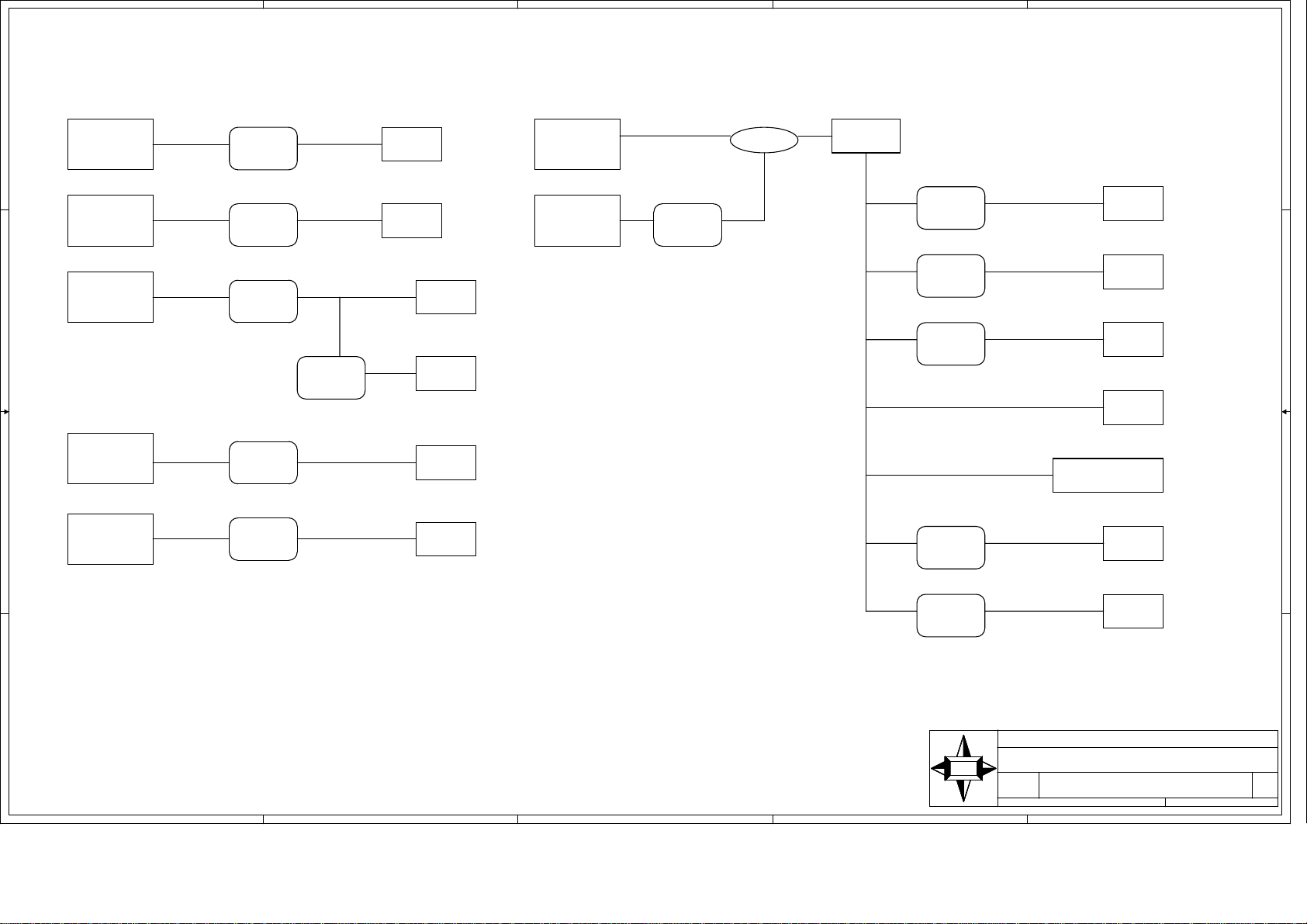

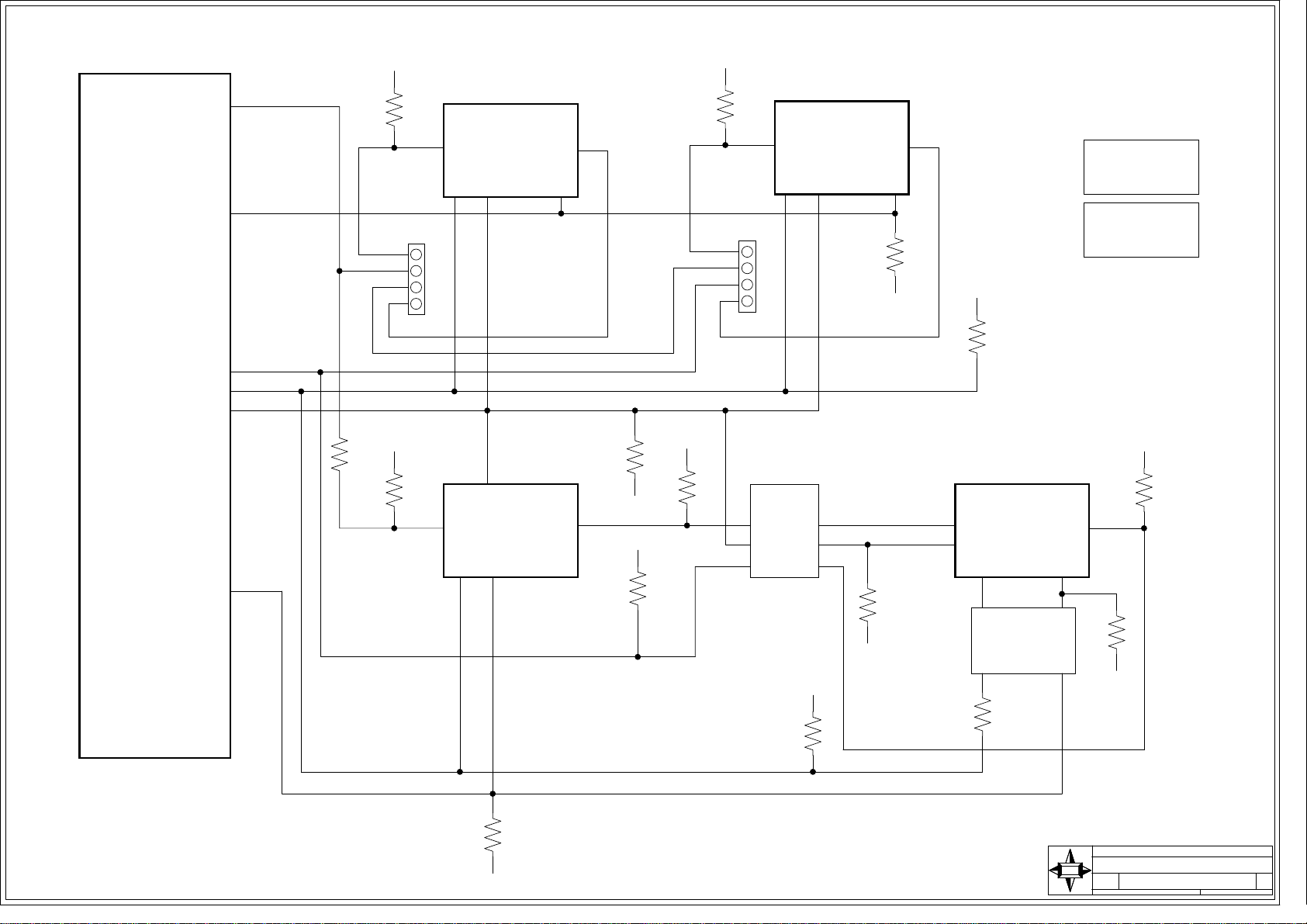

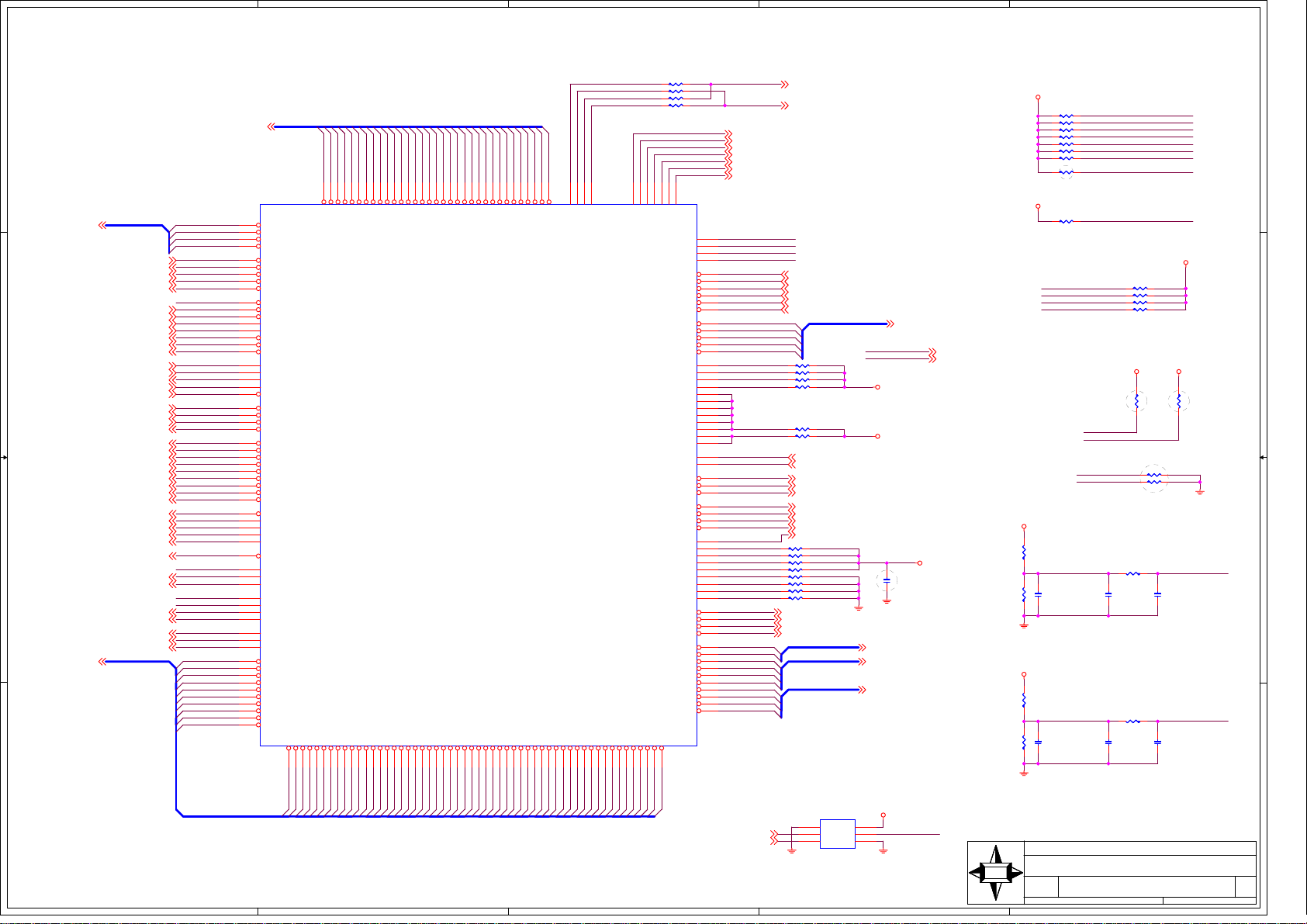

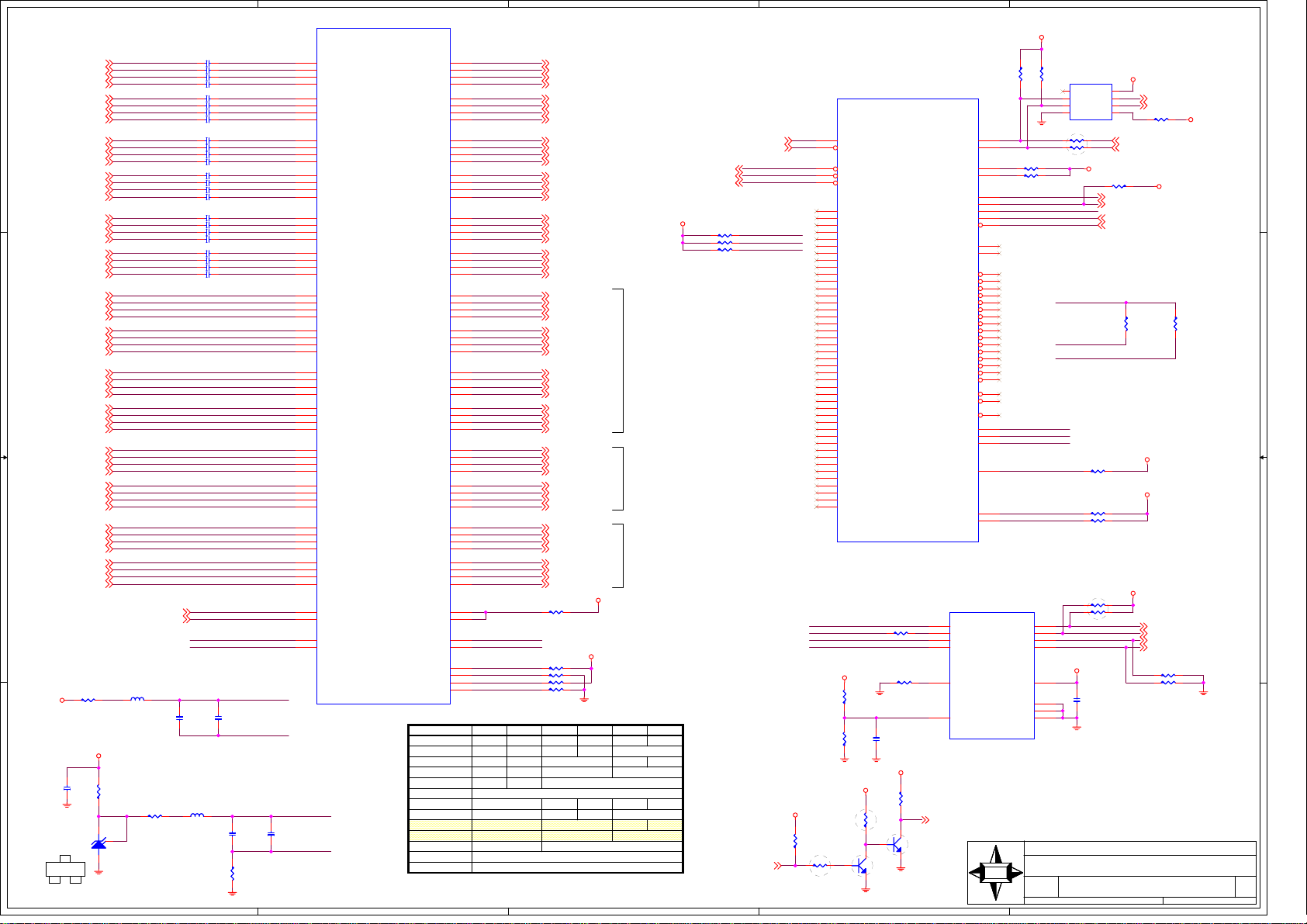

MS-9196 POWER DELIEVERY DIAGRAM

D D

P12V1

VRD11 CPU0

P3V3

SWITCH

P3V3_AUX

1.5V

P12V2

VRD11 CPU1

P5VSB

3.3V

REG

P3VSB

REG

1.8V

C C

P12V3

1.8V

REG

P1V8

FB DIMM

REG

1.2V

P1V5_AUX

P1V8LAN

P1V2LAN

ESB2

GILGAL

GILGAL

REG

1.8V

P0V9

FBD VTT

REG

BMC

PHY

P12V4

1.5V

REG

P1V5

MCH

ESB2

PCI-E, PCI-X,

PCI SLOTS

B B

P12V4

1.2V

REG

P_VTT

FSB VTT

1.8V

REG

1.2V

P1V8AUX

P1V2AUX

BMC

BMC

REG

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

5

4

3

2

MS-9196

POWER DELIVERY BLOCK

POWER DELIVERY BLOCK

POWER DELIVERY BLOCK

Sheet of

Sheet of

Sheet of

1

00A

00A

00A

458

458

458

1

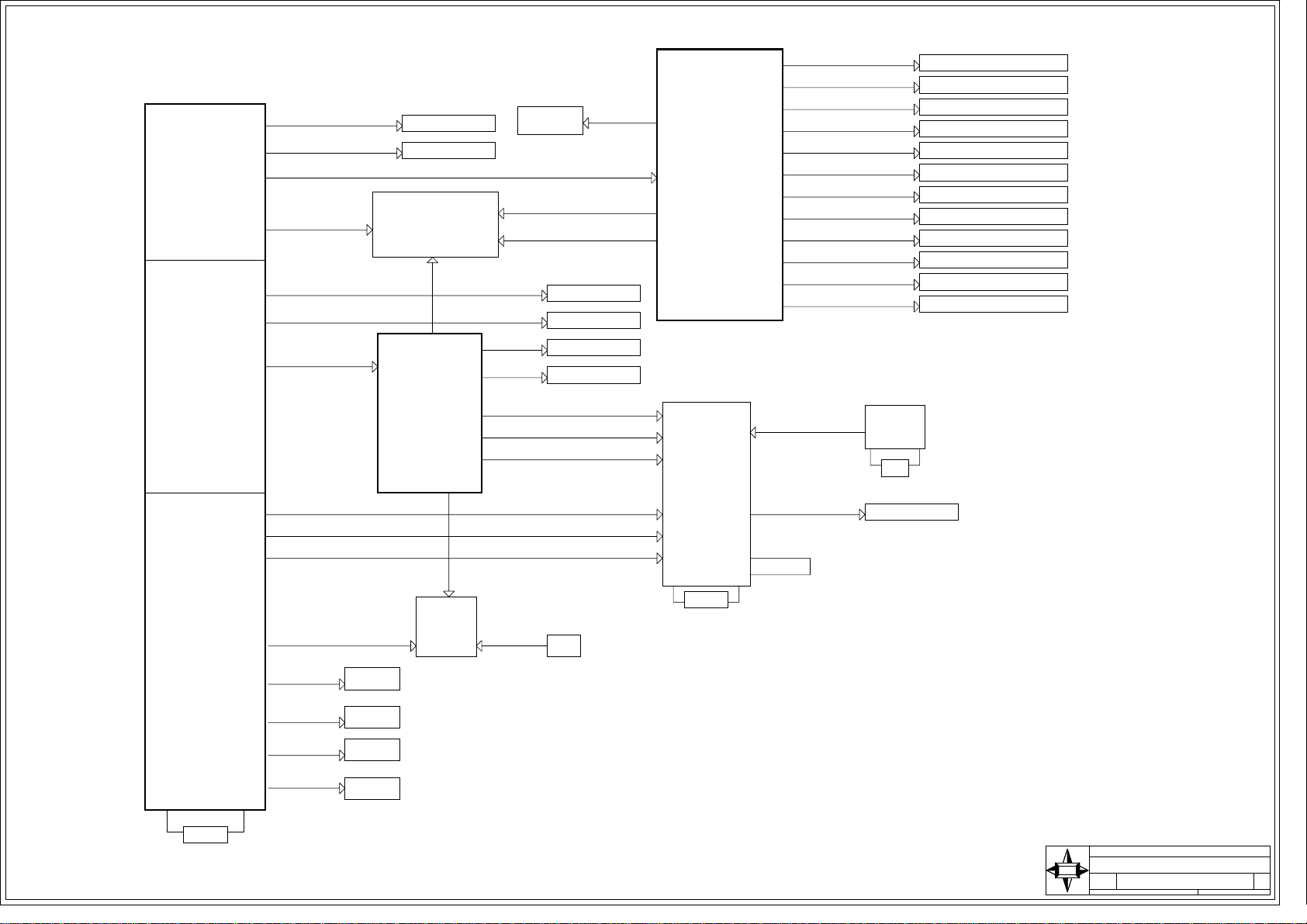

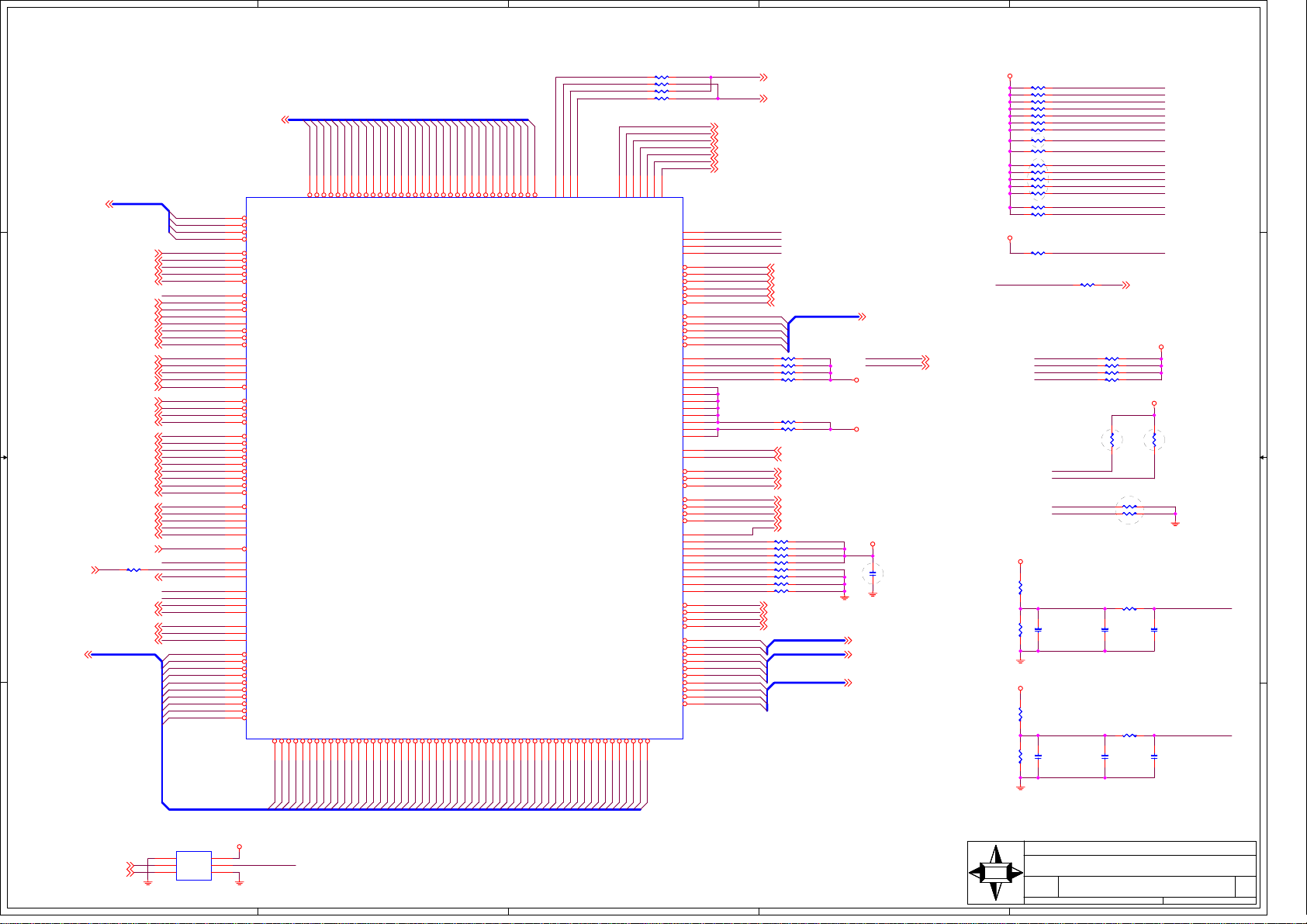

Clock Block Diagram

DB1900

CPU_2P/N

CPU_3P/N

CPU_1P/N

CPU_0P/N

BCLK 267/333MHz

CK_H_P0 (267/333MHz)

CK_H_P1 (267/333MHz)

CK_H_FBD (267/333MHz)

CK_H_MCH (267/333MHz)

CORECLKP/N

MCH_100CLK

(100MHz)

BCLK0/1

BCLK0/1

5000P

PECLKP/N

CPU0

CPU1

FBD01CLKP/N

FBD23CLKP/N

SRC_1P/N

SRC_2P/N

DIF_3P/N

SRC_4P/N

SRC_INP/N

DIF_6P/N

DIF_5P/N

DB800

ICS932S401

A A

Serial Ref Clk 100MHz

USB_48

PCIF_1

REF_1

PCIF_2

CK_48M_ESB

ESB2_PCLK

ESB_14MHZ

SIO_PCLK

DIF_4P/N

PILOT II

LCLK

DIF_2P/N

DIF_1P/N

DIF_0P/N

PCIE_CLK

CLKI

XDP (CPU)

SLOT6_100CLK

SLOT5_100CLK

SLOT4_100CLK

SLOT3_100CLK

ESI_100CLK_P/N (100MHz)

ESB2_100CLK_P/N (100MHz)

SATA_100CLK_P/N (100MHz)

CK_48M_PILOT

CLK

FBD01CLK_P/N

FBD23CLK_P/N

PCI6:PCI-E X8

PCI5:PCI-E X8

PCI4:PCI-E X8

PCI3:PCI-E X8

OSC2

XDP0_BCLK_P/N

DIF_17P/N

CLK_INP/N

DIF_15P/N

DIF_16P/N

ESICLK100P/N

PECLKP/N

SATACLKP/N

632xESB

CLK48

PCICLK

CLK14

32.768KHz

Crystal

DIF_0P/N

DIF_1P/N

DIF_2P/N

DIF_3P/N

DIF_4P/N

DIF_5P/N

DIF_6P/N

DIF_7P/N

DIF_8P/N

DIF_9P/N

DIF_10P/N

DIF_11P/N

SER_CLK_IN

PXPCLKO_0

PXPCLKO_6

PXPCLKI

PXPCLK0

CK_H_FBD0_P/N

CK_H_FBD1_P/N

CK_H_FBD2_P/N

CK_H_FBD3_P/N

CK_H_FBD4_P/N

CK_H_FBD5_P/N

CK_H_FBD6_P/N

CK_H_FBD7_P/N

CK_H_FBD8_P/N

CK_H_FBD9_P/N

CK_H_FBD10_P/N

CK_H_FBD11_P/N

SK_LAN_CLK

Gilgal LAN

PHY_CLK_OUT

25MHz

Crystal

PCI1:PCI-X

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

FB DIMM11

FB DIMM12

FB DIMM13

FB DIMM21

FB DIMM22

FB DIMM23

FB DIMM31

FB DIMM32

FB DIMM33

FB DIMM41

FB DIMM42

FB DIMM43

14.318MHz

Crystal

PCIF_0

PCI_0

PCI_2

PCI_3

XDP0_33MHZ_CLK

FWH_PCLK

PCI_CLK0

PLD_33MHZ_CLK

XDP

FWH

PCI2:PCI32

PLD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

1

Wednesday, May 02, 2007

MS-9196

SYSTEM CLOCK BLOCK DIAGRAM

SYSTEM CLOCK BLOCK DIAGRAM

SYSTEM CLOCK BLOCK DIAGRAM

558

558

558

Sheet of

Sheet of

Sheet of

00A

00A

00A

System Reset Block Diagram

1

VRM0_PWRGD

CK410B

PWRDOWN

DB800

PWRDOWN_N

CPU_VRD_PWRGD

EPLD

CPU0_SKTOCC#

VRM1_PWRGD

CPU1_SKTOCC#

POWER SUPPLY

PWOK

PSON#

ONCTL#

VDDPWR_GD

PILOT II

EPLD

PS_PWROK_BUF

GPIO8

PWBTOUTn

SLPS3n

SLPS5n

CPU_VRD_PWRGD

EPLD

100 ms

Delay

PWR_BT_SSI_#

SYS_PWRGD_BUFF

3.3V STBY

SYS_PWRGD_3_3V

RSMRST#

PWRBTN_N

SLP_S3_N

SLP_S4_N

PERST_N

PXPWROK

PWROK

VRMPWRGD

RSMRST_N

LAN_PWR_GD

PWR BTN

3.3VAUX

10Kohms

GND

PWR_BT_IN#

A A

PLTRST_BUFF1#

THERMTRIP0_N

THERMTRIP1_N

ONCTLn

PWBTINn

PCIRSTn

GPIO19

GPIO20

RST BTN

GND

ESB_SYS_RST_N

SYS_RESET_N

632xESB

PHY_PWR_DOWN

PHY_SLEEP

PHY_PWR_GD

10Kohms

3.3VAUX

PHYRST_0_N

PHY_RESET_N

Pwrgd

CPU1 VRD

Pwrgd

CPU_PWR_GD

PLTRST_IN_N

PXPCIRST_N

THRMTRIP_N

Gilgal

CPU0 VRD

OE

VID[6..0]

OE

VID[6..0]

INIT_N

INIT3_3V_N

PLTRST_N

PCIRST_N

GPIO33

THERMTRIP_N

VRD0_EN

P0VID[6..0]

VRD1_EN

P1VID[6..0]

CPU_PWRGD

INIT#_3_3V

ESB_PLTRST#

PCIRST_N

PXPCIRST_N

EPLD

EPLD

CPU0

EPLD

CPU1

FSB_INIT#

FWH

INIT#

EPLD

PCI32 Slot

PCIX Slot

FBD_RESET

PLTRST_BUFF2#

SYS_PWRGD_3_3V

RST_N

PLTRST_BUFF1#

ESB_SYS_RST_N

PLTRST_N

PCIE_RST#

DBR_N

INIT_N

PWRGOOD

DBR_N

INIT_N

PWRGOOD

IDE_RSTDRV_N

IDE

5000P

PLTRST_N

PCIE_RST4#

PCIE_RST1#

PCIE_RST2#

PCIE_RST3#

FSB VTT VRD

VTTPWRGD

CPU0

CPU1

THERMTRIP_N

RESET#

VTTPWRGD

THERMTRIP_N

RESET#

FSB1RESET_N

FSB0RESET_N

PWRGOOD

SYS_PWRGD_3_3V

EPLD

SYS_PWRGD_3_3V

GLUE

LOGIC

PCI EXPRESS (SLOT #3)

PCI EXPRESS (SLOT #4)

PCI EXPRESS (SLOT #5)

PCI EXPRESS (SLOT #6)

FSB1_THERMTRIP_N

FSB1_RESET_N

FSB0_RESET_N

FBD_BR0_RST#

FBD_BR1_RST#

Level

STAT

VTT_PWRGD

FSB0_THERMTRIP_N

Translation

GTL to 3.3V

Level

Translation

3.3V to GTL

ESB_SYS_RST_N

RESET_IN#

PWRGOOD

DIMM#00,01,02,10,11,12

DIMM#20,21,22,30,31,32

VTT_PWRGD_3_3V

PLD_VTT_PWRGD_3_3V

GLUE

LOGIC

RESET_OUT#

XDP

EPLD

THERMTRIP_N

THERMTRIP0_N

THERMTRIP1_N

ESB2

PILOT

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

1

Wednesday, May 02, 2007

MS-9196

RESET BLOCK DIAGRAM

RESET BLOCK DIAGRAM

RESET BLOCK DIAGRAM

Sheet of

Sheet of

Sheet of

00A

00A

00A

658

658

658

SMBus Block Diagram

1

CPU0 VCORE

VRD11

ADDR

CPU1 VCORE

VRD11

ADDR

1.8V VREG

ADDR

1.5V VREG

ADDR

CLK410B

ADDR 0XD2

ADDR 0XDC

ADDR 0XDE

MAIN_SMBus

DB800

DB1900

SPD0SDA/SPD0SCL

(Master SPD, 100KHz)

5000P

SPD1SDA/SPD1SCL

(Master SPD, 100KHz)

SPD2SDA/SPD2SCL

(Master SPD, 100KHz)

SPD3SDA/SPD3SCL

(Master SPD, 100KHz)

CFGSMBDATA/CFGSMBCLK

(Slave, 100KHz, 0XC0)

3.3V

DIMM #00

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

3.3V MCH_SPD0_SMB

DIMM #10 DIMM #11 DIMM #12

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

3.3V

DIMM #20

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

3.3V MCH_SPD2_SMB

DIMM #30 DIMM #31 DIMM #32

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

3.3V

MCH_SPD1_SMB

MCH_SPD3_SMB

PCI-X Slot

PCI Slot

DIMM #01

Serial EEPROM: 0XA2

AMB:ADDR 0XB2

Serial EEPROM: 0XA2 Serial EEPROM: 0XA4

AMB:ADDR 0XB2

DIMM #21

Serial EEPROM: 0XA2

AMB:ADDR 0XB2

Serial EEPROM: 0XA2 Serial EEPROM: 0XA4

AMB:ADDR 0XB2

DIMM #02

Serial EEPROM: 0XA4

AMB:ADDR 0XB4

AMB:ADDR 0XB4

DIMM #22

Serial EEPROM: 0XA4

AMB:ADDR 0XB4

AMB:ADDR 0XB4

SDA0/SCL0

SMBus

Selector

SDA1/SCL1

SDA2/SCL2

SDA3/SCL3

SDA/SCL

632xESB

A A

SMBDATA/SMBCLK

3.3V AUX

5VSB

PCA9515

SMBus Isolator

3.3V AUX

PCA9515

SMBus Isolator

3.3V AUX

SDA5/SCL5

SDA1/SCL1

SDA2/SCL2

FRU ROM

ADDR 0XAE

PCA9515

SMBus Isolator

IPMB Header

3.3V AUX

PCI-E X8 Slot

PCI-E X8 Slot

PCI-E X8 Slot

PCI-E X8 Slot

SDA3/SCL3

3.3V AUX

HW Monitor

ADT7462

ADDR

HW Monitor

ADT7462

ADDR

POWER

SUPPLY

ADDR

5VSB

PCA9515

SMBus Isolator

3.3V AUX

Front Panel

ADDR

SDA4/SCL4

PILOT II

1

SDA6/SCL6

3.3V AUX

PCA9515

SMBus Isolator

PECI

CY8C21234

ADDR 0X

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

MS-9196

SMBUS BLOCK DIAGRAM

SMBUS BLOCK DIAGRAM

SMBUS BLOCK DIAGRAM

Sheet of

Sheet of

Sheet of

758

758

758

00A

00A

00A

JTAG Block Diagram

1

P_VTT

XDP0_TDI_MAIN

TDI

TCK0

51 OHM

XDP0_TDI_FSB0

TDI

CPU0

TMS TRST#

TDO

TCK

XDP0_TCK0

1

2

CPU XDP0

Connector

0

3

4

XDP0_TDO_FSB0

XDP0_TDI_MAIN_JMP

TDO

TMS

TRST#

A A

0 OHM

P_VTT

51 OHM

XDP0_TDI_MCH

TDI

TMS

TCK1

XDP0_TDO_MAIN

XDP0_TMS_MAIN

XDP0_TRST#

TRST#

MCH

TCK

TDO

MCH in chain

51 OHM

GND

XDP0_TDO_MCH

P_VTT

51 OHM

P_VTT

51 OHM

XDP0_TDI_FSB1

P_VTT

51 OHM

1

2

1

3

4

GTL-TTL

Translator

TRST#

TDO

TDI

TMS TRST#

TDI

CPU1

XDP0_TDO_FSB1

TDO

TCK

51 OHM

GND

XDP0_TDI_ESB

XDP0_TRST_ESB#

1K OHM

GND

P_VTT

51 OHM

TDI

TRST#

XDP0_TMS_ESB

TMS

TMS

ESB2

GTL-TTL

Translator

ESB2 in chain

TDO

TCK

XDP0_TCK1_ESB

TCK

JUMPER 0

1-2, 3-4 : CPU0 in chain

2-3 : CPU0 bypass

JUMPER 1

1-2, 3-4 : CPU1 in chain

2-3 : CPU1 bypass

P3V3

1K OHM

1K OHM

51 OHM

GND

XDP0_TCK1

P_VTT

51 OHM

1

XDP0_TMS_GTL

0 OHM

XDP0_TDO_ESB

GND

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

MS-9196

XDP BLOCK DIAGRAM

XDP BLOCK DIAGRAM

XDP BLOCK DIAGRAM

858

858

858

Sheet of

Sheet of

Sheet of

00A

00A

00A

5

4

3

2

1

P0 Intel LGA771 Signal

VCC0_SENSE2

VSS0_SENSE2

VCC0_SENSE1

VSS0_SENSE1

FSB0_A[35..3]

FSB0_A35

FSB0_A33

FSB0_A34

AJ6

AJ5

AH5

A35#

A34#

A33#

FSB0_A31

FSB0_A30

FSB0_A32

AH4

AG5

AG4

A32#

A31#

FSB0_A29

FSB0_A28

AG6

AF4

A30#

A29#

A28#

FSB0_A27

FSB0_A26

FSB0_A25

AF5

AB4

AC5

A27#

A26#

FSB0_A23

FSB0_A24

AB5

AA5

A25#

A24#

A23#

FSB0_A22

FSB0_A21

AD6

AA4

A22#

FSB0_A18

FSB0_A20

FSB0_A19

A21#

A20#Y4A19#Y6A18#W6A17#

FSB0_A14

FSB0_A13

FSB0_A16

FSB0_A15

FSB0_A17

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

FSB0_A11

FSB0_A12

FSB0_A10

U6

FSB0_A7

FSB0_A4

FSB0_A8

FSB0_A6

FSB0_A9

FSB0_A5

A9#T5A8#R4A7#M4A6#L4A5#L5A4#P6A3#

M5

AN3

AN4

AL8

AL7

VSS_DIE_SENSE

VCC_DIE_SENSE

VSS_DIE_SENSE2

VCC_DIE_SENSE2

LGA771

PART 1

FSB Signal

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

D14#

D13#

D12#D8D11#

D10#

D9#

F21

F20

F18

B15

A14

C14

E22

C15

D17

D20

D22

G22

G21

F17

E21

E19

E18

F15

F14

F12

E16

E15

G17

G18

G16

G15

F11

E13

E10

D13

G14

D10

G13

B12

B10

A11

D11

A10

C12

C11

G23

AE1

AG1

AE8

AH7

AK1

AH2

AN7

AA2

G29

G30

FSB0_A[35..3]15

A8

G11

D19

C20

H4

G8

E3

G7

P2

K3

AK6

L1

K1

N2

M3

P3

AD1

AF1

AC1

AB2

R3

AL2

M2

D2

C2

D4

B2

C1

E4

C3

AD3

AB3

AJ7

AL1

AC2

Y1

V2

V1

W1

H30

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

DBI0#

DBI1#

DBI2#

DBI3#

RESET#

RSP#

BPRI#

TRDY#

DEFER#

SMI#

A20M#

FORCEPR#

LINT1/NMI

LINT0/INTR

IGNNE#

STPCLK#

INIT#

TCK

TDI

TDO

TMS

TRST#

IERR#

FERR#/PBE#

PROCHOT#

THERMTRIP#

ADS#

BNR#

HIT#

DBSY#

DRDY#

HITM#

LOCK#

BINIT#

MCERR#

SKTOCC#

THERMDA2

THERMDC2

THERMDA

THERMDC

DBR#

BOOTSELECT

TEST_BUS

VID_SELECT

LL_ID1

LL_ID0

MS_ID1

MS_ID0

BSEL0

BSEL1

BSEL2

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D D

FSB0_DBI#[3..0]15

C C

CPU1_TESTBUS12

B B

FSB0_D[63..0]15

FSB0_DBI#[3..0]

FSB0_RESET_N15

FSB0_RSP_N15

FSB0_BPRI_N15

FSB0_TRDY_N15

FSB0_DEFER_N15

FSB_A20M#12,25

FSB0_FORCEPR#39

FSB_NMI12,25

FSB_INTR12,25

FSB_IGNNE#12,25

FSB_STPCLK#12,25

FSB_INIT#12,25

XDP0_TCK012,46

XDP0_TDI_FSB046

XDP0_TDO_FSB046

XDP0_TMS_MAIN12,17,46

XDP0_TRST#12,17,46

FSB0_GTL_IERR#47

FSB_FERR#12,25

FSB0_PROCHOT#38

FSB0_THERMTRIP_N29

FSB0_ADS_N15

FSB0_BNR_N15

FSB0_HIT_N15

FSB0_DBSY_N15

FSB0_DRDY_N15

FSB0_HITM_N15

FSB0_LOCK_N15

FSB0_BINIT_N15

FSB0_MCERR_N15

CPU0_SKTOCC#33,38,46,47

P0THERMDA238

P0THERMDC238

P0THERMDA38

P0THERMDC38

CPU_DBR_RST#12,46

R73 0_0402R73 0_0402 R132 49.9RST_0402R132 49.9RST_0402

FSB0_VIDSEL39,46

P0_MS_ID146

P0_MS_ID046

FSB0_BSEL047

FSB0_BSEL147

FSB0_BSEL247

FSB0_D[63..0]

FSB0_DBI#0

FSB0_DBI#1

FSB0_DBI#2

FSB0_DBI#3

FSB0_RESET_N

FSB0_RSP_N

FSB0_BPRI_N

FSB0_TRDY_N

FSB0_DEFER_N

CPU0_SMI_N

FSB_A20M#

FSB0_FORCEPR#

FSB_NMI

FSB_INTR

FSB_IGNNE#

FSB_STPCLK#

FSB_INIT#

XDP0_TCK0

XDP0_TDI_FSB0

XDP0_TDO_FSB0

XDP0_TMS_MAIN

XDP0_TRST#

FSB0_GTL_IERR#

FSB_FERR#

FSB0_PROCHOT#

FSB0_THERMTRIP_N

FSB0_ADS_N

FSB0_BNR_N

FSB0_HIT_N

FSB0_DBSY_N

FSB0_DRDY_N

FSB0_HITM_N

FSB0_LOCK_N

FSB0_BINIT_N

FSB0_MCERR_N

CPU0_SKTOCC#

P0THERMDA2

P0THERMDC2

P0THERMDA

P0THERMDC

CPU_DBR_RST#

CPU0_BOOT

CPU0_TESTBUS

FSB0_VIDSEL

P0_LL_ID1

P0_LL_ID0

P0_MS_ID1

P0_MS_ID0

FSB0_BSEL0

FSB0_BSEL1

FSB0_BSEL2

FSB0_D63

FSB0_D62

FSB0_D61

FSB0_D60

FSB0_D59

FSB0_D58

FSB0_D57

FSB0_D56

FSB0_D55

FSB0_D54

AM5

AL4

AK4

VID6

VID5

GTLREF_DATA_C1

GTLREF_ADD_C1

GTLREF_DATA_C0

GTLREF_ADD_C0

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

R60 0_0402R60 0_0402

R64 0_0402R64 0_0402

R71 0_0402R71 0_0402

R70 0_0402R70 0_0402

AL6

AM3

AL5

AM2

CPU1A

CPU1A

VID4

VID3

VID2

VID1

VID0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1

BCLK0

RS2#

RS1#

RS0#

AP1#

AP0#

BR1#

BR0#

PWRGOOD

COMP7

COMP6

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

SOCKET771

SOCKET771

B4

VID6

VID5

VID4

VID3

VID2

VID1

VID0

F2

H2

G10

H1

AG3

AF2

AG2

AD2

AJ1

AJ2

J6

K6

M6

J5

K4

L2

P1

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

G28

F28

A3

F5

B3

U3

U2

H5

F3

N1

AE3

Y3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

VID6 38,39

VID5 39

VID4 39

VID3 39

VID2 39

VID1 39

VID0 39

P0_GTLREF_DATA1

P0_GTLREF_ADD1

P0_GTLREF_DATA0

P0_GTLREF_ADD0

FSB0_BPM_N5

FSB0_BPM_N4

FSB0_BPM_N3

FSB0_BPM_N2

FSB0_BPM_N1

FSB0_BPM_N0

FSB0_REQ_N4

FSB0_REQ_N3

FSB0_REQ_N2

FSB0_REQ_N1

FSB0_REQ_N0

H_TESTHI11

H_TESTHI10

FSB0_BPM_B2#

FSB0_BPM_B3#

H_TESTHI2_7

H_TESTHI0_1

CK_H_P0_N

CK_H_P0

FSB0_RS2_N

FSB0_RS1_N

FSB0_RS0_N

FSB0_AP1

FSB0_AP0

FSB0_BR_N1

FSB0_BR_N0

H_COMP7

H_COMP6

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

FSB0_DP_N3

FSB0_DP_N2

FSB0_DP_N1

FSB0_DP_N0

FSB0_ADSTB_N1

FSB0_ADSTB_N0

FSB0_DSTBP_N3

FSB0_DSTBP_N2

FSB0_DSTBP_N1

FSB0_DSTBP_N0

FSB0_DSTBN_N3

FSB0_DSTBN_N2

FSB0_DSTBN_N1

FSB0_DSTBN_N0

VCC0_SENSE 39

VSS0_SENSE 39

FSB0_BPM_N5 15,46

FSB0_BPM_N4 15,46

FSB0_BPM_N3 46

FSB0_BPM_N2 46

FSB0_BPM_N1 46

FSB0_BPM_N0 46

FSB0_REQ_N[4..0]

R142 51_0402R142 51_0402

R140 51_0402R140 51_0402

R141 51_0402R141 51_0402

R114 51_0402R114 51_0402

P_VTT

Place BPM Termination Near CPU

R21 51_0402R21 51_0402

R116 51_0402R116 51_0402

CK_H_P0_N 31

CK_H_P0 31

FSB0_RS2_N 15

FSB0_RS1_N 15

FSB0_RS0_N 15

FSB0_AP1 15

FSB0_AP0 15

FSB0_BR_N1 15

FSB0_BR_N0 15

CPU_PWRGD 12,25,46

R121 49.9RST_0402R121 49.9RST_0402

R118 49.9RST_0402R118 49.9RST_0402

R137 49.9RST_0402R137 49.9RST_0402

R127 49.9RST_0402R127 49.9RST_0402

R113 49.9RST_0402R113 49.9RST_0402

R136 49.9RST_0402R136 49.9RST_0402

R37 49.9RST_0402R37 49.9RST_0402

FSB0_DP_N3 15

FSB0_DP_N2 15

FSB0_DP_N1 15

FSB0_DP_N0 15

FSB0_ADSTB_N[1..0]

FSB0_DSTBP_N[3..0]

FSB0_DSTBN_N[3..0]

P_VTT

P_VTT

FSB0_ADSTB_N[1..0] 15

FSB0_DSTBP_N[3..0] 15

FSB0_DSTBN_N[3..0] 15

FSB0_REQ_N[4..0] 15

FSB0_BPM_B2#

FSB0_BPM_B3#

C155

C155

X_0.1u

X_0.1u

FSB0_BPM_B2# 46

FSB0_BPM_B3# 46

Processor 0 Termination

Place Termination Close to CPU At End of Bus

P_VTT

P3V3_AUX

R51

R51

49.9RST_0402

49.9RST_0402

R45

R45

100RST_0402

100RST_0402

R145

R145

49.9RST_0402

49.9RST_0402

R150

R150

100RST_0402

100RST_0402

R115 51_0402R115 51_0402

R147 51_0402R147 51_0402

R119 51_0402R119 51_0402

R125 51_0402R125 51_0402

R133 51_0402R133 51_0402

R135 51_0402R135 51_0402

R36 51_0402R36 51_0402

R117 X_51_0402R117 X_51_0402

R134 150_0402R134 150_0402

R372 X_220_0402R372 X_220_0402

R344 X_220_0402R344 X_220_0402

R371 X_220_0402R371 X_220_0402

R359 X_220_0402R359 X_220_0402

R342 X_220_0402R342 X_220_0402

R374 220_0402R374 220_0402

R343 220_0402R343 220_0402

R61 4.7K_0402R61 4.7K_0402

CPU_DBR_RST#

Place BPM Termination Near CPU

FSB0_BPM_N3

FSB0_BPM_N2

FSB0_BPM_N1

FSB0_BPM_N0

800mV at 1.2V FSB Vtt

P_VTT

Minmum trace and width as wide as possible

12 mils

P0_GTLREF_ADD0

C951uC95

1u

800mV at 1.2V FSB Vtt

P_VTT

Minmum trace and width as wide as possible

12 mils

C1451uC145

1u

R152

R152

0_0402

0_0402

P0_LL_ID0

P0_LL_ID1

P0_MS_ID1

P0_MS_ID0

FSB0_BR_N1

FSB0_BR_N0

FSB0_GTL_IERR#

FSB0_PROCHOT#

FSB0_THERMTRIP_N

FSB_FERR#

FSB0_RESET_N

CPU0_BOOT

CPU_PWRGD

FSB_A20M#

FSB_STPCLK#

FSB_IGNNE#

FSB_INIT#

FSB_INTR

FSB_SMI#

FSB_NMI

CPU0_SKTOCC#

ESB_SYS_RST# 25,33,49

R122 51_0402R122 51_0402

R120 51_0402R120 51_0402

R123 51_0402R123 51_0402

R124 51_0402R124 51_0402

R151

R151

X_4.7K_0402

X_4.7K_0402

R153 X_51_0402R153 X_51_0402

R155 X_51_0402R155 X_51_0402

R2060R206

0

C94

C94

220P

220P

R3920R392

0

C147

C147

220P

220P

P_VTT

P3V3

R154

R154

X_4.7K_0402

X_4.7K_0402

P0_GTLREF_DATA0

C104

C104

220P

220P

P0_GTLREF_DATA1P0_GTLREF_ADD1

C146

C146

220P

220P

FSB0_D26

FSB0_D27

FSB0_D25

FSB0_D22

FSB0_D24

FSB0_D23

FSB0_D21

FSB0_D19

FSB0_D20

FSB0_D18

FSB0_D17

FSB0_D16 FSB0_A3

FSB0_D15

FSB0_D13

FSB0_D14

FSB0_D46

FSB0_D45

FSB0_D44

FSB0_D43

FSB0_D42

FSB0_D40

FSB0_D52

FSB0_D50

FSB0_D47

FSB0_D51

FSB0_D48

FSB0_D49

A A

CPU0 SMI Voltage Translation

U13

U13

A

B4C

BE

PI5C3303

PI5C3303

VCC

GND

2

5

3

FSB_SMI#12,25,33

CPU0_DISABLE_N33,38

6

1

FSB0_D53

P5V

CPU0_SMI_N

FSB0_D37

FSB0_D29

FSB0_D28

FSB0_D31

FSB0_D34

FSB0_D38

FSB0_D33

FSB0_D35

FSB0_D30

FSB0_D32

FSB0_D36

FSB0_D39

FSB0_D41

BE=High, C=B

5

4

FSB0_D10

FSB0_D12

FSB0_D11

FSB0_D7

FSB0_D9

FSB0_D8

FSB0_D6

FSB0_D5

FSB0_D4

FSB0_D3

FSB0_D2

3

FSB0_D1

FSB0_D0

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

2

Wednesday, May 02, 2007

MS-9196

CPU0 SIGNAL

CPU0 SIGNAL

CPU0 SIGNAL

1

Sheet of

Sheet of

Sheet of

958

958

958

00A

00A

00A

5

4

3

2

1

P0 Intel LGA771 Power

VCORE0

D D

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

VCORE0

AF19

VCC

AF18

VCC

AF15

VCC

AF14

VCC

AF12

VCC

AF11

VCC

AE9

VCC

AE23

VCC

AE22

VCC

AE21

VCC

AE19

VCC

AE18

VCC

AE15

VCC

AE14

VCC

AE12

VCC

AE11

VCC

AD8

VCC

AD30

VCC

AD29

VCC

AD28

VCC

AD27

VCC

AD26

VCC

AD25

VCC

C C

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AC8

AB8

AA8

VCORE0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y28

Y29

Y30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

Y27

W30

W29

VCC

VCC

W28

VCC

VCC

W27

VCC

VCC

W26

VCC

VCC

W25

VCC

VCC

W24

VCC

VCC

VCC

W23

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U26

U27

U28

U29

U30

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

CPU1B

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A23

VCCA

B23

VSSA

D23

VCCPLL

C23

VCCIOPLL

F30

VTT

E30

VTT

A25

VTT

A26

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTTPWRGD

VTT_OUT1

VTT_OUT0

NONE

NONE

SOCKET771

SOCKET771

AN29

AN30

VTT_SEL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

LGA771

PART 2

Power

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

T30

U23

U24

U25

N30

N23

N24

N25

N26

N27

N28

N29

M30

M29

M28

M27

M26

M25

M24

M23

K27

K28

K29

K30

T23

T24

T25

T26

T27

T28

T29

J30

K23

K24

K25

K26

AN9

AN8

AN26

AN25

H0_VCCA

H0_VSSA

H0_VCCPLL

VTT_PWRGD

VTT_SEL0

P_VTT

R863 0R863 0

VTT_PWRGD 13,48

VTT_SEL 13,45

B B

Minmum trace and width as wide as possible < 12 mils

P_VTT

DC current if 100mA

L1 10uH-0805-0.1AL1 10uH-0805-0.1A

L2 10uH-0805-0.1AL2 10uH-0805-0.1A

P1V5

A A

5

R200R20

C21

C21

22u-1206

22u-1206

0

C10

C10

103P

103P

C37

C37

X_10u-1206

X_10u-1206

C7

4.7u-0805C74.7u-0805

H0_VCCA

C23

C23

X_1u

X_1u

H0_VSSA

H0_VCCPLL

C8

4.7u-0805C84.7u-0805

4

P_VTT

C35

C35

10u-1206

10u-1206

C164

C164

10u-1206

10u-1206

C703

C703

0.1u

0.1u

C705

C705

0.1u

0.1u

C706

C706

0.1u

0.1u

3

C174

C174

0.1u

0.1u

C175

C175

0.1u

0.1u

C176

C176

0.1u

0.1u

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

2

Wednesday, May 02, 2007

MS-9196

CPU0 POWER

CPU0 POWER

CPU0 POWER

1

10 58

10 58

10 58

Sheet of

Sheet of

Sheet of

00A

00A

00A

5

4

3

2

1

P0 Intel LGA771 GND

A12

A15

A18

A21

A24

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

P_VTT

PECI_CPU 14,34,50

R422

R422

51_0402

51_0402

AC4

AE4

D14

E23

G6

E24

G5

W2

D16

A20

F1

VSS

RESVDC9RESVD

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AE30

RESVD

RESVD

VSS

VSS

AE5

AE7

RESVD

VSS

AF10

AF13

RESVD

RESVD

VSS

VSS

AF16

AF17

RESVD

RESVD

VSS

VSS

AF20

AF23

RESVDD1RESVD

RESVD

VSS

VSS

VSS

AF24

AF25

RESVDE5RESVDE6RESVDE7RESVD

VSS

VSS

VSS

AF26

AF27

AF28

F23

VSS

AF29

AF3

B13

RESVDF6RESVD

VSS

AF30

R57

R57

X_49.9RST_0402

X_49.9RST_0402

P5

E1

RESVDJ3RESVDN4RESVD

RESVD

VSS

VSS

VSS

VSS

VSS

AF6

AF7

AG10

AG13

AG16

AE6

AN5

AN6

RESVDN5RESVD

RESVD

VSS

VSS

VSS

AG17

AG20

AG23

AJ3

RESVD

RESVD

VSS

VSS

AG24

AK3

F29

RESVD

VSS

AH1

AG7

AN28

RESVD

VSS

VSS

AH10

AH13

AN27

NONE

VSS

AH16

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

NONE

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH17

AH20

AH23

AH24

VSS

VSS

AJ10

VSS

AJ13

V30

VSS

AJ16

VSSV3VSS

VSS

AJ17

V29

VSS

AJ20

V28

AJ23

D D

FSB0_BPM_B1#46

C C

B B

P_VTT

R426

R426

51_0402

51_0402

V27

V26

V25

V24

V23

VSS

VSS

VSS

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

LGA771

PART 3

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ24

AJ27

AJ28

AJ29

AJ30

AK10

AK13

VSS

AK16

VSS

AK17

AK2

VSS

VSS

AK20

R30

VSS

AK23

R29

VSS

VSS

AK24

R28

VSS

VSS

AK27

R27

VSS

VSS

AK28

R26

VSS

VSS

AK29

R25

VSS

VSS

AK30

R24

AK5

R23

VSS

VSS

AK7

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

AL10

AL13

VSS

AL16

P30

VSS

AL17

P29

VSS

VSS

AL20

P28

VSS

VSS

AL23

P27

VSS

VSS

AL24

P26

VSS

VSS

AL27

P25

VSS

VSS

AL28

P24

VSS

VSS

AL3

P23

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM1

AM10

AM13

AM16

AM17

AM20

VSS

AM23

VSS

AM24

L30

VSS

AM27

VSSL3VSS

VSS

AM28

L29

VSS

AM4

L28

AM7

VSS

VSS

L27

AN1

VSS

VSS

L26

VSS

VSS

AN10

L25

VSS

VSS

AN13

L24

VSS

VSS

AN16

L23

VSS

VSS

AN17

VSSK7VSSK5VSSK2VSSJ7VSSJ4VSSH9VSSH8VSSH7VSSH6VSSH3VSS

VSS

VSSB5VSS

VSS

VSS

VSS

VSS

VSSB1VSS

VSS

B8

B17

B11

AN24

B14

AN2

AN20

AN23

H29

B20

VSS

H28

B24

H27

VSS

VSS

H26

H25

VSS

VSS

VSS

VSSC4VSS

SOCKET771

SOCKET771

C7

H24

CPU1C

CPU1C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H23

H22

H21

H20

H19

H18

H17

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C24

C22

C19

C16

C13

C10

P_VTT

R402

R402

51_0402

51_0402

FSB0_BPM_B0# 46

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

5

4

3

2

Wednesday, May 02, 2007

MS-9196

CPU0 GND

CPU0 GND

CPU0 GND

Sheet of

Sheet of

Sheet of

1

11 58

11 58

11 58

00A

00A

00A

5

4

3

2

1

P1 Intel LGA771 Signal

Processor 1 Termination

VCC1_SENSE2

VSS1_SENSE2

VCC1_SENSE1

VSS1_SENSE1

D D

FSB1_DBI#[3..0]15

C C

B B

FSB1_D[63..0]15

FSB1_DBI#[3..0]

FSB1_RESET_N15,46

FSB1_RSP_N15

FSB1_BPRI_N15

FSB1_TRDY_N15

FSB1_DEFER_N15

FSB1_FORCEPR#41

FSB_STPCLK#9,25

XDP0_TDI_FSB146

XDP0_TDO_FSB146

XDP0_TMS_MAIN9,17,46

FSB1_GTL_IERR#47

FSB1_PROCHOT#38

FSB1_THERMTRIP_N29

FSB1_DBSY_N15

FSB1_DRDY_N15

FSB1_HITM_N15

FSB1_LOCK_N15

FSB1_BINIT_N15

FSB1_MCERR_N15

CPU1_SKTOCC#33,38,46

P1THERMDA238

P1THERMDC238

CPU_DBR_RST#9,46

CPU1_TESTBUS9

FSB1_VIDSEL41,46

FSB1_D[63..0]

FSB_A20M#9,25

FSB_NMI9,25

FSB_INTR9,25

FSB_IGNNE#9,25

FSB_INIT#9,25

XDP0_TCK09,46

XDP0_TRST#9,17,46

FSB_FERR#9,25

FSB1_ADS_N15

FSB1_BNR_N15

FSB1_HIT_N15

P1THERMDA38

P1THERMDC38

P1_MS_ID146

P1_MS_ID046

FSB1_BSEL047

FSB1_BSEL147

FSB1_BSEL247

FSB1_A[35..3]15

FSB1_DBI#0

FSB1_DBI#1

FSB1_DBI#2

FSB1_DBI#3

FSB1_RESET_N

FSB1_RSP_N

FSB1_BPRI_N

FSB1_TRDY_N

FSB1_DEFER_N

CPU1_SMI_N

FSB_A20M#

FSB1_FORCEPR#

FSB_NMI

FSB_INTR

FSB_IGNNE#

FSB_STPCLK#

FSB_INIT#

XDP0_TCK0

XDP0_TDI_FSB1

XDP0_TDO_FSB1

XDP0_TMS_MAIN

XDP0_TRST#

FSB1_GTL_IERR#

FSB_FERR#

FSB1_PROCHOT#

FSB1_THERMTRIP_N

FSB1_ADS_N

FSB1_BNR_N

FSB1_HIT_N

FSB1_DBSY_N

FSB1_DRDY_N

FSB1_HITM_N

FSB1_LOCK_N

FSB1_BINIT_N

FSB1_MCERR_N

CPU1_SKTOCC#

P1THERMDA2

P1THERMDC2

P1THERMDA

P1THERMDC

CPU_DBR_RST#

CPU1_BOOT

CPU1_TESTBUS

FSB1_VIDSEL

P1_LL_ID1

P1_LL_ID0

P1_MS_ID1

P1_MS_ID0

FSB1_BSEL0

FSB1_BSEL1

FSB1_BSEL2

FSB1_D63

FSB1_D62

FSB1_D61

FSB1_D60

FSB1_D59

FSB1_D58

FSB1_D57

FSB1_D56

FSB1_D55

FSB1_D54

AG1

A8

G11

D19

C20

G23

H4

G8

E3

G7

P2

K3

AK6

L1

K1

N2

M3

P3

AE1

AD1

AF1

AC1

AB2

R3

AL2

M2

D2

C2

D4

B2

C1

E4

C3

AD3

AB3

AE8

AJ7

AH7

AL1

AK1

AC2

Y1

AH2

AN7

AA2

V2

V1

W1

G29

H30

G30

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

DBI0#

DBI1#

DBI2#

DBI3#

RESET#

RSP#

BPRI#

TRDY#

DEFER#

SMI#

A20M#

FORCEPR#

LINT1/NMI

LINT0/INTR

IGNNE#

STPCLK#

INIT#

TCK

TDI

TDO

TMS

TRST#

IERR#

FERR#/PBE#

PROCHOT#

THERMTRIP#

ADS#

BNR#

HIT#

DBSY#

DRDY#

HITM#

LOCK#

BINIT#

MCERR#

SKTOCC#

THERMDA2

THERMDC2

THERMDA

THERMDC

DBR#

BOOTSELECT

TEST_BUS

VID_SELECT

LL_ID1

LL_ID0

MS_ID1

MS_ID0

BSEL0

BSEL1

BSEL2

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

FSB1_A[35..3]

D52#

D51#

D50#

D49#

A14

C14

C15

D17

FSB1_A33

FSB1_A35

FSB1_A34

AJ6

AJ5

AH5

A35#

A34#

D48#

D47#

D20

D22

G22

FSB1_A31

FSB1_A32

AH4

AG5

A33#

A32#

A31#

D46#

D45#

D44#

E22

G21

FSB1_A28

FSB1_A29

FSB1_A30

AG4

AG6

AF4

A30#

A29#

D43#

D42#

F21

F20

E21

FSB1_A27

FSB1_A26

AF5

AB4

A28#

A27#

A26#

D41#

D40#

D39#

E19

E18

FSB1_A23

FSB1_A24

FSB1_A25

AC5

AB5

A25#

A24#

D38#

D37#

F18

F17

FSB1_A22

FSB1_A19

FSB1_A16

FSB1_A15

FSB1_A18

FSB1_A21

FSB1_A20

FSB1_A17

FSB1_A14

AA5

AD6

AA4

AB6

A23#

A22#

A21#

A20#Y4A19#Y6A18#W6A17#

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

LGA771

PART 1

FSB Signal

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

F15

F14

E16

E15

G17

G18

G16

G15

G14

G13

FSB1_A12

FSB1_A13

D27#

D26#

D25#

E13

D13

FSB1_A11

FSB1_A9

FSB1_A8

FSB1_A10

U6

A9#T5A8#R4A7#M4A6#L4A5#L5A4#P6A3#

D24#

D23#

D22#

F12

F11

E10

D10

FSB1_A3

FSB1_A5

FSB1_A7

FSB1_A6

FSB1_A4

M5

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

AL8

AL7

VSS_DIE_SENSE2

VCC_DIE_SENSE2

D14#

D13#

D12#D8D11#

B12

D11

C12

AN3

AN4

VSS_DIE_SENSE

VCC_DIE_SENSE

D10#

D9#

D8#

B10

A11

A10

C11

R231 0_0402R231 0_0402

R232 0_0402R232 0_0402

R244 0_0402R244 0_0402

R241 0_0402R241 0_0402

AM5

AL4

AK4

AL6

AM3

VID6

VID5

VID4

VID3

GTLREF_DATA_C1

GTLREF_ADD_C1

GTLREF_DATA_C0

GTLREF_ADD_C0

PWRGOOD

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

B4

AL5

AM2

CPU2A

CPU2A

VID2

VID1

VID0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1

BCLK0

RS2#

RS1#

RS0#

AP1#

AP0#

BR1#

BR0#

COMP7

COMP6

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

SOCKET771

SOCKET771

P1VID6

P1VID5

P1VID4

P1VID3

P1VID2

P1VID1

P1VID0

F2

H2

G10

H1

AG3

AF2

AG2

AD2

AJ1

AJ2

J6

K6

M6

J5

K4

L2

P1

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

G28

F28

A3

F5

B3

U3

U2

H5

F3

N1

AE3

Y3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

P1VID6 38,41

P1VID5 41

P1VID4 41

P1VID3 41

P1VID2 41

P1VID1 41

P1VID0 41

P1_GTLREF_DATA1

P1_GTLREF_ADD1

P1_GTLREF_DATA0

P1_GTLREF_ADD0

FSB1_BPM_N5

FSB1_BPM_N4

FSB1_BPM_N3

FSB1_BPM_N2

FSB1_BPM_N1

FSB1_BPM_N0

FSB1_REQ_N4

FSB1_REQ_N3

FSB1_REQ_N2

FSB1_REQ_N1

FSB1_REQ_N0

H1_TESTHI11

H1_TESTHI10

FSB1_BPM_B2#

FSB1_BPM_B3#

H1_TESTHI2_7

H1_TESTHI2_7

H1_TESTHI0_1

H1_TESTHI0_1

CK_H_P1_N

CK_H_P1

FSB1_RS2_N

FSB1_RS1_N

FSB1_RS0_N

FSB1_AP1

FSB1_AP0

FSB1_BR_N1

FSB1_BR_N0

H1_COMP7

H1_COMP6

H1_COMP5

H1_COMP4

H1_COMP3

H1_COMP2

H1_COMP1

H1_COMP0

FSB1_DP_N3

FSB1_DP_N2

FSB1_DP_N1

FSB1_DP_N0

FSB1_ADSTB_N1

FSB1_ADSTB_N0

FSB1_DSTBP_N3

FSB1_DSTBP_N2

FSB1_DSTBP_N1

FSB1_DSTBP_N0

FSB1_DSTBN_N3

FSB1_DSTBN_N2

FSB1_DSTBN_N1

FSB1_DSTBN_N0

VCC1_SENSE 41

VSS1_SENSE 41

FSB1_BPM_N5 15,46

FSB1_BPM_N4 15,46

FSB1_BPM_N3 46

FSB1_BPM_N2 46

FSB1_BPM_N1 46

FSB1_BPM_N0 46

FSB1_REQ_N[4..0]

R373 51_0402R373 51_0402

R346 51_0402R346 51_0402

R384 51_0402R384 51_0402

R360 51_0402R360 51_0402

R165 51_0402R165 51_0402

R166 51_0402R166 51_0402

CK_H_P1_N 31

CK_H_P1 31

FSB1_RS2_N 15

FSB1_RS1_N 15

FSB1_RS0_N 15

FSB1_AP1 15

FSB1_AP0 15

FSB1_BR_N1 15

FSB1_BR_N0 15

CPU_PWRGD 9,25,46

R353 49.9RST_0402R353 49.9RST_0402

R350 49.9RST_0402R350 49.9RST_0402

R348 49.9RST_0402R348 49.9RST_0402

R340 49.9RST_0402R340 49.9RST_0402

R375 49.9RST_0402R375 49.9RST_0402

R335 49.9RST_0402R335 49.9RST_0402

R376 49.9RST_0402R376 49.9RST_0402

R212 49.9RST_0402R212 49.9RST_0402

FSB1_DP_N3 15

FSB1_DP_N2 15

FSB1_DP_N1 15

FSB1_DP_N0 15

FSB1_ADSTB_N[1..0]

FSB1_DSTBP_N[3..0]

FSB1_DSTBN_N[3..0]

FSB1_REQ_N[4..0] 15

FSB1_BPM_B2#

FSB1_BPM_B3#

P_VTT

P_VTT

Max Length 1.2 inches

P_VTT

C173

C173

X_0.1u

X_0.1u

FSB1_ADSTB_N[1..0] 15

FSB1_DSTBP_N[3..0] 15

FSB1_DSTBN_N[3..0] 15

FSB1_BPM_B2# 46

FSB1_BPM_B3# 46

49.9RST_0402

49.9RST_0402

100RST_0402

100RST_0402

49.9RST_0402

49.9RST_0402

100RST_0402

100RST_0402

Place Termination Close to CPU At End of Bus

P_VTT

R347 51_0402R347 51_0402

R345 51_0402R345 51_0402

R356 51_0402R356 51_0402

R361 51_0402R361 51_0402

R163 51_0402R163 51_0402

R380 51_0402R380 51_0402

R341 51_0402R341 51_0402

R351 X_51_0402R351 X_51_0402

P3V3_AUX

R381 4.7K_0402R381 4.7K_0402

FSB1_BPM_N3

FSB1_BPM_N2

FSB1_BPM_N1

FSB1_BPM_N0

FSB_FERR#

FSB1_THERMTRIP_N

FSB1_PROCHOT#

FSB1_BR_N0

FSB1_RESET_N

FSB1_GTL_IERR#

FSB1_BR_N1

CPU1_BOOT

CPU1_SKTOCC#

R354 51_0402R354 51_0402

R352 51_0402R352 51_0402

R358 51_0402R358 51_0402

R355 51_0402R355 51_0402

Place BPM Termination Near CPU

R379

R379

X_4.7K_0402

X_4.7K_0402

P1_LL_ID0

P1_LL_ID1

P1_MS_ID1

P1_MS_ID0

P_VTT

800mV at 1.2V FSB Vtt

Minmum trace and width as wide as possible

12 mils

R383

R383

P1_GTLREF_ADD1 P1_GTLREF_DATA1

R365

R365

C3711uC371

1u

P_VTT

800mV at 1.2V FSB Vtt

Minmum trace and width as wide as possible

12 mils

R339

R339

P1_GTLREF_ADD0 P1_GTLREF_DATA0

C3681uC368

R338

R338

1u

R377 X_51_0402R377 X_51_0402

R378 X_51_0402R378 X_51_0402

R3640R364

0

C372

C372

220P

220P

R3670R367

0

C367

C367

220P

220P

C365

C365

220P

220P

C370

C370

220P

220P

P_VTT

P3V3P3V3

R349

R349

X_4.7K_0402

X_4.7K_0402

FSB1_D45

FSB1_D50

FSB1_D48

FSB1_D44

FSB1_D47

FSB1_D51

FSB1_D52

FSB1_D49

FSB1_D46

A A

5

FSB1_D53

FSB1_D41

FSB1_D42

FSB1_D43

FSB1_D39

FSB1_D40

FSB1_D38

4

FSB1_D37

FSB1_D36

FSB1_D35

FSB1_D34

FSB1_D33

FSB1_D32

FSB1_D30

FSB1_D31

FSB1_D29

FSB1_D26

FSB1_D28

FSB1_D27

FSB1_D23

FSB1_D25

FSB1_D24

FSB1_D22

FSB1_D21

FSB1_D20

FSB1_D18

FSB1_D17

FSB1_D19

FSB1_D15

FSB1_D16

FSB1_D14

FSB1_D12

FSB1_D11

FSB1_D13

FSB1_D10

FSB1_D8

FSB1_D9

FSB1_D7

FSB1_D6

FSB1_D5

FSB1_D4

FSB1_D2

FSB1_D3

3

FSB1_D1

FSB1_D0

CPU1 SMI Voltage Translation

U37

U37

6

FSB_SMI#9,25,33

CPU1_DISABLE_N33,38

1

A

B4C

BE

PI5C3303

PI5C3303

BE=High, C=B

VCC

GND

P5V

2

CPU1_SMI_N

5

3

MSI

MSI

MSI

2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

MS-9196

CPU1 SIGNAL

CPU1 SIGNAL

CPU1 SIGNAL

1

Sheet of

Sheet of

Sheet of

12 58

12 58

12 58

00A

00A

00A

5

4

3

2

1

P1 Intel LGA771 Power

VCORE1

D D

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

VCORE1

AF19

VCC

AF18

VCC

AF15

VCC

AF14

VCC

AF12

VCC

AF11

VCC

AE9

VCC

AE23

VCC

AE22

VCC

AE21

VCC

AE19

VCC

AE18

VCC

AE15

VCC

AE14

VCC

AE12

VCC

AE11

VCC

AD8

VCC

AD30

VCC

AD29

VCC

AD28

VCC

AD27

VCC

AD26

VCC

AD25

VCC

AD24

C C

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCORE1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y28

Y29

Y30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

Y27

W30

W29

VCC

VCC

W28

VCC

VCC

W27

VCC

VCC

W26

VCC

VCC

W25

VCC

VCC

W24

VCC

VCC

VCC

W23

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U26

U27

U28

U29

U30

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

CPU2B

CPU2B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A23

VCCA

B23

VSSA

D23

VCCPLL

C23

VCCIOPLL

F30

VTT

E30

VTT

A25

VTT

A26

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

VTT_OUT1

VTT_OUT0

VTT_SEL

NONE

SOCKET771

SOCKET771

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

LGA771

PART 2

Power

VTTPWRGD

VCC

VCC

NONE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

T30

U23

U24

U25

N30

N23

N24

N25

N26

N27

N28

N29

M30

M29

M28

M27

M26

M25

M24

M23

K27

K28

K29

K30

T23

T24

T25

T26

T27

T28

T29

J30

K23

K24

K25

K26

AN9

AN8

AN26

AN25

AN30

AN29

H1_VCCA

H1_VSSA

H1_VCCPLL

VTT_PWRGD

VTT_SEL1

R8660R866

0

P_VTT

VTT_PWRGD 10,48

VTT_SEL 10,45

B B

A A

Minmum trace and width as wide as possible < 12 mils

P_VTT

DC current if 100mA

L5 10uH-0805-0.1AL5 10uH-0805-0.1A

L6 10uH-0805-0.1AL6 10uH-0805-0.1A

P1V5

5

R1780R178

0

C39

C39

22u-1206

22u-1206

C199

C199

103P

103P

C40

C40

X_10u-1206

X_10u-1206

C194

C194

4.7u-0805

4.7u-0805

4

H1_VCCA

C183

C183

X_1u

X_1u

H1_VSSA

H1_VCCPLL

C195

C195

4.7u-0805

4.7u-0805

P_VTT

C764

C764

10u-1206

10u-1206

C760

C760

10u-1206

10u-1206

C755

C755

0.1u

0.1u

C769

C769

0.1u

0.1u

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

3

2

Wednesday, May 02, 2007

MS-9196

CPU1 POWER

CPU1 POWER

CPU1 POWER

1

13 58

13 58

13 58

Sheet of

Sheet of

Sheet of

00A

00A

00A

5

4

3

2

1

P1 Intel LGA771 GND

A12

A15

A18

A21

A24

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

P_VTT

F1

A2

A6

A9

R431

R431

51_0402

51_0402

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D16

A20

RESVDC9RESVD

VSS

VSS

AE5

AE29

AE30

G5

W2

RESVD

RESVD

VSS

VSS

AE7

AF10

G6

E24

RESVD

RESVD

VSS

VSS

AF13

AF16

AC4

AE4

RESVD

RESVD

VSS

VSS

AF17

AF20

D14

RESVD

RESVDD1RESVD

VSS

VSS

AF23

AF24

PECI_CPU 11,34,50

E23

F23

RESVD

RESVDE5RESVDE6RESVDE7RESVD

VSS

VSS

VSS

VSS

VSS

AF25

AF26

AF27

AF28

AF29

D D

FSB1_BPM_B1#46

C C

B B

B13

RESVDF6RESVD

VSS

VSS

VSS

AF3

AF30

P_VTT

R253

R253

X_49.9RST_0402

X_49.9RST_0402

P5

E1

RESVDJ3RESVDN4RESVD

RESVD

VSS

VSS

VSS

VSS

AF6

AF7

AG10

AG13

AG16

R435

R435

51_0402

51_0402

AE6

AN5

AN6

RESVDN5RESVD

RESVD

VSS

VSS

VSS

AG17

AG20

AG23

AJ3

AK3

RESVD

RESVD

VSS

VSS

AG7

AG24

F29

RESVD

RESVD

VSS

VSS

AH1

AH10

VSS

AN27

AN28

NONE

VSS

AH13

AH16

NONE

VSS

VSS

AH17

V30

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AJ10

AJ13

AH24

AJ16

AH20

AH23

VSS

V29

V28

V27

V26

V25

V24

VSSV3VSS

VSS

VSS

VSS

VSS

LGA771

VSS

VSS

VSS

VSS

VSS

VSS

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

V23

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

PART 3

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ30

AK10

AK13

AK16

AK17

AK2

VSS

VSS

AK20

R30

VSS

AK23

R29

VSS

VSS

AK24

R28

VSS

VSS

AK27

R27

VSS

VSS

AK28

R26

VSS

VSS

AK29

R25

VSS

VSS

AK30

R24

VSS

VSS

AK5

R23

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

AK7

AL10

VSS

AL13

VSS

AL16

P30

VSS

AL17

P29

VSS

VSS

AL20

P28

VSS

VSS

AL23

P27

VSS

VSS

AL24

P26

VSS

VSS

AL27

P25

P24

P23

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

AL3

AM1

AL28

AM10

VSS

AM13

VSS

AM16

VSS

AM17

VSS

AM20

VSS

AM23

VSS

AM24

L30

VSS

AM27

L29

VSSL3VSS

VSS

AM4

AM28

VSS

L28

AM7

VSS

VSS

L27

AN1

L26

L25

L24

L23

VSS

VSS

VSS

VSS

VSS

VSSK7VSSK5VSSK2VSSJ7VSSJ4VSSH9VSSH8VSSH7VSSH6VSSH3VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN2

AN10

AN13

AN16

AN17

VSS

AN20

VSS

AN23

AN24

VSSB5VSS

VSS

VSSB1VSS

H29

H28

H27

H26

H25

H24

CPU2C

CPU2C

VSS

VSS

VSS

VSS

VSS

H23

VSS

H22

VSS

H21

VSS

H20

VSS

H19

VSS

H18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSC4VSS

VSS

SOCKET771

B17

B20

B24

SOCKET771

C7

B8

B11

B14

H17

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C24

C22

C19

C16

C13

C10

P_VTT

R427

R427

51_0402

51_0402

FSB1_BPM_B0# 46

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-9196

MS-9196

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, May 02, 2007

Date:

Wednesday, May 02, 2007

Date:

5

4

3

2

Wednesday, May 02, 2007

MS-9196

CPU1 GND

CPU1 GND

CPU1 GND

Sheet of

Sheet of

Sheet of

1

14 58

14 58

14 58

00A

00A

00A

5

5000P FSB0/1

FSB0_D[63..0]9

D D

C C

FSB0_DBI#[3..0]9

FSB0_DSTBP_N[3..0]9

B B

FSB0_DSTBN_N[3..0]9

MCH FSB0 VREF CKTS

P_VTT

R201

R201

49.9RST

49.9RST

R199

R199

100RST

100RST

A A

FSB0_D[63..0]