MSI MS-9189 Schematic 1.3_m

A B C

Dell Controlled Print

D

REVISIONS

1

SUB=NP Always no-pop

BOM options

REV

DESCRIPTIONECO DATE

APPROVED

A00 ECO218834 RELEASE FOR PRODUCTION 3/02/07 Kurtis Bowman

A01 ECO219910

A02 ECO220966 4/13/07 Kurtis Bowman

A03 ECO221932

A04

A05

ECO224477

ECO268380

Increase the hole diameter for a PTH inductor.

Corrected USB disable issue

Revision to PCIe silicon, Update to NB VRDs

Bullion 1.1 Barcelona Support (BIOS required)

Bullion TPM Support (BIOS Required)

3/23/07 Kurtis Bowman

4/26/07 Kurtis Bowman

9/12/07

10/01/08

Kurtis Bowman

Belayneh Million

1

2

0 = Production

1 = Development/Debug parts (non-ST part)

4 = Development/Debug parts (ST parts)

2 = Adds 2U Parts

3 = Adds 1U Parts

5 = Adds parts for Microvue+ on breakaway

6 = Adds parts for interposer on breakaway

7 = Adds parts for serial board on breakaway

8 = Adds parts for ROW TPM

9 = No TPM

BOM Instructions

In order to build a proper BOM, you must run a combo build

*** UT/ Product Test ***

2U= Builds 1,2,4

1U= Builds 1,3,4 <NOT TESTED>

SUB=POP1

SUB=POP4

SUB=POP2

SUB=POP3

SUB=POP5

SUB=POP6

SUB=POP7

SUB=POP8

SUB=POP9

2

*** System Test ***

2U= Builds 0,2,4

1U= Builds 0,3,4 <NOT TESTED>

*** Production ***

2U= Builds 0,2,8 (Boards with TPM)

2U= Builds 0,2,9 (Boards with NO TPM)

1U= Builds 0,3 <NOT TESTED>

*** For Sample Boards with TPM & New SST FWH ***

2U= Builds 0,2,8

3

4

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

x02_12551_ws: updated table of contents (TOC)

x04_13566_ws:ECO# and sign-offs added

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY

OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN

WHOLE OR IN PART AND MUST BE RETURNED TO DELL INC.

UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE

OF THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED

FOR SUCH USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE

LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

PWA: CY813

ASSY: FP976

PWB: FP974

SCH: FP975

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

2U DPNs

03/02/2007Will Smith

Will Smith

Sean Hart

03/02/2007

03/02/2007

Randy Hemingway 03/02/2007

04/13/2007Randy Hemingway

Randy Hemingway 04/26/2007

Randy Hemingway

09/12/2007

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO268380

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

INC.

ROUND ROCK,TEXAS

TITLE

SCHEM, PLN, SV, PE2970

DWG NO.

FP975

DATE

SHEET

3

04/29/2008

4

REV.

A05

1 OF 12010/2/2008

SCHEM, PLN, SV, PE2970

FP975

A05

2 OF 12010/2/2008

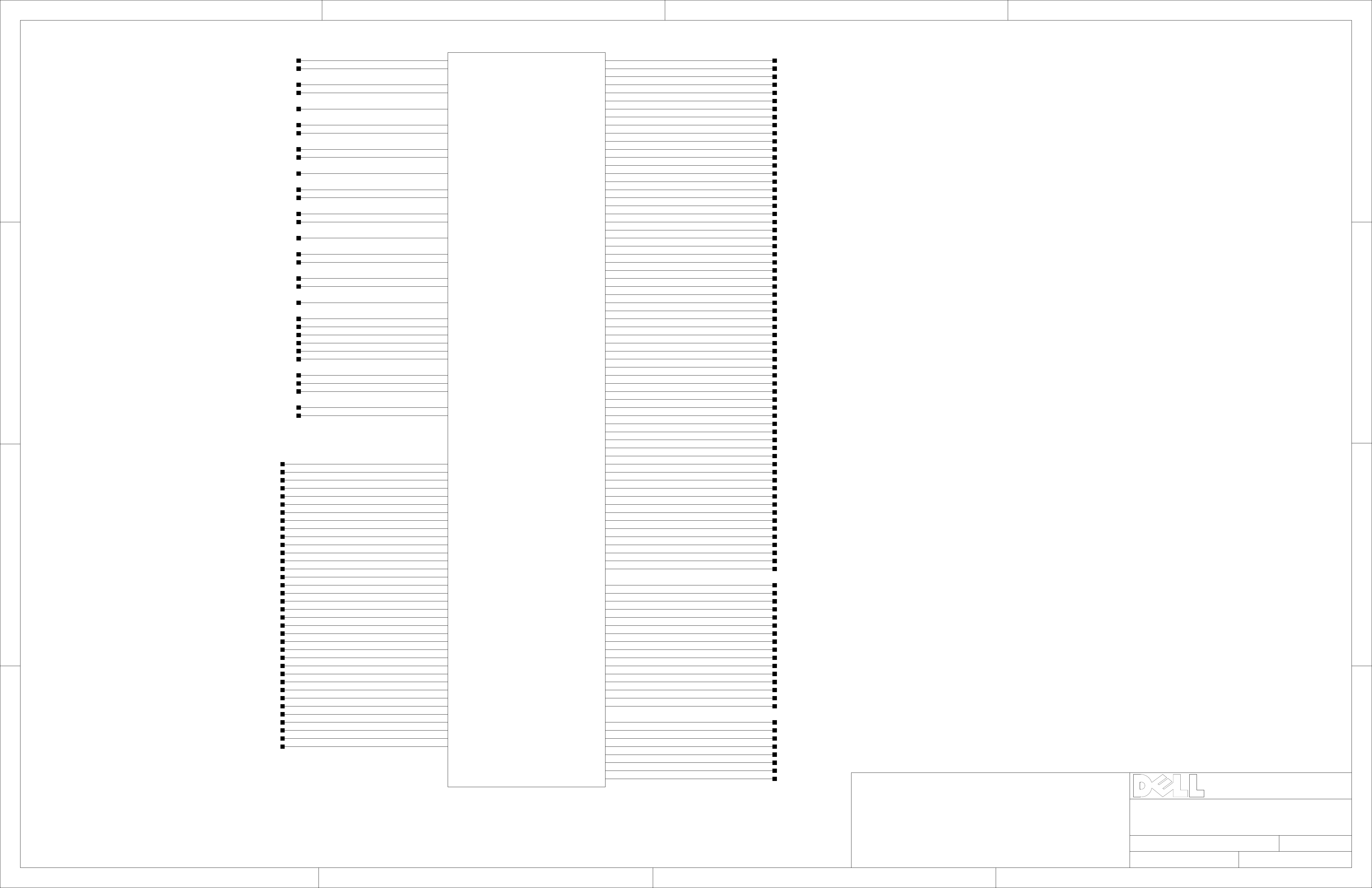

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

REV.

FP975

SHEET

10/2/2008 3 OF 120

DCBA

4

A05

A B C

D

1

1

2

2

3

3

4

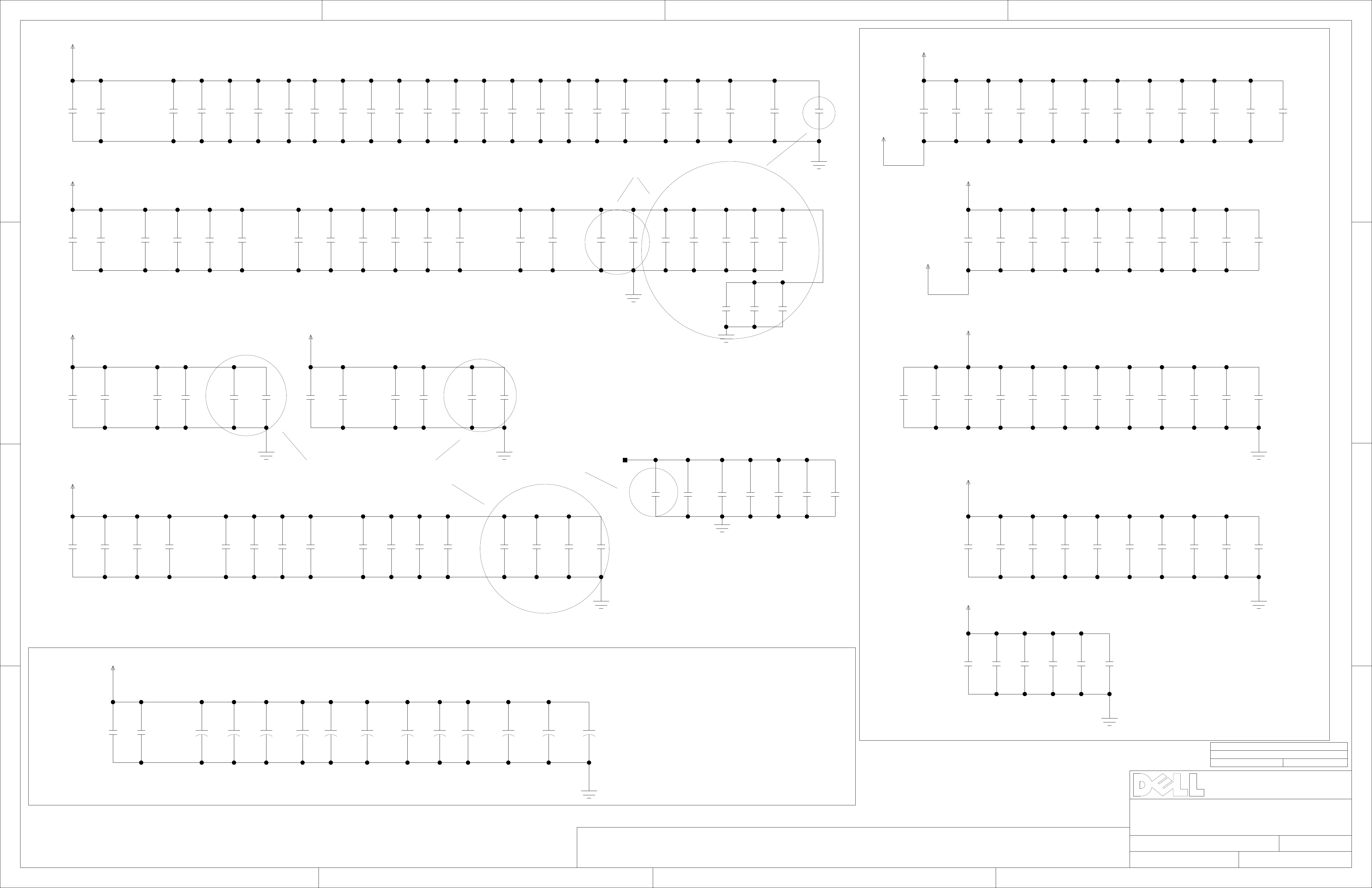

x04_13526_ws: Updated diagrams

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

DCBA

4

REV.

A05

4 OF 12010/2/2008

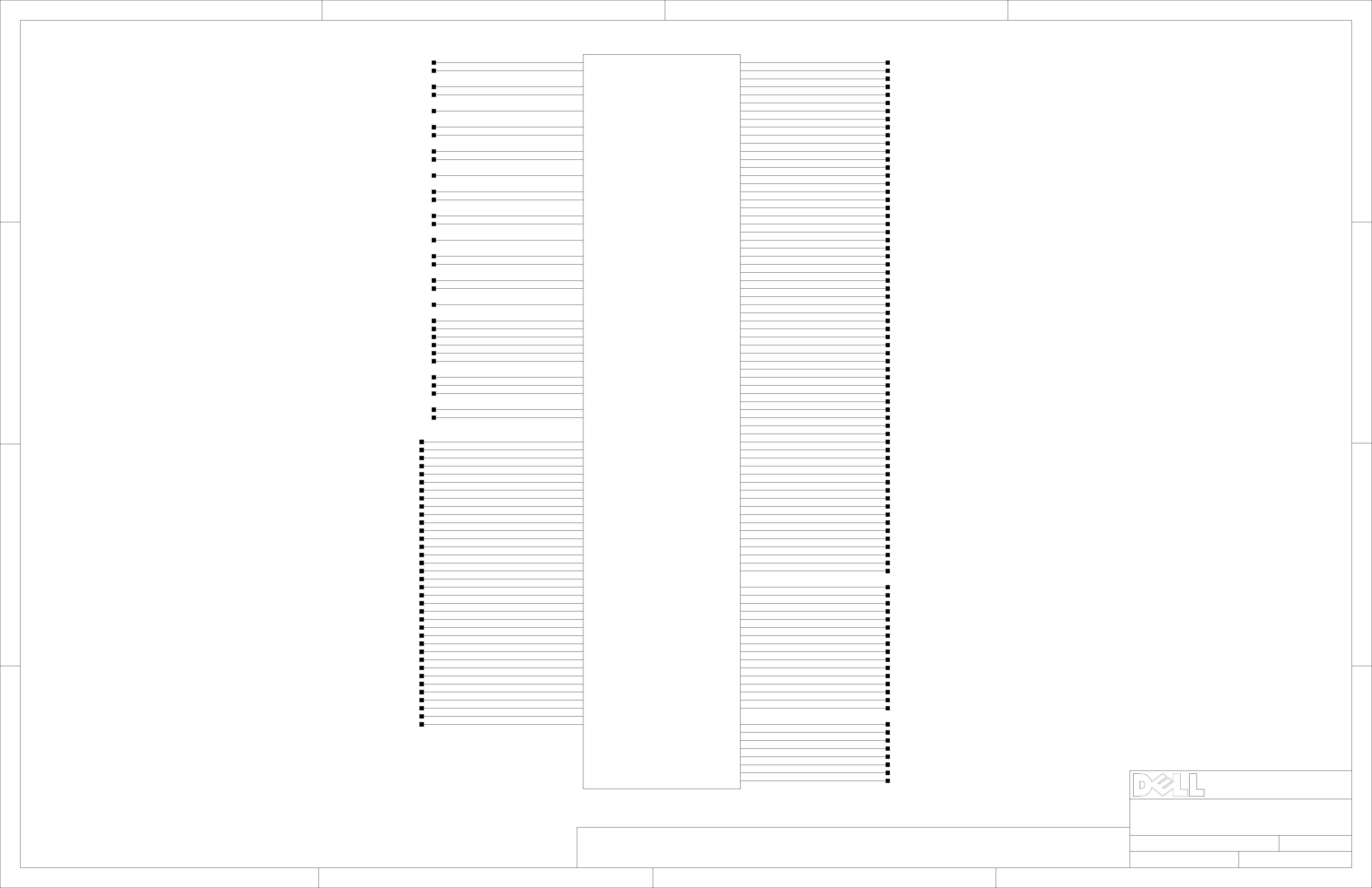

A B C

D

1

1

2

2

3

3

4

x04_13526_ws: Updated diagrams

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

DCBA

4

REV.

A05

5 OF 12010/2/2008

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

DCBA

4

REV.

A05

6 OF 12010/2/2008

A B C

D

1

1

2

2

3

3

4

X03_13327_SCH updated timing diagram to v1.0

Powerup Timing- VRDs

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

DCBA

4

REV.

A05

7 OF 12010/2/2008

A B C

D

1

1

2

2

BLANK PAGE

3

3

4

Power up Timing - Chipset

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

REV.

FP975

SHEET

10/2/2008 8 OF 120

DCBA

4

A05

A B C

D

1

1

2

2

BLANK PAGE

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

REV.

FP975

SHEET

10/2/2008 9 OF 120

DCBA

4

A05

A B C

D

1

1

2

2

BLANK PAGE

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

DCBA

4

REV.

A05

10 OF 12010/2/2008

A B C

D

1

1

2

2

BLANK PAGE

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

DCBA

4

REV.

A05

11 OF 12010/2/2008

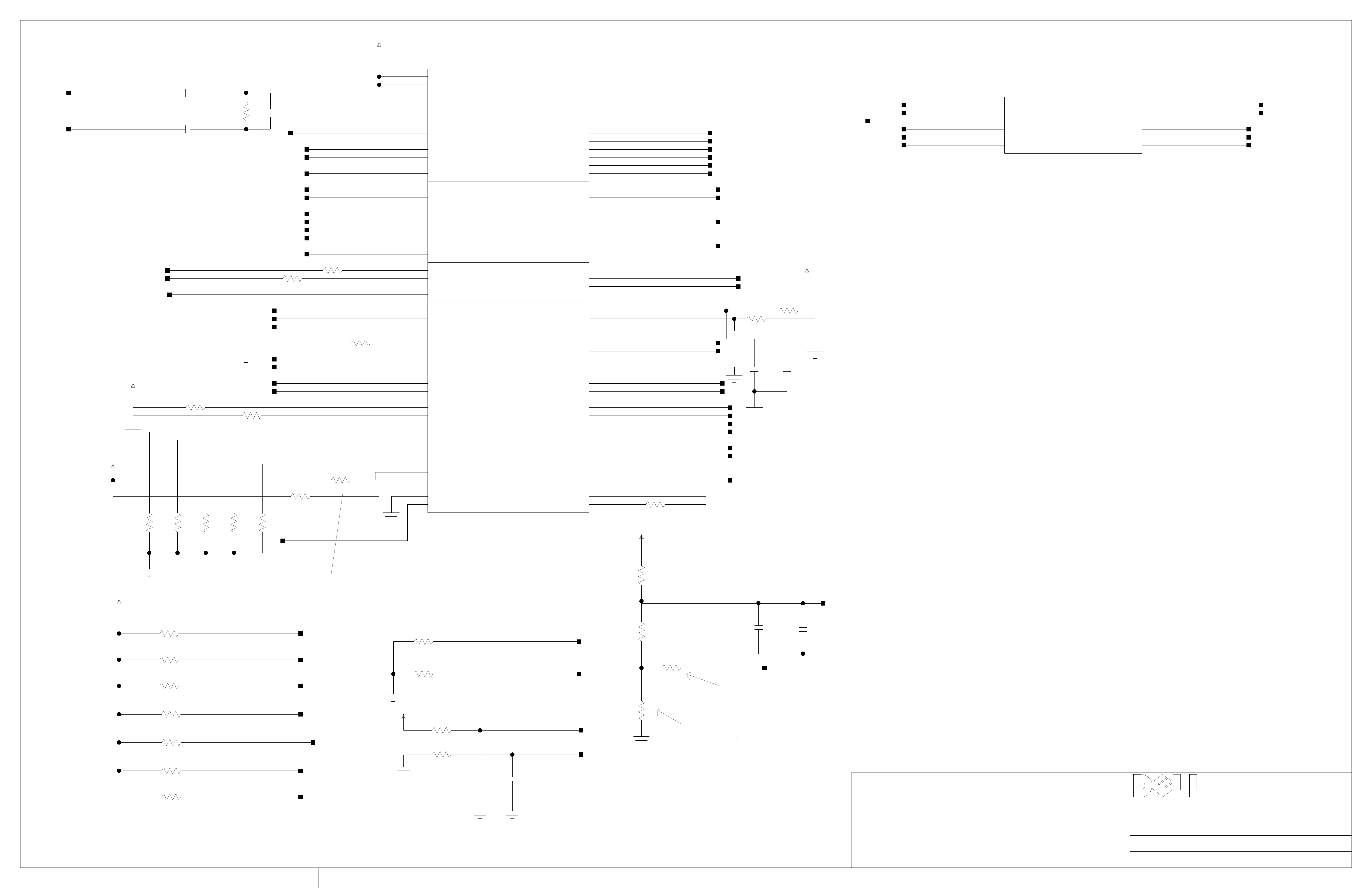

1

A B C

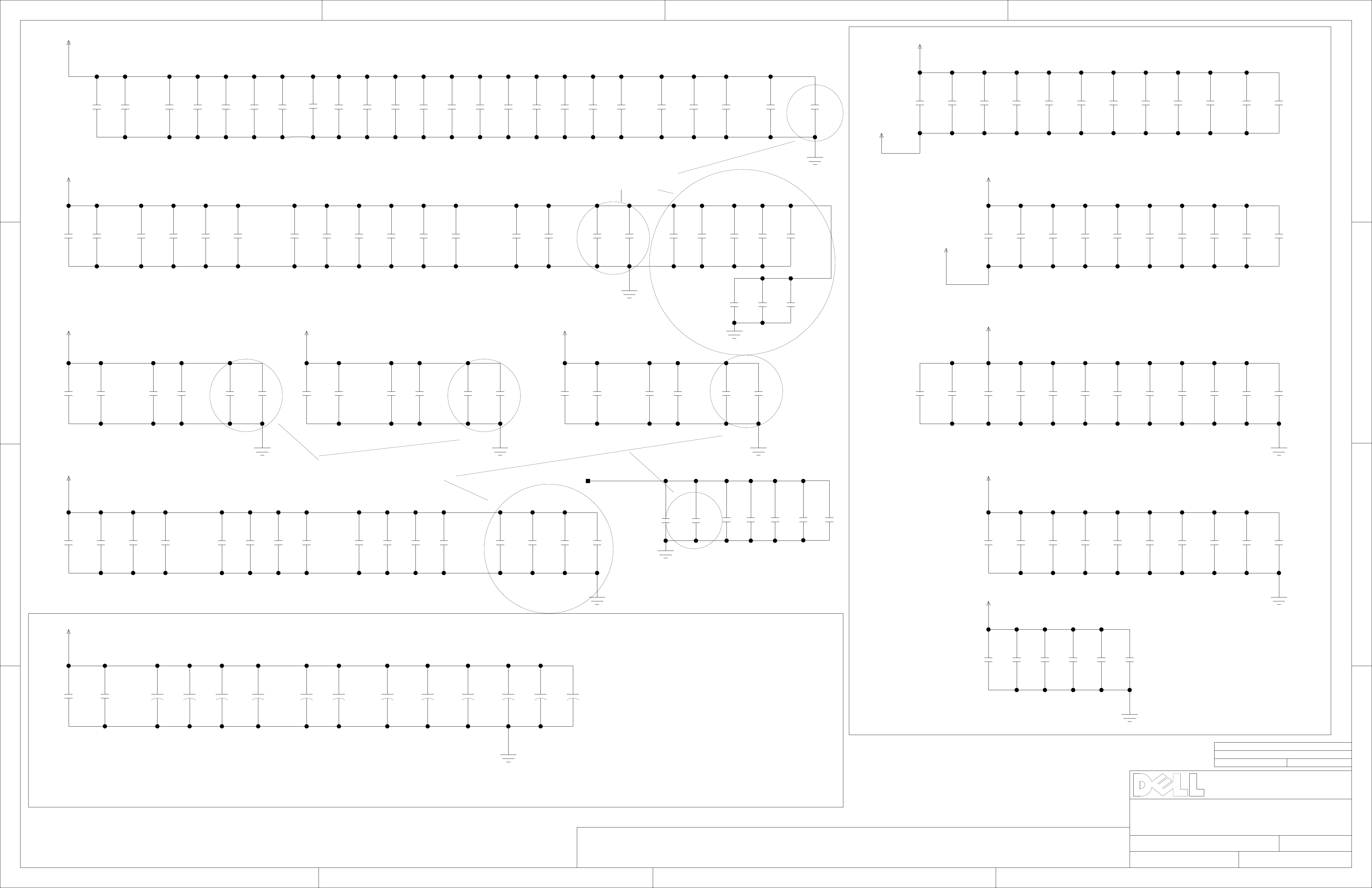

Place series R's within 0.5 inch of U8002

Place shut R within 100 mil of series R's

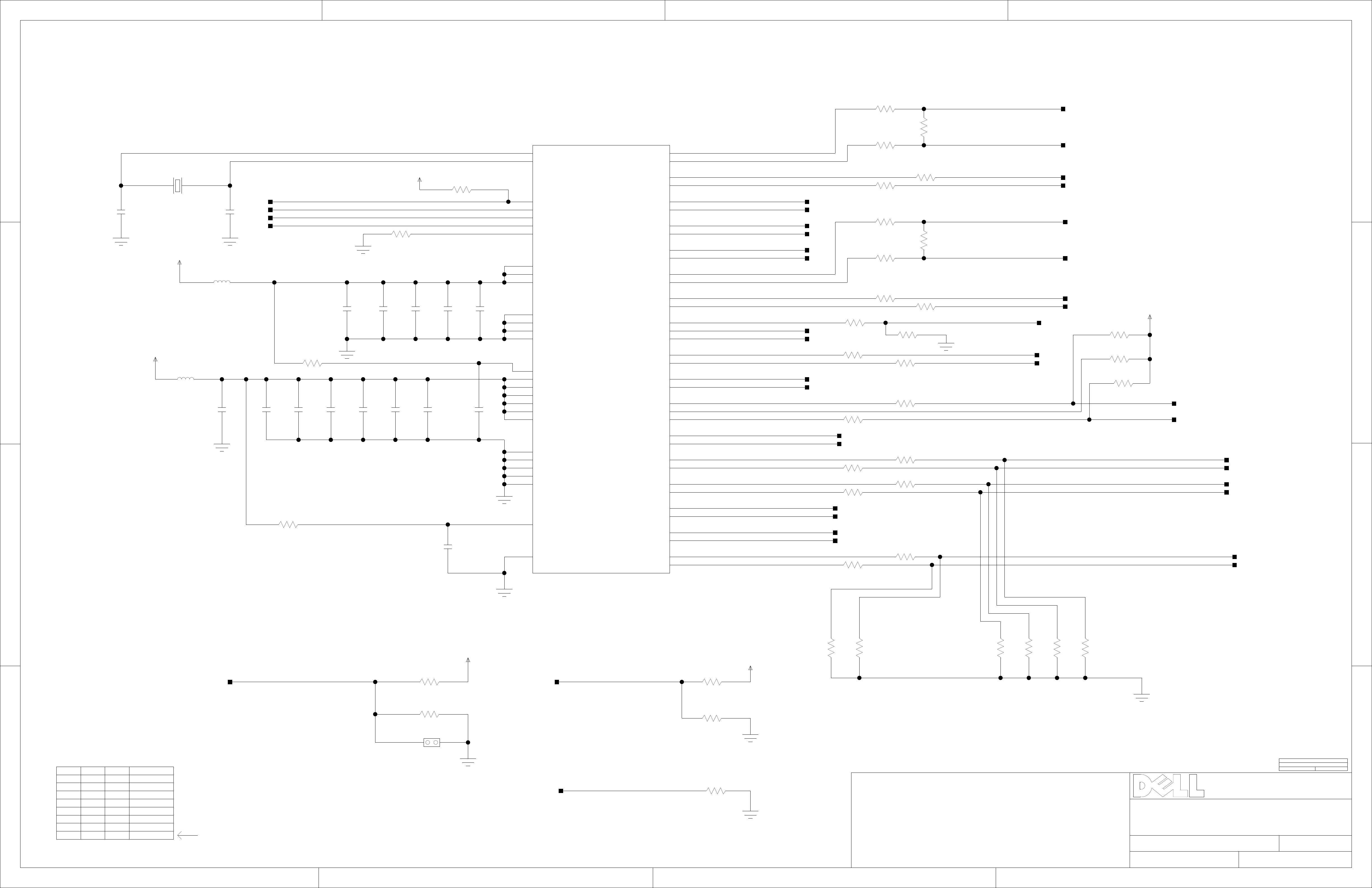

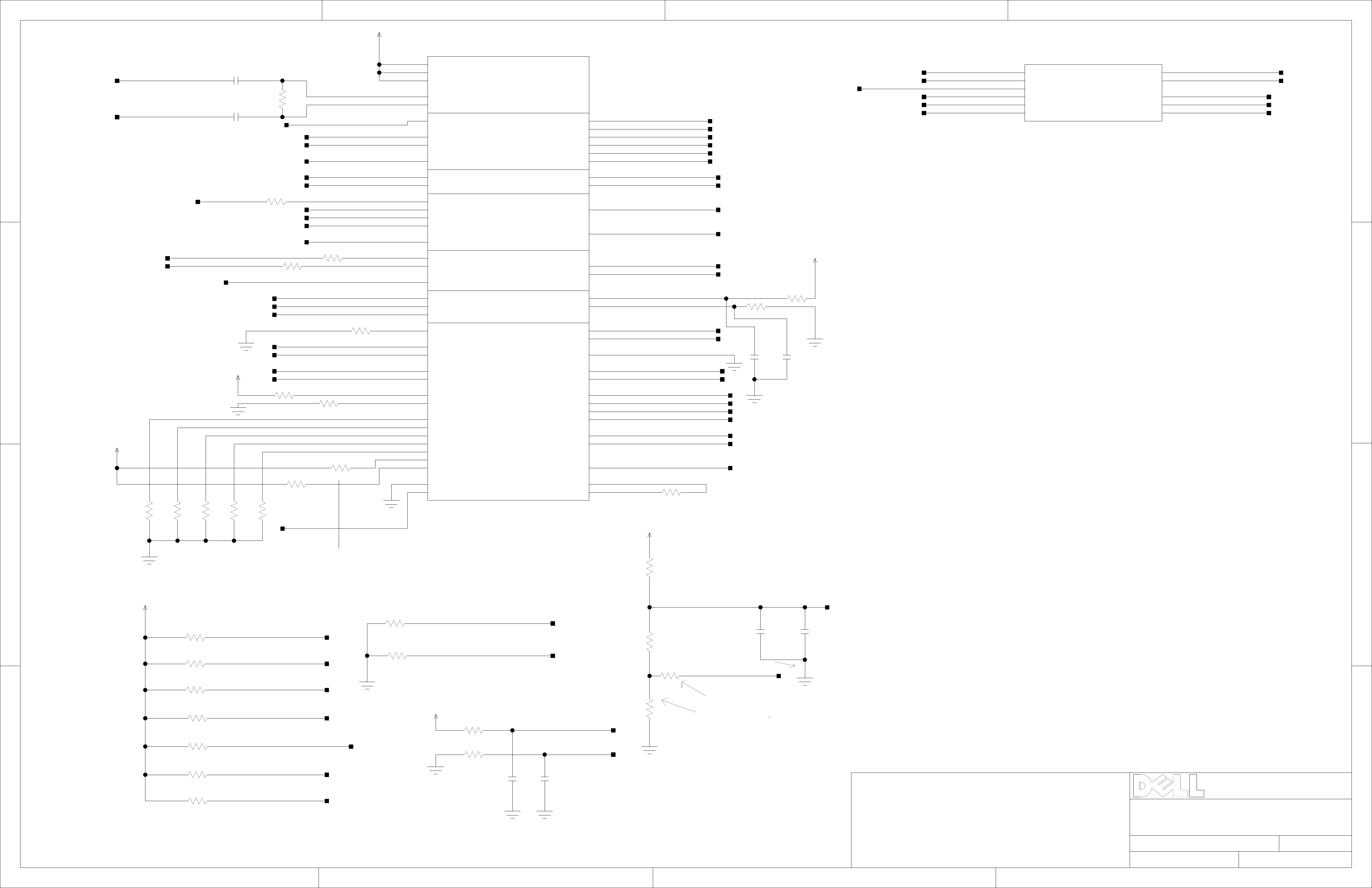

ICS932S805

All Unused Clock Outputs Can be Turned Off

R9427

1 2

47.5-1%

CK_200M_CPU1_C_DP

D

17

1

2

3

21

C8674

22pF

50V-5%

14.31818MHz

+3.3V

X5

12

+3.3V

L1820

BLM21AH601

21

21

C8673

L1819

BLM21AH601

1 2

C8738

88,120

22pF

50V-5%

21

10uF 6.3V

CLKGEN_PD_N

48

48

12

MOD_CLKGEN_VCC3

C8682

I2C_CLKGEN_SDA

I2C_CLKGEN_SCL

MOD_CLKGEN_SSC_EN

MOD_CLKGEN_VDDSRC

21

.1uF

R8661

1 2

2.2-5%

21

C8683

16V-10%

R8678

1-1%

.1uF

16V-10%

1 2

C8739

21

21

C8677

MOD_CLKGEN_VDDA

.1uF

16V-10%

10uF 6.3V

21

C8678

MOD_CLKGEN_XTALI

MOD_CLKGEN_XTALO

+3.3V

R8716

1 2

475-1%

21

C8687

MOD_CLKGEN_VDD48M

.1uF

.1uF

21

C8679

16V-10%

16V-10%

.1uF

MOD_CLKGEN_IREF

21

C8686

C8680

16V-10%

.1uF

16V-10%

21

.1uF

C8688

R8641

1 2

4.7K-5%

21

C8685

16V-10%

1 2

.1uF

C8684

16V-10%

C8681

.047uF

16V-10%

Through SMBus For EMI Consideration

R9425

U8002

1

XTALI

2

XTALO

19

PD_N

14

SDATA

13

SCLK

60

SPREAD_EN

23

IREF

3

VDDREF

15

VDDPCI

64

VDD25MHZ

21

.1uF

16V-10%

21

.1uF

16V-10%

7

GNDREF

18

GNDPCI

20

GND

61

GND25MHZ

8

VDD48MHZ

24

VDDA_24

31

VDDSRC_31

39

VDDSRC_39

41

VDDCPU1

49

VDDCPU2

55

VDDCPU3

12

GND48MHZ

32

GNDSRC

40

GND_40

48

GND_48

54

GND_54

21

VDDA_21

22

GNDA

ICS932S805

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

CPUCLK8T2

CPUCLK8C2

CPUCLK8T3

CPUCLK8C3

CPUCLK8T4

CPUCLK8C4

CPUCLK8T5

CPUCLK8C5

CPUCLK8T6

CPUCLK8C6

48MHZ_0

48MHZ_1

48MHZ_2

FS3/PCICLK0

PCICLK1

25MHZ_0

25MHZ_1

FS0/REF0

FS1/REF1

FS2/REF2

SRCCLKT0

SRCCLKC0

SRCCLKT1

SRCCLKC1

SRCCLKT2

SRCCLKC2

SRCCLKT3

SRCCLKC3

SRCCLKT4

SRCCLKC4

SRCCLKT5

SRCCLKC5

43

42

45

44

47

46

51

50

53

52

57

56

59

58

9

10

11

16

17

63

62

4

5

6

25

26

27

28

29

30

34

33

36

35

38

37

MOD_CLKGEN_K8CLK_0_DP

MOD_CLKGEN_K8CLK_0_DN

MOD_CLKGEN_K8CLK_1_DP

MOD_CLKGEN_K8CLK_1_DN

NC_CLKGEN_K8CLK_2_DP

NC_CLKGEN_K8CLK_2_DN

NC_CLKGEN_K8CLK_3_DP

NC_CLKGEN_K8CLK_3_DN

NC_CLKGEN_K8CLK_4_DP

NC_CLKGEN_K8CLK_4_DN

MOD_CLKGEN_K8CLK_5_DP

MOD_CLKGEN_K8CLK_5_DN

MOD_CLKGEN_K8CLK_6_DP

MOD_CLKGEN_K8CLK_6_DN

R8662

MOD_CLKGEN_CK48M

NC_CLKGEN_48M_1

NC_CLKGEN_48M_2

MOD_CLKGEN_PCICLK0

MOD_CLKGEN_PCICLK1

TP_CLKGEN_25M_0

NC_CLKGEN_25M_1

MOD_CLKGEN_REF0

MOD_CLKGEN_REF1

MOD_CLKGEN_REF2

NC_MOD_CLKGEN_SRCCLK_0_DP

NC_MOD_CLKGEN_SRCCLK_0_DN

MOD_CLKGEN_SRCCLK_1_DP CK_100M_PCIE_NH_B_DP

MOD_CLKGEN_SRCCLK_1_DN CK_100M_PCIE_NH_B_DN

MOD_CLKGEN_SRCCLK_2_DP CK_100M_PCIE_ROMB_DP

MOD_CLKGEN_SRCCLK_2_DN

NC_MOD_CLKGEN_SRCCLK_3_DP

NC_MOD_CLKGEN_SRCCLK_3_DN

NC_MOD_CLKGEN_SRCCLK_4_DP

NC_MOD_CLKGEN_SRCCLK_4_DN

MOD_CLKGEN_SRCCLK_5_DP CK_100M_PCIE_DB400_DN

MOD_CLKGEN_SRCCLK_5_DN

62-5%

R9492

1 2

33-5%

R9271

1 2

33-5%

R8675

1 2

33-5%

R9175

1 2

33-5%

R8951

1 2

33-5%

1 2

47.5-1%

R9408

1 2

15-1%

R9424

1 2

47.5-1%

R9426

1 2

47.5-1%

R9406

1 2

15-1%

21

R8677

1 2

220-5%

R8676

1 2

33-5%

R8671

1 2

33-5%

R8674

1 2

33-5%

R9174

1 2

33-5%

R8950

1 2

33-5%

R9428

R9409

1 2

15-1%

R9429

R9407

1 2

15-1%

1 2

1 2

261-1%

261-1%

CK_200M_CPU1_C_DN

CK_200M_NH_C_DP

CK_200M_NH_C_DN

CK_200M_CPU2_C_DP

CK_200M_CPU2_C_DN

CK_200M_SH_C_DP

CK_200M_SH_C_DN

CK_48M_SH_USB

NOTE: USB Clock is 2.5V, not 3.3V

CK_33M_SMARTVU

CK_33M_SH

40

12,117

41

17

34

34

27

27

42

42

+3.3V

R8621

1 2

8.2K-5%

R8620

1 2

8.2K-5%

R8618

1 2

8.2K-5%

CK_14M_SH

CK_14M_SIO

CK_100M_PCIE_ROMB_DN

CK_100M_PCIE_DB400_DP

12,41

49

36

36

74

74

120

120

2

3

4

FREQUENCY

FS2 FS1 FS0 CPU MHz

0 0

0 0

10

0 1 1

1 0

1

1 0

1

0

1

1

0

1

0

0

1

1

Hi-Z

X/6

180.00

220.00

100.00

133.33

166.67

200.00

12

Default Strapping

Spread Spectrum Clock Enabled

Can be Disabled through SMBus

MOD_CLKGEN_SSC_EN

Debug Jumper for Disable SSC

R8624

1 2

8.2K-5%

R8623

NP

1 2

8.2K-5%

NP

1 2

J7

X

X

+3.3V

SMBUS ADDRESS 0xD2

FS3=1 CPU OverClock Enable

FS3=0 CPU OverClock Disable

12,117

12,41

CK_33M_SMARTVU

CK_14M_SH

FS0

R9240

NP

1 2

8.2K-5%

R8817

1 2

8.2K-5%

NP

1 2

8.2K-5%

R8818

X

X

+3.3V

R8627

1 2

R4197

49.9-1%

1 2

49.9-1%

ROOM=CLOCK_ICS932S805

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

R9094

1 2

R9093

49.9-1%

1 2

R8824

49.9-1%

1 2

R8825

49.9-1%

1 2

49.9-1%

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

10/2/2008

MODULE:

DESC:

REV: OF

REV.

DB410B, DB1200, DB800

A05

12 OF 120

SEC

CK

41

4

C

DBA

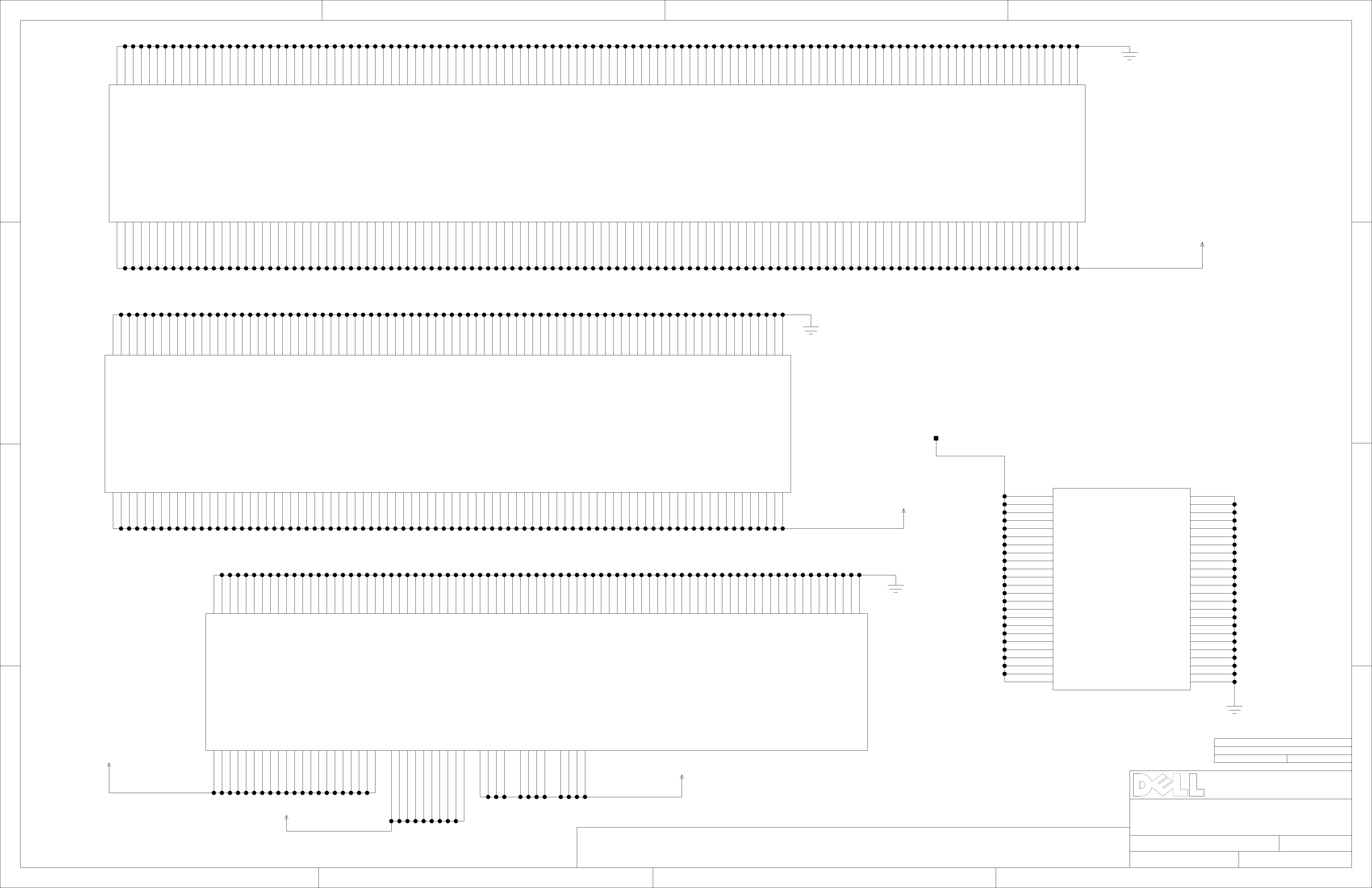

A B C

D

1

HT_CK_C2L0_C1L0_1_DP

23

HT_CK_C2L0_C1L0_1_DN

23

HT_CK_C2L0_C1L0_0_DP

23

HT_CK_C2L0_C1L0_0_DN

23

HT_CT_C2L0_C1L0_1_DP

23

HT_CT_C2L0_C1L0_1_DN

23

HT_CT_C2L0_C1L0_0_DP

23

HT_CT_C2L0_C1L0_0_DN

23

J_CPU1

M6 AC5

L0_CLKIN_H_1 L0_CLKOUT_H_1

N6

L0_CLKIN_L_1

M3 AC1

L0_CLKIN_H_0 L0_CLKOUT_H_0

M2

L0_CLKIN_L_0

U4

L0_CTLIN_H_1

U5

L0_CTLIN_L_1

T1

L0_CTLIN_H_0

U1

L0_CTLIN_L_0

L0_CLKOUT_L_1

L0_CLKOUT_L_0

L0_CTLOUT_H_1

L0_CTLOUT_L_1

L0_CTLOUT_H_0

L0_CTLOUT_L_0

AC4

AB1

W6

V6

V2

V3

HT_CK_C1L0_C2L0_1_DP

HT_CK_C1L0_C2L0_1_DN

HT_CK_C1L0_C2L0_0_DP

HT_CK_C1L0_C2L0_0_DN

HT_CT_C1L0_C2L0_1_DP

HT_CT_C1L0_C2L0_1_DN

HT_CT_C1L0_C2L0_0_DP

HT_CT_C1L0_C2L0_0_DN

23

23

23

23

23

23

23

23

HT_CK_C2L1_C1L2_1_DP

23

HT_CK_C2L1_C1L2_1_DN

23

HT_CK_C2L1_C1L2_0_DP

23

HT_CK_C2L1_C1L2_0_DN

23

HT_CT_C2L1_C1L2_1_DP

23

HT_CT_C2L1_C1L2_1_DN

23

HT_CT_C2L1_C1L2_0_DP

23

HT_CT_C2L1_C1L2_0_DN

23

AK7

AK8

AM7

AN7

AM12

AL12

AP11

AP12

L2_CLKIN_H_1

L2_CLKIN_L_1

L2_CLKIN_H_0

L2_CLKIN_L_0

L2_CTLIN_H_1

L2_CTLIN_L_1

L2_CTLIN_H_0

L2_CTLIN_L_0

J_CPU1

L2_CLKOUT_H_1

L2_CLKOUT_L_1

L2_CLKOUT_H_0

L2_CLKOUT_L_0

L2_CTLOUT_H_1

L2_CTLOUT_L_1

L2_CTLOUT_H_0

L2_CTLOUT_L_0

AM18

AN18

AR18

AR17

AL14

AL13

AP13

AN13

HT_CK_C1L2_C2L1_1_DP

HT_CK_C1L2_C2L1_1_DN

HT_CK_C1L2_C2L1_0_DP

HT_CK_C1L2_C2L1_0_DN

HT_CT_C1L2_C2L1_1_DP

HT_CT_C1L2_C2L1_1_DN

HT_CT_C1L2_C2L1_0_DP

HT_CT_C1L2_C2L1_0_DN

1

23

23

23

23

23

23

23

23

2

3

HT_AD_C2L0_C1L0_15_DP

23

HT_AD_C2L0_C1L0_15_DN

23

HT_AD_C2L0_C1L0_14_DP

23

HT_AD_C2L0_C1L0_14_DN

23

HT_AD_C2L0_C1L0_13_DP

23

HT_AD_C2L0_C1L0_13_DN

23

HT_AD_C2L0_C1L0_12_DP

23

HT_AD_C2L0_C1L0_12_DN

23

HT_AD_C2L0_C1L0_11_DP

23

HT_AD_C2L0_C1L0_11_DN

23

HT_AD_C2L0_C1L0_10_DP

23

HT_AD_C2L0_C1L0_10_DN

23

HT_AD_C2L0_C1L0_9_DP

23

HT_AD_C2L0_C1L0_9_DN

23

HT_AD_C2L0_C1L0_8_DP

23

HT_AD_C2L0_C1L0_8_DN

23

HT_AD_C2L0_C1L0_7_DP

23

HT_AD_C2L0_C1L0_7_DN

23

HT_AD_C2L0_C1L0_6_DP

23

HT_AD_C2L0_C1L0_6_DN

23

HT_AD_C2L0_C1L0_5_DP

23

HT_AD_C2L0_C1L0_5_DN

23

HT_AD_C2L0_C1L0_4_DP

23

HT_AD_C2L0_C1L0_4_DN

23

HT_AD_C2L0_C1L0_3_DP

23

HT_AD_C2L0_C1L0_3_DN

23

HT_AD_C2L0_C1L0_2_DP

23

HT_AD_C2L0_C1L0_2_DN

23

HT_AD_C2L0_C1L0_1_DP

23

HT_AD_C2L0_C1L0_1_DN

23

HT_AD_C2L0_C1L0_0_DP

23

HT_AD_C2L0_C1L0_0_DN

23

T6

L0_CADIN_H_15

U6

L0_CADIN_L_15

R4

L0_CADIN_H_14

R5

L0_CADIN_L_14

P6

L0_CADIN_H_13

R6

L0_CADIN_L_13

N4

L0_CADIN_H_12

N5

L0_CADIN_L_12

L4

L0_CADIN_H_11

L5

L0_CADIN_L_11

K6

L0_CADIN_H_10

L6

L0_CADIN_L_10

J4

L0_CADIN_H_9

J5

L0_CADIN_L_9

H6

L0_CADIN_H_8

J6

L0_CADIN_L_8

T3

L0_CADIN_H_7

P1

L0_CADIN_L_7

T2

L0_CADIN_H_6

R1

L0_CADIN_L_6

P3

L0_CADIN_H_5

P2

L0_CADIN_L_5

M1

L0_CADIN_H_4

N1

L0_CADIN_L_4

K1

L0_CADIN_H_3

L1

L0_CADIN_L_3

K3

L0_CADIN_H_2

K2

L0_CADIN_L_2

H1

L0_CADIN_H_1

J1

L0_CADIN_L_1

H3

L0_CADIN_H_0

H2

L0_CADIN_L_0

L0_CADOUT_H_15

L0_CADOUT_L_15

L0_CADOUT_H_14

L0_CADOUT_L_14

L0_CADOUT_H_13

L0_CADOUT_L_13

L0_CADOUT_H_12

L0_CADOUT_L_12

L0_CADOUT_H_11

L0_CADOUT_L_11

L0_CADOUT_H_10

L0_CADOUT_L_10

L0_CADOUT_H_9

L0_CADOUT_L_9

L0_CADOUT_H_8

L0_CADOUT_L_8

L0_CADOUT_H_7

L0_CADOUT_L_7

L0_CADOUT_H_6

L0_CADOUT_L_6

L0_CADOUT_H_5

L0_CADOUT_L_5

L0_CADOUT_H_4

L0_CADOUT_L_4

L0_CADOUT_H_3

L0_CADOUT_L_3

L0_CADOUT_H_2

L0_CADOUT_L_2

L0_CADOUT_H_1

L0_CADOUT_L_1

L0_CADOUT_H_0

L0_CADOUT_L_0

W5

W4

AA6

Y6

AA5

AA4

AC6

AB6

AE6

AD6

AE5

AE4

AG6

AF6

AG5

AG4

W1

V1

Y2

Y3

AA1

Y1

AB2

AB3

AD2

AD3

AE1

AD1

AF2

AF3

AG1

AF1

HT_AD_C1L0_C2L0_15_DP

HT_AD_C1L0_C2L0_15_DN

HT_AD_C1L0_C2L0_14_DP

HT_AD_C1L0_C2L0_14_DN

HT_AD_C1L0_C2L0_13_DP

HT_AD_C1L0_C2L0_13_DN

HT_AD_C1L0_C2L0_12_DP

HT_AD_C1L0_C2L0_12_DN

HT_AD_C1L0_C2L0_11_DP

HT_AD_C1L0_C2L0_11_DN

HT_AD_C1L0_C2L0_10_DP

HT_AD_C1L0_C2L0_10_DN

HT_AD_C1L0_C2L0_9_DP

HT_AD_C1L0_C2L0_9_DN

HT_AD_C1L0_C2L0_8_DP

HT_AD_C1L0_C2L0_8_DN

HT_AD_C1L0_C2L0_7_DP

HT_AD_C1L0_C2L0_7_DN

HT_AD_C1L0_C2L0_6_DP

HT_AD_C1L0_C2L0_6_DN

HT_AD_C1L0_C2L0_5_DP

HT_AD_C1L0_C2L0_5_DN

HT_AD_C1L0_C2L0_4_DP

HT_AD_C1L0_C2L0_4_DN

HT_AD_C1L0_C2L0_3_DP

HT_AD_C1L0_C2L0_3_DN

HT_AD_C1L0_C2L0_2_DP

HT_AD_C1L0_C2L0_2_DN

HT_AD_C1L0_C2L0_1_DP

HT_AD_C1L0_C2L0_1_DN

HT_AD_C1L0_C2L0_0_DP

HT_AD_C1L0_C2L0_0_DN

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

HT_AD_C2L1_C1L2_15_DP

23

HT_AD_C2L1_C1L2_15_DN

23

HT_AD_C2L1_C1L2_14_DP

23

HT_AD_C2L1_C1L2_14_DN

23

HT_AD_C2L1_C1L2_13_DP

23

HT_AD_C2L1_C1L2_13_DN

23

HT_AD_C2L1_C1L2_12_DP

23

HT_AD_C2L1_C1L2_12_DN

23

HT_AD_C2L1_C1L2_11_DP

23

HT_AD_C2L1_C1L2_11_DN

23

HT_AD_C2L1_C1L2_10_DP

23

HT_AD_C2L1_C1L2_10_DN

23

HT_AD_C2L1_C1L2_9_DP

23

HT_AD_C2L1_C1L2_9_DN

23

HT_AD_C2L1_C1L2_8_DP

23

HT_AD_C2L1_C1L2_8_DN

23

HT_AD_C2L1_C1L2_7_DP

23

HT_AD_C2L1_C1L2_7_DN

23

HT_AD_C2L1_C1L2_6_DP

23

HT_AD_C2L1_C1L2_6_DN

23

HT_AD_C2L1_C1L2_5_DP

23

HT_AD_C2L1_C1L2_5_DN

23

HT_AD_C2L1_C1L2_4_DP

23

HT_AD_C2L1_C1L2_4_DN

23

HT_AD_C2L1_C1L2_3_DP

23

HT_AD_C2L1_C1L2_3_DN

23

HT_AD_C2L1_C1L2_2_DP

23

HT_AD_C2L1_C1L2_2_DN

23

HT_AD_C2L1_C1L2_1_DP

23

HT_AD_C2L1_C1L2_1_DN

23

HT_AD_C2L1_C1L2_0_DP

23

HT_AD_C2L1_C1L2_0_DN

23

AK11

AK12

AM10

AL10

AK9

AK10

AM8

AL8

AM6

AL6

AK5

AK6

AM4

AL4

AK3

AK4

AM11

AN11

AP9

AP10

AM9

AN9

AP7

AP8

AP5

AP6

AM5

AN5

AP3

AP4

AM3

AN3

L2_CADIN_H_15

L2_CADIN_L_15

L2_CADIN_H_14

L2_CADIN_L_14

L2_CADIN_H_13

L2_CADIN_L_13

L2_CADIN_H_12

L2_CADIN_L_12

L2_CADIN_H_11

L2_CADIN_L_11

L2_CADIN_H_10

L2_CADIN_L_10

L2_CADIN_H_9

L2_CADIN_L_9

L2_CADIN_H_8

L2_CADIN_L_8

L2_CADIN_H_7

L2_CADIN_L_7

L2_CADIN_H_6

L2_CADIN_L_6

L2_CADIN_H_5

L2_CADIN_L_5

L2_CADIN_H_4

L2_CADIN_L_4

L2_CADIN_H_3

L2_CADIN_L_3

L2_CADIN_H_2

L2_CADIN_L_2

L2_CADIN_H_1

L2_CADIN_L_1

L2_CADIN_H_0

L2_CADIN_L_0

L2_CADOUT_H_15

L2_CADOUT_L_15

L2_CADOUT_H_14

L2_CADOUT_L_14

L2_CADOUT_H_13

L2_CADOUT_L_13

L2_CADOUT_H_12

L2_CADOUT_L_12

L2_CADOUT_H_11

L2_CADOUT_L_11

L2_CADOUT_H_10

L2_CADOUT_L_10

L2_CADOUT_H_9

L2_CADOUT_L_9

L2_CADOUT_H_8

L2_CADOUT_L_8

L2_CADOUT_H_7

L2_CADOUT_L_7

L2_CADOUT_H_6

L2_CADOUT_L_6

L2_CADOUT_H_5

L2_CADOUT_L_5

L2_CADOUT_H_4

L2_CADOUT_L_4

L2_CADOUT_H_3

L2_CADOUT_L_3

L2_CADOUT_H_2

L2_CADOUT_L_2

L2_CADOUT_H_1

L2_CADOUT_L_1

L2_CADOUT_H_0

L2_CADOUT_L_0

AM14

AN14

AL16

AL15

AM16

AN16

AL18

AL17

AL20

AL19

AM20

AN20

AL22

AL21

AM22

AN22

AR14

AR13

AP15

AN15

AR16

AR15

AP17

AN17

AP19

AN19

AR20

AR19

AP21

AN21

AR22

AR21

HT_AD_C1L2_C2L1_15_DP

HT_AD_C1L2_C2L1_15_DN

HT_AD_C1L2_C2L1_14_DP

HT_AD_C1L2_C2L1_14_DN

HT_AD_C1L2_C2L1_13_DP

HT_AD_C1L2_C2L1_13_DN

HT_AD_C1L2_C2L1_12_DP

HT_AD_C1L2_C2L1_12_DN

HT_AD_C1L2_C2L1_11_DP

HT_AD_C1L2_C2L1_11_DN

HT_AD_C1L2_C2L1_10_DP

HT_AD_C1L2_C2L1_10_DN

HT_AD_C1L2_C2L1_9_DP

HT_AD_C1L2_C2L1_9_DN

HT_AD_C1L2_C2L1_8_DP

HT_AD_C1L2_C2L1_8_DN

HT_AD_C1L2_C2L1_7_DP

HT_AD_C1L2_C2L1_7_DN

HT_AD_C1L2_C2L1_6_DP

HT_AD_C1L2_C2L1_6_DN

HT_AD_C1L2_C2L1_5_DP

HT_AD_C1L2_C2L1_5_DN

HT_AD_C1L2_C2L1_4_DP

HT_AD_C1L2_C2L1_4_DN

HT_AD_C1L2_C2L1_3_DP

HT_AD_C1L2_C2L1_3_DN

HT_AD_C1L2_C2L1_2_DP

HT_AD_C1L2_C2L1_2_DN

HT_AD_C1L2_C2L1_1_DP

HT_AD_C1L2_C2L1_1_DN

HT_AD_C1L2_C2L1_0_DP

HT_AD_C1L2_C2L1_0_DN

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

23

2

3

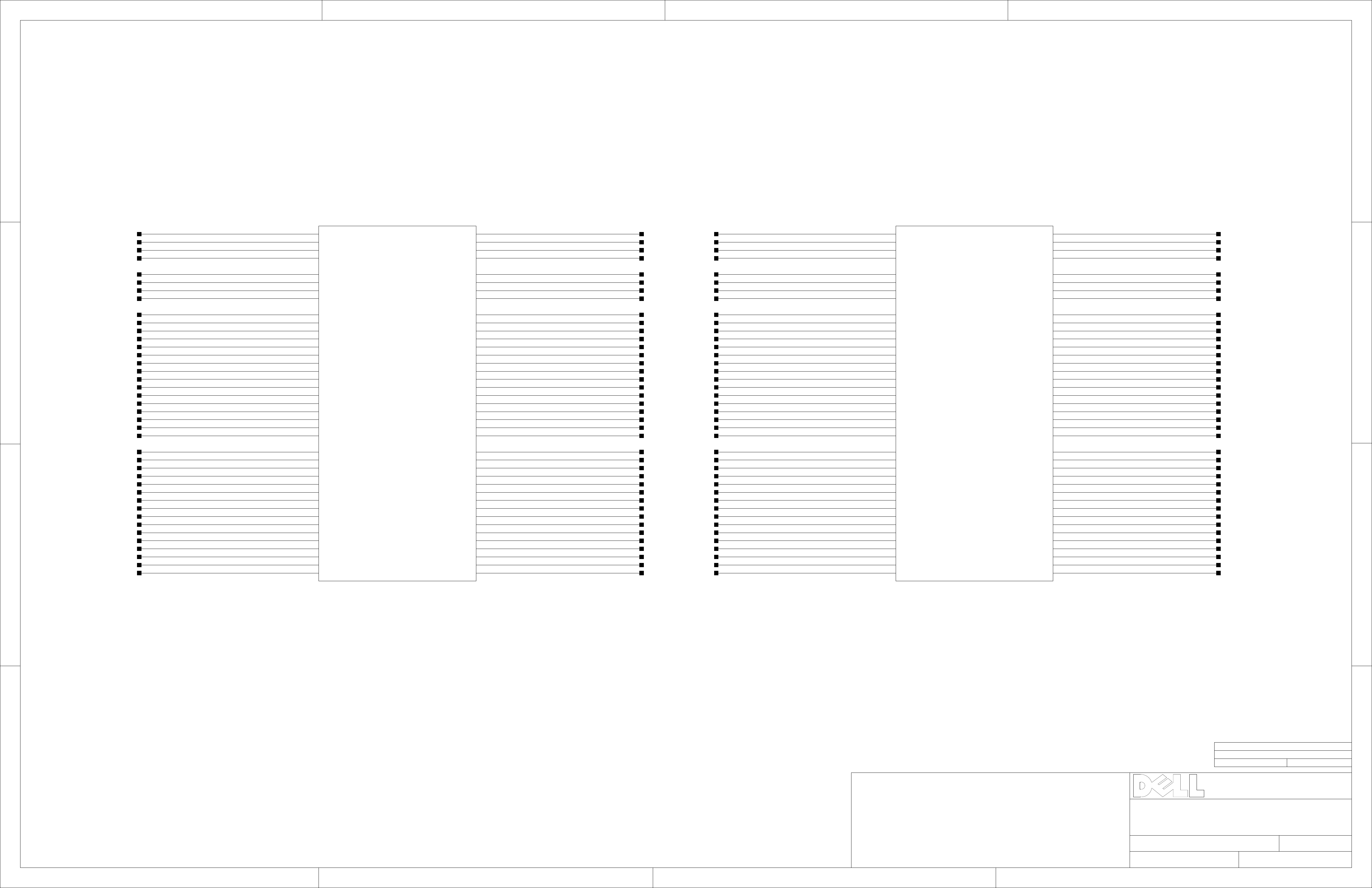

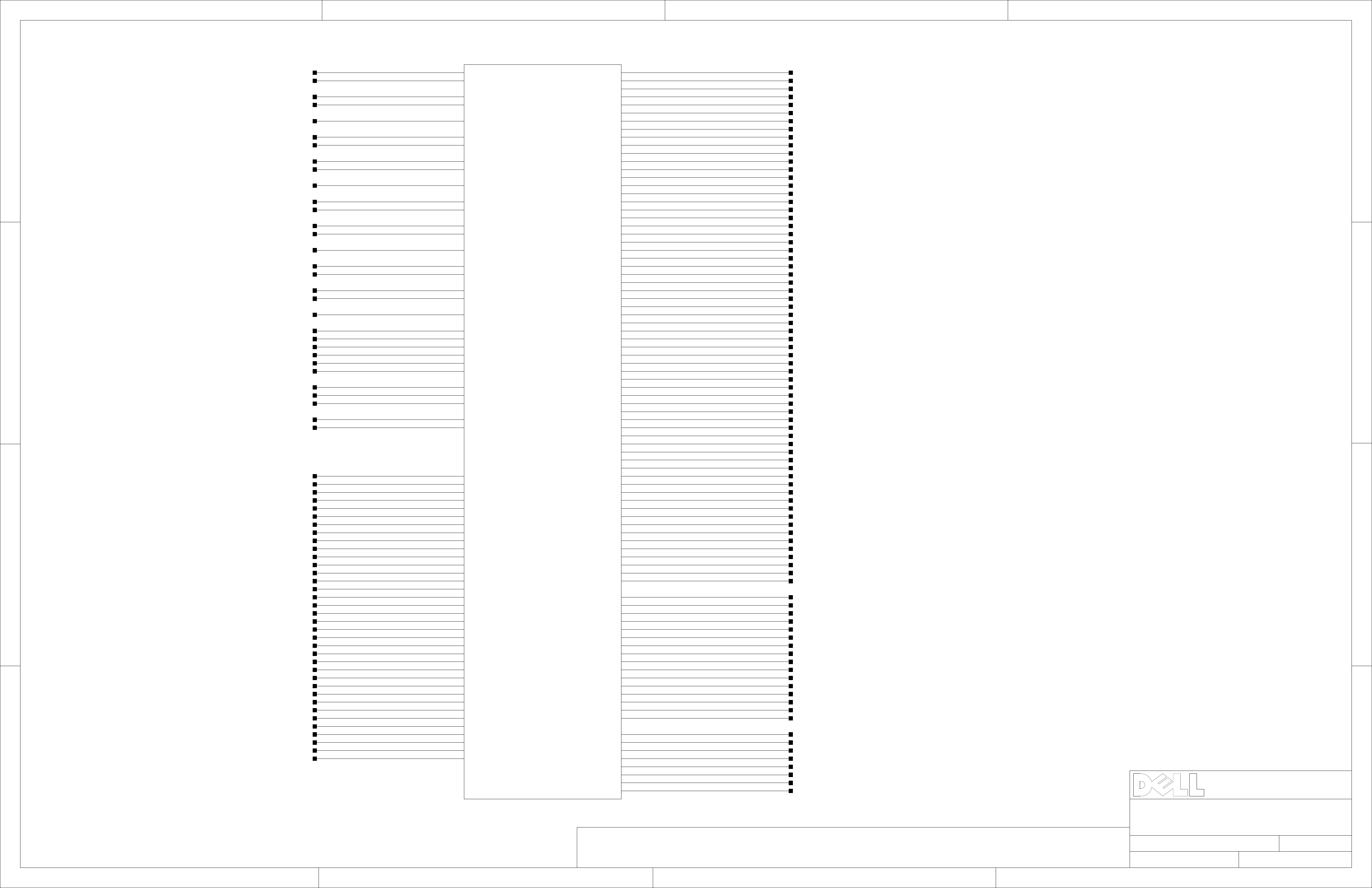

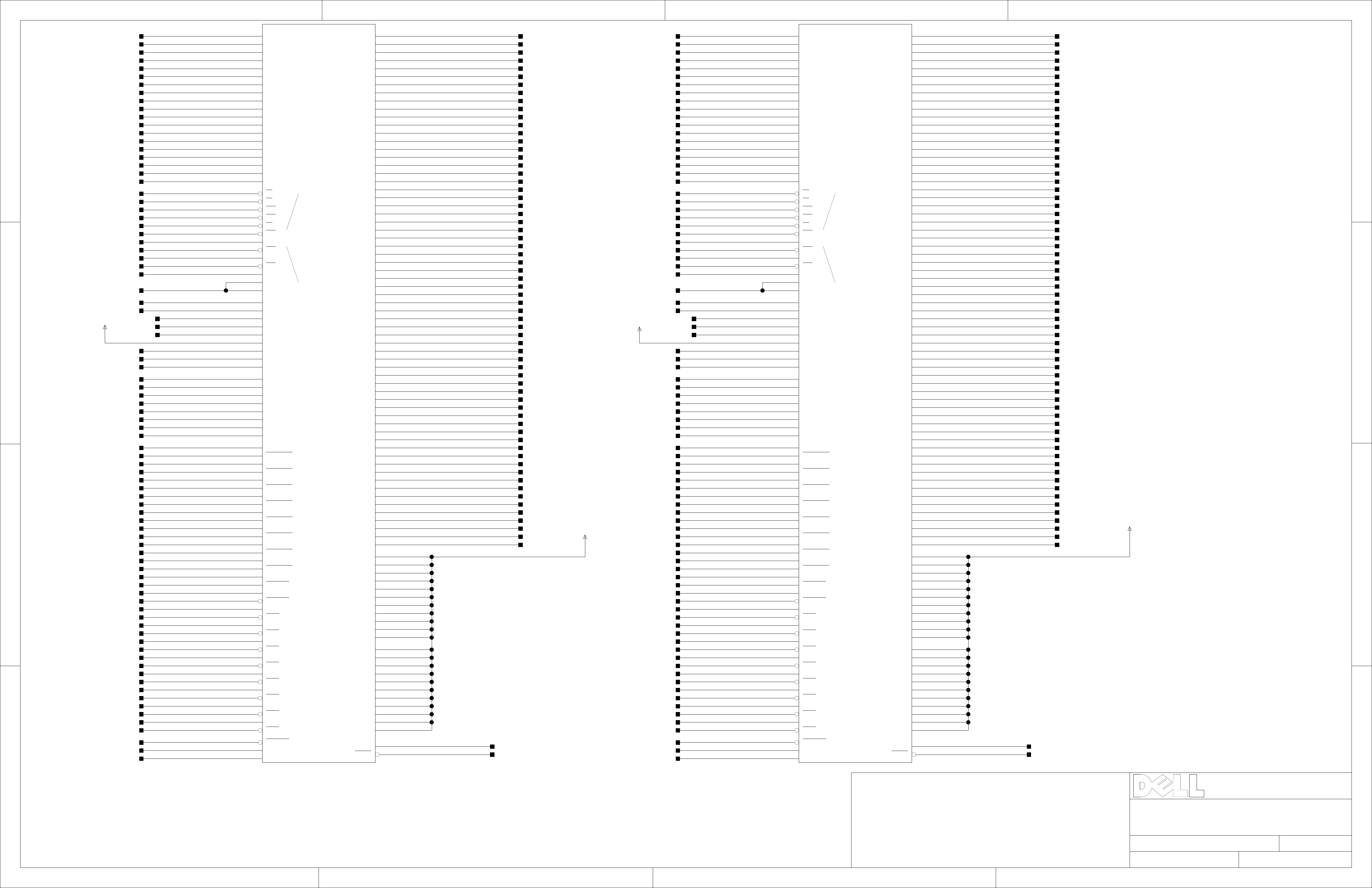

From CPU2 L0

AMC CPU F1207

HETERO 1 OF 11

To CPU2 L0

From CPU2 L1 To CPU2 L1

CPU1 TO CPU2 HYPER TRANSPORT LINKS

AMC CPU F1207

HETERO 3 OF 11

4

ROOM=CPU1

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

C

TITLE

DWG NO.

DATE

MODULE:

DESC:

REV: OF

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

10/2/2008

DBA

SEC

REV.

A05

13 OF 120

211

4

A B C

D

1

+1.2V_VLDT

R8749

51-5%51-5%

1 2

34

34

34

34

34

34

J_CPU1

HT_CK_NBLA_C1L1_1_DP

HT_CK_NBLA_C1L1_1_DN

HT_CK_NBLA_C1L1_0_DP

HT_CK_NBLA_C1L1_0_DN

CPU1_CTLIN_L1_H1 NC_CPU1_AL14

CPU1_CTLIN_L1_L1

HT_CT_NBLA_C1L1_0_DP

HT_CT_NBLA_C1L1_0_DN

E18

L1_CLKIN_H_1

E17

L1_CLKIN_L_1

C18

L1_CLKIN_H_0

B18

L1_CLKIN_L_0

C13

L1_CTLIN_H_1

D13

L1_CTLIN_L_1

A14

L1_CTLIN_H_0

A13

L1_CTLIN_L_0

L1_CLKOUT_H_1

L1_CLKOUT_L_1

L1_CLKOUT_H_0

L1_CLKOUT_L_0

L1_CTLOUT_H_1

L1_CTLOUT_L_1

L1_CTLOUT_H_0

L1_CTLOUT_L_0

E6

D6

B6

B7

F10

F11

C11

D11

HT_CK_C1L1_NBLA_1_DP

HT_CK_C1L1_NBLA_1_DN

HT_CK_C1L1_NBLA_0_DP

HT_CK_C1L1_NBLA_0_DN

NC_CPU1_AL13

HT_CT_C1L1_NBLA_0_DP

HT_CT_C1L1_NBLA_0_DN

1

34

34

34

34

34

34

2

3

R8748

1 2

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

HT_AD_NBLA_C1L1_15_DP

HT_AD_NBLA_C1L1_15_DN

HT_AD_NBLA_C1L1_14_DP

HT_AD_NBLA_C1L1_14_DN

HT_AD_NBLA_C1L1_13_DP

HT_AD_NBLA_C1L1_13_DN

HT_AD_NBLA_C1L1_12_DP

HT_AD_NBLA_C1L1_12_DN

HT_AD_NBLA_C1L1_11_DP

HT_AD_NBLA_C1L1_11_DN

HT_AD_NBLA_C1L1_10_DP

HT_AD_NBLA_C1L1_10_DN

HT_AD_NBLA_C1L1_9_DP

HT_AD_NBLA_C1L1_9_DN

HT_AD_NBLA_C1L1_8_DP

HT_AD_NBLA_C1L1_8_DN

HT_AD_NBLA_C1L1_7_DP

HT_AD_NBLA_C1L1_7_DN

HT_AD_NBLA_C1L1_6_DP

HT_AD_NBLA_C1L1_6_DN

HT_AD_NBLA_C1L1_5_DP

HT_AD_NBLA_C1L1_5_DN

HT_AD_NBLA_C1L1_4_DP

HT_AD_NBLA_C1L1_4_DN

HT_AD_NBLA_C1L1_3_DP

HT_AD_NBLA_C1L1_3_DN

HT_AD_NBLA_C1L1_2_DP

HT_AD_NBLA_C1L1_2_DN

HT_AD_NBLA_C1L1_1_DP

HT_AD_NBLA_C1L1_1_DN

HT_AD_NBLA_C1L1_0_DP

HT_AD_NBLA_C1L1_0_DN

E14

L1_CADIN_H_15

E13

L1_CADIN_L_15

C15

L1_CADIN_H_14

D15

L1_CADIN_L_14

E16

L1_CADIN_H_13

E15

L1_CADIN_L_13

C17

L1_CADIN_H_12

D17

L1_CADIN_L_12

C19

L1_CADIN_H_11

D19

L1_CADIN_L_11

E20

L1_CADIN_H_10

E19

L1_CADIN_L_10

C21

L1_CADIN_H_9

D21

L1_CADIN_L_9

E22

L1_CADIN_H_8

E21

L1_CADIN_L_8

C14

L1_CADIN_H_7

B14

L1_CADIN_L_7

A16

L1_CADIN_H_6

A15

L1_CADIN_L_6

C16

L1_CADIN_H_5

B16

L1_CADIN_L_5

A18

L1_CADIN_H_4

A17

L1_CADIN_L_4

A20

L1_CADIN_H_3

A19

L1_CADIN_L_3

C20

L1_CADIN_H_2

B20

L1_CADIN_L_2

A22

L1_CADIN_H_1

A21

L1_CADIN_L_1

C22

L1_CADIN_H_0

B22

L1_CADIN_L_0

L1_CADOUT_H_15

L1_CADOUT_L_15

L1_CADOUT_H_14

L1_CADOUT_L_14

L1_CADOUT_H_13

L1_CADOUT_L_13

L1_CADOUT_H_12

L1_CADOUT_L_12

L1_CADOUT_H_11

L1_CADOUT_L_11

L1_CADOUT_H_10

L1_CADOUT_L_10

L1_CADOUT_H_9

L1_CADOUT_L_9

L1_CADOUT_H_8

L1_CADOUT_L_8

L1_CADOUT_H_7

L1_CADOUT_L_7

L1_CADOUT_H_6

L1_CADOUT_L_6

L1_CADOUT_H_5

L1_CADOUT_L_5

L1_CADOUT_H_4

L1_CADOUT_L_4

L1_CADOUT_H_3

L1_CADOUT_L_3

L1_CADOUT_H_2

L1_CADOUT_L_2

L1_CADOUT_H_1

L1_CADOUT_L_1

L1_CADOUT_H_0

L1_CADOUT_L_0

E10

D10

F8

F9

E8

D8

F6

F7

F4

F5

E4

D4

F2

F3

E2

D2

B10

B11

C9

D9

B8

B9

C7

D7

C5

D5

B4

B5

C3

D3

B2

B3

HT_AD_C1L1_NBLA_15_DP

HT_AD_C1L1_NBLA_15_DN

HT_AD_C1L1_NBLA_14_DP

HT_AD_C1L1_NBLA_14_DN

HT_AD_C1L1_NBLA_13_DP

HT_AD_C1L1_NBLA_13_DN

HT_AD_C1L1_NBLA_12_DP

HT_AD_C1L1_NBLA_12_DN

HT_AD_C1L1_NBLA_11_DP

HT_AD_C1L1_NBLA_11_DN

HT_AD_C1L1_NBLA_10_DP

HT_AD_C1L1_NBLA_10_DN

HT_AD_C1L1_NBLA_9_DP

HT_AD_C1L1_NBLA_9_DN

HT_AD_C1L1_NBLA_8_DP

HT_AD_C1L1_NBLA_8_DN

HT_AD_C1L1_NBLA_7_DP

HT_AD_C1L1_NBLA_7_DN

HT_AD_C1L1_NBLA_6_DP

HT_AD_C1L1_NBLA_6_DN

HT_AD_C1L1_NBLA_5_DP

HT_AD_C1L1_NBLA_5_DN

HT_AD_C1L1_NBLA_4_DP

HT_AD_C1L1_NBLA_4_DN

HT_AD_C1L1_NBLA_3_DP

HT_AD_C1L1_NBLA_3_DN

HT_AD_C1L1_NBLA_2_DP

HT_AD_C1L1_NBLA_2_DN

HT_AD_C1L1_NBLA_1_DP

HT_AD_C1L1_NBLA_1_DN

HT_AD_C1L1_NBLA_0_DP

HT_AD_C1L1_NBLA_0_DN

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

34

2

3

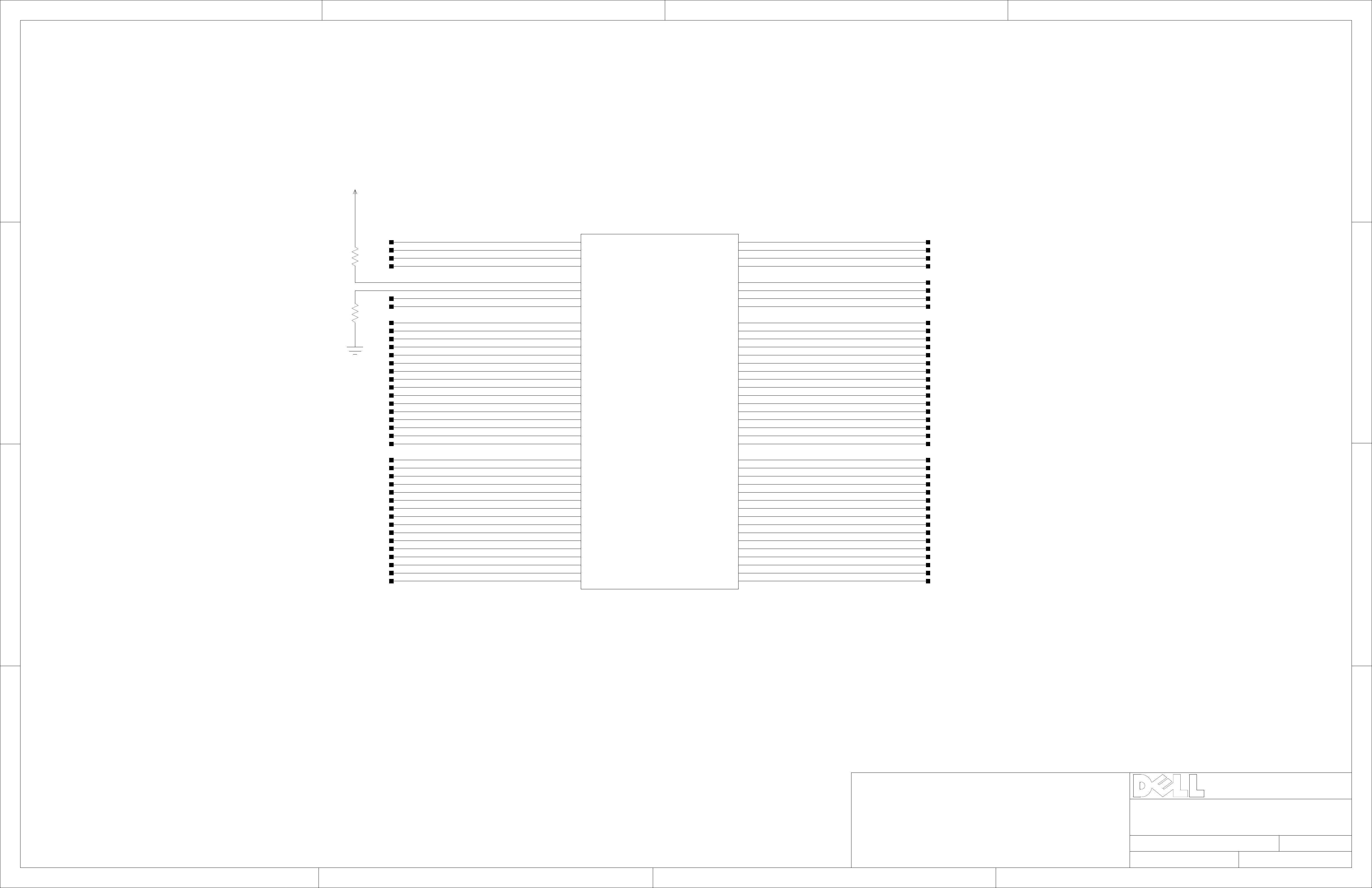

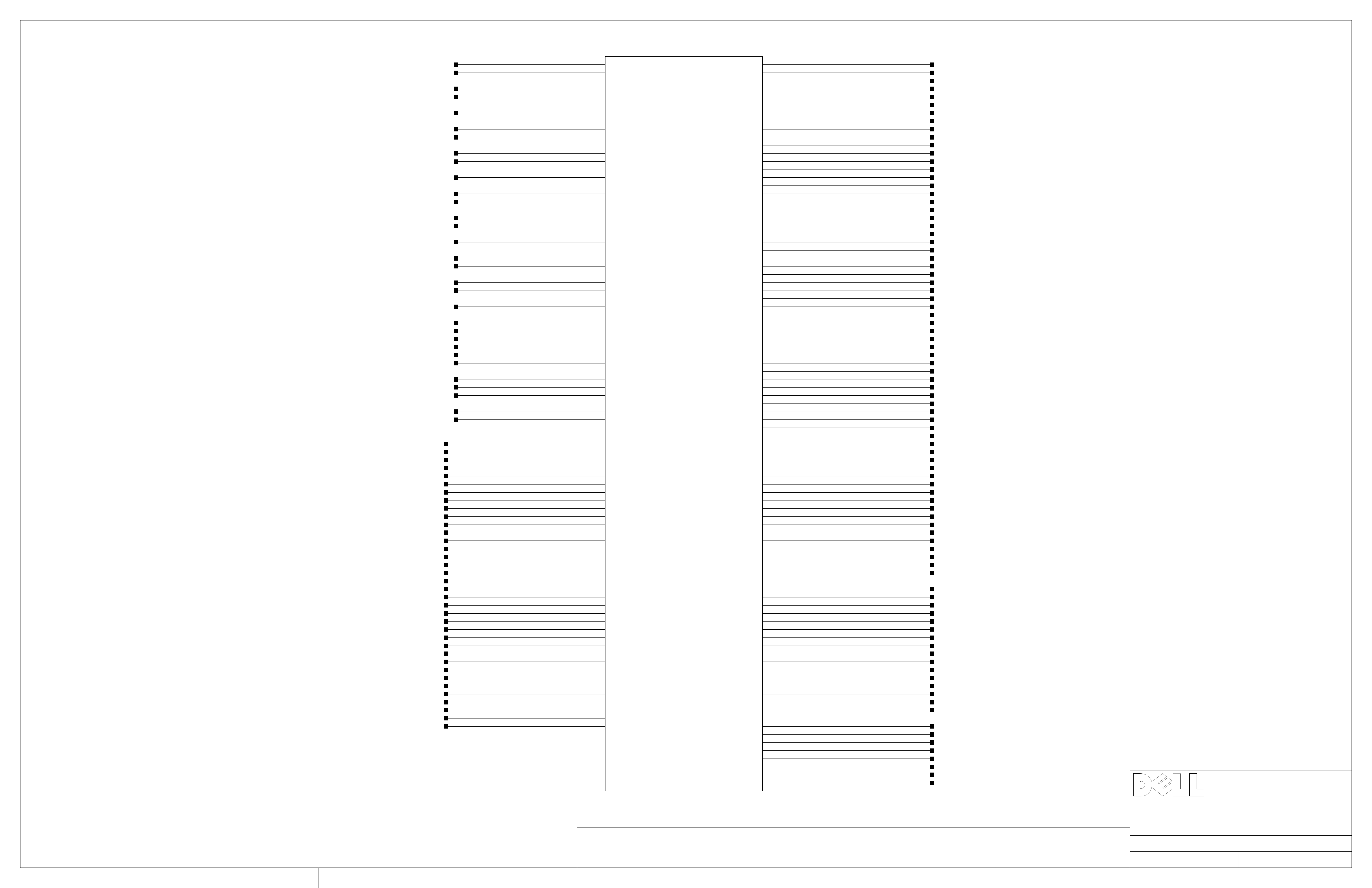

AMC CPU F1207

HETERO 2 OF 11

From HT2100 LA

CPU 1 HYPERTRANSPORT TO HT2100

To HT2100 LA

4

ROOM = CPU1

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

C

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

10/2/2008

DBA

4

REV.

A05

14 OF 120

1

2

3

4

A B C

ROOM=CPU1

20

20

20,22

20,22

20,22

21

21

21,22

21,22

21,22

20,22

20,22

20,22

21,22

21,22

21,22

CK_CPU1_MEM_MA0_DP

CK_CPU1_MEM_MA0_DN

CPU1_MEM_MA0_CS_L1

CPU1_MEM_MA0_CS_L0

CPU1_MEM_MA0_ODT0

CK_CPU1_MEM_MA1_DP

CK_CPU1_MEM_MA1_DN

CPU1_MEM_MA1_CS_L1

CPU1_MEM_MA1_CS_L0

CPU1_MEM_MA1_ODT0

NC_CPU1_Y30

NC_CPU1_Y31

CPU1_MEM_MA2_CS_L1

CPU1_MEM_MA2_CS_L0

CPU1_MEM_MA2_ODT0

NC_CPU1_AA31

NC_CPU1_AA32

CPU1_MEM_MA3_CS_L1

CPU1_MEM_MA3_CS_L0

CPU1_MEM_MA3_ODT0

AD31

AD32

AM34

AH33

AJ32

AE31

AF31

AM35

AH34

AK34

Y30

Y31

AC30

AB32

AB31

AA31

AA32

AD30

AB30

AC32

MA0_CLK_H

MA0_CLK_L

MA0_CS_L_1

MA0_CS_L_0

MA0_ODT_0

MA1_CLK_H

MA1_CLK_L

MA1_CS_L_1

MA1_CS_L_0

MA1_ODT_0

MA2_CLK_H

MA2_CLK_L

MA2_CS_L_1

MA2_CS_L_0

MA2_ODT_0

MA3_CLK_H

MA3_CLK_L

MA3_CS_L_1

MA3_CS_L_0

MA3_ODT_0

X00_DT10369 SCH name fix

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

CPU1_MEM_MA_ERR_R_N

22

20-22

20-22

20-22

20-22

20,21

20-22

20-22

20-22

21,22

20,22

CPU1_MEM_MA_PAR

CPU1_MEM_MA_CAS_N

CPU1_MEM_MA_RAS_N

CPU1_MEM_MA_WE_N

CPU1_MEM_MA_RESET_N

CPU1_MEM_MA_BANK2

CPU1_MEM_MA_BANK1

CPU1_MEM_MA_BANK0

CPU1_MEM_MA_CKE1

CPU1_MEM_MA_CKE0

CPU1_MEM_MA_DQS_17_DP

CPU1_MEM_MA_DQS_17_DN

CPU1_MEM_MA_DQS_16_DP

CPU1_MEM_MA_DQS_16_DN

CPU1_MEM_MA_DQS_15_DP

CPU1_MEM_MA_DQS_15_DN

CPU1_MEM_MA_DQS_14_DP

CPU1_MEM_MA_DQS_14_DN

CPU1_MEM_MA_DQS_13_DP

CPU1_MEM_MA_DQS_13_DN

CPU1_MEM_MA_DQS_12_DP

CPU1_MEM_MA_DQS_12_DN

CPU1_MEM_MA_DQS_11_DP

CPU1_MEM_MA_DQS_11_DN

CPU1_MEM_MA_DQS_10_DP

CPU1_MEM_MA_DQS_10_DN

CPU1_MEM_MA_DQS_9_DP

CPU1_MEM_MA_DQS_9_DN

CPU1_MEM_MA_DQS_8_DP

CPU1_MEM_MA_DQS_8_DN

CPU1_MEM_MA_DQS_7_DP

CPU1_MEM_MA_DQS_7_DN

CPU1_MEM_MA_DQS_6_DP

CPU1_MEM_MA_DQS_6_DN

CPU1_MEM_MA_DQS_5_DP

CPU1_MEM_MA_DQS_5_DN

CPU1_MEM_MA_DQS_4_DP

CPU1_MEM_MA_DQS_4_DN

CPU1_MEM_MA_DQS_3_DP

CPU1_MEM_MA_DQS_3_DN

CPU1_MEM_MA_DQS_2_DP

CPU1_MEM_MA_DQS_2_DN

CPU1_MEM_MA_DQS_1_DP

CPU1_MEM_MA_DQS_1_DN

CPU1_MEM_MA_DQS_0_DP

CPU1_MEM_MA_DQS_0_DN

P30

AF32

AJ33

AH32

AJ31

D33

N32

AF33

AG32

M30

M31

T27

T26

AL26

AM26

AL31

AM31

AH29

AG29

AB27

AC27

J31

J32

L29

K29

D31

D32

F27

F26

U25

U26

AK25

AK26

AK30

AK31

AH28

AJ28

AD26

AD27

K33

J33

H29

G29

F31

E31

D27

D26

MA_ERR_L

MA_PAR

MA_CAS_L

MA_RAS_L

MA_WE_L

MA_RESET_L

MA_BANK_2

MA_BANK_1

MA_BANK_0

MA_CKE_1

MA_CKE_0

MA_DQS_H_17

MA_DQS_L_17

MA_DQS_H_16

MA_DQS_L_16

MA_DQS_H_15

MA_DQS_L_15

MA_DQS_H_14

MA_DQS_L_14

MA_DQS_H_13

MA_DQS_L_13

MA_DQS_H_12

MA_DQS_L_12

MA_DQS_H_11

MA_DQS_L_11

MA_DQS_H_10

MA_DQS_L_10

MA_DQS_H_9

MA_DQS_L_9

MA_DQS_H_8

MA_DQS_L_8

MA_DQS_H_7

MA_DQS_L_7

MA_DQS_H_6

MA_DQS_L_6

MA_DQS_H_5

MA_DQS_L_5

MA_DQS_H_4

MA_DQS_L_4

MA_DQS_H_3

MA_DQS_L_3

MA_DQS_H_2

MA_DQS_L_2

MA_DQS_H_1

MA_DQS_L_1

MA_DQS_H_0

MA_DQS_L_0

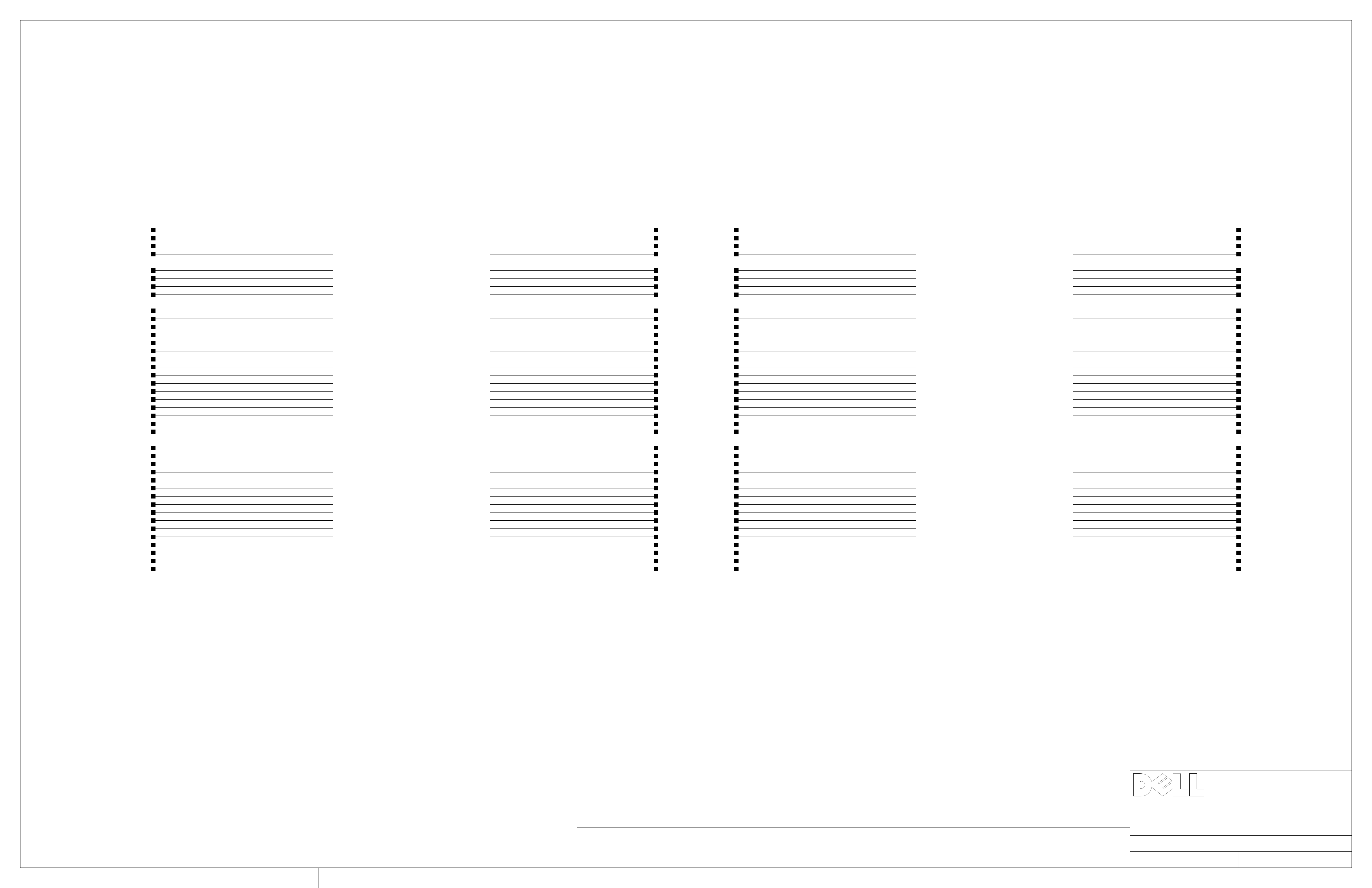

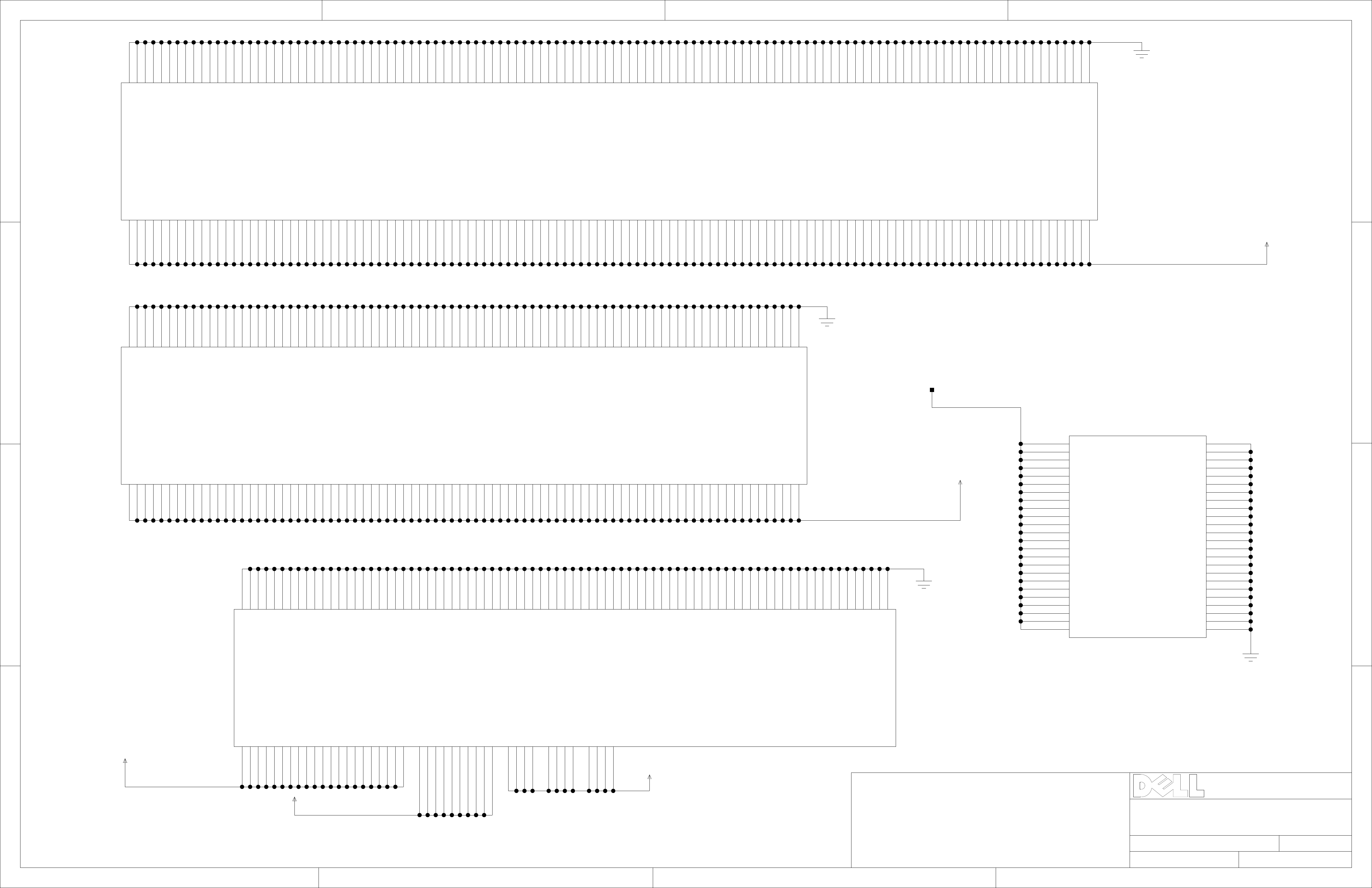

CPU 1 - CHANNEL A MEMORY

J_CPU1

AMC CPU F1207

HETERO 4 OF 11

MA_DATA_63

MA_DATA_62

MA_DATA_61

MA_DATA_60

MA_DATA_59

MA_DATA_58

MA_DATA_57

MA_DATA_56

MA_DATA_55

MA_DATA_54

MA_DATA_53

MA_DATA_52

MA_DATA_51

MA_DATA_50

MA_DATA_49

MA_DATA_48

MA_DATA_47

MA_DATA_46

MA_DATA_45

MA_DATA_44

MA_DATA_43

MA_DATA_42

MA_DATA_41

MA_DATA_40

MA_DATA_39

MA_DATA_38

MA_DATA_37

MA_DATA_36

MA_DATA_35

MA_DATA_34

MA_DATA_33

MA_DATA_32

MA_DATA_31

MA_DATA_30

MA_DATA_29

MA_DATA_28

MA_DATA_27

MA_DATA_26

MA_DATA_25

MA_DATA_24

MA_DATA_23

MA_DATA_22

MA_DATA_21

MA_DATA_20

MA_DATA_19

MA_DATA_18

MA_DATA_17

MA_DATA_16

MA_DATA_15

MA_DATA_14

MA_DATA_13

MA_DATA_12

MA_DATA_11

MA_DATA_10

MA_DATA_9

MA_DATA_8

MA_DATA_7

MA_DATA_6

MA_DATA_5

MA_DATA_4

MA_DATA_3

MA_DATA_2

MA_DATA_1

MA_DATA_0

MA_ADD_0

MA_ADD_1

MA_ADD_2

MA_ADD_3

MA_ADD_4

MA_ADD_5

MA_ADD_6

MA_ADD_7

MA_ADD_8

MA_ADD_9

MA_ADD_10

MA_ADD_11

MA_ADD_12

MA_ADD_13

MA_ADD_14

MA_ADD_15

MA_CHECK_7

MA_CHECK_6

MA_CHECK_5

MA_CHECK_4

MA_CHECK_3

MA_CHECK_2

MA_CHECK_1

MA_CHECK_0

AM24

AM25

AL28

AK28

AK24

AL24

AM27

AL27

AK29

AM30

AL33

AK33

AM29

AL29

AM32

AL32

AF28

AF29

AG30

AE30

AE28

AE29

AH30

AJ30

AB25

AB26

AC29

AB29

AC25

AD25

AD28

AC28

L31

K31

G32

G31

L32

L33

H33

H32

H30

G30

K28

L28

K30

J30

H28

J28

E33

D35

F29

E29

F33

F32

E30

D30

F28

E26

B24

C24

E28

D28

E25

D25

AE33

V33

Y33

U31

U32

U30

T32

R31

T31

P32

AG31

R30

P31

AL34

N30

M32

V29

V27

R29

R28

V25

V28

R25

R26

CPU1_MEM_MA_DATA63

CPU1_MEM_MA_DATA62

CPU1_MEM_MA_DATA61

CPU1_MEM_MA_DATA60

CPU1_MEM_MA_DATA59

CPU1_MEM_MA_DATA58

CPU1_MEM_MA_DATA57

CPU1_MEM_MA_DATA56

CPU1_MEM_MA_DATA55

CPU1_MEM_MA_DATA54

CPU1_MEM_MA_DATA53

CPU1_MEM_MA_DATA52

CPU1_MEM_MA_DATA51

CPU1_MEM_MA_DATA50

CPU1_MEM_MA_DATA49

CPU1_MEM_MA_DATA48

CPU1_MEM_MA_DATA47

CPU1_MEM_MA_DATA46

CPU1_MEM_MA_DATA45

CPU1_MEM_MA_DATA44

CPU1_MEM_MA_DATA43

CPU1_MEM_MA_DATA42

CPU1_MEM_MA_DATA41

CPU1_MEM_MA_DATA40

CPU1_MEM_MA_DATA39

CPU1_MEM_MA_DATA38

CPU1_MEM_MA_DATA37

CPU1_MEM_MA_DATA36

CPU1_MEM_MA_DATA35

CPU1_MEM_MA_DATA34

CPU1_MEM_MA_DATA33

CPU1_MEM_MA_DATA32

CPU1_MEM_MA_DATA31

CPU1_MEM_MA_DATA30

CPU1_MEM_MA_DATA29

CPU1_MEM_MA_DATA28

CPU1_MEM_MA_DATA27

CPU1_MEM_MA_DATA26

CPU1_MEM_MA_DATA25

CPU1_MEM_MA_DATA24

CPU1_MEM_MA_DATA23

CPU1_MEM_MA_DATA22

CPU1_MEM_MA_DATA21

CPU1_MEM_MA_DATA20

CPU1_MEM_MA_DATA19

CPU1_MEM_MA_DATA18

CPU1_MEM_MA_DATA17

CPU1_MEM_MA_DATA16

CPU1_MEM_MA_DATA15

CPU1_MEM_MA_DATA14

CPU1_MEM_MA_DATA13

CPU1_MEM_MA_DATA12

CPU1_MEM_MA_DATA11

CPU1_MEM_MA_DATA10

CPU1_MEM_MA_DATA9

CPU1_MEM_MA_DATA8

CPU1_MEM_MA_DATA7

CPU1_MEM_MA_DATA6

CPU1_MEM_MA_DATA5

CPU1_MEM_MA_DATA4

CPU1_MEM_MA_DATA3

CPU1_MEM_MA_DATA2

CPU1_MEM_MA_DATA1

CPU1_MEM_MA_DATA0

CPU1_MEM_MA_ADD0

CPU1_MEM_MA_ADD1

CPU1_MEM_MA_ADD2

CPU1_MEM_MA_ADD3

CPU1_MEM_MA_ADD4

CPU1_MEM_MA_ADD5

CPU1_MEM_MA_ADD6

CPU1_MEM_MA_ADD7

CPU1_MEM_MA_ADD8

CPU1_MEM_MA_ADD9

CPU1_MEM_MA_ADD10

CPU1_MEM_MA_ADD11

CPU1_MEM_MA_ADD12

CPU1_MEM_MA_ADD13

CPU1_MEM_MA_ADD14

CPU1_MEM_MA_ADD15

CPU1_MEM_MA_CHECK7

CPU1_MEM_MA_CHECK6

CPU1_MEM_MA_CHECK5

CPU1_MEM_MA_CHECK4

CPU1_MEM_MA_CHECK3

CPU1_MEM_MA_CHECK2

CPU1_MEM_MA_CHECK1

CPU1_MEM_MA_CHECK0

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

D

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

10/2/2008

1

2

3

4

REV.

A05

15 OF 120

C

DBA

1

2

3

4

A B C

J_CPU1

CK_CPU1_MEM_MB0_DP

20

CK_CPU1_MEM_MB0_DN

20

20,22

20,22

20,22

21,22

21,22

21,22

CPU1_MEM_MB0_CS_L1

CPU1_MEM_MB0_CS_L0

CPU1_MEM_MB0_ODT0

CK_CPU1_MEM_MB1_DP

21

CK_CPU1_MEM_MB1_DN

21

CPU1_MEM_MB1_CS_L1

CPU1_MEM_MB1_CS_L0

CPU1_MEM_MB1_ODT0

NC_CPU1_U29

NC_CPU1_U28

20,22

20,22

20,22

CPU1_MEM_MB2_CS_L1

CPU1_MEM_MB2_CS_L0

CPU1_MEM_MB2_ODT0

NC_CPU1_T29

NC_CPU1_T28

21,22

21,22

21,22

CPU1_MEM_MB3_CS_L1

CPU1_MEM_MB3_CS_L0

CPU1_MEM_MB3_ODT0

X00_DT10369 SCH name fix

CPU1_MEM_MB_ERR_R_N

22

20-22

20-22

20-22

20-22

20,21

20-22

20-22

20-22

21,22

20,22

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

CPU1_MEM_MB_PAR

CPU1_MEM_MB_CAS_N

CPU1_MEM_MB_RAS_N

CPU1_MEM_MB_WE_N

CPU1_MEM_MB_RESET_N

CPU1_MEM_MB_BANK2

CPU1_MEM_MB_BANK1

CPU1_MEM_MB_BANK0

CPU1_MEM_MB_CKE1

CPU1_MEM_MB_CKE0

CPU1_MEM_MB_DQS_17_DP

CPU1_MEM_MB_DQS_17_DN

CPU1_MEM_MB_DQS_16_DP

CPU1_MEM_MB_DQS_16_DN

CPU1_MEM_MB_DQS_15_DP

CPU1_MEM_MB_DQS_15_DN

CPU1_MEM_MB_DQS_14_DP

CPU1_MEM_MB_DQS_14_DN

CPU1_MEM_MB_DQS_13_DP

CPU1_MEM_MB_DQS_13_DN

CPU1_MEM_MB_DQS_12_DP

CPU1_MEM_MB_DQS_12_DN

CPU1_MEM_MB_DQS_11_DP

CPU1_MEM_MB_DQS_11_DN

CPU1_MEM_MB_DQS_10_DP

CPU1_MEM_MB_DQS_10_DN

CPU1_MEM_MB_DQS_9_DP

CPU1_MEM_MB_DQS_9_DN

CPU1_MEM_MB_DQS_8_DP

CPU1_MEM_MB_DQS_8_DN

CPU1_MEM_MB_DQS_7_DP

CPU1_MEM_MB_DQS_7_DN

CPU1_MEM_MB_DQS_6_DP

CPU1_MEM_MB_DQS_6_DN

CPU1_MEM_MB_DQS_5_DP

CPU1_MEM_MB_DQS_5_DN

CPU1_MEM_MB_DQS_4_DP

CPU1_MEM_MB_DQS_4_DN

CPU1_MEM_MB_DQS_3_DP

CPU1_MEM_MB_DQS_3_DN

CPU1_MEM_MB_DQS_2_DP

CPU1_MEM_MB_DQS_2_DN

CPU1_MEM_MB_DQS_1_DP

CPU1_MEM_MB_DQS_1_DN

CPU1_MEM_MB_DQS_0_DP

CPU1_MEM_MB_DQS_0_DN

Y35

Y34

AJ35

AE35

AG34

AA34

AA33

AK35

AD35

AG35

U29

U28

W31

V32

W32

T29

T28

W30

V30

W33

P33

AB34

AF34

AD33

AE34

A33

N33

AC34

AC33

M34

M35

M29

N29

AN28

AN27

AN33

AN32

AG27

AH27

AA29

AA28

G34

G35

K26

J26

A31

A32

A26

A27

N27

N28

AP26

AP27

AP31

AP32

AJ26

AJ27

W26

W27

H35

H34

H27

G27

C32

B32

B27

C27

MB0_CLK_H

MB0_CLK_L

MB0_CS_L_1

MB0_CS_L_0

MB0_ODT_0

MB1_CLK_H

MB1_CLK_L

MB1_CS_L_1

MB1_CS_L_0

MB1_ODT_0

MB2_CLK_H

MB2_CLK_L

MB2_CS_L_1

MB2_CS_L_0

MB2_ODT_0

MB3_CLK_H

MB3_CLK_L

MB3_CS_L_1

MB3_CS_L_0

MB3_ODT_0

MB_ERR_L

MB_PAR

MB_CAS_L

MB_RAS_L

MB_WE_L

MB_RESET_L

MB_BANK_2

MB_BANK_1

MB_BANK_0

MB_CKE_1

MB_CKE_0

MB_DQS_H_17

MB_DQS_L_17

MB_DQS_H_16

MB_DQS_L_16

MB_DQS_H_15

MB_DQS_L_15

MB_DQS_H_14

MB_DQS_L_14

MB_DQS_H_13

MB_DQS_L_13

MB_DQS_H_12

MB_DQS_L_12

MB_DQS_H_11

MB_DQS_L_11

MB_DQS_H_10

MB_DQS_L_10

MB_DQS_H_9

MB_DQS_L_9

MB_DQS_H_8

MB_DQS_L_8

MB_DQS_H_7

MB_DQS_L_7

MB_DQS_H_6

MB_DQS_L_6

MB_DQS_H_5

MB_DQS_L_5

MB_DQS_H_4

MB_DQS_L_4

MB_DQS_H_3

MB_DQS_L_3

MB_DQS_H_2

MB_DQS_L_2

MB_DQS_H_1

MB_DQS_L_1

MB_DQS_H_0

MB_DQS_L_0

AMC CPU F1207

HETERO 5 OF 11

MB_DATA_63

MB_DATA_62

MB_DATA_61

MB_DATA_60

MB_DATA_59

MB_DATA_58

MB_DATA_57

MB_DATA_56

MB_DATA_55

MB_DATA_54

MB_DATA_53

MB_DATA_52

MB_DATA_51

MB_DATA_50

MB_DATA_49

MB_DATA_48

MB_DATA_47

MB_DATA_46

MB_DATA_45

MB_DATA_44

MB_DATA_43

MB_DATA_42

MB_DATA_41

MB_DATA_40

MB_DATA_39

MB_DATA_38

MB_DATA_37

MB_DATA_36

MB_DATA_35

MB_DATA_34

MB_DATA_33

MB_DATA_32

MB_DATA_31

MB_DATA_30

MB_DATA_29

MB_DATA_28

MB_DATA_27

MB_DATA_26

MB_DATA_25

MB_DATA_24

MB_DATA_23

MB_DATA_22

MB_DATA_21

MB_DATA_20

MB_DATA_19

MB_DATA_18

MB_DATA_17

MB_DATA_16

MB_DATA_15

MB_DATA_14

MB_DATA_13

MB_DATA_12

MB_DATA_11

MB_DATA_10

MB_DATA_9

MB_DATA_8

MB_DATA_7

MB_DATA_6

MB_DATA_5

MB_DATA_4

MB_DATA_3

MB_DATA_2

MB_DATA_1

MB_DATA_0

MB_ADD_0

MB_ADD_1

MB_ADD_2

MB_ADD_3

MB_ADD_4

MB_ADD_5

MB_ADD_6

MB_ADD_7

MB_ADD_8

MB_ADD_9

MB_ADD_10

MB_ADD_11

MB_ADD_12

MB_ADD_13

MB_ADD_14

MB_ADD_15

MB_CHECK_7

MB_CHECK_6

MB_CHECK_5

MB_CHECK_4

MB_CHECK_3

MB_CHECK_2

MB_CHECK_1

MB_CHECK_0

AN25

AR26

AN29

AR29

AP25

AR25

AR28

AP28

AN30

AR31

AR34

AN34

AR30

AP30

AR33

AP33

AG25

AE25

AF26

AE26

AF24

AE24

AG26

AF27

Y26

AA27

W28

W25

Y25

AA26

Y28

Y29

K35

J35

E35

C35

L34

K34

F34

E34

L24

J27

K25

K24

L27

L26

G26

J25

B34

A34

C30

C29

C34

C33

B31

B30

C28

A28

B25

A24

A29

B29

B26

C25

AB35

V34

W35

V35

U34

U35

T33

R33

T34

R35

AC35

R34

P35

AH35

N35

N34

P27

P28

N25

M25

P25

P26

M26

M27

CPU1_MEM_MB_DATA63

CPU1_MEM_MB_DATA62

CPU1_MEM_MB_DATA61

CPU1_MEM_MB_DATA60

CPU1_MEM_MB_DATA59

CPU1_MEM_MB_DATA58

CPU1_MEM_MB_DATA57

CPU1_MEM_MB_DATA56

CPU1_MEM_MB_DATA55

CPU1_MEM_MB_DATA54

CPU1_MEM_MB_DATA53

CPU1_MEM_MB_DATA52

CPU1_MEM_MB_DATA51

CPU1_MEM_MB_DATA50

CPU1_MEM_MB_DATA49

CPU1_MEM_MB_DATA48

CPU1_MEM_MB_DATA47

CPU1_MEM_MB_DATA46

CPU1_MEM_MB_DATA45

CPU1_MEM_MB_DATA44

CPU1_MEM_MB_DATA43

CPU1_MEM_MB_DATA42

CPU1_MEM_MB_DATA41

CPU1_MEM_MB_DATA40

CPU1_MEM_MB_DATA39

CPU1_MEM_MB_DATA38

CPU1_MEM_MB_DATA37

CPU1_MEM_MB_DATA36

CPU1_MEM_MB_DATA35

CPU1_MEM_MB_DATA34

CPU1_MEM_MB_DATA33

CPU1_MEM_MB_DATA32

CPU1_MEM_MB_DATA31

CPU1_MEM_MB_DATA30

CPU1_MEM_MB_DATA29

CPU1_MEM_MB_DATA28

CPU1_MEM_MB_DATA27

CPU1_MEM_MB_DATA26

CPU1_MEM_MB_DATA25

CPU1_MEM_MB_DATA24

CPU1_MEM_MB_DATA23

CPU1_MEM_MB_DATA22

CPU1_MEM_MB_DATA21

CPU1_MEM_MB_DATA20

CPU1_MEM_MB_DATA19

CPU1_MEM_MB_DATA18

CPU1_MEM_MB_DATA17

CPU1_MEM_MB_DATA16

CPU1_MEM_MB_DATA15

CPU1_MEM_MB_DATA14

CPU1_MEM_MB_DATA13

CPU1_MEM_MB_DATA12

CPU1_MEM_MB_DATA11

CPU1_MEM_MB_DATA10

CPU1_MEM_MB_DATA9

CPU1_MEM_MB_DATA8

CPU1_MEM_MB_DATA7

CPU1_MEM_MB_DATA6

CPU1_MEM_MB_DATA5

CPU1_MEM_MB_DATA4

CPU1_MEM_MB_DATA3

CPU1_MEM_MB_DATA2

CPU1_MEM_MB_DATA1

CPU1_MEM_MB_DATA0

CPU1_MEM_MB_ADD0

CPU1_MEM_MB_ADD1

CPU1_MEM_MB_ADD2

CPU1_MEM_MB_ADD3

CPU1_MEM_MB_ADD4

CPU1_MEM_MB_ADD5

CPU1_MEM_MB_ADD6

CPU1_MEM_MB_ADD7

CPU1_MEM_MB_ADD8

CPU1_MEM_MB_ADD9

CPU1_MEM_MB_ADD10

CPU1_MEM_MB_ADD11

CPU1_MEM_MB_ADD12

CPU1_MEM_MB_ADD13

CPU1_MEM_MB_ADD14

CPU1_MEM_MB_ADD15

CPU1_MEM_MB_CHECK7

CPU1_MEM_MB_CHECK6

CPU1_MEM_MB_CHECK5

CPU1_MEM_MB_CHECK4

CPU1_MEM_MB_CHECK3

CPU1_MEM_MB_CHECK2

CPU1_MEM_MB_CHECK1

CPU1_MEM_MB_CHECK0

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20-22

20,21

20,21

20,21

20,21

20,21

20,21

20,21

20,21

D

1

2

3

4

INC.

ROUND ROCK,TEXAS

TITLE

CPU1 - CHANNEL B MEMORY

ROOM=CPU1

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

SCHEM, PLN, SV, PE2970

FP975

SHEET

10/2/2008

DCBA

REV.

A05

16 OF 120

1

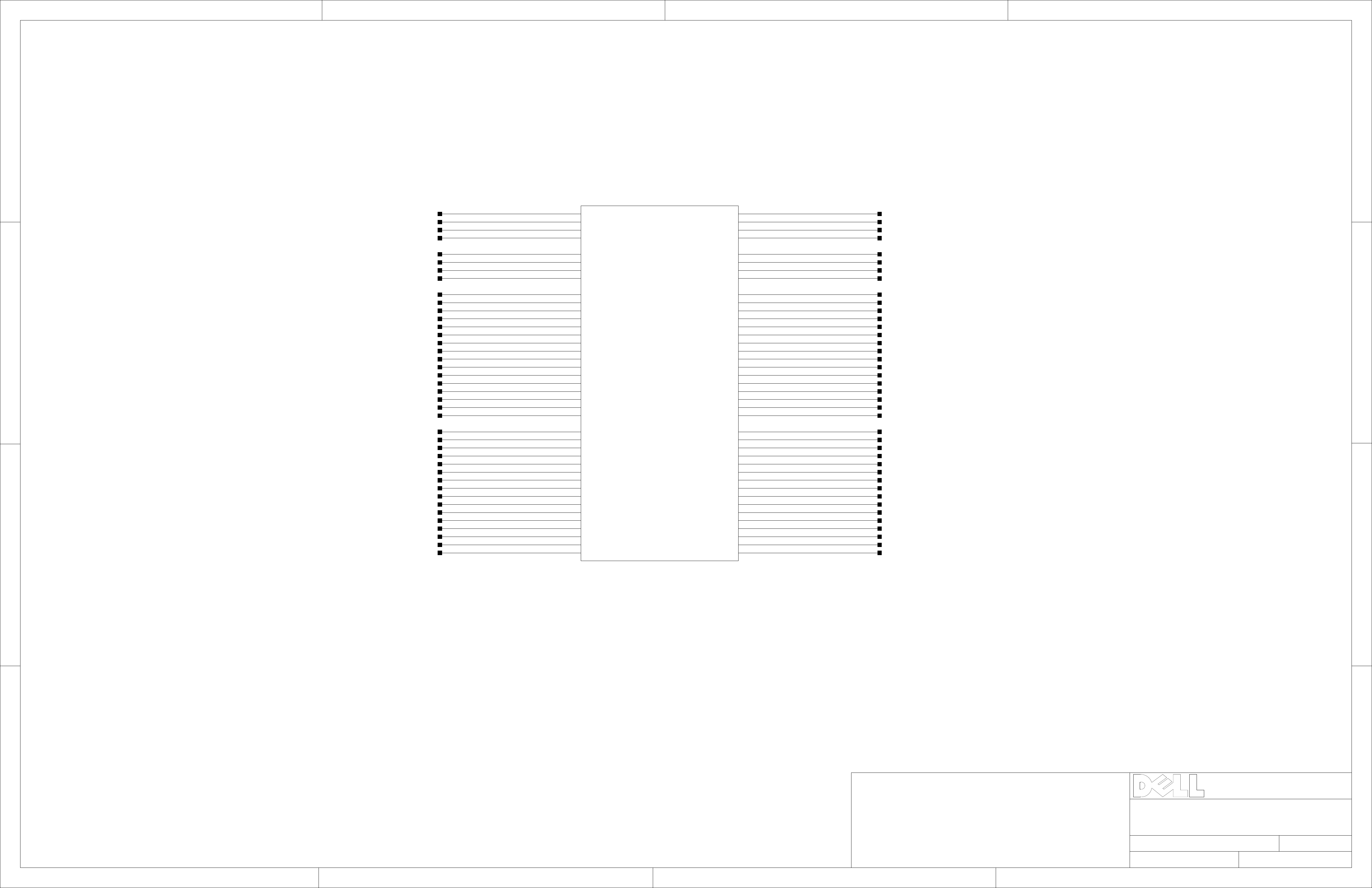

A B C

CK_200M_CPU1_C_DP

12

12

X00_DT9693 SCH routes to CPLD now

CK_200M_CPU1_C_DN

C9383

21

3900pF

50V-10%

C9384

21

3900pF

50V-10%

R9109

1 2

169-1%

17,91

CK_200M_CPU1_DP

CK_200M_CPU1_DN

SYSTEM_PWRGOOD_CPU1

17,91

17,91

49,88

17

17

RST_CPU1_N

CPU1_LDTSTOP_N

CPU1_PRES_N

MOD_CPU1_SIC

MOD_CPU1_SID

+VDDA_CPU1

G2

G3

G4

K22

J22

F21

F19

H25

AP1

AG19

AF19

VDDA1

VDDA2

VDDA3

CLKIN_H

CLKIN_L

PWROK

RESET_L

LDTSTOP_L

CPU_PRESENT_L

SIC

SID

J_CPU1

VID_5

VID_4

VID_3

VID_2

VID_1

VID_0

THERMTRIP_L

PROCHOT_L

E24

G18

J19

H19

K19

H18

AH19

AJ19

CPU1_VID5

CPU1_VID4

CPU1_VID3

CPU1_VID2

CPU1_VID1

CPU1_VID0

CPU1_THERMTRIP_N

CPU1_PROCHOT_N

90,93

90,93

90,93

90,93

90,93

90,93

17,88

17,88

90,97

NC_CPU1_J18

NC_CPU1_G19

CPU1_CORE_TYPE

NC_CPU1_H11

NC_CPU1_J11

NC_CPU1_K11 NC_CPU1_AG18

J18

G19

AN1

H11

J11

K11

RSVD_J18

RSVD_G19

RSVD_AN1

RSVD_H11

RSVD_J11

RSVD_K11

J_CPU1

AMC CPU F1207

HETERO 7 OF 11

RSVD_H10

RSVD_H9

RSVD_AJ18

RSVD_AH18

RSVD_AG18

H10

H9

AJ18

AH18

AG18

D

CPU1_NB_COREFB_POS

CPU1_NB_COREFB_NEG

NC_CPU1_AJ18

NC_CPU1_AH18

97

97

1

2

+MEM_CPU1

93

93

102

CPU1_COREFB_POS

CPU1_COREFB_NEG

CPU1_DDRVTT_SENSE

17,117

17

17

17

17

33

33

33

33

33

R9113

1 2

0-5%

CPU1_PLLTEST_1

CPU1_PLLTEST_0

NC_MOD_CPU1_TEST_2

NC_MOD_CPU1_TEST_3

CPU1_TDI

CPU1_TRST_N

CPU1_TCK

CPU1_TMS

CPU1_DBREQ_N

R9112

1 2

V_MEM_CPU1_VREF

CPU1_M_ZN

CPU1_M_ZP

0-5%

R9180

NP

1 2

300-5%

X

AJ22

AG22

AF22

AJ21

F24

J9

J10

AF17

F18

AJ25

AH25

AF20

F23

F20

AG8

AG9

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST23

TEST18

TEST19

TEST2

TEST3

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

THERMDA

THERMDC

TEST13

TEST28_H

TEST28_L

AH22

J24

AG17

AH17

V7

U7

AF8

AF9

AH8

L8

M9

CPU1_TDO

CPU1_DBRDY

V_MEM_CPU1_SENSE_POS

V_MEM_CPU1_SENSE_NEG

MOD_CPU1_L0_REF_1

MOD_CPU1_L0_REF_0

MOD_CPU1_THERMDA

MOD_CPU1_THERMDC

NC_CPU1_TEST_28_DP

NC_CPU1_TEST_28_DN

27,33

33

80

80

103

103

R9234

1 2

44.2-1%

C9352

1 2

R9233

1 2

44.2-1%

C9353

1000pF

50V-10%

+1.2V_VLDT

1 2

1000pF

50V-10%

2

3

+MEM_CPU1

R9184

1 2

NP

R9183

X

300-5%

1 2

R9220

1 2

510-5%

NP

R9179

X

300-5%

1 2

NP

R9181

X

300-5%

1 2

R9221

1 2

510-5%

NP

R9182

X

300-5%

1 2

MOD_CPU1_SCANEN

MOD_CPU1_SCANCK2

MOD_CPU1_SCANCK1

MOD_CPU1_SCANSHIFTENA

MOD_CPU1_SCANSHIFTENB

R9178

NP

1 2

R9185

1 2

300-5%

300-5%

NC_MOD_CPU1_TEST_6

300-5%

X

G21

H21

AJ20

AH20

AG20

AG21

AF21

AH21

AF18

U8

AH9

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST26

TEST9

TEST6

AMC CPU F1207

HETERO 6 OF 11

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

J20

G20

K20

H20

J8

V8

H8

G23

G24

NC_MOD_CPU1_TEST_17

NC_MOD_CPU1_TEST_16

NC_MOD_CPU1_TEST_15

NC_MOD_CPU1_TEST_14

NC_MOD_CPU1_TEST_7

NC_MOD_CPU1_TEST_10

NC_MOD_CPU1_TEST_8

R9154

1 2

80.6-1%

+MEM_CPU1

3

4

+MEM_CPU1

ROOM = CPU1

R9318

1 2

300-5%

R9319

1 2

300-5%

R9320

1 2

300-5%

R9321

1 2

300-5%

R9322

NP

1 2

300-5%

R9323

NP

1 2

300-5%

R9324

NP

1 2

300-5%

CPU1_THERMTRIP_N

CPU1_PROCHOT_N

MOD_CPU1_SIC

MOD_CPU1_SID

SYSTEM_PWRGOOD_CPU1

X

RST_CPU1_N

X

CPU1_LDTSTOP_N

X

X00_DT9809 SCH depop'd R

17,88

17,88

17

17

17,91

17,91

17,91

CPU1 MISC

R9325

1 2

300-5%

R9326

1 2

300-5%

+MEM_CPU1

1 2

1 2

X00_DT9808 SCH added caps

CPU1_PLLTEST_1

CPU1_PLLTEST_0

R9216

39.2-1%

R9215

39.2-1%

C9766

1 2

C9767

1000pF

50V-10%

CPU1_M_ZN

CPU1_M_ZP

1 2

1000pF

50V-10%

17

17

17

17

R9430

1 2

R9805

1 2

R9431

1 2

15-1%

0-5%

R9812

1 2

10K-5%

V_MEM_CPU1_VREF

C9539

1 2

V_MEM_CPU1_VREF_FEEDBACK

1000pF

50V-10%

117

21

C9537

17,117

.1uF

16V-10%

This value calculated to be negative 14ohm.

Hence just keeping a place holder with 10kohm

15-1%

This value calculated to be negative 16ohm. left as is

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

PROPRIETARY NOTE

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2970

FP975

SHEET

10/2/2008

4

REV.

A05

17 OF 120

C

DBA

1

A9

A5

VSS_A9

VSS_A5

A B C

AJ24

AJ23

AJ17

AJ15

AJ11

AJ9

AJ7

AJ5

AJ3

AJ1

AH26

AH24

AH16

AH14

AH12

AH10

AH6

AG28

AG23

AG15

AG13

AG11

AG7

AF30

AF25

AF16

AF14

AF12

AF10

AE27

AE23

AE21

AE19

AE17

AE15

AE13

AE11

AE9

AE7

AE3

AE2

AD29

AD24

AD22

AD20

AD18

AD16

AD14

AD12

AD10

AD8

AD5

AD4

AC26

AC23

AC21

AC19

AC17

AC15

AC13

AC11

AC9

AC7

AB28

AB24

AB22

AB20

AB18

AB16

AB14

AB12

AB10

AB8

AA25

AA23

AA21

AA19

AA17

AA15

AA13

AA11

AA9

AA7

AA3

AA2

A30

A25

VSS_AJ9

VSS_AJ7

VSS_AJ5

VSS_AJ3

VSS_AA2

VSS_A30

VSS_A25

VSS_AA9

VSS_AA7

VSS_AA3

VSS_AA15

VSS_AA13

VSS_AA11

VSS_AA21

VSS_AA19

VSS_AA17

VSS_AB8

VSS_AA25

VSS_AA23

VSS_AB14

VSS_AB12

VSS_AB10

VSS_AB20

VSS_AB18

VSS_AB16

VSS_AB28

VSS_AB24

VSS_AB22

VSS_AC9

VSS_AC7

VSS_AC11

VSS_AC17

VSS_AC15

VSS_AC13

VSS_AC23

VSS_AC21

VSS_AC19

VSS_AD5

VSS_AD4

VSS_AC26

VSS_AD8

VSS_AD12

VSS_AD10

VSS_AD18

VSS_AD16

VSS_AD14

VSS_AD24

VSS_AD22

VSS_AD20

VSS_AE3

VSS_AE2

VSS_AD29

VSS_AE9

VSS_AE7

VSS_AE11

VSS_AE17

VSS_AE15

VSS_AE13

VSS_AE23

VSS_AE21

VSS_AE19

VSS_AF12

VSS_AF10

VSS_AE27

VSS_AF25

VSS_AF16

VSS_AF14

VSS_AG7

VSS_AG11

VSS_AF30

VSS_AG23

VSS_AG15

VSS_AG13

VSS_AH6

VSS_AH10

VSS_AG28

VSS_AH16

VSS_AH14

VSS_AH12

VSS_AJ1

VSS_AH26

VSS_AH24

VSS_AJ17

VSS_AJ15

VSS_AJ11

VSS_AJ24

VSS_AJ23

AK14

AK2

AJ29

VSS_AK2

VSS_AK14

VSS_AJ29

AK20

AK18

AK16

VSS_AK20

VSS_AK18

VSS_AK16

AK27

AK23

AK22

VSS_AK27

VSS_AK23

VSS_AK22

AL3

AL1

AK32

VSS_AL3

VSS_AL1

VSS_AK32

AL25

AL11

AL7

VSS_AL7

VSS_AL11

AM19

AM15

AL30

VSS_AM15

VSS_AL30

VSS_AL25

AN6

AM33

AM28

VSS_AM33

VSS_AM28

VSS_AM19

AN24

AN10

VSS_AN6

VSS_AN24

VSS_AN10

AN35

AN31

AN26

VSS_AN35

VSS_AN31

VSS_AN26

AP22

AP18

AP14

VSS_AP22

VSS_AP18

VSS_AP14

AP29

AP24

VSS_AP29

VSS_AP24

D

1

J_CPU1

VDD_A6

A6

VDD_AA8

VDD_A10

AA8

A10

AA10

VDD_AA14

VDD_AA12

VDD_AA10

AA16

AA14

AA12

VDD_AA20

VDD_AA18

VDD_AA16

AB4

AA20

AA18

VDD_AB7

VDD_AB5

VDD_AB4

AB7

AB5

VDD_AB11

VDD_AB9

AB9

AB13

AB11

VDD_AB17

VDD_AB15

VDD_AB13

AB19

AB17

AB15

VDD_AC2

VDD_AB21

VDD_AB19

AC3

AC2

AB21

VDD_AC10

VDD_AC8

VDD_AC3

AC8

AC10

VDD_AC16

VDD_AC14

VDD_AC12

AC16

AC14

AC12

VDD_AD7

VDD_AC20

VDD_AC18

AD7

AC20

AC18

VDD_AD11

VDD_AD9

AD9

AD11

VDD_AD17

VDD_AD15

VDD_AD13

AD17

AD15

AD13

VDD_AE8

VDD_AD21

VDD_AD19

AE8

AD21

AD19

VDD_AE14

VDD_AE12

VDD_AE10

AE14

AE12

AE10

VDD_AE20

VDD_AE18

VDD_AE16

AE20

AE18

AE16

VDD_AF5

VDD_AF4

AF7

AF5

AF4

VDD_AF13

VDD_AF11

VDD_AF7

AF13

AF11

VDD_AG3

VDD_AG2

VDD_AF15

AG3

AG2

AF15

VDD_AG14

VDD_AG12

VDD_AG10

AG14

AG12

AG10

VDD_AH7

VDD_AH5

VDD_AG16

AH7

AH5

AG16

VDD_AH15

VDD_AH13

VDD_AH11

AH15

AH13

AH11

VDD_AJ4

VDD_AJ2

AJ6

AJ4

AJ2

VDD_AJ10

VDD_AJ8

VDD_AJ6

AJ8

AJ10

VDD_AJ16

VDD_AJ14

VDD_AJ12

AJ16

AJ14

AJ12

VDD_AK13

VDD_AK1

AK1

AK15

AK13

VDD_AK19

VDD_AK17

VDD_AK15

AK21

AK19

AK17

VDD_AL5

VDD_AL2

VDD_AK21

AL9

AL5

AL2

VDD_AM13

VDD_AM1

VDD_AL9

AM1

AM13

VDD_AN4

VDD_AM21

VDD_AM17

AN4

AM21

AM17

VDD_AN12

VDD_AN8

AN8

AP16

AN12

VDD_AR6

VDD_AP20

VDD_AP16

AR6

AR10

AP20

VDD_B19

VDD_B15

VDD_AR10

C2

B19

B15

VDD_C6

VDD_C2

C6

C10

VDD_D16

VDD_C12

VDD_C10

D16

C12

VDD_E3

VDD_D20

E7

E3

D20

VDD_E11

VDD_E7

E12

E11

VDD_F15

VDD_F13

VDD_E12

F15

F13

VDD_G1

VDD_F17

G6

G1

F17

VDD_G8

VDD_G6

G8

G10

VDD_G14

VDD_G12

VDD_G10

G14

G12

VDD_H7

VDD_G16

H7

H13

G16

VDD_H17

VDD_H15

VDD_H13

H17

H15

VDD_J16

VDD_J14

J12

J16

J14

VDD_K5

VDD_K4

VDD_J12

K5

K4

AMC CPU F1207

HETERO 8 OF 11

VDD_K7

K7

CPU socket screws

ADD=ADD*_RP956

ADD1=ADD*_RP956

ADD2=ADD*_RP956

ADD3=ADD*_RP956

CPU socket washers

ADD4=ADD*_GR683

ADD5=ADD*_GR683

ADD6=ADD*_GR683

ADD7=ADD*_GR683

X01_DT12339_GT

+VCORE_CPU1

2

3

AP34

VSS_AP34

J_CPU1

VDD_K9

K9

AR9

AR5

AP35

VSS_AR9

VSS_AR5

VSS_AP35

VDD_K17

VDD_K15

VDD_K13

K17

K15

K13

AR32

AR27

AR24

VSS_AR32

VSS_AR27

VSS_AR24

VDD_L10

VDD_L3

VDD_L2

L3

L2

L10

B17

B13

B12

VSS_B13

VSS_B12

VDD_L14

VDD_L12

L16

L14

L12

B28

B21

VSS_B28

VSS_B21

VSS_B17

VDD_L20

VDD_L18

VDD_L16

L20

L18

J_CPU1

C4

B35

B33

VSS_B35

VSS_B33

VDD_M11

VDD_M7

M7

M13

M11

N17

N15

VSS_N17

VSS_N15

C26

C8

VSS_C8

VSS_C4

VSS_C26

VDD_M17

VDD_M15

VDD_M13

M17

M15

N23

N21

N19

VSS_N21

VSS_N19

D14

D12

C31

VSS_D12

VSS_C31

VDD_M21

VDD_M19

N8

M21

M19

P8

N26

VSS_P8

VSS_N26

VSS_N23

D22

D18

VSS_D22

VSS_D18

VSS_D14

VDD_N12

VDD_N10

VDD_N8

N12

N10

P14

P12

P10

VSS_P12

VSS_P10

D34

D29

D24

VSS_D29

VSS_D24

VDD_N16

VDD_N14

N18

N16

N14

P18

P16

VSS_P18

VSS_P16

VSS_P14

E9

E5

VSS_E9

VSS_E5

VSS_D34

VDD_P4

VDD_N20

VDD_N18

P4

N20

P24

P22

P20

VSS_P22

VSS_P20

F14

E32

E27

VSS_E32

VSS_E27

VDD_P7

VDD_P5

P9

P7

P5

R7

P29

VSS_R7

VSS_P29

VSS_P24

F22

F16

VSS_F22

VSS_F16

VSS_F14

VDD_P13

VDD_P11

VDD_P9

P13

P11

R13

R11

R9

VSS_R9

VSS_R11

F35

F30

F25

VSS_F30

VSS_F25

VDD_P17

VDD_P15

P19

P17

P15

R17

R15

VSS_R17

VSS_R15

VSS_R13

G7

G5