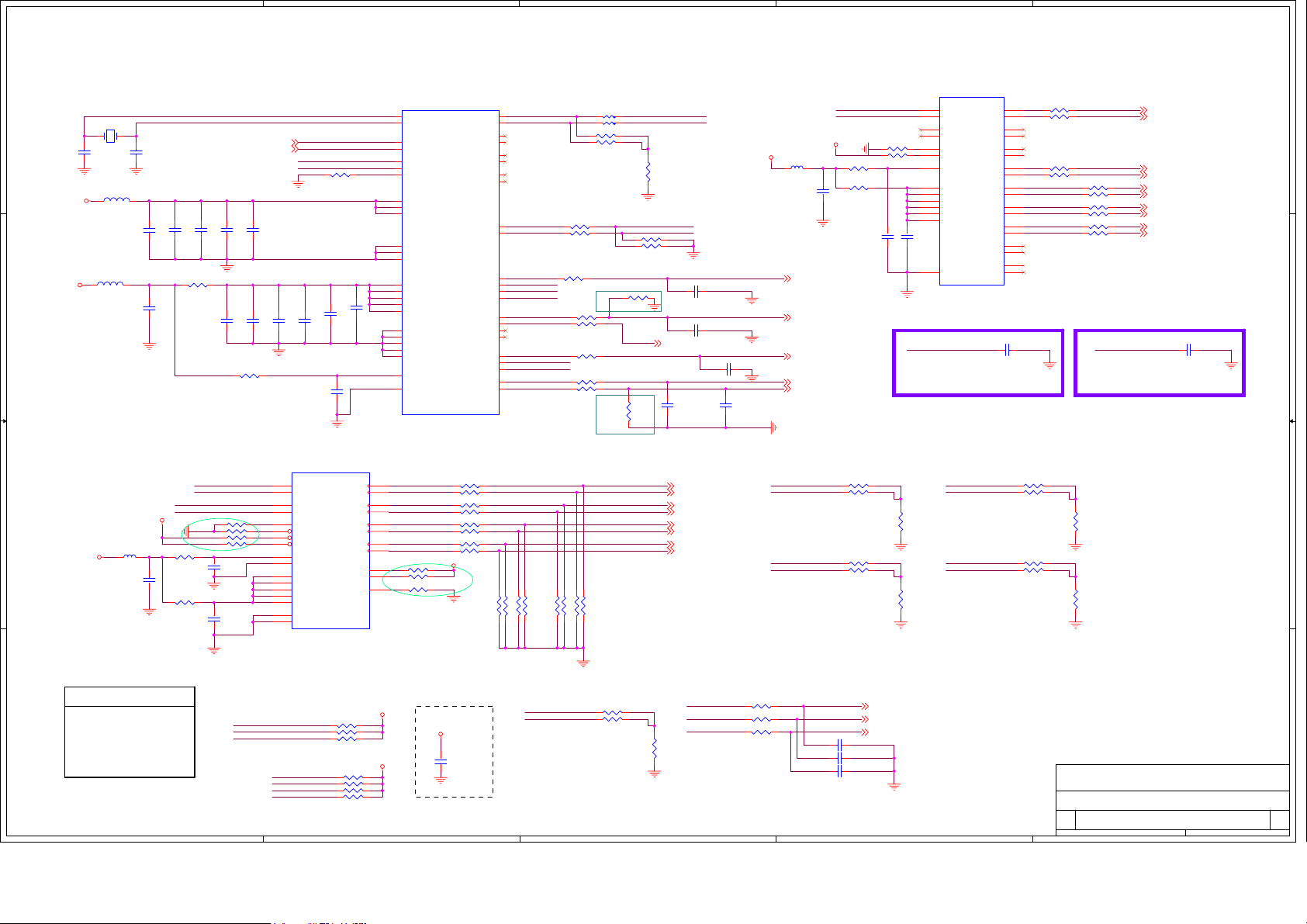

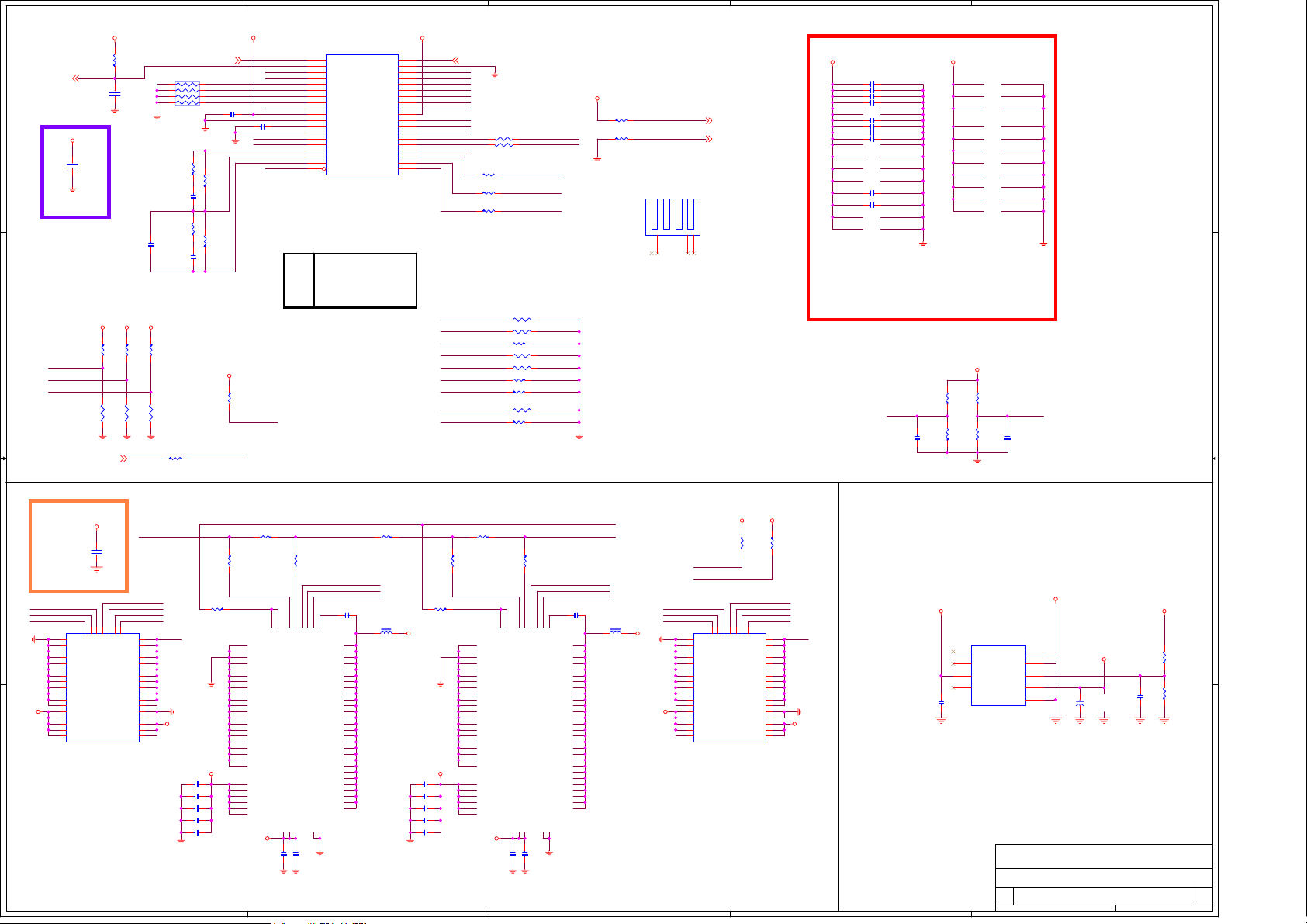

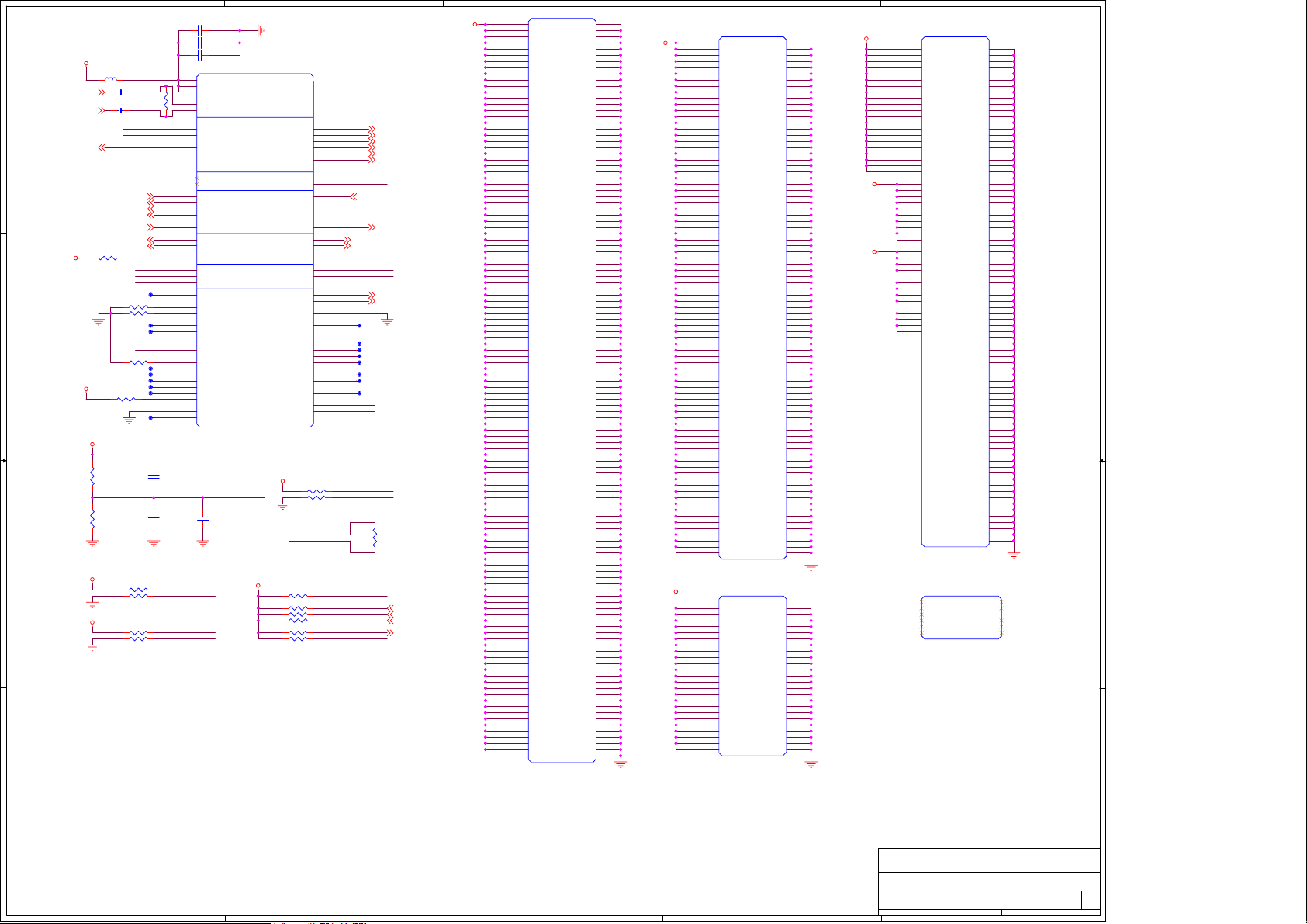

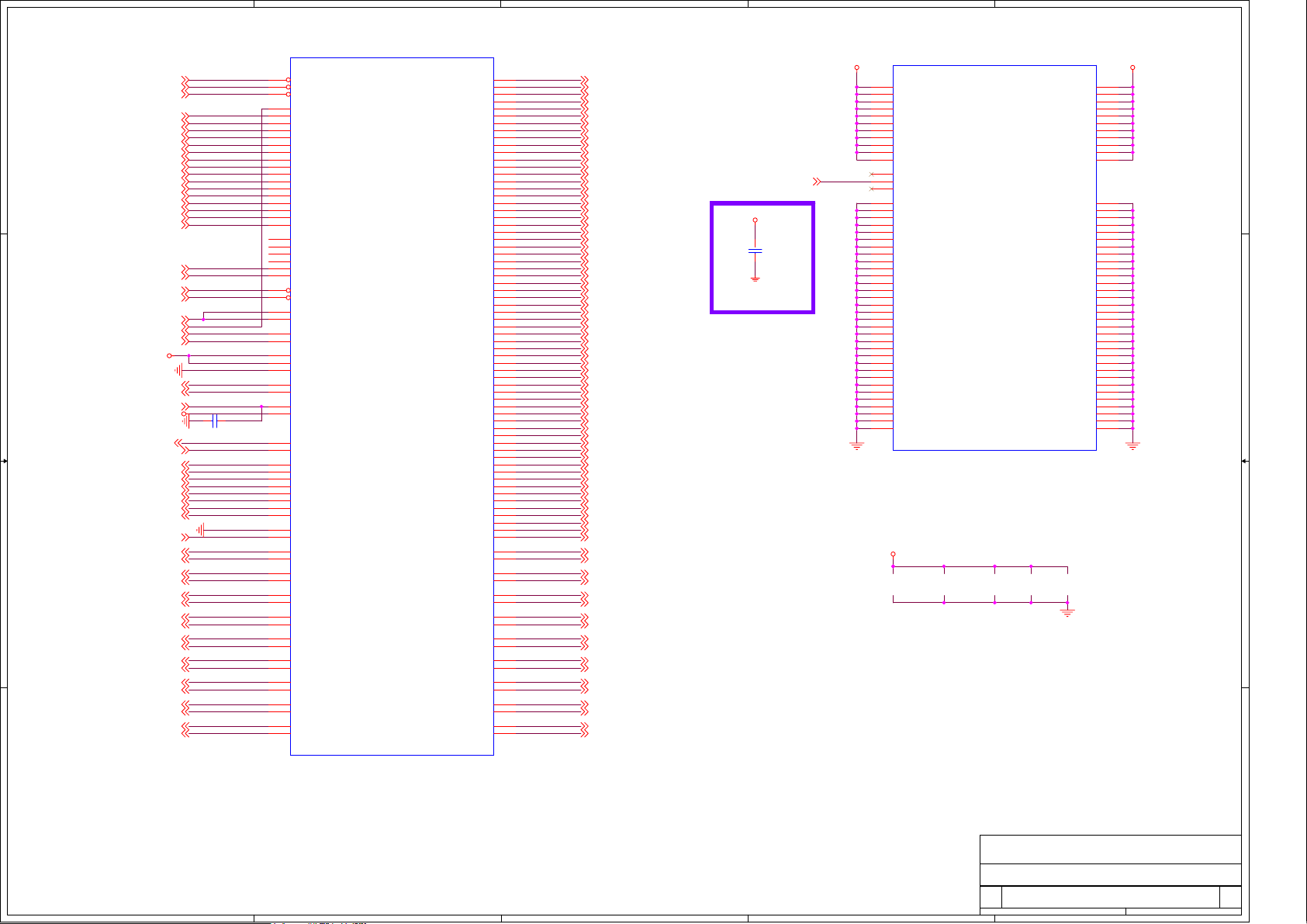

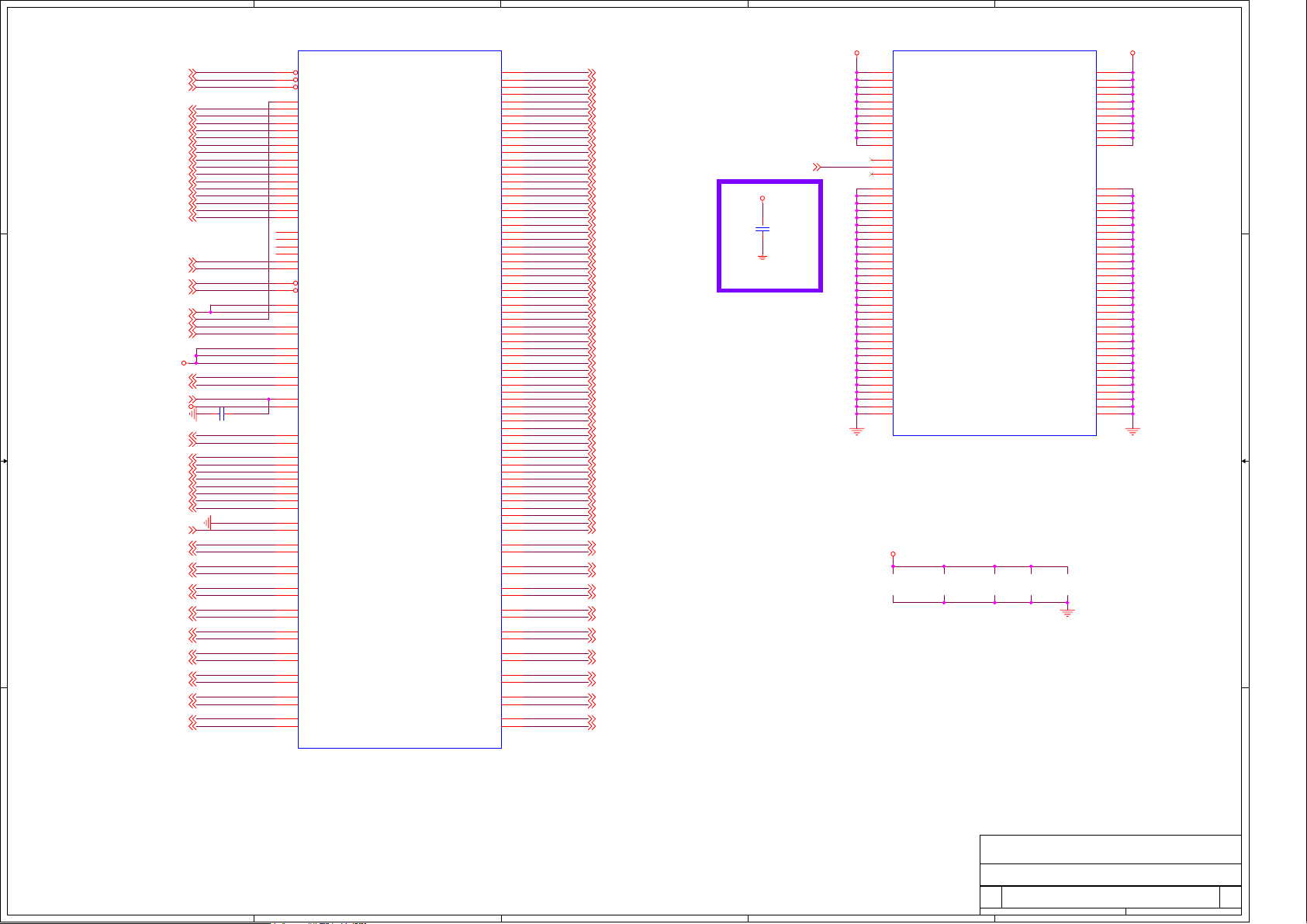

MSI MS-9185 9185_0C_0417_1650

5

4

3

2

1

001

001 COVER

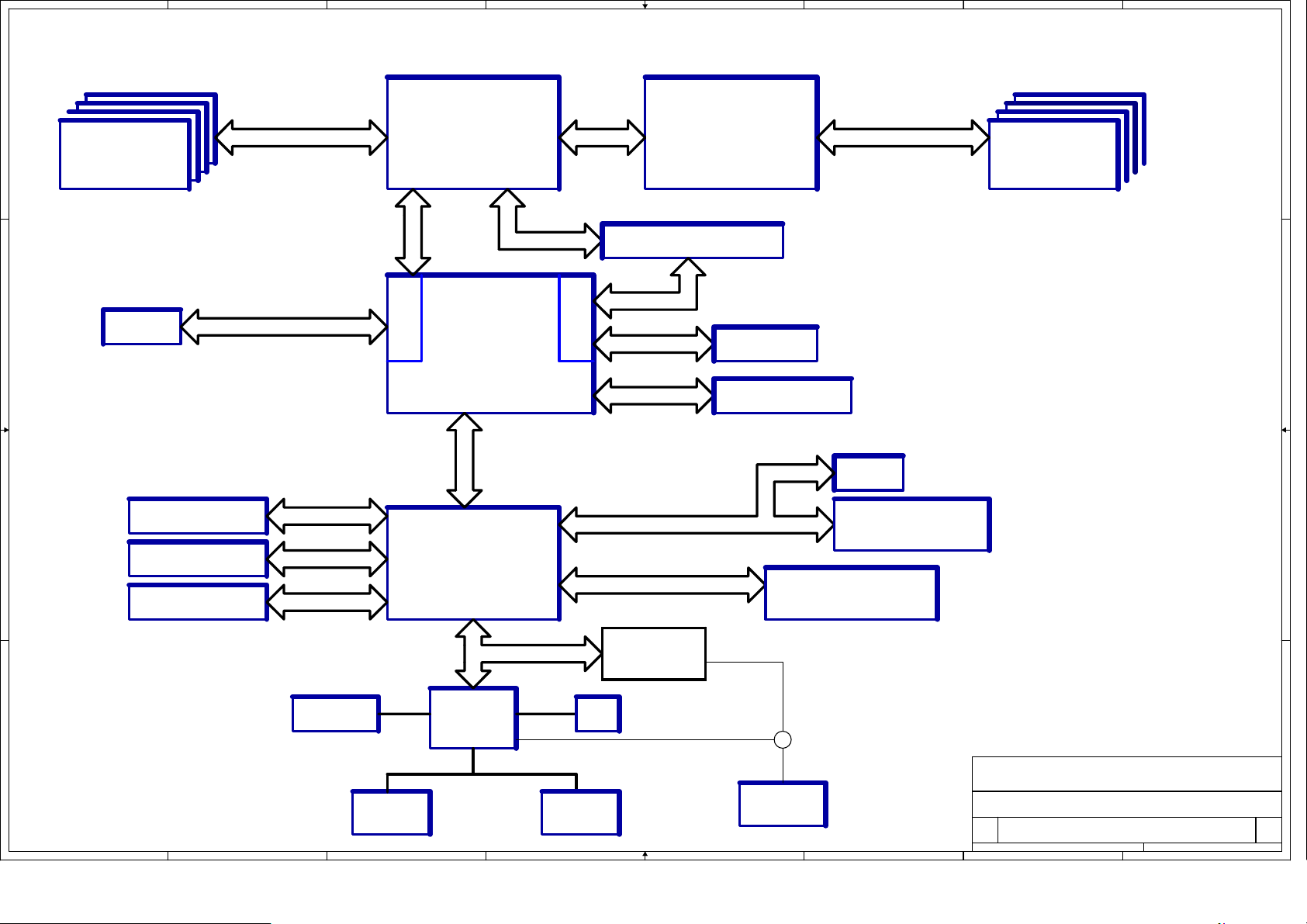

002 Block Diagram

D D

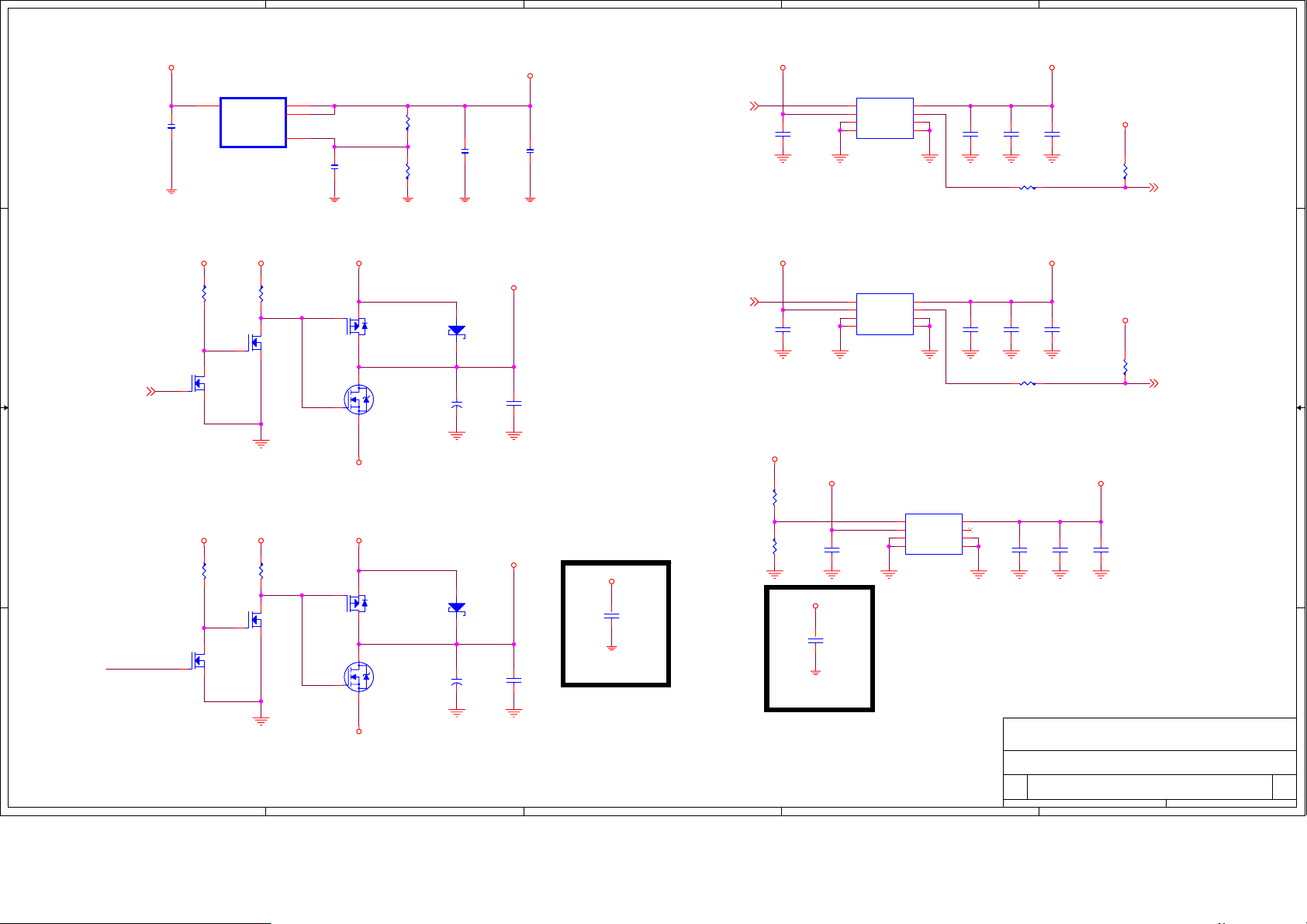

003 Main Power

004 1.2V Power

005 POWER CONNECTOR

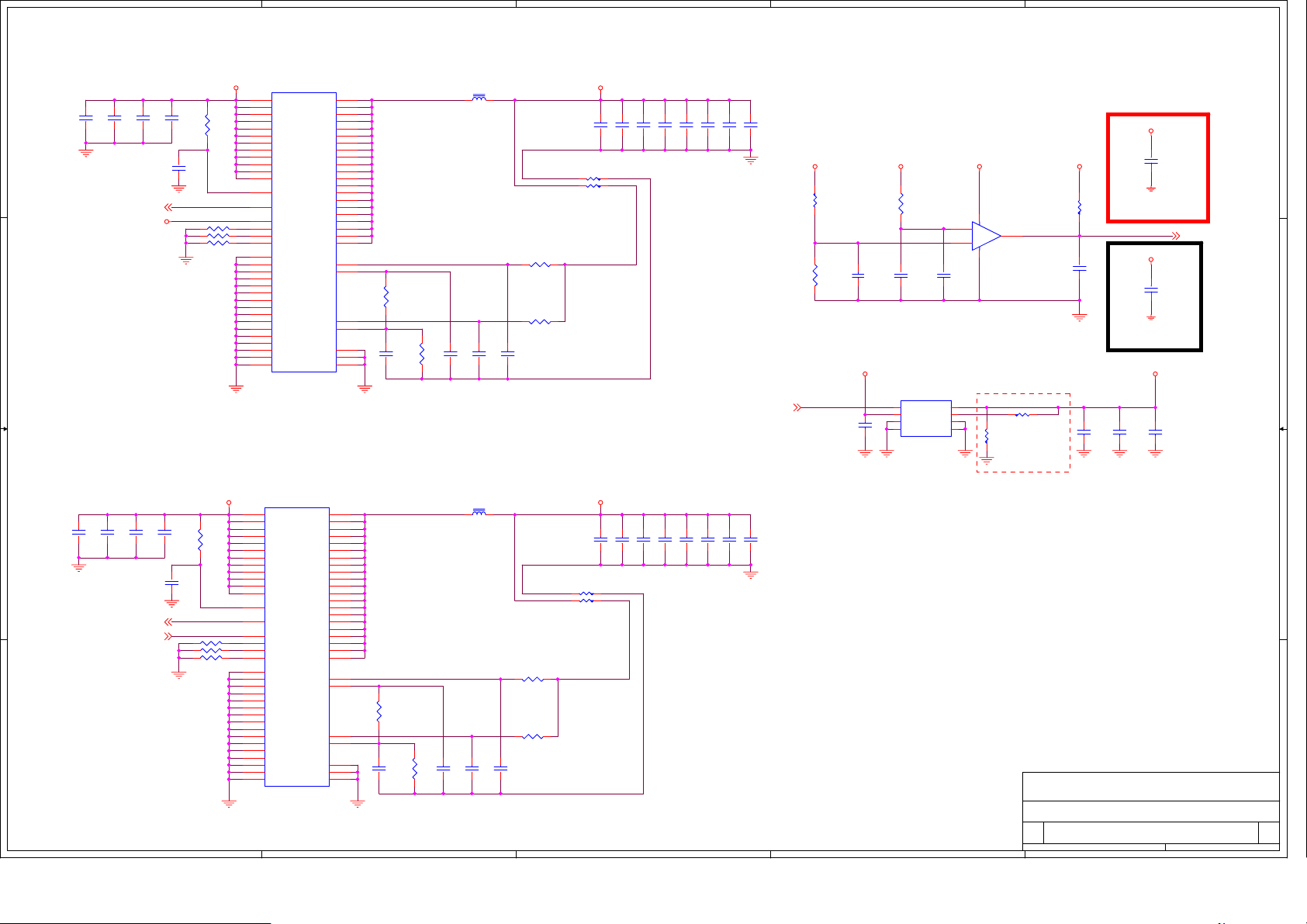

006 Clock Synthesizer

007 CPU0_VT1115M

008 CPU0_VT1135S

009 CPU3_VT1115M

010 CPU3_VT1135S

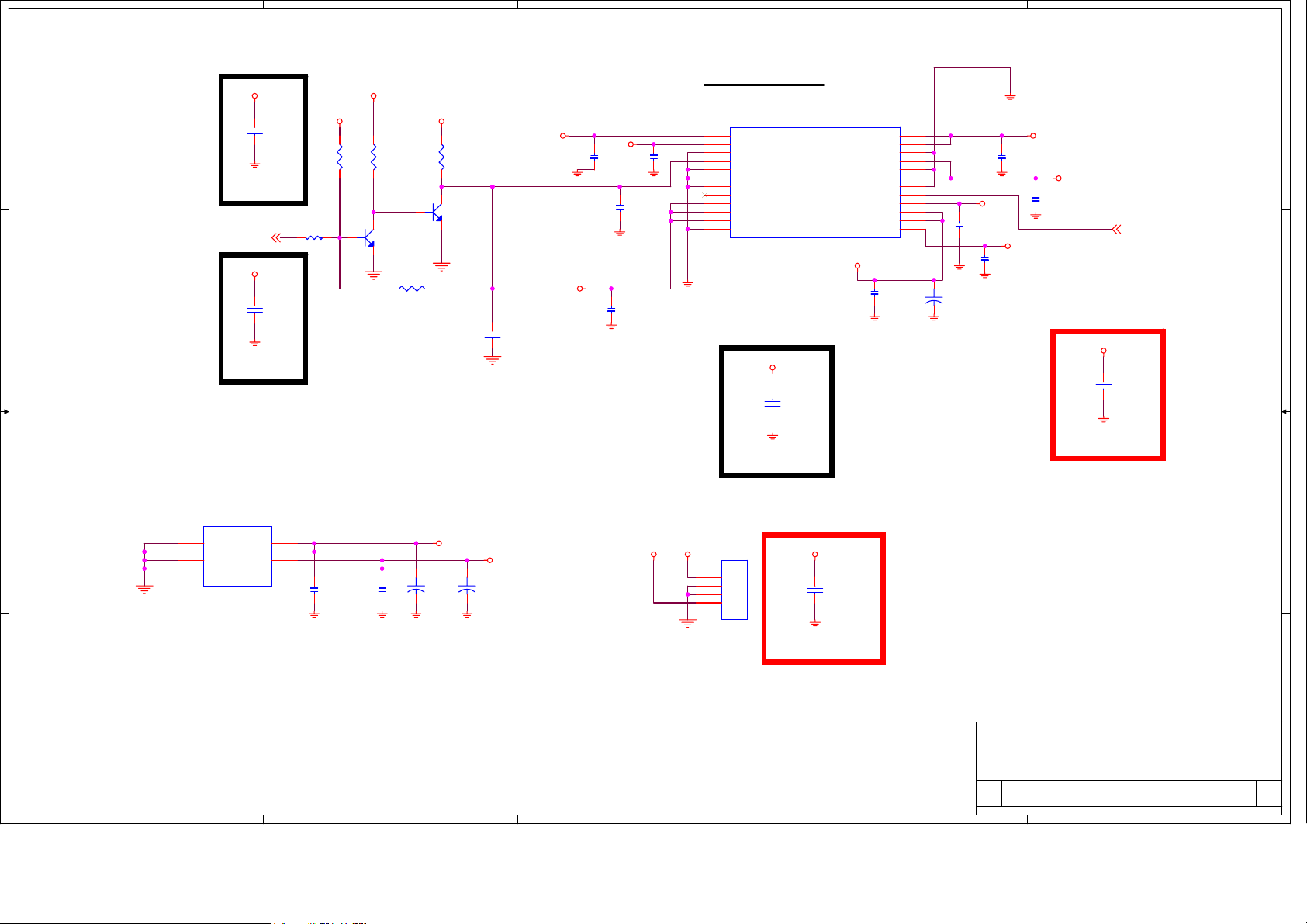

011 CPU0 DDR POWER

012 CPU3 DDR POWER

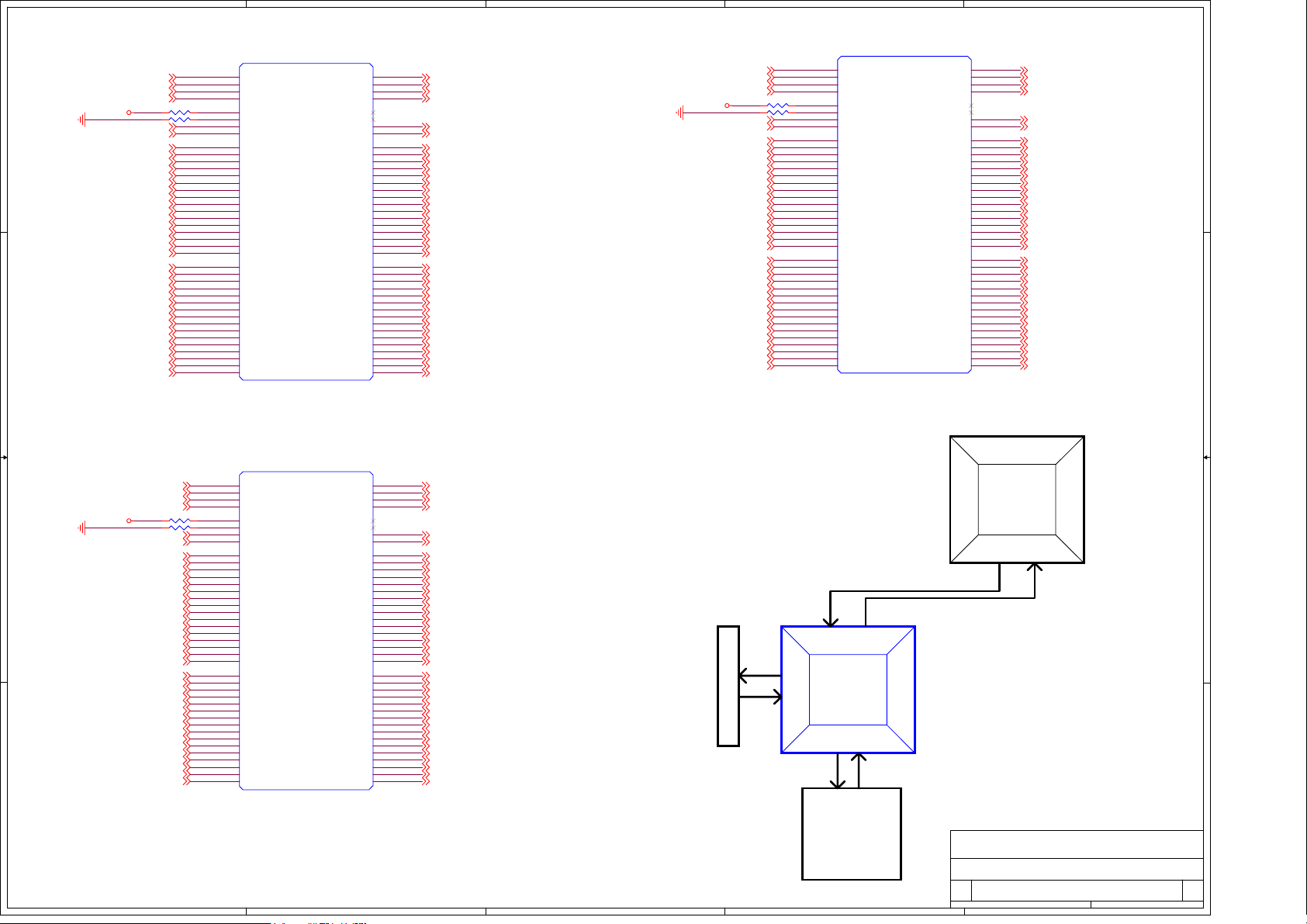

013 CPU0 HT Interface

C C

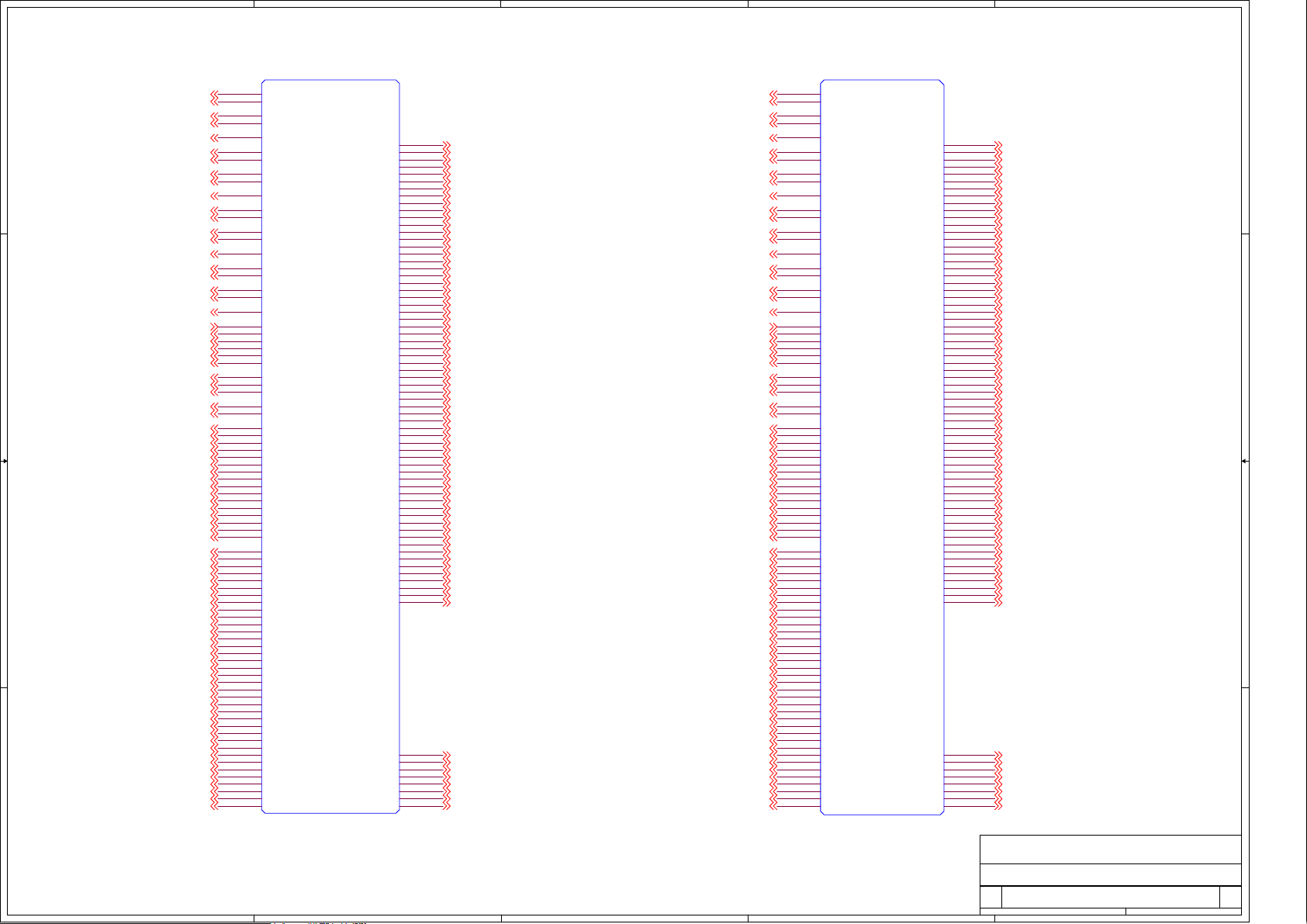

014 CPU0 Memory Interface

015 CPU0 MISC/ POWER /GND

016 DDR2 Connector A1_P0

017 DDR2 Connector A2_P0

018 DDR2 Connector A3_P0

019 DDR2 Connector A4_P0

020 DDR2 Connector B1_P0

021 DDR2 Connector B2_P0

022 DDR2 Connector B3_P0

023 DDR2 Connector B4_P0

024 DDR2 Termination/Caps_ P0

025 CPU0 Decoupling CAP

B B

026 CPU3 HT Interface

027 CPU3 Memory Interface

028 CPU3 MISC/ POWER /GND

029 DDR2 Connector A1_P3

030 DDR2 Connector A2_P3

031 DDR2 Connector A3_P3

032 DDR2 Connector A4_P3

033 DDR2 Connector B1_P3

034 DDR2 Connector B2_P3

035 DDR2 Connector B3_P3

036 DDR2 Connector B4_P3

A A

037 DDR2 Termination/Caps_ P3

MS-9185 Dual K8-DDR II System Date : 2005/11/21Revision : 0B

039 8 x PCI-E slot & HTX Slot

040 HT2K_Power&Decoupling

041 HT2K_GND

Power

CPU 0

CPU 3

CPU 0

CPU 3

CPU 0

CPU 3

042 HT2K_HT&PCI-E

043 HT2K_Dual LAN

044 HT2K_PCI-X

045 HT2K_Strapping

046 PCIX 133MHz slot

047 PCIE 8X slot

048 HT1K_Power&GND&Decoupling

049 HT1K_HT&PCI

050 HT1K_PCI-X&SATA&USB&IRQ

051 HT1K_IDE&LPC

052 VGA RADEON 7000-M 1/2

053 VGA RADEON 7000-M 2/2

054 VGA Connector&TMDS

055 PCI Slot

056 AIC-8130 SATAII Converter

057 AIC-8130 SATAII Power

058 Super IO 87417

059 BIOS&Keyboard&Mouse&Print

060 USB&IDE

061 FAN

062 HM ADT7476*2+ADT7463

063 SMBUS Isolation

064 SSI connector+SPK+RESET

065 GAL POWER SEQ.

066 OPMA Connector

067 SYSTEM Logic

068 HDT_new

069 Misc Parts

070 SO-DIMM SMBUS connection

071 HT1000 GPIO

072 SIO-PC87417 GPIO

073 Power deliver

074 Routing

075 Change history

HT 2000

HT 1000

VGA ATi

RADEON 7000-M

SATA II

此電路中只有 CPU 0 與 CPU 3 兩顆處理器

POWER DEFINITIONM

P0_VCORE, P3_VCORE

P0_VDDA_2.5

P3_VDDA_2.5

+1.2V_HT

P0_VDIMM_2.5V, P3_VDIMM_2.5V

P0_VTT_1.25V, P3_VTT_1.25V

+2.5V

+1.2V

+5VSB

+2.5VDUAL

+1.2VDUAL

LAN_2.5V

LAN_1.25V

VGA_2.5V

CPU Voltage

For CPU0

For CPU3

HT_LINK Voltage

DDR Dimm Voltage

DIMM Termination

Normal 2.5V

Normal 1.2V

Standby Voltage

Dual-Voltage+3.3VDUAL

Dual-Voltage

Dual-Voltage

Dual-Voltage (For G-LAN)

Dual-Voltage (For G-LAN)

For ATI VGA Voltage

For Battrey VoltageVBAT

038 CPU3 Decoupling CAP

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

COVER

MS-9185

1

175Monday, April 17, 2006

0BCustom

of

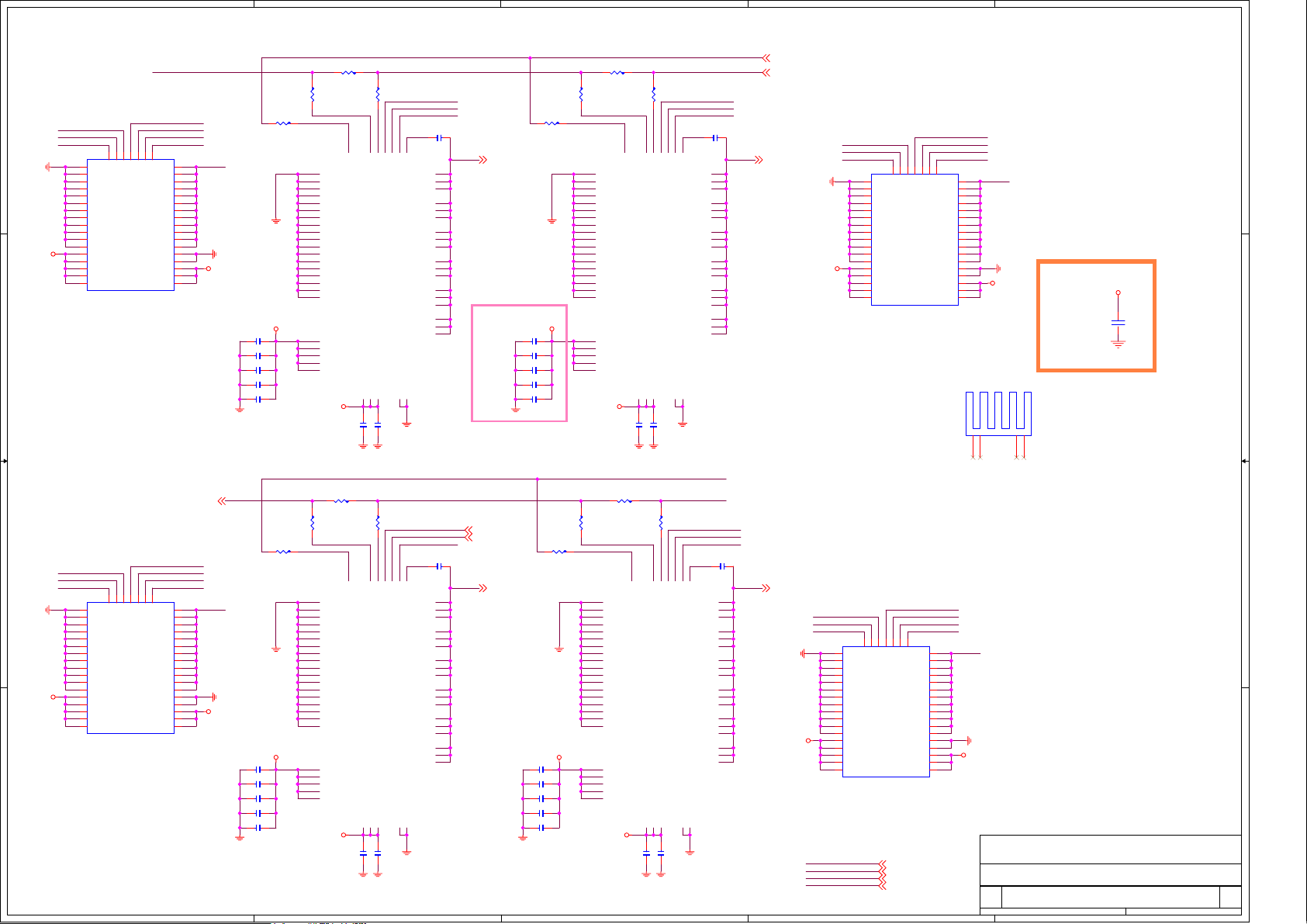

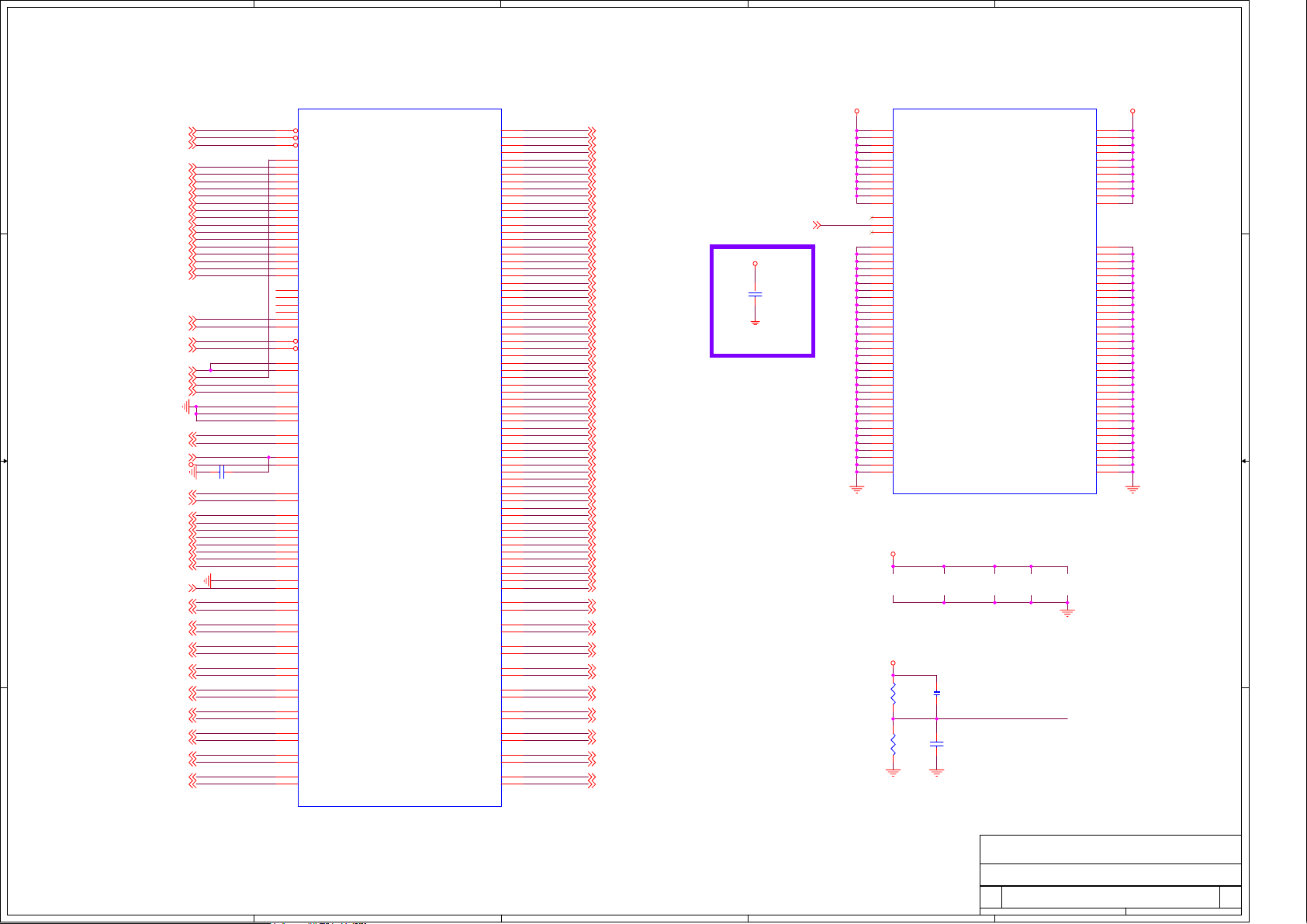

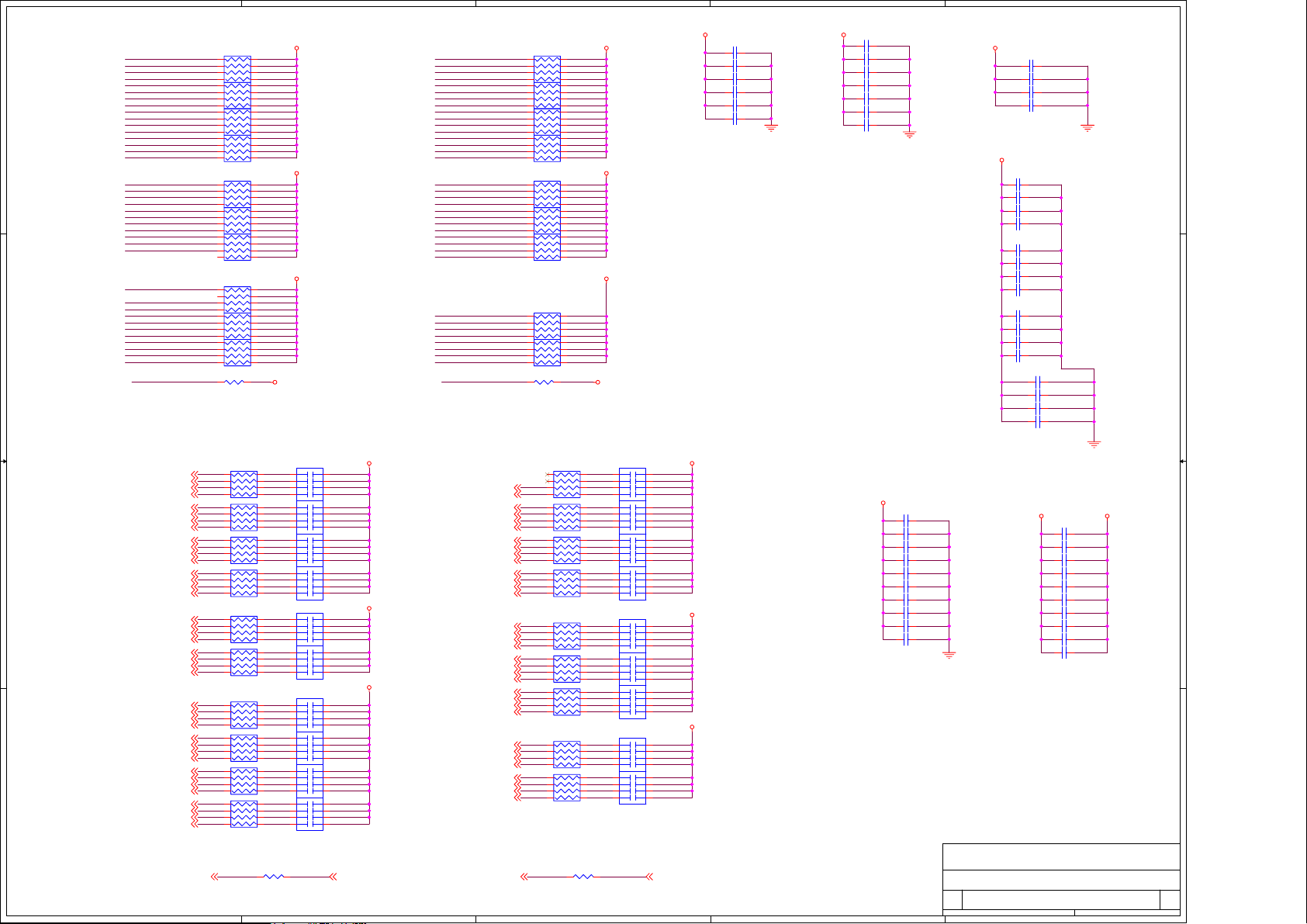

002

8

7

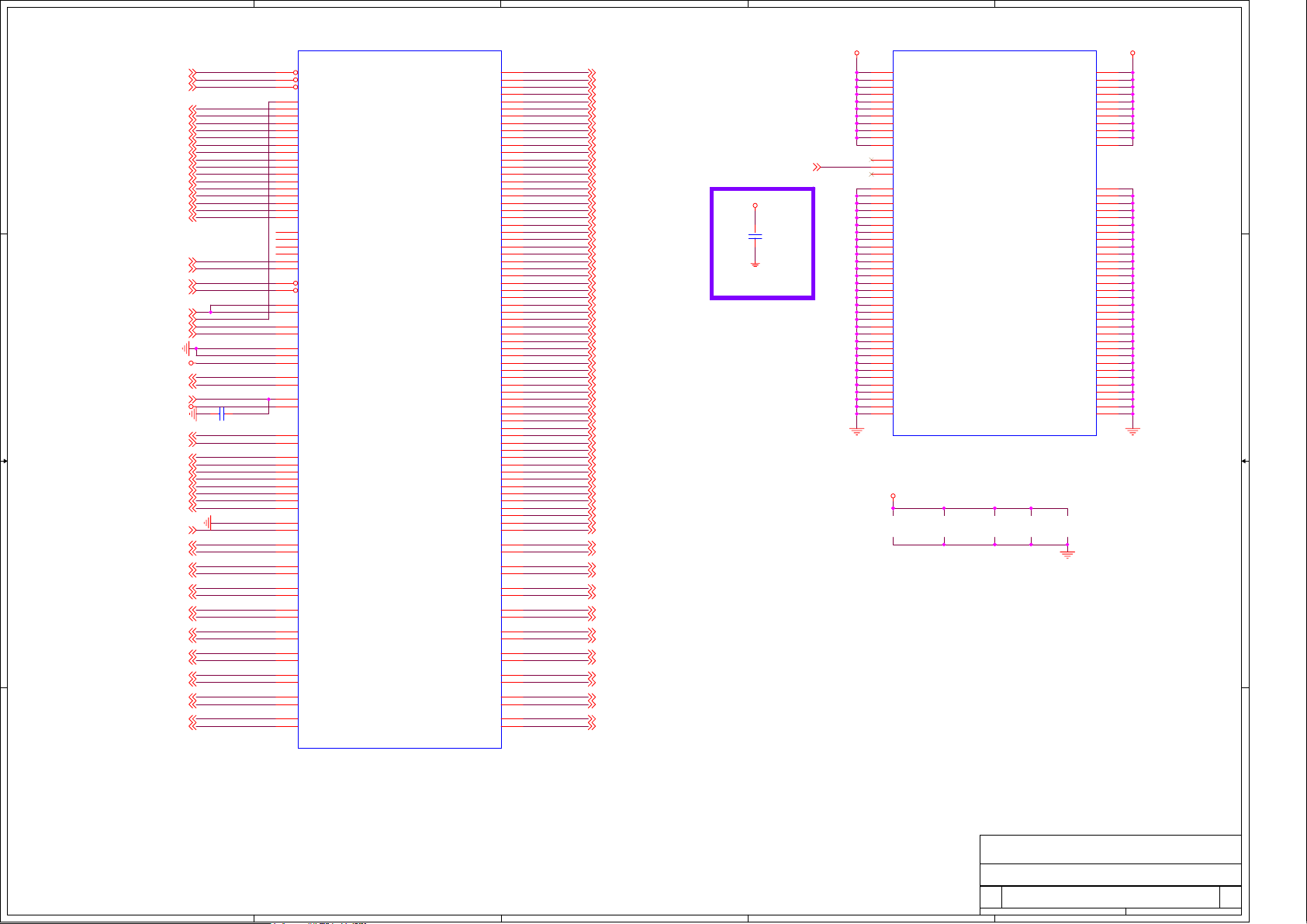

BLOCK DIAGRAM

6

5

4

3

2

1

D D

8 DDR II

128 bits / 400-667 MHz

Opteron II

L1 Processor

HT Link

Registered DIMMs

HT Link

16x16 ncHyperTransport @ 2000MT/s

16x16ncHyperTransport @ 2000MT/s

8 X PCI-E & HTX SlotHT Link

Opteron II

L1 Processor

( P3 )( P0 )

128 bits / 400-667 MHz

8 DDR II

Registered DIMMs

8 X PCI-E

Server Works

C C

B B

PCI-X Slot

Single IDE Channel

USB Port 1/2/3/4

4 x SATA Ports

PCI-X Bus 64 bit /133 MHz

EIDE ATA/100

USB 2.0

SATA

( SWC-HT2k )

PCI-X Bus

HT Link

8x8 ncHyperTransport @ 1200MT/s

Server Works

( HT-1000 )

8 X PCI-E 8 X PCI-E slot

PCI-E Bus

2 GbE ports 2 X RJ45 connectors

PCI Bus 32 bit / 33 MHz

PCI-X Bus 64 bit /133 MHz

PCI Slot

ATI RADEON-7000M

with 16 MB RAM

AIC-8130

4 x SATA II Ports

LPC

OPMA

Flash ROM

A A

LPC SIO

NS/PC87417

FDD

I2C Bus

I2C Bus

OR

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Keyboard

& Mouse

8

7

6

Serial

(COM1,2)

5

ADT7476*2

ADT7463*1

4

3

Title

Size Document Number Rev

Date: Sheet

2

Block diagram

MS-9185

275Monday, April 17, 2006

of

1

0BCustom

5

4

3

2

1

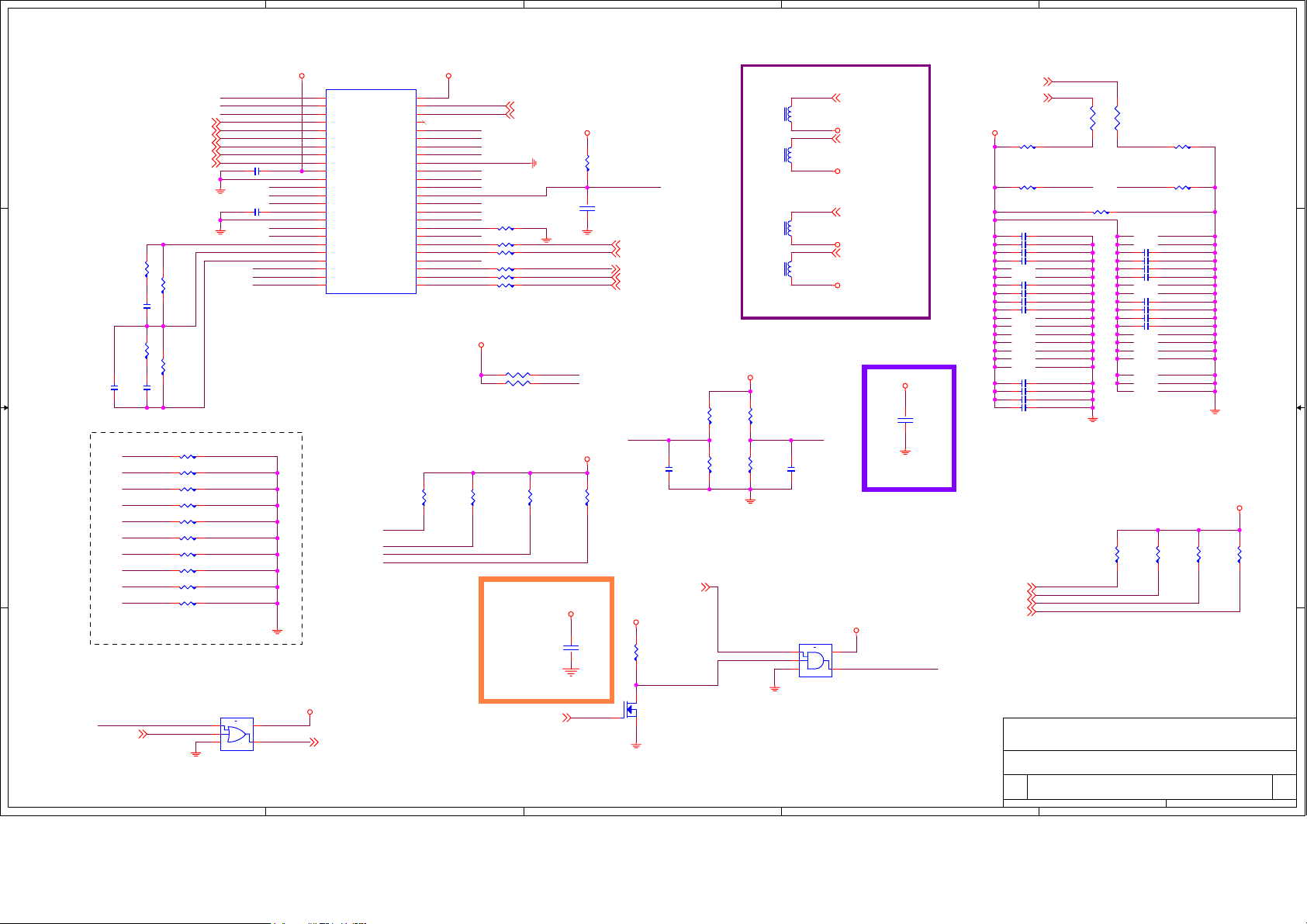

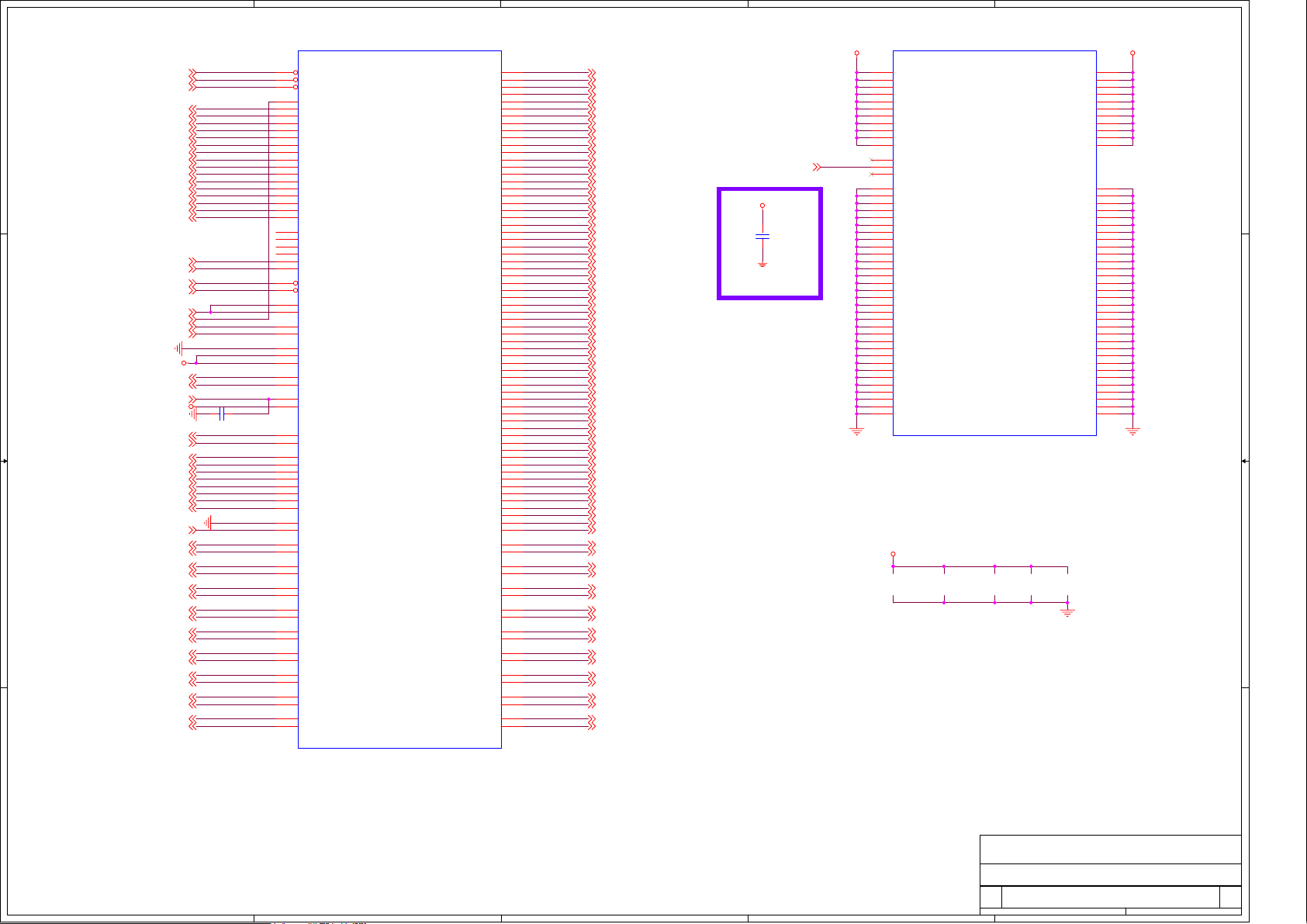

003

+5VSB

Q30

+12V +3.3VSB+5VSB

+12V +5VSB+5VSB

VOUT

ADJ

R671

4.7K

DS

Q33

2N7002

R320

4.7K

DS

Q20

2N7002

2

4

1

C435

102p_50V

Q34

P-SI2305DS_SOT23

G

D S

P-CH

DS

G

N-CH

+3.3V

Q19

P-SI2305DS_SOT23

G

D S

P-CH

DS

G

N-CH

+5V

R603

191_1%

R604

324_1%

SOT23SGD_T

SOT-23

Q36

IPD06N03LA/TO252

TO-252

SOT23SGD_T

SOT-23

Q18

IPD06N03LA/TO252

TO-252

4

AC

+

1000u_6.3V

AC

+

1000u_6.3V

D D

C C

SYS_PWRGD<65,67>

B B

SYS_PWRGD

A A

G

G

5

C421

.1u_16V

VIN3VOUT

REF.=1.25V

SOT-223

RC1117S/SOT223

FAIRCHILD/RC1117S

R670

4.7K

G

DS

Q35

2N7002

R330

4.7K

G

DS

Q21

2N7002

C432

22u_10V-1206

D23

1N5817

EC18

D18

1N5817

EC9

+3.3VSB

+3.3VDUAL

+5VDUAL

C479

1u_10V

C310

1u_10V

C426

.1u_16V

3A

8A

+5VSB

Near D18

for EMI

CI77

104P

PWRSEQ_3_EN<4,65>

PWRSEQ_6_EN<65>

3

+3.3V +2.5V

+2.5V

VR6

1

EN

2

IN

5

C466

10u_10V-1206

+3.3V +2.5VPLL

GND

6

GND

L6932D2.5_SO8

+2.5VPLL

VR4

1

EN

2

IN

5

C384

10u_10V-1206

+5VSB

R314

1K_1%_0603

R315

1K_1%_0603

+3.3VDUAL

Near VR3

for EMI

6

+3.3VDUAL

C305

10u_10V-1206

CI65

104P

GND

GND

L6932D2.5_SO8

SB : 0.08A

CPU 0/1/2/3: 0.135A

Totally 0.62A

3

OUT

4

PG

7

GND

GND

OUT

GND

GND

8

3

4

PG

7

8

C469

.1u_16V

C387

.1u_16V

+2.5VDUAL

VR3

1

EN

2

IN

5

GND

6

GND

L6932D2.5_SO8

2

OUT

GND

GND

3

4

PG

7

8

C470

.1u_16V

R660 0

C474

22u_16V-1210

+5V

R661

X_10K

PWRSEQ_3_GD <4,65>

Totally 0.21A

+2.5VDUAL

+5V

R459

10K

PWRSEQ_6_GD <65>

C386

.1u_16V

R455 0

C391

100u/1210

Totally 1.6A

C309

.1u_16V

C308

22u_16V-1210

C307

.1u_16V

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

Main Power

MS-9185

1

of

375Monday, April 17, 2006

B0Custom

5

4

3

2

1

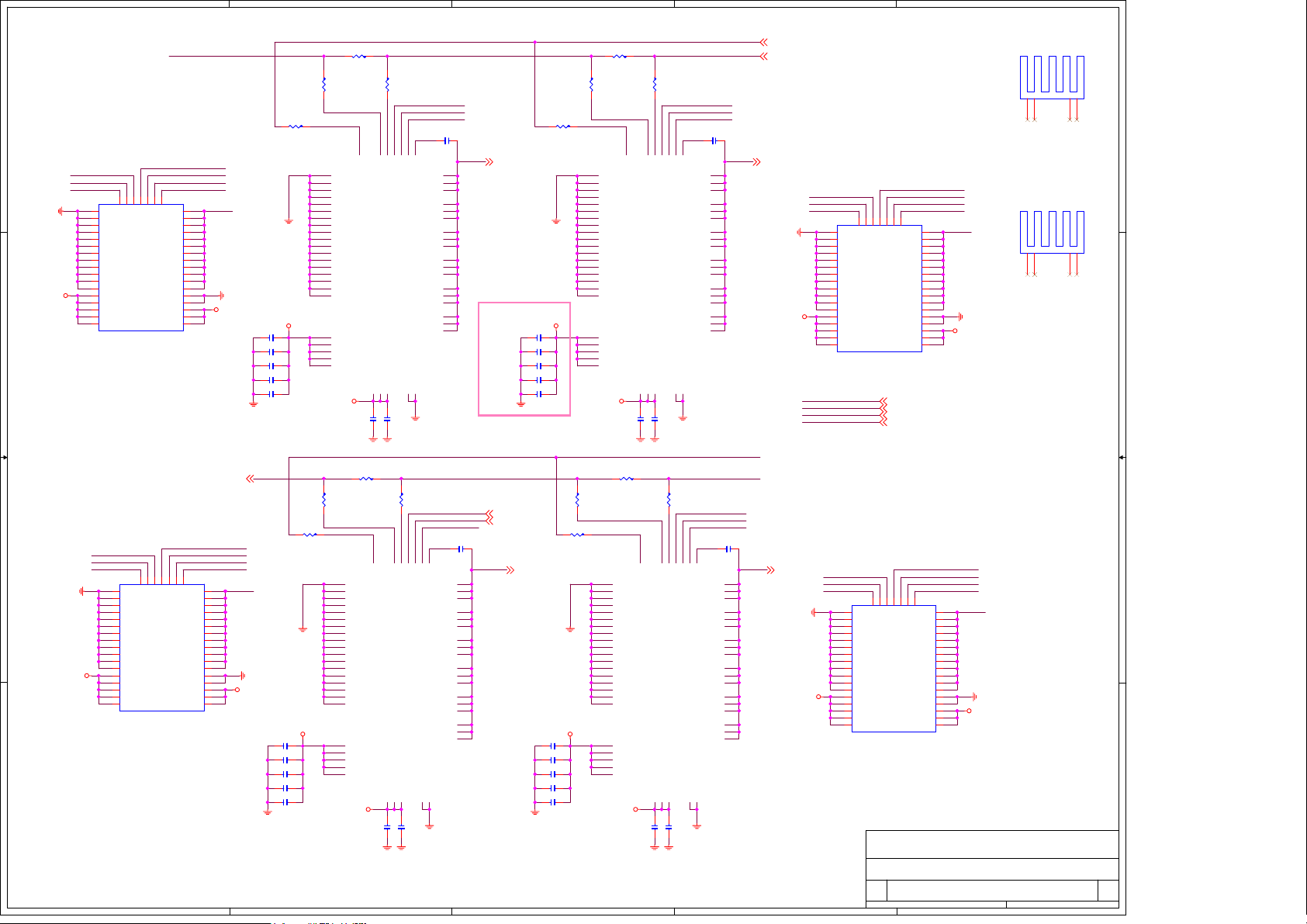

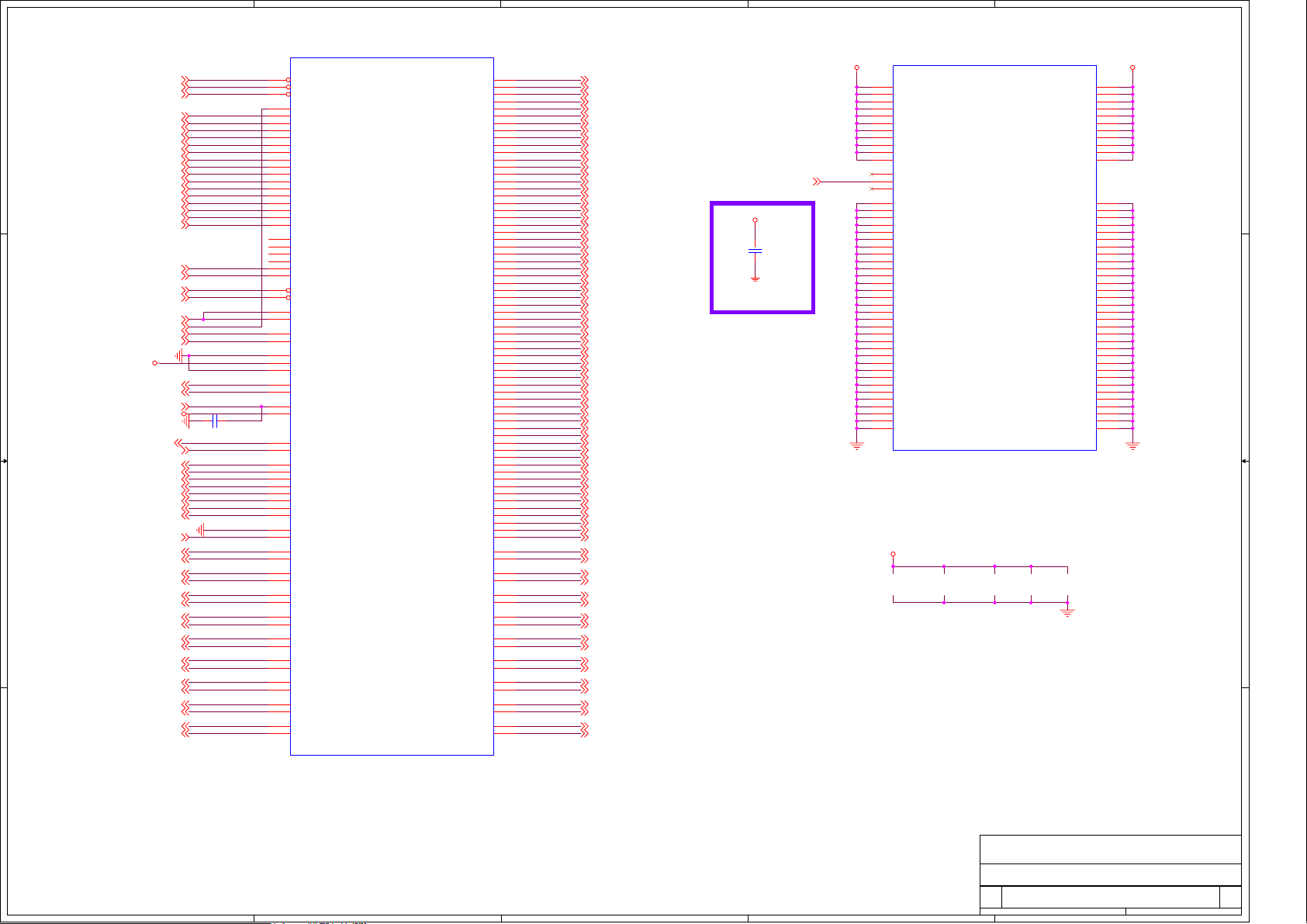

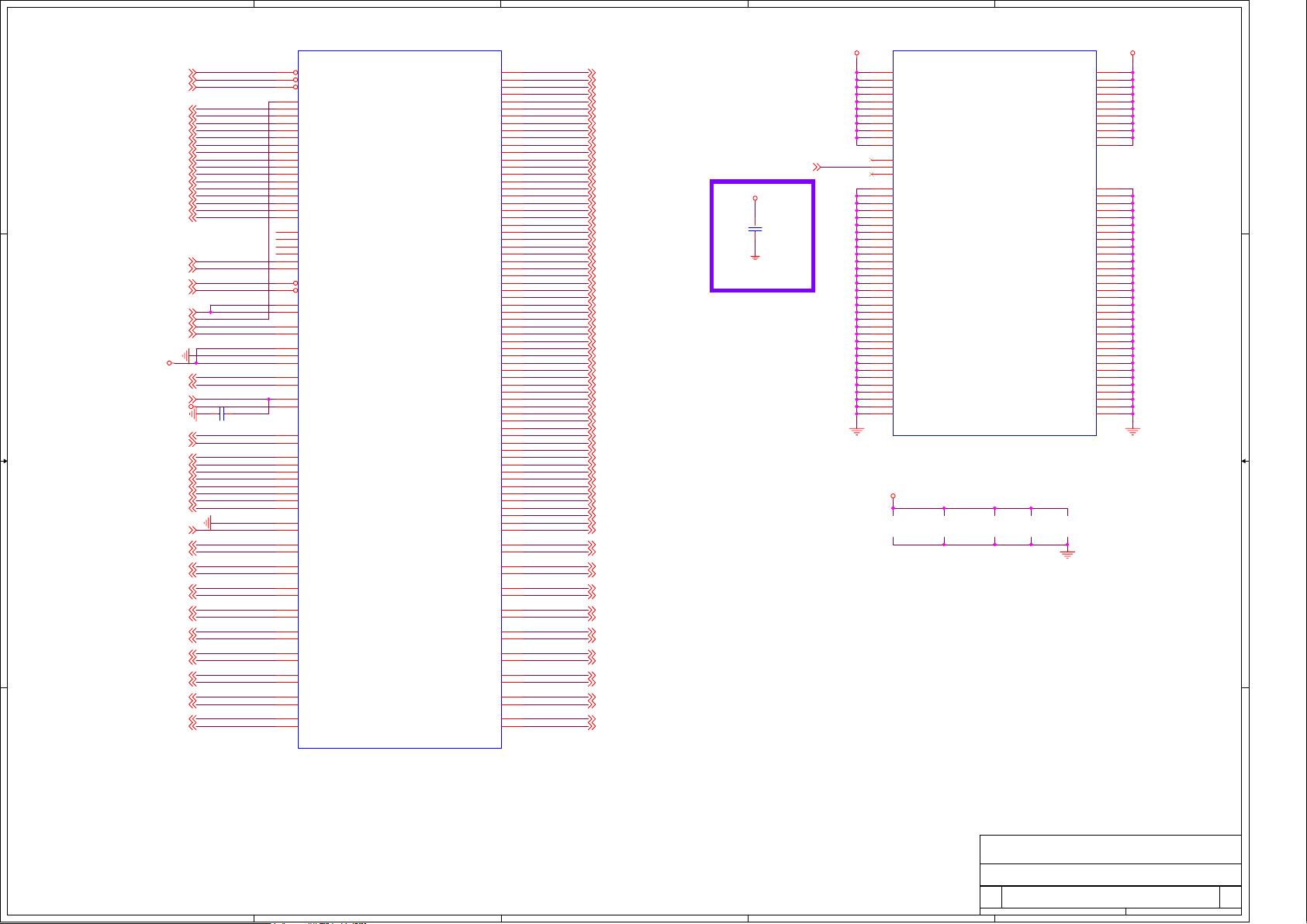

004

+1.2V_DUAL

+5VDUAL

C265

C269

D D

C C

C279

0.1u

10u

PWRSEQ_3_GD<3,65>

+3.3VDUAL

07.17 Joe, Need to fine-tune

to meet 1.2V

07.25 33K CHANGE TO 30K,

meet 1.2V spec

07.17 Joe, Need to fine-tune to meet 1.2V

07.25 63.4k CHANGE TO 42.2k ,meet 1.2V spec

10u

C275

R271

0.1u

10

C251

0.1u

R887 8.45KRST

R277 30KRST

R888 43.2KRST

U42

A1

VDD

A2

VDD

A3

VDD

C1

VDD

C2

VDD

C3

VDD

E1

VDD

E2

VDD

E3

VDD

G1

VDD

G2

VDD

G3

VDD

H1

AVDD

J1

STAT

K1

EN

K7

IMAX

K6

IRIPL

J7

BIAS

A4

GND

A5

GND

A6

GND

A7

GND

C4

GND

C5

GND

C6

GND

C7

GND

E4

GND

E5

GND

E6

GND

E7

GND

G4

GND

G5

GND

G6

GND

G7

GND

VT225

VDES

PGIN

VREF

AGND

AGND

AGND

VFB

B1

VX

B2

VX

B3

VX

B4

VX

B5

VX

B6

VX

B7

VX

D1

VX

D2

VX

D3

VX

D4

VX

D5

VX

D6

VX

D7

VX

F1

VX

F2

VX

F3

VX

F4

VX

F5

VX

F6

VX

F7

VX

K4

K3

R269

100K

K5

K2

H5

H6

H7

+1.2V_HT

+5V

U86

A1

VDD

A2

B B

A A

C625

10u

07.17 Joe, Need to fine-tune

to meet 1.2V

07.25 33K CHANGE TO 30K,

meet 1.2V spec

C627

0.1u

PWRSEQ_8_GD<65>

C624

C626

10u

PWRSEQ_8_EN<65>

5

R972

0.1u

10

C984

0.1u

PWRSEQ_8_GD

PWRSEQ_8_EN

R720 8.45KRST

R721 30KRST

R719 43.2KRST

VDD

A3

VDD

C1

VDD

C2

VDD

C3

VDD

E1

VDD

E2

VDD

E3

VDD

G1

VDD

G2

VDD

G3

VDD

H1

AVDD

J1

STAT

K1

EN

K7

IMAX

K6

IRIPL

J7

BIAS

A4

GND

A5

GND

A6

GND

A7

GND

C4

GND

C5

GND

C6

GND

C7

GND

E4

GND

E5

GND

E6

GND

E7

GND

G4

GND

G5

GND

G6

GND

G7

GND

VT225

VDES

PGIN

VREF

AGND

AGND

AGND

VFB

B1

VX

B2

VX

B3

VX

B4

VX

B5

VX

B6

VX

B7

VX

D1

VX

D2

VX

D3

VX

D4

VX

D5

VX

D6

VX

D7

VX

F1

VX

F2

VX

F3

VX

F4

VX

F5

VX

F6

VX

F7

VX

K4

K3

R973

100K

K5

K2

H5

H6

H7

Totally 10.4A

R273 0

R266 0

1.2VDUAL_SENSE+

1.2VDUAL_SENSE-

R704 0

R705 0

1.2V_HT_SENSE+

1.2V_HT_SENSE-

+1.2VDUAL

C281

22u

+1.2V_HT

C578

22u

V1P2_DUAL

1.2VDUAL_VDES

C250

100p

SB : 0.6A

CPU 0: 2A

CPU 1/2/3: 1A

HTX: 1A

SAS:1.55A

Totally 8.15A

V1P2_HT

1.2V_HT_VDES

C981

100p

07.17 Joe, Need to fine-tune to meet 1.2V

07.25 63.4k CHANGE TO 42.2k ,meet 1.2V spec

4

R270

42.2K

R974

42.2K

CHOK1 200nH

C249

C247

1000p

0.01u

CHOK5 200nH

C601

C980

0.01u

1000p

R268 220

R267 10K

C248

220p

R739 220

R724 10K

C606

220p

C276

22u

C570

22u

C263

C255

C258

C287

22u

C553

22u

22u

C559

22u

C293

22u

C569

22u

PWRSEQ_3_EN<3,65>

22u

+2.5VDUAL +1.2V +5VSB

R693

11.8K_1%

R692

4.7K

(1.087V)

R694

C519

C520

X_102p

NOPOP

.1u_16V

9.09K_1%

C518

1u_10V

+5V

3

+

2

-

U79A

NS-LM358MX/SOIC8

4 8

+1.2V

PWRSEQ_3_EN

10u_10V-1206

C577

22u

C436

VR5

1

EN

IN2ADJ

5

GND

6

GND

L6932D1.2_SO8

OUT

GND

GND

4

3

7

8

R620 1K_1%_0603

R624

60.4K_1%

+5V

CI19

104P

R703

Near U3

for EMI

10K

1

PWRSEQ_3_GD

C531

1u_10V

Near U79

for EMI

+5VSB

+1.2V+3.3V

CI75

104P

PWRSEQ_3_GD <3,65>

SB:1.7A

C444

.1u_16V

C441

22u_16V-1210

C445

.1u_16V

C267

22u

C560

22u

22u

C554

22u

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

3

2

Date: Sheet

1.2V Power

MS-9185

1

0BCustom

of

475Monday, April 17, 2006

005

5

4

3

2

1

+5V

D D

CI80

104P

Near R557

for EMI

+5V

CI81

104P

R478 33

TO_PS_PWRONJ<65>

C C

+5VSB

+3.3VDUAL +5VSB

R483

4.7K

R532

X_10K

NOPOP NOPOP

Q26

B

X_2N3904

NOPOP

E C

R490 0

Q29

X_2N3904

B

NOPOP

E C

R557

X_10K

C418

X_.1u_16V

+3.3V

0.1u 0402

+5V

C363

C419

102P

-12V

C364

0.1u 0402

C420

102P

Near R478

for EMI

SSI Connector

13

3.3V

14

-12V

15

GND4

16

PS_ON

17

GND5

18

GND6

19

GND7

20

3VSBY

21

5V

22

5V

23

5V

24

GND8

POWERCONN2X12

12VP3_IN

CI61

104P

JPWR2

12VP3_IN

3.3V

3.3V

GND1

GND2

+5V

GND3

PWROK

5VSBY

12V

12V

3.3V

5V

C382

0.1u 0402

1

2

3

4

5

6

7

ATXPWOK

8

9

10

11

12

+

EC12

1000u/16V

+5VSB

C389

0.1u 0402

C433

0.1u 0402

+3.3V

C427

0.1u 0402

+3.3V

C411

0.1u 0402

+5V

ATX_PWR_OK <67>

+3.3VDUAL

CI9

104P

Near C76

Near EC12

for EMI

for EMI

B B

JPWR3

1

GND

2

GND

3

GND

GND4+12V

POWERCONN2X4

+12V

+12V

+12V

8

7

6

5

C635

X_103P

C673

X_103P

EC20

+

1000u/16V

12VP0_IN

EC23

+

1000u/16V

+12V

+12V+5V

4

3

2

1

HTX Aux power

JPWR1

12V

GND

GND

5V

D1x4

+5V

CI6

104P

Near JPWR4

for EMI

(Close to HTX Slot)

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

POWER CONNECTOR

MS-9185

575Monday, April 17, 2006

1

0BB

of

006

5

4

3

2

1

Note:ICS Requirement:

CL= 18pF = Ext. 30pF

.1u_16V

C375

R83 2.2

R84 2.2

R479 2.2

SMB_2_CLK

SMB_2_DATA

C857

.047u_16V_X7R

R38 4.7K

R40 4.7K

R37 4.7K

R36 4.7K

CL= 20pF = Ext. 33pF

14MHZ_XTAL_X1

14MHZ_XTAL_X2

SMB_2_CLK<58,62,63>

SMB_2_DATA<58,62,63>

C870

C872

BOT/.047u_16V_X7R

BOT/.047u_16V_X7R

C874

C869

C871

BOT/.1u_16V

SRCCLK_P_100MHz

SRCCLK_N_100MHz

C43

0.1u_16V

C29

0.1u_16V

BOT/.047u_16V_X7R

R476 2.2

BOT/.047u_16V_X7R

C873

U6

2

CLK_IN

3

CLK_IN#

13

SCLK

14

SDATA

12

BYPASS#/PLL

17

PLL_BW

15

PD#

16

SRC_STOP#

28

VDDA

27

GNDA

24

VDD5

18

VDD4

11

VDD3

5

VDD2

1

VDD1

4

GND1

25

GND2

ICS9DB104BF

SMB_2_CLK

SMB_2_DATA

SYN_PD_L

SYN_SPREAD_EN

R477 475_1%

C858

.047u_16V_X7R

BOT/.047u_16V_X7R

C393

.047u_16V_X7R

SYN_IREF

SYN_VCC3

SYN_VDD_PLL

C394

BOT/.047u_16V_X7R

SYN_AVDD

DIF_3

DIF_3#

DIF_2

DIF_2#

DIF_1

DIF_1#

DIF_0

DIF_0#

OE_0

OE_2

IREF

XTALI

XTALO

SCLK

SDATA

PD_L

SPREAD_EN

IREF

VDD66

VDDPCI

VDDREF

GNDP66

GNDPCI

GNDREF

VDD48

VDDSRC

VDDCPU1

VDDCPU2

VDDCPU3

GND48

GNDSRC

GNDCPU1

GNDCPU2

GNDCPU3

VDDA

GNDA

ICS932S801AG

R56 1K

R58 1K

U58

TSSOP48

R54 33

R45 33

R69 33

R64 33

R49 33

R41 33

R66 33

R59 33

+3.3V

1

2

7

8

21

29

24

9

15

48

14

20

44

3

27

33

37

41

6

28

32

36

40

22

23

20

19

23

22

9

10

6

7

8

21

R81 475_1%

26

pls double check it

HCLK0_P

HCLK0_L

HCLK1_P

HCLK1_L

HCLK2_P

HCLK2_L

HCLK3_P

HCLK3_L

SRCCLK_P

SCRCLK_L

PCICLK0_F0

PCICLK1

PCICLK2

PCICLK3

P66CLK0

P66CLK1

P66CLK2

P66CLK3

FS0_REF0

FS1_REF1

48MHz_0

48MHz_1

CG_CLKP

43

CG_CLKN

42

39

38

35

34

31

30

SRCCLKRP

26

SRCCLKRN

25

PCICLK0

16

PCICLK1

17

PCICLK2

18

PCICLK3

19

NB SUGGEST

P66CLK0

10

HTXCLK

11

12

13

FS0_REF0

47

FS0_REF1

46

FS0_REF2

45

FS2

48MHz_CLK0

4

48MHz_CLK1

5

SB SUGGEST

Address:OxD2

R6749.9_1%

R5049.9_1%

R4249.9_1%

R6049.9_1%

R456 33

R460 33

R448 33

R440 91

R443 91

R424 33

R422 33

R426 47

R6849.9_1%

R6349.9_1%

R434 0

R439 0

R433 49.9_1%

R438 49.9_1%

R442 62

SB_14MHz_CLK

PCIEB_NB_CLKP

PCIEB_NB_CLKN

PCIEC_NB_CLKP

PCIEC_NB_CLKN

PCIEB_SL1_CLKP

PCIEB_SL1_CLKN

PCIEC_SL2_CLKP

PCIEC_SL2_CLKN

R5349.9_1%

R4449.9_1%

BF_CLKP

BF_CLKN

R441

15_1%

SRCCLK_P_100MHz

SRCCLK_N_100MHz

R461 49.9_1%

R457 49.9_1%

HTX_REFCLK <39>

220

R432

SB_REFCLK_IN

C385 X_10P/16V/NPO

GC_REFCLK_IN

C383 X_10P/16V/NPO

C381 X_10P/16V/NPO

C379

10P/50V/NPO

PCIEB_NB_CLKP <42>

PCIEB_NB_CLKN <42>

PCIEC_NB_CLKP <42>

PCIEC_NB_CLKN <42>

PCIEB_SL1_CLKP <39>

PCIEB_SL1_CLKN <39>

PCIEC_SL2_CLKP <46>

PCIEC_SL2_CLKN <46>

C380

10P/50V/NPO

+3.3V

L12

80_3A-0805

P3_CPUCLKIN

P3_CPUCLKINJ

SB_CLK_P

SB_CLK_L

C414

10u_6.3V

SB_REFCLK_IN <51>

GC_REFCLK_IN <44>

SB_14MHz_CLK <51>

SIO_CLK_48MHz <58>

USB_CLK_48MHz <50>

D D

C C

+3.3V

+3.3V

14.318MHz

Y4

C376

33p_50V_NPO

14_318MHz

300 ohm/700mA/0805

L41

300 ohm/700mA/0805

L11

C377

33p_50V_NPO

C865

10u_6.3V_0805

C395

10u_6.3V_0805

add smbus address

L8

80_3A-0805

10u_6.3V

+3.3V

C57

B B

pls double check it

+3.3V

BF_CLKP

BF_CLKN

+3.3V

R586 2.2

R546 2.2

C422

0.1u_16V

R508 49.9_1%

R509 49.9_1%

R510 49.9_1%

R511 49.9_1%

R587 1K

R588 1K

U70

2

CLK

3

nCLK

5

PCLK

6

nPCLK

4

CLK_SEL

8

CLK_EN

1

VCC

9

VCCO

16

VCCO

17

VCCO

24

VCCO

25

VCCO

32

VCCO

C417

0.1u_16V

7

VEE

ICS853031

SRCCLK_P_100MHz SRCCLK_N_100MHz

R496

15_1%

R497

15_1%

GC_CLK_P

GC_CLK_L

HTX_CLK_P

HTX_CLK_L

CI11

Near U7

for EMI

31

Q0

30

nQ0

29

Q1

28

nQ1

27

Q2

26

nQ2

23

Q3

22

nQ3

21

Q4

20

nQ4

19

Q5

18

nQ5

15

Q6

14

nQ6

13

Q7

12

nQ7

11

Q8

10

nQ8

10P_50V

R512 49.9_1%

R513 49.9_1%

R550 49.9_1%

R551 49.9_1%

R575 0

R570 0

R525 0

R526 0

HCLKP0

HCLKN0

HCLKP1

HCLKN1

HTXCLKP0

HTXCLKN0

R527 0

R528 0

R529 0

R530 0

R565 0

R566 0

R498

15_1%

R552

15_1%

P0_CPUCLKIN <15>

P0_CPUCLKINJ <15>

P3_CPUCLKIN <28>

P3_CPUCLKINJ <28>

SB_CLK_P <49>

SB_CLK_L <49>

GC_CLK_P <42>

GC_CLK_L <42>

HTX_CLK_P <39>

HTX_CLK_L <39>

CI13

10P_50V

Near U7

for EMI

Address:OxDC

FS2 FS1 FS0 CPU HTT PCI

MHz MHz MHz

0 0 0 Hi-Z Hi-Z Hi-Z

0 0 1 X X/3 X/6

0 1 0 180.0 60.2 30.0

A A

0 1 1 220.0 36.5 73.12

1 0 0 100.0 66.6 33.3

1 0 1 133.3 66.6 33.3

1 1 0 166.6 66.6 33.3

1 1 1 200.0 66.6 33.3

5

SYN_PD_L

SMB_2_CLK

SMB_2_DATA

SYN_SPREAD_EN

FS0_REF2

FS0_REF1

FS0_REF0

R463 4.7K

R431 X_4.7K

R435 X_4.7K

R451 10K

R427 10K

R425 10K

R423 10K

+3.3V

+3.3V

EMI

+3.3V

C396

X_.1u_16V

4

P0_CPUCLKIN

P0_CPUCLKINJ

R574 49.9_1%

R569 49.9_1%

3

R579

15_1%

PCICLK3

PCICLK2

PCICLK1

R450 33

R453 33

R458 33

C388 X_10P/16V/NPO

C390 X_10P/16V/NPO

C392 X_10P/16V/NPO

PCI_IRQ_CLK0 <50>

PCI_IRQ_CLK1 <50>

OPMA_PCI_CLK <66>

2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

Clock Synthesizer

MS-9185

1

675Monday, April 17, 2006

of

0BCustom

5

4

3

2

1

007

PWRSEQ_7_EN<9,65>

D D

R803

249RST

C C

B B

A A

C660

680P

R839

845RST

C661

C655

X_103P

0.12uF

R_SEL7

R_SEL6

R_SEL5

R_SEL4

R_SEL3

R_SEL2

R_SEL1

R_SEL0

R_FREQ

R_REF

Configuration Resistors,Rref

P0_VID5<15,62>

P0_VID4<15,62>

P0_VID3<15,62>

P0_VID2<15,62>

P0_VID1<15,62>

P0_VID0<15,62>

R819

499RST

R800

2.49K

R783 5.9KST-0402

R756 1.02K_0402

R740 340RST

R755 3.74KR1%-LF

R757 8.66KST-0402 R971

R735 11.3K

R759 5.11K-0402

R749 340RST

R758 26.1K-0402

R741 11KST-0402

VID7

VID6

VID5

VID4

VID3

VID2

VID1

VID0

+3.3V +3.3V

U92

1

OE

2

VID<7>

3

VID<6>

4

VID<5>

5

VID<4>

6

VID<3>

7

VID<2>

8

VID<1>

9

4.7uC615

OVP+

OVPOVP_OUT R_FREQ

6800PC664

SENSE+

SENSE-

VR_HOT

VR_FAN

FAULTB

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

VID<0>

VDD

GND

OVP+

OVPOVP_out

Vnom+

Vnomsense+

senseVamp_out1

Vamp_in

Vamp_out2

Vr_Hot

Vr_Fan

FaultB

VT1115M

EXT_REF

R_sel<7>

R_sel<6>

R_sel<5>

R_sel<4>

R_sel<3>

R_sel<2>

Load_Current

R_sel<1>

R_sel<0>

VDD

GND

R_ref

Pwrgd

R_freq

Vin_ov

Vin_uv

Ides_n

Ides_p

DBO

DBI

sphase

36

47

SC

46

SD

45

44

43

42

41

40

39

38

37

48

35

34

33

32

31

30

29

28

27

26

25

R_SEL0 =340ohm

SMBUS = E0h

+3.3V

R801 4.7K

R802 4.7K

VID7

VID6

MASTER

Reported Faults

R789

10K-0402

FAULTB

OVP_OUT

VR_FAN

VR_HOT

SMB_6_CLK <9,11,12,63>

R_SEL7

R_SEL6

R_SEL5

R_SEL4

R_REF

R_SEL3

R_SEL2

VIN_OV

VIN_UV

R_SEL1

R_SEL0

SMB_6_DATA <9,11,12,63>

R748 10K_0603

R779 0_0402

R775 0_0402

R765 0_0402

R768 0_0402

R769 0_0402

VIN_OV VIN_UV

R742

C617

10.7KST

0.1uF

R808

10K-0402

R736

100K

10K-0402

R795

+5V

R794

10K_0603

C630

1u_10V

IDES_N

IDES_P

DBI

DBO

SPHASE

12VP0_IN

CPU0POWER_GD <9>

IDES_N <8>

IDES_P <8>

DBI <8>

DBO <8>

SPHASE <8>

R737

63.4k 1%

R743

10K

+3.3V

R786

10K-0402

C618

0.1uF

L27

INDUCTOR_4_PHASE_8pin

Slave

Faults

Slave1_FAULTB<8>

Slave2_FAULTB<8>

Slave3_FAULTB<8>

Slave4_FAULTB<8>

1

50nH

2

3

50nH

4

5

50nH50nH

6

7

8

VX1 <8>

P0_VCORE

VX2 <8>

P0_VCORE

VX3 <8>

P0_VCORE

VX4 <8>

P0_VCORE

10K-0402

Slave1_FAULTB

Slave2_FAULTB

Slave3_FAULTB

Slave4_FAULTB

P0_VCORE_FB_N<15>

P0_VCORE_FB_P<15>

P0_VCORE

R746

56_0603

R820

0

R805

0

SENSE+

OVP+

R852 100/1206

47u_6.3V_1206C594

47u_6.3V_1206C644

47u_6.3V_1206C480

47u_6.3V_1206C516

47u_6.3V_1206C665

47u_6.3V_1206C501

47u_6.3V_1206C562

22u_6.3V_1206C616

22u_6.3V_1206C580

22u_6.3V_1206C1009

22u_6.3V_1206C951

R806

0

SENSE-

OVP-

47u_6.3V_1206C536

47u_6.3V_1206C51147u_6.3V_1206C652

47u_6.3V_1206C475

47u_6.3V_1206C526

47u_6.3V_1206C484

47u_6.3V_1206C587

47u_6.3V_1206C605

47u_6.3V_1206C631

R747

56_0603

R821

0

10/4 Joe, 47uF x4 pcs per phase by Voltera recommend

R964

R966

10K-0402

10K-0402

+3.3V

R982

10K-0402

+3.3V

CI16

104P

Near U10

for EMI

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

CPU0_VT1115M

Size Document Number Rev

MS-9185

5

4

3

2

Date: Sheet

1

of

775Monday, April 17, 2006

0BCustom

5

4

3

2

1

008

SPHASE

R711

0

VX1_DBI

C561

1u

R752

0

VX3_DBI

C619

1u

DBI

IDES_P

IDES_N

C0_BST1

SPHASE

DB3

IDES_N

Slave3_FAULTB

C0_BST3

1uC579

DB3

H1

H2

DBO

SPHASE

G2

DBI

D1

C2

IDESP

IDES_P

IDES_N

Slave2_FAULTB

C0_BST2

B1

A3

VX

BST

VX

IDESN

VX

FAULTB

VX

VX

VX

VX

VX

VX

VX

VX

VX

GND

GND

VDD

VDD

VCC

VT1135S

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

B2

A2

VX2

+3.3V

1u

1u

1u

10u_16V_1206

10u_16V_1206

D D

12VP0_IN

C C

C0_DBI2

VX2_DBO

SPHASE0_VT2

U84

A5

VSS

A7

VSS

B5

VSS

B7

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

R717

1KST

12VP0_IN 12VP0_IN

C609

C608

C607

C592

C593

R965 X_0

R715

0

VX2_DBO

SPHASE0_VT2

+3.3V +3.3V

C589

R716

IDES_P

0

IDES_N

Slave2_FAULTB

C0_DBI2

C590

1u

1u

C0_BST2

1uC600

VX2

VX2 <7>

C583

1u

C584

1u

C585

1u

C572

10u_16V_1206

C573

10u_16V_1206

R709

1KST

R706 X_0

R710

0

C0_DBO1 Slave1_FAULTB

SPHASE0_VT1

C563

1u

Input Cap. totally 1u/0603x3, 10u/16Vx2 each phase

DBO<7>

R799

1KST

12VP0_IN

H1

H2

DBO

SPHASE

G2

DBI

D1

5

C2

IDESP

IDES_P

IDES_N

Slave4_FAULTB

C0_BST4

B1

A3

VX

BST

VX

IDESN

VX

FAULTB

VX

VX

VX

VX

VX

VX

VX

VX

VX

GND

GND

VDD

VDD

VCC

VT1135S

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

B2

A2

VX4

+3.3V

C641

1u

C642

1u

C643

1u

C653

10u_16V_1206

C654

10u_16V_1206

B B

12VP0_IN

A A

C0_DBI4

VX4_DBO

SPHASE0_VT4

U94

A5

VSS

A7

VSS

B5

VSS

B7

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

R980 X_0

R797

0

VX4_DBO

SPHASE0_VT4

+3.3V

C649

R798

IDES_P IDES_P

0

IDES_N

Slave4_FAULTB

C0_DBI4

C0_BST4

C647

1u

1u

4

IDES_P <7>

IDES_N <7>

1uC659

VX4

R750

1KST

VX4 <7> VX3 <7>

12VP0_IN

C668

1u

C667

1u

C666

1u

C622

10u_16V_1206

C623

10u_16V_1206

R970 X_0

R751

0

C0_DBO3

SPHASE0_VT3

+3.3V

C620

3

1u

SPHASE <7>

DBI <7>

REMOVE BYPASS R

IDES_P

H1

G2

H2

DBI

DBO

SPHASE

IDES_P

IDES_N

Slave3_FAULTB

C0_BST3

C2

B1

A3

BST

IDESN

FAULTB

GND

GND

VDD

VDD

VCC

VT1135S

D1

IDESP

VX

VX

VX

VX

VX

VX

VX

VX

VX

VX

VX

VX

C2

B1

IDESN

VT1135S

A3

FAULTB

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

B2

A2

IDES_N

Slave1_FAULTB

C0_BST1

A4

VX

A6

BST

VX

B4

VX

B6

VX

C4

VX

C6

VX

D4

VX

D6

VX

E4

VX

E6

VX

F4

VX

F6

VX

F1

GND

E2

GND

A1

VDD

B2

VDD

A2

VCC

HS4

112

2

VRD_HEATSINK_4 Phase

VX3

+3.3V

VX1

+3.3V

334

4

Near C653

for EMI

12VP0_IN

CI54

104P

VX1_DBI

VX1

VX1 <7>

12VP0_IN

1uC634

VX3

12VP0_IN

SPHASE0_VT1

VX3_DBI

C0_DBO3

SPHASE0_VT3

U90

A5

VSS

A7

VSS

B5

VSS

B7

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

C0_DBO1

A5

A7

B5

B7

C5

C7

D5

D7

E5

E7

F5

F7

B3

C3

D3

E3

F3

H2

SPHASE

U82

H1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDDH

VDDH

VDDH

VDDH

VDDH

G2

DBO

D1

DBI

IDESP

Micro-Star Int'l Co., Ltd.

Slave1_FAULTB

Slave2_FAULTB

Slave3_FAULTB

Slave4_FAULTB

Slave1_FAULTB <7>

Slave2_FAULTB <7>

Slave3_FAULTB <7>

Slave4_FAULTB <7>

2

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

CPU0_VT1135S

MS-9185

1

of

875Monday, April 17, 2006

0BCustom

5

4

3

2

1

009

+3.3V

CPU3POWER_EN

P3_VID7

D D

R186

249RST

C168

X_103P

C161

680P

R204

845RST

C167

0.12uF

C C

R187

499RST

R205

2.49K

P3_VID6

P3_VID5

P3_VID5<28,62>

P3_VID4

P3_VID4<28,62>

P3_VID3

P3_VID3<28,62>

P3_VID2

P3_VID2<28,62>

P3_VID1

P3_VID1<28,62>

P3_VID0

P3_VID0<28,62>

4.7uC141

P3OVP+

P3OVPP3OVP_OUT

6800PC150

P3SENSE+

P3SENSE-

P3VR_HOT

P3VR_FAN

P3FAULTB

U22

1

OE

2

VID<7>

3

VID<6>

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

VID<5>

VID<4>

VID<3>

VID<2>

VID<1>

VID<0>

VDD

GND

OVP+

OVPOVP_out

Vnom+

Vnomsense+

senseVamp_out1

Vamp_in

Vamp_out2

Vr_Hot

Vr_Fan

FaultB

VT1115M

EXT_REF

R_sel<7>

R_sel<6>

R_sel<5>

R_sel<4>

R_sel<3>

R_sel<2>

Load_Current

R_sel<1>

R_sel<0>

R_SEL0 =2.43K

SMBUS = E6h

MASTER

P3R_SEL7

R144 5.9KST-0402

P3R_SEL6

R148 1.02K_0402

P3R_SEL5

R147 340RST

P3R_SEL4

B B

P3R_SEL3

P3R_SEL2

P3R_SEL1

P3R_SEL0

P3R_FREQ

P3R_REF

R150 3.74KR1%-LF

R156 8.66KST-0402

R159 11.3K

R203 5.11K-0402

R197 2.43K-0603

R163 26.1K-0402

R152 11KST-0402

Reported Faults

P3FAULTB

P3OVP_OUT

P3VR_FAN

P3VR_HOT

Configuration Resistors,Rref

+5V

5

4

PWRSEQ_7_GD <65>

A A

CPU0POWER_GD<7>

CPU3POWER_GD

5

1

2

3

U25

VCC

GND

NC7S32

VDD

SC

SD

GND

R_ref

Pwrgd

R_freq

Vin_ov

Vin_uv

Ides_n

Ides_p

DBO

DBI

sphase

R193

10K-0402

4

36

47

46

45

44

43

42

41

40

39

38

37

48

35

34

33

32

31

30

29

28

27

26

25

+3.3V

10K-0402

SMB_6_CLK <7,11,12,63>

P3R_SEL7

P3R_SEL6

P3R_SEL5

P3R_SEL4

P3R_REF

P3R_SEL3

P3R_SEL2

P3R_FREQ

P3VIN_OV

P3VIN_UV

P3R_SEL1

P3R_SEL0

+3.3V

R158

SMB_6_DATA <7,11,12,63>

R182 10K_0603

R202 0_0402

R201 0_0402

R198 0_0402

R199 0_0402

R200 0_0402

R139 4.7K

R140 4.7K 22u_6.3V_1206C144

R194

10K-0402

Near R179

for EMI

H3_PRESENT_N<28,51>

P3IDES_N

P3IDES_P

P3DBI

P3DBO

P3SPHASE

P3_VID7

P3_VID6

R192

10K-0402

P3_VCORE

+3.3V

+5V

CI53

104P

R142

10K_0603

CPU3POWER_GD

1u_10V

C130

P3IDES_N <10>

P3IDES_P <10>

P3DBI <10>

P3DBO <10>

P3SPHASE <10>

P3VIN_OV

+5V

DS

G

C151

0.1uF

PWRSEQ_7_EN<7,65>

R179

10K

Q17

2N7002

3

R181

100K

R175

10.7KST

For individual part by Voltera recommend

12VP3_IN

R188

63.4k 1%

P3VIN_UV

R206

10K

1

2

3

U19

100nH

U20

100nH

U18

100nH

U17

100nH

C156

0.1uF

U27

GND

NC7S08

VCC

P3_VX1 <10>

P3_VCORE

P3_VX2 <10>

P3_VCORE

P3_VX3 <10>

P3_VCORE

P3_VX4 <10>

P3_VCORE

+5V

5

CPU3POWER_EN

4

+3.3V

CI30

104P

Near U29

for EMI

2

P3_VCORE_FB_N<28>

P3_VCORE_FB_P<28>

P3_VCORE

R282

56_0603

R155

0

47u_6.3V_1206C162

47u_6.3V_1206C246

47u_6.3V_1206C174

47u_6.3V_1206C741

47u_6.3V_1206C183

47u_6.3V_1206C191

47u_6.3V_1206C203

47u_6.3V_1206C216

22u_6.3V_1206C153

22u_6.3V_1206C134

22u_6.3V_1206C742

R169

R177

0

0

P3SENSE+ P3SENSE-

P3OVP+ P3OVP-

R153 100/1206

47u_6.3V_1206C228

47u_6.3V_1206C239

47u_6.3V_1206C730

47u_6.3V_1206C114

47u_6.3V_1206C113

47u_6.3V_1206C115

47u_6.3V_1206C116

47u_6.3V_1206C117

R284

56_0603

R161

0

10/4 Joe, 47uF x4 pcs per phase by Voltera recommend

Slave

R883

Faults

P3Slave1_FAULTB<10>

P3Slave2_FAULTB<10>

P3Slave3_FAULTB<10>

P3Slave4_FAULTB<10>

P3Slave1_FAULTB

P3Slave2_FAULTB

P3Slave3_FAULTB

P3Slave4_FAULTB

R881

10K-0402

10K-0402

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

CPU3_VT1115M

10K-0402

MS-9185

1

R882

10K-0402

975Monday, April 17, 2006

+3.3V

R884

0BCustom

of

5

4

3

2

1

010

P3DB3

D D

H1

H2

SPHASE

U13

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDDH

VDDH

VDDH

VDDH

VDDH

5

DBO

G2

DBI

C2

D1

IDESP

IDESN

H1

H2

DBO

SPHASE

A3

B1

FAULTB

VT1135S

D1

G2

DBI

P3IDES_P

P3IDES_N

P3Slave2_FAULTB

C3_BST2

P3_VX2

A4

VX

A6

BST

VX

B4

VX

B6

VX

C4

VX

C6

VX

D4

VX

D6

VX

E4

VX

E6

VX

F4

VX

F6

VX

F1

GND

E2

GND

A1

VDD

B2

VDD

A2

VCC

P3IDES_P

P3IDES_N

P3Slave4_FAULTB

C3_BST4

C2

A3

B1

VX

BST

VX

IDESP

IDESN

VX

FAULTB

VX

VX

VX

VX

VX

VX

VX

VX

VX

GND

GND

VDD

VDD

VCC

VT1135S

+3.3V

1u

1u

1u

10u_16V_1206

10u_16V_1206

P3DBO<9>

P3_VX4 SPHASE3_VT3

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

B2

A2

C3_DBI2

P3_VX2_DBO

SPHASE3_VT2

U16

A5

VSS

A7

VSS

B5

VSS

B7

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

12VP3_IN

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

C3_DBI4

P3_VX4_DBO

SPHASE3_VT4

A5

A7

B5

B7

C5

C7

D5

D7

E5

E7

F5

F7

B3

C3

D3

E3

F3

12VP3_IN

C C

B B

A A

R94

1KST

12VP3_IN 12VP3_IN

C74

C62

C52

C69

C56

R93

+3.3V

12VP3_IN

C71

1u

C59

1u

C49

1u

C66

10u_16V_1206

C53

10u_16V_1206

R879 X_0

P3_VX2_DBO

C80

1u

R103

0

P3IDES_P

C3_DBI2

P3IDES_N

P3Slave2_FAULTB

1uC88

C3_BST2 C3_BST1

P3_VX2

1u

1u

1u

10u_16V_1206

10u_16V_1206

C89

1u

R92

C73

C61

C51

C68

C55

R98

0

SPHASE3_VT2

+3.3V +3.3V

Input Cap. totally 1u/0603x3, 10u/16Vx2 each phase

1KST

R97

0

P3_VX4_DBO

SPHASE3_VT4

+3.3V

4

R102

0

P3IDES_P

P3IDES_N

C3_DBI4

P3Slave4_FAULTB

C3_BST4

C77

C83

1u

1u

1uC82

P3IDES_P <9>

P3IDES_N <9>

P3_VX4

P3_VX4 <9>

C72

1u

C60

1u

C50

1u

C67

10u_16V_1206

C54

10u_16V_1206

R878 X_0

R96

0

C3_DBO1 P3Slave1_FAULTB

SPHASE3_VT1

1KST

C79

1u

R877 X_0R880 X_0

R95

0

C3_DBO3

SPHASE3_VT3

R91

1KST

12VP3_IN

+3.3V

3

R101

0

P3IDES_P

P3_VX1_DBI

P3IDES_N

1uC86

C87

1u

P3SPHASE

R100

0

P3IDES_P

P3_VX3_DBI

P3IDES_N

P3Slave3_FAULTB

C3_BST3

C85

C78

1u

1u

P3_VX1

P3DB3

1uC84

P3_VX3

P3SPHASE <9>

P3DBI <9>

REMOVE BYPASS R

P3_VX1 <9>P3_VX2 <9>

SPHASE3_VT1

12VP3_IN

REMOVE BYPASS R

P3_VX3 <9>

12VP3_IN

2

P3_VX1_DBI

C3_DBO1

H2

U15

A5

VSS

A7

VSS

B5

VSS

B7

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

P3Slave1_FAULTB

P3Slave2_FAULTB

P3Slave3_FAULTB

P3Slave4_FAULTB

P3_VX3_DBI

C3_DBO3

U14

A5

VSS

A7

VSS

B5

VSS

B7

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

HS1

112

334

2

4

VRD_HEATSINK_2 Phase

P3IDES_P

P3IDES_N

P3Slave1_FAULTB

C2

D1

H1

B1

G2

DBI

DBO

IDESP

IDESN

SPHASE

VT1135S

P3Slave1_FAULTB <9>

P3Slave2_FAULTB <9>

P3Slave3_FAULTB <9>

P3Slave4_FAULTB <9>

D1

H1

H2

G2

DBI

DBO

SPHASE

C3_BST1

A3

VX

BST

VX

VX

FAULTB

VX

VX

VX

VX

VX

VX

VX

VX

VX

GND

GND

VDD

VDD

VCC

P3IDES_P

P3IDES_N

P3Slave3_FAULTB

C3_BST3

C2

A3

B1

BST

IDESP

IDESN

FAULTB

GND

GND

VDD

VDD

VCC

VT1135S

P3_VX1

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

+3.3V

B2

A2

P3_VX3

A4

VX

A6

VX

B4

VX

B6

VX

C4

VX

C6

VX

D4

VX

D6

VX

E4

VX

E6

VX

F4

VX

F6

VX

F1

E2

A1

+3.3V

B2

A2

HS2

112

334

2

VRD_HEATSINK_2 Phase

4

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

CPU3_VT1135S

MS-9185

1

of

10 75Monday, April 17, 2006

0BCustom

5

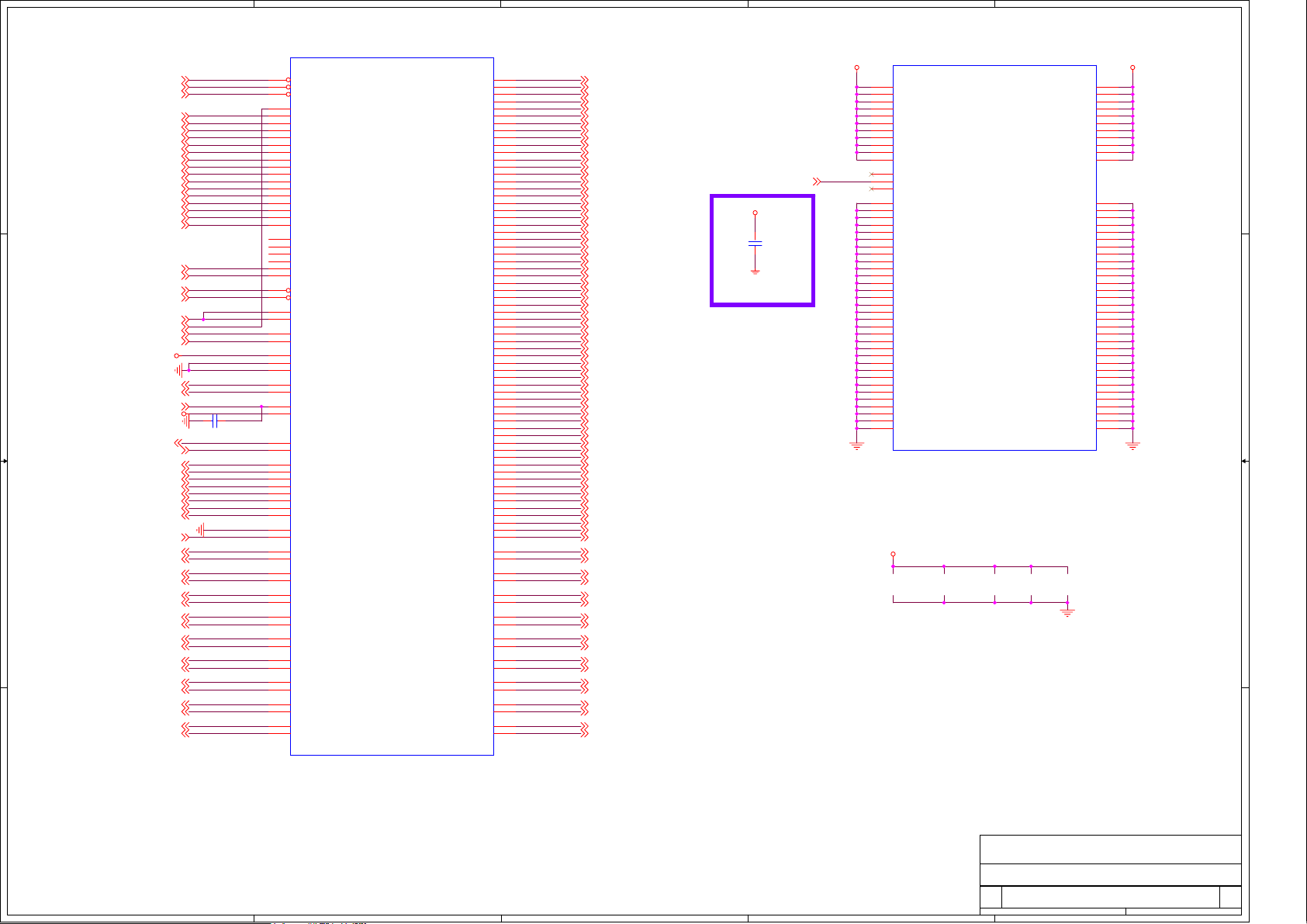

011

PWRSEQ_5_GD<12,65>

D D

Near U36

for EMI

C C

P0_P1V8VID5

P0_P1V8VID0

P0_P1V8OEN

+3.3V

+5V

10K

R804

1u_10V

C648

CI17

104P

C636

X_103P

R979

R787

X_10K

10K

R981

R776

X_0

X_0

PWRSEQ_5_EN<12,65>

SMB_6_CLK<7,9,12,63> SMB_6_DATA <7,9,12,63>

RN137

1 2

3 4

5 6

+3.3V+3.3V+3.3V

7 8

249RST

R766

360RST

C621

47nF

R978

10K-0402

R788

X_0_0402

R976 0

8P4R-0R

R773

C632

680P

4.7uC639

R781

499RST

R774

1.27K

MASTER

Reported Faults

+3.3V

R796

10K-0402

P0_P1V8OEN

P1V8 Regulator

+3.3V

Master

1

2

P0_P1V8OEN

3

P0_P1V8VID5

4

P0_P1V8VID4

5

P0_P1V8VID3

6

P0_P1V8VID2

7

P0_P1V8VID1

8

P0_P1V8VID0

9

10

P0_P1V8FAULT

R_SEL0

R_SEL1

R_SEL2

R_SEL3

R_SEL4

R_SEL5

R_SEL6

11

12

13

14

15

16

17

18

19

SMbus address=E8h

Setpoint=-6.3mV

PowerGood & OVP voltage

VR9 VID codes

Imax=36A,Slave setting=1

Slave Program

Uncoupled Inductor

6800PC640

P0_P1V8SENSE+

P0_P1V8SENSE-

Vnom+ and Vnom- have

to connect to cap

directly,

then connect to GND

P0_P1V8FAULT

U93

SC

Pwrgd

OEN

VID<5>

VID<4>

VID<3>

VID<2>

VID<1>

VID<0>

VDD

GND

Vnom+

Vnomsense+

senseVamp_out1

Vamp_in

Vamp_out2

FaultB#

VT1105M

R_SEL0 =7.15K

SMBUS = E8h

4

R_sel<6>

R_sel<5>

R_sel<4>

R_sel<3>

R_sel<2>

R_sel<1>

R_sel<0>

GND

R_ref

R_freq

Vin_ov

Vin_uv

Ides_n

Ides_p

sphase

3

+3.3V

38

SD

37

P0_P1V8SEL6

36

P0_P1V8SEL5

35

P0_P1V8SEL4

34

P0_P1V8REF

33

P0_P1V8SEL3

32

P0_P1V8SEL2

31

P0_P1V8FREQ

30

29

VDD

P0_P1V8VIN_OV

28

P0_P1V8VIN_UV

27

P0_P1V8SEL1

26

P0_P1V8IDESNR

25

P0_P1V8IDESPR

24

P0_P1V8SEL0

23

22

DBO

21

DBI

20

R848 0_0402

R847 0_0402

R809 0_0402

R811 0_0402

R818 0_0402

IDESP & IDESN use

T-routing is better

than daisy chain.

P0_P1V8IDESN

P0_P1V8IDESP

P0_P1V8DBI

P0_P1V8DBO

P0_P1V8SPHASE

Sense resistor should be

together and away from

controller.

connect to a bypass cap is

better.

P0_P1V8

R778 0_0402

R777 0_0402 47u_6.3V_1206C962

P0_P1V8SENSE+

P0_P1V8SENSE-

HS5

1122334

VRD_HEATSINK_2 Phase

P0_VDDIO_FB_H <15>

P0_VDDIO_FB_L <15>

4

2

P0_P1V8 P0_P1V8

47u_6.3V_1206C595

47u_6.3V_1206C588

47u_6.3V_1206C961

47u_6.3V_1206C568

47u_6.3V_1206C965

47u_6.3V_1206C964

47u_6.3V_1206C963

22u_6.3V_1206C960

22u_6.3V_1206C959

10/04 Joe, change 47u x 4 pcs per phase

1

For 1.8V application

P0_P1V8SEL6

P0_P1V8SEL5

P0_P1V8SEL4

P0_P1V8SEL3

P0_P1V8SEL2

P0_P1V8SEL1

P0_P1V8SEL0

P0_P1V8REF

P0_P1V8FREQ

R812 340RST

R813 340RST

R845 5.11K-0402

R843 5.9KST-0402

R842 23.7KST-0402

R849 5.11K-0402

R822 7.15KST-0402

R844 11KST-0402

R841 26.1K-0402

each phase needs 100u~150u capacitance

+12V

R868

R869

100K

R871

10.7KST

63.4k 1%

R872

10K

C670

103P

P0_P1V8VIN_OV P0_P1V8VIN_UV

C671

103P

Configuration Resistors,Rref

P1V8 Regulator

+12V

Near C532

for EMI

B B

C0_P1V8DBI2 SPHASE0_P1V8VT1

SPHASE0_P1V8VT2 C0_P1V8BST1

A5

A7

B5

B7

C5

C7

D5

D7

E5

E7

F5

F7

B3

+12V

C3

D3

E3

F3

A A

CI51

104P

P0_P1V8IDESP

P0_P1V8IDESN

P0_P1V8FAULTS2P0_P1V8DBO_IN

C0_P1V8BST2

H1

A3

D1

H2

C2

G2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDDH

VDDH

VDDH

VDDH

VDDH

B1

VX

DBI

BST

VX

DBO

IDESP

IDESN

VX

FAULTB

SPHASE

VX

VX

VX

VX

VX

VX

VX

VX

VX

GND

GND

VDD

VDD

VCC

VT1135S

5

U87

P0_P1V8DBO

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

B2

A2

P1V8VX2

C628

1u

C633

1u

C638

1u

C629

10u_16V_1206

C637

10u_16V_1206

Slave

R763

1K-0402

R754 X_0_0402

R760

0

P0_P1V8DBO_IN

SPHASE0_P1V8VT2

C602

P0_P1V8SPHASE

P0_P1V8DBI_IN

R962

0

C556

1u

P0_P1V8DBI

P0_P1V8IDESP

P0_P1V8IDESN

P0_P1V8FAULTS1

1uC557

C0_P1V8BST1

P1V8VX1

CHOK4

120nH

3

R753 0_0402

R745

0

C0_P1V8DBI2

P0_P1V8IDESP

P0_P1V8IDESN

1uC603

C0_P1V8BST2

P1V8VX2

C610

1u

1u

4

CHOK6

120nH

C528

1u

C522

1u

C535

1u

C523

10u_16V_1206

C532

10u_16V_1206

R959

P0_P1V8

1K-0402

+12V+12V

R961 X_0_0402

R762

0

C0_P1V8DBO1P0_P1V8FAULTS2

+3.3V+3.3V

C544

1u

P0_P1V8

+12V

Slave

Faults

P0_P1V8DBI_IN

C0_P1V8DBO1

SPHASE0_P1V8VT1

A5

A7

B5

B7

C5

C7

D5

D7

E5

E7

F5

F7

B3

C3

D3

E3

F3

P0_P1V8FAULTS1

P0_P1V8FAULTS2

H1

H2

G2

U81

VSS

DBI

VSS

DBO

VSS

SPHASE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDDH

VDDH

VDDH

VDDH

VDDH

+3.3V +3.3V

10K-0402

R963

P0_P1V8IDESP

P0_P1V8IDESN

P0_P1V8FAULTS1

A3

D1

C2

B1

VX

BST

VX

IDESP

IDESN

VX

FAULTB

VX

VX

VX

VX

VX

VX

VX

VX

VX

GND

GND

VDD

VDD

VCC

VT1135S

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

B2

A2

10K-0402

R744

P1V8VX1

DDRII VTT Power

+3.3V

U100

APL5331KAC

8

NC

7

NC

6

VCNTL

5

NC

C967

+3.3V+3.3V

2

0.1U25V_0603

Title

Size Document Number Rev

Date: Sheet

P0_P1V8

1

VREF1

VOUT

VIN

2

GND

3

4

9

NC

+

12

1000U

EC21

P0_VTT_0.9V

C993

0.1U

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

CPU0 DDR POWER

MS-9185

1

11 75Monday, April 17, 2006

P0_P1V8

of

R975

1K_1%_0603

R977

1K_1%_0603

0BC

5

012

PWRSEQ_5_GD<11,65>

D D

Near U51

for EMI

C C

P3_P1V8VID5

P3_P1V8VID0

P3_P1V8OEN

+3.3V

CI34

104P

+5V

10K

R387

1u_10V

C338

C340

X_103P

R396

X_10K

R896

X_0

PWRSEQ_5_EN<11,65>

SMB_6_CLK<7,9,11,63> SMB_6_DATA <7,9,11,63>

RN54

1 2

3 4

5 6

R399

10K

R898

X_0

+3.3V+3.3V+3.3V

7 8

249RST

R404

360RST

C352

47nF

R395

X_10K-0402

R897

X_0_0402

R405 0

8P4R-0R

R403

C351

680P

4.7uC346

R393

499RST

R394

1.27K

MASTER

Reported Faults

+3.3V

R389

10K-0402

P3_P1V8OEN

P1V8 Regulator

+3.3V

Master

1

2

P3_P1V8OEN

3

P3_P1V8VID5

4

P3_P1V8VID4

5

P3_P1V8VID3

6

P3_P1V8VID2

7

P3_P1V8VID1

8

P3_P1V8VID0

9

10

P3_P1V8FAULT

R_SEL0

R_SEL1

R_SEL2

R_SEL3

R_SEL4

R_SEL5

R_SEL6

11

12

13

14

15

16

17

18

19

SMbus address=EEh

Setpoint=-6.3mV

PowerGood & OVP voltage

VR9 VID codes

Imax=36A,Slave setting=1

Slave Program

Uncoupled Inductor

6800PC358

P3_P1V8SENSE+

P3_P1V8SENSE-

Vnom+ and Vnom- have

to connect to cap

directly,

then connect to GND

P3_P1V8FAULT

4

+3.3V

U53

SC

Pwrgd

OEN

VID<5>

VID<4>

VID<3>

VID<2>

VID<1>

VID<0>

VDD

GND

Vnom+

Vnomsense+

senseVamp_out1

Vamp_in

Vamp_out2

FaultB#

VT1105M

38

SD

37

GND

36

R_sel<6>

35

R_sel<5>

34

R_sel<4>

33

R_ref

32

R_sel<3>

31

R_sel<2>

30

R_freq

29

VDD

28

Vin_ov

27

Vin_uv

26

R_sel<1>

25

Ides_n

24

Ides_p

23

R_sel<0>

22

DBO

21

DBI

20

sphase

R_SEL0 =9.31K

SMBUS = EEh

P3_P1V8SEL6

P3_P1V8SEL5

P3_P1V8SEL4

P3_P1V8SEL3

P3_P1V8SEL2

P3_P1V8SEL1

P3_P1V8SEL0

P3_P1V8REF

P3_P1V8FREQ

R379 340RST

R381 340RST

R361 5.11K-0402

R362 5.9KST-0402

R373 23.7KST-0402

R375 5.11K-0402

R364 9.31KST-0402

R372 11KST-0402

R374 26.1K-0402

P3_P1V8SEL6

P3_P1V8SEL5

P3_P1V8SEL4

P3_P1V8REF

P3_P1V8SEL3

P3_P1V8SEL2

P3_P1V8FREQ

P3_P1V8VIN_OV

P3_P1V8VIN_UV

P3_P1V8SEL1

P3_P1V8IDESNR

P3_P1V8IDESPR

P3_P1V8SEL0

R363 0_0402

R376 0_0402

R377 0_0402

R365 0_0402

R378 0_0402

IDESP & IDESN use

T-routing is better

than daisy chain.

Configuration Resistors,Rref

P3_P1V8IDESN

P3_P1V8IDESP

P3_P1V8DBI

P3_P1V8DBO

P3_P1V8SPHASE

3

Sense resistor should be

together and away from

controller.

connect to a bypass cap is

better.

P3_P1V8

R397 0_0402

R398 0_0402

HS6

1122334

VRD_HEATSINK_2 Phase

P3_P1V8SENSE+

P3_P1V8SENSE-

4

P3_VDDIO_FB_H <28>

P3_VDDIO_FB_L <28>

2

P3_P1V8 P3_P1V8

47u_6.3V_1206C325

47u_6.3V_1206C331

47u_6.3V_1206C332

47u_6.3V_1206C179

47u_6.3V_1206C326

1

10/04 Joe, change 47u x 4 pcs per phase

Heatsink

+12V

R371

R370

63.4k 1%

100K

P3_P1V8VIN_OV P3_P1V8VIN_UV

R360

C328

103P

R359

10.7KST

10K

C327

103P

+12V

D1

C2

DBI

IDESP

CI50

104P

P3_P1V8IDESP

P3_P1V8IDESN

P3_P1V8FAULTS2

C31V8_BST2

A3

B1

VX

BST

VX

IDESN

VX

FAULTB

VX

VX

VX

VX

VX

VX

VX

VX

VX

GND

GND

VDD

VDD

VCC

VT1135S

5

P3_P1V8DBO

A4

A6

B4

B6

C4

C6

D4

D6

E4

E6

F4

F6

F1

E2

A1

B2

A2

Near C342

for EMI

B B

C3_P1V8DBI2

P3_P1V8DBO_IN

SPHASE3P1V8_VT2

+12V

A A

H1

H2

G2

U55

A5

VSS

A7

VSS

DBO

B5

VSS

B7

SPHASE

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

P1V8 Regulator

Slave

R388

1K-0402

P3_P1V8VX2

+3.3V

C339

1u

C344

1u

C348

1u

C342

10u_16V_1206

C347

10u_16V_1206

R346

1K-0402

P3_P1V8

+12V+12V

R354 X_0_0402

R347

0

C3_P1V8DBO1

+3.3V+3.3V

1u

R385 X_0_0402

R386

0

P3_P1V8DBO_IN

SPHASE3P1V8_VT2 SPHASE3_P1V8VT1

R382

0

C3_P1V8DBI2

C31V8_BST2

C333

C335

1u

1u

P3_P1V8IDESP

P3_P1V8IDESN

P3_P1V8FAULTS2

1uC334

R384 0_0402

P3_P1V8VX2

4

CHOK3

120nH

C318

1u

C315

1u

C312

1u

C317

10u_16V_1206

C313

10u_16V_1206

C322

P3_P1V8DBI

R353

0

P3_P1V8DBI_IN

C320

1u

P3_P1V8SPHASE

P3_P1V8IDESP

P3_P1V8IDESN

P3_P1V8FAULTS1

C3_P1V8BST1

1uC321

P3_P1V8VX1

CHOK2

120nH

3

P3_P1V8

Slave

Faults

P3_P1V8DBI_IN

C3_P1V8DBO1

SPHASE3_P1V8VT1

+12V

P3_P1V8FAULTS1

P3_P1V8FAULTS2

H2

U48

A5

VSS

A7

VSS

B5

VSS

B7

SPHASE

VSS

C5

VSS

C7

VSS

D5

VSS

D7

VSS

E5

VSS

E7

VSS

F5

VSS

F7

VSS

B3

VDDH

C3

VDDH

D3

VDDH

E3

VDDH

F3

VDDH

+3.3V +3.3V

10K-0402

R891

P3_P1V8IDESP

P3_P1V8IDESN

P3_P1V8FAULTS1

C3_P1V8BST1

H1

A3

D1

C2

G2

B1

DBI

BST

DBO

IDESP

IDESN

FAULTB

GND

GND

VT1135S

10K-0402

DDRII VTT Power

R380

+3.3V

U28

APL5331KAC

8

P3_P1V8VX1

A4

VX

A6

VX

B4

VX

B6

VX

C4

VX

C6

VX

D4

VX

D6

VX

E4

VX

E6

VX

F4

VX

F6

VX

F1

E2

A1

+3.3V

VDD

B2

VDD

A2

VCC

2

NC

7

NC

6

VCTNL

5

NC

C160

0.1U25V_0603

Title

Size Document Number Rev

Date: Sheet

P3_P1V8

+

12

EC6

1000U/6.3V

1

VREF1

VOUT

VIN

2

GND

3

4

9

NC

+

12

1000U

EC5

P3_VTT_0.9V

C180

0.1U

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

CPU3 DDR POWER

MS-9185

1

12 75Monday, April 17, 2006

P3_P1V8

of

R217

1K_1%_0603

R216

1K_1%_0603

0BC

5

4

3

2

1

013

CPU0A

HTX_TO_P0_CLKOUT_H1<39>

HTX_TO_P0_CLKOUT_L1<39>

HTX_TO_P0_CLKOUT_H0<39>

HTX_TO_P0_CLKOUT_L0<39>

D D

C C

HTX_TO_P0_CTLOUT_H0<39>

HTX_TO_P0_CTLOUT_L0<39>

HTX_TO_P0_CADOUT_H15<39>

HTX_TO_P0_CADOUT_L15<39>

HTX_TO_P0_CADOUT_H14<39>

HTX_TO_P0_CADOUT_L14<39>

HTX_TO_P0_CADOUT_H13<39>

HTX_TO_P0_CADOUT_L13<39>

HTX_TO_P0_CADOUT_H12<39>

HTX_TO_P0_CADOUT_L12<39>

HTX_TO_P0_CADOUT_H11<39>

HTX_TO_P0_CADOUT_L11<39>

HTX_TO_P0_CADOUT_H10<39>

HTX_TO_P0_CADOUT_L10<39>

HTX_TO_P0_CADOUT_H9<39>

HTX_TO_P0_CADOUT_L9<39>

HTX_TO_P0_CADOUT_H8<39>

HTX_TO_P0_CADOUT_L8<39>

HTX_TO_P0_CADOUT_H7<39>

HTX_TO_P0_CADOUT_L7<39>

HTX_TO_P0_CADOUT_H6<39>

HTX_TO_P0_CADOUT_L6<39>

HTX_TO_P0_CADOUT_H5<39>

HTX_TO_P0_CADOUT_L5<39>

HTX_TO_P0_CADOUT_H4<39>

HTX_TO_P0_CADOUT_L4<39>

HTX_TO_P0_CADOUT_H3<39>

HTX_TO_P0_CADOUT_L3<39>

HTX_TO_P0_CADOUT_H2<39>

HTX_TO_P0_CADOUT_L2<39>

HTX_TO_P0_CADOUT_H1<39>

HTX_TO_P0_CADOUT_L1<39>

HTX_TO_P0_CADOUT_H0<39>

HTX_TO_P0_CADOUT_L0<39>

+1.2V_HT

R958 49.9_1%

R956 49.9_1%

M6

L0_CLKIN_H(1)

N6

L0_CLKIN_L(1)

M3

L0_CLKIN_H(0)

M2

L0_CLKIN_L(0)

U4

L0_CTLIN_H(1)

U5

L0_CTLIN_L(1)

T1

L0_CTLIN_H(0)

U1

L0_CTLIN_L(0)

T6

L0_CADIN_H(15)

U6

L0_CADIN_L(15)

R4

L0_CADIN_H(14)

R5

L0_CADIN_L(14)

P6

L0_CADIN_H(13)

R6

L0_CADIN_L(13)

N4

L0_CADIN_H(12)

N5

L0_CADIN_L(12)

L4

L0_CADIN_H(11)

L5

L0_CADIN_L(11)

K6

L0_CADIN_H(10)

L6

L0_CADIN_L(10)

J4

L0_CADIN_H(9)

J5

L0_CADIN_L(9)

H6

L0_CADIN_H(8)

J6

L0_CADIN_L(8)

T3

L0_CADIN_H(7)

T2

L0_CADIN_L(7)

P1

L0_CADIN_H(6)

R1

L0_CADIN_L(6)

P3

L0_CADIN_H(5)

P2

L0_CADIN_L(5)

M1

L0_CADIN_H(4)

N1

L0_CADIN_L(4)

K1

L0_CADIN_H(3)

L1

L0_CADIN_L(3)

K3

L0_CADIN_H(2)

K2

L0_CADIN_L(2)

H1

L0_CADIN_H(1)

J1

L0_CADIN_L(1)

H3

L0_CADIN_H(0)

H2

L0_CADIN_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

SOCKET-F(1207)

AC5

AC4

AC1

AB1

W6

V6

V2

V3

W5

W4

AA6

Y6

AA5

AA4

AC6

AB6

AE6

AD6

AE5

AE4

AG6

AF6

AG5

AG4

W1

V1

Y2

Y3

AA1

Y1

AB2

AB3

AD2

AD3

AE1

AD1

AF2

AF3

AG1

AF1

P0_TO_HTX_CLKOUT_H1 <39>

P0_TO_HTX_CLKOUT_L1 <39>

P0_TO_HTX_CLKOUT_H0 <39>

P0_TO_HTX_CLKOUT_L0 <39>

P0_TO_HTX_CTLOUT_H0 <39>

P0_TO_HTX_CTLOUT_L0 <39>

P0_TO_HTX_CADOUT_H15 <39>

P0_TO_HTX_CADOUT_L15 <39>

P0_TO_HTX_CADOUT_H14 <39>

P0_TO_HTX_CADOUT_L14 <39>

P0_TO_HTX_CADOUT_H13 <39>

P0_TO_HTX_CADOUT_L13 <39>

P0_TO_HTX_CADOUT_H12 <39>

P0_TO_HTX_CADOUT_L12 <39>

P0_TO_HTX_CADOUT_H11 <39>

P0_TO_HTX_CADOUT_L11 <39>

P0_TO_HTX_CADOUT_H10 <39>

P0_TO_HTX_CADOUT_L10 <39>

P0_TO_HTX_CADOUT_H9 <39>

P0_TO_HTX_CADOUT_L9 <39>

P0_TO_HTX_CADOUT_H8 <39>

P0_TO_HTX_CADOUT_L8 <39>

P0_TO_HTX_CADOUT_H7 <39>

P0_TO_HTX_CADOUT_L7 <39>

P0_TO_HTX_CADOUT_H6 <39>

P0_TO_HTX_CADOUT_L6 <39>

P0_TO_HTX_CADOUT_H5 <39>

P0_TO_HTX_CADOUT_L5 <39>

P0_TO_HTX_CADOUT_H4 <39>

P0_TO_HTX_CADOUT_L4 <39>

P0_TO_HTX_CADOUT_H3 <39>

P0_TO_HTX_CADOUT_L3 <39>

P0_TO_HTX_CADOUT_H2 <39>

P0_TO_HTX_CADOUT_L2 <39>

P0_TO_HTX_CADOUT_H1 <39>

P0_TO_HTX_CADOUT_L1 <39>

P0_TO_HTX_CADOUT_H0 <39>

P0_TO_HTX_CADOUT_L0 <39>

P3_TO_P0_CLKOUT_H1<26>

P3_TO_P0_CLKOUT_L1<26>

P3_TO_P0_CLKOUT_H0<26>

P3_TO_P0_CLKOUT_L0<26>

P3_TO_P0_CTLOUT_H0<26>

P3_TO_P0_CTLOUT_L0<26>

P3_TO_P0_CADOUT_H15<26>

P3_TO_P0_CADOUT_L15<26>

P3_TO_P0_CADOUT_H14<26>

P3_TO_P0_CADOUT_L14<26>

P3_TO_P0_CADOUT_H13<26>

P3_TO_P0_CADOUT_L13<26>

P3_TO_P0_CADOUT_H12<26>

P3_TO_P0_CADOUT_L12<26>

P3_TO_P0_CADOUT_H11<26>

P3_TO_P0_CADOUT_L11<26>

P3_TO_P0_CADOUT_H10<26>

P3_TO_P0_CADOUT_L10<26>

P3_TO_P0_CADOUT_H9<26>

P3_TO_P0_CADOUT_L9<26>

P3_TO_P0_CADOUT_H8<26>

P3_TO_P0_CADOUT_L8<26>

P3_TO_P0_CADOUT_H7<26>

P3_TO_P0_CADOUT_L7<26>

P3_TO_P0_CADOUT_H6<26>

P3_TO_P0_CADOUT_L6<26>

P3_TO_P0_CADOUT_H5<26>

P3_TO_P0_CADOUT_L5<26>

P3_TO_P0_CADOUT_H4<26>

P3_TO_P0_CADOUT_L4<26>

P3_TO_P0_CADOUT_H3<26>

P3_TO_P0_CADOUT_L3<26>

P3_TO_P0_CADOUT_H2<26>

P3_TO_P0_CADOUT_L2<26>

P3_TO_P0_CADOUT_H1<26>

P3_TO_P0_CADOUT_L1<26>

P3_TO_P0_CADOUT_H0<26>

P3_TO_P0_CADOUT_L0<26>

+1.2V_HT

R590 49.9_1%

R583 49.9_1%

E18

E17

C18

B18

C13

D13

A14

A13

E14

E13

C15

D15

E16

E15

C17

D17

C19

D19

E20

E19

C21

D21

E22

E21

C14

B14

A16

A15

C16

B16

A18

A17

A20

A19

C20

B20

A22

A21

C22

B22

L1_CLKIN_H(1)

L1_CLKIN_L(1)

L1_CLKIN_H(0)

L1_CLKIN_L(0)

L1_CTLIN_H(1)

L1_CTLIN_L(1)

L1_CTLIN_H(0)

L1_CTLIN_L(0)

L1_CADIN_H(15)

L1_CADIN_L(15)

L1_CADIN_H(14)

L1_CADIN_L(14)

L1_CADIN_H(13)

L1_CADIN_L(13)

L1_CADIN_H(12)

L1_CADIN_L(12)

L1_CADIN_H(11)

L1_CADIN_L(11)

L1_CADIN_H(10)

L1_CADIN_L(10)

L1_CADIN_H(9)

L1_CADIN_L(9)

L1_CADIN_H(8)

L1_CADIN_L(8)

L1_CADIN_H(7)

L1_CADIN_L(7)

L1_CADIN_H(6)

L1_CADIN_L(6)

L1_CADIN_H(5)

L1_CADIN_L(5)

L1_CADIN_H(4)

L1_CADIN_L(4)

L1_CADIN_H(3)

L1_CADIN_L(3)

L1_CADIN_H(2)

L1_CADIN_L(2)

L1_CADIN_H(1)

L1_CADIN_L(1)

L1_CADIN_H(0)

L1_CADIN_L(0)

CPU0B

L1_CLKOUT_H(1)

L1_CLKOUT_L(1)

L1_CLKOUT_H(0)

L1_CLKOUT_L(0)

L1_CTLOUT_H(1)

L1_CTLOUT_L(1)

L1_CTLOUT_H(0)

L1_CTLOUT_L(0)

L1_CADOUT_H(15)

L1_CADOUT_L(15)

L1_CADOUT_H(14)

L1_CADOUT_L(14)

L1_CADOUT_H(13)

L1_CADOUT_L(13)

L1_CADOUT_H(12)

L1_CADOUT_L(12)

L1_CADOUT_H(11)

L1_CADOUT_L(11)

L1_CADOUT_H(10)

L1_CADOUT_L(10)

L1_CADOUT_H(9)

L1_CADOUT_L(9)

L1_CADOUT_H(8)

L1_CADOUT_L(8)

L1_CADOUT_H(7)

L1_CADOUT_L(7)

L1_CADOUT_H(6)

L1_CADOUT_L(6)

L1_CADOUT_H(5)

L1_CADOUT_L(5)

L1_CADOUT_H(4)

L1_CADOUT_L(4)

L1_CADOUT_H(3)

L1_CADOUT_L(3)

L1_CADOUT_H(2)

L1_CADOUT_L(2)

L1_CADOUT_H(1)

L1_CADOUT_L(1)

L1_CADOUT_H(0)

L1_CADOUT_L(0)

SOCKET-F(1207)

E6

D6

B6

B7

F10

F11

C11

D11

E10

D10

F8

F9

E8

D8

F6

F7

F4

F5

E4

D4

F2

F3

E2

D2

B10

B11

C9

D9

B8

B9

C7

D7

C5

D5

B4

B5

C3

D3

B2

B3

P0_TO_P3_CLKOUT_H1 <26>

P0_TO_P3_CLKOUT_L1 <26>

P0_TO_P3_CLKOUT_H0 <26>

P0_TO_P3_CLKOUT_L0 <26>

P0_TO_P3_CTLOUT_H0 <26>

P0_TO_P3_CTLOUT_L0 <26>

P0_TO_P3_CADOUT_H15 <26>

P0_TO_P3_CADOUT_L15 <26>

P0_TO_P3_CADOUT_H14 <26>

P0_TO_P3_CADOUT_L14 <26>

P0_TO_P3_CADOUT_H13 <26>

P0_TO_P3_CADOUT_L13 <26>

P0_TO_P3_CADOUT_H12 <26>

P0_TO_P3_CADOUT_L12 <26>

P0_TO_P3_CADOUT_H11 <26>

P0_TO_P3_CADOUT_L11 <26>

P0_TO_P3_CADOUT_H10 <26>

P0_TO_P3_CADOUT_L10 <26>

P0_TO_P3_CADOUT_H9 <26>

P0_TO_P3_CADOUT_L9 <26>

P0_TO_P3_CADOUT_H8 <26>

P0_TO_P3_CADOUT_L8 <26>

P0_TO_P3_CADOUT_H7 <26>

P0_TO_P3_CADOUT_L7 <26>

P0_TO_P3_CADOUT_H6 <26>

P0_TO_P3_CADOUT_L6 <26>

P0_TO_P3_CADOUT_H5 <26>

P0_TO_P3_CADOUT_L5 <26>

P0_TO_P3_CADOUT_H4 <26>

P0_TO_P3_CADOUT_L4 <26>

P0_TO_P3_CADOUT_H3 <26>

P0_TO_P3_CADOUT_L3 <26>

P0_TO_P3_CADOUT_H2 <26>

P0_TO_P3_CADOUT_L2 <26>

P0_TO_P3_CADOUT_H1 <26>

P0_TO_P3_CADOUT_L1 <26>

P0_TO_P3_CADOUT_H0 <26>

P0_TO_P3_CADOUT_L0 <26>

HT-LINK2

CPU0C

HT_TO_P0_CLKOUT_H1<42>

HT_TO_P0_CLKOUT_L1<42>

HT_TO_P0_CLKOUT_H0<42>

HT_TO_P0_CLKOUT_L0<42>

HT_TO_P0_CTLOUT_H0<42>

HT_TO_P0_CTLOUT_L0<42>

HT_TO_P0_CADOUT_H15<42>

HT_TO_P0_CADOUT_L15<42>

HT_TO_P0_CADOUT_H14<42>

HT_TO_P0_CADOUT_L14<42>

HT_TO_P0_CADOUT_H13<42>

HT_TO_P0_CADOUT_L13<42>

HT_TO_P0_CADOUT_H12<42>

HT_TO_P0_CADOUT_L12<42>

HT_TO_P0_CADOUT_H11<42>

HT_TO_P0_CADOUT_L11<42>

HT_TO_P0_CADOUT_H10<42>

HT_TO_P0_CADOUT_L10<42>

HT_TO_P0_CADOUT_H9<42>

HT_TO_P0_CADOUT_L9<42>

HT_TO_P0_CADOUT_H8<42>

HT_TO_P0_CADOUT_L8<42>

HT_TO_P0_CADOUT_H7<42>

HT_TO_P0_CADOUT_L7<42>

HT_TO_P0_CADOUT_H6<42>

HT_TO_P0_CADOUT_L6<42>

HT_TO_P0_CADOUT_H5<42>

HT_TO_P0_CADOUT_L5<42>

HT_TO_P0_CADOUT_H4<42>

HT_TO_P0_CADOUT_L4<42>

HT_TO_P0_CADOUT_H3<42>

HT_TO_P0_CADOUT_L3<42>

HT_TO_P0_CADOUT_H2<42>

HT_TO_P0_CADOUT_L2<42>

HT_TO_P0_CADOUT_H1<42>

HT_TO_P0_CADOUT_L1<42>

HT_TO_P0_CADOUT_H0<42>

HT_TO_P0_CADOUT_L0<42>

R725 49.9_1%

R726 49.9_1%

+1.2V_HT

B B

A A

AM7

AN7

AM12

AL12

AP11

AP12

AK11

AK12

AM10

AL10

AK10

AM8

AM6

AM4

AM11

AN11

AP10

AM9

AN9

AM5

AN5

AM3

AN3

AK7

AK8

AK9

AL8

AL6

AK5

AK6

AL4

AK3

AK4

AP9

AP7

AP8

AP5

AP6

AP3

AP4

L2_CLKIN_H(1)

L2_CLKIN_L(1)

L2_CLKIN_H(0)

L2_CLKIN_L(0)

L2_CTLIN_H(1)

L2_CTLIN_L(1)

L2_CTLIN_H(0)

L2_CTLIN_L(0)

L2_CADIN_H(15)

L2_CADIN_L(15)

L2_CADIN_H(14)

L2_CADIN_L(14)

L2_CADIN_H(13)

L2_CADIN_L(13)

L2_CADIN_H(12)

L2_CADIN_L(12)

L2_CADIN_H(11)

L2_CADIN_L(11)

L2_CADIN_H(10)

L2_CADIN_L(10)

L2_CADIN_H(9)

L2_CADIN_L(9)

L2_CADIN_H(8)

L2_CADIN_L(8)

L2_CADIN_H(7)

L2_CADIN_L(7)

L2_CADIN_H(6)

L2_CADIN_L(6)

L2_CADIN_H(5)

L2_CADIN_L(5)

L2_CADIN_H(4)

L2_CADIN_L(4)

L2_CADIN_H(3)

L2_CADIN_L(3)

L2_CADIN_H(2)

L2_CADIN_L(2)

L2_CADIN_H(1)

L2_CADIN_L(1)

L2_CADIN_H(0)

L2_CADIN_L(0)

L2_CLKOUT_H(1)

L2_CLKOUT_L(1)

L2_CLKOUT_H(0)

L2_CLKOUT_L(0)

L2_CTLOUT_H(1)

L2_CTLOUT_L(1)

L2_CTLOUT_H(0)

L2_CTLOUT_L(0)

L2_CADOUT_H(15)

L2_CADOUT_L(15)

L2_CADOUT_H(14)

L2_CADOUT_L(14)

L2_CADOUT_H(13)

L2_CADOUT_L(13)

L2_CADOUT_H(12)

L2_CADOUT_L(12)

L2_CADOUT_H(11)

L2_CADOUT_L(11)

L2_CADOUT_H(10)

L2_CADOUT_L(10)

L2_CADOUT_H(9)

L2_CADOUT_L(9)

L2_CADOUT_H(8)

L2_CADOUT_L(8)

L2_CADOUT_H(7)

L2_CADOUT_L(7)

L2_CADOUT_H(6)

L2_CADOUT_L(6)

L2_CADOUT_H(5)

L2_CADOUT_L(5)

L2_CADOUT_H(4)

L2_CADOUT_L(4)

L2_CADOUT_H(3)

L2_CADOUT_L(3)

L2_CADOUT_H(2)

L2_CADOUT_L(2)

L2_CADOUT_H(1)

L2_CADOUT_L(1)

L2_CADOUT_H(0)