MSI MS-9181, MS- Schematic 21

A B C

Dell Controlled Print

D

REVISIONS

1

2

3

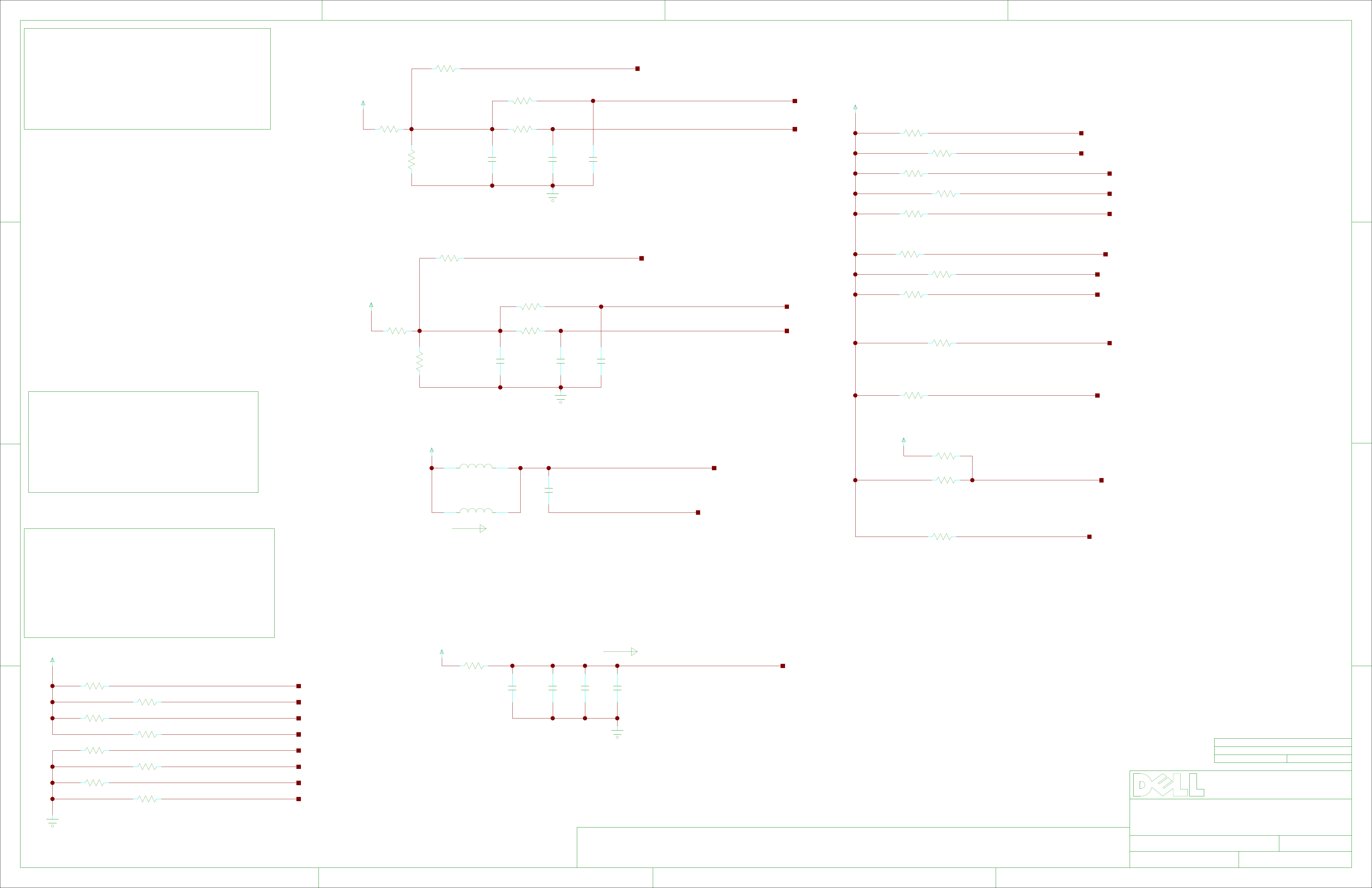

SUB=NP Always no-pop

SUB=NP0 Populate only for debug

BOM options

0 = 5708 Production

1 = 5708 development

2 = LOM2 5721J

3 = CTPM Sinosun Populated

4 = ROW TPM ST Populated

6 = LOM1 5721J

7 = Adds London Parts

8 = Adds Berlin Parts

9 = Adds System Test debug components (non-production)

BOM Instructions

Builds 0, 1, and 2 are leveraged from Montreal

builds 7 and 8 are specfic to london/berlin

Build 3 is specific to China TPM (CTPM)

In order to build a proper BOM, you must run a combo build

To build london for production (ROW TPM), use builds 0, 4 and 7

To build london for production (CTPM), use builds 0, 3 and 7

To build a 5708 debug build for london (ROW TPM) use builds 1,4 and 7

To build Berlin for production (ROW TPM), use builds 0,4 and 8

To build Berlin for production (CTPM), use builds 0, 3 and 8

To build a 5708 debug build for berlin (ROW TPM) use builds 1,4 and 8

Only add build 5 if you want microview parts

London system test build (With ROW TPM) is a combined build of 0479

London system test build (With CTPM) is a combined build of 0379

Berlin system test build (With ROW TPM) is a combined build of 0489

Berlin system test build (With CTPM) is a combined build of 0389

REV

X00

PNR724925

229098 09/07/2007

INITIAL PROTOTYPE RELEASE

INITIAL PRODUCTION RELEASE

DESCRIPTIONECO DATE

TABLE OF CONTENTS

Page 1-11.

Page 12-15.

Page 16-19.

Page 20-21.

Page 22-29.

Page 30-31.

Page 32-39.

Page 40-43.

Page 45.

Page 46-47.

Page 59.

Page 60.

Page 61.

Page 62.

Page 63.

Page 64-65.

Page 66.

Page 67.

Page 68.

Page 69.

Page 70.

Page 71-73.

Page 74-79.

Page 81-82.

Page 83-84.

Page 85.

Page 86-88

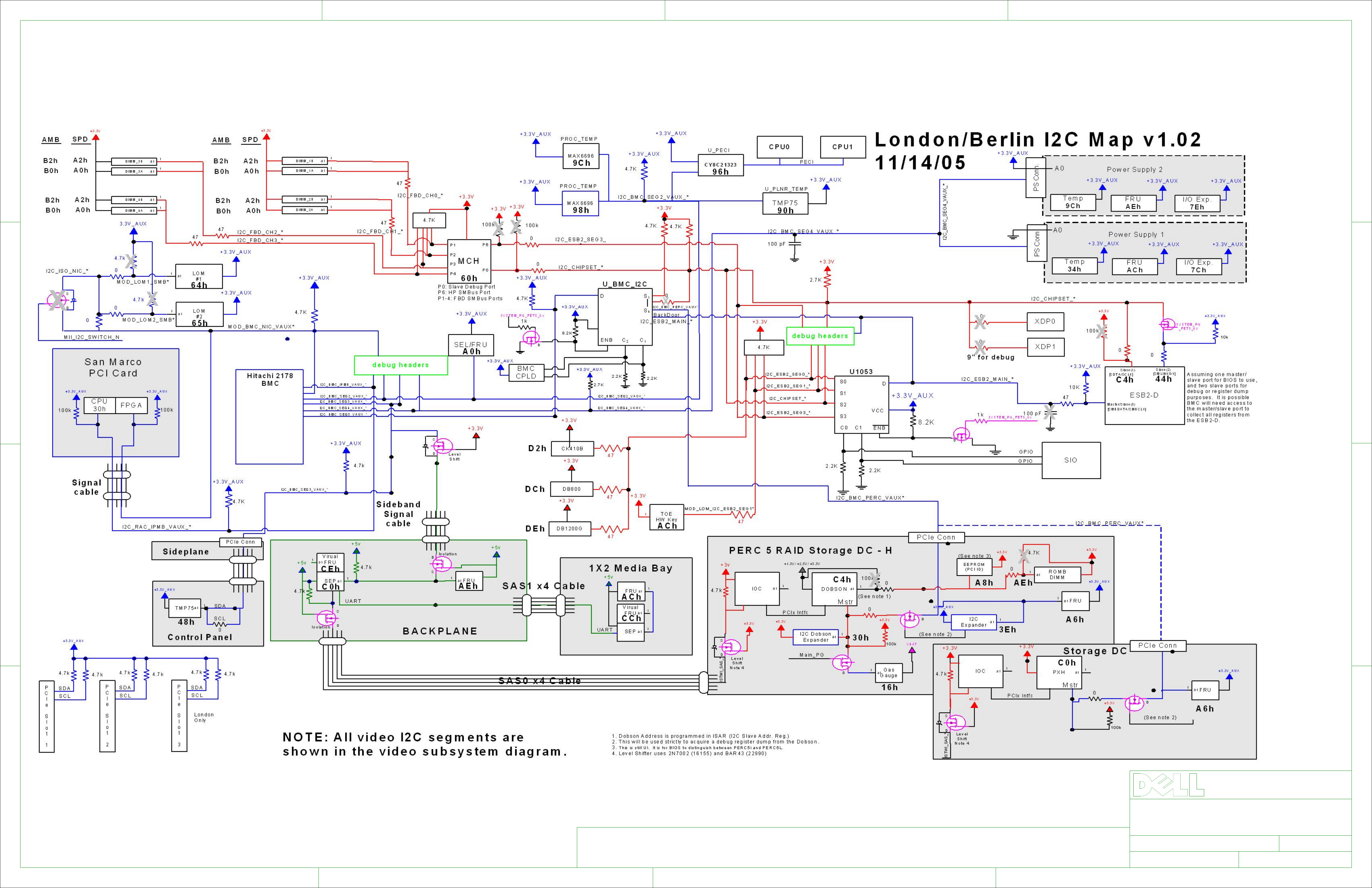

Page 89. BMC - temp sensors/debug port

Page 90.

Page 91.

Page 92.

Page 93.

Page 80, 94.

Page 95.

Page 96.

Page 97-103.

Page 104-107.

Page 108-119.

Page 120.

Page 121.

Page 122.

Page 123.

Page 124.

Page 125. Impedance Coupons (48SE, 50SE, 75D, 85D)

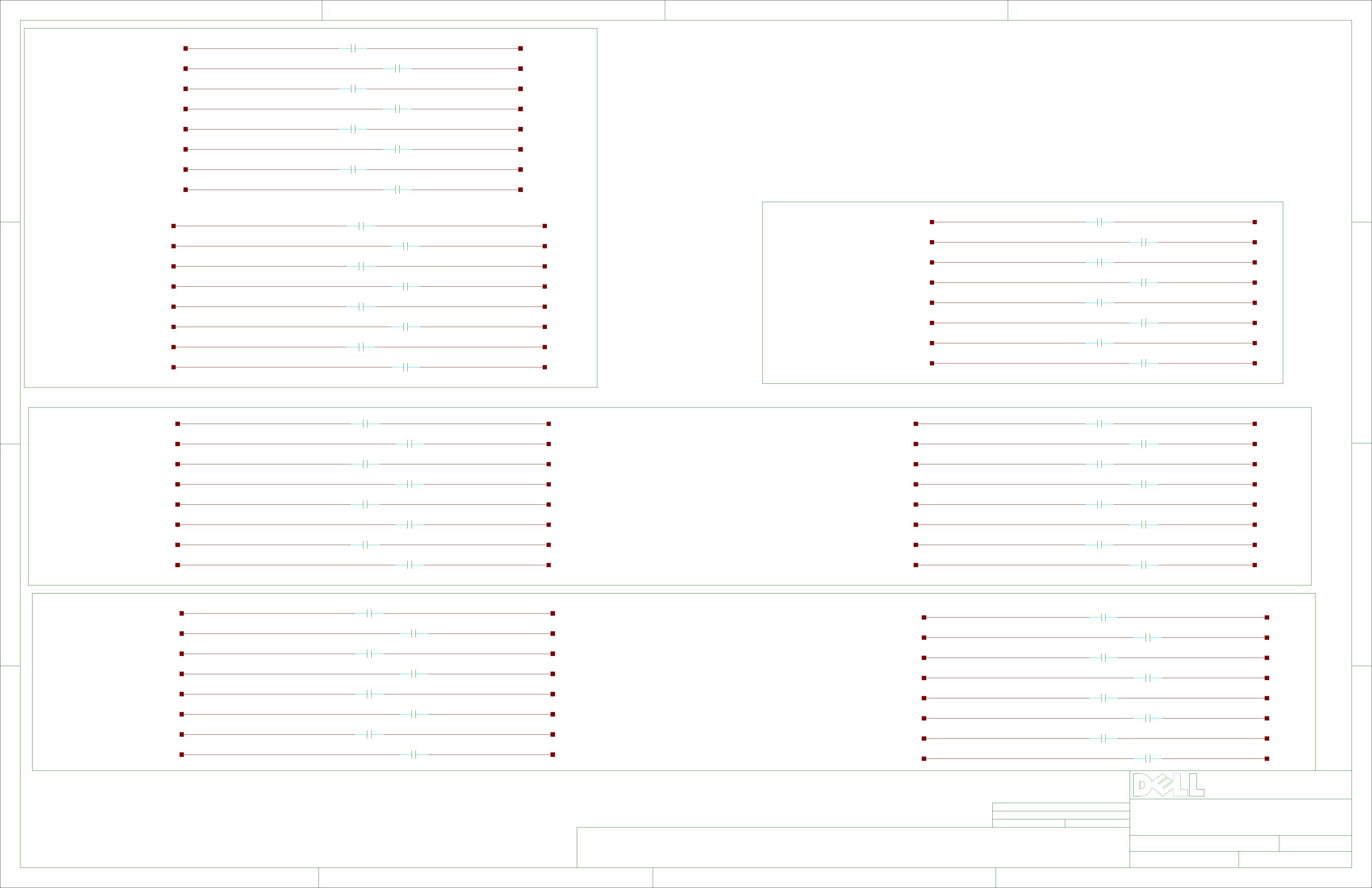

Page 126-127.

Page 128-129.

Page 130-135.

Page 136.

BLOCK DIAGRAMS

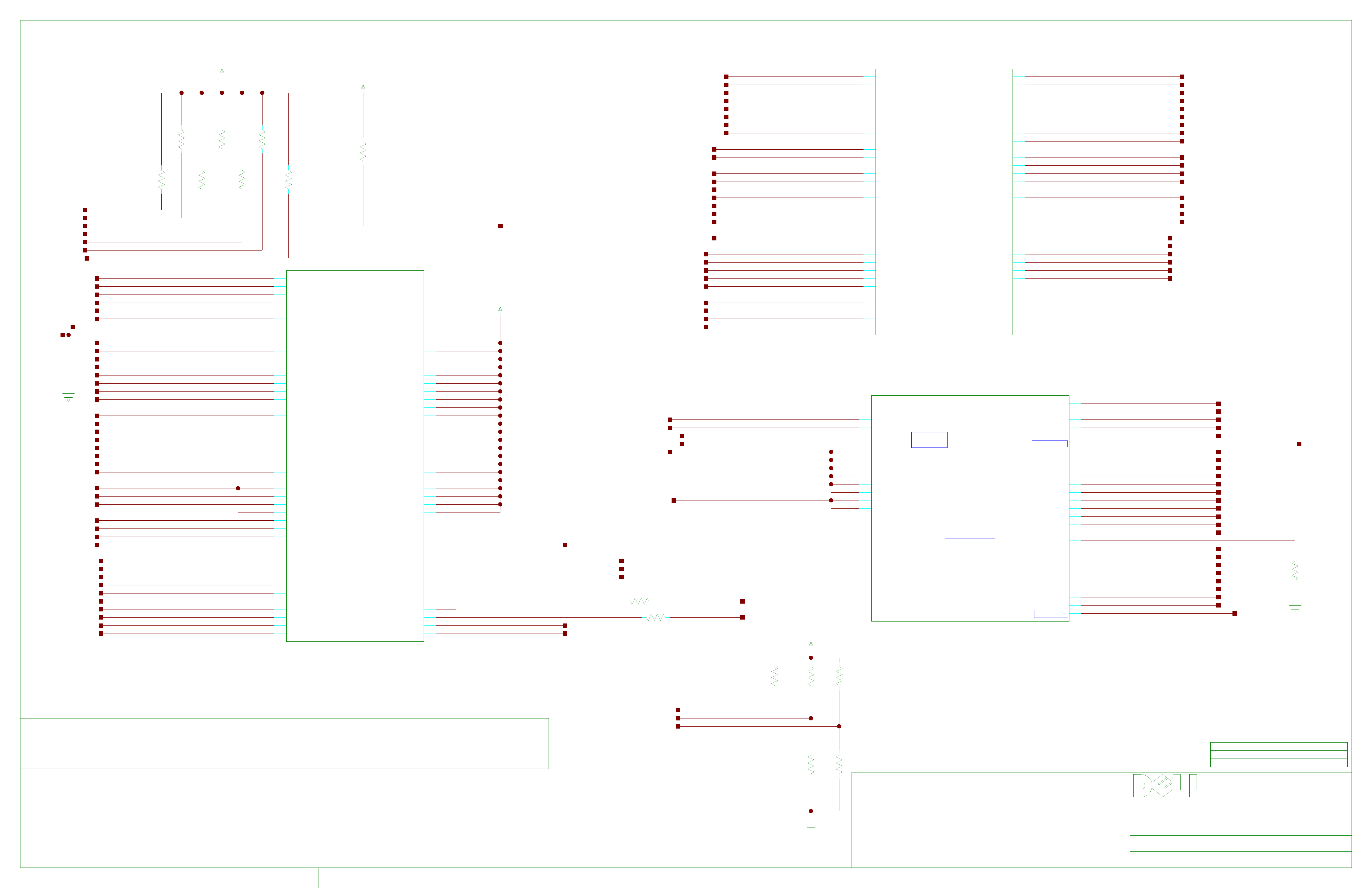

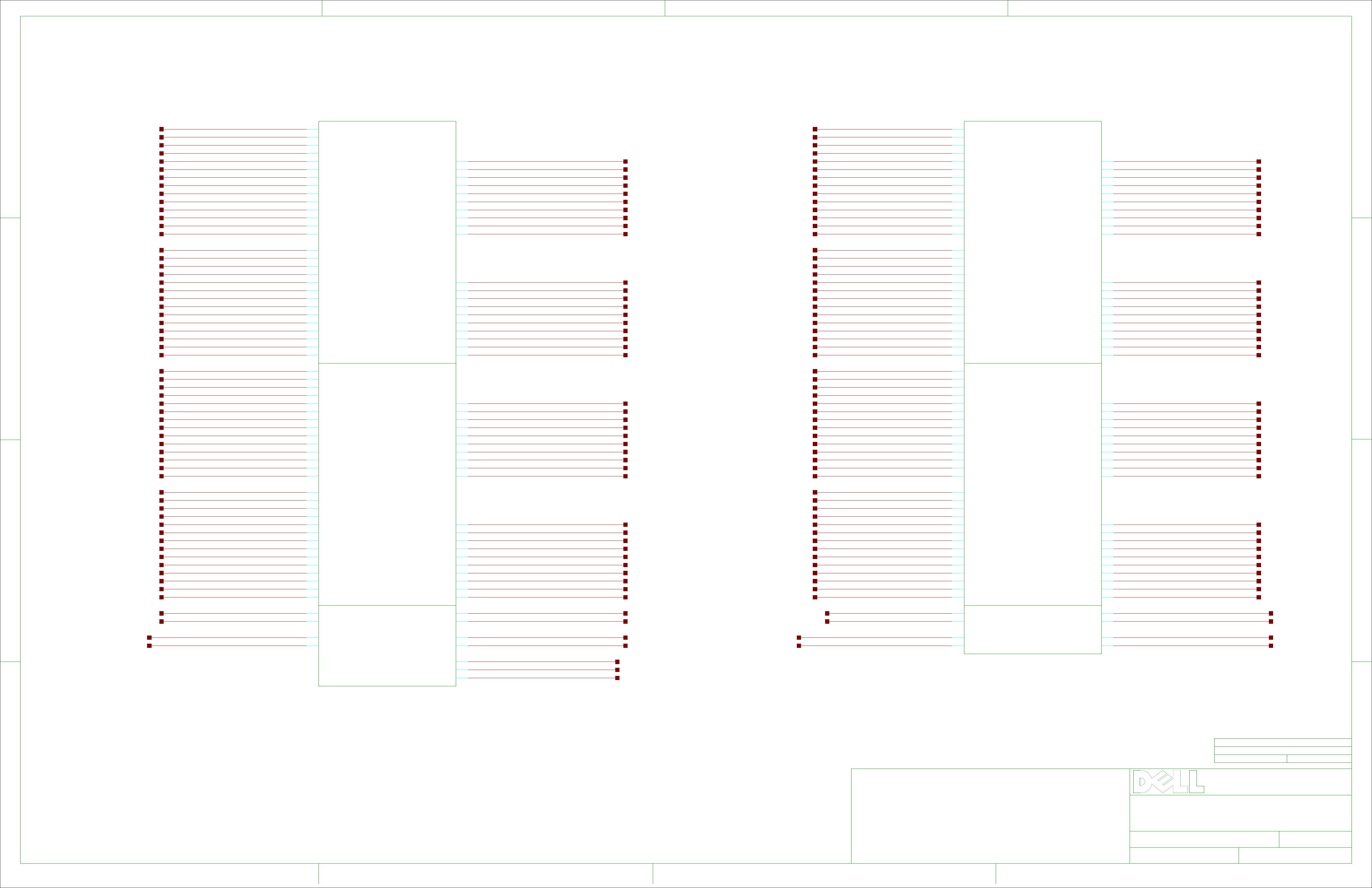

Processor 0

Processor 1

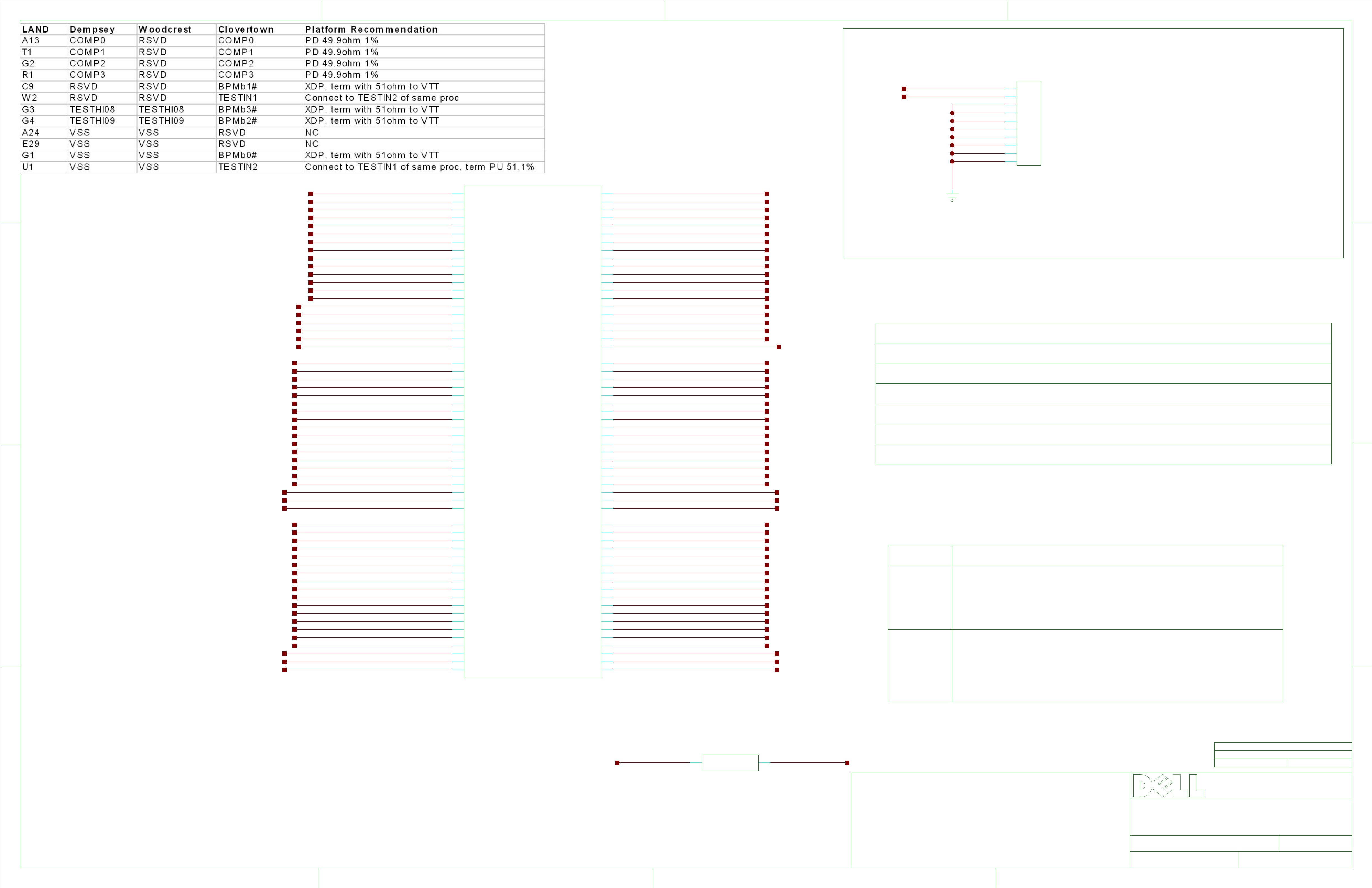

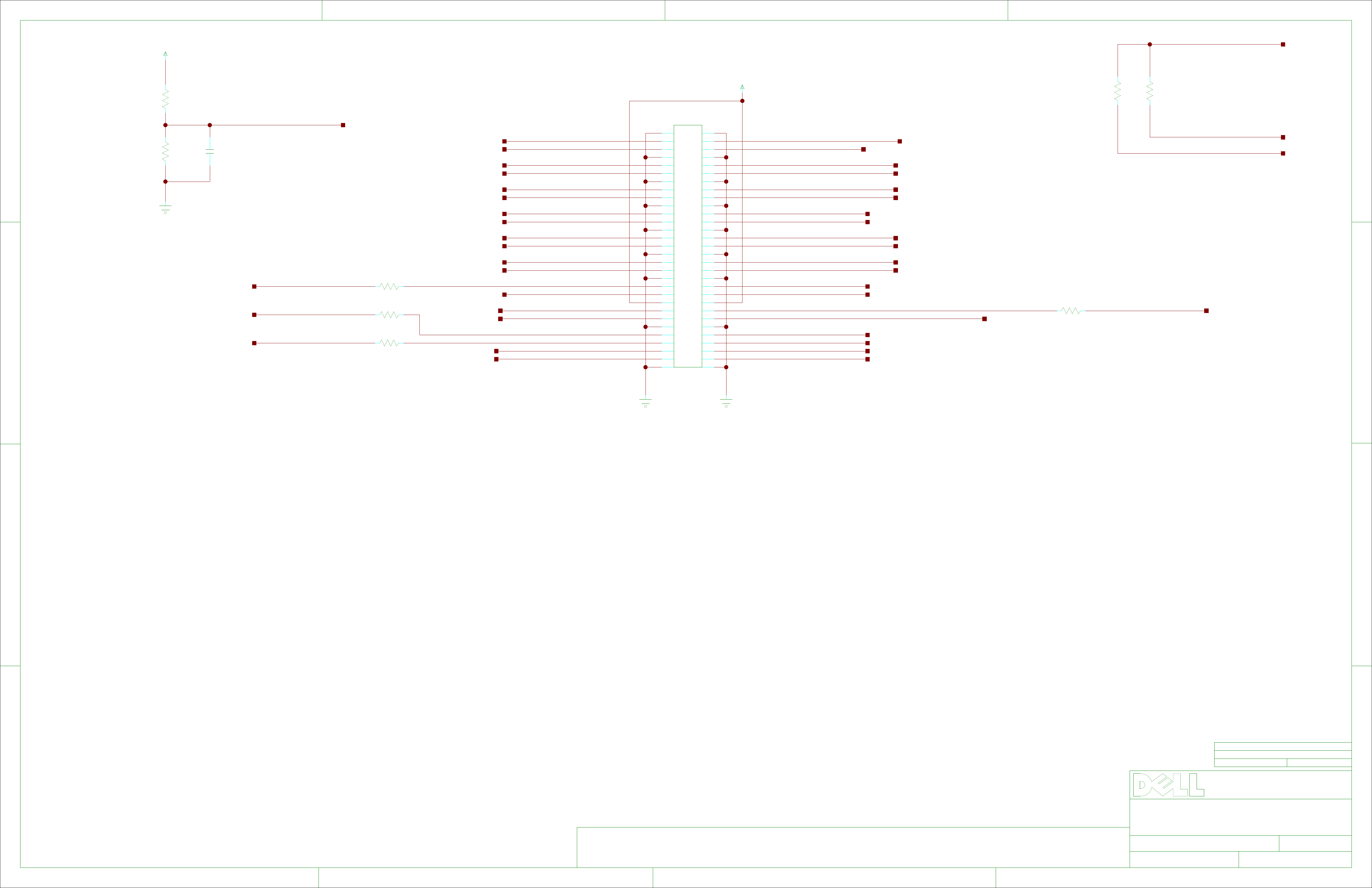

XDP0 and GTL Translation

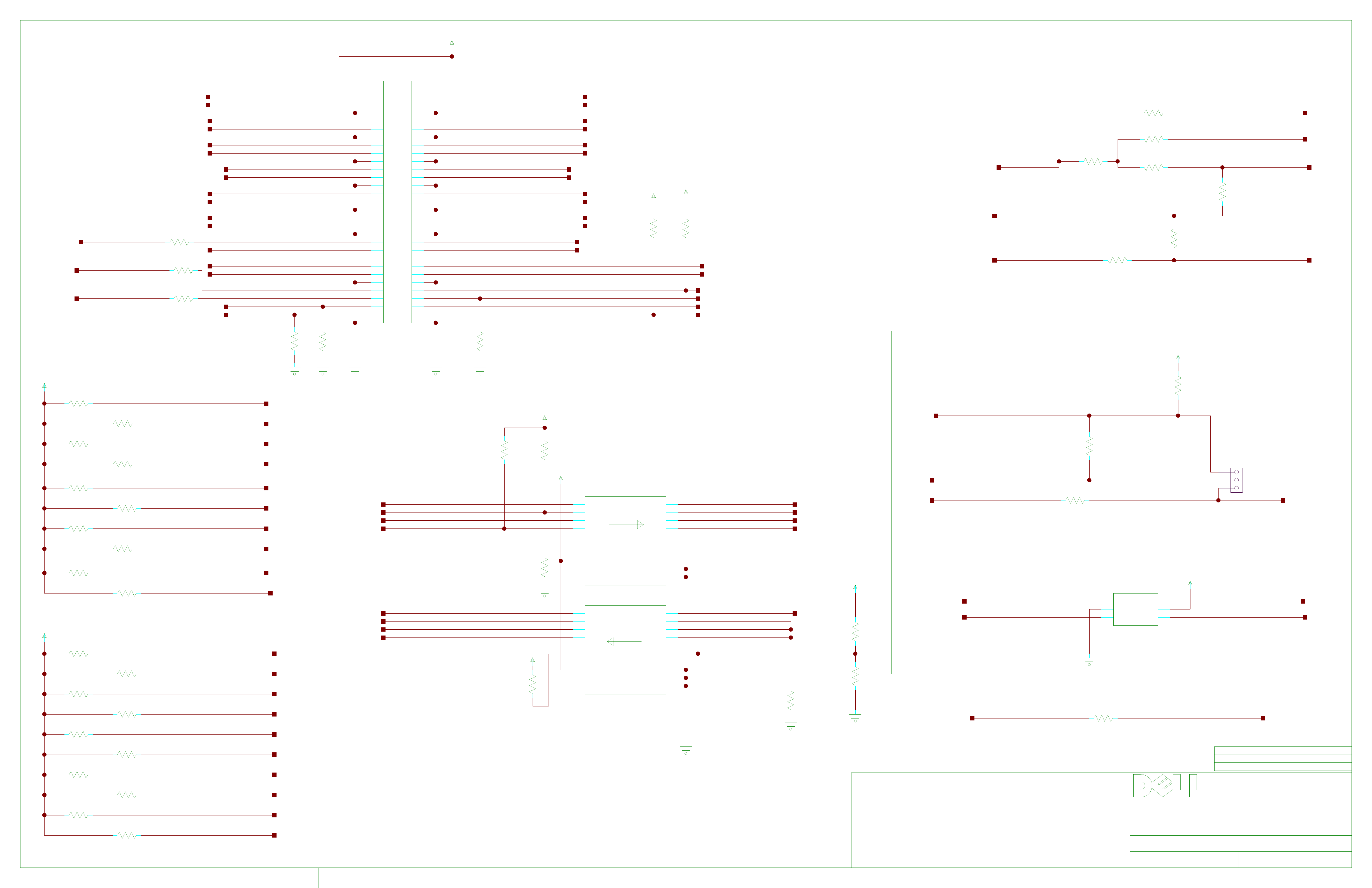

Blackford MCH

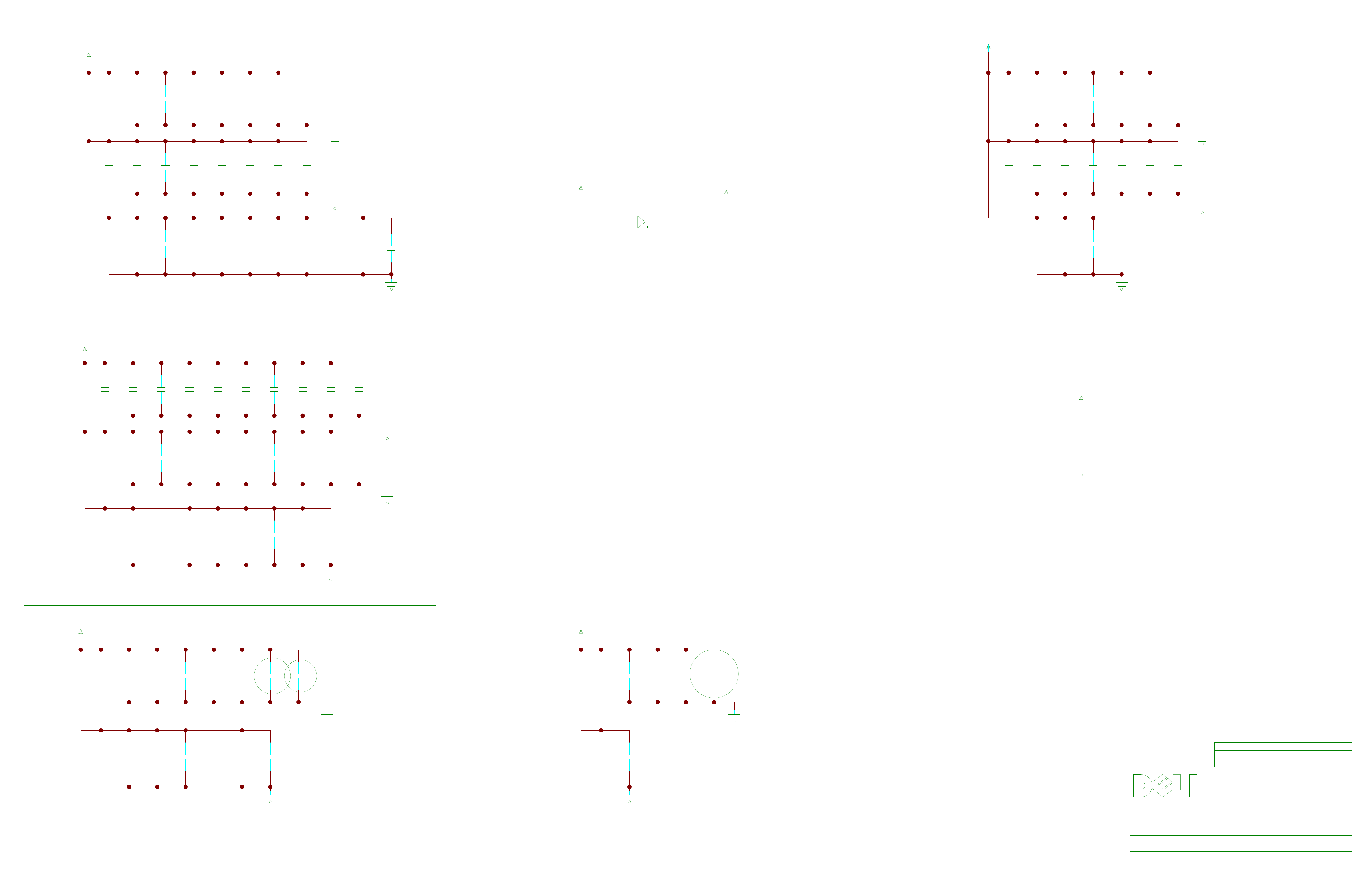

CPU decoupling

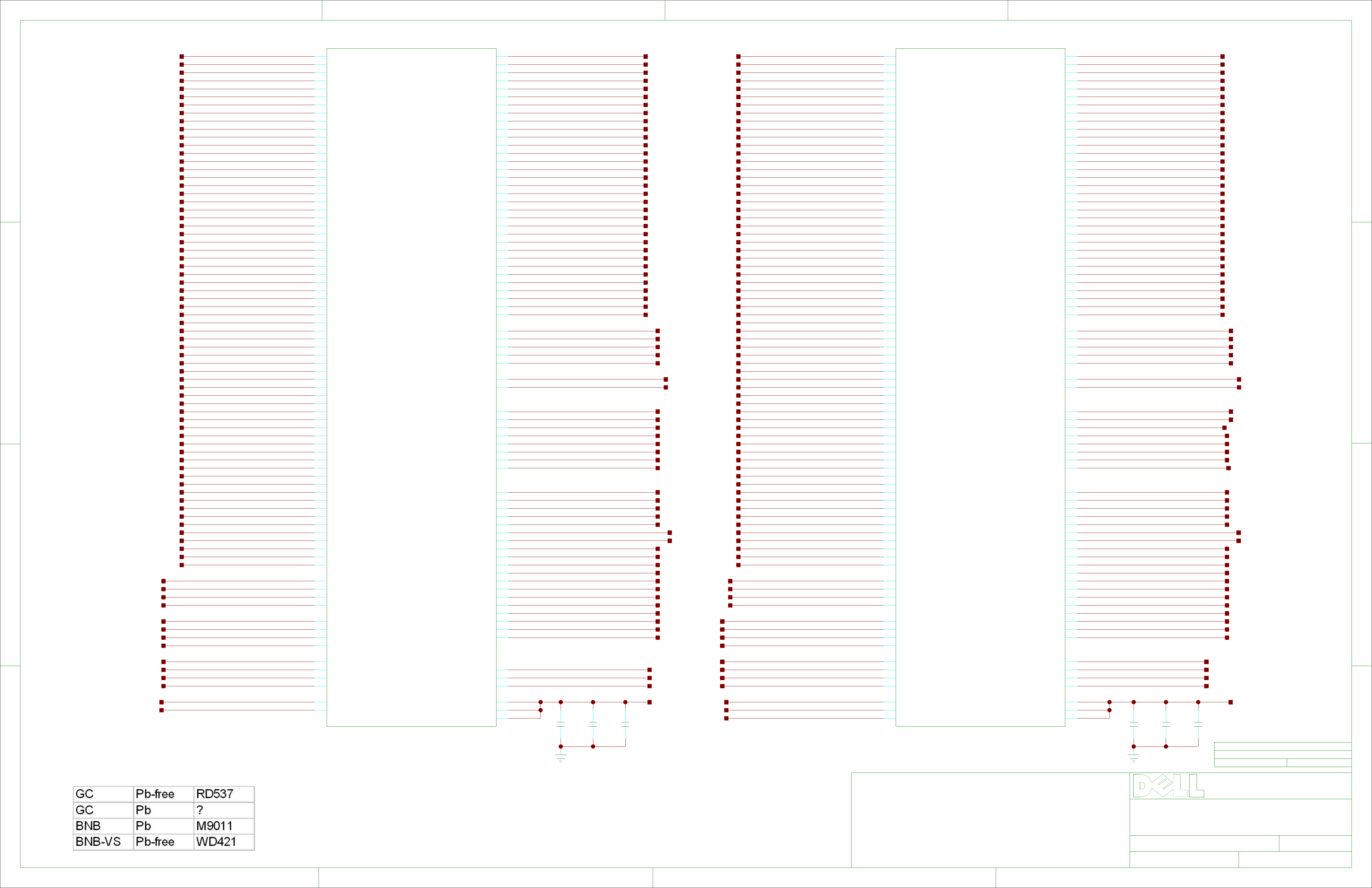

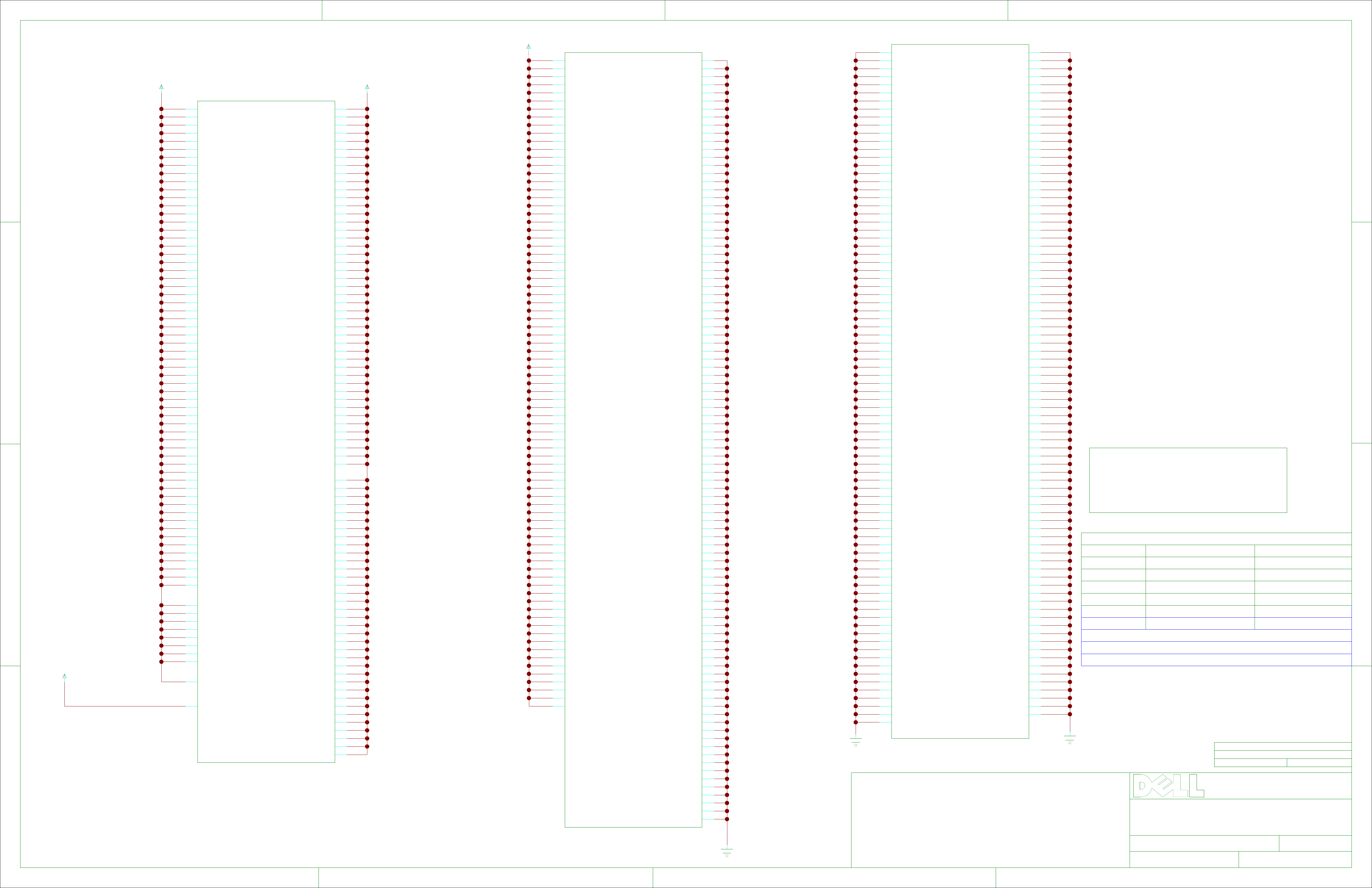

FB DIMMs (8)

Blank

FBD ResetPage 44.

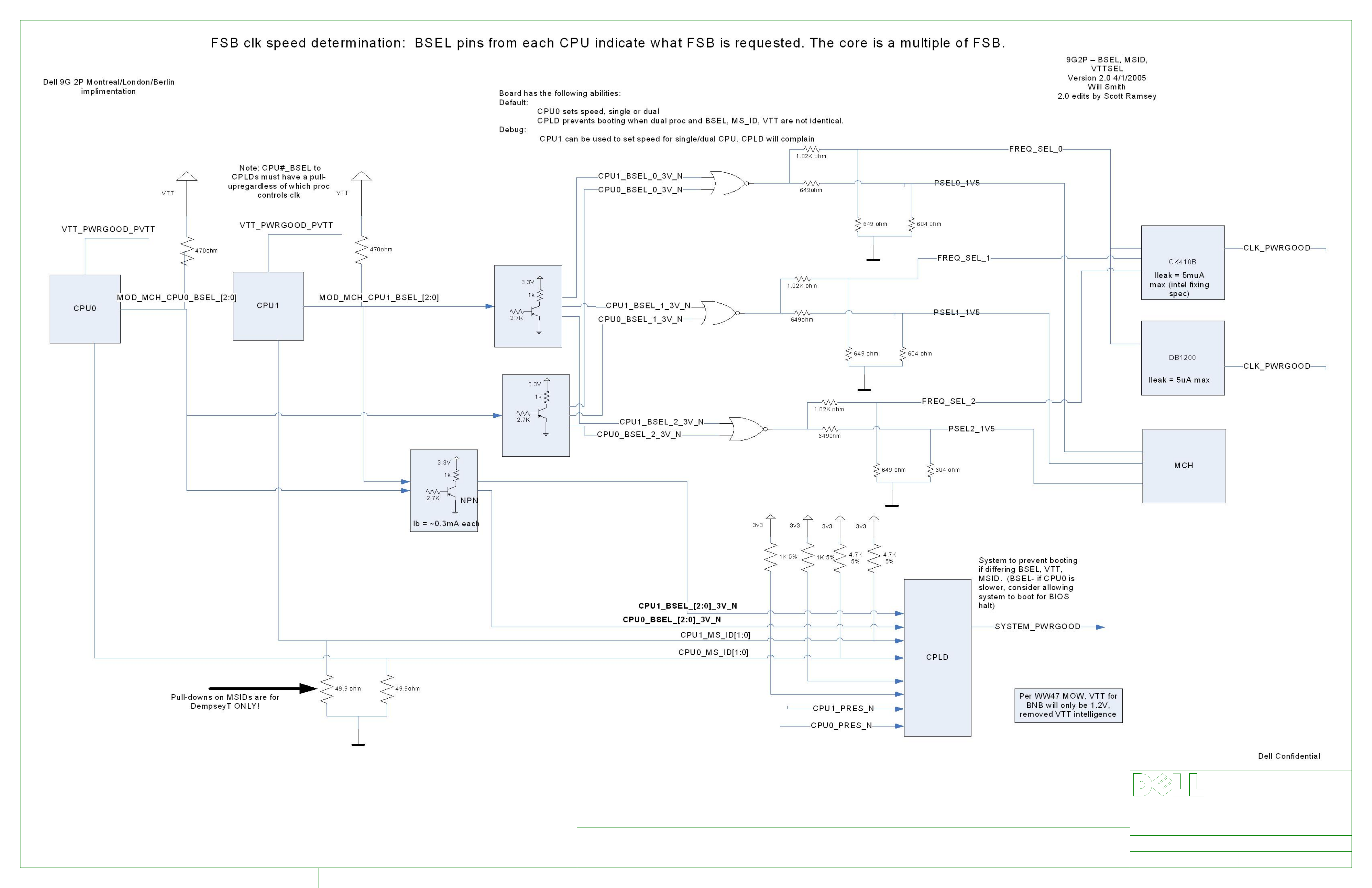

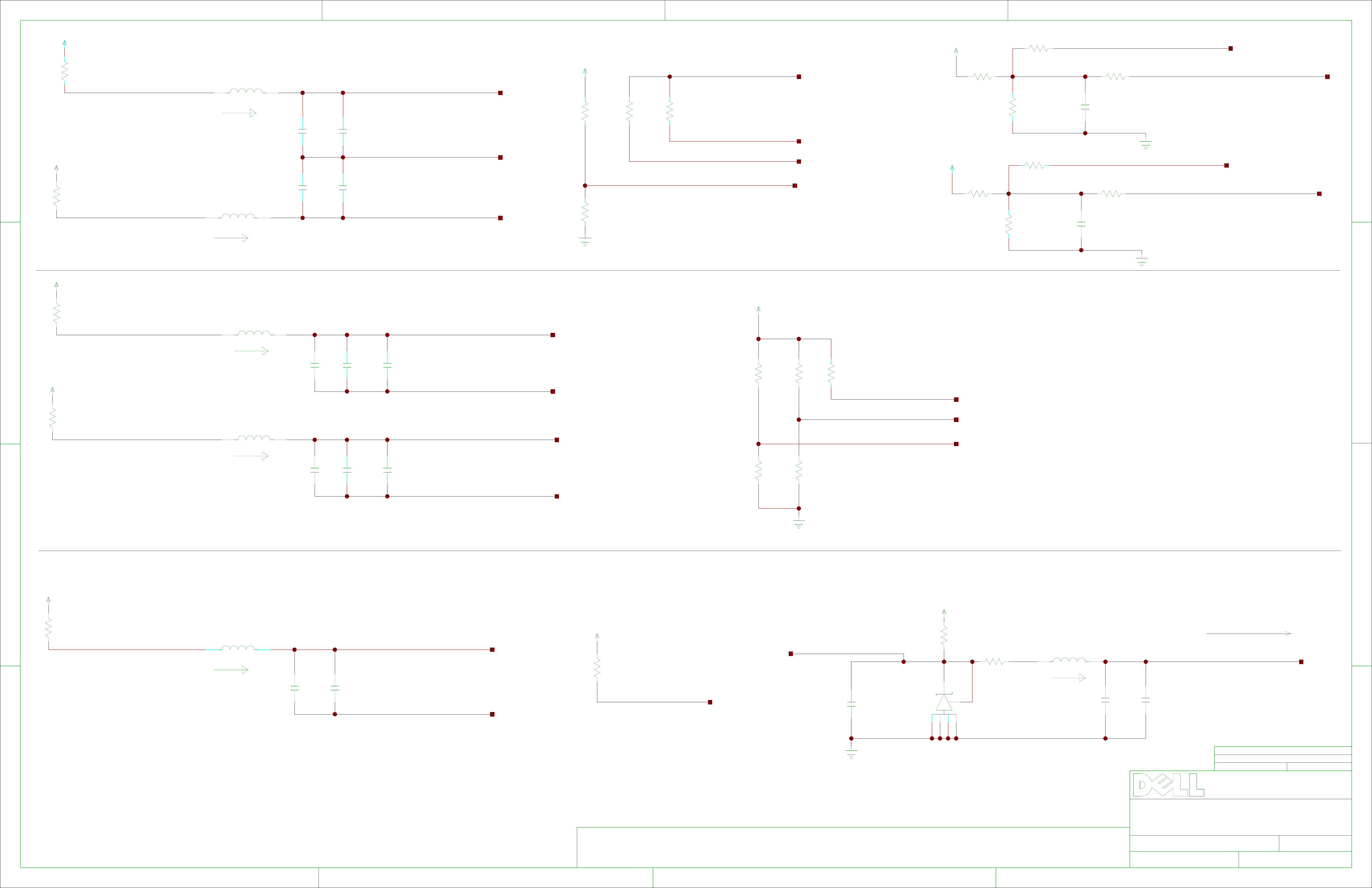

Clock Generator: CK410B

Clock buffer: DB1200

Clock buffer: DB800Page 48.

ESB2Page 49-57.

USB Connectors and ButtonsPage 58.

Floppy Connector

Blank (LAI Connectors if there is room)

SATA Connectors

Voltage Doubler and Intusion Detect

ESB2 I2C MUX and Header

Blank

Super I/O

TPM, PCI Reset, Jumpers

Firmware Hub

Coin Cell Battery

Sideplane (PERC5/I, Control Panel, IDE)

Risers (3)

Blank, PME to Wake on Page 77

Broadcom LOM 1

Broadcom LOM 2

LOM power switch

BMC

COM port

BMC I2C MUX and Header

San Marco Connectors (Mgmt, MII)

Rear ID, Cyclops

Fan Connectors and Tach

BMC - CPLD, master and slave

OmniIVu- CPLD and header

Video RN50

Video Output

VRDs

Power Connectors

Power LED

Power sequencing and VRD enable chaining

Ground Clips

Impedance Coupons (90D, 95D, 100D)

System powergood and Reset buffering

Second source CPLDs

Blank, strappings, SATA, OV/UV

+1.8V Current sense

APPROVED

JINTO JOSE02/25/2007

JINTO JOSEA00

1

2

3

4

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

Berlin MLK PWA (CTPM): XR362

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY

OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN

WHOLE OR IN PART AND MUST BE RETURNED TO DELL INC.

UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE

OF THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED

FOR SUCH USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE

LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

M2LB_Change_Note:

1 - 11, 13, 17, 24, 28, 29, 32 - 43,

45 - 51, 53, 54, 58 - 61, 64 - 66, 68, 70 - 81,

83, 86 - 88, 89, 90, 94, 95, 106, 108 - 128

PROPRIETARY NOTE

London MLK PWA (ROW): HX368London MLK PWA (CTPM): RU411

Berlin MLK PWA (ROW): TT740

PWB: JN309

SCH: HX601

London MLK ASSY: WY108

Berlin MLK ASSY: CR344

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

SHOBHIT CHAHAR

SHOBHIT CHAHAR

JINTO N JOSE

JINTO N JOSE

04/04/2007

04/04/2007

06/15/2007

06/15/2007

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

SCHEM, PLN, SV, PE2950, MLK

DWG NO.

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

INC.

ROUND ROCK,TEXAS

HX601

DATE

SHEET

9/7/2007 1 OF 136

09/07/2007229098

4

REV.

A00

DCBA

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

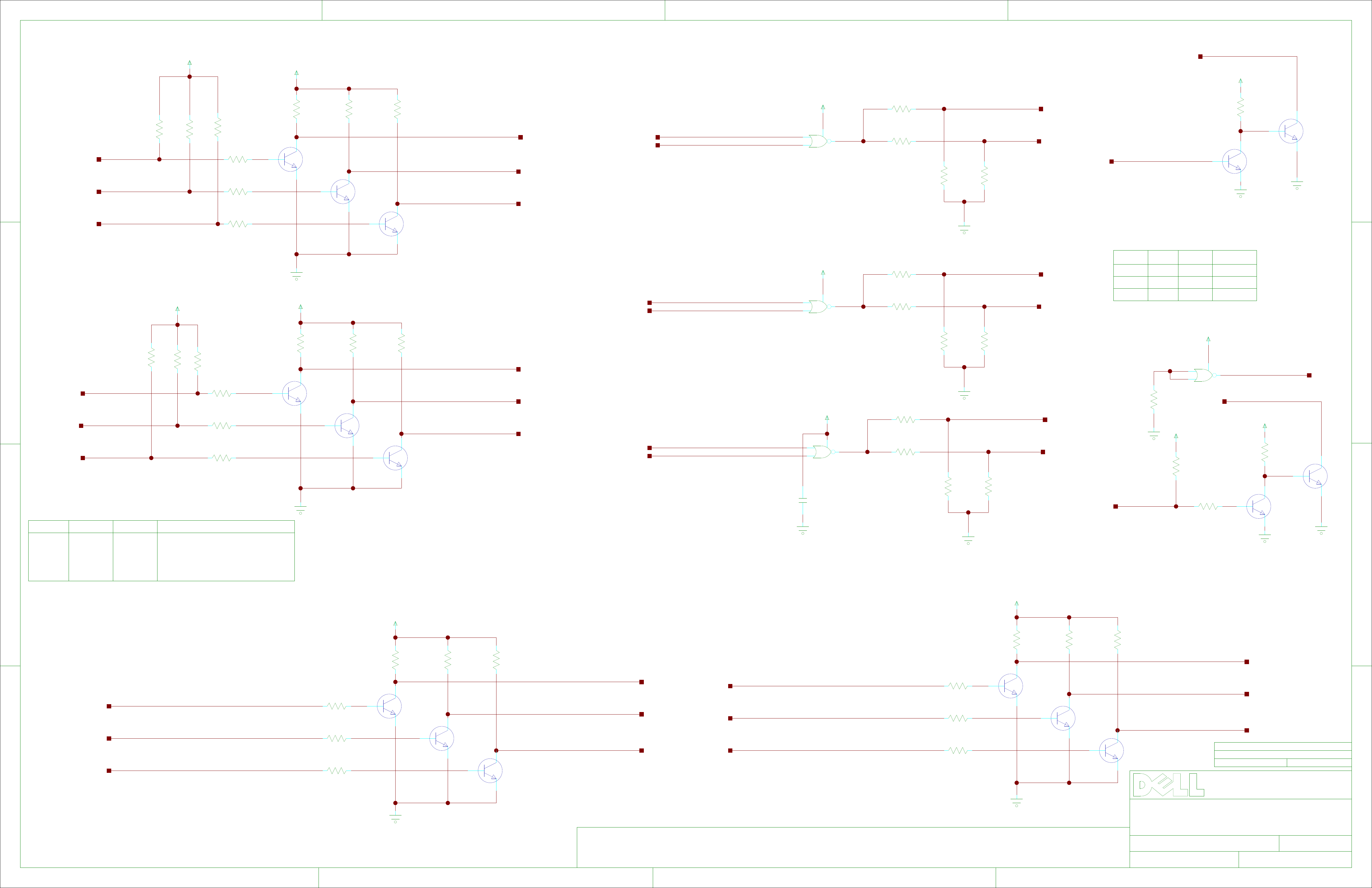

P19_DT9214_rt_update_block_diagram

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 2 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

P19_DT9214_rt_update_block_diagram

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 3 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 4 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 5 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 6 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

Powerup Timing- VRDs

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 7 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

Power up Timing - Chipset

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 8 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

9/7/2007 9 OF 136

DCBA

4

A00

A B C

D

1

1

2

2

3

3

4

JTAG Block Diagram

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

A00

9/7/2007 10 OF 136

DCBA

4

A B C

D

1

1

2

2

3

3

4

NOTE: this is not completely up to date

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

REV.

HX601

SHEET

A00

9/7/2007 11 OF 136

DCBA

4

1

2

3

A B C

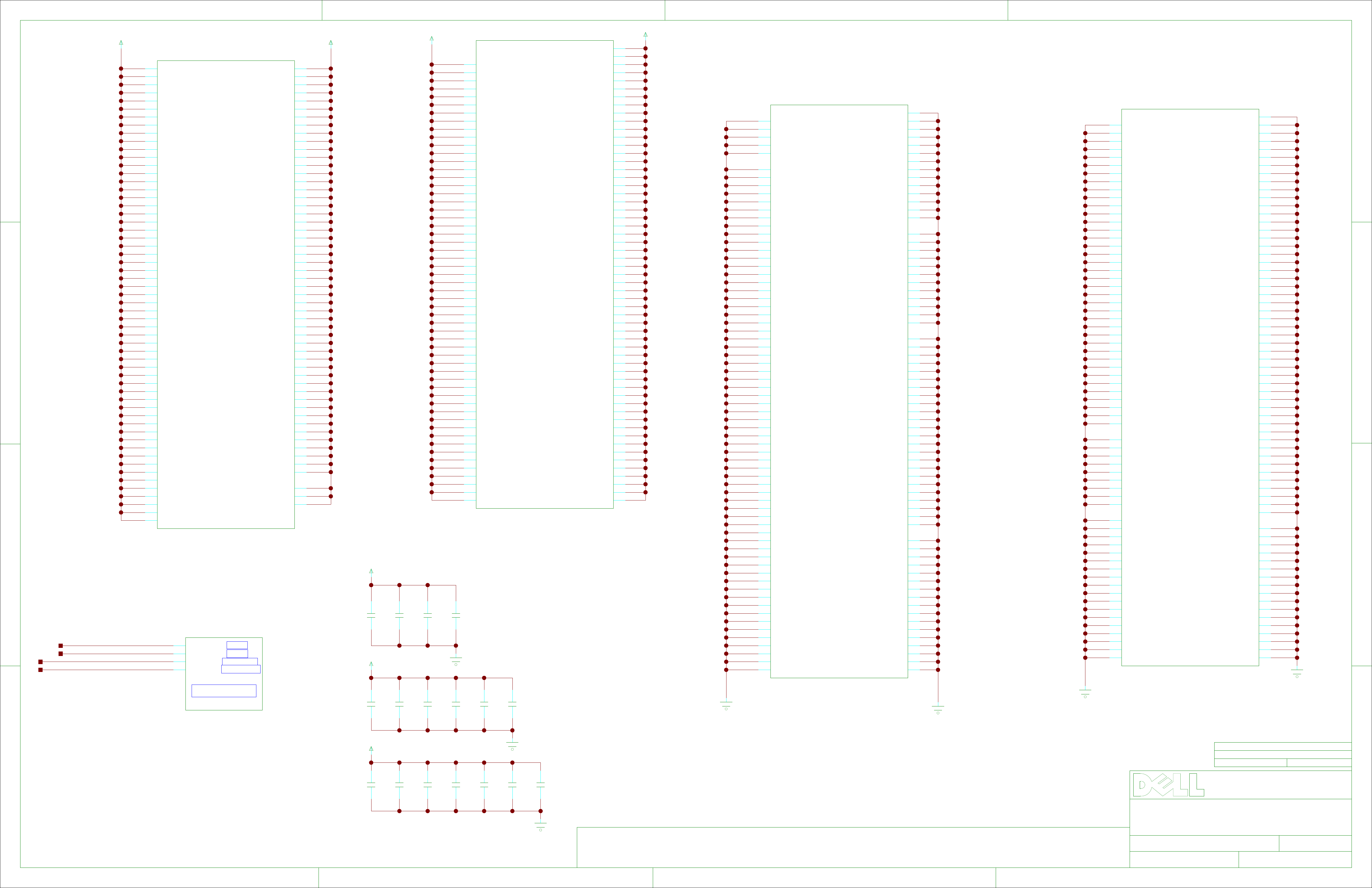

J_CPU0

MOD_MCH_FSB0_A16_N

22

MOD_MCH_FSB0_A15_N

22

MOD_MCH_FSB0_A14_N

22

MOD_MCH_FSB0_A13_N

22

MOD_MCH_FSB0_A12_N

22

MOD_MCH_FSB0_A11_N

22

MOD_MCH_FSB0_A10_N

22

MOD_MCH_FSB0_A9_N

22

MOD_MCH_FSB0_A8_N

22

MOD_MCH_FSB0_A7_N

22

MOD_MCH_FSB0_A6_N

22

MOD_MCH_FSB0_A5_N

22

MOD_MCH_FSB0_A4_N

22

MOD_MCH_FSB0_A3_N

22

MOD_MCH_FSB0_REQ_4_N

22

MOD_MCH_FSB0_REQ_3_N

22

MOD_MCH_FSB0_REQ_2_N

22

MOD_MCH_FSB0_REQ_1_N

22

MOD_MCH_FSB0_REQ_0_N

22

MOD_MCH_FSB0_ADSTB_0_N

22

MOD_MCH_FSB0_D15_N

22

MOD_MCH_FSB0_D14_N

22

MOD_MCH_FSB0_D13_N

22

MOD_MCH_FSB0_D12_N

22

MOD_MCH_FSB0_D11_N

22

MOD_MCH_FSB0_D10_N

22

MOD_MCH_FSB0_D9_N

22

MOD_MCH_FSB0_D8_N

22

MOD_MCH_FSB0_D7_N

22

MOD_MCH_FSB0_D6_N

22

MOD_MCH_FSB0_D5_N

22

MOD_MCH_FSB0_D4_N

22

MOD_MCH_FSB0_D3_N

22

MOD_MCH_FSB0_D2_N

22

MOD_MCH_FSB0_D1_N

22

MOD_MCH_FSB0_D0_N

22

MOD_MCH_FSB0_DBI_0_N

22

MOD_MCH_FSB0_DSTBN_0_N

22

MOD_MCH_FSB0_DSTBP_0_N

22

MOD_MCH_FSB0_D31_N

22

MOD_MCH_FSB0_D30_N

22

MOD_MCH_FSB0_D29_N

22

MOD_MCH_FSB0_D28_N

22

MOD_MCH_FSB0_D27_N

22

MOD_MCH_FSB0_D26_N

22

MOD_MCH_FSB0_D25_N

22

MOD_MCH_FSB0_D24_N

22

MOD_MCH_FSB0_D23_N

22

MOD_MCH_FSB0_D22_N

22

MOD_MCH_FSB0_D21_N

22

MOD_MCH_FSB0_D20_N

22

MOD_MCH_FSB0_D19_N

22

MOD_MCH_FSB0_D18_N

22

MOD_MCH_FSB0_D17_N

22

MOD_MCH_FSB0_D16_N

22

MOD_MCH_FSB0_DBI_1_N

22

MOD_MCH_FSB0_DSTBN_1_N

22

MOD_MCH_FSB0_DSTBP_1_N

22

W5

A16_N

V4

A15_N

V5

A14_N

U4

A13_N

U5

A12_N

T4

A11_N

U6

A10_N

T5

A9_N

R4

A8_N

M4

A7_N

L4

A6_N

L5

A5_N

P6

A4_N

M5

A3_N

J6

REQ_4_N

K6

REQ_3_N

M6

REQ_2_N

J5

REQ_1_N

K4

REQ_0_N

R6 AD5

ADSTB0_N ADSTB1_N

D11

D15_N

C12

D14_N

B12

D13_N

D8

D12_N

C11

D11_N

B10

D10_N

A11

D9_N

A10

D8_N

A7

D7_N

B7

D6_N

B6

D5_N

A5

D4_N

C6

D3_N

A4

D2_N

C5

D1_N

B4

D0_N

A8

DBI0_N

C8

DSTBN0_N

B9

DSTBP0_N

G15

D31_N

F15

D30_N

G14

D29_N

F14

D28_N

G13

D27_N

E13

D26_N

D13

D25_N

F12

D24_N

F11

D23_N

D10

D22_N

E10

D21_N

D7

D20_N

E9

D19_N

F9

D18_N

F8

D17_N

G9

D16_N

G11

DBI1_N

G12

DSTBN1_N

E12

DSTBP1_N

A35_N

A34_N

A33_N

A32_N

A31_N

A30_N

A29_N

A28_N

A27_N

A26_N

A25_N

A24_N

A23_N

A22_N

A21_N

A20_N

A19_N

A18_N

A17_N

D47_N

D46_N

D45_N

D44_N

D43_N

D42_N

D41_N

D40_N

D39_N

D38_N

D37_N

D36_N

D35_N

D34_N

D33_N

D32_N

DBI2_N

DSTBN2_N

DSTBP2_N

D63_N

D62_N

D61_N

D60_N

D59_N

D58_N

D57_N

D56_N

D55_N

D54_N

D53_N

D52_N

D51_N

D50_N

D49_N

D48_N

DBI3_N

DSTBN3_N

DSTBP3_N

INTEL LGA771 PINOUT

HETERO 2 OF 9

SILKSCREEN=CPU1

ADD*_PR288

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

AC5

AB5

AA5

AD6

AA4

Y4

Y6

W6

AB6

G22

D22

E22

G21

F21

E21

F20

E19

E18

F18

F17

G17

G18

E16

E15

G16

D19

G20

G19

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

B15

C14

C15

A14

D17

D20

C20

A16

C17

MOD_MCH_FSB0_A35_N

MOD_MCH_FSB0_A34_N

MOD_MCH_FSB0_A33_N

MOD_MCH_FSB0_A32_N

MOD_MCH_FSB0_A31_N

MOD_MCH_FSB0_A30_N

MOD_MCH_FSB0_A29_N

MOD_MCH_FSB0_A28_N

MOD_MCH_FSB0_A27_N

MOD_MCH_FSB0_A26_N

MOD_MCH_FSB0_A25_N

MOD_MCH_FSB0_A24_N

MOD_MCH_FSB0_A23_N

MOD_MCH_FSB0_A22_N

MOD_MCH_FSB0_A21_N

MOD_MCH_FSB0_A20_N

MOD_MCH_FSB0_A19_N

MOD_MCH_FSB0_A18_N

MOD_MCH_FSB0_A17_N

MOD_MCH_FSB0_ADSTB_1_N

MOD_MCH_FSB0_D47_N

MOD_MCH_FSB0_D46_N

MOD_MCH_FSB0_D45_N

MOD_MCH_FSB0_D44_N

MOD_MCH_FSB0_D43_N

MOD_MCH_FSB0_D42_N

MOD_MCH_FSB0_D41_N

MOD_MCH_FSB0_D40_N

MOD_MCH_FSB0_D39_N

MOD_MCH_FSB0_D38_N

MOD_MCH_FSB0_D37_N

MOD_MCH_FSB0_D36_N

MOD_MCH_FSB0_D35_N

MOD_MCH_FSB0_D34_N

MOD_MCH_FSB0_D33_N

MOD_MCH_FSB0_D32_N

MOD_MCH_FSB0_DBI_2_N

MOD_MCH_FSB0_DSTBN_2_N

MOD_MCH_FSB0_DSTBP_2_N

MOD_MCH_FSB0_D63_N

MOD_MCH_FSB0_D62_N

MOD_MCH_FSB0_D61_N

MOD_MCH_FSB0_D60_N

MOD_MCH_FSB0_D59_N

MOD_MCH_FSB0_D58_N

MOD_MCH_FSB0_D57_N

MOD_MCH_FSB0_D56_N

MOD_MCH_FSB0_D55_N

MOD_MCH_FSB0_D54_N

MOD_MCH_FSB0_D53_N

MOD_MCH_FSB0_D52_N

MOD_MCH_FSB0_D51_N

MOD_MCH_FSB0_D50_N

MOD_MCH_FSB0_D49_N

MOD_MCH_FSB0_D48_N

MOD_MCH_FSB0_DBI_3_N

MOD_MCH_FSB0_DSTBN_3_N

MOD_MCH_FSB0_DSTBP_3_N

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

Processor 0 heatsink retention modules

ST1

NC_MOD_MCH_ST1_1

NC_MOD_MCH_ST1_2

10

1

2

3

4

5

6

7

8

9

NC1

NC2

GND_V1

GND_V2

GND_V3

GND_V4

GND_V5

GND_V6

GND_V7

GND_V8

BRACKET RETENTION

SUPPORT, GROUNDED

ADD1=ADD*_JC664

ADD2=ADD*_JC664

ADD3=ADD*_JC664

NOTE : heatsink retention clips needing a single trace to each pin, not solid

connection concern doesn't apply to the CPU HS brackets

Nocona-T Dempsy-T Dempsy/WoodcrestPlatform Change

requiredrequired

Use "LE" Blackford

Pull down reserved pin F6

Pull down MS_ID[1:0] to Vss

Isolate LL_ID[1:0]

Manually set VR loadline

required

optional

optional

optional

required required

required

required

required

required

Mechanical Parts on the following pages:

12, 16

Socket J part numbers:

DescriptionDell p/n

Y9236

P9381

Leaded Socket J - SKT,LGA,771P,G,SF,ZIF,SL,SM

Vendors:

Foxconn PN: PE077107-1041-01

Tyco PN: 1747890-1

Lead-free socket J - SKT,LGA,771P,G,SF,ZIF,SL,SM

Vendors:

Foxconn PN: PE077127-1041-01

Tyco PN: 1-1747890-1

D

CPU Heatsink

frame screws

ADD4=ADD*_RC078

ADD5=ADD*_RC078

ADD6=ADD*_RC078

ADD7=ADD*_RC078

1

CPU Heatsink

clip asm

ADD8=ADD*_H3668

ADD9=ADD*_H3668

2

No use LGA771Use LGA775

No use real blackford

No treat as reserved and leave pin No Connect

No revert back to POR

No revert back to POR

No revert back to POR

3

4

ROOM=PROC0

ECAD NOTE: Please put triangle pointing to pin1

CPU0_REG

NC_CPU0_REG_1 NC_CPU0_REG_2

1 2

COMMON NEG

REG07 A NGO

COUPON TEST

ROOM=PROC0

PROCESSOR 0

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

C

TITLE

DWG NO.

DATE

MODULE:

DESC:

REV: OF

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

HX601

SHEET

12 OF 1369/7/2007

DBA

CPUS,FSB,NB,XDP0,XDP1

SEC

REV.

A00

MCH

211

4

A B C

D

9-7-2007_16:36

1

2

3

13,117

13,117

13,117

13,117

13,117

13,117

13,117

15

15,17,21,54

NP

X

1 2

C8600

15,95,117,128

MLK: Routed to CPLD for CPU Identification

13,95,117,128

FSB0_VID_6

FSB0_VID_5

FSB0_VID_4

FSB0_VID_3

FSB0_VID_2

FSB0_VID_1

FSB0_VID_0

MOD_MCH_CPU0_BSEL_2

20

MOD_MCH_CPU0_BSEL_1

20

MOD_MCH_CPU0_BSEL_0

20

MOD_MCH_FSB0_GTLREF_DATA_CORE1

15

MOD_MCH_FSB0_GTLREF_ADD_CORE1

15

MOD_MCH_FSB0_GTLREF_DATA_CORE0

15

MOD_MCH_FSB0_GTLREF_ADD_CORE0

CPU_PWRGOOD

15

15

15

100pF

50V-5%

15

15

15

15

15

13,117

13,117

13,117

13,117

13,117

13,117

13,117

15

15

15

117

117

117

117

13,89

13,89

**

CPU0_VCC_DIE_SENSE

CPU0_VCC_DIE_SENSE2

CPU0_VSS_DIE_SENSE

CPU0_VSS_DIE_SENSE2

CPU0_PRES_N

CPU0_THERMD_A_1

89

CPU0_THERMD_A_2

89

CPU0_THERMD_C_12

CPU0_THERMD_C_12

*

NC_MOD_MCH_FSB0_DBR_N

*

NC_MOD_MCH_FSB0_ITP_CLK1

*

NC_MOD_MCH_FSB0_ITP_CLK0

NC_MOD_MCH_FSB0_RSVD_Y1

MOD_MCH_FSB0_TESTBUS

15

MOD_MCH_FSB0_COMP_3

MOD_MCH_FSB0_COMP_1

MOD_MCH_FSB0_COMP_0

FSB0_VID_6

FSB0_VID_5

FSB0_VID_4

FSB0_VID_3

FSB0_VID_2

FSB0_VID_1

FSB0_VID_0

FSB0_VID_SELECT

MOD_MCH_V_VTT_FSB0_VCCA

MOD_MCH_V_VSS_FSB0_VSSA

MOD_MCH_V_1V5_FSB0_VCCPLL

21

R4248

R4247

MOD_MCH_FSB0_COMP_5

MOD_MCH_FSB0_COMP_4

MOD_MCH_FSB0_COMP_2

511-1%

1 2

MOD_MCH_FSB0_COMP_7

MOD_MCH_FSB0_COMP_6

511-1%

R4249

1 2

+CPU_VTT

21

R4250

511-1%

511-1%

R4251

1 2

21

R4252

511-1%

+CPU_VTT

511-1%

R26

R4253

G30

H30

G29

F2

H2

G10

H1

N1

AE3

Y3

T2

J2

R1

G2

T1

A13

AM5

AL4

AK4

AL6

AM3

AL5

AM2

AN7

A23

B23

D23

C23

AN3

AL8

AN4

AL7 AM6

AE8

AL1

AJ7

AK1

AH7

AC2

AJ3

AK3

Y1

AH2

511-1%

1 2

J_CPU0

BSEL2

BSEL1

BSEL0

GTLREF_DATA_CORE1

GTLREF_ADD_CORE1

GTLREF_DATA_CORE0

GTLREF_ADD_CORE0

PWRGOOD

COMP7

COMP6

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

VID6

VID5

VID4

VID3

VID2

VID1

VID0

VID_SELECT

VCCA

VSSA

VCCPLL

VCCIOPLL

VCC_DIE_SENSE

VCC_DIE_SENSE2

VSS_DIE_SENSE

VSS_DIE_SENSE2 VTTPWRGD

SKTOCC_N

THERMDA

THERMDA2

THERMDC

THERMDC2

DBR_N

ITP_CLK1

ITP_CLK0

BOOT_SELECT

TEST_BUS

INTEL LGA771 PINOUT

HETERO 3 OF 9

SILKSCREEN=CPU1

51-5%

1 2

MOD_MCH_XDP0_TDI_CPU0

MLK: Pull Up Added on XDP0_TDI_CPU0 signal

VTT_A25

VTT_A26

VTT_B25

VTT_B26

VTT_B27

VTT_B28

VTT_B29

VTT_B30

VTT_C25

VTT_C26

VTT_C27

VTT_C28

VTT_C29

VTT_C30

VTT_D25

VTT_D26

VTT_D27

VTT_D28

VTT_D29

VTT_D30

VTT_E30/NC_E30

VTT_F30/NC_F30

VTT_OUT_1

VTT_OUT_0

VTT_SEL

LL_ID1

LL_ID0

MS_ID1

MS_ID0

A25

A26

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

E30

F30

AA1

J1

F27

AA2

V2

V1

W1

13,21

+CPU_VTT

MOD_MCH_VTT_CPU_PWRGOOD

NC_MOD_MCH_FSB0_VTT_OUT_1

NC_MOD_MCH_FSB0_VTT_OUT_0

MOD_MCH_VTT_SEL_CPU0

MOD_MCH_CPU0_LL_ID1_R

MOD_MCH_CPU0_LL_ID0_R

CPU0_MS_ID1

CPU0_MS_ID0

15,17,20

13,95,128

13,95,128

15,22

45

45

15,17,54

15,17,54

15,17,20

15,17,54

15,17,54

15,17,54

15,17,54

15,17,54

17,21

13,21

17,21,24

17,21,24

15,20

15,17,54

15,20

15,20

MOD_MCH_FSB0_TESTHI_11

15

MOD_MCH_FSB0_TESTHI_10

15

21

21

15

15

MLK: VTT_SEL Signal going to VTT REG Ckt

109

R5498

0-5%

12

R5499

12

0-5%

MOD_MCH_FSB0_BPMB_2_N

MOD_MCH_FSB0_BPMB_3_N

MOD_MCH_FSB0_TESTHI_02_07

MOD_MCH_FSB0_TESTHI_00_01

CPU0_LL_ID1

Depop for dempsyT

MOD_MCH_XDP0_TCK0

MOD_MCH_XDP0_TDI_CPU0

MOD_MCH_XDP0_TDO_CPU0

21

MOD_MCH_XDP0_TMS

MOD_MCH_XDP0_TRST_N

MOD_MCH_CPU0_IERR_N

FSB_FERR_N

MOD_MCH_CPU0_PROCHOT_N

MOD_MCH_CPU0_THERMTRIP_N

CPU0_LL_ID0

MOD_MCH_FSB0_RST_N

MOD_MCH_FSB0_RSP_N

22

MOD_MCH_FSB0_BPRI_N

22

MOD_MCH_FSB0_TRDY_N

22

MOD_MCH_FSB0_DEFER_N

22

MOD_MCH_FSB0_RS_0_N

22

MOD_MCH_FSB0_RS_1_N

22

22

MOD_MCH_FSB0_RS_2_N

CK_333M_CPU0_N

CK_333M_CPU0_P

FSB_SMI_N

FSB_A20M_N

MOD_MCH_CPU_FORCEPR_N

FSB_INTR

FSB_NMI

FSB_IGNNE_N

FSB_STPCLK_N

FSB_INIT_N

117

117

+3.3V

G23

RESET_N

H4

RSP_N

G8

BPRI_N

E3

TRDY_N

G7

DEFER_N

B3

RS0_N

F5

RS1_N

A3

RS2_N

G28

BCLK1

P2

SMI_N

K3

A20M_N

AK6

FORCEPR_N

K1

LINT0

L1

LINT1

N2

IGNNE_N

M3

STPCLK_N

P3

INIT_N

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST_N

AB2

IERR_N

R3

FERR/PBE_N

AL2

PROCHOT_N

M2

THRMTRIP_N

L2

TESTHI11

P1

TESTHI10

G4

TESTHI09/BPMB2_N

G3

TESTHI08/BPMB3_N

F24

TESTHI07

G24

TESTHI06

G26

TESTHI05

G27

TESTHI04

G25

TESTHI03

F25

TESTHI02

W3

TESTHI01

F26

TESTHI00

J_CPU0

INTEL LGA771 PINOUT

HETERO 1 OF 9

SILKSCREEN=CPU1

J_CPU0

Clovertown

INTEL LGA771 PINOUT

HETERO 4 OF 9

SILKSCREEN=CPU1

ADS_N

BNR_N

HIT_N

DBSY_N

DRDY_N

HITM_N

LOCK_N

BINIT_N

MCERR_N

AP1_NBCLK0

AP0_N

BR1_N

BR0_N

DP3_N

DP2_N

DP1_N

DP0_N

BPM5_N

BPM4_N

BPM3_N

BPM2_N

BPM1_N

BPM0_N

D2

C2

D4

B2

C1

E4

C3

AD3

AB3

U3F28

U2

H5

F3

J17

H16

H15

J16

AG3

AF2

AG2

AD2

AJ1

AJ2

RSVD_C9/BPMB1_N

RSVD_E1/NC_E1

RSVD_W2/TESTIN1

MOD_MCH_FSB0_BPM_5_N

MOD_MCH_FSB0_BPM_4_N

MOD_MCH_FSB0_BPM_3_N

MOD_MCH_FSB0_BPM_2_N

MOD_MCH_FSB0_BPM_1_N

MOD_MCH_FSB0_BPM_0_N

RSVD_A20

RSVD_AC4

RSVD_AE4

RSVD_AE6

RSVD_B13

RSVD_D1

RSVD_D14

RSVD_D16

RSVD_E23

RSVD_E24

RSVD_E5

RSVD_E6

RSVD_E7

RSVD_F23

RSVD_F29

RSVD_F6

PECI

RSVD_G6

RSVD_J3

RSVD_N4

RSVD_N5

RSVD_P5

RSVD_AN5

RSVD_AN6

MOD_MCH_FSB0_ADS_N

MOD_MCH_FSB0_BNR_N

MOD_MCH_FSB0_HIT_N

MOD_MCH_FSB0_DBSY_N

MOD_MCH_FSB0_DRDY_N

MOD_MCH_FSB0_HITM_N

MOD_MCH_FSB0_LOCK_N

MOD_MCH_FSB0_BINIT_N

MOD_MCH_FSB0_MCERR_N

MOD_MCH_FSB0_AP_1_N

MOD_MCH_FSB0_AP_0_N

MOD_MCH_FSB0_BREQ_1_N

MOD_MCH_FSB0_BREQ_0_N

MOD_MCH_FSB0_DP_3_N

MOD_MCH_FSB0_DP_2_N

MOD_MCH_FSB0_DP_1_N

MOD_MCH_FSB0_DP_0_N

A20

AC4

AE4

AE6

B13

C9

D1

D14

D16

E23

E24

E1

E5

E6

E7

F23

F29

F6

G5

G6

J3

N4

N5

P5

AN5

AN6

W2

NC_MOD_MCH_FSB0_RSVD_A20

NC_MOD_MCH_FSB0_RSVD_AC24

NC_MOD_MCH_FSB0_RSVD_AE24

NC_MOD_MCH_FSB0_RSVD_AE6

NC_MOD_MCH_FSB0_RSVD_B13

NC_MOD_MCH_FSB0_RSVD_D1

NC_MOD_MCH_FSB0_RSVD_D14

NC_MOD_MCH_FSB0_RSVD_D16

NC_MOD_MCH_FSB0_RSVD_E23

NC_MOD_MCH_FSB0_RSVD_E24

NC_MOD_MCH_FSB0_RSVD_E1

NC_MOD_MCH_FSB0_RSVD_E5

NC_MOD_MCH_FSB0_RSVD_E6

NC_MOD_MCH_FSB0_RSVD_E7

NC_MOD_MCH_FSB0_RSVD_F23

NC_MOD_MCH_FSB0_RSVD_F29

PECI_CPU

NC_MOD_MCH_FSB0_RSVD_G6

NC_MOD_MCH_FSB0_RSVD_J3

NC_MOD_MCH_FSB0_RSVD_N4

NC_MOD_MCH_FSB0_RSVD_N5

NC_MOD_MCH_FSB0_RSVD_P5

NC_MOD_MCH_FSB0_RSVD_AN5

NC_MOD_MCH_FSB0_RSVD_AN6

MOD_MCH_CPU0_TESTIN

22

22

22

22

22

22

22

22

22

22

22

15,22

15,22

22

22

22

22

21,22

21,22

21

21

21

21

MOD_MCH_FSB0_BPMB_1_N

MOD_MCH_FSB0_F6_PD_DEMPSY_T

17,90

14,15

Don't care for NoconaT

Populate for DempseyT

Depop for Dempsey/Woodcrest

NP

R5495

X

2 1

1

2

21

3

49.9-1%

4

Do not place VTT_SEL or CPU_PRES_N on 3v3Aux, VTT_SEL is used in main domain VRD logic,

CPU_PRES_N is used on 3v3 part during development.

The rest are placed on 3v3 to simplify routing, no need for 3v3 aux near CPU.ort (leave LL_ID float)

ECAD: VCC/VSS_DIE_SENSE LINES

Route DIFF @ 25mil thick /5 mil space, same length, 20mil to other sigs

Follow PDG 0.7 256-257

ECAD: CPU THERMD_C_12 to be routed as 2 nets, differentially with A_1 and A_2. Only bring nets together as they enter sensor

* NOTE: DBR and ITP_CLK are outputs from a in-socket debugger- Dell has no plans for this debug model.mpsey-T support8

** NOTE: WW10 MOW documents that bootselect is being removed

and to leave pin floating

ROOM=PROC0

13,95,117,128

13,95,128

13,95,128

CPU0_PRES_N

CPU0_MS_ID1

CPU0_MS_ID0

R211

1 2

4.7K-5%

R4829

NP

R5503

X

1 2

2 1

R4828

4.7K-5%

1 2

NP

R5502

X

49.9-1%

2 1

Depop for dempsyT

4.7K-5%49.9-1%

Pop for DempseyT

PROCESSOR 0

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

M2LB_Change_Note:

Changed PECI_CPU1 to PECI_CPU.

TITLE

SCHEM, PLN, SV, PE2950, MLK

DWG NO.

HX601

DATE

MODULE:

DESC:

REV: OF

CPUS,FSB,NB,XDP0,XDP1

SEC

INC.

ROUND ROCK,TEXAS

REV.

A00

SHEET

13 OF 1369/7/2007

MCH

211

4

C

DBA

A B C

D

1

2

3

21

13,15

NC_J_CPU0_A24.

NC_J_CPU0_E29

MOD_MCH_FSB0_BPMB_0_N

MOD_MCH_CPU0_TESTIN

AA8

AB8

AC23

AC24

AC25

AC26

AC27

AC28

AC29

AC30

AC8

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD8

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AE9

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

AF8

AF9

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

AG8

AG9

AH11

VCC_AA8

VCC_AB8

VCC_AC23

VCC_AC24

VCC_AC25

VCC_AC26

VCC_AC27

VCC_AC28

VCC_AC29

VCC_AC30

VCC_AC8

VCC_AD23

VCC_AD24

VCC_AD25

VCC_AD26

VCC_AD27

VCC_AD28

VCC_AD29

VCC_AD30

VCC_AD8

VCC_AE11

VCC_AE12

VCC_AE14

VCC_AE15

VCC_AE18

VCC_AE19

VCC_AE21

VCC_AE22

VCC_AE23

VCC_AE9

VCC_AF11

VCC_AF12

VCC_AF14

VCC_AF15

VCC_AF18

VCC_AF19

VCC_AF21

VCC_AF22

VCC_AF8

VCC_AF9

VCC_AG11

VCC_AG12

VCC_AG14

VCC_AG15

VCC_AG18

VCC_AG19

VCC_AG21

VCC_AG22

VCC_AG25

VCC_AG26

VCC_AG27

VCC_AG28

VCC_AG29

VCC_AG30

VCC_AG8

VCC_AG9

VCC_AH11

SILKSCREEN=CPU1

A24

E29

G1

U1

J_CPU0

INTEL LGA771 PINOUT

HETERO 5 OF 9

J_CPU0

VSS_A24/RSVD

VSS_E29/RSVD

VSS_G1/BPMB0_N

VSS_U1/TESTIN2

Clovertown

INTEL LGA771 PINOUT

HETERO 9 OF 9

VCC_AH12

VCC_AH14

VCC_AH15

VCC_AH18

VCC_AH19

VCC_AH21

VCC_AH22

VCC_AH25

VCC_AH26

VCC_AH27

VCC_AH28

VCC_AH29

VCC_AH30

VCC_AH8

VCC_AH9

VCC_AJ11

VCC_AJ12

VCC_AJ14

VCC_AJ15

VCC_AJ18

VCC_AJ19

VCC_AJ21

VCC_AJ22

VCC_AJ25

VCC_AJ26

VCC_AJ8

VCC_AJ9

VCC_AK11

VCC_AK12

VCC_AK14

VCC_AK15

VCC_AK18

VCC_AK19

VCC_AK21

VCC_AK22

VCC_AK25

VCC_AK26

VCC_AK8

VCC_AK9

VCC_AL11

VCC_AL12

VCC_AL14

VCC_AL15

VCC_AL18

VCC_AL19

VCC_AL21

VCC_AL22

VCC_AL25

VCC_AL26

VCC_AL29

VCC_AL30

VCC_AL9

VCC_AM11

VCC_AM12

AH12

AH14

AH15

AH18

AH19

AH21

AH22

AH25

AH26

AH27

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL9

AM11

AM12

M23

M24

M25

M26

M27

M28

M29

M30

M8

N23

N24

N25

N26

N27

N28

N29

N30

N8

P8

R8

T23

T24

T25

T26

T27

T28

T29

T30

T8

U23

U24

U25

U26

U27

U28

U29

U30

U8

V8

W23

W24

W25

W26

W27

W28

W29

W30

W8

Y8

Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

+CPU_VID0

A12

A15

A18

A2

A21

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AE5

AE7

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

AG10

AG13

AG16

AG17

VSS_A12

VSS_A15

VSS_A18

VSS_A2

VSS_A21

VSS_A6

VSS_A9

VSS_AA23

VSS_AA24

VSS_AA25

VSS_AA26

VSS_AA27

VSS_AA28

VSS_AA29

VSS_AA3

VSS_AA30

VSS_AA6

VSS_AA7

VSS_AB1

VSS_AB23

VSS_AB24

VSS_AB25

VSS_AB26

VSS_AB27

VSS_AB28

VSS_AB29

VSS_AB30

VSS_AB7

VSS_AC3

VSS_AC6

VSS_AC7

VSS_AD4

VSS_AD7

VSS_AE10

VSS_AE13

VSS_AE16

VSS_AE17

VSS_AE2

VSS_AE20

VSS_AE24

VSS_AE25

VSS_AE26

VSS_AE27

VSS_AE28

VSS_AE29

VSS_AE30

VSS_AE5

VSS_AE7

VSS_AF10

VSS_AF13

VSS_AF16

VSS_AF17

VSS_AF20

VSS_AF23

VSS_AF24

VSS_AF25

VSS_AF26

VSS_AF27

VSS_AF28

VSS_AF29

VSS_AF3

VSS_AF30

VSS_AF6

VSS_AF7

VSS_AG10

VSS_AG13

VSS_AG16

VSS_AG17

SILKSCREEN=CPU1

J_CPU0

INTEL LGA771 PINOUT

HETERO 7 OF 9

VSS_AG20

VSS_AG23

VSS_AG24

VSS_AG7

VSS_AH1

VSS_AH10

VSS_AH13

VSS_AH16

VSS_AH17

VSS_AH20

VSS_AH23

VSS_AH24

VSS_AH3

VSS_AH6

VSS_AJ10

VSS_AJ13

VSS_AJ16

VSS_AJ17

VSS_AJ20

VSS_AJ23

VSS_AJ24

VSS_AJ27

VSS_AJ28

VSS_AJ29

VSS_AJ30

VSS_AJ4

VSS_AK10

VSS_AK13

VSS_AK16

VSS_AK17

VSS_AK2

VSS_AK20

VSS_AK23

VSS_AK24

VSS_AK27

VSS_AK28

VSS_AK29

VSS_AK30

VSS_AK5

VSS_AK7

VSS_AL10

VSS_AL13

VSS_AL16

VSS_AL17

VSS_AL20

VSS_AL23

VSS_AL24

VSS_AL27

VSS_AL28

VSS_AL3

VSS_AM1

VSS_AM10

VSS_AM13

VSS_AM16

VSS_AM17

VSS_AM20

VSS_AM23

VSS_AM24

VSS_AM27

VSS_AM28

VSS_AM4

VSS_AM7

VSS_AN01

VSS_AN02

VSS_AN10

VSS_AN13

VSS_AN16

AG20

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AL3

AM1

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AM4

AM7

AN1

AN2

AN10

AN13

AN16

AN17

AN20

AN23

AN24

B1

B11

B14

B17

B20

B24

B8

B5

C10

C13

C16

C19

C22

C24

C4

C7

D12

D15

D18

D21

D24

D3

D5

D6

D9

E11

E14

E17

E2

E20

E25

E26

E27

E28

E8

F1

F10

F13

F16

F19

F22

F4

F7

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

H29

VSS_AN17

VSS_AN20

VSS_AN23

VSS_AN24

VSS_B1

VSS_B11

VSS_B14

VSS_B17

VSS_B20

VSS_B24

VSS_B5

VSS_B8

VSS_C10

VSS_C13

VSS_C16

VSS_C19

VSS_C22

VSS_C24

VSS_C4

VSS_C7

VSS_D12

VSS_D15

VSS_D18

VSS_D21

VSS_D24

VSS_D3

VSS_D5

VSS_D6

VSS_D9

VSS_E11

VSS_E14

VSS_E17

VSS_E2

VSS_E20

VSS_E25

VSS_E26

VSS_E27

VSS_E28

VSS_E8

VSS_F1

VSS_F10

VSS_F13

VSS_F16

VSS_F19

VSS_F22

VSS_F4

VSS_F7

VSS_H10

VSS_H11

VSS_H12

VSS_H13

VSS_H14

VSS_H17

VSS_H18

VSS_H19

VSS_H20

VSS_H21

VSS_H22

VSS_H23

VSS_H24

VSS_H25

VSS_H26

VSS_H27

VSS_H28

VSS_H29

J_CPU0

INTEL LGA771 PINOUT

HETERO 8 OF 9

SILKSCREEN=CPU1

VSS_H3

VSS_H6

VSS_H7

VSS_H8

VSS_H9

VSS_J4

VSS_J7

VSS_K2

VSS_K5

VSS_K7

VSS_L23

VSS_L24

VSS_L25

VSS_L26

VSS_L27

VSS_L28

VSS_L29

VSS_L3

VSS_L30

VSS_L6

VSS_L7

VSS_M1

VSS_M7

VSS_N3

VSS_N6

VSS_N7

VSS_P23

VSS_P24

VSS_P25

VSS_P26

VSS_P27

VSS_P28

VSS_P29

VSS_P30

VSS_P4

VSS_P7

VSS_R2

VSS_R23

VSS_R24

VSS_R25

VSS_R26

VSS_R27

VSS_R28

VSS_R29

VSS_R30

VSS_R5

VSS_R7

VSS_T3

VSS_T6

VSS_T7

VSS_U7

VSS_V23

VSS_V24

VSS_V25

VSS_V26

VSS_V27

VSS_V28

VSS_V29

VSS_V3

VSS_V30

VSS_V6

VSS_V7

VSS_W4

VSS_W7

VSS_Y2

VSS_Y5

VSS_Y7

9-7-2007_16:36

H3

H6

H7

H8

H9

J4

J7

K2

K5

K7

L23

L24

L25

L26

L27

L28

L29

L3

L30

L6

L7

M1

M7

N3

N6

N7

P23

P24

P25

P26

P27

P28

P29

P30

P4

P7

R2

R23

R24

R25

R26

R27

R28

R29

R30

R5

R7

T3

T6

T7

U7

V23

V24

V25

V26

V27

V28

V29

V3

V30

V6

V7

W4

W7

Y2

Y5

Y7

1

2

3

+CPU_VID0+CPU_VID0

+CPU_VTT

21

+CPU_VID0

21

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

AN25

AN26

AN8

AN9

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J8

J9

K23

K24

K25

K26

K27

K28

K29

K30

K8

L8

VCC_AM14

VCC_AM15

VCC_AM18

VCC_AM19

VCC_AM21

VCC_AM22

VCC_AM25

VCC_AM26

VCC_AM29

VCC_AM30

VCC_AM8

VCC_AM9

VCC_AN11

VCC_AN12

VCC_AN14

VCC_AN15

VCC_AN18

VCC_AN19

VCC_AN21

VCC_AN22

VCC_AN25

VCC_AN26

VCC_AN8

VCC_AN9

VCC_J10

VCC_J11

VCC_J12

VCC_J13

VCC_J14

VCC_J15

VCC_J18

VCC_J19

VCC_J20

VCC_J21

VCC_J22

VCC_J23

VCC_J24

VCC_J25

VCC_J26

VCC_J27

VCC_J28

VCC_J29

VCC_J30

VCC_J8

VCC_J9

VCC_K23

VCC_K24

VCC_K25

VCC_K26

VCC_K27

VCC_K28

VCC_K29

VCC_K30

VCC_K8

VCC_L8

INTEL LGA771 PINOUT

SILKSCREEN=CPU1

J_CPU0

VCC_M23

VCC_M24

VCC_M25

VCC_M26

VCC_M27

VCC_M28

VCC_M29

VCC_M30

VCC_M8

VCC_N23

VCC_N24

VCC_N25

VCC_N26

VCC_N27

VCC_N28

VCC_N29

VCC_N30

VCC_N8

VCC_P8

VCC_R8

VCC_T23

VCC_T24

VCC_T25

VCC_T26

VCC_T27

VCC_T28

VCC_T29

VCC_T30

VCC_T8

VCC_U23

VCC_U24

VCC_U25

VCC_U26

VCC_U27

VCC_U28

VCC_U29

VCC_U30

VCC_U8

VCC_V8

VCC_W23

VCC_W24

VCC_W25

VCC_W26

VCC_W27

VCC_W28

VCC_W29

VCC_W30

VCC_W8

VCC_Y8

VCC_Y23

VCC_Y24

VCC_Y25

VCC_Y26

VCC_Y27

VCC_Y28

VCC_Y29

VCC_Y30

HETERO 6 OF 9

Room = PROC0_VTT_CAPS_22UF

C2568

1 2

+CPU_VTT

C2566

22uF 6.3V

21

C2567

1 2

22uF 6.3V

C2565

22uF 6.3V

21

dell p/n C5127

22uF 6.3V

21

Room = PROC0_VTT_CAPS_1uF

dell p/n D8579

C2547

1 2

C2546

1uF 6.3V

C2548

1 2

1uF 6.3V

C2545

1uF 6.3V

C2543

1uF 6.3V

C2544

1 2

1uF 6.3V

1uF 6.3V

4

ROOM=PROC0

SILKSCREEN=CPU1

+CPU_VTT

21

C2587

.1uF

C2586

10V-10%

21

.1uF

C2585

10V-10%

21

TODO: Intel: VTT decoup reqs TBDetero

.1uF

C2588

10V-10%

MODULE:

DESC:

REV: OF

21

21

21

21

Room = PROC0_VTT_CAPS_P1UF

CPUS,FSB,NB,XDP0,XDP1

SEC

dell p/n J5734

.1uF

C2583

10V-10%

.1uF

C2584

10V-10%

.1uF

C2582

10V-10%

.1uF

10V-10%

INC.

ROUND ROCK,TEXAS

TITLE

MCH

211

4

PROCESSOR 0

SCHEM, PLN, SV, PE2950, MLK

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

REV.

HX601

SHEET

A00

9/7/2007 14 OF 136

DCBA

A B C

D

1

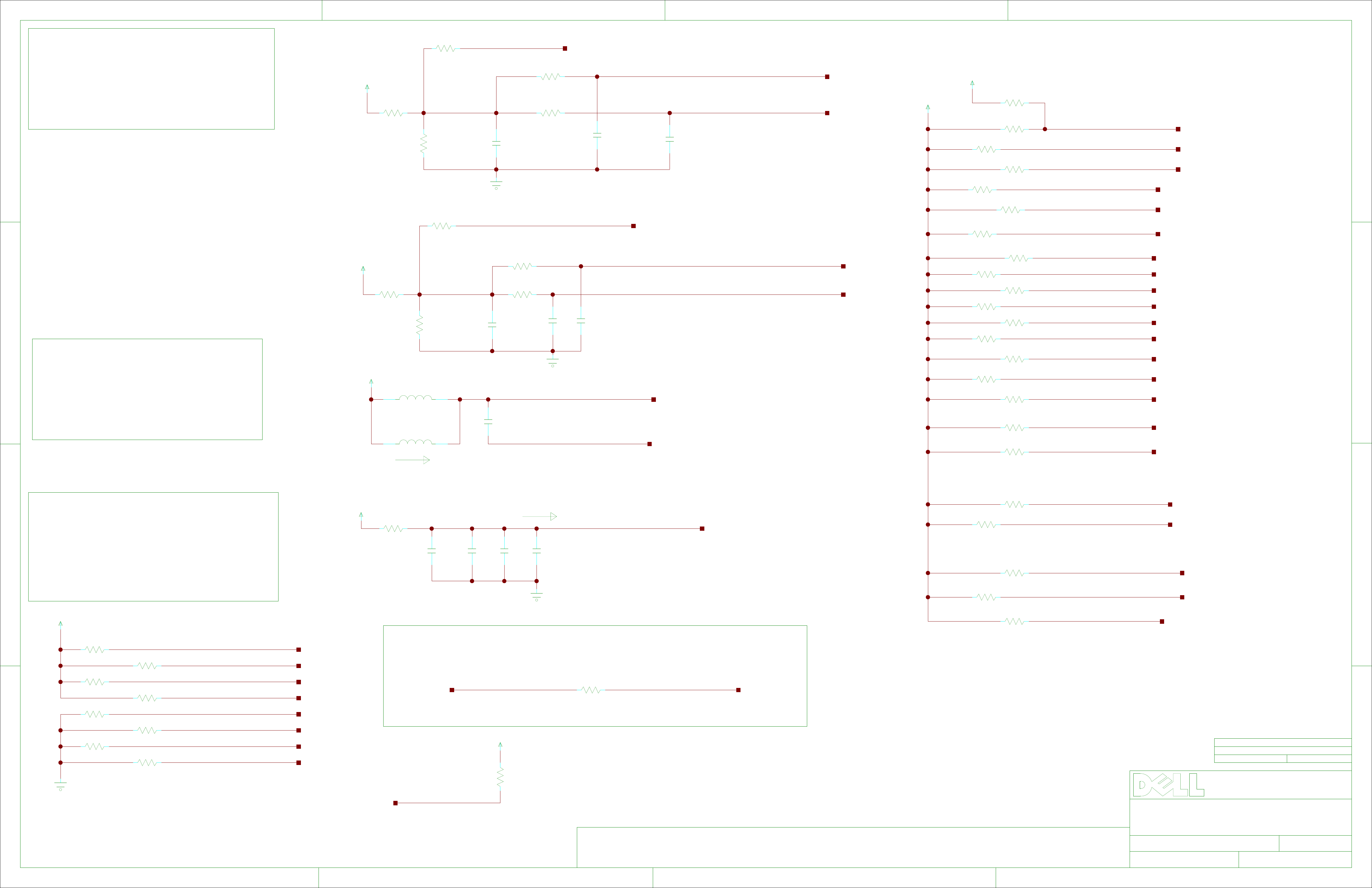

MOD_MCH_FSB0_GTLREF_DATA/ ADD

(800mV @1.2V VTT)

(733mV @1.1V VTT)

Place components:

Group associate components together

and as physically close to the associated

pin as possbile with the 220pf cap

closest to the pin

Make traces wide as possible >12mils

ROOM = PROC0_VREF_CORE1

CPU0 GTL VREF

+CPU_VTT

R4379

1 2

49.9-1%

R4386

1 2

21

R4354

680-5%

SUB=NP0

100-1%

TP_MOD_MCH_FSB0_GTLREF_DATA_R

NET_PHYSICAL_TYPE=30MIL

0-5%

R5270

0-5%

R5414

C2601

1 2

1uF 6.3V

Place termination close to CPU 0 at end of bus

rewired 5271 and 5270. Added C3396 C3395 R5415 and R5414

MOD_MCH_FSB0_GTLREF_DATA_CORE1

21

MOD_MCH_FSB0_GTLREF_ADD_CORE1

21

1 2

220pF

50V-10%

C2746

1 2

220pF

50V-10%

ECAD: Place 220pf caps under CPU

ECAD: Route <1.5" trace.

ECAD: Route at 30-50milscs (& Paris) DT#2256

C3395

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MILS

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MILS

13

13

+CPU_VTT

+3.3V

1 2

51-5%

R4677

R139

R5978

4.7K-5%

NP

1 2

4.7K-5%

1 2

51-5%

21

R210

R140

21

X

FSB0_VID_SELECT

MOD_MCH_FSB0_BREQ_1_N

MOD_MCH_FSB0_BREQ_0_N

MOD_MCH_CPU0_IERR_N

1

13,95,117,128

13,22

13,22

13,20

2

MOD_MCH_V_VTT_FSB0_VCCA / VSS

Place components:

Route trace from one of the L to

pin A23 of the CPU.

Route a trace from the other L to

pin of cap.

Place cap between CPU.A23 and VSSA.

Make traces wide as possible >12mils

ROOM = PROC0_VREF_CORE0

+CPU_VTT

+CPU_VTT

R4378

21

49.9-1%

L1759 & L1758 = dell p/n: N3305

L1759

10uH 165MA

26ohm+/-30%

L1758

1 2

10uH 165MA

R4385

1 2

R4353

680-5%

SUB=NP0

100-1%

21

TP_MOD_MCH_FSB0_GTLREF_ADD_R

21

NET_PHYSICAL_TYPE=30MIL

0-5%

1 2

R5271

0-5%

1 2

R5415

21

C2600

1uF 6.3V

MOD_MCH_V_VTT_FSB0_VCCA

12

C2569

22uF 6.3V

MOD_MCH_V_VSS_FSB0_VSSA

C2745

1 2

220pF

C3396

50V-10%

1 2

220pF

50V-10%

MOD_MCH_FSB0_GTLREF_DATA_CORE0

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MILS

MOD_MCH_FSB0_GTLREF_ADD_CORE0

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MILS

ECAD: Place 220pf caps under CPU

ECAD: Route <1.5" trace.

ECAD: Route at 30-50mils

13

13

13

13

51-5%

R4679

1 2

51-5%

R252

NP

1 2

220-5%

R246

NP

1 2

220-5%

R250

NP

1 2

220-5%

R1861

NP

1 2

220-5%

R4928

51-5%

X

R248

NP

220-5%

X

R247

NP

220-5%

X

R249

NP

220-5%

X

R125

1 2

51-5%

R92

1 2

150-1%

R5632

21

R138

51-5%

MOD_MCH_CPU0_PROCHOT_N

MOD_MCH_CPU0_THERMTRIP_N

21

21

MOD_MCH_FSB0_RST_N

X

21

X

21

X

CPU_PWRGOOD

21

MOD_MCH_VTT_CPU_PWRGOOD

FSB_SMI_N

FSB_A20M_N

FSB_NMI

FSB_INTR

FSB_INIT_N

FSB_IGNNE_N

FSB_STPCLK_N

FSB_FERR_N

13,20

13,20

13,22

13,17,54

13,17,54

13,17,54

13,17,54

13,17,54

13,17,54

13,17,54

13,17,54

BSEL PU's on Translation page

13,17,21,54

13,17,20

2

3

MOD_MCH_V_1V5_FSB0_VCCPLL

Place components:

Group associate components together

and as physically close to the associated

pin as possbile with one of the 0.1uF cap

closest to the pin

Make traces wide as possible >12mils

Route VCCIOPLL in parrallel to VSSA.

+CPU_VTT

Inductor stats: DCR (worst case) = .338 ohms SRF=30MHz 10uH +/- 10%& AR409 DT#2287

+1.5V

R4237

1 2

ROOM = PROCO_1V5_VCC

220mA Total

0-5%

6.3V-10%

4.7uF

21

C2575

ROOM = PROC0_VTT_VCC

CT:250mA, WC:125mA

6.3V-10%

4.7uF

C2577

21

50V-10%

0.01uF

C2569 = Dell p/n: C5127

MOD_MCH_V_1V5_FSB0_VCCPLL

21

50V-10%

C2950

0.01uF

C2589

21

P19_DT9175_jp

13

301-1%

X01_DT5560_SMR - deleted notes

R4244

21

MOD_MCH_FSB0_TESTHI_11

R4240

1 2

51-5%

R4245

1 2

51-5%

51-5%

R4243

51-5%

R5805

1 2

MOD_MCH_FSB0_TESTHI_10

21

MOD_MCH_FSB0_TESTHI_02_07

MOD_MCH_FSB0_TESTHI_00_01

MOD_MCH_CPU0_TESTIN

13

13

3

13

13

13,14

4

R5252

49.9-1%

R5251

49.9-1%

R5249

49.9-1%

R4299

49.9-1%

per MOW WW11 comp[7:4] now 50ohm +/- 15 ohm

21

R5253

1 2

21

21

21

49.9-1%

R5250

1 2

49.9-1%

R5248

1 2

49.9-1%

R4300

1 2

49.9-1%

MOD_MCH_FSB0_COMP_7

MOD_MCH_FSB0_COMP_6

MOD_MCH_FSB0_COMP_5

MOD_MCH_FSB0_COMP_4

MOD_MCH_FSB0_COMP_3

MOD_MCH_FSB0_COMP_2

MOD_MCH_FSB0_COMP_1

MOD_MCH_FSB0_COMP_0

X01_DT5511_SMR - added constraints to comp signalsm intel

PROPAGATION_DELAY=L:S::1200

PROPAGATION_DELAY=L:S::1200

PROPAGATION_DELAY=L:S::1200

PROPAGATION_DELAY=L:S::1200

PROPAGATION_DELAY=L:S::1200

NET_PHYSICAL_TYPE=15MIL

PROPAGATION_DELAY=L:S::1200

NET_PHYSICAL_TYPE=15MIL

PROPAGATION_DELAY=L:S::1200

NET_PHYSICAL_TYPE=15MIL

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=15MIL

13

13

13

13

13

13

13

13

13,17,20

ECAD: Total length of trace < 6"

17

PSMI

MOD_MCH_CPU_FORCEPR_N

Note: FORCEPR has internal termination

MOD_MCH_FSB1_TESTBUS

+CPU_VTT

NP

R4588

X

1 2

1K-1%

1 2

0-5%

R95

MOD_MCH_FSB0_TESTBUS

13

51-5%

TITLE

MODULE:

DESC:

REV: OF

CPUS,FSB,NB,XDP0,XDP1

SEC

INC.

ROUND ROCK,TEXAS

MCH

211

4

SCHEM, PLN, SV, PE2950, MLK

ROOM=PROC0

todo: can 1k be 5%?

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

REV.

HX601

SHEET

A00

9/7/2007 15 OF 136

DCBA

A B C

D

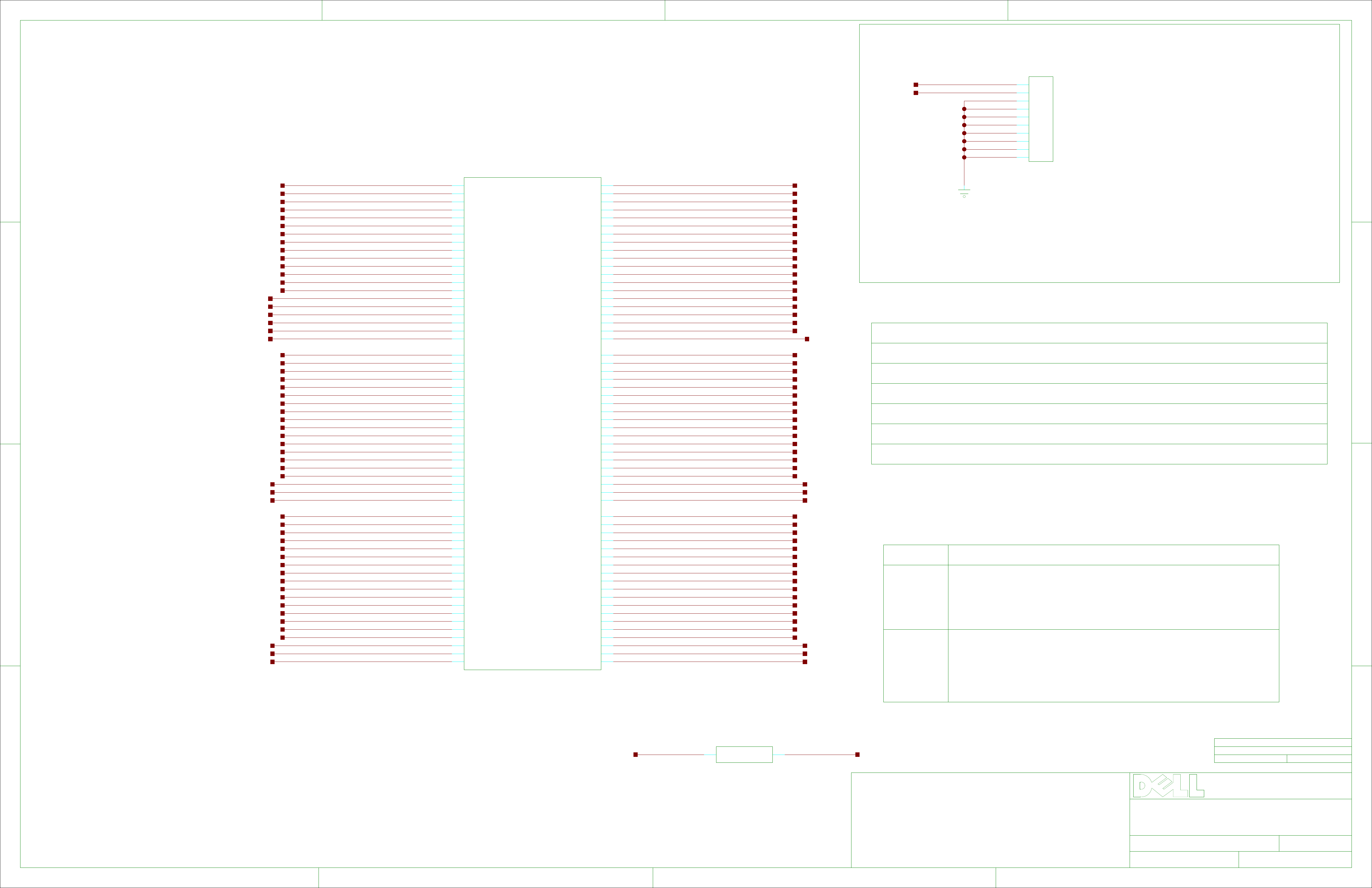

Processor 1 heatsink retention modules

ST2

1

2

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

MOD_MCH_FSB1_A16_N

MOD_MCH_FSB1_A15_N

MOD_MCH_FSB1_A14_N

MOD_MCH_FSB1_A13_N

MOD_MCH_FSB1_A12_N

MOD_MCH_FSB1_A11_N

MOD_MCH_FSB1_A10_N

MOD_MCH_FSB1_A9_N

MOD_MCH_FSB1_A8_N

MOD_MCH_FSB1_A7_N

MOD_MCH_FSB1_A6_N

MOD_MCH_FSB1_A5_N

MOD_MCH_FSB1_A4_N

MOD_MCH_FSB1_A3_N

MOD_MCH_FSB1_REQ_4_N

MOD_MCH_FSB1_REQ_3_N

MOD_MCH_FSB1_REQ_2_N

MOD_MCH_FSB1_REQ_1_N

MOD_MCH_FSB1_REQ_0_N

MOD_MCH_FSB1_ADSTB_0_N

J_CPU1

W5

A16_N

V4

A15_N

V5

A14_N

U4

A13_N

U5

A12_N

T4

A11_N

U6

A10_N

T5

A9_N

R4

A8_N

M4

A7_N

L4

A6_N

L5

A5_N

P6

A4_N

M5

A3_N

J6

REQ_4_N

K6

REQ_3_N

M6

REQ_2_N

J5

REQ_1_N

K4

REQ_0_N

R6 AD5

ADSTB0_N ADSTB1_N

A35_N

A34_N

A33_N

A32_N

A31_N

A30_N

A29_N

A28_N

A27_N

A26_N

A25_N

A24_N

A23_N

A22_N

A21_N

A20_N

A19_N

A18_N

A17_N

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

AC5

AB5

AA5

AD6

AA4

Y4

Y6

W6

AB6

MOD_MCH_FSB1_A35_N

MOD_MCH_FSB1_A34_N

MOD_MCH_FSB1_A33_N

MOD_MCH_FSB1_A32_N

MOD_MCH_FSB1_A31_N

MOD_MCH_FSB1_A30_N

MOD_MCH_FSB1_A29_N

MOD_MCH_FSB1_A28_N

MOD_MCH_FSB1_A27_N

MOD_MCH_FSB1_A26_N

MOD_MCH_FSB1_A25_N

MOD_MCH_FSB1_A24_N

MOD_MCH_FSB1_A23_N

MOD_MCH_FSB1_A22_N

MOD_MCH_FSB1_A21_N

MOD_MCH_FSB1_A20_N

MOD_MCH_FSB1_A19_N

MOD_MCH_FSB1_A18_N

MOD_MCH_FSB1_A17_N

MOD_MCH_FSB1_ADSTB_1_N

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

NC_MOD_MCH_ST2_1

NC_MOD_MCH_ST2_2

1

NC1

2

NC2

3

GND_V1

4

GND_V2

5

GND_V3

6

GND_V4

7

GND_V5

8

GND_V6

9

GND_V7

10

GND_V8

BRACKET RETENTION

SUPPORT, GROUNDED

CPU Heatsink

frame screws

ADD4=ADD*_RC078

ADD5=ADD*_RC078

ADD6=ADD*_RC078

ADD7=ADD*_RC078

CPU Heatsink

ADD8=ADD*_H3668

ADD9=ADD*_H3668

ADD1=ADD*_JC664

ADD2=ADD*_JC664

ADD3=ADD*_JC664

NOTE : heatsink retention clips needing a single trace to each pin, not solid

connection concern *doesn't* apply to the CPU HS brackets

Nocona-T

Platform Change

Dempsy-T

1

clip asm

Dempsy/Woodcrest

2

3

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

MOD_MCH_FSB1_D15_N

MOD_MCH_FSB1_D14_N

MOD_MCH_FSB1_D13_N

MOD_MCH_FSB1_D12_N

MOD_MCH_FSB1_D11_N

MOD_MCH_FSB1_D10_N

MOD_MCH_FSB1_D9_N

MOD_MCH_FSB1_D8_N

MOD_MCH_FSB1_D7_N

MOD_MCH_FSB1_D6_N

MOD_MCH_FSB1_D5_N

MOD_MCH_FSB1_D4_N

MOD_MCH_FSB1_D3_N

MOD_MCH_FSB1_D2_N

MOD_MCH_FSB1_D1_N

MOD_MCH_FSB1_D0_N

MOD_MCH_FSB1_DBI_0_N

MOD_MCH_FSB1_DSTBN_0_N

MOD_MCH_FSB1_DSTBP_0_N

MOD_MCH_FSB1_D31_N

MOD_MCH_FSB1_D30_N

MOD_MCH_FSB1_D29_N

MOD_MCH_FSB1_D28_N

MOD_MCH_FSB1_D27_N

MOD_MCH_FSB1_D26_N

MOD_MCH_FSB1_D25_N

MOD_MCH_FSB1_D24_N

MOD_MCH_FSB1_D23_N

MOD_MCH_FSB1_D22_N

MOD_MCH_FSB1_D21_N

MOD_MCH_FSB1_D20_N

MOD_MCH_FSB1_D19_N

MOD_MCH_FSB1_D18_N

MOD_MCH_FSB1_D17_N

MOD_MCH_FSB1_D16_N

MOD_MCH_FSB1_DBI_1_N

MOD_MCH_FSB1_DSTBN_1_N

MOD_MCH_FSB1_DSTBP_1_N

D11

C12

B12

D8

C11

B10

A11

A10

A7

B7

B6

A5

C6

A4

C5

B4

A8

C8

B9

G15

F15

G14

F14

G13

E13

D13

F12

F11

D10

E10

D7

E9

F9

F8

G9

G11

G12

E12

D15_N

D14_N

D13_N

D12_N

D11_N

D10_N

D9_N

D8_N

D7_N

D6_N

D5_N

D4_N

D3_N

D2_N

D1_N

D0_N

DBI0_N

DSTBN0_N

DSTBP0_N

D31_N

D30_N

D29_N

D28_N

D27_N

D26_N

D25_N

D24_N

D23_N

D22_N

D21_N

D20_N

D19_N

D18_N

D17_N

D16_N

DBI1_N

DSTBN1_N

DSTBP1_N

D47_N

D46_N

D45_N

D44_N

D43_N

D42_N

D41_N

D40_N

D39_N

D38_N

D37_N

D36_N

D35_N

D34_N

D33_N

D32_N

DBI2_N

DSTBN2_N

DSTBP2_N

D63_N

D62_N

D61_N

D60_N

D59_N

D58_N

D57_N

D56_N

D55_N

D54_N

D53_N

D52_N

D51_N

D50_N

D49_N

D48_N

DBI3_N

DSTBN3_N

DSTBP3_N

G22

D22

E22

G21

F21

E21

F20

E19

E18

F18

F17

G17

G18

E16

E15

G16

D19

G20

G19

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

B15

C14

C15

A14

D17

D20

C20

A16

C17

MOD_MCH_FSB1_D47_N

MOD_MCH_FSB1_D46_N

MOD_MCH_FSB1_D45_N

MOD_MCH_FSB1_D44_N

MOD_MCH_FSB1_D43_N

MOD_MCH_FSB1_D42_N

MOD_MCH_FSB1_D41_N

MOD_MCH_FSB1_D40_N

MOD_MCH_FSB1_D39_N

MOD_MCH_FSB1_D38_N

MOD_MCH_FSB1_D37_N

MOD_MCH_FSB1_D36_N

MOD_MCH_FSB1_D35_N

MOD_MCH_FSB1_D34_N

MOD_MCH_FSB1_D33_N

MOD_MCH_FSB1_D32_N

MOD_MCH_FSB1_DBI_2_N

MOD_MCH_FSB1_DSTBN_2_N

MOD_MCH_FSB1_DSTBP_2_N

MOD_MCH_FSB1_D63_N

MOD_MCH_FSB1_D62_N

MOD_MCH_FSB1_D61_N

MOD_MCH_FSB1_D60_N

MOD_MCH_FSB1_D59_N

MOD_MCH_FSB1_D58_N

MOD_MCH_FSB1_D57_N

MOD_MCH_FSB1_D56_N

MOD_MCH_FSB1_D55_N

MOD_MCH_FSB1_D54_N

MOD_MCH_FSB1_D53_N

MOD_MCH_FSB1_D52_N

MOD_MCH_FSB1_D51_N

MOD_MCH_FSB1_D50_N

MOD_MCH_FSB1_D49_N

MOD_MCH_FSB1_D48_N

MOD_MCH_FSB1_DBI_3_N

MOD_MCH_FSB1_DSTBN_3_N

MOD_MCH_FSB1_DSTBP_3_N

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

requiredrequired

Use "LE" Blackford

Pull down reserved pin F6

Pull down MS_ID[1:0] to Vss

Isolate LL_ID[1:0]

Manually set VR loadline

required

optional

optional

optional

required

required

required

required

required

required

Mechanical Parts on the following pages:

12, 16

Socket J part numbers:

Dell p/n

Y9236

P9381

Description

Leaded Socket J - SKT,LGA,771P,G,SF,ZIF,SL,SM

Vendors:

Foxconn PN: PE077107-1041-01

Tyco PN: 1747890-1

Lead-free socket J - SKT,LGA,771P,G,SF,ZIF,SL,SM

Vendors:

No use LGA771Use LGA775

No use real blackford

No treat as reserved, leave pin No Connect

No revert back to POR

No revert back to POR

No revert back to POR

3

4

ROOM=PROC1

INTEL LGA771 PINOUT

HETERO 2 OF 9

SILKSCREEN=CPU2

ADD*_PR288

ECAD NOTE: Please put triangle pointing to pin1

NC_CPU1_REG_1

CPU1_REG

1 2

COMMON NEG

REG07 A NGO

COUPON TEST

NC_CPU1_REG_2

Foxconn PN: PE077127-1041-01

Tyco PN: 1-1747890-1

PROCESSOR 1

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF

LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST

AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF

THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT

THE PRIOR WRITTEN CONSENT OF DELL INC.

TITLE

DWG NO.

DATE

MODULE:

DESC:

REV: OF

INC.

ROUND ROCK,TEXAS

SCHEM, PLN, SV, PE2950, MLK

HX601

SHEET

16 OF 1369/7/2007

CPUS,FSB,NB,XDP0,XDP1

SEC

REV.

A00

MCH

211

4

C

DBA

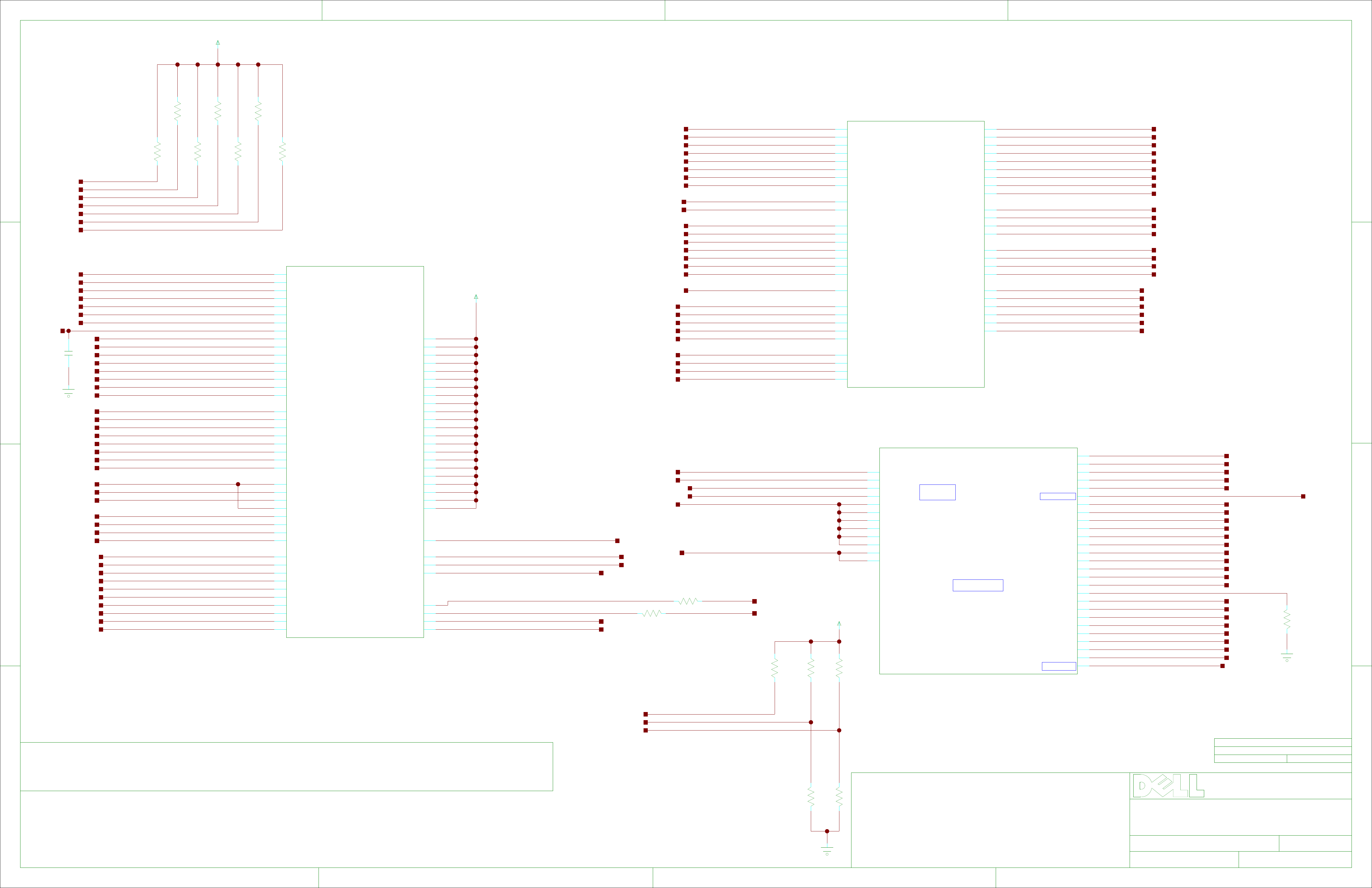

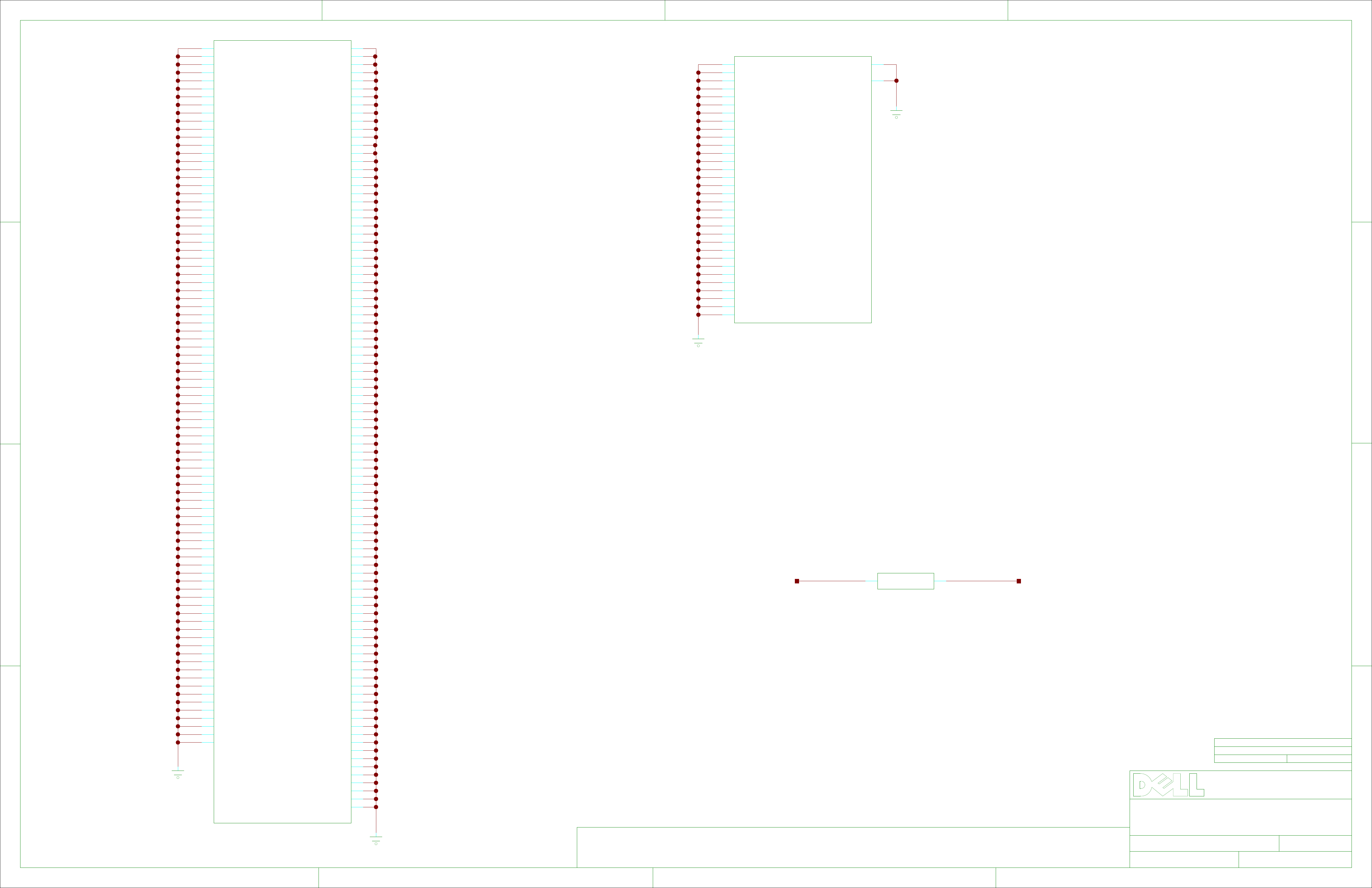

A B C

+CPU_VTT

D

1

2

3

21

R4255

R4260

17,119

17,119

17,119

17,119

17,119

17,119

17,119

13,15,21,54

NP

X

1 2

C8599

19,95,119,128

MLK: Routed to CPLD for CPU Identification

17,21,95,119,128

Do not place VTT_SEL or CPU_PRES_N on 3v3Aux, VTT_SEL is used in main domain VRD logic,

CPU_PRES_N is used on 3v3 part during development.

The rest are placed on 3v3 to simply routing, no need for 3v3 aux near CPU.

FSB1_VID_6

FSB1_VID_5

FSB1_VID_4

FSB1_VID_3

FSB1_VID_2

FSB1_VID_1

FSB1_VID_0

20

20

20

19

19

19

19

100pF

50V-5%

17,119

17,119

17,119

17,119

17,119

17,119

17,119

119

119

119

119

17,89

17,89

**

MOD_MCH_CPU1_BSEL_2

MOD_MCH_CPU1_BSEL_1

MOD_MCH_CPU1_BSEL_0

MOD_MCH_FSB1_GTLREF_DATA_CORE1

MOD_MCH_FSB1_GTLREF_ADD_CORE1

MOD_MCH_FSB1_GTLREF_DATA_CORE0

MOD_MCH_FSB1_GTLREF_ADD_CORE0

CPU_PWRGOOD

19

19

19

19

19

19

19

19

19

19

19

89

89

15

MOD_MCH_FSB1_COMP_7

MOD_MCH_FSB1_COMP_6

MOD_MCH_FSB1_COMP_5

MOD_MCH_FSB1_COMP_4

MOD_MCH_FSB1_COMP_3

MOD_MCH_FSB1_COMP_2

MOD_MCH_FSB1_COMP_1

MOD_MCH_FSB1_COMP_0

FSB1_VID_6

FSB1_VID_5

FSB1_VID_4

FSB1_VID_3

FSB1_VID_2

FSB1_VID_1

FSB1_VID_0

FSB1_VID_SELECT

MOD_MCH_V_VTT_FSB1_VCCA

MOD_MCH_V_VSS_FSB1_VSSA

MOD_MCH_V_1V5_FSB1_VCCPLL

CPU1_VCC_DIE_SENSE

CPU1_VCC_DIE_SENSE2

CPU1_VSS_DIE_SENSE

CPU1_VSS_DIE_SENSE2

CPU1_PRES_N

CPU1_THERMD_A_2

CPU1_THERMD_C_12

CPU1_THERMD_C_12

NC_MOD_MCH_FSB1_DBR_N

*

NC_MOD_MCH_FSB1_ITP_CLK1

*

NC_MOD_MCH_FSB1_ITP_CLK0

*

NC_MOD_MCH_FSB1_RSVD_Y1

MOD_MCH_FSB1_TESTBUS

511-1%

511-1%

PROC1

R4256

1 2

21

R4257

511-1%

511-1%

R4259

1 2

21

R4258

511-1%

511-1%

R4254

G30

H30

G29

G10

AE3

A13

AM5

AL4

AK4

AL6

AM3

AL5

AM2

AN7

A23

B23

D23

C23

AN3

AL8

AN4

AL7 AM6

AE8

AL1

AJ7

AK1

AH7

AC2

AJ3

AK3

AH2

511-1%

1 2

J_CPU1

BSEL2

BSEL1

BSEL0

F2

GTLREF_DATA_CORE1

H2

GTLREF_ADD_CORE1

GTLREF_DATA_CORE0

H1

GTLREF_ADD_CORE0

N1

PWRGOOD

COMP7

Y3

COMP6

T2

COMP5

J2

COMP4

R1

COMP3

G2

COMP2

T1

COMP1

COMP0

VID6

VID5

VID4

VID3

VID2

VID1

VID0

VID_SELECT

VCCA

VSSA

VCCPLL

VCCIOPLL

VCC_DIE_SENSE

VCC_DIE_SENSE2

VSS_DIE_SENSE

VSS_DIE_SENSE2 VTTPWRGD

SKTOCC_N

THERMDA

THERMDA2

THERMDC

THERMDC2

DBR_N

ITP_CLK1

ITP_CLK0

Y1

BOOT_SELECT

TEST_BUS

INTEL LGA771 PINOUT

HETERO 3 OF 9

SILKSCREEN=CPU2

VTT_E30/NC_E30

VTT_F30/NC_F30

VTT_OUT_1

VTT_OUT_0

VTT_A25

VTT_A26

VTT_B25

VTT_B26

VTT_B27

VTT_B28

VTT_B29

VTT_B30

VTT_C25

VTT_C26

VTT_C27

VTT_C28

VTT_C29

VTT_C30

VTT_D25

VTT_D26

VTT_D27

VTT_D28

VTT_D29

VTT_D30

VTT_SEL

LL_ID1

LL_ID0

MS_ID1

MS_ID0

A25

A26

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

E30

F30

AA1

J1

F27

AA2

V2

V1

W1

* NOTE: DBR and ITP_CLK are outputs from a in-socket debugger- Dell has no plans for this debug model.

** NOTE: WW10 MOW documents that bootselect is being removed

and to leave pin floating

+CPU_VTT

MOD_MCH_VTT_CPU_PWRGOOD

NC_MOD_MCH_FSB1_VTT_OUT_1

NC_MOD_MCH_FSB1_VTT_OUT_0CPU1_THERMD_A_1

MOD_MCH_VTT_SEL_CPU1

MOD_MCH_CPU1_LL_ID1_R

MOD_MCH_CPU1_LL_ID0_R CPU1_LL_ID0

CPU1_MS_ID1

CPU1_MS_ID0

19,21,22

45

45

13,15,54

13,15,54

13,15,20

13,15,54

13,15,54

13,15,54

13,15,54

13,15,54

13,21

21

21

13,21,24

13,21,24

19,20

13,15,54

19,20

19,20

19

19

19

13,15,20

19

109

MLK: VTT_SEL Signal going to VTT REG Ckt

17,95,128

17,95,128

17,21,95,119,128

17,95,128

17,95,128

R5501

0-5%

12

NP for DempseyT

CPU1_PRES_N

CPU1_MS_ID1

CPU1_MS_ID0

MOD_MCH_FSB1_RST_N

MOD_MCH_FSB1_RSP_N

22

MOD_MCH_FSB1_BPRI_N

22

MOD_MCH_FSB1_TRDY_N

22

MOD_MCH_FSB1_DEFER_N

22

MOD_MCH_FSB1_RS_0_N

22

MOD_MCH_FSB1_RS_1_N

22

MOD_MCH_FSB1_RS_2_N

22

CK_333M_CPU1_N

CK_333M_CPU1_P

FSB_SMI_N

FSB_A20M_N

MOD_MCH_CPU_FORCEPR_N

FSB_INTR

FSB_NMI

FSB_IGNNE_N

FSB_STPCLK_N

FSB_INIT_N

MOD_MCH_XDP0_TCK0

MOD_MCH_XDP0_TDI_CPU1

MOD_MCH_XDP0_TDO_CPU1

MOD_MCH_XDP0_TMS

MOD_MCH_XDP0_TRST_N

MOD_MCH_CPU1_IERR_N

FSB_FERR_N

MOD_MCH_CPU1_PROCHOT_N

MOD_MCH_CPU1_THERMTRIP_N

MOD_MCH_FSB1_TESTHI_11

MOD_MCH_FSB1_TESTHI_10

MOD_MCH_FSB1_BPMB_2_N

21

MOD_MCH_FSB1_BPMB_3_N

21

MOD_MCH_FSB1_TESTHI_02_07

MOD_MCH_FSB1_TESTHI_00_01

R5500

0-5%

J_CPU1

G23

RESET_N

H4

RSP_N

G8

BPRI_N

E3

TRDY_N

G7

DEFER_N

B3

RS0_N

F5

RS1_N

A3

RS2_N

G28

BCLK1

P2

SMI_N

K3

A20M_N

AK6

FORCEPR_N

K1

LINT0

L1

LINT1

N2

IGNNE_N

M3

STPCLK_N

P3

INIT_N

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST_N

AB2

IERR_N

R3

FERR/PBE_N

AL2

PROCHOT_N

M2

THRMTRIP_N

INTEL LGA771 PINOUT

HETERO 1 OF 9

SILKSCREEN=CPU2

J_CPU1

L2

TESTHI11

P1

TESTHI10

G4