MSI MS-9179 Schematic 0826_optab

5

MSI

MS-91 79 REV 0A

4

3

2

1

D D

Table of Contents

Page

01

02

03

04

05

06

07

08~10

11~13

14~17

18~21

C C

22

23

24

26

25

27

28

29

30

31

32

33

34

Title

Cover / Table of Contents

System Block Diagram

Power Delive ry Block Diagram

System Clock Block D i a g r a m

System Reset Block Dia g ram

System SMBus Block Dia g r a m

DDRII Routing Block Diagram

CPU1

CPU2

GREENCREEK

FBD DIMM 1 ~ 8

PCI EXPRESS X16/X8 SLOT

CPU BSEL

ESB2 PCI / PCI-X

ESB2 PCI-E / USB / LAN

ESB2 SATA / IDE / RTC

ESB2 POWER / GND

PCI-X SLOT X 2

PCI & mi n PCI SLOT

AC'97 ADI AD1981B CODEC

GILGAL LAN

IEEE 1394

CLOCKGEN / CLOCK BUFFER

SIO NS P C87366 IO Port

35 USB CONNECTOR

36~37

B B

38~39

40

41

P0 VRD- 1 VT1115M&VT1115S

P1 VRD- 1 VT1115M&VT1115S

FBD DIMM POWER 1.8V

System p ower-1.5V

42 System Power Control

43

44

45

46

SYSTEM MAIN POWER VR

PLD & XD P

Front Panel /Power Conn/NMI

SAS LSI 1064 #1

SAS LSI 1064 #247

48

49

50

PERR / FWH / HWM

MSIC

History

Revision History

Revision

History

0A - (xx/xx/xx)

2005/7/7

BOM

1) For NEC, Gilgal single + ESB2V

2) Opt A, For channel, Gilgal single + ESB2V

3) Opt B, For channel, Gilgal dual +ESB2A

Page

GREENCREEK + ESB2 Schematics

A A

Micro-Star Int'l Co., Ltd.

No. 6 9, L i -D e S t , Ju ng- He C i ty, Tai p ei Hs ien, T ai wan . h tt p: / /www. ms i . c om. t w

Title

Cover /Table of Contents

Size Document Number Re v

MS-9179

5

4

3

2

Date: Sheet

150Friday, A ugust 26, 2005

1

0ACustom

of

5

4

shadow Cat

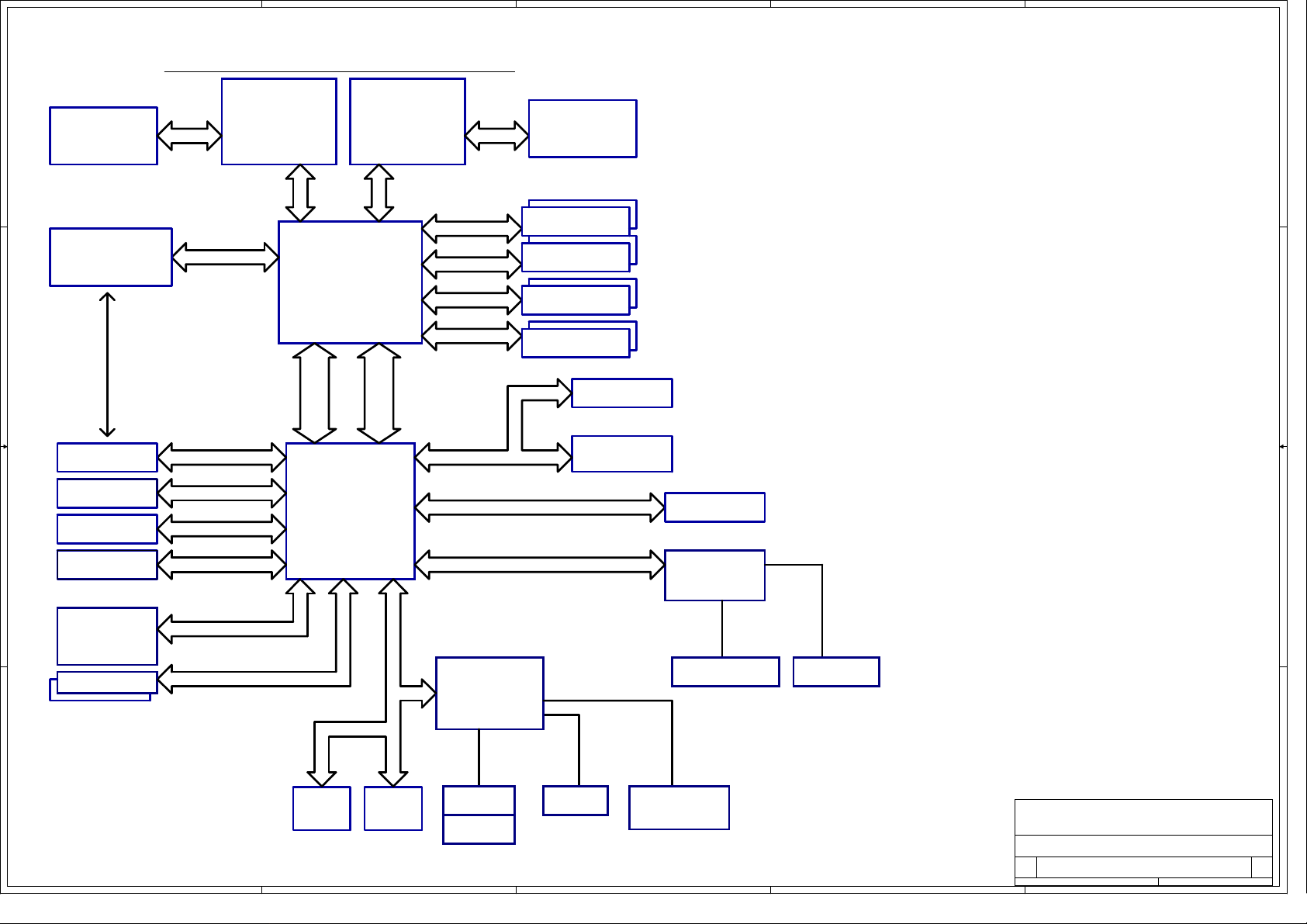

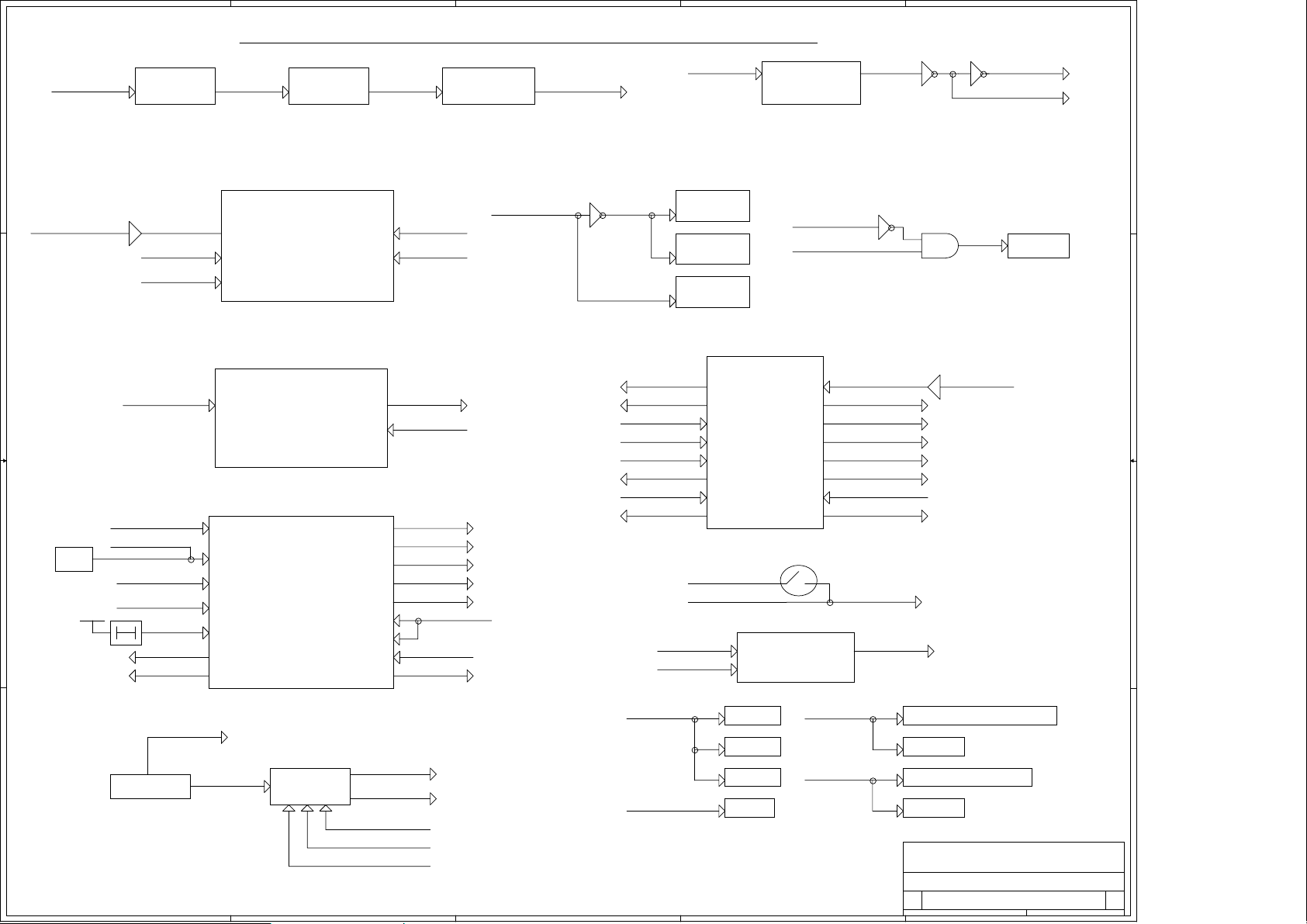

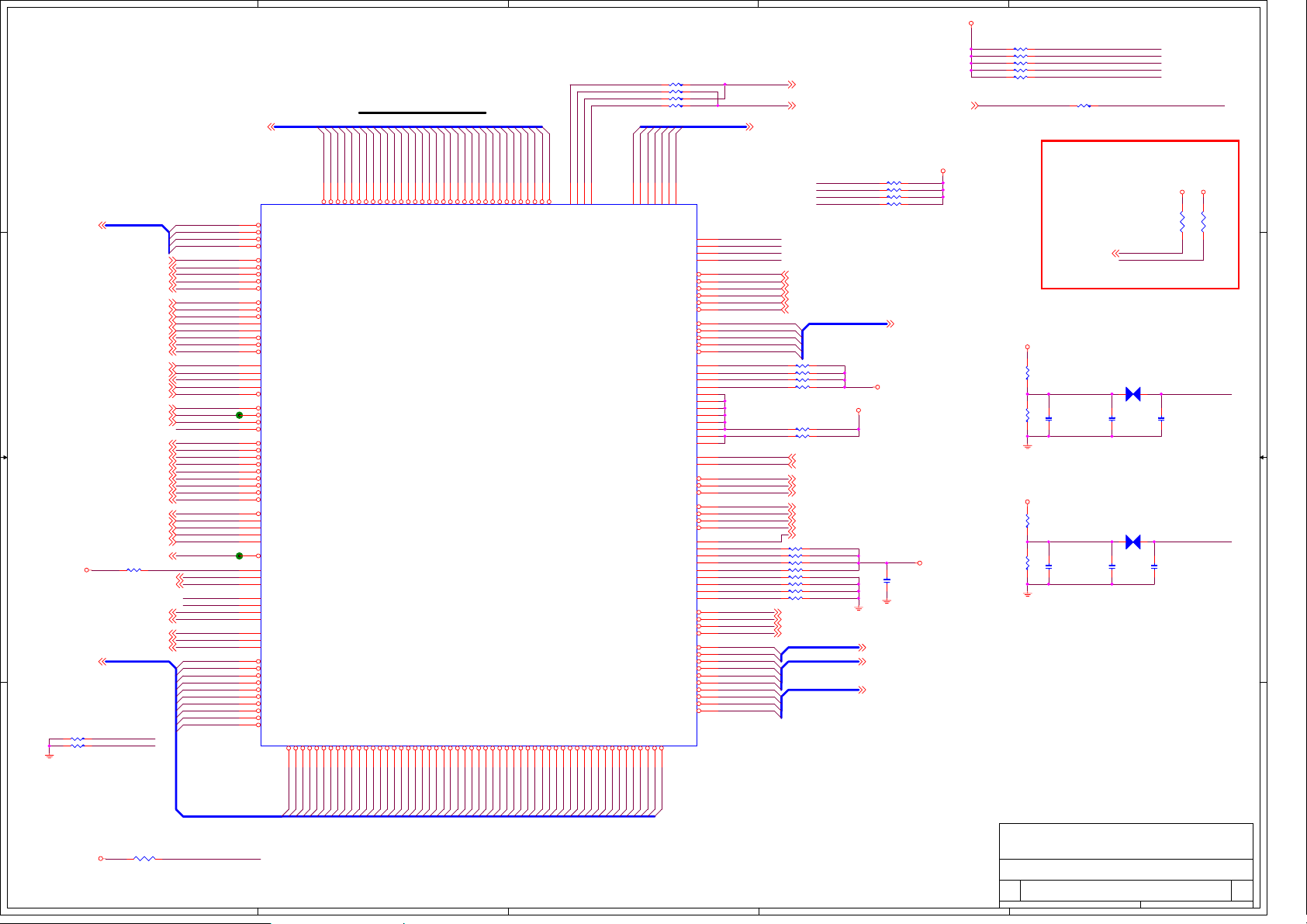

MS-9179 SYSTEM BLOCK DIAGRAM

3

2

1

CPU0

D D

VRD 11

VT1115M

VRD VRD

5-Phase PWM

Intel L GA - 771

DEMPSEY/

WOODCREST

FSB0

1066MHz

External

Graphics Card

16X Connector

C C

PCI Express X16

GREENCREEK

SLI

1066MHz

PCIE X4 BUS

CPU1

Intel L GA - 771

DEMPSEY/

WOODCREST

FSB1

DDR2 Channel 0

DDR2 Channel 1

DDR2 Channel 2

DDR2 Channel 3

ESI X 8 BUS

VRM 11

VT1115M

5-Phase PWM

FBDIMM x2

Modules

FBDIMM x2

Modules

FBDIMM x2

Modules

FBDIMM x2

Modules

PCI SLOT

Prelimi n a r y Spec

* Intel GREENCREEK / ESB2V Chipset

* Intel LGA-771 DEMPSEY / WOODCREST

* 8 Layer BTX Form Factor (W 394mm X L 330mm)

* 8 DDR2 FBDIMM (2 Branch / 4 Channel)

* PCI Express X16 for Graphic + PCI Express X 8

* USB 2.0 (Rear x4 , Front x2)

* 2 PCI-X slot

* 1 PCI-X slot

* AC'97 ADI AD1981B CODEC

* Serial ATA (4 channel)

* IEEE 1394 TI Chip on-board (Rear x1, Front x1)

* Gigabit LAN INTEL GILGAL PHY 82563EB

* LSI SAS 1064E 3.0Gbit/s serial attached

SCSI controller

PCI Express X 16

Connector

ATA Primary

SATA 0~3

PCI Ex press X 8

Ultra DMA 66/100

SATA

ESB2

PCI BUS

LAN PHY BUS

IEEE 1394

TI/TS B43A B22

INTEL

GILGAL PHY

* LPC SIO NS/PC87366

* VRD 11 VT1115M 5-Phase PWM

* TPM Infineon SLD9630

B B

USB2 .0 Port 0~5

USB 2.0

PCI EXPRESS X 4

SAS controller

LSI 1064E

ADI AD1981B

AC' 97 Link

AC'97 Codec

SAS X 4

Connector

PCI-X SLOT

PCI-X BUS X 2

LPC SIO

32KX8 NVSRAM

NS/PC87366

LPC Bus

A A

TPM

FWH

PS2 - KB

PS2 - MS

5

4

Floppy

2 X Serial Port

1 X Parallel port

3

Micro-Star Int'l Co., Ltd.

No. 6 9, L i -D e S t , Ju ng- He C i ty, Tai p ei Hs ien, T ai wan . h tt p: / /www. ms i . c om. t w

Title

System Block Diagram

Size Document Number Re v

MS-9179

2

Date: Sheet

250Friday, A ugust 26, 2005

1

0ACustom

of

5

4

3

2

1

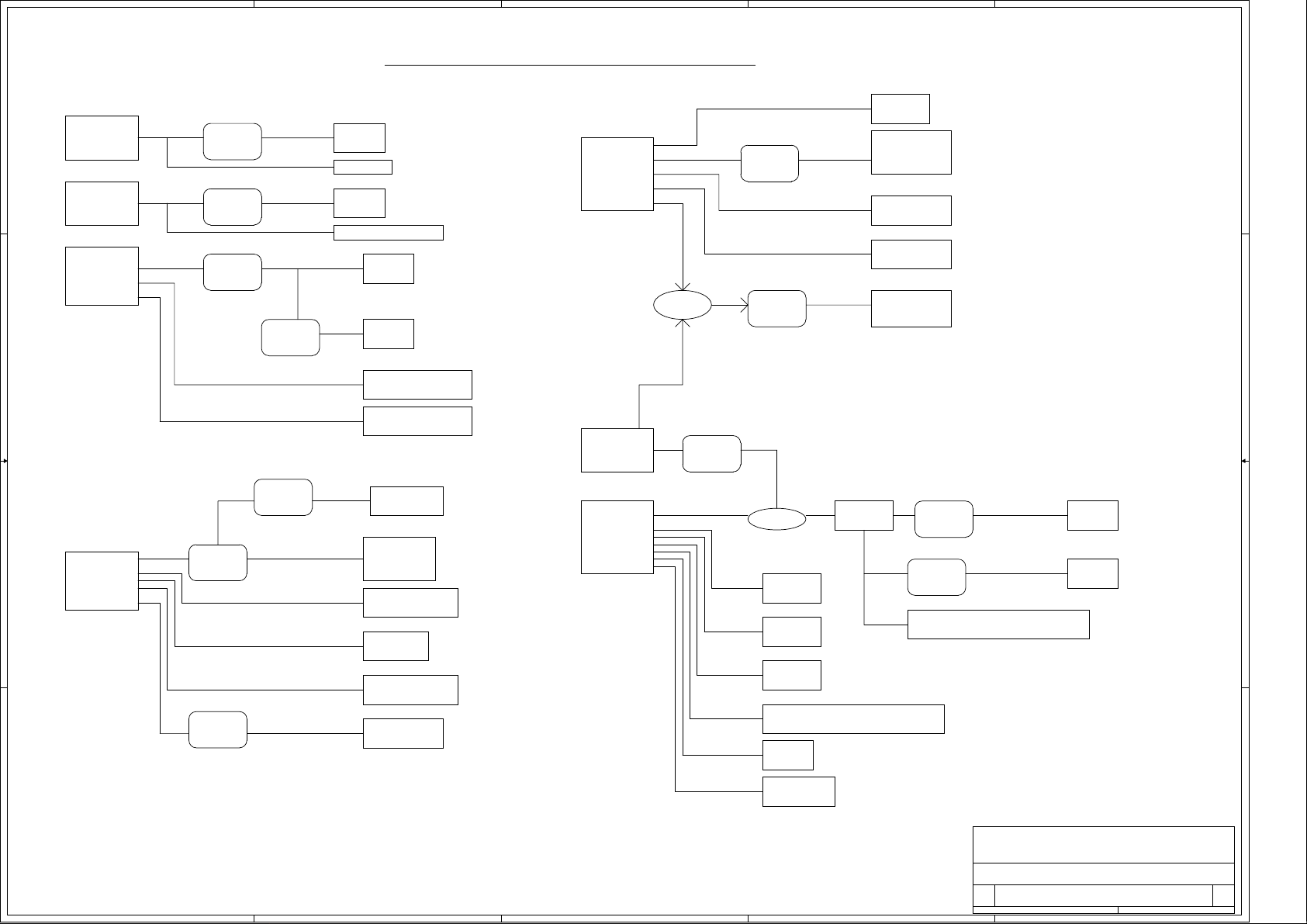

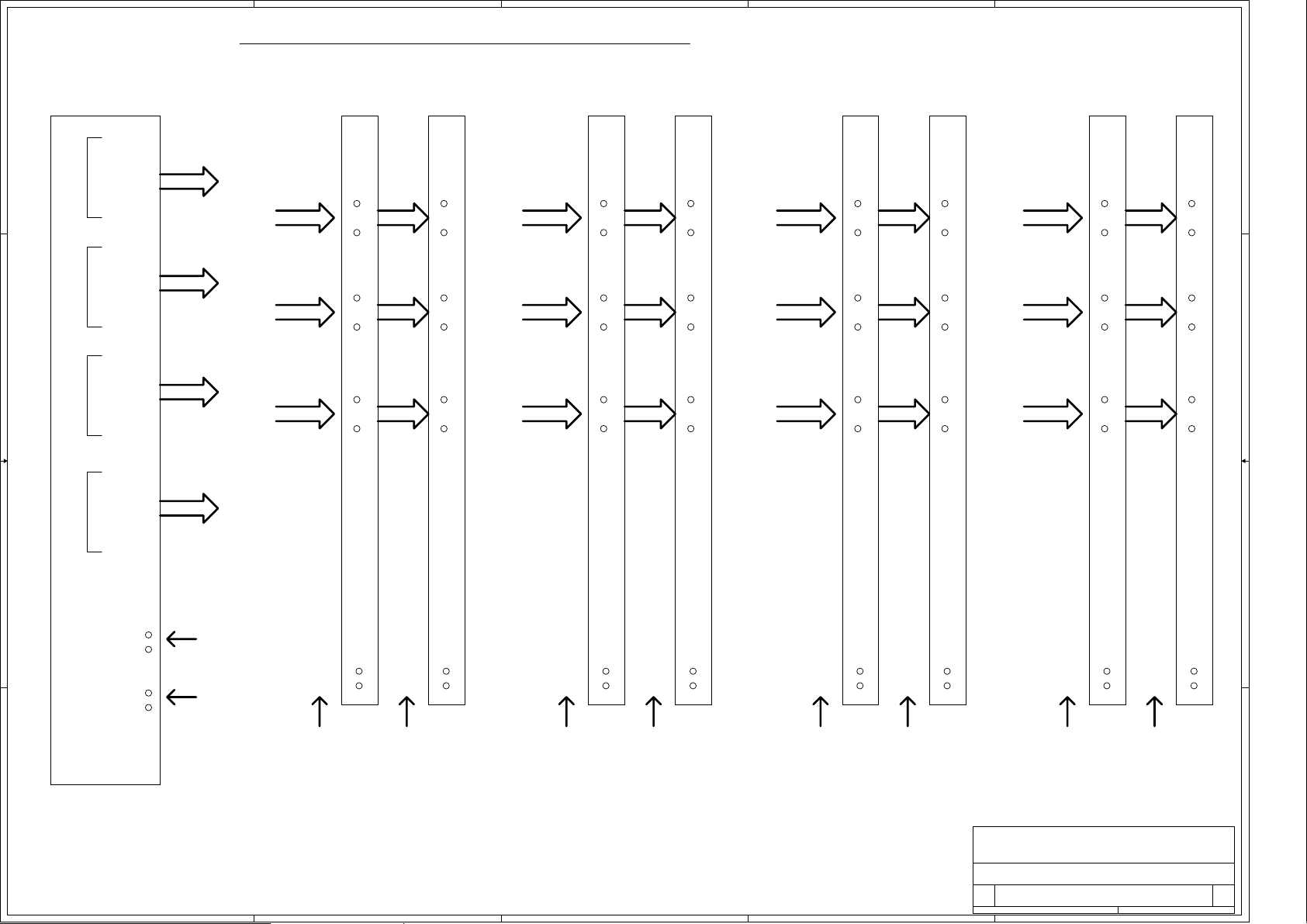

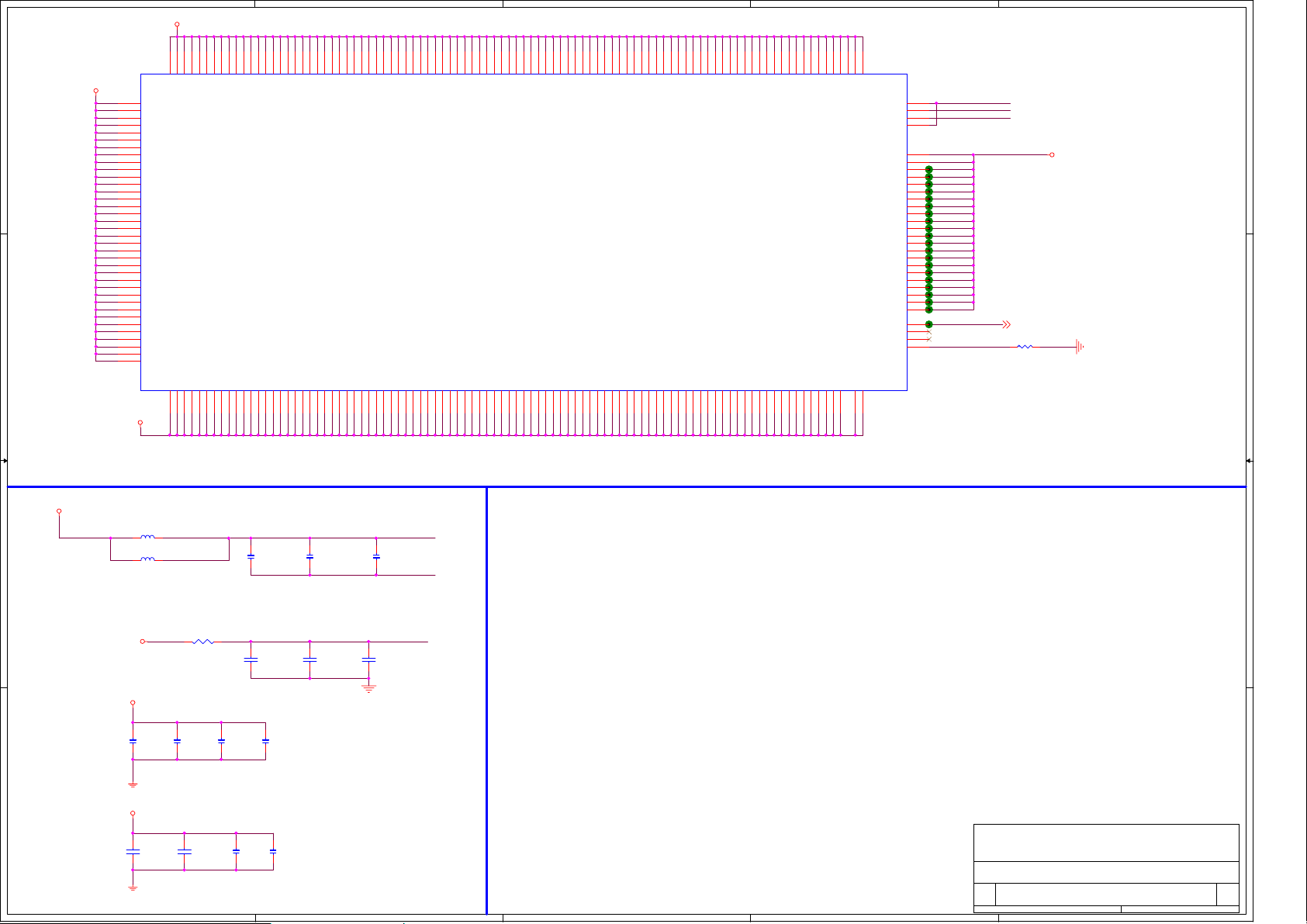

MS-9179 POWER DELIEVERY DIAGRAM

D D

P12V1

P12V2

13.95A

15.1A

VRD11 CPU0

CPUFAN1

VRD11 CPU1

P5V

4.1A

1.88A

2A

1.2V

REG

V_FSB_VTT

GREENCREEK

ESB2

CPU

PCI-X 2 SLOT

CPUFAN2 & SYSFAN2

PCI X 1 SLOT

1394 CHIP

P12V3

C C

8.04A

1.8V

REG

3.3A

0.2A

2.95A

B B

P12V3

1.5V

REG

3.19A

1.15A

2.5A

P1V8

1.8V

REG

1.2V

REG

P1V5

P0V9

P1V2_SAS

FB DIMM

FBD VTT

PCIE_16X/8X SLOT

PCI-X SLOT X 2

SAS CHIP

GREENCREEK

ESB2

FBDIMM

HDD/CD-ROM/FDD

SYSFAN1

P5VSB

P3V3

SWITCH

3.3V

REG

minPCI SLOT

P5V_AUX USB X 4 PORT

KB/MS

P3VSB

SWITCH

P3V3_AUX

1394 CHIP

CLK GEN.

PCI-E & PCI-X Slot/PCI Device

REG

1.5V

REG

P1V8&P1V2 LAN

P1V5_AUX

LAN1.2V&1.8V

ESB2

0.8A

5V

REG

P5V_AUD

1394 Connector

7.35A

AUDIO CODEC

1.27A

Super IO

PCI-E & PCI-X Slot

ESB2

SAS CHIP

A A

Micro-Star Int'l Co., Ltd.

No.69, Li- D e St, J ung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Power Delivery Block Di agram

Size Doc u m ent N u m b er R e v

MS-9179

5

4

3

2

Date: Sheet

350Fr id ay, August 26, 2005

1

0ACustom

of

5

4

3

2

1

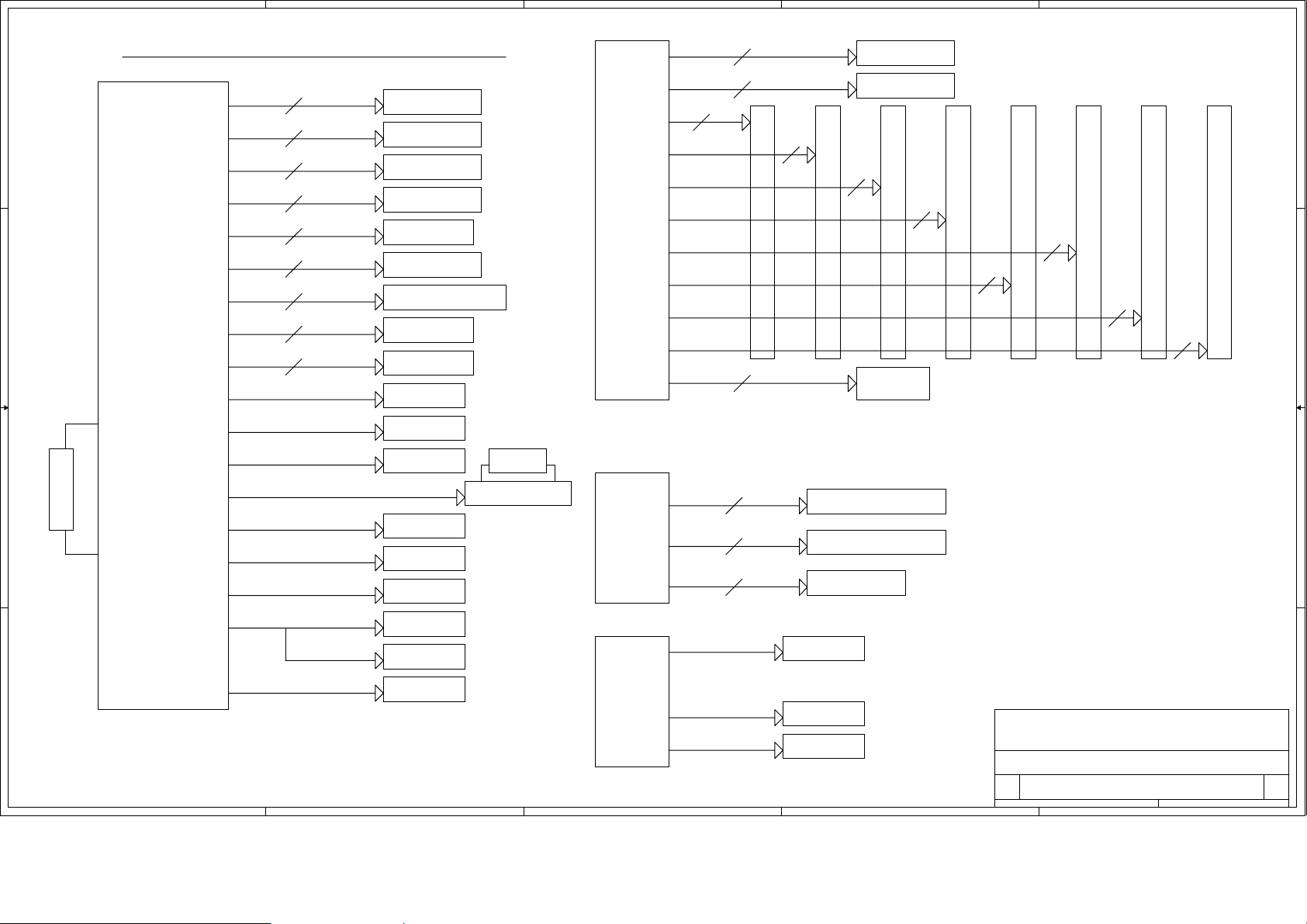

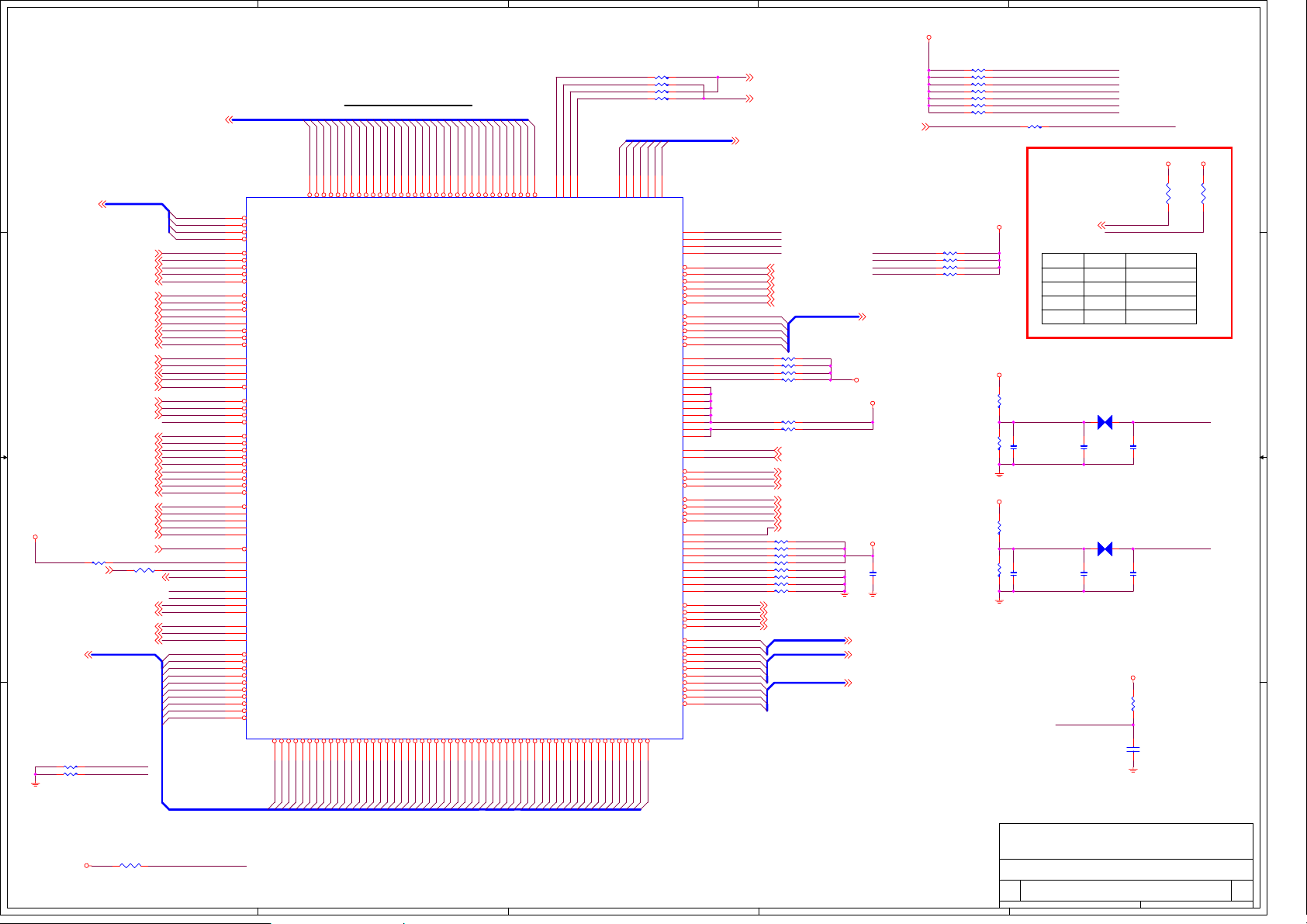

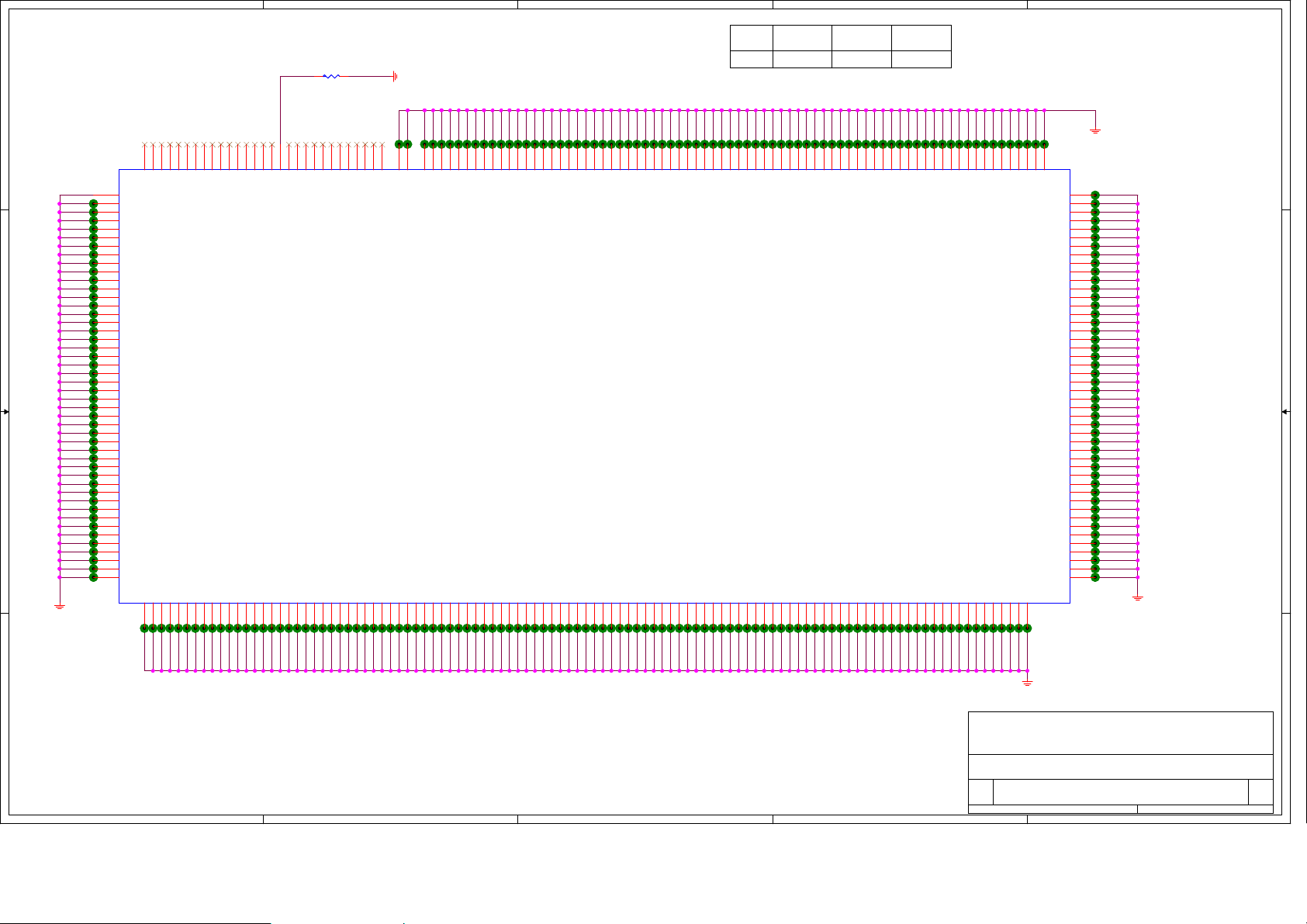

MS-9179 CLOCK BLOCK DIAGRAM

CK410B(ICS932S401EGLF)

45/46

D D

C C

B B

A A

14.318MHZ

Crystal

5

CPU0

CPU1

CPU2

CPU3

SRC0

SRC1

SRC2

SRC3

SRC4

PCI_F0

PCI_F1

PCI_F2

PCI_0

PCI_1

PCI_2

PCI_2

USB_48

REF0

42/43

39/40

36/37

16/17

18/19

21/22

23/24

26/27

9

10

11

3

4

5

6

13

55

MCH_CLK_P/N

2

DB12 00_C LK _P/N

2

CPU0_CLK_P/N

2

CPU1_CLK_P/N

2

ESI_SRC_CK_P/N

2

MCH_SRC_CK_P/N

2

SAS_SRC_CLK_P/N

2

ESB2_SRC_CK_P/N

2

DB800_SRC_C K _P/N

2

FWH_33MHZ_CLK

ESB2_33MHZ_CLK

SIO_33M HZ _CLK

1394_33MHZ_CLK

PCI_33MHZ_CLK

PLD _33MH Z_C LK

33MHZ CLK BUF

USB_48MHZ_CLK

IO_48M HZ_C LK

ESB2_14MHZ_CLK

GREENCREEN

CK DB1200

Dempsey CPU0

Dempsey CPU1

ESB2

GREENCREEN

SAS LSI 1064E CHIP

ESB2

CK DB800

FWH

ESB2

Super I/O

PCI SLOT

XC9536XL_C

PCICLK BUF

ESB2

Super I/O

ESB2

4

24.576MHZ

Crystal

IEEE 1394

CK DB1200

6/7

DIF0

9/10

DIF1

FBD0_CLK_P/N

13/14

DIF2

FBD1_CLK_P/N

16/17

DIF3

FBD2_CLK_P/N

19/20

DIF4

FBD3_CLK_P/N

24/25

DIF5

FBD4_CLK_P/N

32/33

DIF6

FBD5_CLK_P/N

35/36

DIF7

FBD6_CLK_P/N

39/40

DIF8

FBD7_CLK_P/N

42/43

DIF9

47/48

DIF10

CK DB800(ICS9D801BGLF)

PCIE16X_SL OT _SR C_CLK_P/N

8/9

DIF0

PCIE8X_SLO T_ SR C_CLK_P/N

12/13

DIF1

SATA_SRC_CLK_P/N

DIF2

16/17

PCICLK Buffer(ICW-W163)

PERR_33MHZ_CLK

CLK1

CLK2

CLK3

CLK4

3

TPM_33MHZ_C LK

5

XDP0_33MHZ_C LK

7

3

2

NB_FBD23_CLK _P/N

2

NB_FBD013_CLK _P/N

2

DDR II FBD DIMM 11

XDP0_BCLK_P/N

2

2

2

2

NB_FBD 23

NB_FBD 01

2

2

DDR II FBD DIMM 12

XDP

PCI EXPRESS X16 SLOT

PCI EXPRESS X8 SLOT

ESB2 SATA

GAL16V8D

Infineon

SLD9630

XDP

2

2

DDR II FBD DIMM 21

DDR II FBD DIMM 22

DDR II FBD DIMM 31

2

DDR II FBD DIMM 32

DDR II FBD DIMM 41

2

DDR II FBD DIMM 42

2

Micro- Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Clock Block Diagram

Size Document Number R ev

MS-9179

2

Date: Sheet

450Friday, August 26, 2005

1

of

0ACustom

5

4

3

2

1

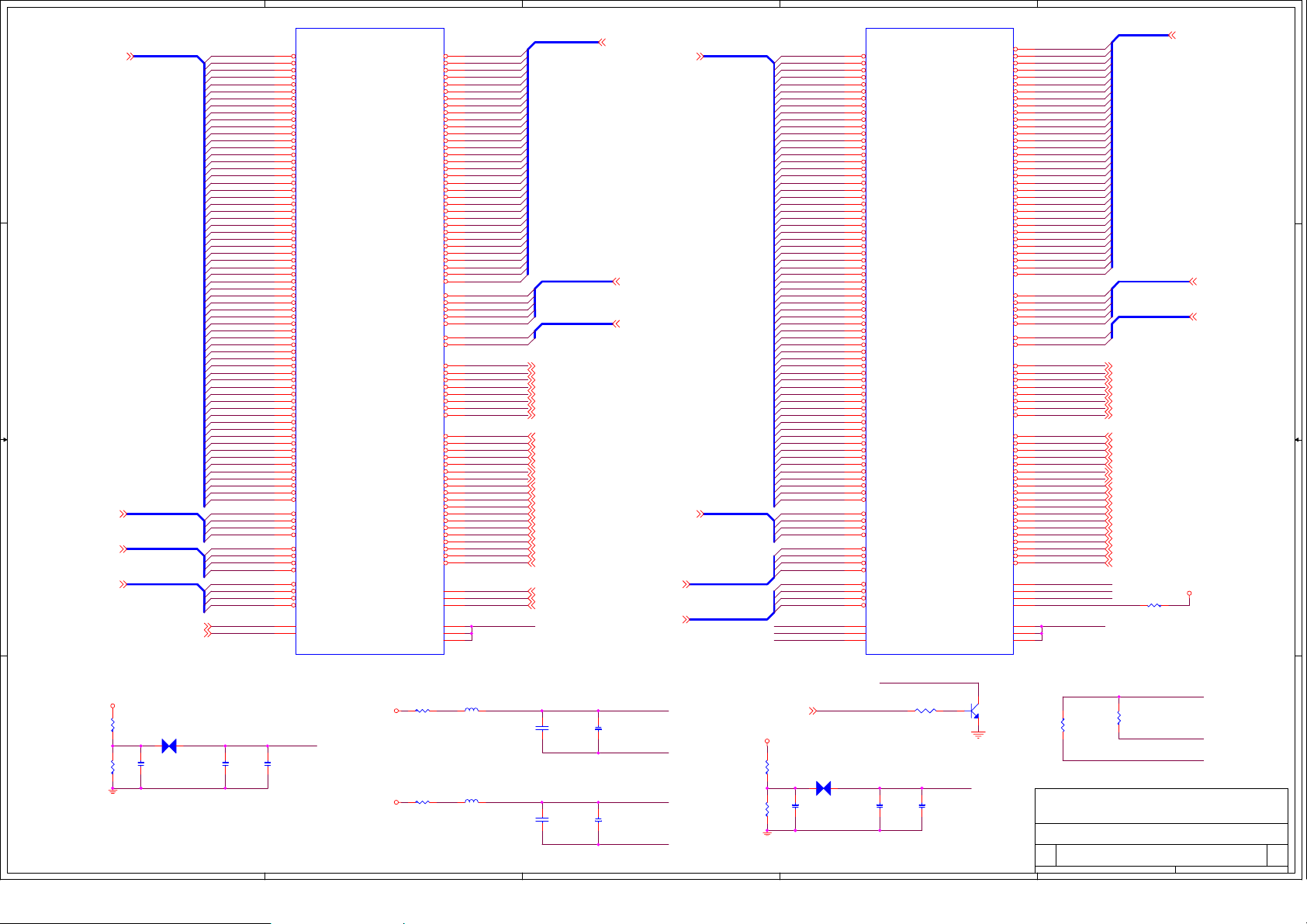

MS-9179 SYSTEM RESET & POWER ON SEQUENCINGBLOCK DIAGRAM

PS_PWROK_BUF

D D

P1V5 Reg

PWRGDENABLE

P1V5_PWRGD

Dempsey or Woodcrest

VTT_PWRGDPLD_VTT_PWRGD_3_3V

FSB_RESET_N

CPU_DBR_RST#

C C

VTTPWRGD

RESET#

DBR#

GREENCREEK

SYS_PWRGD_3_3V

PWRGOOD

P1V8 Reg

PWRGDENABLE

(LGA771 CPU)

FSB_RESET_N

P1V8_GD FSB_VTT_PWRGD

V_FSB_VTT Reg

PWRGDENABLE

CPU_VRD_PWR_GD

FSB_INIT#

INIT#

PWRGOOD

CPU_PWRGD

FSB_RESET_N

PLTRST_N

PLTRST_N

CLK_GD#

PLTRST_N

IDE_RSTDRV#

SUSCLK

ESB_PLTRST#

VRD0_PWRGD

VRD0_EN

VRD1_PWRGD

ESB2_PWRBTN_N

FP_RESET_N

HWM

B B

3.3V STBY

CPU_VRD_PWRGD

SYS_PWRGD_3_3V

RSM_RST_N

CPU_PWRGD

FBD_RESET

PWRBTN_N

SYS_RESET_N

VRMPWRGD

PWROK

RSMRST_N

CPUPWRGD

GPIO33

ESB2

INI T_N

SLP_S3_N

SLP_S4_N

SUSCLK

PCIRST_N

PERST_N

PXPWROK

PLTRST_IN_N

PLTRST_N

FSB_INIT#

SLP_S3_N

SLP_S4_N

SUSCLK

PCIRST_N

SYS_PWRGD_BUFF

PLTRST_N

ESB_PLTRST#

VRD1_EN

PSON_N

CK410

VTT_PWRGD#

DB1200

VTT_PWRGD#

DB800

PWRDWN_N

IO10

IO13

IO14

IO25

IO112

IO113

IO114

IO115

PLTRST_BUFF2#

SYS_PWRGD_BUFF

FSB_RESET_N

CPU_PWRGD

PS_ON_N PWR_OK

Power Supply

XC9536XL

XDP

RESET_N

PWRGD

FBD_RESET

SYS_PWRGD_3_3V

IO217

IO212

IO29

IO28

IO27

IO24

IO22

IO21

RESET_OUT#

PS_PWROK

VTT_PWRGD_3_3V

PLD_VTT_PWRGD_3_3V

SYS_PWRGD_3_3V

SYS_PWRGD_BUFF

PLTRST_BUFF2#

PLTRST_BUFF1#

PS_PWRGD_N

CPU_VRD_PWRGD

PCIE_RST#

CPU_DBR_RST#

PS_PWROK_BUF

PS_PWRGD_N

FBD SLOT

FSB_VTT_PWRGD

PLTRST_BUFF1#

FP_RESET_N

FWH

TPM

SSI Front Panel

A A

SIO_PWBTIN#

Super I/O

NS PC87366

ESB2_PWRBTN_N

PSON_N

SLP_S3_N

PERR

IDE_RSTDRV#

PCIE_RST#

PCIRST_N

PCI EXPRESS (SLOT X16 / X8)

SAS CHIP

PCI 32 (SLOT 1 & MiniPCI)

1394 CHIPIDE

SLP_S4_N

PLTRST_BUFF1#

5

4

3

2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, T ai wan. http://www.m s i .com.tw

Title

RESET & PWRGD Diagram

Size Docum en t N u m ber R ev

MS-9179

Date: Sheet

1

of

550Frid a y, August 26, 2005

0ACustom

5

4

3

2

1

MS-9179 SMBus Block Diagram

GREENCREEK

D D

C C

FBD0SCL

FBD0SDA

FBD1SCL

FBD1SDA

FBD2SCL

FBD2SDA

FBD2SCL

FBD2SDA

CFG_SCL

CFG_SDA

FBD0_SCL/SDA

2

FBD1_SCL/SDA

2

FBD2_SCL/SDA

2

FBD3_SCL/SDA

2

2

2

DIMM 21 DIMM 22

DIMM 31 DIMM 32

DIMM 41 DIMM 42

2

2

2

2

PCIX Slot 1

DIMM 12DIMM 11

2

2

2

CK410B

DB800

DB1200G

ESB2

2

SMBDATA

SMBCLK

B B

ESB2_SMBCLK/DAT(AUX)

2

2

PCIX Slot 2

SMBCLK/DAT(MAIN)

PCA9515

HWM AD T7 462 #1

2

2

2

Super I/O

NS PC87366

VRD VCORE0 IC

VRD VCORE1 IC

2

2

2

A A

5

HWM AD T7 462 #2

PCI-E xp re ss X16 Slot

PCI-E xp re ss X8 Slot

4

2

2

3

2

FBD +1.8V IC

SYS +1.5V IC

Micro -Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. htt p://www.msi.com.tw

Title

System SMBus Block Diagram

Size Docu m ent Nu m b er Rev

MS-9179

Date: Sheet

650Friday, August 26, 2005

of

1

0ACustom

5

4

3

2

1

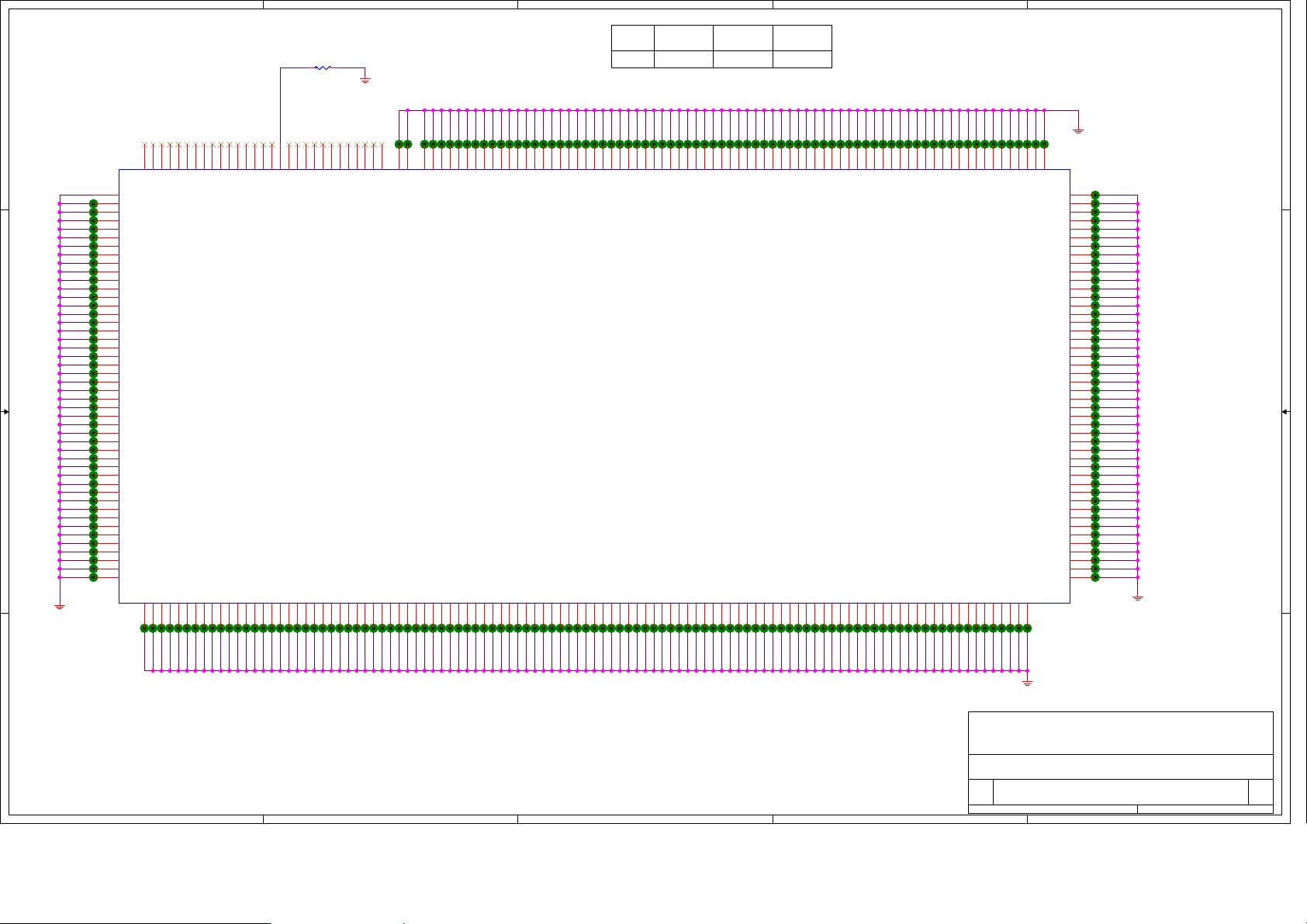

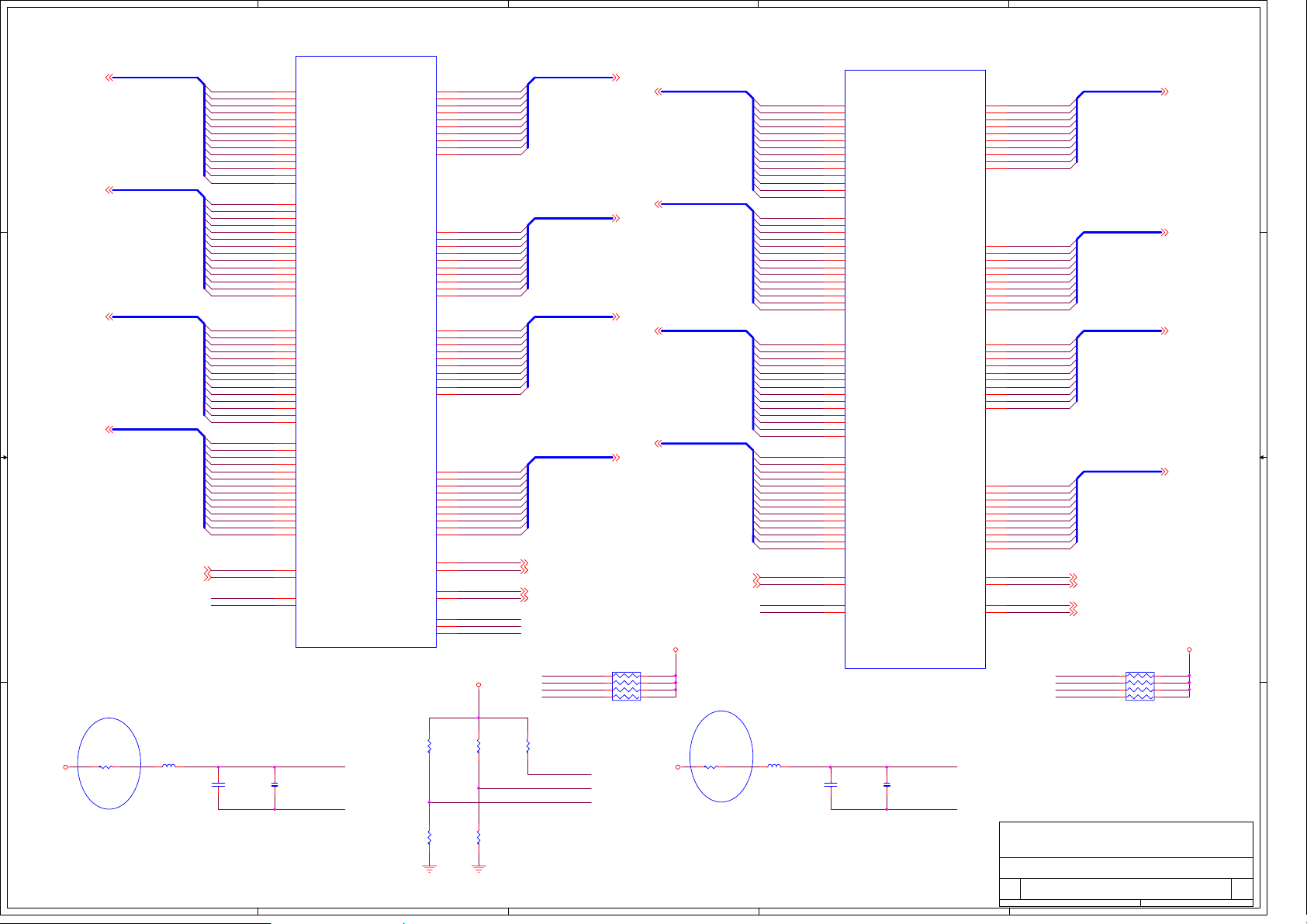

MS-9179 DDRII FBD Routing Block Diagram

Channel 1 Channel 2 Channel 3 Channel 4

Greencreek

D D

C C

NB0_P0~13

NB0_N0~13

SB0_P0~9

SB0_N0~9

FBD0SCL0

Channel 1Channel 2Channel 3Channel 2

FBD0SDA0

NB1_P0~13

NB1_N0~13

SB1_P0~9

SB1_N0~9

FBD0SCL1

FBD0SDA1

NB2_P0~13

NB2_N0~13

SB2_P0~9

SB2_N0~9

FBD0SCL2

FBD0SDA2

DIMM11

NB0_P0~13

NB0_N0~13

SB0_P0~9

SB0_N0~9

FBD0SCL0

FBD0SDA0

NB0_P0~13

NB0_N0~13

SB0_P0~9

SB0_N0~9

FBD0SCL0

FBD0SDA0

DIMM12

NB1_P0~13

NB1_N0~13

SB1_P0~9

SB1_N0~9

FBD0SCL1

FBD0SDA1

DIMM21

NB1_P0~13

NB1_N0~13

SB1_P0~9

SB1_N0~9

FBD0SCL1

FBD0SDA1

DIMM22

NB2_P0~13

NB2_N0~13

SB2_P0~9

SB2_N0~9

FBD0SCL2

FBD0SDA2

DIMM31

NB2_P0~13

NB2_N0~13

SB2_P0~9

SB2_N0~9

FBD0SCL2

FBD0SDA2

DIMM32

NB3_P0~13

NB3_N0~13

SB3_P0~9

SB3_N0~9

FBD0SCL3

FBD0SDA3

DIMM41

DIMM42

NB3_P0~13

NB3_N0~13

SB3_P0~9

SB3_N0~9

FBD0SCL3

FBD0SDA3

NB3_P0~13

NB3_N0~13

SB3_P0~9

SB3_N0~9

FBD0SCL3

FBD0SDA3

B B

NB_01_CLKP

NB_01_CLKN

NB_23_CLKP

NB_23_CLKN

DB1200G

DB1200G

CLKP0

CLKN0

CLKP1

CLKN1

CLKP2

CLKN2

CLKP3

CLKN3

CLKP5

CLKN5

CLKP4

CLKN4

CLKP6

CLKN6

CLKP7

CLKN7

DB1200G DB1200G DB1200G DB1200G DB1200G DB1200G DB1200G DB1200G

A A

Micro-Star Int'l Co., Ltd.

No.69, Li- D e St, J ung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

DDRII Routing Block Diagram

Size Doc u m ent N u m b er R e v

MS-9179

5

4

3

2

Date: Sheet

750Fr id ay, August 26, 2005

1

0ACustom

of

5

4

3

2

V_FSB_VTT

1

VCC0_SENSE2

VSS0_SENSE2

VCC0_SENSE1

CPU SIGNAL BLOCK

D D

FSB0_DBI#[3..0]14

C C

V_FSB_VTT

B B

A A

CPU1_TESTBUS11

FSB0_D[63..0]14

R228 X_51R

R229 51R

FSB0_DBI#[3..0]

FSB0_RESET_N14

FSB0_RSP_N14

FSB0_BPRI_N14

FSB0_TRDY_N14

FSB0_DEFER_N14

FSB_SMI#11,25

FSB_A20M#11,25

FSB0_FORCEPR#36

FSB_NMI11,25

FSB_INTR11,25

FSB_IGNNE#11,25

FSB_STPCLK#11,25

FSB_INIT#11,25

XDP0_TCK011,44

XDP0_TDI_FSB044

XDP0_TDO_FSB044

XDP0_TMS_MAIN11,16,44

XDP0_TRST#11,16,44

FSB0_GTL_IERR#23

FSB_FERR#11,25

FSB0_PROCHOT#48

FSB0_ADS_N14

FSB0_BNR_N14

FSB0_HIT_N14

FSB0_DBSY_N14

FSB0_DRDY_N14

FSB0_HITM_N14

FSB0_LOCK_N14

FSB0_BINIT_N14

FSB0_MCERR_N14

FSB0_SKTOCC#23,44

CPU0_THERMDA248

CPU0_THERMDC248

CPU0_THERMDA48

CPU0_THERMDC48

CPU_DBR_RST#11,44

R199 X_51R_0402

R185 0R

FSB0_VIDSEL36

P0_MS_ID144

P0_MS_ID044

FSB0_BSEL023

FSB0_BSEL123

FSB0_BSEL223

FSB0_D[63..0]

P0_MS_ID1

P0_MS_ID0

FSB0_A[35..3]14

FSB0_DBI#0

FSB0_DBI#1

FSB0_DBI#2

FSB0_DBI#3

FSB0_RESET_N

FSB0_RSP_N

FSB0_BPRI_N

FSB0_TRDY_N

FSB0_DEFER_N

FSB_SMI#

FSB_A20M#

FSB0_FORCEPR#

FSB_NMI

FSB_INTR

FSB_IGNNE#

FSB_STPCLK#

FSB_INIT#

XDP0_TCK0

XDP0_TDI_FSB0

XDP0_TDO_FSB0

XDP0_TMS_MAIN

XDP0_TRST#

FSB0_GTL_IERR#

FSB_FERR#

FSB0_PROCHOT#

P0_THERMTRIP_N

FSB0_ADS_N

FSB0_BNR_N

FSB0_HIT_N

FSB0_DBSY_N

FSB0_DRDY_N

FSB0_HITM_N

FSB0_LOCK_N

FSB0_BINIT_N

FSB0_MCERR_N

FSB0_SKTOCC#

CPU0_THERMDA2

CPU0_THERMDC2

CPU0_THERMDA

CPU0_THERMDC

CPU_DBR_RST#

CPU_BOOT

CPU0_TESTBUS

FSB0_VIDSEL

P0_LL_ID0

P0_LL_ID1

P0_MS_ID1

P0_MS_ID0

FSB0_D63

FSB0_D62

FSB0_D61

FSB0_D60

FSB0_D59

FSB0_D58

FSB0_D57

FSB0_D56

FSB0_D55

FSB0_D54

FSB0_A[35..3]

A8

G11

D19

C20

G23

H4

G8

E3

G7

P2

K3

AK6

L1

K1

N2

M3

P3

AE1

AD1

AF1

AC1

AG1

AB2

R3

AL2

M2

D2

C2

D4

B2

C1

E4

C3

AD3

AB3

AE8

AJ7

AH7

AL1

AK1

AC2

Y1

AH2

AN7

AA2

V2

V1

W1

G29

H30

G30

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

DBI0#

DBI1#

DBI2#

DBI3#

RESET#

RSP#

BPRI#

TRDY#

DEFER#

SMI#

A20M#

FORCEPR#

LINT1/NMI

LINT0/INTR

IGNNE#

STPCLK#

INIT#

TCK

TDI

TDO

TMS

TRST#

IERR#

FERR#/PBE#

PROCHOT#

THERMTRIP#

ADS#

BNR#

HIT#

DBSY#

DRDY#

HITM#

LOCK#

BINIT#

MCERR#

SKTOCC#

THERMDA2

THERMDC2

THERMDA

THERMDC

DBR#

BOOTSELECT

TEST_BUS

VID_SELECT

LL_ID1

LL_ID0

MS_ID1

MS_ID0

BSEL0

BSEL1

BSEL2

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

FSB0_D52

FSB0_D53

FSB0_A35

FSB0_A31

FSB0_A33

FSB0_A30

FSB0_A32

FSB0_A34

AJ6

AJ5

AH5

AH4

AG5

AG4

A35#

A34#

A33#

A32#

A31#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

A14

C14

C15

FSB0_D50

FSB0_D51

F21

E22

D17

D20

D22

G22

G21

FSB0_D47

FSB0_D46

FSB0_D43

FSB0_D45

FSB0_D48

FSB0_D44

FSB0_D49

FSB0_A23

FSB0_A27

FSB0_A22

FSB0_A24

FSB0_A29

FSB0_A28

AG6

AF4

A30#

A29#

D43#

D42#

F20

E21

FSB0_D41

FSB0_D42

FSB0_A21

FSB0_A26

FSB0_A25

AF5

AB4

AC5

AB5

AA5

AD6

AA4

A28#

A27#

A26#

A25#

A24#

A23#

A22#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

F18

F17

E19

E18

E16

G17

G18

FSB0_D34

FSB0_D38

FSB0_D35

FSB0_D36

FSB0_D39

FSB0_D37

FSB0_D40

FSB0_A20

FSB0_A19

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

E15

G16

FSB0_D33

FSB0_D32

FSB0_A16

FSB0_A18

FSB0_A17

AB6

D32#

D31#

D30#

F15

G15

G14

FSB0_D31

FSB0_D30

FSB0_D29

FSB0_A14

FSB0_A13

FSB0_A11

FSB0_A12

FSB0_A10

FSB0_A15

U6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D29#

D28#

D27#

D26#

D25#

D24#

F14

F12

F11

E13

D13

G13

FSB0_D28

FSB0_D26

FSB0_D27

FSB0_D24

FSB0_D25

FSB0_D23

FSB0_A7

FSB0_A8

FSB0_A6

FSB0_A9

A9#T5A8#R4A7#M4A6#L4A5#L5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

D10

FSB0_D21

FSB0_D22

FSB0_D19

FSB0_D20

FSB0_A4

FSB0_A5

FSB0_D18

FSB0_D17

VSS0_SENSE1

AN4

M5

AN3

AL7

AL8

VSS_DIE_SENSE

VCC_DIE_SENSE

VSS_DIE_SENSE2

VCC_DIE_SENSE2

D14#

D13#

D12#D8D11#

D10#

B12

B10

A11

D11

C12

C11

FSB0_D10

FSB0_D15

FSB0_D13

FSB0_D12

FSB0_D14

FSB0_D16 FSB0_A3

FSB0_D9

FSB0_D11

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

FSB0_D6

FSB0_D5

FSB0_D7

FSB0_D8

R181 10_0402

R182 10_0402

R184 10_0402

R183 10_0402

P0_VID3

P0_VID1

P0_VID4

P0_VID2

P0_VID5

P0_VID6

AM5

AL4

AK4

AL6

AM3

AL5

VID6

VID5

VID4

VID3

VID2

VID1

GTLREF_DATA_C1

GTLREF_ADD_C1

GTLREF_DATA_C0

GTLREF_ADD_C0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

PWRGOOD

COMP7

COMP6

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

B4

FSB0_D3

FSB0_D1

FSB0_D2

FSB0_D0

FSB0_D4

P0_VID0

AM2

CPU1A

VID0

BCLK1

BCLK0

RS2#

RS1#

RS0#

AP1#

AP0#

BR1#

BR0#

DP3#

DP2#

DP1#

DP0#

TEJAS

P0_VID[6 ..0 ]

F2

H2

G10

H1

AG3

AF2

AG2

AD2

AJ1

AJ2

J6

K6

M6

J5

K4

L2

P1

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

G28

F28

A3

F5

B3

U3

U2

H5

F3

N1

AE3

Y3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

P0_VID[6..0] 36,48

P0_GTLREF_DATA1

P0_GTLREF_ADD1

P0_GTLREF_DATA0

P0_GTLREF_ADD0

FSB0_BPM_N5

FSB0_BPM_N4

FSB0_BPM_N3

FSB0_BPM_N2

FSB0_BPM_N1

FSB0_BPM_N0

FSB0_REQ_N4

FSB0_REQ_N3

FSB0_REQ_N2

FSB0_REQ_N1

FSB0_REQ_N0

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI0_1

CK_H_P0_N

CK_H_P0_P

FSB0_RS2_N

FSB0_RS1_N

FSB0_RS0_N

FSB0_AP1

FSB0_AP0

FSB0_BR_N1

FSB0_BR_N0

CPU_PWRGD

H_COMP7

H_COMP6

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

FSB0_DP_N3

FSB0_DP_N2

FSB0_DP_N1

FSB0_DP_N0

FSB0_ADSTB_N1

FSB0_ADSTB_N0

FSB0_DSTBP_N3

FSB0_DSTBP_N2

FSB0_DSTBP_N1

FSB0_DSTBP_N0

FSB0_DSTBN_N3

FSB0_DSTBN_N2

FSB0_DSTBN_N1

FSB0_DSTBN_N0

VCC0_SENSE 36

VSS0_SENSE 36

THERMTRIP_N11,25

PLACE BPM TERMINATION NEAR CPU

FSB0_BPM_N3

FSB0_BPM_N2

FSB0_BPM_N5 14,44

FSB0_BPM_N4 14,44

FSB0_BPM_N3 44

FSB0_BPM_N2 44

FSB0_BPM_N1 44

FSB0_BPM_N0 44

FSB0_REQ_N[4..0]

R204 51R

R207 51R

R226 51R

R218 51R

R90 51R

R230 51R

CK_H_P0_N 33

CK_H_P0_P 33

FSB0_RS2_N 14

FSB0_RS1_N 14

FSB0_RS0_N 14

FSB0_AP1 14

FSB0_AP0 14

FSB0_BR_N1 14

FSB0_BR_N0 14

CPU_PWRGD 11,25,44

R212 49.9RST

R200 49.9RST

R210 49.9RST

R203 49.9RST

R208 49.9RST C210

R217 49.9RST

R209 49.9RST

R140 49.9RST

FSB0_DP_N3 14

FSB0_DP_N2 14

FSB0_DP_N1 14

FSB0_DP_N0 14

FSB0_ADSTB_N[1..0]

FSB0_DSTBP_N[3..0]

FSB0_DSTBN_N[3..0]

FSB0_BPM_N1

FSB0_BPM_N0

FSB0_REQ_N[4..0] 14

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

X_0.1u

FSB0_ADSTB_N[1..0] 14

FSB0_DSTBP_N[3..0] 14

FSB0_DSTBN_N[3..0] 14

R220 51R

R225 51R

R214 51R

R237 51R

R934 51R_B

R202 51R

R219 51R

R215 51R

R211 51R

R213 51R

R216 51R

V_FSB_VTT

V_FSB_VTT

R146

49.9RST

R160

100RST

V_FSB_VTT

R221

49.9RST

R236

100RST

FSB0_PROCHOT#

THERMTRIP_N

FSB_FERR#

FSB0_BR_N0

FSB0_RESET_N

FSB0_GTL_IERR#

FSB0_BR_N1

R205 2.2R

P0_THERMTRIP_NTHERMTRIP_N

For VR11 Load Line

P0_LL_ID036

LL_ID1 LL_ID0 Description

P0_GTLREF_ADD0

C145

1u

220p-0402

C200

1u

220p-0402

close to CPU0 pin

by CPU

00

001

1

11

CP1

X_COPPER

C150

CP2

X_COPPER

C208

CPU_PWRGD

P0_LL_ID0

P0_LL_ID1

Reserved

Dempsey

Reserved

Reserved

V_FSB_VTT

P3V3 P3V3

R201

R231

4.7K

4.7K

P0_GTLREF_DATA0

C133

220p-0402

P0_GTLREF_DATA1P0_GTLREF_ADD1

C209

220p-0402

R206

300

C201

X_100p

P3V3_STBY

R178 510R

5

FSB0_SKTOCC#

Micro -Star Int'l Co., Ltd.

No. 6 9, L i -D e S t , Ju ng -H e City , T ai pe i H s i en , Ta iwa n . h t tp :/ / www. ms i. c om .t w

Title

Intel LGA771 Signal Block

Size Document Number Re v

MS-9179

4

3

2

Date: Sheet

850Friday, August 26, 2005

1

0ACustom

of

5

VCORE

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

VCORE

AF19

AF18

AF15

D D

C C

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AE9

AB8

AA8

VCORE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

Y27

Y28

Y29

VCC

VCC

VCCW8VCC

W30

VCC

VCC

W29

VCC

VCC

W28

VCC

VCC

W27

VCC

VCC

W26

VCC

VCC

W25

VCC

VCC

W24

VCC

VCC

W23

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

U28

U29

U30

VCC

VCC

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

U23

4

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

VCC

VCCN8VCCP8VCCR8VCC

AJ18

N30

VCC

VCC

AJ19

N29

VCC

VCC

AJ21

N28

VCC

VCC

AJ22

N27

VCC

VCC

AJ25

N26

VCC

VCC

AJ26

VCC

VCC

N25

3

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

M26

M25

M24

M23

K30

AN9

AN8

N23

N24

M27

M28

M29

M30

VCC

VCC

AN15

VCC

VCC

AN26

AN18

VCC

VCC

AN25

AN19

VCC

AN21

AN30

2

AN22

VCC

VCC

VCCPLL

VCCIOPLL

VTTPWRGD

VTT_OUT1

VTT_OUT0

VTT_SEL

NONE

NONE

AN29

CPU1B

VCCA

VSSA

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

TEJAS

A23

B23

D23

C23

F30

E30

A25

A26

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

H0_VCCA

H0_VSSA

H0_VCCPLL

VTT_PWRGD

V_FSB_VTT

VTT_PWRGD 12,44

R933 X_1K_B

NOPOP

1

V_FSB_VTT

PLACE COMPONENTS AS CLO SE AS PO SSIBL E TO PR O CESSO R SO CK ET

It support DC curr ent if 100mA.

L1 10uH-0805-0.1A

L2 10uH-0805-0.1A

DC voltage drop should

B B

EC5

22u-1206

EC6

10u-1206

H0_VCCA

C52

X_1u/10V

H0_VSSA

NOPOP

be less than 70mV.

R138 0R

P1V5

A A

C902

0.1u_B

C900

0.1u_B

C55

0.1u

5

C115

0.01u

C62

0.1u

C113

4.7u-0805

V_FSB_VTTV_FSB_VTT

C57

10u-1206

C114

4.7u-0805

C56

10u-1206

H0_VCCPLL

4

C903

0.1u_B

C904

0.1u_B

Micro-Star Int'l Co., Ltd.

No.69, Li-D e St, Ju ng-H e City , Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Intel L G A7 71 Power

Size Document Number R ev

MS-9179

3

2

Date: Sheet

950Friday, A ug u st 26, 2005

1

0ACustom

of

5

4

3

2

1

R702 Nocona-T Dempsey-T Dempsey

R172 X_49.9RST

D D

AN27

AC4

AE4

D14

E23

F23

B13

P5

RESVDE5RESVDE6RESVDE7RESVD

RESVDF6RESVD

VSS

VSS

VSS

VSS

VSS

AF3

AF27

AF28

AF29

VSS

AF30

E1

RESVD

VSS

AF6

AF7

RESVDJ3RESVDN4RESVD

RESVDN5RESVD

VSS

VSS

VSS

VSS

AG10

AG13

AG16

AE6

AG17

VSS

AN5

RESVD

VSS

AG20

E24

W2

D16

A20

F1

VSS

A12

A15

A18

A21

A24

AA23

AA24

AA25

AA26

AA27

C C

B B

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

RESVDC9RESVD

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AE30

RESVD

VSS

AE5

AE7

VSS

RESVD

RESVD

RESVDD1RESVD

RESVD

RESVDG6RESVD

RESVDG5RESVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AN6

RESVD

VSS

AG23

AJ3

RESVD

VSS

AG24

AK3

AG7

F29

RESVD

RESVD

VSS

VSS

AH1

AN28

NONE

NONE

VSS

VSS

VSS

AH10

AH13

AH16

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH17

AH20

AH23

AH24

AJ10

VSS

V30

V29

V28

V27

V26

V25

V24

V23

VSSV3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AK2

AK10

AK13

AK16

AK17

AK20

Optional YES NO

R30

R29

R28

R27

R26

R25

R24

R23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK5

AK7

AL10

AL13

AK23

AK24

AK27

AK28

AK29

AL16

AK30

P30

AL17

VSS

P29

AL20

P28

VSS

VSS

AL23

VSS

VSS

P27

AL24

VSS

VSS

P26

AL27

VSS

VSS

P25

VSS

VSS

AL28

Woodcrest

P24

P23

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

AL3

AM1

AM10

AM13

AM16

L30

L29

L28

L27

L26

L25

L24

L23

VSSL3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSK7VSSK5VSSK2VSSJ7VSSJ4VSSH9VSSH8VSSH7VSSH6VSSH3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB1VSS

AN1

AM4

AM17

AM20

AM7

AM23

AM24

AM27

AM28

AN2

AN10

AN13

AN16

AN17

AN20

AN23

AN24

VSSB5VSS

B8

H29

H28

H27

H26

H25

H24

CPU1C

VSS

VSS

VSS

VSS

VSS

H23

VSS

H22

VSS

H21

VSS

H20

VSS

H19

VSS

H18

VSS

H17

VSS

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

VSS

VSS

VSS

VSSC4VSS

VSS

B17

B11

B14

TEJAS

C7

B20

B24

A A

5

4

3

2

Micro- S tar Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com .tw

Title

Intel LGA 771 GND

Size Docume nt Number Rev

MS-9179

Date: Sheet

1

of

10 50Fr id ay, August 26, 2005

0ACustom

5

4

3

2

V_FSB_VTT

1

R457 51R

R408 51R

R478 51R

R427 51R

VCC1_SENSE2

VSS1_SENSE2

VCC1_SENSE1

D D

FSB1_DBI#[3..0]14

C C

V_FSB_VTT

B B

FSB1_D[63..0]14

R420 51R

R419 51R

FSB1_DBI#[3..0]

FSB1_RESET_N14,44

FSB1_RSP_N14

FSB1_BPRI_N14

FSB1_TRDY_N14

FSB1_DEFER_N14

FSB_SMI#8,25

FSB_A20M#8,25

FSB1_FORCEPR#38

FSB_NMI8,25

FSB_INTR8,25

FSB_IGNNE#8,25

FSB_STPCLK#8,25

FSB_INIT#8,25

XDP0_TCK08,44

XDP0_TDI_FSB144

XDP0_TDO_FSB144

XDP0_TMS_MAIN8,16,44

XDP0_TRST#8,16,44

FSB1_GTL_IERR#23

FSB_FERR#8,25

FSB1_PROCHOT#48

FSB1_ADS_N14

FSB1_BNR_N14

FSB1_HIT_N14

FSB1_DBSY_N14

FSB1_DRDY_N14

FSB1_HITM_N14

FSB1_LOCK_N14

FSB1_BINIT_N14

FSB1_MCERR_N14

FSB1_SKTOCC#44

CPU1_THERMDA248

CPU1_THERMDC248

CPU1_THERMDA48

CPU1_THERMDC48

CPU_DBR_RST#8,44

R404 X_51R_0402

CPU1_TESTBUS8

FSB1_VIDSEL38

P1_MS_ID144

P1_MS_ID044

FSB1_BSEL023

FSB1_BSEL123

FSB1_BSEL223

FSB1_D[63..0]

P1_MS_ID1

P1_MS_ID0

FSB1_A[35..3]14

FSB1_DBI#0

FSB1_DBI#1

FSB1_DBI#2

FSB1_DBI#3

FSB1_RESET_N

FSB1_RSP_N

FSB1_BPRI_N

FSB1_TRDY_N

FSB1_DEFER_N

FSB_SMI#

FSB_A20M#

FSB1_FORCEPR#

FSB_NMI

FSB_INTR

FSB_IGNNE#

FSB_STPCLK#

FSB_INIT#

XDP0_TCK0

XDP0_TDI_FSB1

XDP0_TDO_FSB1

XDP0_TMS_MAIN

XDP0_TRST#

FSB1_GTL_IERR#

FSB_FERR#

FSB1_PROCHOT#

P1_THERMTRIP_N

FSB1_ADS_N

FSB1_BNR_N

FSB1_HIT_N

FSB1_DBSY_N

FSB1_DRDY_N

FSB1_HITM_N

FSB1_LOCK_N

FSB1_BINIT_N

FSB1_MCERR_N

FSB1_SKTOCC#

CPU1_THERMDA2

CPU1_THERMDC2

CPU1_THERMDA

CPU1_THERMDC

CPU_DBR_RST#

CPU1_BOOT

CPU1_TESTBUS

FSB1_VIDSEL

P1_LL_ID0

P1_LL_ID1

P1_MS_ID1

P1_MS_ID0

FSB1_BSEL0

FSB1_BSEL1

FSB1_BSEL2

FSB1_D63

FSB1_D62

FSB1_D61

FSB1_D60

FSB1_D59

FSB1_D58

FSB1_D57

FSB1_D56

FSB1_D55

FSB1_D54

G11

D19

C20

G23

AK6

AE1

AD1

AF1

AC1

AG1

AB2

AD3

AB3

AE8

AH7

AK1

AC2

AH2

AN7

AA2

G29

H30

G30

C21

C18

A8

H4

G8

E3

G7

P2

K3

L1

K1

N2

M3

P3

R3

AL2

M2

D2

C2

D4

B2

C1

E4

C3

AJ7

AL1

Y1

V2

V1

W1

B22

A22

A19

B19

B21

B18

A17

B16

DBI0#

DBI1#

DBI2#

DBI3#

RESET#

RSP#

BPRI#

TRDY#

DEFER#

SMI#

A20M#

FORCEPR#

LINT1/NMI

LINT0/INTR

IGNNE#

STPCLK#

INIT#

TCK

TDI

TDO

TMS

TRST#

IERR#

FERR#/PBE#

PROCHOT#

THERMTRIP#

ADS#

BNR#

HIT#

DBSY#

DRDY#

HITM#

LOCK#

BINIT#

MCERR#

SKTOCC#

THERMDA2

THERMDC2

THERMDA

THERMDC

DBR#

BOOTSELECT

TEST_BUS

VID_SELECT

LL_ID1

LL_ID0

MS_ID1

MS_ID0

BSEL0

BSEL1

BSEL2

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

FSB1_A[35..3]

FSB1_A35

D52#

D51#

D50#

D49#

A14

C14

C15

D17

FSB1_A22

FSB1_A19

FSB1_A16

FSB1_A12

FSB1_A11

FSB1_A31

FSB1_A28

FSB1_A32

FSB1_A33

FSB1_A34

FSB1_A30

AJ6

AJ5

AH5

AH4

AG5

AG4

A35#

A34#

A33#

A32#

A31#

D48#

D47#

D46#

D45#

D44#

F21

E22

D20

D22

G22

G21

FSB1_A23

FSB1_A29

FSB1_A27

FSB1_A24

FSB1_A26

FSB1_A25

AG6

AF4

AF5

AB4

AC5

AB5

AA5

AD6

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

F20

F18

F17

E21

E19

E18

G17

G18

FSB1_A21

AA4

A22#

D35#

E16

FSB1_A20

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

E15

G16

FSB1_A18

FSB1_A17

AB6

D32#

D31#

D30#

F15

G15

G14

FSB1_A15

FSB1_A14

FSB1_A13

FSB1_A10

U6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D29#

D28#

D27#

D26#

D25#

D24#

F14

F12

F11

E13

D13

G13

FSB1_A7

FSB1_A6

FSB1_A9

FSB1_A8

A9#T5A8#R4A7#M4A6#L4A5#L5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

D10

FSB1_A5

FSB1_A4

CPU SIGNAL BLOCK

VSS1_SENSE1

FSB1_A3

AL8

AN4

M5

AN3

AL7

VSS_DIE_SENSE

VCC_DIE_SENSE

VSS_DIE_SENSE2

VCC_DIE_SENSE2

D14#

D13#

D12#D8D11#

D10#

B12

B10

A11

D11

C12

C11

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

R305 10_0402

R307 10_0402

R314 10_0402

R309 10_0402

P1_VID1

P1_VID6

P1_VID3

P1_VID5

P1_VID4

P1_VID2

AM5

AL4

AK4

AL6

AM3

AL5

VID6

VID5

VID4

VID3

VID2

VID1

GTLREF_DATA_C1

GTLREF_ADD_C1

GTLREF_DATA_C0

GTLREF_ADD_C0

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

PWRGOOD

COMP7

COMP6

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

B4

P1_VID0

AM2

CPU2A

VID0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

BCLK1

BCLK0

RS2#

RS1#

RS0#

AP1#

AP0#

BR1#

BR0#

DP3#

DP2#

DP1#

DP0#

TEJAS

P1_VID[6 ..0 ]

P1_GTLREF_DATA1

F2

P1_GTLREF_ADD1

H2

P1_GTLREF_DATA0

G10

P1_GTLREF_ADD0

H1

FSB1_BPM_N5

AG3

FSB1_BPM_N4

AF2

FSB1_BPM_N3

AG2

FSB1_BPM_N2

AD2

FSB1_BPM_N1

AJ1

FSB1_BPM_N0

AJ2

FSB1_REQ_N4

J6

FSB1_REQ_N3

K6

FSB1_REQ_N2

M6

FSB1_REQ_N1

J5

FSB1_REQ_N0

K4

H1_TESTHI11

L2

H1_TESTHI10

P1

H1_TESTHI9

G4

H1_TESTHI8

G3

F24

G24

G26

G27

G25

F25

W3

F26

G28

F28

A3

F5

B3

U3

U2

H5

F3

CPU_PWRGD

N1

H1_COMP7

AE3

H1_COMP6

Y3

H1_COMP5

T2

H1_COMP4

J2

H1_COMP3

R1

H1_COMP2

G2

H1_COMP1

T1

H1_COMP0

A13

FSB1_DP_N3

J17

FSB1_DP_N2

H16

FSB1_DP_N1

H15

FSB1_DP_N0

J16

FSB1_ADSTB_N1

AD5

FSB1_ADSTB_N0

R6

FSB1_DSTBP_N3

C17

FSB1_DSTBP_N2

G19

FSB1_DSTBP_N1

E12

FSB1_DSTBP_N0

B9

FSB1_DSTBN_N3

A16

FSB1_DSTBN_N2

G20

FSB1_DSTBN_N1

G12

FSB1_DSTBN_N0

C8

VCC1_SENSE

VSS1_SENSE

P1_VID[6..0] 38,48

H1_TESTHI2_7

H1_TESTHI0_1

CK_H_P1_N

CK_H_P1_P

FSB1_RS2_N

FSB1_RS1_N

FSB1_RS0_N

FSB1_AP1

FSB1_AP0

FSB1_BR_N1

FSB1_BR_N0

VCC1_SENSE 38

VSS1_SENSE 38

FSB1_BPM_N3

FSB1_BPM_N2

FSB1_BPM_N1

FSB1_BPM_N0

PLACE BPM TERMINATION NEAR CPU

FSB1_BPM_N5 14,44

FSB1_BPM_N4 14,44

FSB1_BPM_N3 44

FSB1_BPM_N2 44

FSB1_BPM_N1 44

FSB1_BPM_N0 44

FSB1_REQ_N[4..0]

R415 51R

R413 51R

R407 51R

R406 51R

R248 51R

R252 51R

CK_H_P1_N 33

CK_H_P1_P 33

FSB1_RS2_N 14

FSB1_RS1_N 14

FSB1_RS0_N 14

FSB1_AP1 14

FSB1_AP0 14

FSB1_BR_N1 14

FSB1_BR_N0 14

CPU_PWRGD 8,25,44

R423 49.9RST

R414 49.9RST

R418 49.9RST

R410 49.9RST

R416 49.9RST

R411 49.9RST

R417 49.9RST

R291 49.9RST

FSB1_DP_N3 14

FSB1_DP_N2 14

FSB1_DP_N1 14

FSB1_DP_N0 14

FSB1_ADSTB_N[1..0]

FSB1_DSTBP_N[3..0]

FSB1_DSTBN_N[3..0]

R459 51R

R458 51R

R424 51R

R425 51R

V_FSB_VTT

FSB1_ADSTB_N[1..0] 14

FSB1_DSTBP_N[3..0] 14

FSB1_DSTBN_N[3..0] 14

THERMTRIP_N8,25

FSB1_REQ_N[4..0] 14

V_FSB_VTT

V_FSB_VTT

C484

X_0.1u

V_FSB_VTT

R421 51R

V_FSB_VTT

R460

49.9RST

R462

100RST

V_FSB_VTT

R463

49.9RST

R464

100RST

FSB1_PROCHOT#

FSB1_BR_N0

FSB1_RESET_N

FSB1_GTL_IERR#

FSB1_BR_N1

R412 2.2R

P1_THERMTRIP_NTHERMTRIP_N

For VR11 Load Line

P3V3P3V3

R422

4.7K

P1_LL_ID038

P1_GTLREF_ADD1 P1_GTLREF_DATA1

C471

1u

P1_GTLREF_ADD0 P1_GTLREF_DATA0

C469

1u

P1_LL_ID0

P1_LL_ID1

CP7

X_COPPER

C470

220p-0402

CP8

X_COPPER

C472

220p-0402

C480

220p-0402

R426

C462

220p-0402

4.7K

FSB1_D45

FSB1_D50

FSB1_D48

FSB1_D44

FSB1_D47

FSB1_D51

FSB1_D52

A A

P3V3_STBY

R468 4.7K

5

FSB1_SKTOCC#

FSB1_D53

FSB1_D46

FSB1_D49

FSB1_D37

FSB1_D36

FSB1_D41

FSB1_D42

FSB1_D43

FSB1_D34

FSB1_D39

FSB1_D33

FSB1_D35

FSB1_D40

FSB1_D38

4

FSB1_D30

FSB1_D32

FSB1_D31

FSB1_D29

FSB1_D22

FSB1_D21

FSB1_D18

FSB1_D12

FSB1_D11

FSB1_D26

FSB1_D23

FSB1_D25

FSB1_D28

FSB1_D27

FSB1_D24

FSB1_D15

FSB1_D20

FSB1_D13

FSB1_D10

FSB1_D16

FSB1_D17

FSB1_D19

FSB1_D14

FSB1_D8

FSB1_D7

FSB1_D9

FSB1_D6

FSB1_D5

FSB1_D4

FSB1_D2

FSB1_D3

FSB1_D1

FSB1_D0

Micro -Star Int'l Co., Ltd.

No. 6 9, L i -D e S t , Ju ng -H e City , T ai pe i H s i en , Ta iwa n . h t tp :/ / www. ms i. c om .t w

Title

Intel LGA775 Signal Block

Size Document Number Re v

MS-9179

3

2

Date: Sheet

11 50Friday, August 26, 2005

1

0ACustom

of

5

VCORE1

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

VCORE1

AF19

AF18

AF15

D D

C C

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AE9

AB8

AA8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

VCORE1

Y30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

Y27

Y28

Y29

VCC

VCC

VCCW8VCC

W30

VCC

VCC

W29

VCC

VCC

W28

VCC

VCC

W27

VCC

VCC

W26

VCC

VCC

W25

VCC

VCC

W24

VCC

VCC

W23

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

U28

U29

U30

VCC

VCC

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

U24

VCC

VCC

AH22

VCC

U23

4

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

VCC

VCCN8VCCP8VCCR8VCC

AJ18

N30

VCC

VCC

AJ19

N29

VCC

VCC

AJ21

N28

VCC

VCC

AJ22

N27

VCC

VCC

AJ25

N26

VCC

VCC

AJ26

VCC

VCC

N25

3

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

M26

M25

M24

M23

K30

AN9

AN8

N23

N24

M27

M28

M29

M30

VCC

VCC

AN15

VCC

VCC

AN26

AN18

VCC

VCC

AN25

AN19

VCC

AN21

AN30

2

AN22

VCC

VCC

VCCPLL

VCCIOPLL

VTTPWRGD

VTT_OUT1

VTT_OUT0

VTT_SEL

NONE

NONE

AN29

CPU2B

VCCA

VSSA

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

TEJAS

A23

B23

D23

C23

F30

E30

A25

A26

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

H1_VCCA

H1_VSSA

H1_VCCPLL

VTT_PWRGD

1

V_FSB_VTT

VTT_PWRGD 9,44

R244 X_1K

V_FSB_VTT

PLACE COMPONENTS AS CLO SE AS PO SSIBL E TO PR O CESSO R SO CK ET

It support DC curr ent if 100mA.

L6 10uH-0805-0.1A

L7 10uH-0805-0.1A

B B

DC voltage drop should

be less than 70mV.

5

C250

0.1u

C390

10u-1206

R255 0R

C251

0.1u

C354

10u-1206

P1V5

V_FSB_VTT

A A

V_FSB_VTT

C249

0.01u

C932

0.1u_B

C934

0.1u_B

EC10

22u-1206

C936

0.1u_B

EC11

10u-1206

C252

4.7u-0805

C930

0.1u_B

H1_VCCA

C265

X_1u/10V

H1_VSSA

H1_VCCPLL

C253

4.7u-0805

4

Micro-Star Int'l Co., Ltd.

No.69, Li-D e St, Ju ng-H e City , Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Intel L G A7 75 Power

Size Document Number R ev

MS-9179

3

2

Date: Sheet

12 50Friday, A ug u st 26, 2005

1

0ACustom

of

5

4

3

2

1

R654 Nocona-T Dempsey-T Dempsey

Woodcrest

Optional YES NO

R327 X_49.9RST

D D

AN27

AC4

AE4

D14

E23

F23

B13

P5

RESVDE5RESVDE6RESVDE7RESVD

RESVDF6RESVD

VSS

VSS

VSS

VSS

VSS

AF3

AF27

AF28

AF29

VSS

AF30

E1

RESVD

VSS

AF6

AF7

RESVDJ3RESVDN4RESVD

RESVDN5RESVD

VSS

VSS

VSS

VSS

AG10

AG13

AG16

AE6

AG17

VSS

AN5

RESVD

VSS

AG20

E24

W2

D16

A20

F1

VSS

A12

A15

A18

A21

A24

AA23

AA24

AA25

AA26

AA27

C C

B B

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

RESVDC9RESVD

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AE30

RESVD

VSS

AE5

AE7

VSS

RESVD

RESVD

RESVDD1RESVD

RESVD

RESVDG6RESVD

RESVDG5RESVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AN6

RESVD

VSS

AG23

AJ3

RESVD

VSS

AG24

AK3

AG7

F29

RESVD

RESVD

VSS

VSS

AH1

AN28

NONE

NONE

VSS

VSS

VSS

AH10

AH13

AH16

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH17

AH20

AH23

AH24

AJ10

VSS

V30

V29

V28

V27

V26

V25

V24

V23

VSSV3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ13

AJ16

AJ17

AJ20

AJ23

AJ4

AJ24

AJ27

AJ28

AJ29

AJ30

AK10

R30

R29

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK2

AK13

AK16

AK17

AK20

AK23

AK5

AK7

AL10

AL13

AL16

AK24

AK27

AK28

AK29

AK30

AL17

AL20

AL23

AL24

AL27

AL28

AL3

AM1

AM10

AM13

L30

L29

L28

L27

L26

L25

L24

L23

VSSL3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSK7VSSK5VSSK2VSSJ7VSSJ4VSSH9VSSH8VSSH7VSSH6VSSH3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB1VSS

AN1

AM4

AM16

AM17

AM20

AM7

AM23

AM24

AM27

AM28

AN2

AN10

AN13

AN16

AN17

AN20

AN23

AN24

VSSB5VSS

B8

H29

H28

H27

H26

H25

H24

CPU2C

VSS

VSS

VSS

VSS

VSS

H23

VSS

H22

VSS

H21

VSS

H20

VSS

H19

VSS

H18

VSS

H17

VSS

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

VSS

VSS

VSS

VSSC4VSS

VSS

B17

B11

B14

TEJAS

C7

B20

B24

A A

5

4

3

2

Micro- S tar Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com .tw

Title

Intel LGA 775 GND

Size Docume nt Number Rev

MS-9179

Date: Sheet

1

of

13 50Fr id ay, August 26, 2005

0ACustom

5

U35D

FSB0_D[63..0]8

D D

C C

FSB0_DBI#[3..0]8 FSB1_DBI#[3..0]11

B B

FSB0_DSTBP_N[3..0]8

FSB0_DSTBN_N[3..0]8

FSB0_D[63..0]

FSB0_DBI#[3..0]

FSB0_DSTBP_N[3..0]

FSB0_DSTBN_N[3..0]

CK_H_MCH_P33

CK_H_MCH_N33

FSB0_D63

FSB0_D62

FSB0_D61

FSB0_D60

FSB0_D59

FSB0_D58

FSB0_D57

FSB0_D56

FSB0_D55

FSB0_D54

FSB0_D53

FSB0_D52

FSB0_D51

FSB0_D50

FSB0_D49

FSB0_D48

FSB0_D47

FSB0_D46

FSB0_D45

FSB0_D44

FSB0_D43

FSB0_D42

FSB0_D41

FSB0_D40

FSB0_D39

FSB0_D38

FSB0_D37

FSB0_D36

FSB0_D35

FSB0_D34

FSB0_D33

FSB0_D32

FSB0_D31

FSB0_D30

FSB0_D29

FSB0_D28

FSB0_D27

FSB0_D26

FSB0_D25

FSB0_D24

FSB0_D23

FSB0_D22

FSB0_D21

FSB0_D20

FSB0_D19

FSB0_D18

FSB0_D17

FSB0_D16

FSB0_D15

FSB0_D14

FSB0_D13

FSB0_D12

FSB0_D11

FSB0_D10

FSB0_D9

FSB0_D8

FSB0_D7

FSB0_D6

FSB0_D5

FSB0_D4

FSB0_D3

FSB0_D2

FSB0_D1

FSB0_D0

FSB0_DBI#2

FSB0_DBI#1

FSB0_DBI#0

FSB0_DSTBP_N3

FSB0_DSTBP_N2

FSB0_DSTBP_N1

FSB0_DSTBP_N0

FSB0_DSTBN_N3

FSB0_DSTBN_N2

FSB0_DSTBN_N1

FSB0_DSTBN_N0

CK_H_MCH_P

CK_H_MCH_N

GREENCREEK 4/11

AE37

FSB0_D63

AE36

FSB0_D62

AH36

FSB0_D61

AG36

FSB0_D60

AF38

FSB0_D59

AE38

FSB0_D58

AH38

FSB0_D57

AJ38

FSB0_D56

AJ37

FSB0_D55

AG35

FSB0_D54

AK36

FSB0_D53

AL37

FSB0_D52

AL36

FSB0_D51

AL38

FSB0_D50

AJ34

FSB0_D49

AF37

FSB0_D48

AE28

FSB0_D47

AD29

FSB0_D46

AF28

FSB0_D45

AC31

FSB0_D44

AE29

FSB0_D43

AC30

FSB0_D42

AD30

FSB0_D41

AE31

FSB0_D40

AE32

FSB0_D39

AD35

FSB0_D38

AF33

FSB0_D37

AG32

FSB0_D36

AF31

FSB0_D35

AE34

FSB0_D34

AG30

FSB0_D33

AG33

FSB0_D32

AM37

FSB0_D31

AK35

FSB0_D30

AM34

FSB0_D29

AM38

FSB0_D28

AP38

FSB0_D27

AN36

FSB0_D26

AL35

FSB0_D25

AN35

FSB0_D24

AP36

FSB0_D23

AT37

FSB0_D22

AU36

FSB0_D21

AP34

FSB0_D20

AT36

FSB0_D19

AP35

FSB0_D18

AL34

FSB0_D17

AN33

FSB0_D16

AJ33

FSB0_D15

AG27

FSB0_D14

AG29

FSB0_D13

AM33

FSB0_D12

AH31

FSB0_D11

AJ30

FSB0_D10

AH32

FSB0_D9

AJ31

FSB0_D8

AL31

FSB0_D7

AK30

FSB0_D6

AN32

FSB0_D5

AH29

FSB0_D4

AK29

FSB0_D3

AH28

FSB0_D2

AL29

FSB0_D1

AJ28

FSB0_D0

AH37

FSB0_DBI3

AF30

FSB0_DBI2

AP37

FSB0_DBI1

AL32

FSB0_DBI0

AH35

FSB0_DSTBP3

AD33

FSB0_DSTBP2

AR38

FSB0_DSTBP1

AK33

FSB0_DSTBP0

AH34

FSB0_DSTBN3

AD32

FSB0_DSTBN2

AR37

FSB0_DSTBN1

AK32

FSB0_DSTBN0

AN17

CORECLKP

AP17

CORECLKN

FSB 0

FSB0_DEFER_N

FSB0_RESET_N

FSB0_MCERR_N

4

FSB0_A35

FSB0_A34

FSB0_A33

FSB0_A32

FSB0_A31

FSB0_A30

FSB0_A29

FSB0_A28

FSB0_A27

FSB0_A26

FSB0_A25

FSB0_A24

FSB0_A23

FSB0_A22

FSB0_A21

FSB0_A20

FSB0_A19

FSB0_A18

FSB0_A17

FSB0_A16

FSB0_A15

FSB0_A14

FSB0_A13

FSB0_A12

FSB0_A11

FSB0_A10

FSB0_A9

FSB0_A8

FSB0_A7

FSB0_A6

FSB0_A5

FSB0_A4

FSB0_A3

FSB0_REQ4

FSB0_REQ3

FSB0_REQ2

FSB0_REQ1

FSB0_REQ0

FSB0_ADSTB1

FSB0_ADSTB0

FSB0_BPRI_N

FSB0_RS2

FSB0_RS1

FSB0_RS0

FSB0_RSP_N

FSB0_TRDY_N

FSB0_ADS_N

FSB0_AP1

FSB0_AP0

FSB0_BINIT_N

FSB0_BNR_N

FSB0_BPM5

FSB0_BPM4

FSB0_BREQ1

FSB0_BREQ0

FSB0_DBSY_N

FSB0_DP3

FSB0_DP2

FSB0_DP1

FSB0_DP0

FSB0_DRDY_N

FSB0_HIT_N

FSB0_HITM_N

FSB0_LOCK_N

PSEL2

PSEL1

PSEL0

FSB0_VREF

FSB0_VREF

FSB0_VREF

3

FSB0_A35

AV22

FSB0_A34

AU22

FSB0_A33

AR22

FSB0_A32

AP22

FSB0_A31

AV24

FSB0_A30

AT23

FSB0_A29

AU23

FSB0_A28

AV25

FSB0_A27

AT24

FSB0_A26

AR25

FSB0_A25

AU26

FSB0_A24

AT26

FSB0_A23

AT27

FSB0_A22

AU25

FSB0_A21

AU28

FSB0_A20

AR24

FSB0_A19

AR27

FSB0_A18

AP25

FSB0_A17 FSB1_A16

AV28

FSB0_A16

AF22

FSB0_A15

AG23

FSB0_A14

AF25

FSB0_A13

AH22

FSB0_A12

AL22

FSB0_A11

AJ22

FSB0_A10

AG24

FSB0_A9

AM22

FSB0_A8

AH23

FSB0_A7

AP26

FSB0_A6

AN26

FSB0_A5

AM25

FSB0_A4

AN24

FSB0_A3

AL25

FSB0_REQ_N4

AJ25

FSB0_REQ_N3

AJ24

FSB0_REQ_N2

AK24

FSB0_REQ_N1

AH25

FSB0_REQ_N0

AL26

FSB0_ADSTB_N1

AP23

FSB0_ADSTB_N0

AL23

FSB0_BPRI_N

AU34

FSB0_DEFER_N

AV34

FSB0_RESET_N

AN30

FSB0_RS2_N

AU31

FSB0_RS1_N

AL28

FSB0_RS0_N

AV31

FSB0_RSP_N

AN27

FSB0_TRDY_N

AT32

FSB0_ADS_N

AU29

FSB0_AP1

AK26

FSB0_AP0

AH26

FSB0_BINIT_N

AK27

FSB0_BNR_N

AV30

FSB0_BPM_N5

AP29

FSB0_BPM_N4

AR28

FSB0_BR_N1

AG26

FSB0_BR_N0

AM28

FSB0_DBSY_N

AR30

FSB0_DP_N3

AN29

FSB0_DP_N2FSB0_DBI#3

AP31

FSB0_DP_N1

AT33

FSB0_DP_N0

AR31

FSB0_DRDY_N

AT29

FSB0_HIT_N

AU32

FSB0_HITM_N

AV33

FSB0_LOCK_N

AT30

FSB0_MCERR_N

AJ27

MCH_SEL0

AB1

MCH_SEL1

AB2

MCH_SEL2

AC1

FSB0_VREF

AF34

AM30

AM27

FSB0_A[35..3]

FSB0_REQ_N[4..0]

FSB0_ADSTB_N[1..0]

FSB0_BPRI_N 8

FSB0_DEFER_N 8

FSB0_RESET_N 8

FSB0_RS2_N 8

FSB0_RS1_N 8

FSB0_RS0_N 8

FSB0_RSP_N 8

FSB0_TRDY_N 8

FSB0_ADS_N 8

FSB0_AP1 8

FSB0_AP0 8

FSB0_BINIT_N 8

FSB0_BNR_N 8

FSB0_BPM_N5 8,44

FSB0_BPM_N4 8,44

FSB0_BR_N1 8

FSB0_BR_N0 8

FSB0_DBSY_N 8

FSB0_DP_N3 8

FSB0_DP_N2 8

FSB0_DP_N1 8

FSB0_DP_N0 8

FSB0_DRDY_N 8

FSB0_HIT_N 8

FSB0_HITM_N 8

FSB0_LOCK_N 8

FSB0_MCERR_N 8

MCH_SEL0 23

MCH_SEL1 23

MCH_SEL2 23

FSB0_A[35..3] 8

FSB0_REQ_N[4..0] 8

FSB0_ADSTB_N[1..0] 8

FSB1_DSTBP_N[3..0]11

FSB1_DSTBN_N[3..0]11

FSB1_D[63..0]11

FSB1_D[63..0]

FSB1_DBI#[3..0]

FSB1_DSTBP_N[3..0]

FSB1_DSTBN_N[3..0]

FSB1_D63

FSB1_D62

FSB1_D61

FSB1_D60

FSB1_D59

FSB1_D58

FSB1_D57

FSB1_D56

FSB1_D55

FSB1_D54

FSB1_D53

FSB1_D52

FSB1_D51

FSB1_D50

FSB1_D49

FSB1_D48

FSB1_D47

FSB1_D46

FSB1_D45

FSB1_D44

FSB1_D43

FSB1_D42

FSB1_D41

FSB1_D40

FSB1_D39

FSB1_D38

FSB1_D37

FSB1_D36

FSB1_D35

FSB1_D34

FSB1_D33

FSB1_D32

FSB1_D31

FSB1_D30

FSB1_D29

FSB1_D28

FSB1_D27

FSB1_D26

FSB1_D25

FSB1_D24

FSB1_D23

FSB1_D22

FSB1_D21

FSB1_D20

FSB1_D19

FSB1_D18

FSB1_D17

FSB1_D16

FSB1_D15

FSB1_D14

FSB1_D13

FSB1_D12

FSB1_D11

FSB1_D10

FSB1_D9

FSB1_D8

FSB1_D7

FSB1_D6

FSB1_D5

FSB1_D4

FSB1_D3

FSB1_D2

FSB1_D1

FSB1_D0

FSB1_DBI#3

FSB1_DBI#2

FSB1_DBI#1

FSB1_DBI#0

FSB1_DSTBP_N3

FSB1_DSTBP_N2

FSB1_DSTBP_N1

FSB1_DSTBP_N0

FSB1_DSTBN_N3

FSB1_DSTBN_N2

FSB1_DSTBN_N1

FSB1_DSTBN_N0

MCH_CORE_VCCA

MCH_FSB_VCCA

MCH_CORE_VSSA

AF16

AG14

AJ16

AJ15

AG15

AF15

AJ13

AL16

AP16

AH16

AN15

AL14

AM15

AN14

AM16

AH14

AP14

AR12

AR13

AP11

AP13

AT12

AT11

AV12

AV10

AU10

AV9

AR9

AU8

AV7

AK12

AL13

AL11

AM13

AN11

AM12

AN12

AN9

AN8

AP8

AM9

AM6

AK9

AN6

AU5

AR7

AU7

AR6

AV4

AV6

AR4

AR3

AR1

AP4

AP5

AP1

AH13

AU11

AK11

AP7

AK15

AR10

AM10

AU4

AK14

AP10

AL10

AU3

AT17

AU17

AU16

AT8

AT9

AL8

AL7

AT6

AT5

AT3

AT2

2

U35E

GREENCREEK 5/11

FSB1_D63

FSB1_D62

FSB1_D61

FSB1_D60

FSB1_D59

FSB1_D58

FSB1_D57

FSB1_D56

FSB1_D55

FSB1_D54

FSB1_D53

FSB1_D52

FSB1_D51

FSB1_D50

FSB1_D49

FSB1_D48

FSB1_D47

FSB1_D46

FSB1_D45

FSB1_D44

FSB1_D43

FSB1_D42

FSB1_D41

FSB1_D40

FSB1_D39

FSB1_D38

FSB1_D37

FSB1_D36

FSB1_D35

FSB1_D34

FSB1_D33

FSB1_D32

FSB1_D31

FSB1_D30

FSB1_D29

FSB1_D28

FSB1_D27

FSB1_D26

FSB1_D25

FSB1_D24

FSB1_D23

FSB1_D22

FSB1_D21

FSB1_D20

FSB1_D19

FSB1_D18

FSB1_D17

FSB1_D16

FSB1_D15

FSB1_D14

FSB1_D13

FSB1_D12

FSB1_D11

FSB1_D10

FSB1_D9

FSB1_D8

FSB1_D7

FSB1_D6

FSB1_D5

FSB1_D4

FSB1_D3

FSB1_D2

FSB1_D1

FSB1_D0

FSB1_DBI3

FSB1_DBI2

FSB1_DBI1

FSB1_DBI0

FSB1_DSTBP3

FSB1_DSTBP2

FSB1_DSTBP1

FSB1_DSTBP0

FSB1_DSTBN3

FSB1_DSTBN2

FSB1_DSTBN1

FSB1_DSTBN0

COREVCCA

FSBVCCA

COREVSSA

FSB 1

FSB1_A35

FSB1_A34

FSB1_A33

FSB1_A32

FSB1_A31

FSB1_A30

FSB1_A29

FSB1_A28

FSB1_A27

FSB1_A26

FSB1_A25

FSB1_A24

FSB1_A23

FSB1_A22

FSB1_A21

FSB1_A20

FSB1_A19

FSB1_A18

FSB1_A17

FSB1_A16

FSB1_A15

FSB1_A14

FSB1_A13

FSB1_A12

FSB1_A11

FSB1_A10

FSB1_A9

FSB1_A8

FSB1_A7

FSB1_A6

FSB1_A5

FSB1_A4

FSB1_A3

FSB1_REQ4

FSB1_REQ3

FSB1_REQ2

FSB1_REQ1

FSB1_REQ0

FSB1_ADSTB1

FSB1_ADSTB0

FSB1_BPRI_N

FSB1_DEFER_N

FSB1_RESET_N

FSB1_RS2

FSB1_RS1

FSB1_RS0

FSB1_RSP_N

FSB1_TRDY_N

FSB1_ADS_N

FSB1_AP1

FSB1_AP0

FSB1_BINIT_N

FSB1_BNR_N

FSB1_BPM5

FSB1_BPM4

FSB1_BREQ1

FSB1_BREQ0

FSB1_DBSY_N

FSB1_DP3

FSB1_DP2

FSB1_DP1

FSB1_DP0

FSB1_DRDY_N

FSB1_HIT_N

FSB1_HITM_N

FSB1_LOCK_N

FSB1_MCERR_N

FSBCRES

FSBODTCRES

FSBSLWCRES

FSBSLWCTRL

FSB1_VREF

FSB1_VREF

FSB1_VREF

FSB1_A35

AC3

FSB1_A34

AC4

FSB1_A33

AD2

FSB1_A32