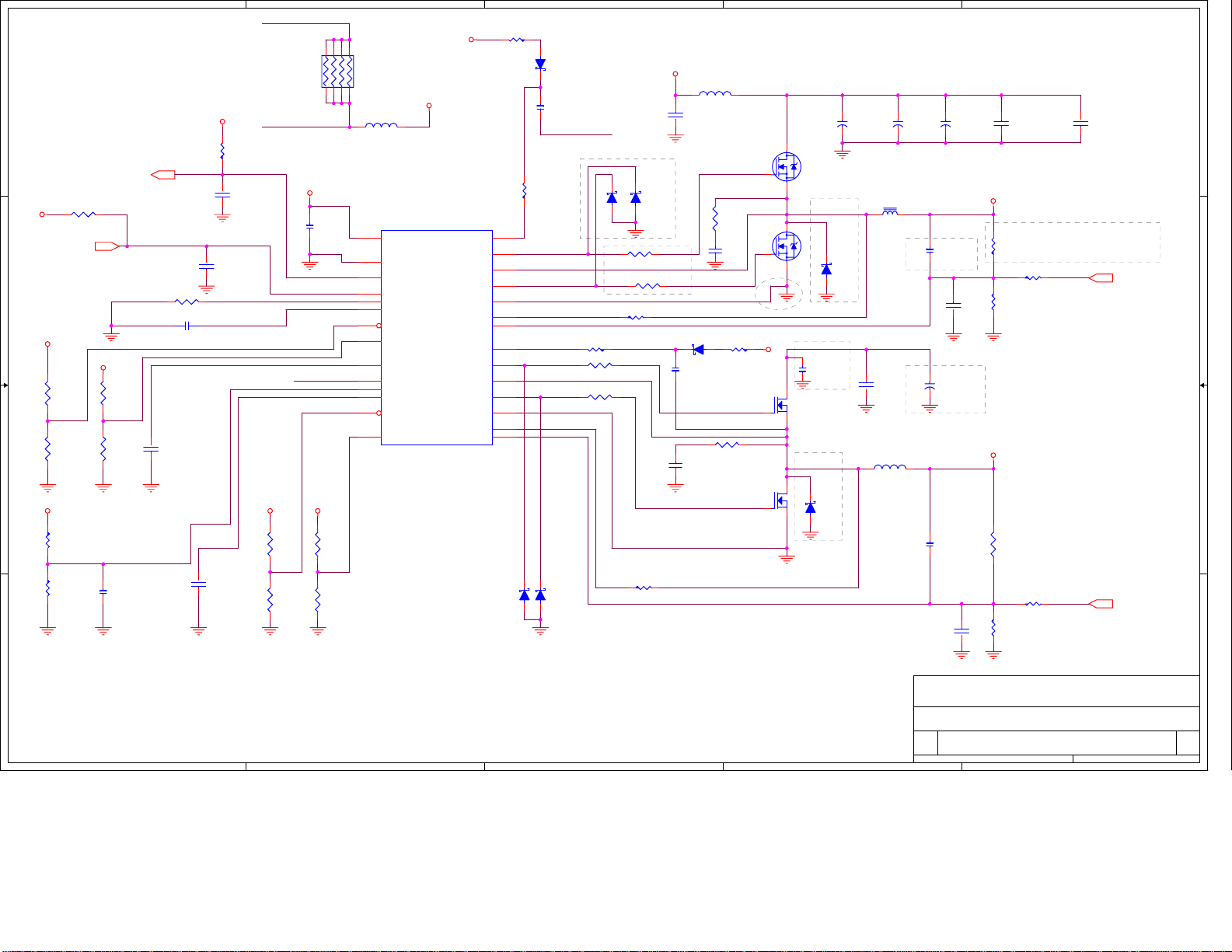

MSI MS-9166 Schematic 0520

5

4

3

2

1

MS-9166 Dual K8 1U System Date : 2005/05/16Revision : 0C

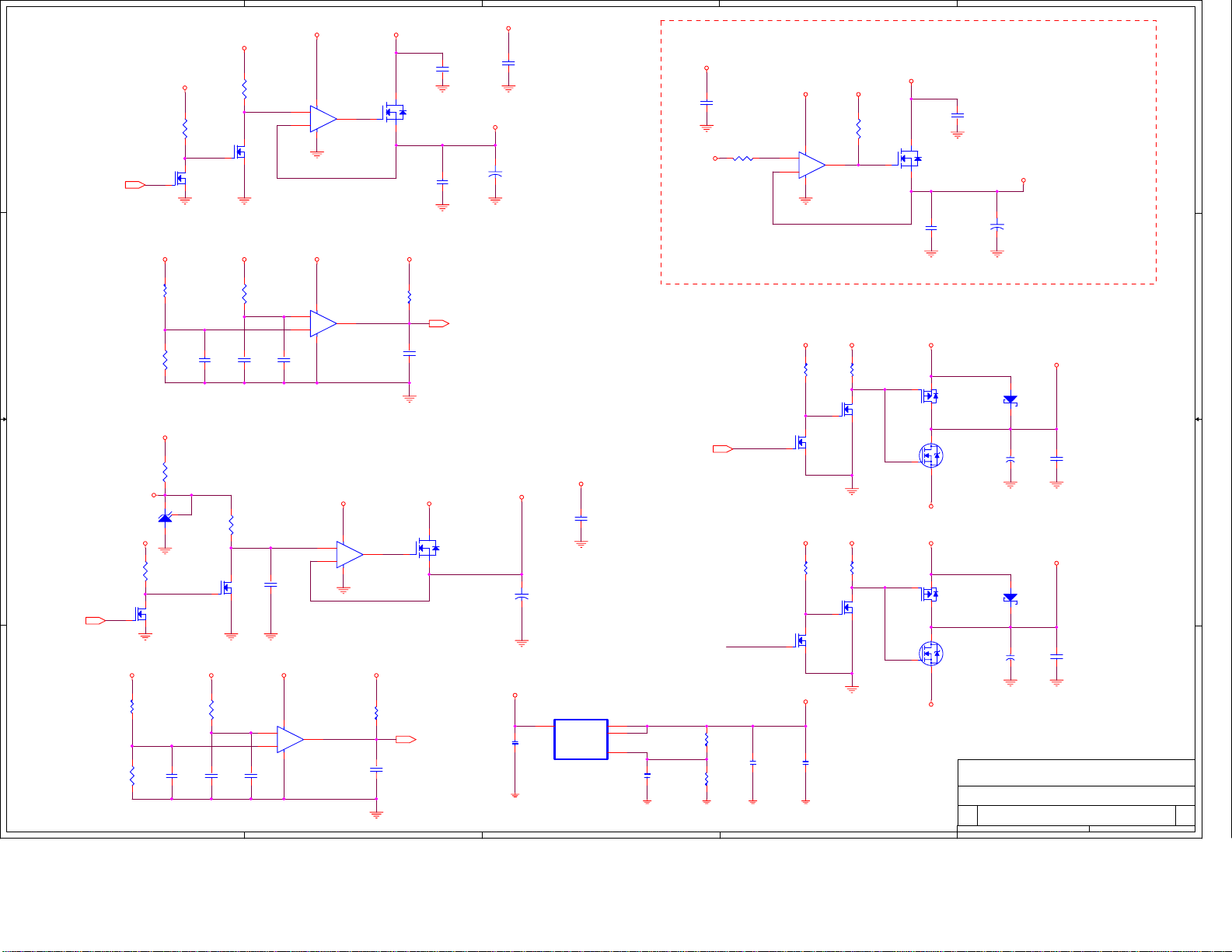

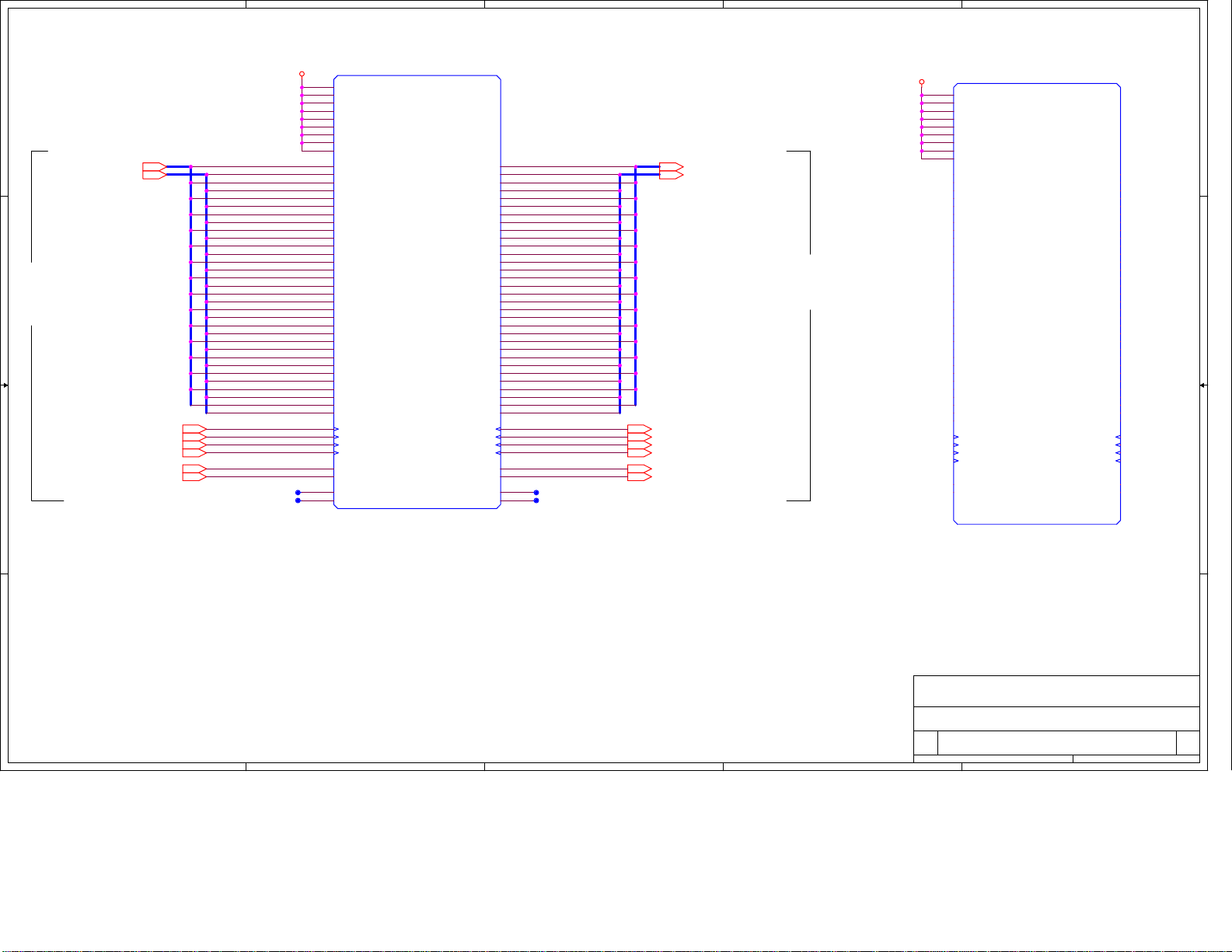

001 COVER

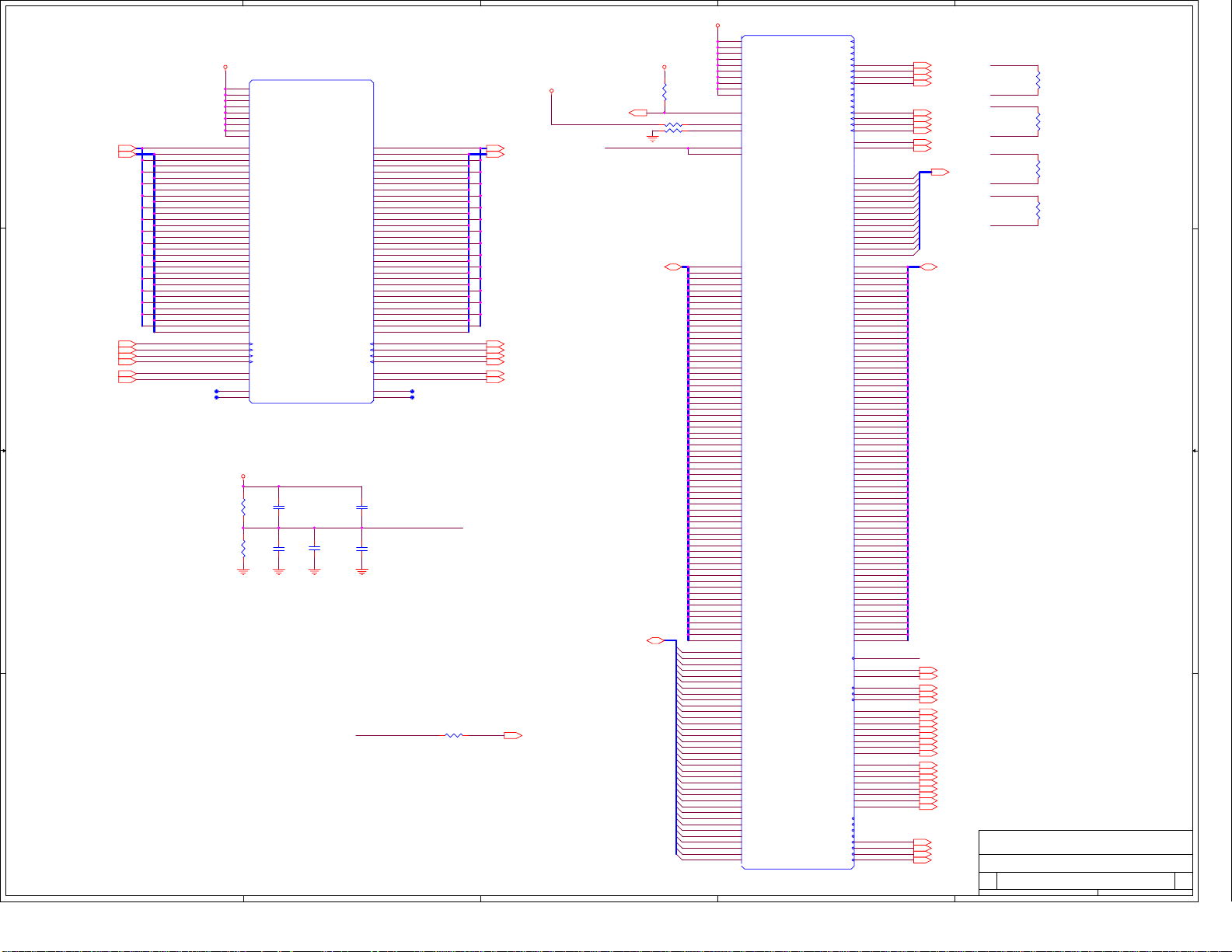

002 Block Diagram

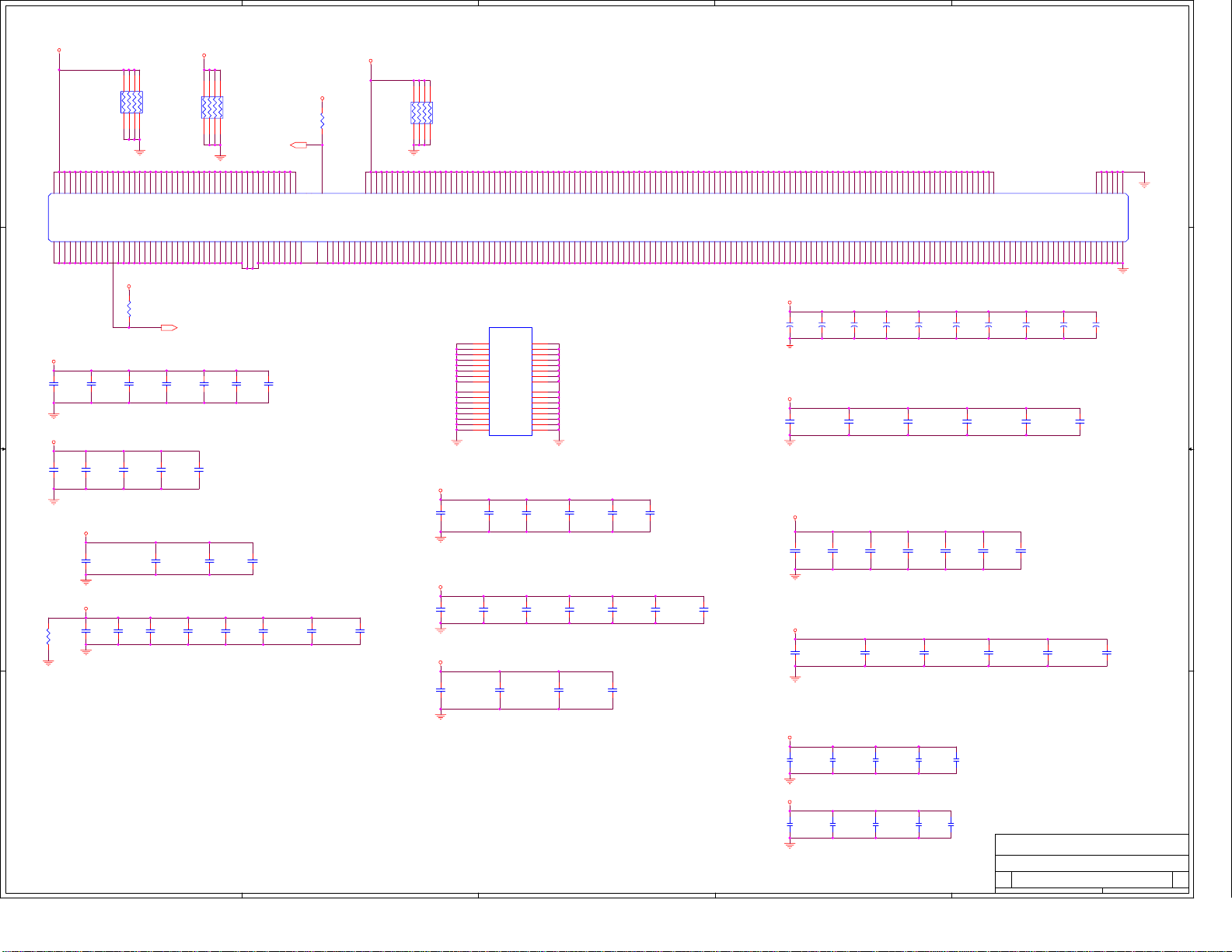

003 K8 CPU0 Vcore Power

004 K8 CPU1 Vcore Power

D D

005 CPU0 DDR POWER

006 CPU1 DDR POWER

007 1.2V Power

008 3.3V & 5V & -12 Power

009 Main Power

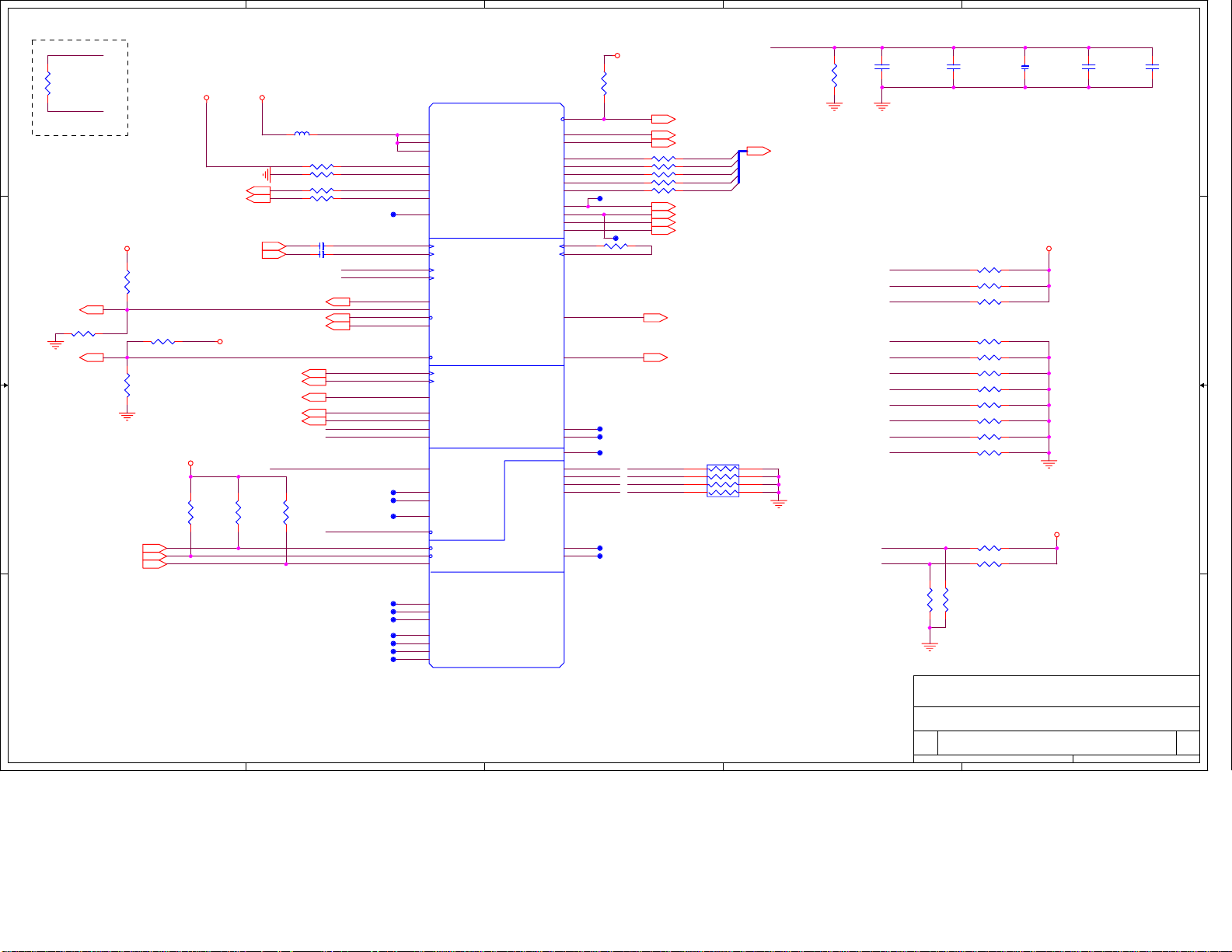

010 Clock Synthesizer

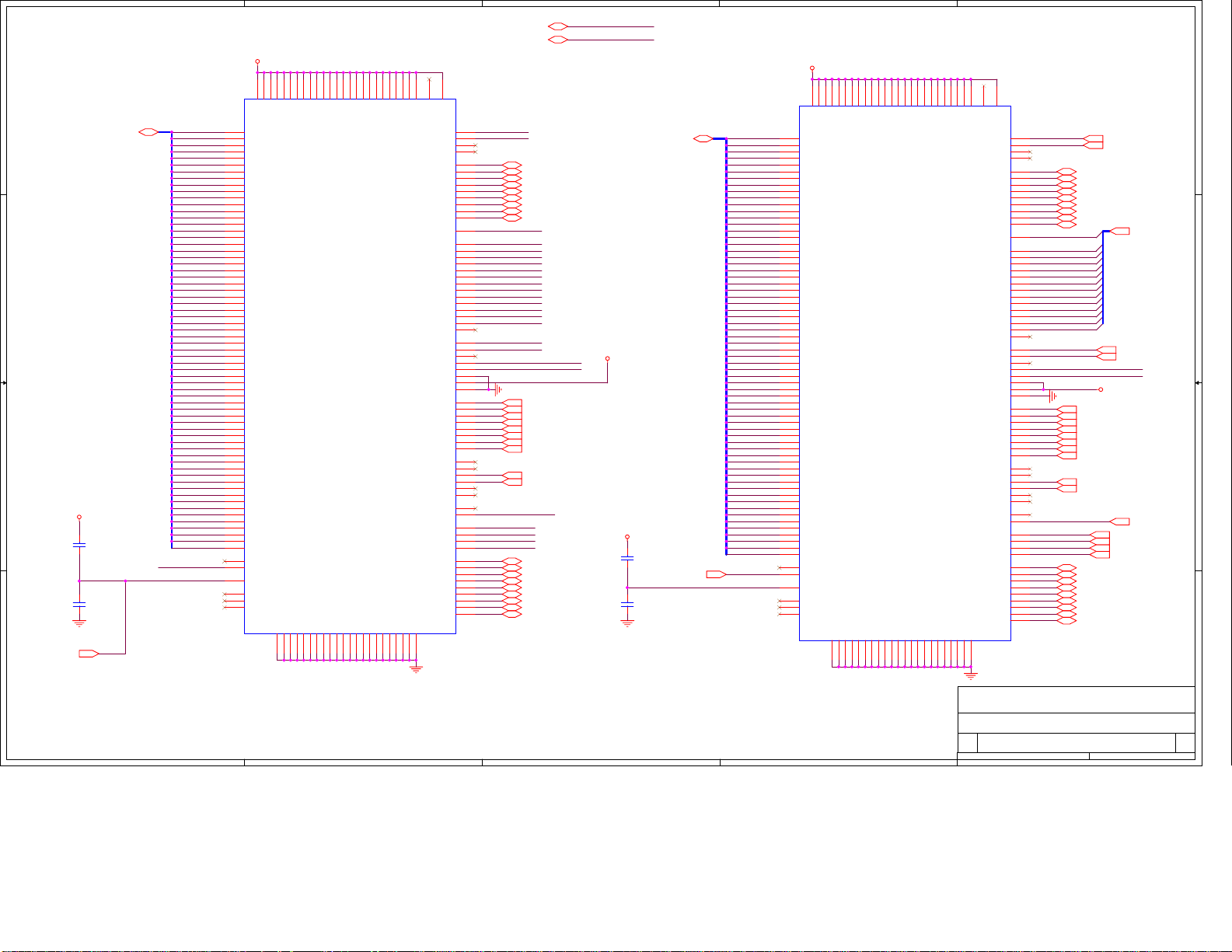

011 CPU0 DDR & HT2 TO CPU1

012 CPU0 HDT & MISC

013 CPU0 HT0(NC HT)& HT1 TO LH

014 CPU0 POWER & GND

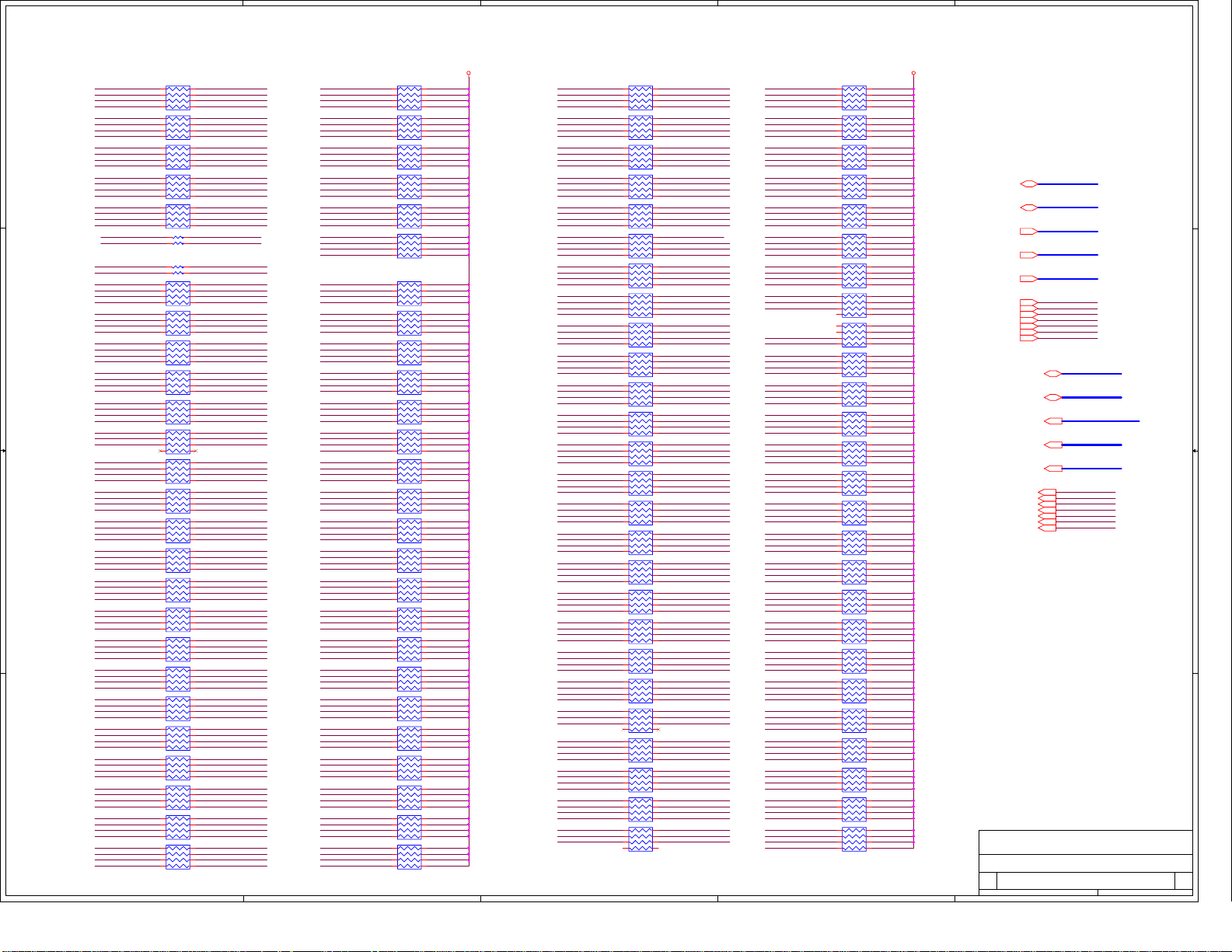

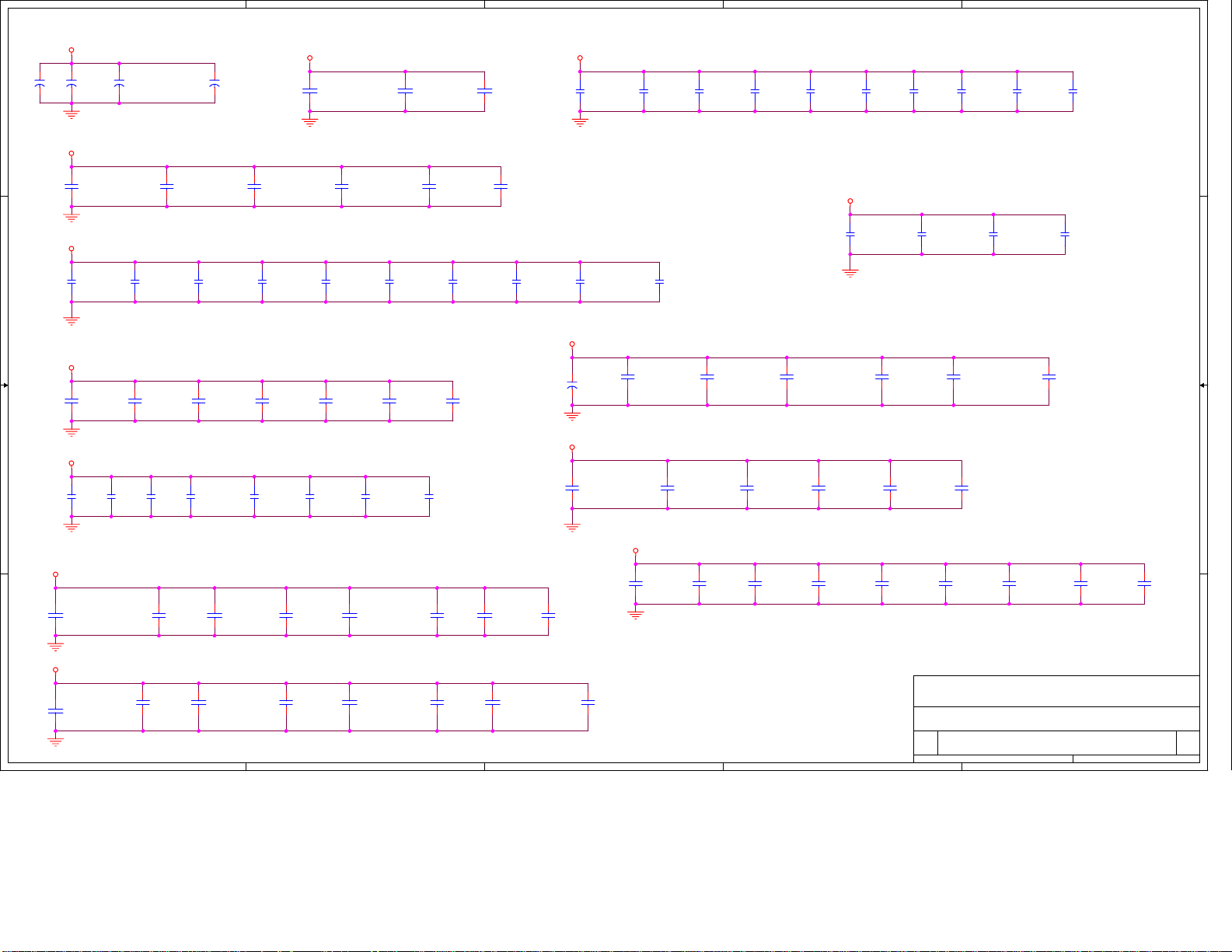

015 CPU0 Register DDR DIMM1 & DIMM2

016 CPU0 Register DDR DIMM3 & DIMM4

017 CPU0 DDR Terminations

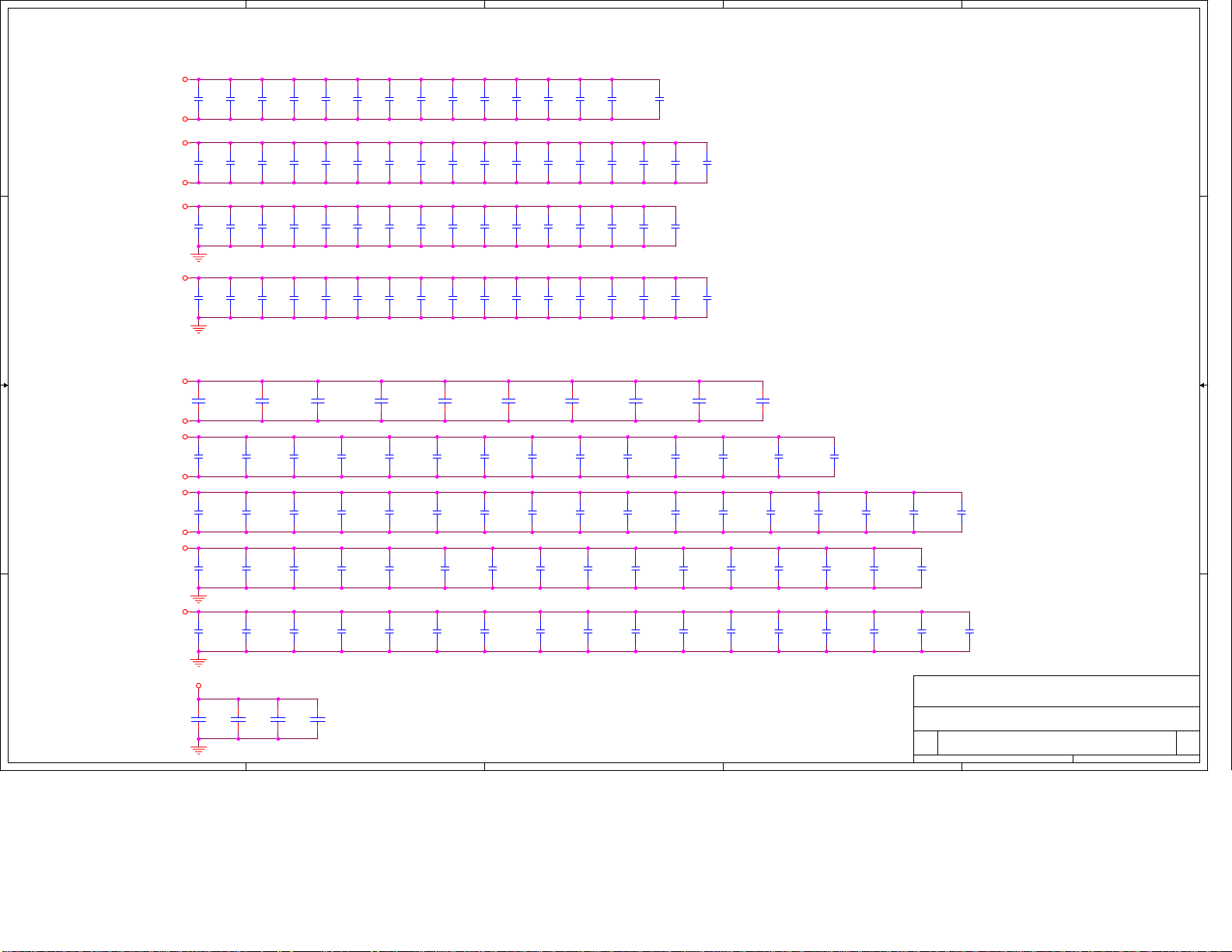

018 CPU0 DDR Decoupling(1)

019 CPU0 DDR Decoupling(2)

020 CPU1 DDR & HT2 TO CPU0

021 CPU1 HDT & MISC

022 CPU1 HT0 & HT1(NC HT)

023 CPU1 POWER & GND

C C

024 CPU1 Register DDR DIMM1 & 2

025 CPU1 Register DDR DIMM3 & 4

026 CPU1 DDR Terminations

027 CPU1 DDR Decoupling(1)

028 CPU1 DDR Decoupling(2)

029 HDT

030 HT-LE HT & PCI-E

031 HT-LE PCI-X

032 HT-LE Dual LAN

033 HT-LE POWER & Decoupling

034 HT-LE GND

035 Strapping

036 SCSI PCI-X & Power & GND

037 SCSI Differential Signal

038 SCSI Connector

039 SCSI Memory Signal

040 SB1 PCI

041 SB1 PCI-X

042 SB1 IDE & LPC

B B

043 SB1 POWER & GND

044 SMBUS Isolation

045 PCI-X & PCI-E SLOT

046 ATI RN50 PCI

047 ATI RN50 Memory

048 VGA Connector

049 SIO PC87417

050 BIOS Flash & ASR & ABR

051 ADM 1027

052 FAN CIRCUIT

053 USB & IDE Connector

054 COM Port KB Mouse

055 GAL POWER SEQ

056 FRONT PANEL

057 SO-DIMM CONN

058 SM_Hardware Monitor & VPD

059 Diagnotic LED & CPLD

060 Layout comp & Opt part

A A

061 System Decoupling

POWER DEFINITIONM

P0_VCORE, P1_VCORE

P0_VDDA_2.5

P1_VDDA_2.5

+1.2V_HT

P0_VDIMM_2.5V, P1_VDIMM_2.5V

P0_VTT_1.25V, P1_VTT_1.25V

+2.5V

+1.2V

+5VSB

+2.5VDUAL

+1.2VDUAL

LAN_2.5V

LAN_1.25V

VGA_2.5V

CPU Voltage

For CPU0

For CPU1

HT Voltage

DDR Dimm Voltage

DIMM Termination

Normal 2.5V

Normal 1.8V

Standby Voltage

Dual-Voltage+3.3VDUAL

Dual-Voltage

Dual-Voltage

Dual-Voltage (For G-LAN)

Dual-Voltage (For G-LAN)

For ATI VGA Voltage

For Battrey VoltageVBAT

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

CPVER

MS-9166

1

0CC

of

169Friday, May 20, 2005

8

7

6

5

4

3

2

1

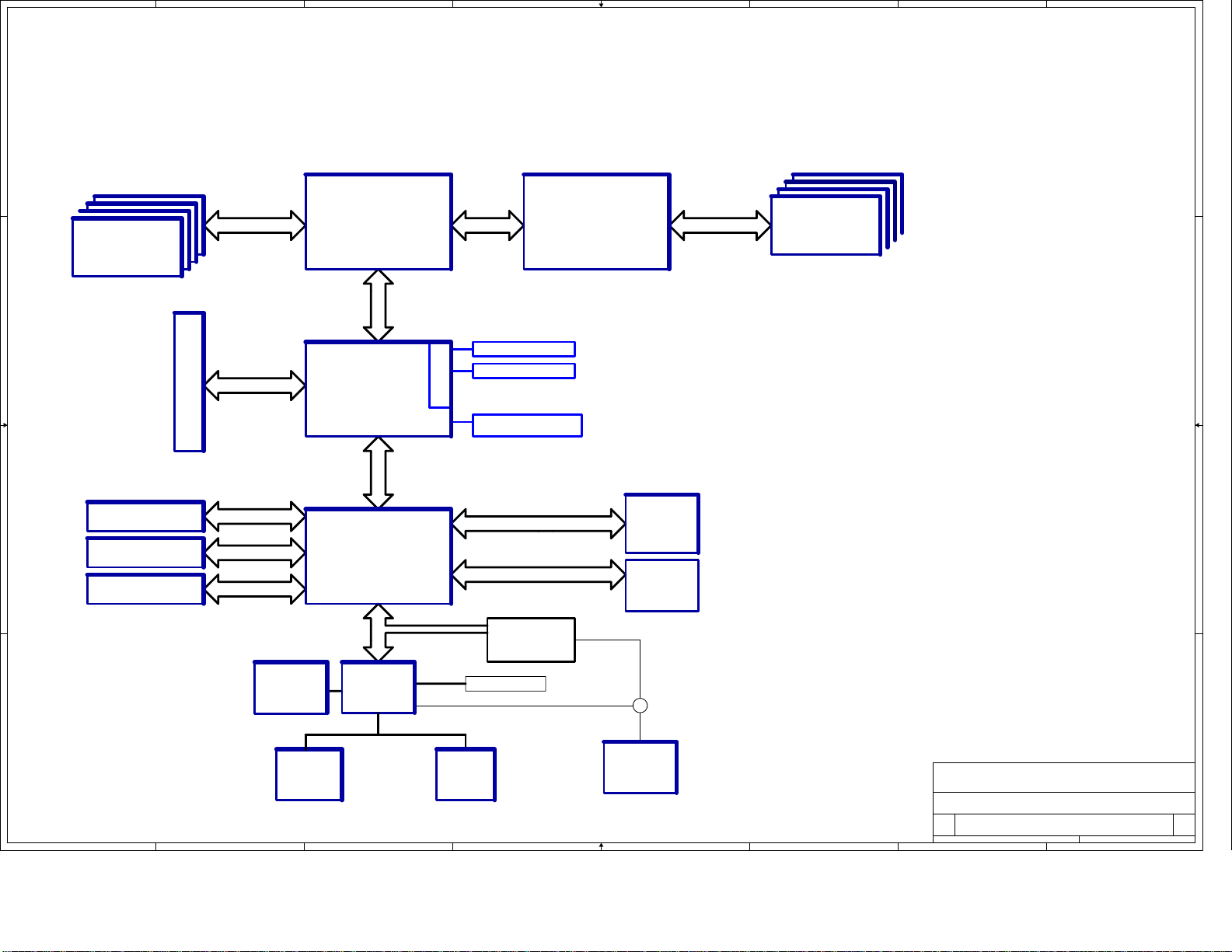

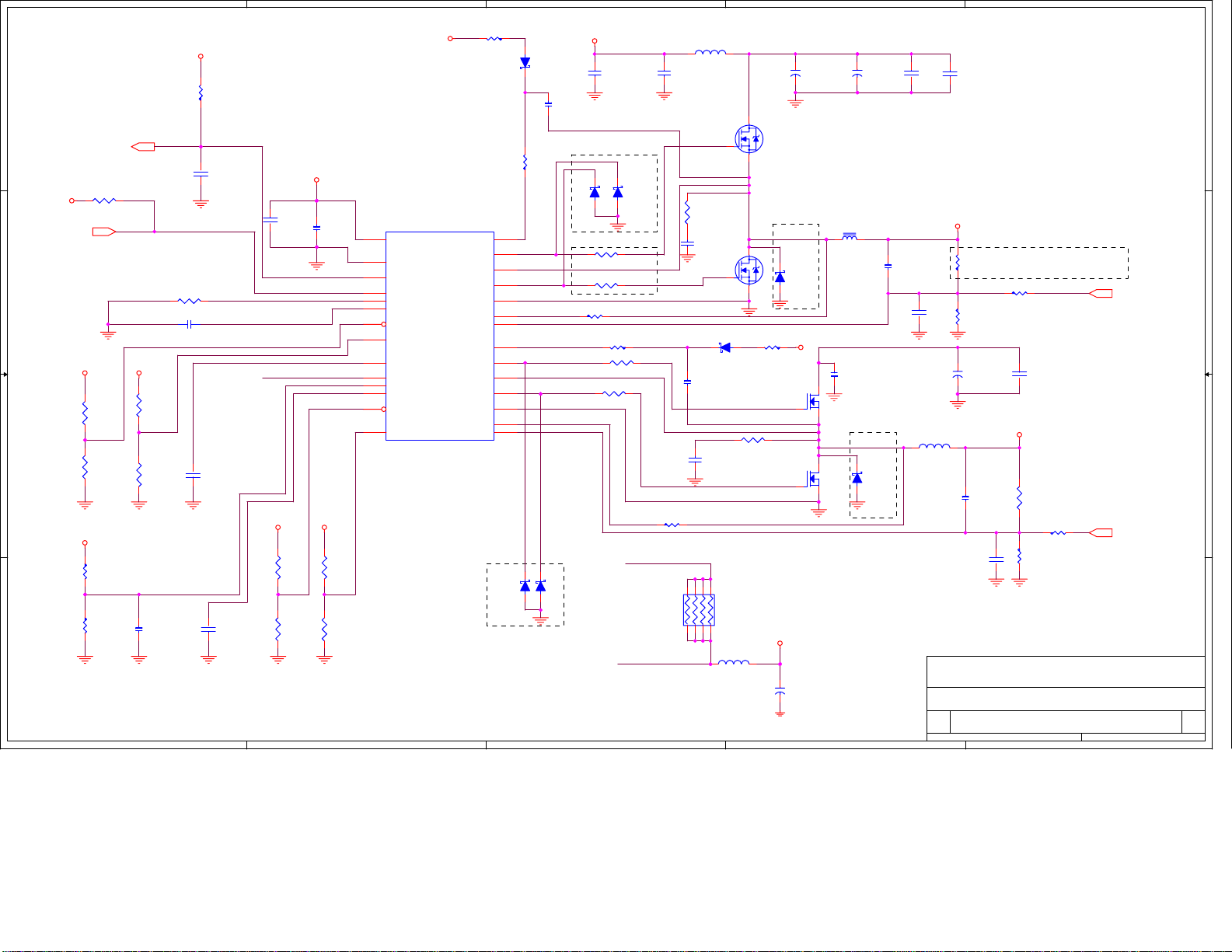

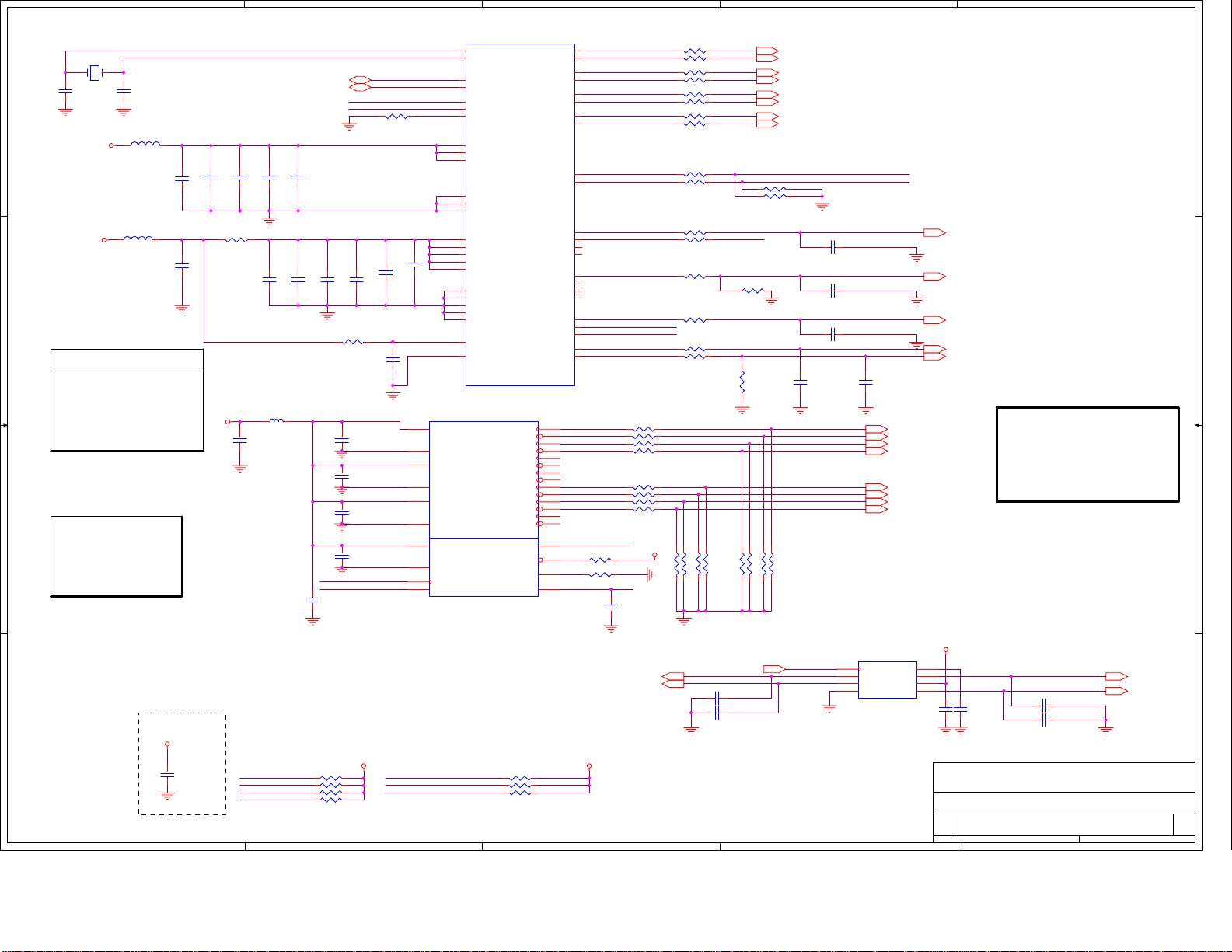

BLOCK DIAGRAM

D D

BLOCK DIAGRAM

16x16ncHyperTransport @ 2000MT/s

Sledgehammer DP

( H1 )( H0 )

128 bit

200 - 400 MHz

4 DDR DIMM

Registered

4 DDR DIMM

128 bit

200 - 400 MHz

Sledgehammer DP

HTLINK

Registered

HTLINK

16x16 ncHyperTransport @ 2000MT/s

C C

PCI-X Slot

64 bit

133 MHz

HT-LE

( SWC-HT2k )

PCI-X Bus

8 X PCI-E

8 X PCI-E

PCI-E Bus

2 Ports GbE

HTLINK

8x8 ncHyperTransport @ 1200MT/s

I2C Bus

ATI RN-50

8 MB RAM

VGA

LSI

5SC1020

B B

Single IDE Chan nel

USB Port 1/2/3/4

SATA Port 1/2

EIDE ATA/100

USB 2.0

SSTA

SB1

( HT-1000 )

LPC

PCI Bus 32 bit / 33 MHz

PCI-X Bus 64 bit /133 MHz

BMC Card

(MS-XXXX)

H8 2168

Flash ROM

A A

Keyboard

& Mouse

(OPT)

8

7

LPC SIO

NS/PC87417

6

Serial

(COM1,2)

FDD

5

I2C Bus

OR

ADM1027

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Tai p e i H s i e n , T a i w a n . h t t p :/ /www.msi.c om.tw

Title

Size Document Number Rev

4

3

Date: Sheet

2

Block Diagram

MS-9166

0CA3

of

269Friday, May 20, 2005

1

5

4

3

2

1

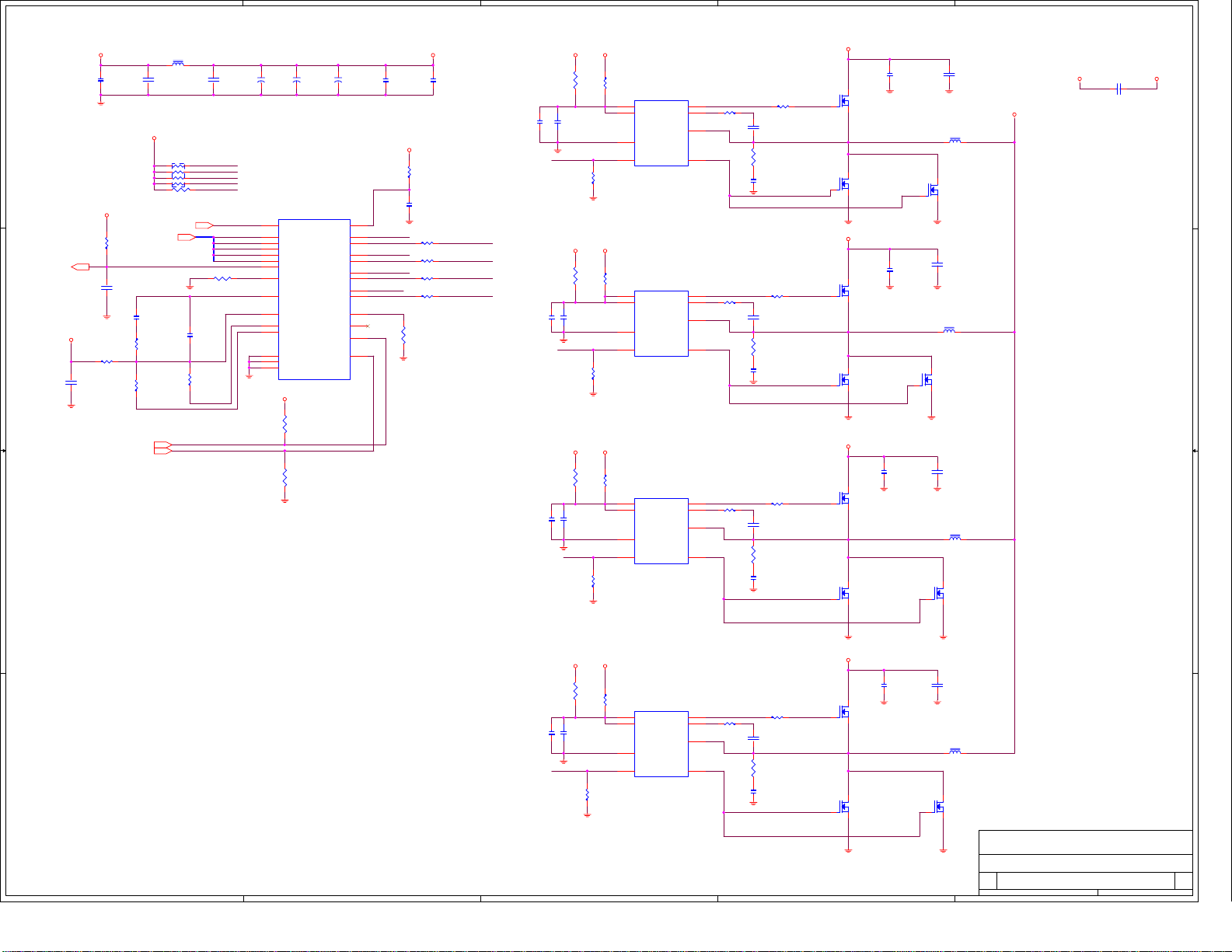

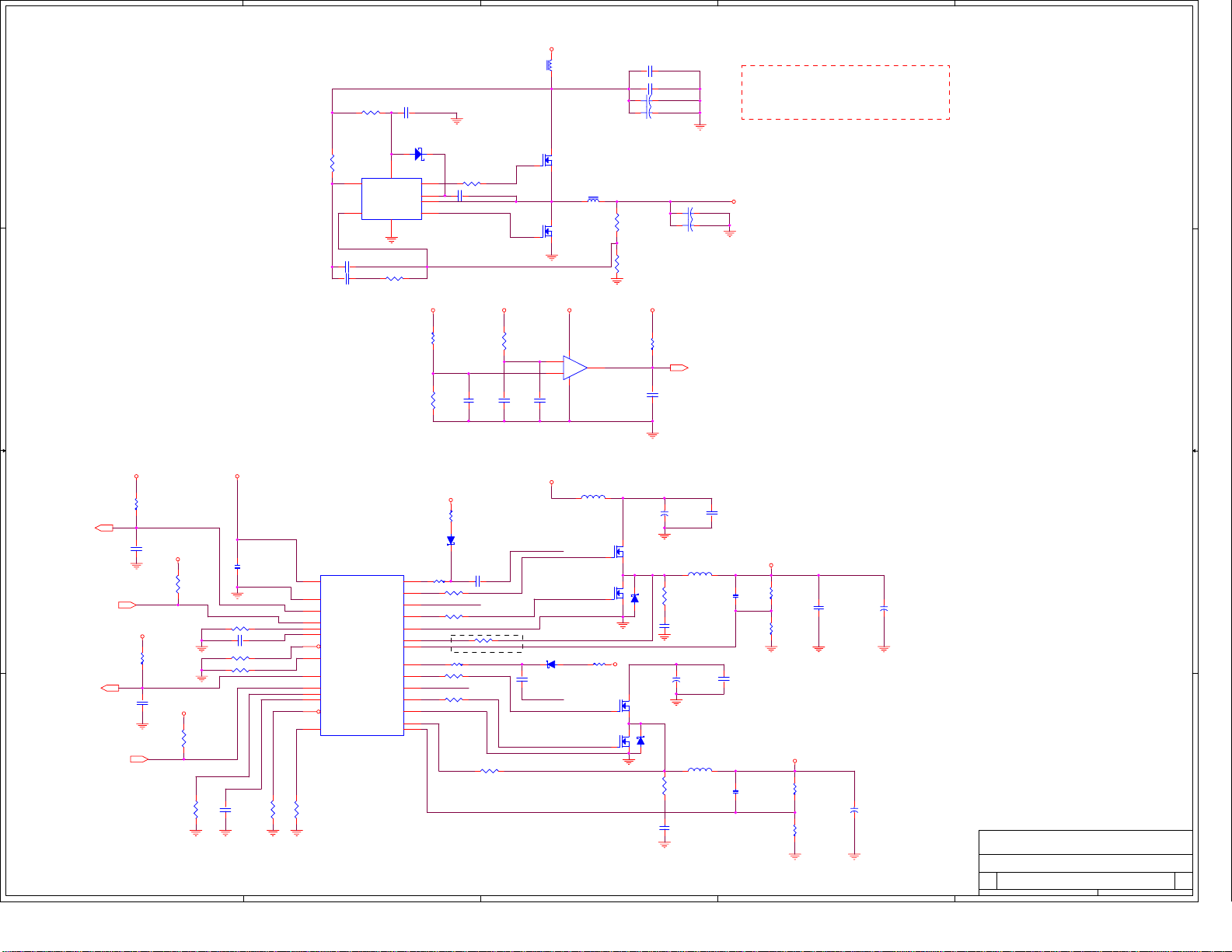

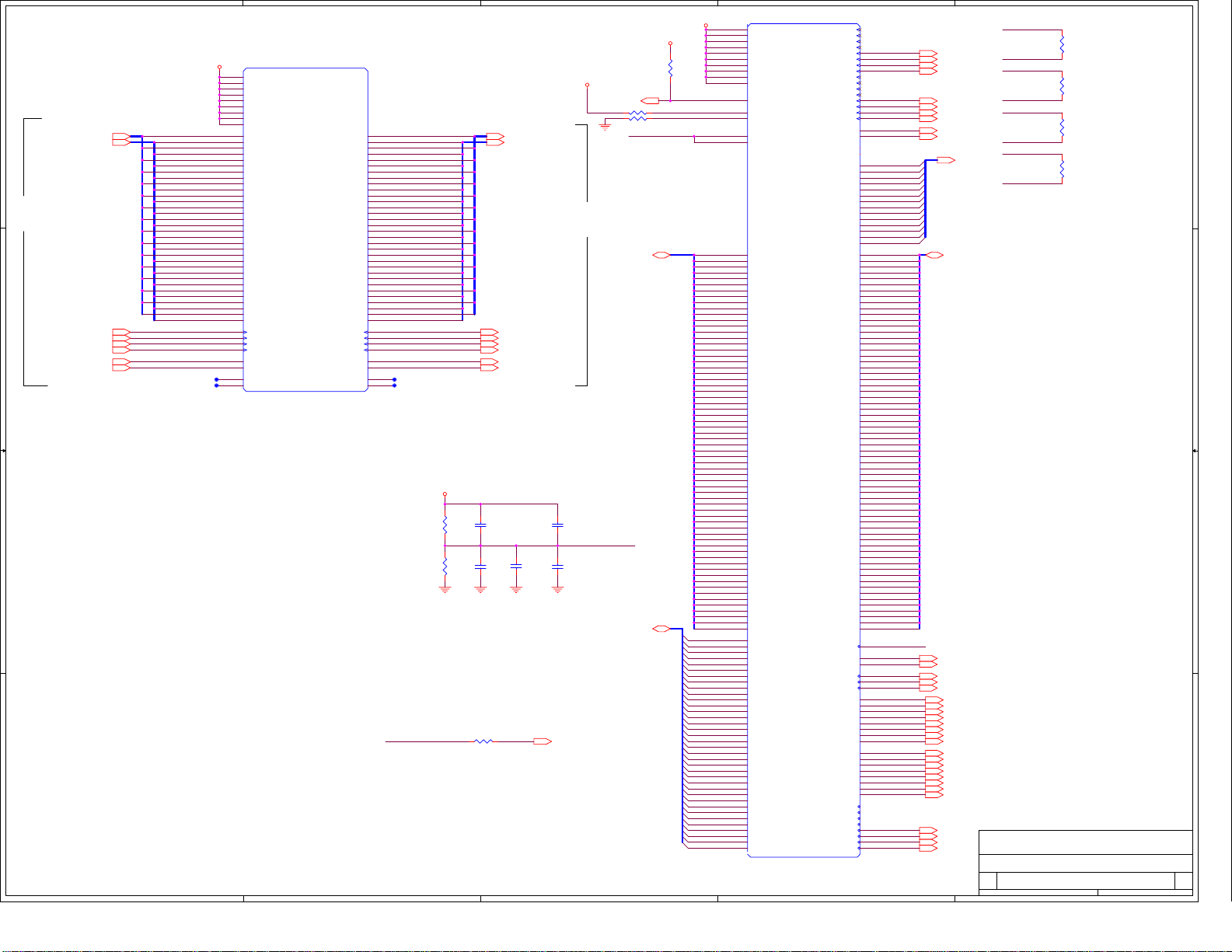

CPU0 Vcore Power

+12V

C670

.1u_16V

CHOK6 1.1uH_25A

C657

47p_50V

C698

47p_50V

CT33

270u_16V

CT35

270u_16V

CT23

270u_16V

270uF/16V x4

D D

CPU0POWER_GD4

NOPOP

+5V

C829

X_1u_10V

C C

+5V

R922

10K

C875

1u_10V

R813 X_100K_1%

NOPOP

P0_COREFB12

P0_COREFBJ12

P0_VDIMM_2.5V

RN162 X_1K-8P4R

R890 X_1K

PWRSEQ_7_EN55

P0_VID[4..0]12

C856

5600p_50V

R839

10K

R824

0

7 8

5 6

3 4

1 2

NOPOP

NOPOP

P0_VID1

P0_VID2

P0_VID3

P0_VID4

P0_VID0

P0_VID4

P0_VID3

P0_VID2

P0_VID1

P0_VID0

R925 68K_1%

C848

X_22p

NOPOP

R821

1K

U91

28

EN

3

VID4

4

VID3

5

VID2

6

VID1

7

VID0

26

PGOOD

9

COMP

10

FB

12

VDIFF

11

IDROOP

20

GND

15

GND

1

GND

ISL6559CB

P0_VCORE

R808

R809

51_1%

51_1%

PWM1

ISEN1

PWM2

ISEN2

PWM3

ISEN3FS/DIS

PWM4

ISEN4

VSEN

RGND

16

VCC

H0_PWM1

22

23

H0_PWM2

21

19

H0_PWM3

17

1827

H0_PWM4

25

24

8

OFS

2

OVP

13

14

VDD_12_VRM_H0

C677

4.7u_35V-1206

+5V

R889 2.2K_1%

R841 2.2K_1%

R838 2.2K_1%

R899 2.2K_1%

R876

2.2K

Offset Adjustment

R807

0-0805

C831

1u_16V-0805

C669

4.7u_35V-1206

H0_PHASE1

H0_PHASE2

H0_PHASE3

H0_PHASE4

C884

2.2u_16V-0805

2.2u_16V-0805

NOPOP

NOPOP

C859

NOPOP

C837

2.2u_16V-0805

B B

+12V

R933

X_2.2-0805

C893

.22u_16V

H0_PWM1

+12V

R847

X_2.2-0805

C873

.22u_16V

H0_PWM2

+12V

R805

X_2.2-0805

C842

.22u_16V

H0_PWM3

+5V

R913

4.7-0805

U95

6

VCC

7

PVCC

4

GND

3

PWM

R930

MOSDVR-INTS-HIP6605-SOIC8

499K_1%

+5V

R874

4.7-0805

U92

6

VCC

7

PVCC

4

GND

3

PWM

MOSDVR-INTS-HIP6605-SOIC8

R875

499K_1%

+5V

R817

4.7-0805

U90

6

VCC

7

PVCC

4

GND

3

PWM

MOSDVR-INTS-HIP6605-SOIC8

R825

499K_1%

BOOT

PHASE

BOOT

PHASE

BOOT

PHASE

1

U_G

R923 0

2

8

5

L_G

1

U_G

R845 0

2

8

5

L_G

1

U_G

R804 0

2

8

5

L_G

R921 2.2-0805

C874

.1u_16V

R911

2.2-0805

C878

X_.01u

NOPOP

R812 2.2-0805

C847

.1u_16V

R815

2.2-0805

C830

X_.01u

NOPOP

R782 2.2-0805

C827

.1u_16V

R761

2.2-0805

C731

X_.01u

NOPOP

H0_PHASE1

H0_PHASE2

H0_PHASE3

VDD_12_VRM_H0

DS

Q106

G

IPD09N03L/TO252

DS

Q105

G

IPD06N03LA/TO252

VDD_12_VRM_H0

DS

Q90

G

IPD09N03L/TO252

DS

Q92

G

IPD06N03LA/TO252

VDD_12_VRM_H0

DS

Q76

IPD09N03L/TO252

G

DS

Q78

G

IPD06N03LA/TO252

C1424

BOT/1u_16V-0805

G

C1422

BOT/1u_16V-0805

CHOK9 0.8uH

G

C1413

BOT/1u_16V-0805

C1423

BOT/.1u_16V

CHOK10 0.8uH

DS

Q104

IPD06N03LA/TO252

C1421

BOT/.1u_16V

DS

Q91

IPD06N03LA/TO252

C1410

BOT/.1u_16V

CHOK8 0.8uH

DS

Q77

G

IPD06N03LA/TO252

P0_VCORE

P0_VCORE

2005/3/18 Schematic

Update

C828

.1u_16V

+12V

H0_PHASE4

VDD_12_VRM_H0

DS

Q70

IPD09N03L/TO252

G

DS

Q69

G

IPD06N03LA/TO252

C671

1u_16V-0805

C699

.1u_16V

CHOK7 0.8uH

DS

Q68

G

IPD06N03LA/TO252

+5V

+12V

R723

R724

X_2.2-0805

4.7-0805

NOPOP

C688

C687

2.2u_16V-0805

A A

.22u_16V

H0_PWM4

6

7

4

3

MOSDVR-INTS-HIP6605-SOIC8

R726

499K_1%

U71

VCC

PVCC

GND

PWM

BOOT

PHASE

1

U_G

2

8

5

L_G

R732 0

R734 2.2-0805

C689

.1u_16V

R746

2.2-0805

C703

X_.01u

NOPOP

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

K8 CPU0 Vcore Power

MS-9166

1

0CC

of

369Friday, May 20, 2005

5

4

3

2

1

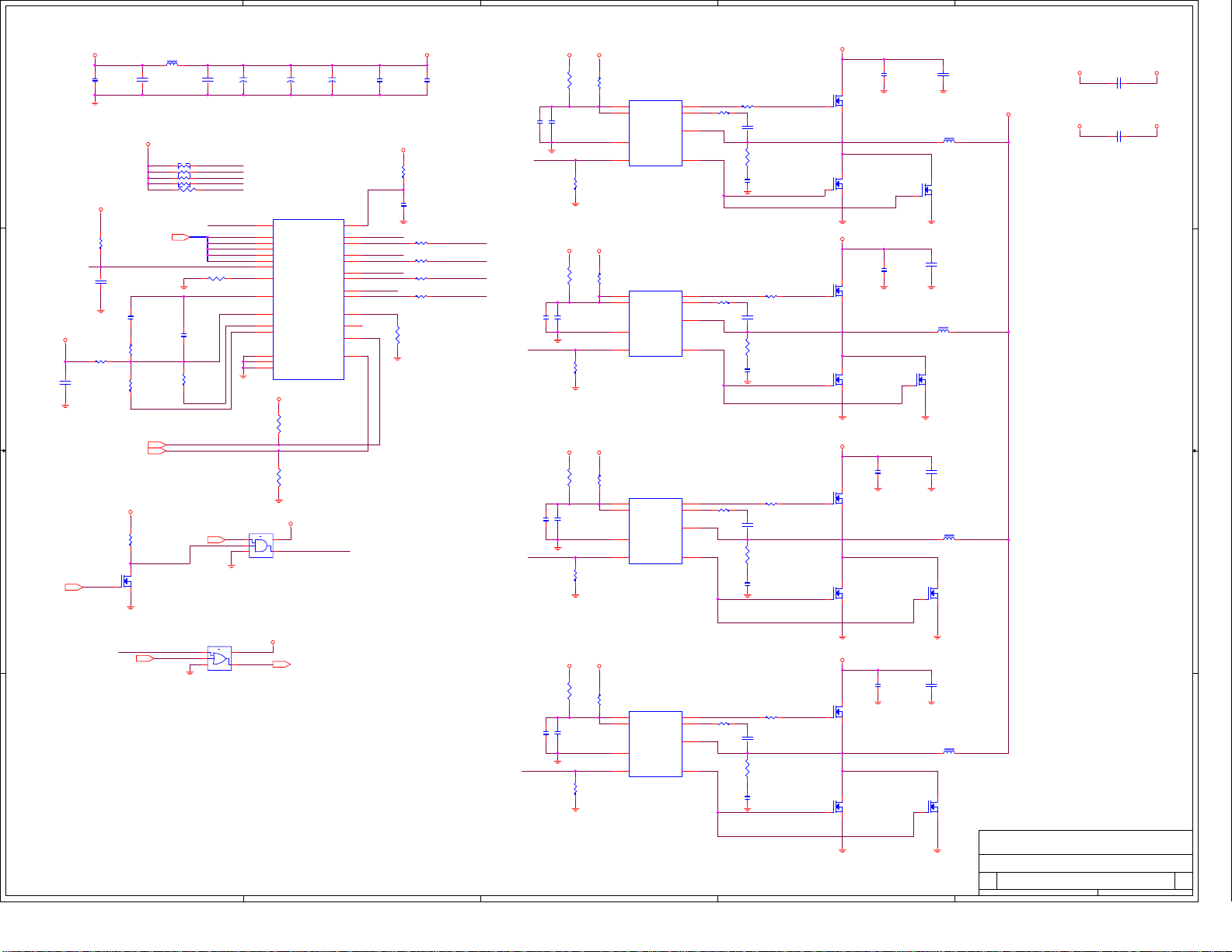

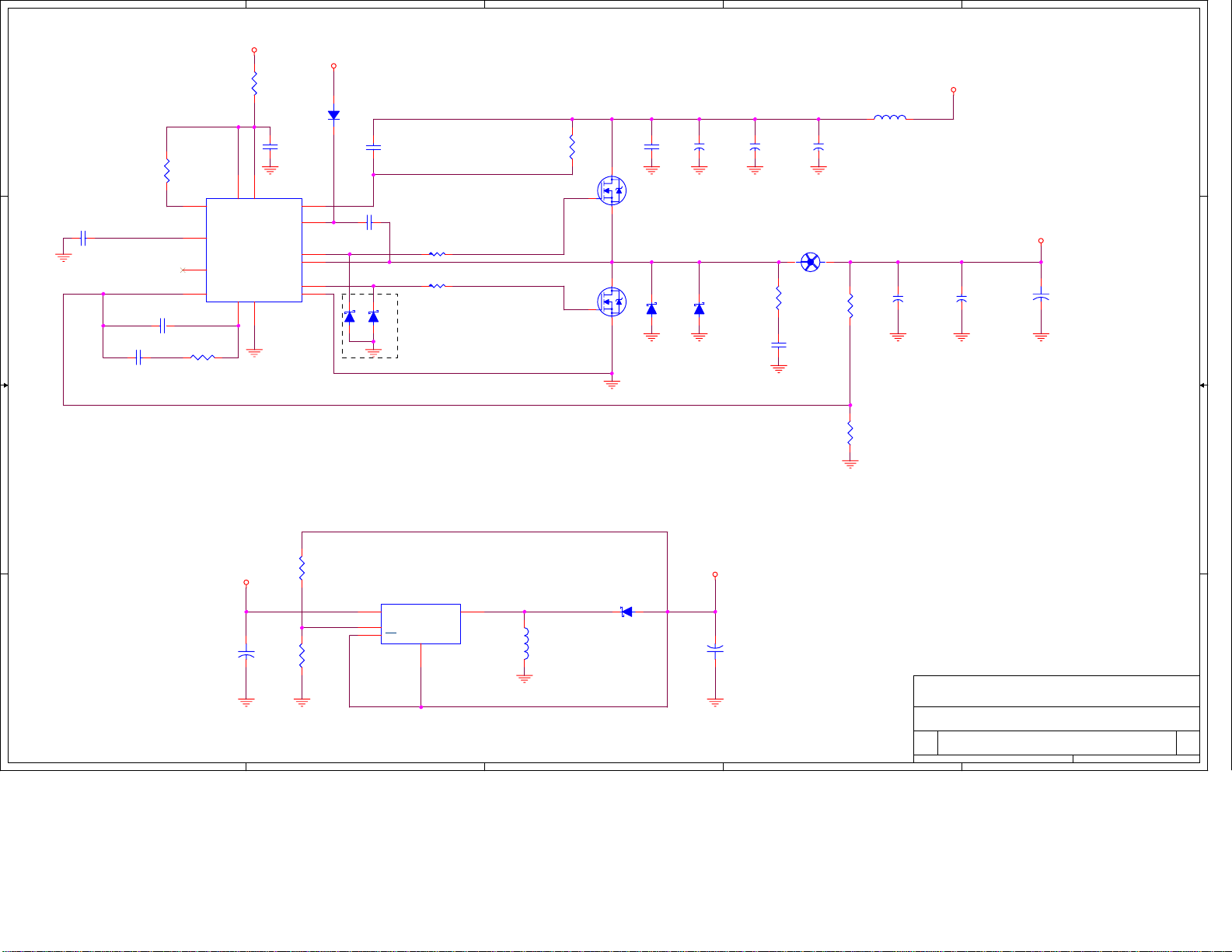

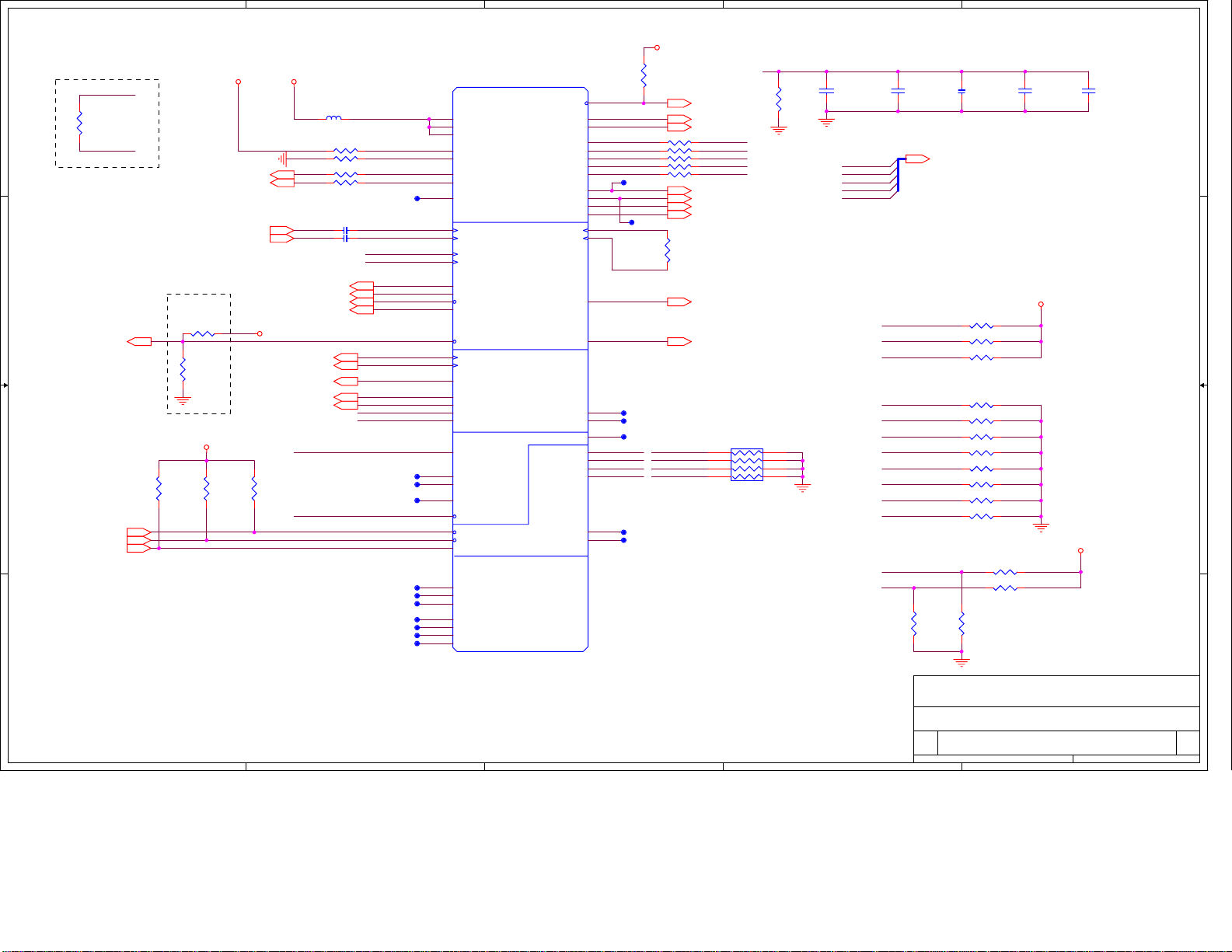

CPU1 Vcore Power

H1_PWM1

H1_PWM2

H1_PWM3

H1_PWM4

VDD_12_VRM_H1

C598

4.7u_35V-1206

+5V

R354 2.2K_1%

R352 2.2K_1%

R353 2.2K_1%

R356 2.2K_1%

R427

2.2K

Offset Adjustment

R350

0-0805

C320

1u_16V-0805

C362

4.7u_35V-1206

H1_PHASE1

H1_PHASE2

H1_PHASE3

H1_PHASE4

C600

2.2u_16V-0805

2.2u_16V-0805

2.2u_16V-0805

NOPOP

H1_PWM1

NOPOP

C573

H1_PWM2

NOPOP

C505

H1_PWM3

+12VB

C323

.1u_16V

CHOK1 1.1uH_25A

C106

47p_50V

C593

47p_50V

CT12

270u_16V

CT5

270u_16V

CT15

270u_16V

Sanyo OS-CON 270uF/16V( Ripple current = 4.4A) x 3

D D

P1_VDIMM_2.5V

RN40 X_1K-8P4R

7 8

5 6

3 4

1 2

R426 X_1K

P1_VID[4..0]21

C374

5600p_50V

R440

10K

R424

0

R741

10K

Q67

2N7002

NOPOP

PWRSEQ_7_EN55

+5V

R355

10K

CPU1POWER_GD

C324

1u_10V

NOPOP

H1_PRESENT23

+5V

R441 X_100K_1%

NOPOP

C400

X_1u_10V

P1_COREFB21

P1_COREFBJ21

+5V

DS

G

C C

B B

NOPOP

P1_VID1

P1_VID2

P1_VID3

P1_VID4

P1_VID0

CPU1POWER_EN

P1_VID4

P1_VID3

P1_VID2

P1_VID1

P1_VID0

R357 68K_1%

C375

X_22p

NOPOP

R425

1K

1

2

3

U77

GND

NC7S08

28

3

4

5

6

7

26

9

10

12

11

20

15

1

P1_VCORE

VCC

U40

EN

VID4

VID3

VID2

VID1

VID0

PGOOD

COMP

FB

VDIFF

IDROOP

GND

GND

GND

ISL6559CB

+5V

5

4

R423

51_1%

R422

51_1%

CPU1POWER_EN

PWM1

ISEN1

PWM2

ISEN2

PWM3

ISEN3FS/DIS

PWM4

ISEN4

VSEN

RGND

16

VCC

22

23

21

19

17

1827

25

24

8

OFS

2

OVP

13

14

+12V

C599

.22u_16V

+12V

C572

.22u_16V

+12V

C506

.22u_16V

R625

X_2.2-0805

499K_1%

R577

X_2.2-0805

499K_1%

R504

X_2.2-0805

499K_1%

R653

R583

R536

+5V

R622

4.7-0805

U65

6

VCC

7

PVCC

4

GND

3

PWM

MOSDVR-INTS-HIP6605-SOIC8

+5V

R578

4.7-0805

U62

6

VCC

7

PVCC

4

GND

3

PWM

MOSDVR-INTS-HIP6605-SOIC8

+5V

R503

4.7-0805

U53

6

VCC

7

PVCC

4

GND

3

PWM

MOSDVR-INTS-HIP6605-SOIC8

BOOT

PHASE

BOOT

PHASE

BOOT

PHASE

R712 2.2-0805

1

U_G

R668 0

2

8

5

L_G

1

U_G

R609 0

2

8

5

L_G

1

U_G

R537 0

2

8

5

L_G

C624

.1u_16V

R620

2.2-0805

C588

X_.01u

NOPOP

R608 2.2-0805

C585

.1u_16V

R603

2.2-0805

C586

X_.01u

NOPOP

R549 2.2-0805

C526

.1u_16V

R502

2.2-0805

C424

X_.01u

NOPOP

H1_PHASE1

H1_PHASE2

H1_PHASE3

VDD_12_VRM_H1

DS

Q64

G

IPD09N03L/TO252

DS

Q59

G

IPD06N03LA/TO252

VDD_12_VRM_H1

DS

Q47

G

IPD09N03L/TO252

DS

Q48

G

IPD06N03LA/TO252

VDD_12_VRM_H1

DS

Q42

IPD09N03L/TO252

G

DS

Q41

G

IPD06N03LA/TO252

C647

1u_16V-0805

C565

1u_16V-0805

C544

1u_16V-0805

CHOK5 0.8uH

DS

Q54

G

IPD06N03LA/TO252

C567

.1u_16V

CHOK4 0.8uH

DS

Q49

G

IPD06N03LA/TO252

C553

.1u_16V

CHOK3 0.8uH

DS

G

C658

.1u_16V

Q38

IPD06N03LA/TO252

P1_VCORE

VDD_12_VRM_H1

VDD_12_VRM_H1

C643

.1u_16V

C661

.1u_16V

2005/3/18 Schematic

Update

P1_VCORE

+12V

U76

CPU0POWER_GD3

A A

CPU1POWER_GD

1

2

3

GND

NC7S32

VCC

+5V

5

4

PWRSEQ_7_GD 55

NOPOP

C368

2.2u_16V-0805

H1_PWM4

+12V

R401

X_2.2-0805

C384

.22u_16V

+5V

R448

4.7-0805

R406

MOSDVR-INTS-HIP6605-SOIC8

499K_1%

6

VCC

7

PVCC

4

GND

3

PWM

BOOT

PHASE

1

U_G

2

8

5

L_G

R453 0

R467 2.2-0805U44

C405

.1u_16V

R479

2.2-0805

NOPOP

C425

X_.01u

H1_PHASE4

VDD_12_VRM_H1

DS

Q29

IPD09N03L/TO252

G

DS

Q30

G

IPD06N03LA/TO252

C379

1u_16V-0805

C406

.1u_16V

CHOK2 0.8uH

DS

Q31

G

IPD06N03LA/TO252

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

K8 CPU1 Vcore Power

MS-9166

1

0CC

of

469Friday, May 20, 2005

5

VCC_SWT_H0

D D

PWRSEQ_5_GD55

R994 BOT/1K

+5V

R368

X_0

NOPOPNOPOP

R369

100K

C337

.01u_50V

PWRSEQ_5_EN

R384 47K

4.7u_6.3V-0805

PWRSEQ_5_EN55

C C

P0_VDIMM_2.5V

+5V

R400

X_0

R407

0

B B

P0_VDIMM_2.5V

R364

10K_1%

R365

10K_1%

.1u_16VC347

+5V

C1121

X_1u

NOPOP

C345

X_.01u

NOPOP

R363

X_10K

C336

1u_10V

P0_VTT_1.25V

+2.5VDIMM_SWT_H0

+5V

C398

.1u_16V

PWRSEQ_5_EN

+5V

R411

X_0

NOPOP

R421

0

4

123456

78

RN37

X_0_8P4R

NOPOP

L30 1.2uH_8A

E_CHKTC3052_1R2M080S

U42

28

VCC

1

AGND

15

PG1

8

EN1

11

ILIM1

12

SS1

9 10

FPWM1# VSEN1

14

VIN

16

PG2/REF2OUT

21

EN2

18

ILIM2/REF2

17

SS2

20

FPWM2#

13

DDR

ISL6539-TSSOP28PIN

R367

0

R366

X_0

P0_VDIMM_2.5V

+5V

BOOT1

HDRV1

SW1

LDRV1

PGND1

ISNS1

BOOT2

HDRV2

SW2

LDRV2

PGND2

ISNS2

VSEN2

R428 1

6

5

4

2

3

7

23

24

25

27

26

22

19

D49

BOT/1N5817

D48

C364

.1u_16V

R405

0

D51

BOT/1N5817

BOT/1N5817

PHASE_2V5_H0

3

Near U27,update 6/9

D50

BOT/1N5817

R362 2.2-0805

PHASE_2V5_H0

R451 0-0805

R399

R414 0

R437 2.2-0805

PHASE_1V25_H0

R442 0-0805

R432 10K_1%

+5V

D46

BOT/1N5817

Update 6/9

3K_1%

E_CHKTC3052_1R2M080S

L27 1.2uH_8A

C29010u_6.3V_0805

PHASE_2V5_H0

R431

2.2-0805

C372

1000p

Connect to here

BOT/1N5817

D47

R379 1

C377

.1u_16V

IPD09N03AL/TO252

PHASE_1V25_H0

R439 2.2-0805C338

C399

1000p

IPD09N03AL/TO252

G

G

Q35

FDB6670AL/TO263

+5V

Q27

G

G

Q28

VCC_SWT_H0

DS

Q25

FDB6670AL/TO263

Near Q25

DS

C357

4.7u_6.3V-0805

DS

Near Q23

Near Q26

DS

D31

1N5817

2

390u_6.3V_OS-CON

+

EC29

390u_6.3V_OS-CON

L29 0.8uH

D29

1N5817

+2.5VDIMM_SWT_H0

C403

1u_10V

E_CHKTC3052_1R2M080S

L31 1.2uH_8A

+

EC32

390u_6.3V_OS-CON

Update 6/9

C354

.01u_50V

Update 2003/06/24

+

EC33

390u_6.3V_OS-CON

C358

.01u_50V

5/5 update

+

EC24

NOPOP

P0_VDIMM_2.5V

C353

X_100p

P0_VTT_1.25V

C352

X_100p

NOPOP

C319

4.7u_6.3V-0805

R385

1.87K_1%

R371 X_1.82K_1%

R382

1K_1%

R402

0

R387 X_1K_1%

R383

X_2.55K

NOPOP

To support DDR400.

VDIMM=2.57V.

NOPOPNOPOP

1

C355

1u_10V

P0_VDDIO_SENSE 14

P0_VTT_SENSE 11

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

CPU0 DDR Power

MS-9166

1

0CB

of

569Friday, May 20, 2005

5

4

3

2

1

R893 1

+5V

R924

PWRSEQ_5_EN

.1u_16VC849

C903

4.7u_6.3V-0805

X_10K

C885

1u_10V

C898

X_.01u

NOPOP

C88010u_6.3V_0805

P1_VTT_1.25V

R949

X_0

NOPOP

R935

0

+5V

C902

.1u_16V C841

+5V

28

1

15

8

11

12

9 10

14

16

21

18

17

20

13

ISL6539-TSSOP28PIN

R856

0

R857

X_0

NOPOP

4

D D

PWRSEQ_5_GD55

R936 1K

+5V

PWRSEQ_5_EN55

C C

P1_VDIMM_2.5V

R859

X_0

NOPOP

B B

A A

R858

0

P1_VDIMM_2.5V

R944

10K_1%

R945

10K_1%

+5V

5

R900 47K

R894

X_0

NOPOP

R895

100K

C899

.01u_50V

+5V

U93

VCC

AGND

PG1

EN1

ILIM1

SS1

FPWM1# VSEN1

VIN

PG2/REF2OUT

EN2

ILIM2/REF2

SS2

FPWM2#

DDR

BOOT1

HDRV1

SW1

LDRV1

PGND1

ISNS1

BOOT2

HDRV2

SW2

LDRV2

PGND2

ISNS2

VSEN2

D53

BOT/1N5817

R896

0

6

5

4

2

3

7

23

24

25

27

26

22

19

D57

BOT/1N5817

BOT/1N5817

Near U64,update 6/9

+5V

C852

.1u_16V

PHASE_2V5_H1

Near U64,update 6/9

BOT/1N5817

Update 6/9

R955 2.2-0805

R888 0-0805

R860 3K_1%

R937 0

PHASE_1V25_H1PWRSEQ_5_EN

R823 0-0805

D56

CT4

100u_6.3V/MLCC

D52

BOT/1N5817

PHASE_2V5_H1

R912 2.2-0805

3

E_CHKTC3052_1R2M080S

CT3

100u_6.3V/MLCC

D55

FDB6670AL/TO263

R943 10K_1%

VCC_SWT_H1

+2.5VDIMM_SWT_H1

E_CHKTC3052_1R2M080S

L461.2uH_8A

G

PHASE_2V5_H1

R834

2.2-0805

1000p

Q96

G

D44 1N5817

C901

.1u_16V

PHASE_1V25_H1

R873 2.2-0805

C843

1000p

123456

78

RN156

X_0_8P4R

NOPOP

1.2uH_8A

VCC_SWT_H1

EC78

270u_16V

DS

Sanyo OS-CON 270uF/16V( Ripple current = 4.4A) x 2

Q107

FDB6670AL/TO263

Update_0D

2003/07/16

Near Q66

Q94

D54

BOT/1N5817

Q95

G

G

EC64

3300u/6.3V

L41 0.8uH

+5V

DS

R958 1

IPD09N03AL/TO252

IPD09N03AL/TO252

P1_VDIMM_2.5V

L42

DS

DS

EC79

270u_16V

C869

4.7u_6.3V-0805

Update_0D

2003/07/16

Near Q69

D58

BOT/1N5817

2

C850

.01u_50V

+2.5VDIMM_SWT_H1

Near Q68

L43 1.2uH_8A

E_CHKTC3052_1R2M080S

C892

C894

1u_10V

4.7u_6.3V-0805

P1_VDIMM_2.5V

To support DDR400.

VDIMM=2.57V.

X_1.82K_1%

R837

NOPOP

C858

1u_10V

P1_VDDIO_SENSE 23

C851

X_100p

NOPOP

R836

1.87K_1%

R835

1K_1%

EC67

270u_16V

Sanyo OS-CON 270uF/16V( Ripple current = 4.4A) x 1

P1_VTT_1.25V

R946

0

R947 X_1K_1%

NOPOP

R948

X_2.55K

NOPOP

P1_VTT_SENSE 20

NOPOP

C908

.01u_50V

C900

X_100p

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

CPU1 DDR POWER

MS-9166

1

669Friday, May 20, 2005

of

0CCustom

5

D D

2005/3/8 Delete

power enable

R348

22K

P1_VTT = 1.2V

10P/50V/NPO

1500p_50V

C309

C316

7

4

R323

2.2-0805

COMP

R331 47K

A C

5

UGATE

VCC

PHASE

LGATEFB

GND

U36

3

ISL6520A

C293

4.7u_6.3V-0805

D27

1N5817

BOOT

2

1

8

46

Vref = 0.8V

R315

2.2-0805

C331

.22u_16V

+5VDUAL

CHOCK1

CH-1.2U8A

DS

Q21

G

IPD09N03L/TO252

CHOCK2

CH-1.5u10A

DS

Q24

G

IPD06N03LA/TO252

+5VSB+2.5VDUAL +1.2VDUAL +5VSB

3

C308

1 2

1 2

10u_6.3V_0805

C295

10u_6.3V_0805

+

EC27

1000u_6.3V

+

EC25

1000u_6.3V

1.Add EC105 for 5VDUAL input voltage

2

1

2005/3/14 Schematic Update

NB:7.9A

R347

1.8K_1%

R329

3.6K

1 2

+

+

820u2.5VOS

TC4

EC17

270u_16V

+1.2VDUAL

R701

C C

11.8K_1%

1.087V

R688

9.09K_1%

+5V

R649

X_10K

PWRSEQ_3_GD55

B B

PWRSEQ_3_EN55

PWRSEQ_8_GD55

PWRSEQ_8_EN55

A A

C625

+5V

1u_10V

+5V

R669

X_10K

C630

+5V

1u_10V

5

R613

X_1K

R634

1K

R670

47K

+5V

C629

1u_16V-0805

R611 47K

C590 .01u_50V

R612 0

R591 100K

C631

.01u_50V

U64

28

VCC

1

AGND

15

PG1

8

EN1

11

ILIM1

12

SS1

9 10

FPWM1# VSEN1

14

VIN

16

PG2/REF2OUT

21

EN2

18

ILIM2/REF2

17

SS2

20

FPWM2#

13

DDR

ISL6539-TSSOP28PIN

Vref = 0.9V

R610

R671

0

0

+5V

R584

1

D33

1N5817

R615 0

6

BOOT1

5

HDRV1

4

SW1

2

LDRV1

3

PGND1

7

ISNS1

23

BOOT2

24

HDRV2

25

SW2

27

LDRV2

26

PGND2

22

ISNS2

19

VSEN2

4

C589 .1u_16V

R594 2.2-0805

PHASE_1V8

R616 0-0805

R614 1K_1%

R673 0

R755 2.2-0805

PHASE_1V2

R742 0-0805

R672 1K_1%

C649

X_102p

NOPOP

R665

4.7K

C632

.1u_16V

PHASE_1V8

Update 06/23/2003

For OC protection

C628

.1u_16V

PHASE_1V2

3

+

2

-

U68A

NS-LM358MX/SOIC8

4 8

C642

1u_10V

+5V

E_CHKTC3052_1R2M080S

L39 1.2uH_8A

IPD09N03L/TO252

IPD06N03LA/TO252

D36

1N5817

IPD09N03L/TO252

IPD06N03LA/TO252

1

Q46

Q43

R710 1

Q71

R700

10K

PWRSEQ_3_GD 55

C648

1u_10V

VCC_1V8-1V2

+

EC51

D34

1N5817

DS

DS

PHASE_1V2

390u_6.3V_OS-CON

PHASE_1V8

R595

2.2-0805

1000p

390u_6.3V_OS-CON

D38

1N5817

R760

2.2-0805

1000p

DS

G

DS

G

+5V

G

Q72

G

3

3.3uH_4A

C584

VCC_1V8-1V2

+

EC57

3.3uH_4A

C733

C592

1u_10V

C719

1u_10V

C591

.01u_50V

C644

.01u_50V

+1.2V

R593

10K_1%

R592

30K_1%

+1.2V_HT

R691

10K_1%

R690

30K_1%

CT13

100u_6.3V/MLCC

+

2

EC65

1000u_6.3V

+

EC48

1000u_6.3V

SB:1.7A

SB:0.6A

P1:2A

P2:1A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

1.2V Power

MS-9166

1

0CC

of

769Friday, May 20, 2005

L38

L40

5

+12V

R223

144

13

VCCCOMP

7

4.7-0805

C209

1u_16V-0805

U25

OCSET

PVCC

BOOT

UGATE

PHASE

LGATE

PGND

GND

ISL6522CB-TR5190

2

10

9

8

12

11

D D

R163

10K

6

EN

C212 .1u

C C

C194 22p_50V

C203 .01u_50V R224 15K_1%

3

SS

1

RT

5

FB

4

+12V

D12

1N4148

C192 .1u_50V-0805

D20

1N5817

1N5817

Near U19,update 6/9

C214

102p_50V

R221 0-0805

R107 0-0805

D19

R253

1.5K

G

G

Q6

FDB6670AL/TO263

3

DS

Q12

FDB6670AL/TO263

DS

C232

1u_10V

D13

1N5817

Near Q4

390u_6.3V_OS-CON

C254

390u_6.3V_OS-CON

D17

1N5817

C286

390u_6.3V_OS-CON

E_CHKM5052_100109Y1

L7 3uH_20A

R172

2.2-0805

C185

102p_50V

2

E_CHKTC3052_1R2M080S

L21 1.2uH_8A

C271

R178

2K_1%

R184

634_1%

+

EC8

1000u_6.3V

470uF/6.3V x 2

+5V

+

EC11

1000u_6.3V

+3.3V

+

12

EC2

47u_16V

1

B B

+12V

C109

+

A A

47u_16V

R98

1.5K_1%

R90

13K_1%

U7 LM2575T-12

1 2

V IN OUTPUT

4

FB

5

ON/OFF

GND

3

L6

100uH_0.5A

D8 SS14

-12V

+

C89

470u_16V

0.2A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

3.3V & -12V Power

MS-9166

1

0CB

of

869Friday, May 20, 2005

5

+2.5V

2.5VSBREF

+12V

D D

PWRSEQ_3_EN55

R826

4.7K

DS

Q86

G

2N7002

R897

1K

DS

Q102

G

2N7002

+12V +3.3V

5

+

6

-

7

U94B

NS-LM358MX/SOIC8

4 8

4

+12V

3

2

1

+2.5V Dual

+2.5V

EC75

+

1000u_6.3V

C904

.1u_16V

P1:0.135

P2:0.135

SB:0.08A

C907

47p_50V

D

Q103

NDS351AN/SOT23

G

S

C911

102p_50V

+5VSB

2.5VSBREF

C288

.1u_16V

R800

1K

+5VSB

3

+

2

-

U31A

NS-LM393MX/SOIC8

4 8

R314

+3.3VDUAL

C313

Q22

FDD6676/TO252

47p_50V

1+0.6 A

+2.5VDUAL

4.7K

D

G

S

+5VSB

1

C301

102p_50V

+5V+2.5VDUAL +2.5V +5V

3/7 update

R791

1K_1%

C C

B B

A A

Threshold voltage = 2.27V

PWRSEQ_6_EN55

Threshold voltage = 2.27V

2.5VSBREF

G

5

100

+12V

DS

R783

1K_1%

R784

10K_1%

R833

4.7K

Q88

2N7002

R785

10K_1%

+5VSB

R811

100-0805

2

VR4

YREG431S/Vf=2.5V

3 1

3/7 update

C817

X_102p

NOPOP

C742

X_102p

NOPOP

G

R794

C814

.1u_16V

R795

4.7K

C816

C815

1u_10V

.1u_16V

+2.5VPLL 0.21A

R898

4.7K

DS

Q98

C872

1u_10V

2N7002

+5V+2.5VDUAL +2.5VPL L +5V

4.7K

3

+

2

-

U83A

NS-LM358MX/SOIC8

4 8

C813

1u_10V

5

+

7

6

-

U83B

NS-LM358MX/SOIC8

4 8

+12V +3.3V

3

+

2

-

U94A

NS-LM358MX/SOIC8

4 8

1

R766

X_10K

PWRSEQ_3_GD 55

C740

X_1u_10V

DS

G

G

C419

22u_10V-1206

+3.3VSB

Q36

2N7002

DS

Q9

2N7002

R457

191_1%

R458

324_1%

SB_PWROK1

SB_PWROK1

SB_PWROK155

EC72

1000u_6.3V

Q32

3 2

VIN VOUT

REF.=1.25V

SOT-223

RC1117S/SOT223

FAIRCHILD/RC1117S

+5V

C737

.1u_16V

4

VOUT

1

ADJ

C414

102p_50V

3

+2.5VPLL

D

Q89

G

PWRSEQ_6_GD 55

NDS351AN/SOT23

S

+

+5VSB

C387

.1u_16V

1

R771

10K

C739

1u_10V

4

2005/3/14 Schematic Update

+12V +3.3VSB+5VSB

R489

R470

4.7K

4.7K

DS

Q34

G

2N7002

+12V +5VSB+5VSB

R236

R254

4.7K

4.7K

DS

Q11

G

2N7002

C402

.1u_16V

2

Q33

G

P-CH

G

N-CH

Q10

G

P-CH

G

N-CH

SOT23SGD_T

P-SI2305DS_SOT23

SOT-23

D S

DS

Q26

IPD06N03LA/TO252

TO-252

+3.3V

SOT23SGD_T

P-SI2305DS_SOT23

SOT-23

D S

DS

Q13

IPD06N03LA/TO252

TO-252

+5V

EC21

+

1000u_6.3V

+3.3VDUAL

AC

D30

1N5817

3A

+

1000u_6.3V

AC

EC28

D21

1N5817

C418

1u_10V

+5VDUAL

8A

+

1000u_6.3V

EC15

C292

1u_10V

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

Main Power

MS-9166

1

969Friday, May 20, 2005

of

0CCustom

5

Note:ICS Requirement:

CL= 18pF = Ext. 30pF

CL= 20pF = Ext. 33pF

14.318MHz

Y3

+3.3V

300 ohm/700mA/0805

C366

33p_50V_NPO

300 ohm/700mA/0805

L23

C349

10u_6.3V_0805

L32

C423

10u_6.3V_0805

.1u_16V

C367

R488 2.2

+3.3V

C350

.047u_16V_X7R

C365

33p_50V_NPO

D D

C C

B B

14_318MHz

+3.3V

FS2 FS1 FS0 CPU HTT PCI

MHz MHz MHz

0 0 0 Hi-Z Hi-Z Hi-Z

0 0 1 X X/3 X/6

0 1 0 180.0 60.2 30.0

0 1 1 220.0 36.5 73.12

1 0 0 100.0 66.6 33.3

1 0 1 133.3 66.6 33.3

1 1 0 166.6 66.6 33.3

1 1 1 200.0 66.6 33.3

ICS9DB108

-------------------------------PCIE_DIV_L:

0 = SRC/2 1= SRC

PCI_BP_L:

0 = Bypass Mode, 1 = PLL Mode

PCIE_HBW_L:

0 = High 1 = Low

14MHZ_XTAL_X1

14MHZ_XTAL_X2

SB_VCC_SMB10CLK15,16,24,25,44,45

SB_VCC_SMB10DATA15,16,24,25,44,45

C1139

C1134

BOT/.047u_16V_X7R

BOT/.047u_16V_X7R

C1135

C1141

BOT/.1u_16V

BOT/.047u_16V_X7R

L37 80_3A-0805

C504

.1u_16V

C1130

EMI

NOPOP

5

+3.3V

C434

X_.1u_16V

SYN_SPREAD_EN SYN_PD_L

FS0_REF2

FS0_REF1

FS0_REF0

R474 10K

R429 10K

R418 10K

R409 10K

A A

4

XTALI

XTALO

SCLK

SDATA

PD_L

SPREAD_EN

IREF

VDD66

VDDPCI

VDDREF

GNDP66

GNDPCI

GNDREF

VDD48

VDDSRC

VDDCPU1

VDDCPU2

VDDCPU3

GND48

GNDSRC

GNDCPU1

GNDCPU2

GNDCPU3

VDDA

GNDA

ICS932S801AG

PCIEXCLKC0

PCIEXCLKT1

PCIEXCLKC1

PCIEXCLKT2

PCIEXCLKC2

PCIEXCLKT3

PCIEXCLKC3

PCIEXCLKT4

PCIEXCLKC4

PCIEXCLKT5

PCIEXCLKC5

PCIEXCLKT6

PCIEXCLKC6

R471 4.7K

R494 4.7K

R490 4.7K

U46

TSSOP48

1

2

SB_VCC_SMB10CLK

SB_VCC_SMB10DATA

SYN_PD_L

SYN_SPREAD_EN

R472 475_1%

SYN_VDD_PLL

C1147

C430

C1127

.047u_16V_X7R

C427

.047u_16V_X7R

4

BOT/.047u_16V_X7R

SYN_AVDD

SB_VCC_SMB10CLK

SB_VCC_SMB10DATA

BOT/.047u_16V_X7R

BOT/.047u_16V_X7R

R481 2.2

+3.3_CLK

C1154

BOT/.1u_16V

C1219

BOT/.1u_16V

C1223

BOT/.1u_16V

C1227

BOT/.1u_16V

SB_VCC_SMB10CLK

SB_VCC_SMB10DATA

C501

10u_6.3V_0805

+3.3V +3.3V

7

8

21

29

SYN_IREF

24

SYN_VCC3

9

15

48

14

20

44

3

27

33

37

41

6

28

32

36

40

22

23

U49

7 5

VDDPCIEX PCIEXCLKT0

8

GND

16

VDDPCIEX

15

GND

22

VDDPCIEX

21

GND

28

VDDA

27

GNDA

3

SCLK

2

SDATA

ICS9FG110

REFIN

PD#

IREF

VDD

HCLK0_P

HCLK0_L

HCLK1_P

HCLK1_L

HCLK2_P

HCLK2_L

HCLK3_P

HCLK3_L

SRCCLK_P

SCRCLK_L

PCICLK0_F0

PCICLK1

PCICLK2

PCICLK3

P66CLK0

P66CLK1

P66CLK2

P66CLK3

FS0_REF0

FS1_REF1

FS2

48MHz_0

48MHz_1

6

9

10

11

12

13

14

18

17

20

19

24

23

1

R497 4.7K

4

26

25

Address:OxDC

3

HCLKP0

43

HCLKN0

42

HCLKP1

39

HCLKN1

38

HCLKP2

35

HCLKN2

34

HCLKP3

31

HCLKN3

30

SRCCLKRP

26

SRCCLKRN

25

PCICLK0

16

REF_33CLK_R REF_33CLK

17

18

19

P66CLK0

10

11

12

13

FS0_REF0

47

FS0_REF1

46

FS0_REF2

45

48MHz_CLK0

4

48MHz_CLK1

5

R433 15_1%

R443 15_1%

R452 15_1%

R459 15_1%

R462 15_1%

R464 15_1%

R468 15_1%

R473 15_1%

R477 33

R484 33

R461 33

R465 33

R449 91

R403 33

R417 33

R436 47

Address:OxD2

R507 33

R512 33

R523 33

R529 33

R525 33

R533 33

R509 33

R515 33

REF_33CLK

R501 475_1%

+3.3_CLK

C1224

BOT/.1u_16V

PCI_VGA_CLK46

PCI_IRQ_CLK141

3

+3.3V

NOPOP

NOPOP

R51049.9_1%

R51649.9_1%

C95 X_10P/16V/NPO

C94 X_10P/16V/NPO

R456 62

R52649.9_1%

R53449.9_1%

PCICLK_BUF40

SB_CLK_P 40

SB_CLK_L 40

GC_CLK_P 30

GC_CLK_L 30

P0_CPUCLKIN 12

P0_CPUCLKINJ 12

P1_CPUCLKIN 21

P1_CPUCLKINJ 21

R485 49.9_1%

R478 49.9_1%

220

R430

PCIE1_CLK100P

PCIE1_CLK100N

PCIE3_CLK100P

PCIE3_CLK100N

R51149.9_1%

R52849.9_1%

R50649.9_1%

R52249.9_1%

PCICLK_BUF

PCI_VGA_CLK

PCI_IRQ_CLK1

2

SRCCLK_P

SRCCLK_N

C412 X_10P/16V/NPO

NOPOP

C404 X_10P/16V/NPO

GC_REFCLK_IN

NOPOP

C361 X_10P/16V/NPO

NOPOP

C371

10P/50V/NPO

PCIE3_L0_CLKP

PCIE3_L0_CLKN

PCIE2_L0_CLKP

PCIE2_L0_CLKN

1

2

3

4

2

SB_REFCLK_IN

SB_14MHz_CLK

C381

10P/50V/NPO

PCIE1_CLK100P 45

PCIE1_CLK100N 45

PCIE2_CLK100P 45

PCIE2_CLK100N 45

PCIE3_L0_CLKP 30

PCIE3_L0_CLKN 30

PCIE2_L0_CLKP 30

PCIE2_L0_CLKN 30

U16

REF

CLKOUT

CLK2

CLK4

CLK1

CLK3

GND

ICW-W163

1

SB_REFCLK_IN 42

GC_REFCLK_IN 31

SB_14MHz_CLK 42

SIO_CLK_48MHz 49

USB_CLK48MHz 41

03/03/2005

Add C1931,C1932,C1933,C1934

C1935,C1936,C1937,C1938,C1939

for EMI requirement

+3.3V

8

PCI_IRQ_CLK2

7

6

VDD

5

C144

.1u_16V

C142

X_.1u_16V

C141 X_10P/16V/NPO

C140 X_10P/16V/NPO

2005/3/8 BOM Update

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Tai p e i H s i e n , T a i w a n . h t t p :/ /www.msi.c om.tw

Title

Size Document Number Rev

Date: Sheet

Clock Synthesizer

MS-9166

1

PCI_IRQ_CLK2 41

BMC_LPC_CLK 57

NOPOP

NOPOP

10 69Friday, May 20, 2005

0CA3

of

5

HT0 is for SH0 & Golem connection

+1.2V_HT

AB10

VLDT_2(1)

AC11

VLDT_2(2)

AD10

VLDT_2(3)

AD8

VLDT_2(4)

AB14

VLDT_2(5)

AC15

VLDT_2(6)

AB16

VLDT_2(7)

TP45

TP46

AC16

AG11

AG12

AH10

AG10

AK11

AL10

AL11

AL12

AJ12

AH12

AC9

AJ10

AG9

AJ8

AH8

AJ6

AH6

AG5

AG6

AJ4

AH4

AG3

AG4

AJ11

AL9

AJ9

AK9

AL7

AL8

AL5

AL6

AJ5

AK5

AL3

AL4

AJ3

AK3

AG7

AG8

AJ7

AK7

VLDT_2(8)

VLDT_2(9)

L2_CADIN_H(15)

L2_CADIN_L(15)

L2_CADIN_H(14)

L2_CADIN_L(14)

L2_CADIN_H(13)

L2_CADIN_L(13)

L2_CADIN_H(12)

L2_CADIN_L(12)

L2_CADIN_H(11)

L2_CADIN_L(11)

L2_CADIN_H(10)

L2_CADIN_L(10)

L2_CADIN_H(9)

L2_CADIN_L(9)

L2_CADIN_H(8)

L2_CADIN_L(8)

L2_CADIN_H(7)

L2_CADIN_L(7)

L2_CADIN_H(6)

L2_CADIN_L(6)

L2_CADIN_H(5)

L2_CADIN_L(5)

L2_CADIN_H(4)

L2_CADIN_L(4)

L2_CADIN_H(3)

L2_CADIN_L(3)

L2_CADIN_H(2)

L2_CADIN_L(2)

L2_CADIN_H(1)

L2_CADIN_L(1)

L2_CADIN_H(0)

L2_CADIN_L(0)

L2_CLKIN_H(1)

L2_CLKIN_L(1)

L2_CLKIN_H(0)

L2_CLKIN_L(0)

L2_CTLIN_H(0)

L2_CTLIN_L(0)

L2_RSVD1

L2_RSVD2

D D

P1_TO_P0_CADOUT_H[15..0]20

P1_TO_P0_CADOUT_L[15..0]20

FROM CPU1

P1_TO_P0_CLKOUT_H120

C C

B B

A A

P1_TO_P0_CLKOUT_L120

P1_TO_P0_CLKOUT_H020

P1_TO_P0_CLKOUT_L020

P1_TO_P0_CTLOUT_H020

P1_TO_P0_CTLOUT_L020

5

P1_TO_P0_CADOUT_H15

P1_TO_P0_CADOUT_L15

P1_TO_P0_CADOUT_H14

P1_TO_P0_CADOUT_L14

P1_TO_P0_CADOUT_H13

P1_TO_P0_CADOUT_L13

P1_TO_P0_CADOUT_H12

P1_TO_P0_CADOUT_L12

P1_TO_P0_CADOUT_H11

P1_TO_P0_CADOUT_L11

P1_TO_P0_CADOUT_H10

P1_TO_P0_CADOUT_L10

P1_TO_P0_CADOUT_H9

P1_TO_P0_CADOUT_L9

P1_TO_P0_CADOUT_H8

P1_TO_P0_CADOUT_L8

P1_TO_P0_CADOUT_H7

P1_TO_P0_CADOUT_L7

P1_TO_P0_CADOUT_H6

P1_TO_P0_CADOUT_L6

P1_TO_P0_CADOUT_H5

P1_TO_P0_CADOUT_L5

P1_TO_P0_CADOUT_H4

P1_TO_P0_CADOUT_L4

P1_TO_P0_CADOUT_H3

P1_TO_P0_CADOUT_L3

P1_TO_P0_CADOUT_H2

P1_TO_P0_CADOUT_L2

P1_TO_P0_CADOUT_H1

P1_TO_P0_CADOUT_L1

P1_TO_P0_CADOUT_H0

P1_TO_P0_CADOUT_L0

CPU1F

SledgeHammer

R658, R659 change to 22ohm reduce ripple

voltage. 03/07.

L2_CADOUT_H(15)

L2_CADOUT_L(15)

L2_CADOUT_H(14)

L2_CADOUT_L(14)

L2_CADOUT_H(13)

L2_CADOUT_L(13)

L2_CADOUT_H(12)

L2_CADOUT_L(12)

L2_CADOUT_H(11)

L2_CADOUT_L(11)

L2_CADOUT_H(10)

L2_CADOUT_L(10)

L2_CADOUT_H(9)

L2_CADOUT_L(9)

L2_CADOUT_H(8)

L2_CADOUT_L(8)

L2_CADOUT_H(7)

L2_CADOUT_L(7)

L2_CADOUT_H(6)

L2_CADOUT_L(6)

L2_CADOUT_H(5)

L2_CADOUT_L(5)

L2_CADOUT_H(4)

L2_CADOUT_L(4)

L2_CADOUT_H(3)

L2_CADOUT_L(3)

L2_CADOUT_H(2)

L2_CADOUT_L(2)

L2_CADOUT_H(1)

L2_CADOUT_L(1)

L2_CADOUT_H(0)

L2_CADOUT_L(0)

L2_CLKOUT_H(1)

L2_CLKOUT_L(1)

L2_CLKOUT_H(0)

L2_CLKOUT_L(0)

L2_CTLOUT_H(0)

L2_CTLOUT_L(0)

L2_RSVD3

L2_RSVD4

4

AH14

AJ14

AG16

AG15

AH16

AJ16

AG18

AG17

AG20

AG19

AH20

AJ20

AG22

AG21

AH22

AJ22

AL14

AL13

AK15

AJ15

AL16

AL15

AK17

AJ17

AK19

AJ19

AL20

AL19

AK21

AJ21

AL22

AL21

AH18

AJ18

AL18

AL17

AK13

AJ13

AG13

AG14

4

P0_TO_P1_CADOUT_H15

P0_TO_P1_CADOUT_L15

P0_TO_P1_CADOUT_H14

P0_TO_P1_CADOUT_L14

P0_TO_P1_CADOUT_H13

P0_TO_P1_CADOUT_L13

P0_TO_P1_CADOUT_H12

P0_TO_P1_CADOUT_L12

P0_TO_P1_CADOUT_H11

P0_TO_P1_CADOUT_L11

P0_TO_P1_CADOUT_H10

P0_TO_P1_CADOUT_L10

P0_TO_P1_CADOUT_H9

P0_TO_P1_CADOUT_L9

P0_TO_P1_CADOUT_H8

P0_TO_P1_CADOUT_L8

P0_TO_P1_CADOUT_H7

P0_TO_P1_CADOUT_L7

P0_TO_P1_CADOUT_H6

P0_TO_P1_CADOUT_L6

P0_TO_P1_CADOUT_H5

P0_TO_P1_CADOUT_L5

P0_TO_P1_CADOUT_H4

P0_TO_P1_CADOUT_L4

P0_TO_P1_CADOUT_H3

P0_TO_P1_CADOUT_L3

P0_TO_P1_CADOUT_H2

P0_TO_P1_CADOUT_L2

P0_TO_P1_CADOUT_H1

P0_TO_P1_CADOUT_L1

P0_TO_P1_CADOUT_H0

P0_TO_P1_CADOUT_L0

TP41

TP40

P0_VDIMM_2.5V

3/7 update

H0_MEMRESET1_L

R749

22_1%

R745

22_1%

R1049 0

C720

.1u_16V

C715

.1u_16V

P0_VDIMM_2.5V

P0_TO_P1_CADOUT_H[15..0] 20

P0_TO_P1_CADOUT_L[15..0] 20

TO CPU1

P0_TO_P1_CLKOUT_H1 20

P0_TO_P1_CLKOUT_L1 20

P0_TO_P1_CLKOUT_H0 20

P0_TO_P1_CLKOUT_L0 20

P0_TO_P1_CTLOUT_H0 20

P0_TO_P1_CTLOUT_L0 20

C1306

BOT/.1u_16V

C1312

C711

102p_50V

BOT/.1u_16V

H0_MEMRESET_L 15,16

TO DIMM

3

P0_VTT_SENSE5

R1013 BOT/42.2_1

R1012 BOT/42.2_1

P0_DDR_VREF0

VREF should be connected to both

VREF pins on the processor. 02/26.

H0_MD[127..64]17

P0_DDR_VREF0

H0_MDQS[35..0]17

3

P0_VTT_1.25V

P0_VTT_1.25V

R624

51_1%

H0_MD127

H0_MD126

H0_MD125

H0_MD124

H0_MD123

H0_MD122

H0_MD121

H0_MD120

H0_MD119

H0_MD118

H0_MD117

H0_MD116

H0_MD115

H0_MD114

H0_MD113

H0_MD112

H0_MD111

H0_MD110

H0_MD109

H0_MD108

H0_MD107

H0_MD106

H0_MD105

H0_MD104

H0_MD103

H0_MD102

H0_MD101

H0_MD100

H0_MD99

H0_MD98

H0_MD97

H0_MD96

H0_MD95

H0_MD94

H0_MD93

H0_MD92

H0_MD91

H0_MD90

H0_MD89

H0_MD88

H0_MD87

H0_MD86

H0_MD85

H0_MD84

H0_MD83

H0_MD82

H0_MD81

H0_MD80

H0_MD79

H0_MD78

H0_MD77

H0_MD76

H0_MD75

H0_MD74

H0_MD73

H0_MD72

H0_MD71

H0_MD70

H0_MD69

H0_MD68

H0_MD67

H0_MD66

H0_MD65

H0_MD64

H0_MDQS35

H0_MDQS34

H0_MDQS33

H0_MDQS32

H0_MDQS31

H0_MDQS30

H0_MDQS29

H0_MDQS28

H0_MDQS27

H0_MDQS26

H0_MDQS25

H0_MDQS24

H0_MDQS23

H0_MDQS22

H0_MDQS21

H0_MDQS20

H0_MDQS19

H0_MDQS18

H0_MDQS17

H0_MDQS16

H0_MDQS15

H0_MDQS14

H0_MDQS13

H0_MDQS12

H0_MDQS11

H0_MDQS10

H0_MDQS9

H0_MDQS8

H0_MDQS7

H0_MDQS6

H0_MDQS5

H0_MDQS4

H0_MDQS3

H0_MDQS2

H0_MDQS1

H0_MDQS0

AC19

AE19

AE18

AC18

AF18

AF19

AF17

AE16

AF22

AG24

AH25

AG26

AH27

AF23

AH24

AF25

AG27

AF26

AF28

AE29

AH29

AE27

AD26

AD27

AC26

AA26

AA28

AD28

AC27

AB29

AA27

AG25

AF27

AB27

AF24

AG28

AC28

AD29

AA31

AE31

J19

H19

F20

G19

F21

F22

AJ26

AJ29

Y27

Y28

V28

U26

Y26

W27

V27

U27

P28

N29

M26

L28

P27

P26

M27

L27

K29

K27

H28

G29

L26

J28

H27

H26

F27

F26

D29

D27

G27

F28

E27

C27

C26

E25

D24

F23

E26

F25

E24

G23

R27

W29

N27

J27

E29

F24

R28

V26

M28

J26

E28

D25

U31

AJ25

AJ30

M30

H30

C30

B25

T31

AL25

AL29

Y29

M29

H29

C29

C25

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT_SENSE

MEMZN

MEMZP

MEMVREF0

MEMVREF1

MEMDATA(127)

MEMDATA(126)

MEMDATA(125)

MEMDATA(124)

MEMDATA(123)

MEMDATA(122)

MEMDATA(121)

MEMDATA(120)

MEMDATA(119)

MEMDATA(118)

MEMDATA(117)

MEMDATA(116)

MEMDATA(115)

MEMDATA(114)

MEMDATA(113)

MEMDATA(112)

MEMDATA(111)

MEMDATA(110)

MEMDATA(109)

MEMDATA(108)

MEMDATA(107)

MEMDATA(106)

MEMDATA(105)

MEMDATA(104)

MEMDATA(103)

MEMDATA(102)

MEMDATA(101)

MEMDATA(100)

MEMDATA(99)

MEMDATA(98)

MEMDATA(97)

MEMDATA(96)

MEMDATA(95)

MEMDATA(94)

MEMDATA(93)

MEMDATA(92)

MEMDATA(91)

MEMDATA(90)

MEMDATA(89)

MEMDATA(88)

MEMDATA(87)

MEMDATA(86)

MEMDATA(85)

MEMDATA(84)

MEMDATA(83)

MEMDATA(82)

MEMDATA(81)

MEMDATA(80)

MEMDATA(79)

MEMDATA(78)

MEMDATA(77)

MEMDATA(76)

MEMDATA(75)

MEMDATA(74)

MEMDATA(73)

MEMDATA(72)

MEMDATA(71)

MEMDATA(70)

MEMDATA(69)

MEMDATA(68)

MEMDATA(67)

MEMDATA(66)

MEMDATA(65)

MEMDATA(64)

MEMDQS(35)

MEMDQS(34)

MEMDQS(33)

MEMDQS(32)

MEMDQS(31)

MEMDQS(30)

MEMDQS(29)

MEMDQS(28)

MEMDQS(27)

MEMDQS(26)

MEMDQS(25)

MEMDQS(24)

MEMDQS(23)

MEMDQS(22)

MEMDQS(21)

MEMDQS(20)

MEMDQS(19)

MEMDQS(18)

MEMDQS(17)

MEMDQS(16)

MEMDQS(15)

MEMDQS(14)

MEMDQS(13)

MEMDQS(12)

MEMDQS(11)

MEMDQS(10)

MEMDQS(9)

MEMDQS(8)

MEMDQS(7)

MEMDQS(6)

MEMDQS(5)

MEMDQS(4)

MEMDQS(3)

MEMDQS(2)

MEMDQS(1)

MEMDQS(0)

CPU1B

MEMCLK_UP_H(3)

MEMCLK_UP_L(3)

MEMCLK_UP_H(2)

MEMCLK_UP_L(2)

MEMCLK_UP_H(1)

MEMCLK_UP_L(1)

MEMCLK_UP_H(0)

MEMCLK_UP_L(0)

MEMCLK_LO_H(3)

MEMCLK_LO_L(3)

MEMCLK_LO_H(2)

MEMCLK_LO_L(2)

MEMCLK_LO_H(1)

MEMCLK_LO_L(1)

MEMCLK_LO_H(0)

MEMCLK_LO_L(0)

MEMCHECK(15)

MEMCHECK(14)

MEMCHECK(13)

MEMCHECK(12)

MEMCHECK(11)

MEMCHECK(10)

SledgeHammer

2

MEMCKE_UP

MEMCKE_LO

RSVD_MA(15)

RSVD_MA(14)

MEMADD(13)

MEMADD(12)

MEMADD(11)

MEMADD(10)

MEMADD(9)

MEMADD(8)

MEMADD(7)

MEMADD(6)

MEMADD(5)

MEMADD(4)

MEMADD(3)

MEMADD(2)

MEMADD(1)

MEMADD(0)

MEMDATA(63)

MEMDATA(62)

MEMDATA(61)

MEMDATA(60)

MEMDATA(59)

MEMDATA(58)

MEMDATA(57)

MEMDATA(56)

MEMDATA(55)

MEMDATA(54)

MEMDATA(53)

MEMDATA(52)

MEMDATA(51)

MEMDATA(50)

MEMDATA(49)

MEMDATA(48)

MEMDATA(47)

MEMDATA(46)

MEMDATA(45)

MEMDATA(44)

MEMDATA(43)

MEMDATA(42)

MEMDATA(41)

MEMDATA(40)

MEMDATA(39)

MEMDATA(38)

MEMDATA(37)

MEMDATA(36)

MEMDATA(35)

MEMDATA(34)

MEMDATA(33)

MEMDATA(32)

MEMDATA(31)

MEMDATA(30)

MEMDATA(29)

MEMDATA(28)

MEMDATA(27)

MEMDATA(26)

MEMDATA(25)

MEMDATA(24)

MEMDATA(23)

MEMDATA(22)

MEMDATA(21)

MEMDATA(20)

MEMDATA(19)

MEMDATA(18)

MEMDATA(17)

MEMDATA(16)

MEMDATA(15)

MEMDATA(14)

MEMDATA(13)

MEMDATA(12)

MEMDATA(11)

MEMDATA(10)

MEMDATA(9)

MEMDATA(8)

MEMDATA(7)

MEMDATA(6)

MEMDATA(5)

MEMDATA(4)

MEMDATA(3)

MEMDATA(2)

MEMDATA(1)

MEMDATA(0)

MEMRESET_L

MEMBANK(1)

MEMBANK(0)

MEMRAS_L

MEMCAS_L

MEMWE_L

MEMCHECK(9)

MEMCHECK(8)

MEMCHECK(7)

MEMCHECK(6)

MEMCHECK(5)

MEMCHECK(4)

MEMCHECK(3)

MEMCHECK(2)

MEMCHECK(1)

MEMCHECK(0)

MEMCS_L(7)

MEMCS_L(6)

MEMCS_L(5)

MEMCS_L(4)

MEMCS_L(3)

MEMCS_L(2)

MEMCS_L(1)

MEMCS_L(0)

2

G20

G21

AE21

AE20

H0_MEMCLK_H3

L24

H0_MEMCLK_L3

L25

H0_MEMCLK_H2

R23

H0_MEMCLK_L2

T23

H23

J23

AD21

AD20

H0_MEMCLK_H1

Y23

H0_MEMCLK_L1

AA23

H0_MEMCLK_H0

U25

H0_MEMCLK_L0

U24

H0_MCKEUP

H24

H0_MCKELO

H25

V23

M23

H0_MAA13

AE23

H0_MAA12

J24

H0_MAA11

J25

H0_MAA10

V24

H0_MAA9

K23

H0_MAA8

L23

H0_MAA7

K25

H0_MAA6

M25

H0_MAA5

M24

H0_MAA4

N25

H0_MAA3

N23

H0_MAA2

P23

H0_MAA1

T25

H0_MAA0

V25

H0_MD63

AJ24

H0_MD62

AK25

H0_MD61

AK27

H0_MD60

AJ27

H0_MD59

AL24

H0_MD58

AK24

H0_MD57

AL26

H0_MD56

AL27

H0_MD55

AJ28

H0_MD54

AK30

H0_MD53

AJ31

H0_MD52

AG29

H0_MD51

AL28

H0_MD50

AK28

H0_MD49

AH31

H0_MD48

AG30

H0_MD47

AG31

H0_MD46

AF30

H0_MD45

AD31

H0_MD44

AC30

H0_MD43

AF29

H0_MD42

AF31

H0_MD41

AD30

H0_MD40

AC29

H0_MD39

AB31

H0_MD38

AA29

H0_MD37

Y31

H0_MD36

W31

H0_MD35

AC31

H0_MD34

AA30

H0_MD33

Y30

H0_MD32

V29

H0_MD31

P31

H0_MD30

M31

H0_MD29

L30

H0_MD28

L29

H0_MD27

P29

H0_MD26

N31

H0_MD25

L31

H0_MD24

K31

H0_MD23

J30

H0_MD22

J29

H0_MD21

G31

H0_MD20

F29

H0_MD19

J31

H0_MD18

H31

H0_MD17

F31

H0_MD16

F30

H0_MD15

D31

H0_MD14

C31

H0_MD13

B30

H0_MD12

C28

H0_MD11

E31

H0_MD10

E30

H0_MD9

A29

H0_MD8

B28

H0_MD7

B27

H0_MD6

A26

H0_MD5

C24

H0_MD4

A24

H0_MD3

A28

H0_MD2

A27

H0_MD1

A25

H0_MD0

B24

H0_MEMRESET1_L

G25

W25

W23

H0_-MSRASA

Y25

H0_-MSCASA

AA25

Y24

H0_MEMCHECK15

U28

H0_MEMCHECK14

T29

H0_MEMCHECK13

P24

H0_MEMCHECK12

P25

H0_MEMCHECK11

T27

H0_MEMCHECK10

R26

H0_MEMCHECK9

R25

H0_MEMCHECK8

R24

H0_MEMCHECK7

V30

H0_MEMCHECK6

U29

H0_MEMCHECK5

R30

H0_MEMCHECK4

P30

H0_MEMCHECK3

V31

H0_MEMCHECK2

U30

H0_MEMCHECK1

R29

H0_MEMCHECK0

R31

AD23

AE25

AD24

AD25

H0_-MCS3

AC24

H0_-MCS2

AC25

H0_-MCS1

AB25

H0_-MCS0

AA24

1

H0_MEMCLK_H3

R1010

H0_MEMCLK_H3 16

H0_MEMCLK_L3 16

H0_MEMCLK_H2 15

H0_MEMCLK_L2 15

H0_MEMCLK_H1 16

H0_MEMCLK_L1 16

H0_MEMCLK_H0 15

H0_MEMCLK_L0 15

H0_MCKEUP 17

H0_MCKELO 17

H0_MAA[13..0] 17

H0_MD[63..0] 17

H0_MEMBAKA1 17

H0_MEMBAKA0 17

H0_-MSRASA 17

H0_-MSCASA 17

H0_-MSWEA 17

H0_MEMCHECK15 17

H0_MEMCHECK14 17

H0_MEMCHECK13 17

H0_MEMCHECK12 17

H0_MEMCHECK11 17

H0_MEMCHECK10 17

H0_MEMCHECK9 17

H0_MEMCHECK8 17

H0_MEMCHECK7 17

H0_MEMCHECK6 17

H0_MEMCHECK5 17

H0_MEMCHECK4 17

H0_MEMCHECK3 17

H0_MEMCHECK2 17

H0_MEMCHECK1 17

H0_MEMCHECK0 17

H0_-MCS3 17

H0_-MCS2 17

H0_-MCS1 17

H0_-MCS0 17

BOT/120_1%/

H0_MEMCLK_L3

H0_MEMCLK_H2

R1008

BOT/120_1%/

H0_MEMCLK_L2

H0_MEMCLK_H1

R1009

BOT/120_1%/

H0_MEMCLK_L1

H0_MEMCLK_H0

R1011

BOT/120_1%/

H0_MEMCLK_L0

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

Date: Sheet

CPU0 DDR & HT

MS-9166

1

0CC

of

11 69Friday, May 20, 2005

5

4

3

2

1

R667 should be pulled to VDDIO_RUN through

TP59

P0_R_CLKIN

P0_R_CLKINJ

P0_NC_G14

P0_NC_H14

P0_NC_T3

P0_NC_T4

TP54

TP52

TP39

TP66

TP65

TP53

TP64

TP61

TP57

TP58

a 680ohm 02/26.

C1

VDDA1

D2

VDDA2

C2

VDDA3

E1

L0_REF1

D1

L0_REF0

L7

COREFB_H

L6

COREFB_L

K7

CORESENSE_H

G16

CLKIN_H

H16

CLKIN_L

G14

NC_G14

H14

NC_H14

AE6

TMS

AE7

TCK

AD7

TRST_L

AF7

TDI

J7

DBREQ_L

AE10

NC_AE10

AE11

NC_AE11

AF11

NC_AF11

AE13

NC_AE13

AE12

NC_AE12

T3

NC_T3

T4

NC_T4

AF13

NC_AF13

L8

NC_L8

K8

NC_K8

AF15

NC_AF15

AE14

NC_AE14

G12

RESET_L

J6

LDTSTOP_L

F12

PWROK

AG1

NC

AH2

NC

H9

NC

AJ2

NC

AA6

NC

AC6

NC

N6

NC

RSVD_SMBUSC

RSVD_SMBUSD

SledgeHammer

CPU1C

THERMTRIP_L

THERMDA

THERMDC

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

NC_H13/BP(3)

NC_G6/BP(2)

NC_F7/BP(1)

NC_H12/BP(0)

FBCLKOUT_H

FBCLKOUT_L

DBRDY

NC_V5

NC_U5

NC_H7

NC_T7

NC_W6

NC_R6

NC_U6

TDO

AE15

AJ1

AH1

G9

F9

G10

H11

G11

H13

G6

F7

H12

G18

H18

AE8

G8

V5

U5

H7

T7

W6

R6

U6

AF9

AE9

P0_T7

P0_W6

P0_R6

P0_U6

VERY CLOSE TO CPU

OPTERON_RSTJ55

CPU_LDTSTOPJ55

P0_R_CLKIN

R1014

BOT/169_1%

P0_R_CLKINJ

P0_DBREQJ29

CPU_PWROK55

R904

X_84.5_1%

NOPOP

D D

C C

B B

A A

+1.2V_HT +2.5VPLL

P0_COREFB3

P0_COREFBJ3

P0_CPUCLKIN10

P0_CPUCLKINJ10

R905

X_120_1%

NOPOP

R906

X_120_1%

NOPOP

P0_VDIMM_2.5V

R907

84.5_1%

P0_VDIMM_2.5V

P0_SCANCLK129

P0_SCANCLK229

P0_SCANEN29

P0_SSENA29

P0_SSENB29

R903

84.5_1%

L45 180nH_.45A-1210

P0_VDDA_2.5V

R880 42.2_1%

R879 42.2_1%

R909 0

R908 0

BOT/3900p_50V

C1412

C1411

BOT/3900p_50V

P0_TMS29

P0_TCK29

P0_TRSTJ29

P0_TDI29

P0_NC_AE14

P0_VDIMM_2.5V

R763

680

P0_P1_THERMTRIPJ 55,57

P0_THERMDA 56

P0_THERMDC 56

P0_VID4

P0_VID3

P0_VID2

P0_VID1

P0_VID0

P0_BP3 29

P0_BP2 29

P0_BP1 29

P0_BP0 29

R752

80.6_1%

P0_TDO 29

P0_DBRDY 29

P0_R6

P0_U6

P0_T7

P0_W6

RN217 nopop. (Opteron Ananlog pins does

not need pull down (pin U6, R6, W6, T7)

02/26.

RN161

X_510-8P4R

NOPOP

TP44

TP62

TP63

TP56

TP49

TP50

TP60

R792 560

R787 560

R786 560

R772 560

R776 560

P0_VDDA_2.5V

R934

549_1%

C906

4.7u_6.3V-0805

Will try 560ohm to instead of 0ohm

P0_VID4

P0_VID3

P0_VID2

P0_VID1

P0_VID0

C882

102p_50V

C1416

BOT/3900p_50V

P0_VID[4..0] 3,51

C1415

BOT/.22u_16V

VID[4:0] should have 560ohm series resistors placed on the signals. 02/26.

NC_H13, NC_G6 should have only one test point (no pullup or pulldown). 02/26.

R671 should be populated. 02/26.

STRAPPINGS

3/7 update

P0_NC_G14

P0_NC_AE14

P0_NC_AF13

P0_NC_H14

P0_SCANEN

P0_SCANCLK1

12

34

56

78

P0_SCANCLK2P0_NC_AF13

P0_SSENA

P0_SSENB

P0_BP1

P0_BP0

P0_NC_T4

P0_NC_T3

R762 820_1%

R764

R765

R767 820_1%

R788 680

R793 680

R789 680

R777 680

R778 680

R881 680

R882 680

03/12 update

R886

49.9_1%

P0_VDIMM_2.5V

680

680

+1.2V_HT

R901 49.9_1%

R887 X_49.9_1%

R902

X_49.9

NOPOP

NOPOP

CT34

100u_6.3V/MLCC

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

CPU0 HDT & MISC

MS-9166

1

0CB

of

12 69Friday, May 20, 2005

5

4

3

2

1

+1.2V_HT

K10

VLDT_1(1)

J11

VLDT_1(2)

H10

D D

L0_TO_P0_CADOUT_H[15..0]30

L0_TO_P0_CADOUT_L[15..0]30

C C

L0_TO_P0_CLKOUT_H130

L0_TO_P0_CLKOUT_L130

L0_TO_P0_CLKOUT_H030

L0_TO_P0_CLKOUT_L030

L0_TO_P0_CTLOUT_H30

B B

L0_TO_P0_CTLOUT_L30

L0_TO_P0_CADOUT_H15

L0_TO_P0_CADOUT_L15

L0_TO_P0_CADOUT_H14

L0_TO_P0_CADOUT_L14

L0_TO_P0_CADOUT_H13

L0_TO_P0_CADOUT_L13

L0_TO_P0_CADOUT_H12

L0_TO_P0_CADOUT_L12

L0_TO_P0_CADOUT_H11

L0_TO_P0_CADOUT_L11

L0_TO_P0_CADOUT_H10

L0_TO_P0_CADOUT_L10

L0_TO_P0_CADOUT_H9

L0_TO_P0_CADOUT_L9

L0_TO_P0_CADOUT_H8

L0_TO_P0_CADOUT_L8

L0_TO_P0_CADOUT_H7

L0_TO_P0_CADOUT_L7

L0_TO_P0_CADOUT_H6

L0_TO_P0_CADOUT_L6

L0_TO_P0_CADOUT_H5

L0_TO_P0_CADOUT_L5

L0_TO_P0_CADOUT_H4

L0_TO_P0_CADOUT_L4

L0_TO_P0_CADOUT_H3

L0_TO_P0_CADOUT_L3

L0_TO_P0_CADOUT_H2

L0_TO_P0_CADOUT_L2

L0_TO_P0_CADOUT_H1

L0_TO_P0_CADOUT_L1

L0_TO_P0_CADOUT_H0

L0_TO_P0_CADOUT_L0

TP43

TP42

K14

K16

E14

E13

C15

D15

E16

E15

C17

D17

C19

D19

E20

E19

C21

D21

E22

E21

C14

B14

A16

A15

C16

B16

A18

A17

A20

A19

C20

B20

A22

A21

C22

B22

E18

E17

C18

B18

A14

A13

C13

D13

H8

J15

J16

J9

VLDT_1(3)

VLDT_1(4)

VLDT_1(5)

VLDT_1(6)

VLDT_1(7)

VLDT_1(8)

VLDT_1(9)

L1_CADIN_H(15)

L1_CADIN_L(15)

L1_CADIN_H(14)

L1_CADIN_L(14)

L1_CADIN_H(13)

L1_CADIN_L(13)

L1_CADIN_H(12)

L1_CADIN_L(12)

L1_CADIN_H(11)

L1_CADIN_L(11)

L1_CADIN_H(10)

L1_CADIN_L(10)

L1_CADIN_H(9)

L1_CADIN_L(9)

L1_CADIN_H(8)

L1_CADIN_L(8)

L1_CADIN_H(7)

L1_CADIN_L(7)

L1_CADIN_H(6)

L1_CADIN_L(6)

L1_CADIN_H(5)

L1_CADIN_L(5)

L1_CADIN_H(4)

L1_CADIN_L(4)

L1_CADIN_H(3)

L1_CADIN_L(3)

L1_CADIN_H(2)

L1_CADIN_L(2)

L1_CADIN_H(1)

L1_CADIN_L(1)

L1_CADIN_H(0)

L1_CADIN_L(0)

L1_CLKIN_H(1)

L1_CLKIN_L(1)

L1_CLKIN_H(0)

L1_CLKIN_L(0)

L1_CTLIN_H(0)

L1_CTLIN_L(0)

L1_RSVD1

L1_RSVD2

SledgeHammer

CPU1E

L1_CADOUT_H(15)

L1_CADOUT_L(15)

L1_CADOUT_H(14)

L1_CADOUT_L(14)

L1_CADOUT_H(13)

L1_CADOUT_L(13)

L1_CADOUT_H(12)

L1_CADOUT_L(12)

L1_CADOUT_H(11)

L1_CADOUT_L(11)

L1_CADOUT_H(10)

L1_CADOUT_L(10)

L1_CADOUT_H(9)

L1_CADOUT_L(9)

L1_CADOUT_H(8)

L1_CADOUT_L(8)

L1_CADOUT_H(7)

L1_CADOUT_L(7)

L1_CADOUT_H(6)

L1_CADOUT_L(6)

L1_CADOUT_H(5)

L1_CADOUT_L(5)

L1_CADOUT_H(4)

L1_CADOUT_L(4)

L1_CADOUT_H(3)

L1_CADOUT_L(3)

L1_CADOUT_H(2)

L1_CADOUT_L(2)

L1_CADOUT_H(1)

L1_CADOUT_L(1)

L1_CADOUT_H(0)

L1_CADOUT_L(0)

L1_CLKOUT_H(1)

L1_CLKOUT_L(1)

L1_CLKOUT_H(0)

L1_CLKOUT_L(0)

L1_CTLOUT_H(0)

L1_CTLOUT_L(0)

L1_RSVD3

L1_RSVD4

P0_TO_L0_CADOUT_H15

D11

P0_TO_L0_CADOUT_L15

C11

P0_TO_L0_CADOUT_H14

E9

P0_TO_L0_CADOUT_L14

E10

P0_TO_L0_CADOUT_H13

D9

P0_TO_L0_CADOUT_L13

C9

P0_TO_L0_CADOUT_H12

E7

P0_TO_L0_CADOUT_L12

E8

P0_TO_L0_CADOUT_H11

E5

P0_TO_L0_CADOUT_L11

E6

P0_TO_L0_CADOUT_H10

D5

P0_TO_L0_CADOUT_L10

C5

P0_TO_L0_CADOUT_H9

E3

P0_TO_L0_CADOUT_L9

E4

P0_TO_L0_CADOUT_H8

D3

P0_TO_L0_CADOUT_L8

C3

P0_TO_L0_CADOUT_H7

A11

P0_TO_L0_CADOUT_L7

A12

P0_TO_L0_CADOUT_H6

B10

P0_TO_L0_CADOUT_L6

C10

P0_TO_L0_CADOUT_H5

A9

P0_TO_L0_CADOUT_L5

A10

P0_TO_L0_CADOUT_H4

B8

P0_TO_L0_CADOUT_L4

C8

P0_TO_L0_CADOUT_H3

B6

P0_TO_L0_CADOUT_L3

C6

P0_TO_L0_CADOUT_H2

A5

P0_TO_L0_CADOUT_L2

A6

P0_TO_L0_CADOUT_H1

B4

P0_TO_L0_CADOUT_L1

C4

P0_TO_L0_CADOUT_H0

A3

P0_TO_L0_CADOUT_L0

A4

D7

C7

A7

A8

B12

C12

E11

TP47

E12

TP48

P0_TO_L0_CADOUT_H[15..0] 30

P0_TO_L0_CADOUT_L[15..0] 30

P0_TO_L0_CLKOUT_H1 30

P0_TO_L0_CLKOUT_L1 30

P0_TO_L0_CLKOUT_H0 30

P0_TO_L0_CLKOUT_L0 30

P0_TO_L0_CTLOUT_H 30

P0_TO_L0_CTLOUT_L 30

+1.2V_HT

N7

VLDT_0(1)

R7

VLDT_0(2)

U7

VLDT_0(3)

W7

VLDT_0(4)

M8

VLDT_0(5)

P8

VLDT_0(6)

AA7

VLDT_0(7)

V8

VLDT_0(8)

Y8

VLDT_0(9)

R5

L0_CADIN_H(15)

T5

L0_CADIN_L(15)

P3

L0_CADIN_H(14)

P4

L0_CADIN_L(14)

N5

L0_CADIN_H(13)

P5

L0_CADIN_L(13)

M3

L0_CADIN_H(12)

M4

L0_CADIN_L(12)

K3

L0_CADIN_H(11)

K4

L0_CADIN_L(11)

J5

L0_CADIN_H(10)

K5

L0_CADIN_L(10)

H3

L0_CADIN_H(9)

H4

L0_CADIN_L(9)

G5

TO GOLEMFROM GOLEM

H5

R3

R2

N1

P1

N3

N2

L1

M1

J1

K1

J3

J2

G1

H1

G3

G2

L5

M5

L3

L2

R1

T1

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

SledgeHammer

CPU1A

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

V4

V3

Y5

W5

Y4

Y3

AB5

AA5

AD5

AC5

AD4

AD3

AF5

AE5

AF4

AF3

V1

U1

W2

W3

Y1

W1

AA2

AA3

AC2

AC3

AD1

AC1

AE2

AE3

AF1

AE1

AB4

AB3

AB1

AA1

U2

U3

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

CPU0 HT0 & HT2

MS-9166

1

0CB

of

13 69Friday, May 20, 2005

5

4

3

2

1

P0_VDIMM_2.5V

123456

78

RN119

L19

W21

AA21

VDDIO1

VDDIO2

VDDIO3

VSS6

VSS7

VSS8

F17

P19

N30F1F2K2P2

C1328

BOT/.22u_16V

C1151

BOT/102p_50V

R796

1K

J21

M22

VDDIO4

VDDIO5

VSS9

VSS10

+1.2V_HT

+1.2V_HT

P22

T22

VDDIO6

VSS11

VDDIO7

VSS12

1K-8P4R

V22

Y22

AB22

AJ23

AA19

C23

E23

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VSS92

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

T13V2AB2

AF2

AK2B3AH3G4L4R4V13W4AC4F5D6H6M7

+5VSB

C1408

BOT/.22u_16V

C1329

BOT/102p_50V

CT51

BOT/100u_6.3V/MLCC

C865

C835

.22u_16V

.22u_16V

K26

T26

AE28

VDDIO15

VDDIO16

VDDIO17

VSS19

VSS20

VSS21

R877

X_10K

NOPOP

C1405

BOT/.22u_16V

C1406

BOT/102p_50V

D D

CPU1D

C C

+1.2V_HT

+1.2V_HT

B B

G26

VDDIO18

VSS93

N26

W26

VDDIO19

VSS22

C743

102p_50V

RN127

1K-8P4R

AE26

AG23

K20

D28

K28

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VSS23

VSS24

VSS25

VSS26

VSS27

AB7Y6AD6

H0_PRESENT 42

C1149

BOT/.22u_16V

C1409

BOT/102p_50V

CT31

100u_6.3V/MLCC

P0_VTT_1.25V

T28

AB28

AH28

VDDIO25

VDDIO26

VDDIO27

VSS28

VSS29

VSS30

J17

C1420

BOT/102p_50V

123456

78

AH26

G28

N28

W28

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VSS94

VSS31

VSS32

VSS33

VSS34

AK6B7F14P7V7Y7M6

C1150

BOT/.22u_16V

C1407

BOT/102p_50V

C818

4.7u_35V-1206

AB26

AB20

L21

VDDIO33

VDDIO34

VDDIO35

VSS35

VSS36

VSS37

C1335

BOT/102p_50V

P0_VDDIO_SENSE5

N21

R21

U21

H22

VDDIO36

VDDIO37

VDDIO38

VDDIO40

VSS95

VSS38

VSS39

VSS40

Y13N8R8U8W8

C1225

BOT/.22u_16V

C860

4.7u_6.3V-0805

D26

K22

A23

U23

AL23

AC21

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VSS41

VSS42

VSS43

VSS44

VSS45

AA8

AF8F8G17K9AB13M9P9

C1232

BOT/.22u_16V

C1324

BOT/102p_50V

VDDIO47

VSS46

AD22

VDDIO48

VSS96

VSS47

P0_VDIMM_2.5V

R623

AB23

AC23

AF20

VDDIOFB_L

VDDIOFB_H

VDDIO_SENSE

VSS48

VSS49

T9

C1414

BOT/102p_50V

51_1%

VSS50

AC22Y9AB9

VSS51

VSS52

AD9

P0_VCORE

VSS53

VSS54

D10

J10

VSS55

V6

AD12H2AA4

VDD117

VDD118

VSS97

VSS56

AD13

L10

C864

.22u_16V

X_68-8P4R

VDD1

VDD2

VSS57

VSS58

N10

R10

RN164

NOPOP

T18

V18

VDD3

VDD4

VSS59

VSS60

U10T6AA10

123456

78

Y18

K12

F19

N19

R19

U19

W19

D20

AE4

M20

P20

T20

V20

Y20

AK20

B21

AH21

AK4B5AH5K6P6T8AB6

VDD5

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VSS71

VSS99

VSS72

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

V11

N14

Y11

AA12

N16

AF12

F13

G15

F10

AD15

VSS61

VDD119

VSS62

VSS63

VSS64

VSS98

VSS65

VSS66

VSS67

VSS68

VSS69

AC10

VSS70

AK10

B11

L14

H15J8K11

M11

P11

T11

Screw holes connect to GND 5/5 update

CPU1G

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

SledgeHammer

P0_VCORE

P0_VCORE

4.7u_35V-1206

P0_VCORE

C887

.22u_16V

C838

C861

.22u_16V

LAYOUT: Place clolse to socket.

C819

4.7u_35V-1206

VDD25

VSS88

AF6M2F6D8G7

AB8

AK8B9K18L9N9R9T2U9W9

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VSS89

VSS101

VSS90

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

K13

U14

M13

AB11

AD11

AH11

G13

J12

N12

R12

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

C867

.22u_16V

C870

4.7u_35V-1206

VDD35

VSS79

VDD36

VSS80

U12

VDD37

VDD38

VDD39

VSS100

VSS81

VSS102

R14

W12

W14

C857

.22u_16V

C725

4.7u_35V-1206

VDD40

VSS103

AA14

VDD41

VSS104

AC14

VDD42

VSS105

AH15

AK14

AA9

VDD43

VSS106

B15

AB18

AH9

W13

VDD44

VDD45

VDD46

VSS107

VSS108

VSS109

K15

M15

B23