MSI MS-9161 Schematic 0B_0119

5

4

MS-9161 Dual K8 1U Rackmount / Tower System

Revision : 00A

3

2

1

D D

C C

Date : 11/28/2003

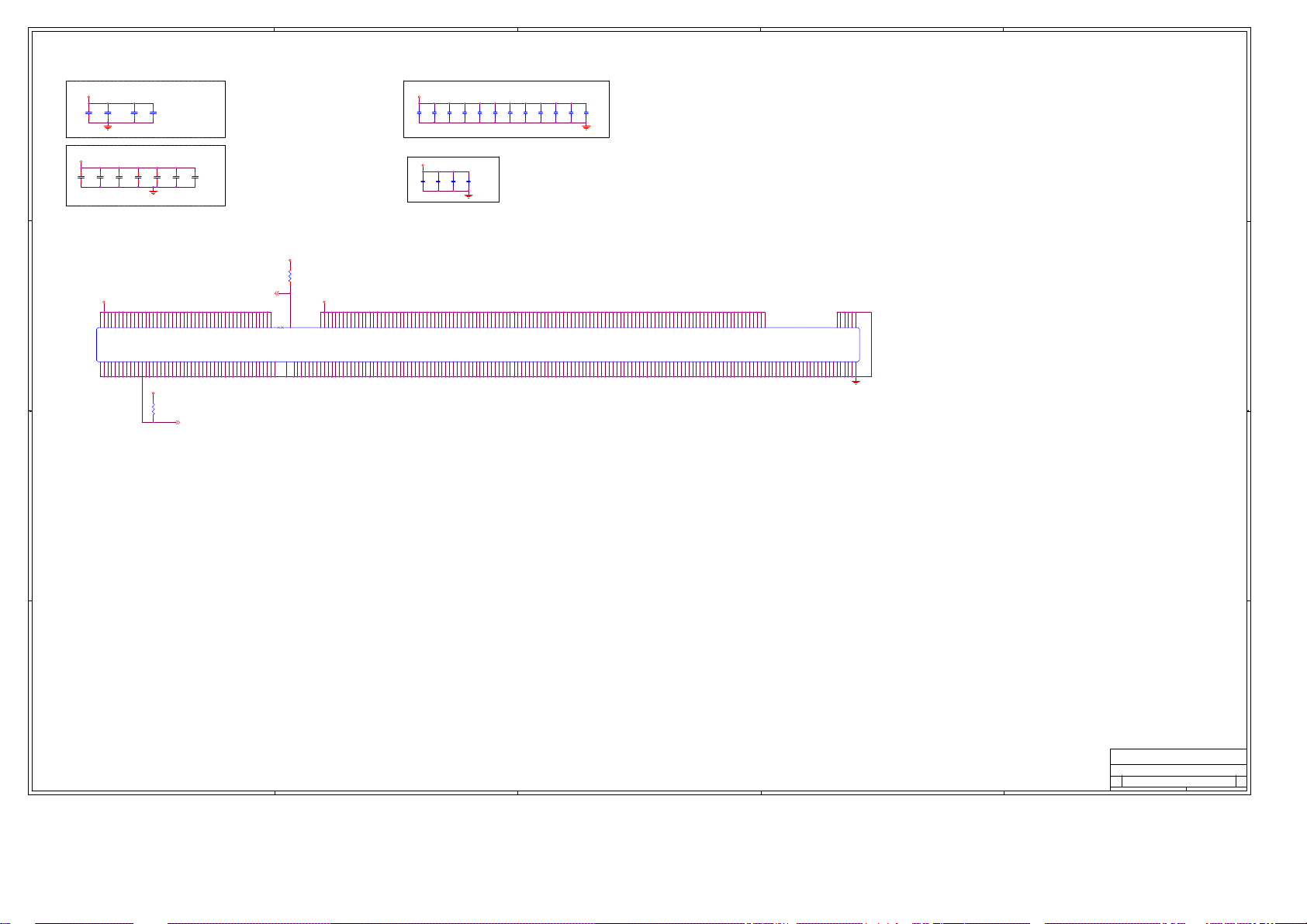

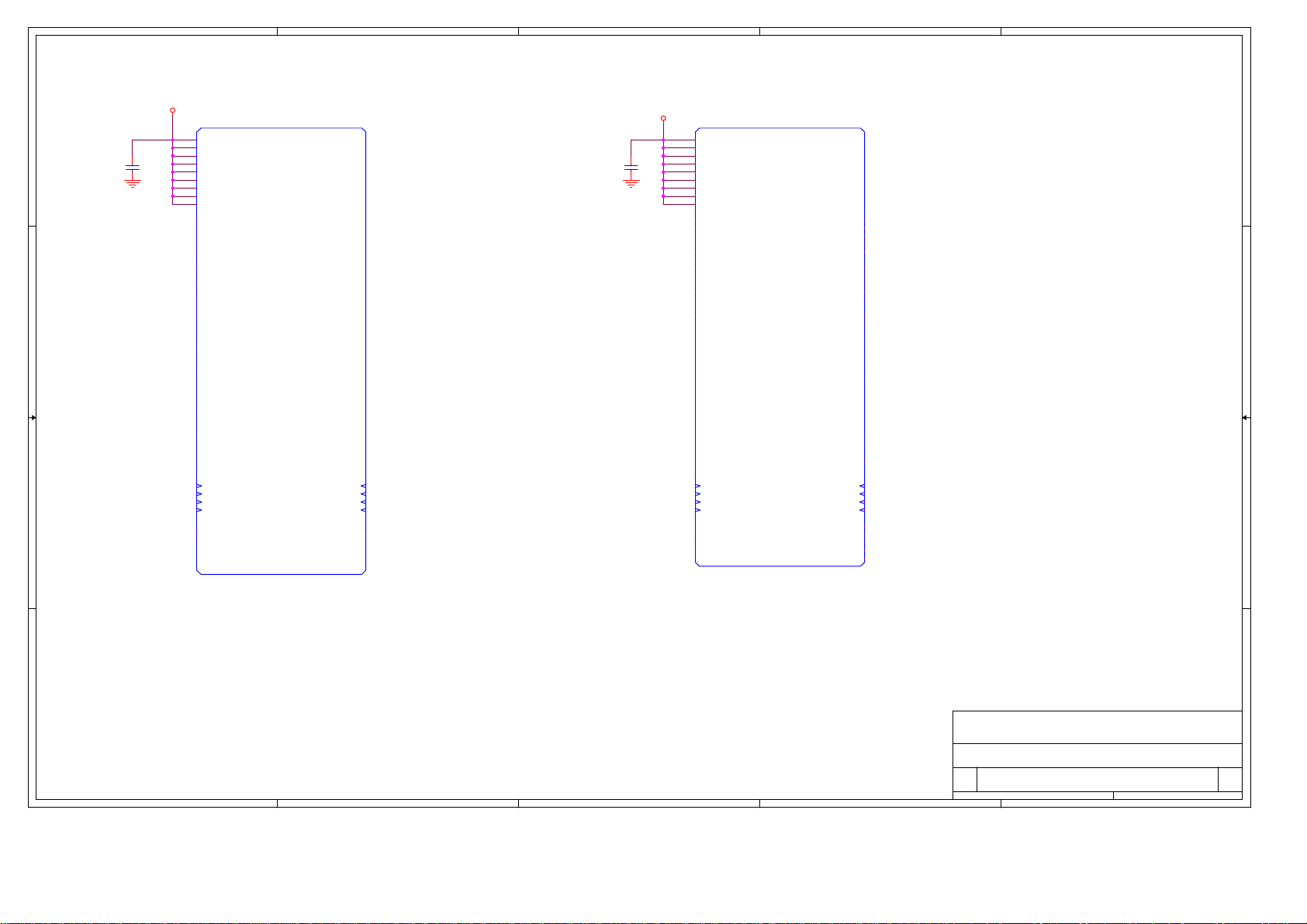

01 COVER

02 Block Diagram

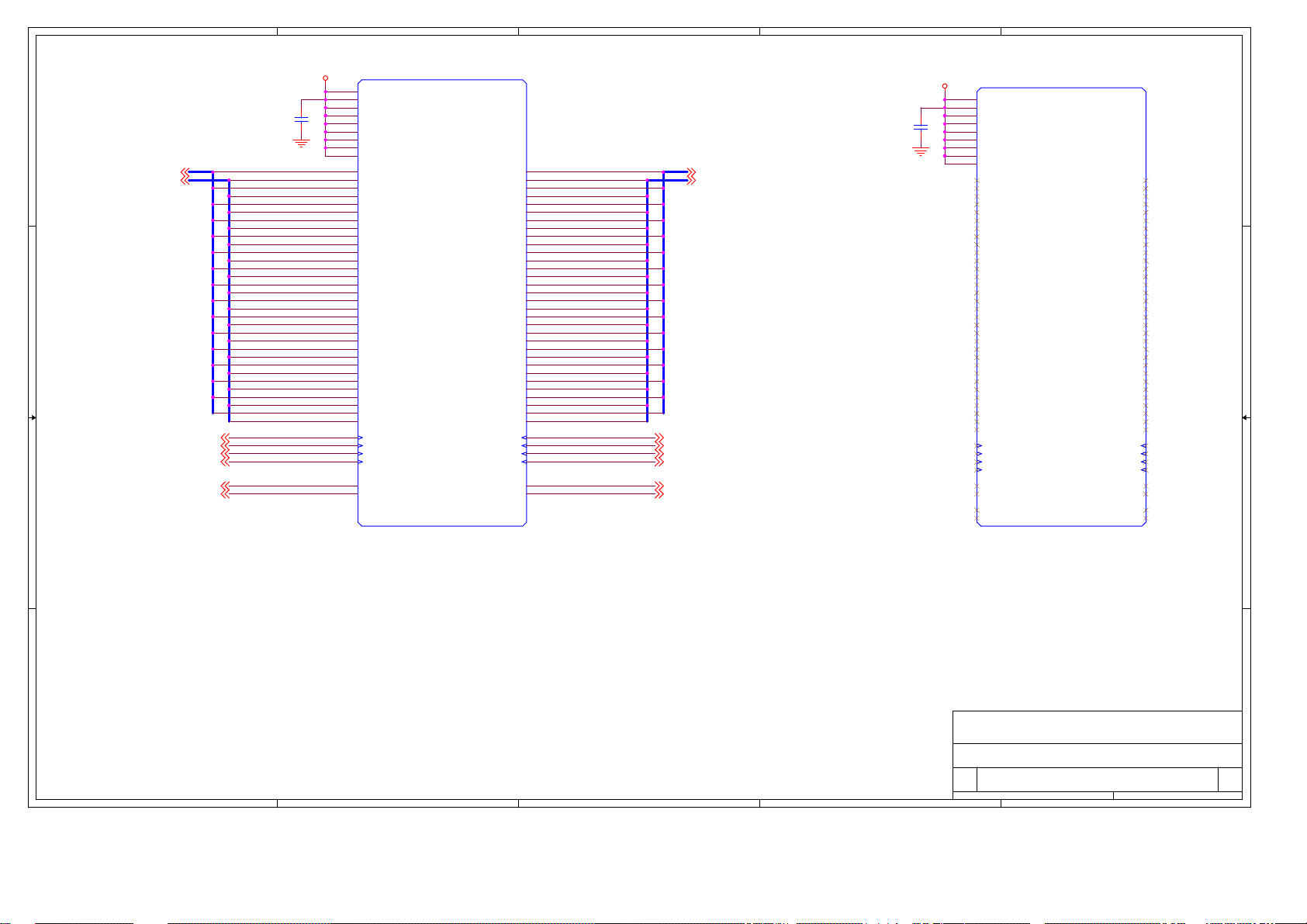

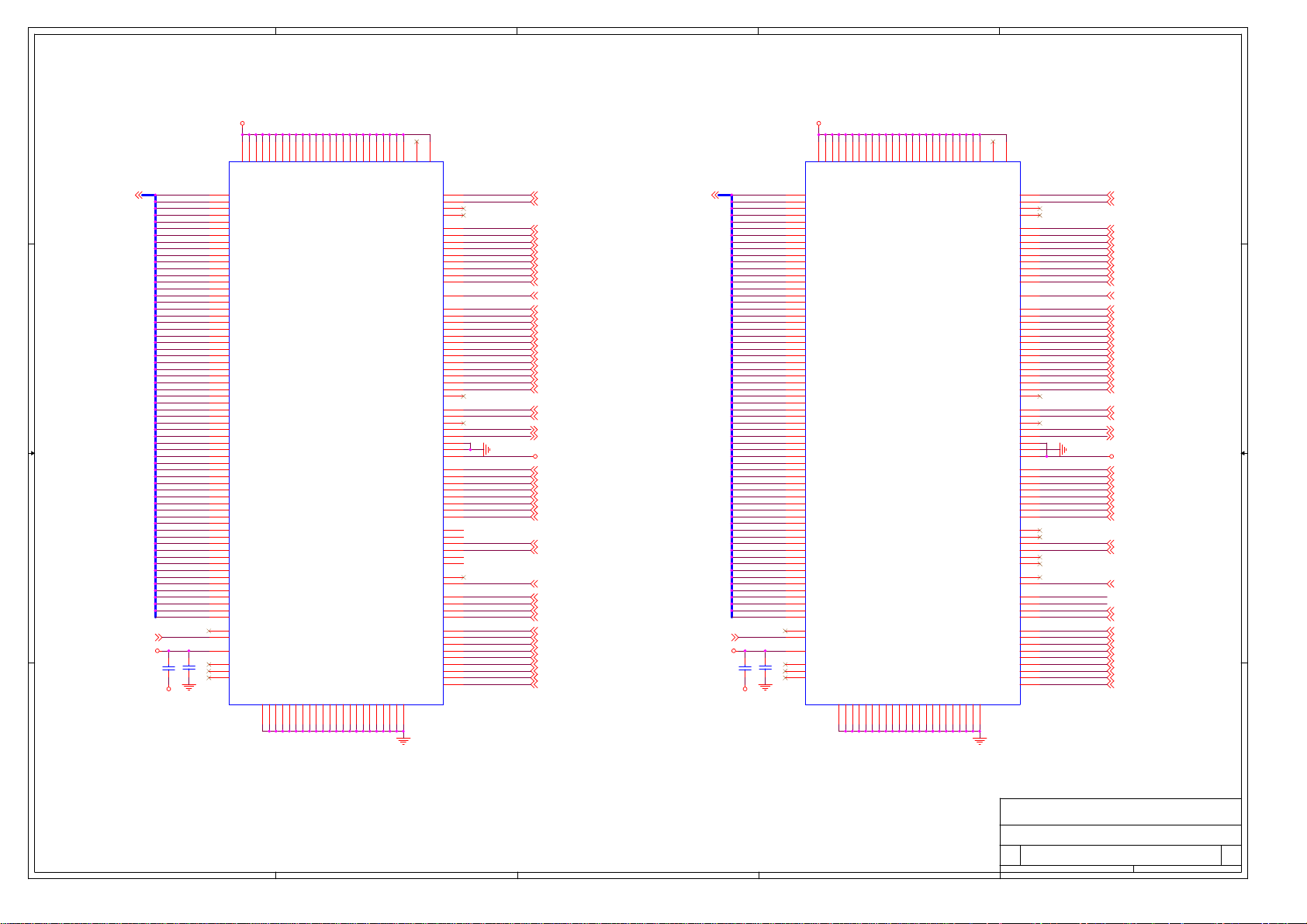

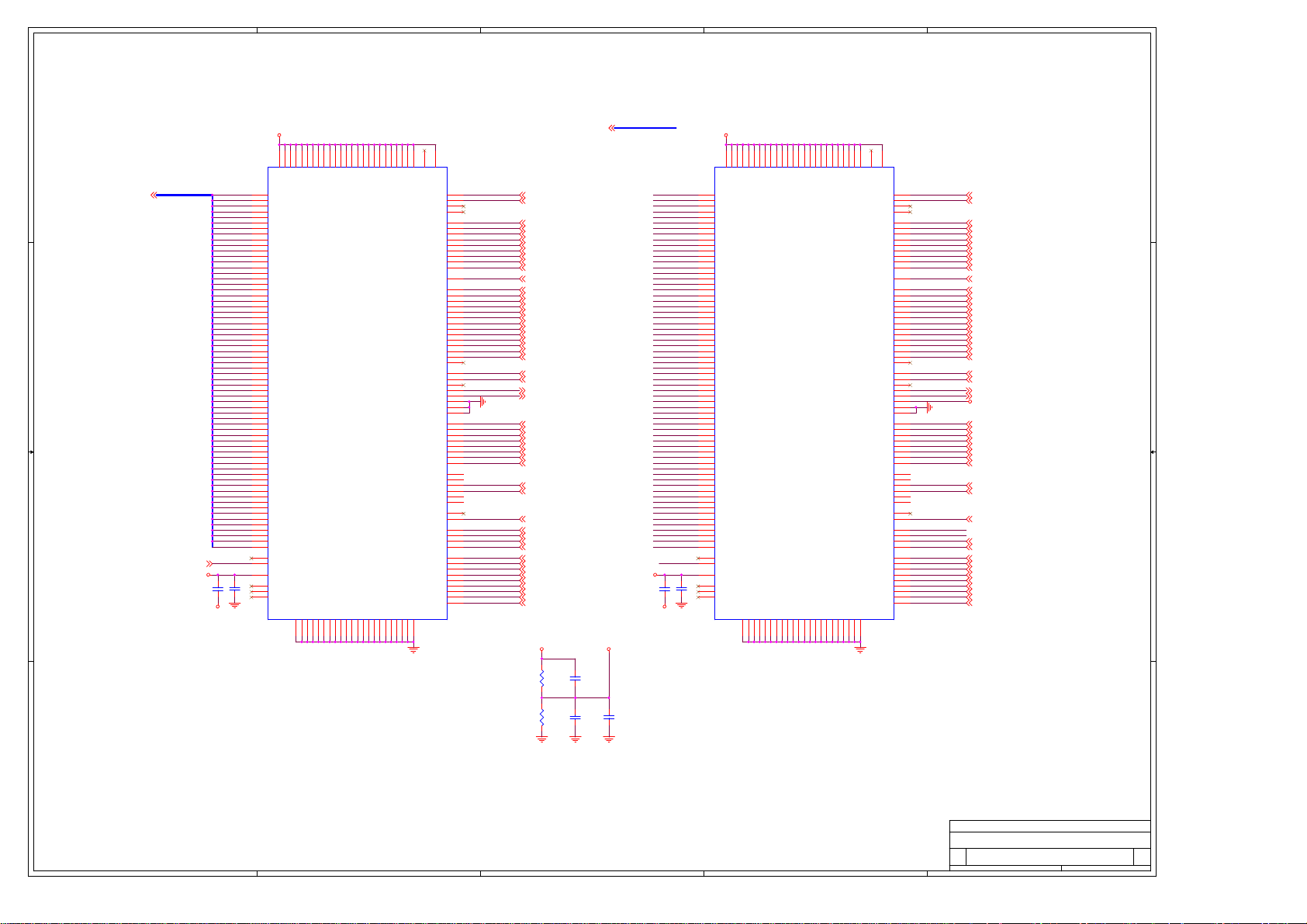

03 CPU0_K8 DDR & HT1

04 CPU0_K8 HDT & MISC

05 CPU0_K8 HT0 & HT2

06 CPU0_K8 POWER & GND

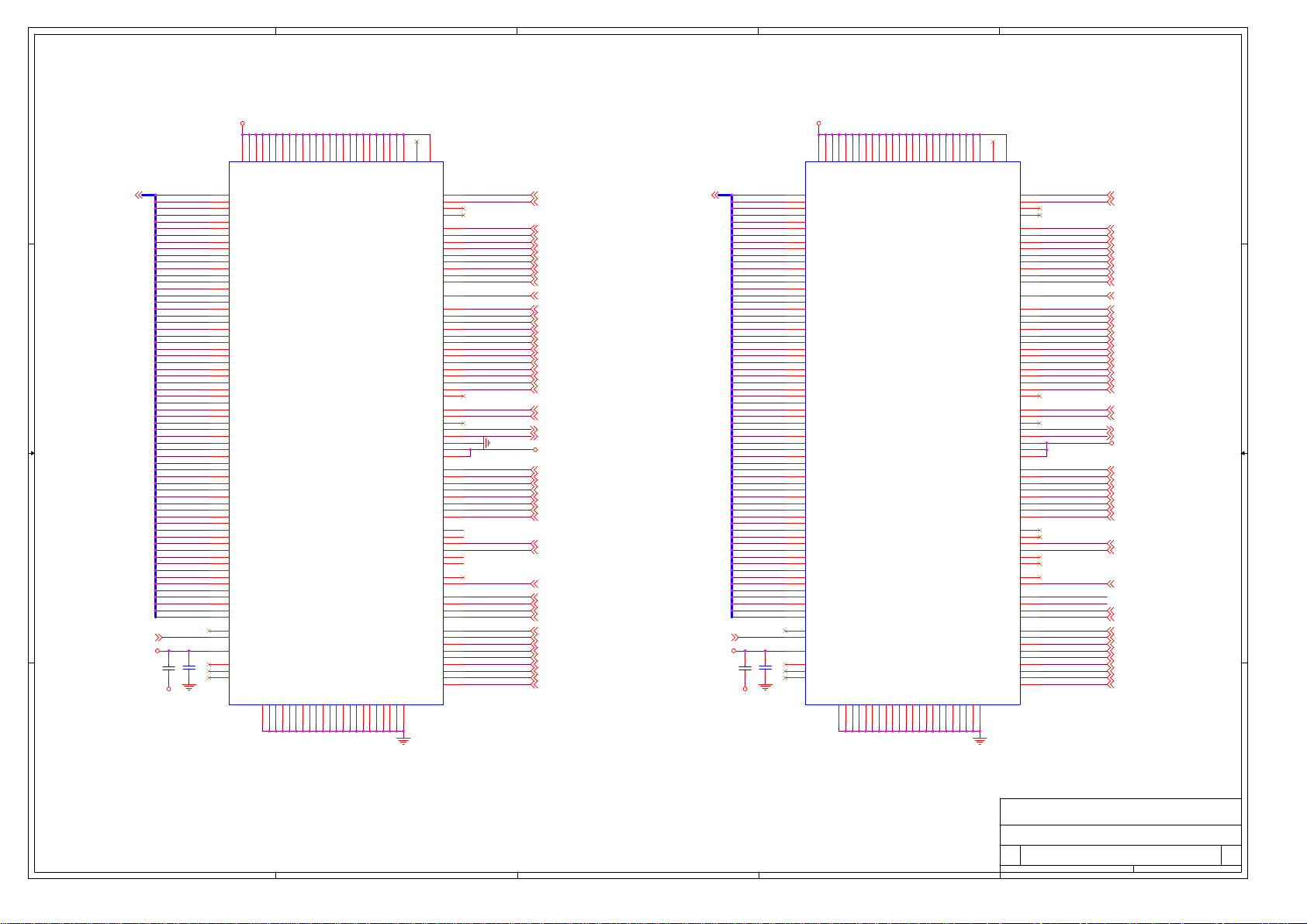

07 CPU0 Register DDR DIMM1 & 2

08 CPU0 Register DDR DIMM3 & 4

09 CPU0 DIMM5 & 6

10 CPU0 DIMM7 & 8

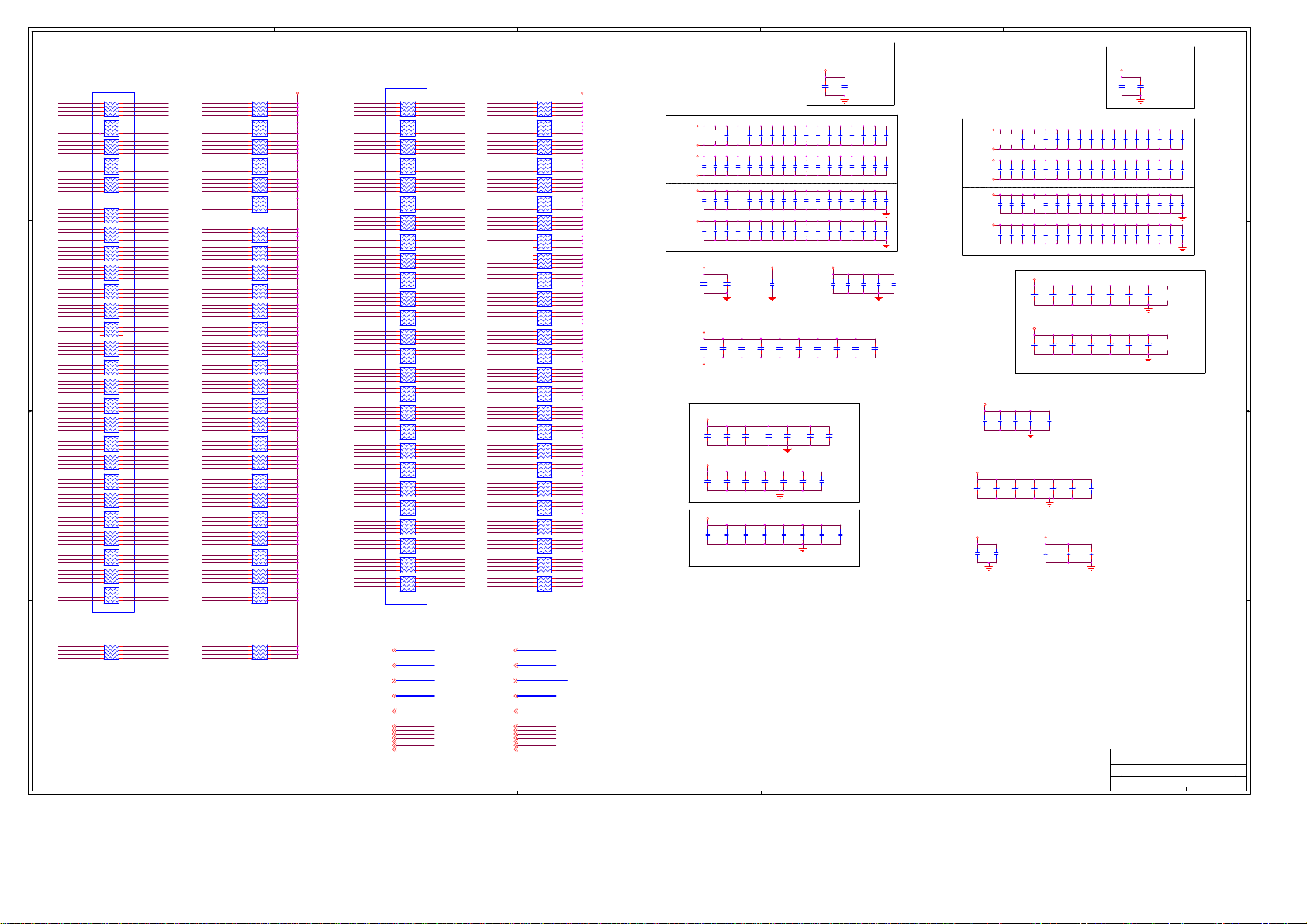

11 CPU0 DDR Terminations

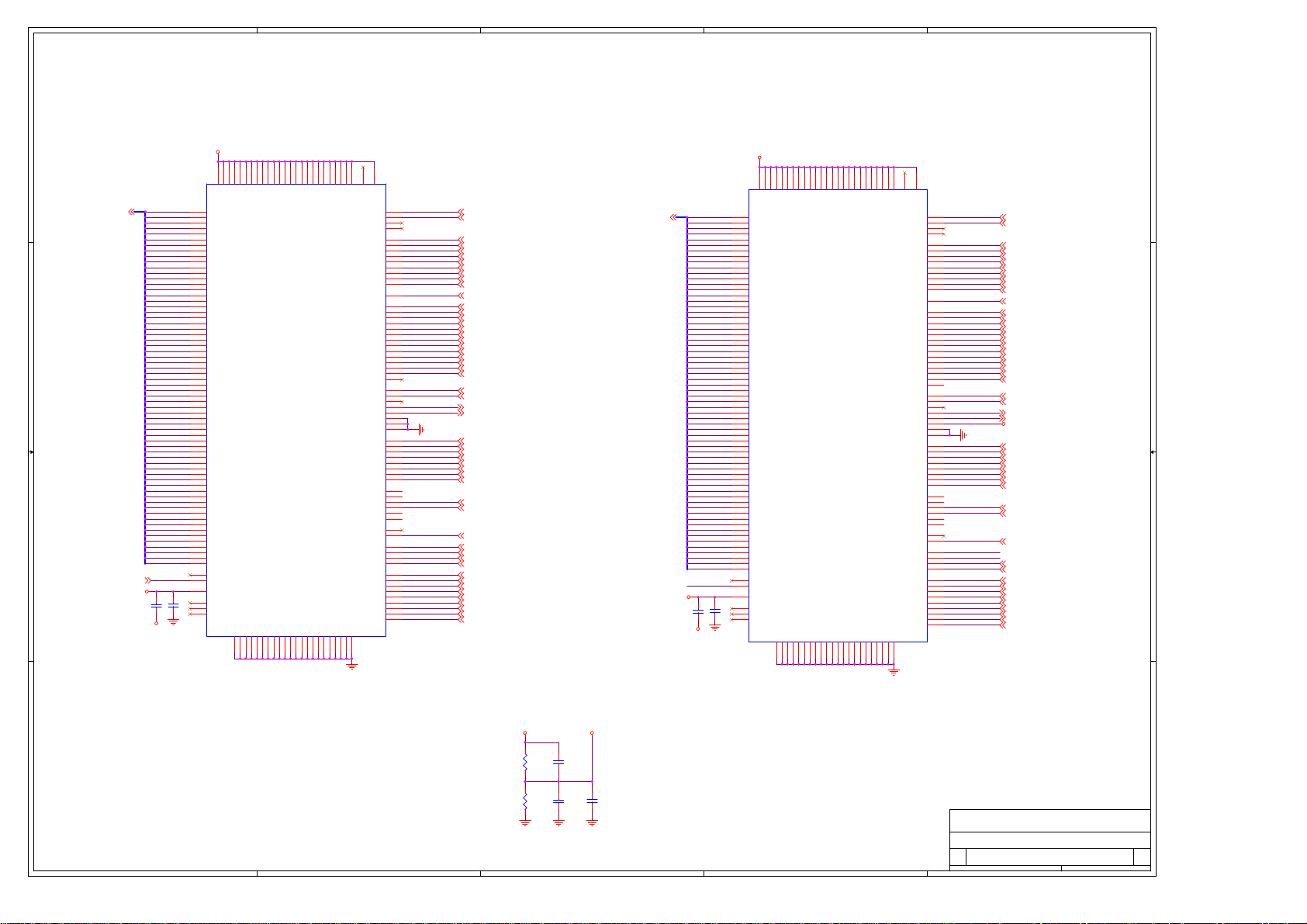

12 CPU1_K8 DDR & HT1

13 CPU1_K8 HDT & MISC

14 CPU1_K8 HT0 & HT2

15 CPU1_K8 POWER & GND

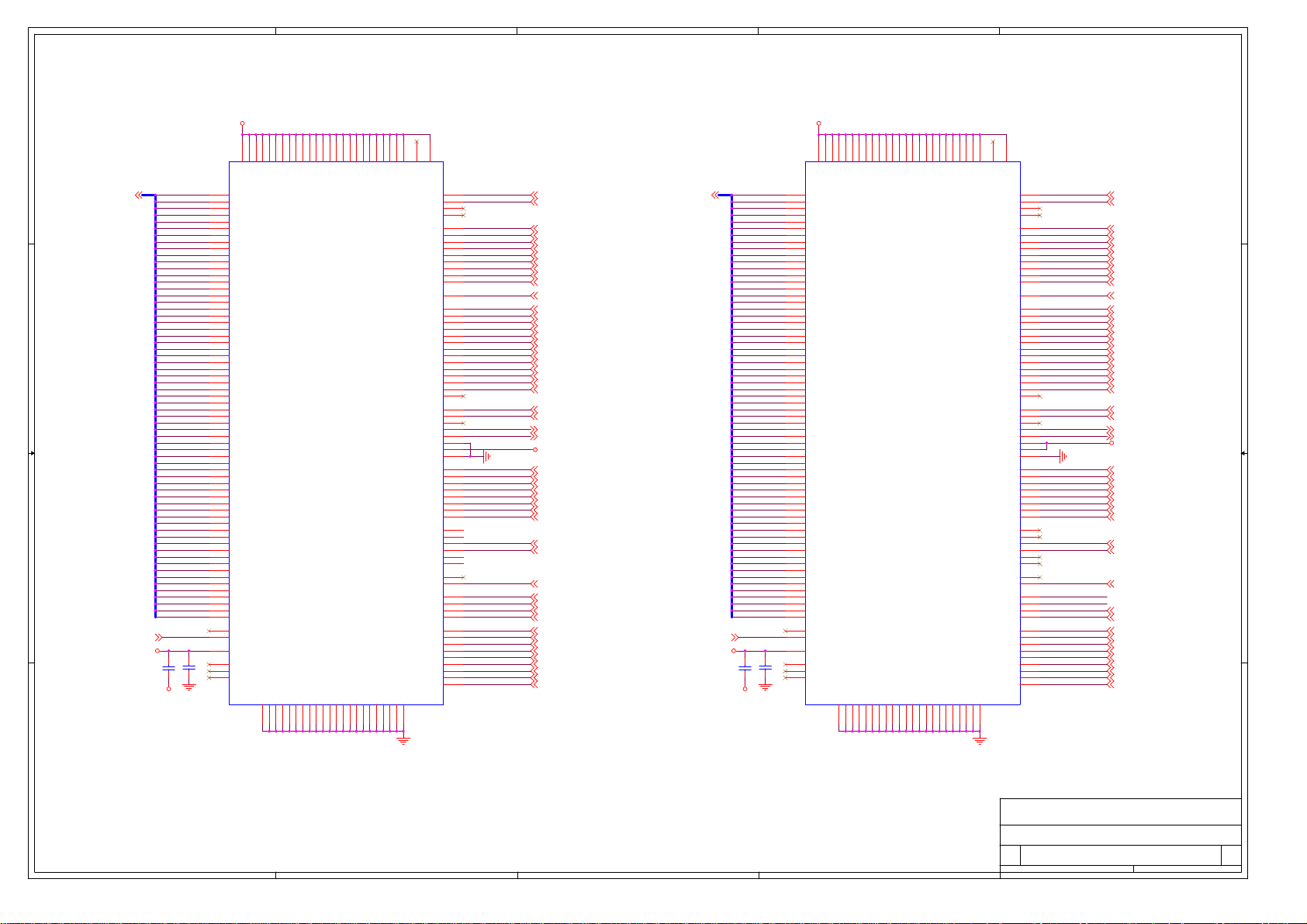

16 CPU1 DIMM9 & 10

17 CPU1 DIMM11 & 12

18 CPU1 DDR Terminations

19 Clock Synthesizer

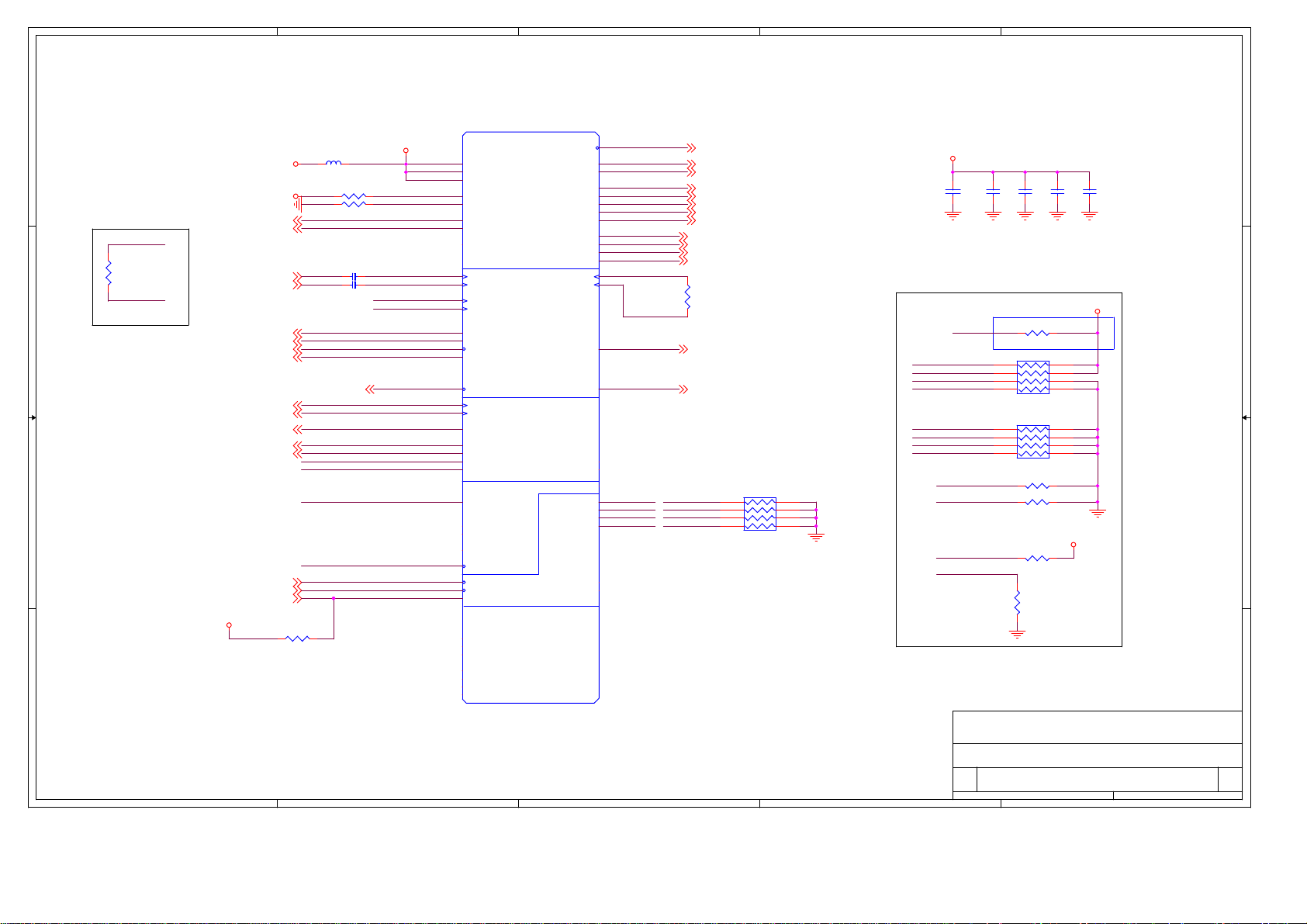

20 GOLEM HT

21 GOLEM PCI-X BRIDGE

A

22 GOLEM PCI-X SLOT A

23 GOLEM PCI-X BRIDGE B

24 GOLEM PCI-X SLOT B

25 GOLEM POWER and DECOUPLING

26 LAN BCM5704(I)

27 LAN BCM5704(II)

28 GbE CONN.

29 SCSI AIC-7901 (I)

30 SCSI AIC-7901 (II)

31 ZCR

32 THOR HT, LPC, MII, PCI, IDE

33 THOR AC97, USB, MISC

34 THOR POWER & STRIP

35 PCI32-1 & PCI32-2 SLOT

36 VGA ATI Rage XL

37 SATA Sil3114

38 LPC SIO & Flash ROM

39 USB Port & IDE Connector

40 COM, VGA, PRT, PS2 & Floppy

41 mBMC (PC87431)

42 BULK / Decopuling

43 H0 & H1 DDR POWER & HT POWER

44 GAL POWER SEQ.

45 Power & SSI Power Conn.

46 HW Monitor W83782D

47 Front Panel & FAN Control

48 K8 CPU H0 Core Power

49 K8 CPU H1 Core Power

50 HDT

51 Manul Part

52 Configuration Table

53 SMBUS diagram

POWER DEFINITIONM

VCORE_H0, VCORE_H1

B B

H0_VDDA_2.5

H1_VDDA_2.5

+1.2V

+2.5VDIMM_H0, +2.5VDIMM_H1

+1.25VTT_H0, +1.25VTT_H1

+2.5V

+1.8V

+5VDUAL

CPU Voltage

For H0 CPU

For H1 CPU

HT Voltage

DDR Dimm Voltage

DIMM Termination

Normal 2.5V (S0)

Normal 1.8V (S0)

Dual-Voltage S0 ---- +5V ; S3 ---- +5VSB

Dual-Voltage S0 & S3+3.3VDUAL

+2.5VDUAL

+1.8VDUAL

+2.5VDU

A A

+1.2VDU

SVCC18

VCC25_A For SCSI chip

+2.5VGA

VBAT

5

4

Dual-Voltage S0 & S3

Dual-Voltage S0 & S3

Dual-Voltage (For G-LAN) S0 & S3

Dual-Voltage (For G-LAN) S0 & S3

For SCSI chip

For ATI VGA Voltage

For Battrey Voltage

3

Title

<Title>

Size Document Number Rev

<Doc> <RevCode>

C

2

Date: Sheet of

1

1 53Monday, January 19, 2004

8

7

6

5

4

3

2

1

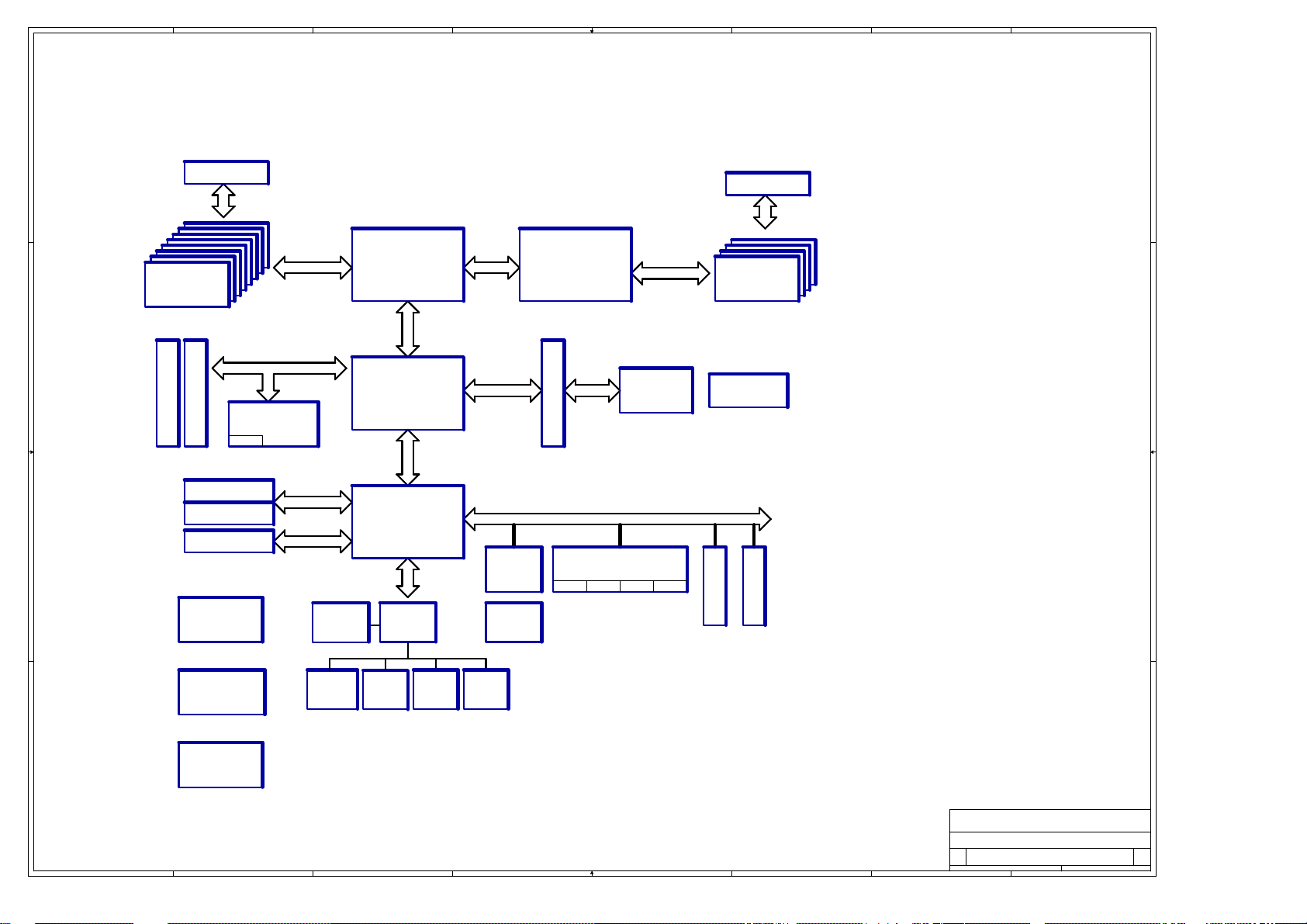

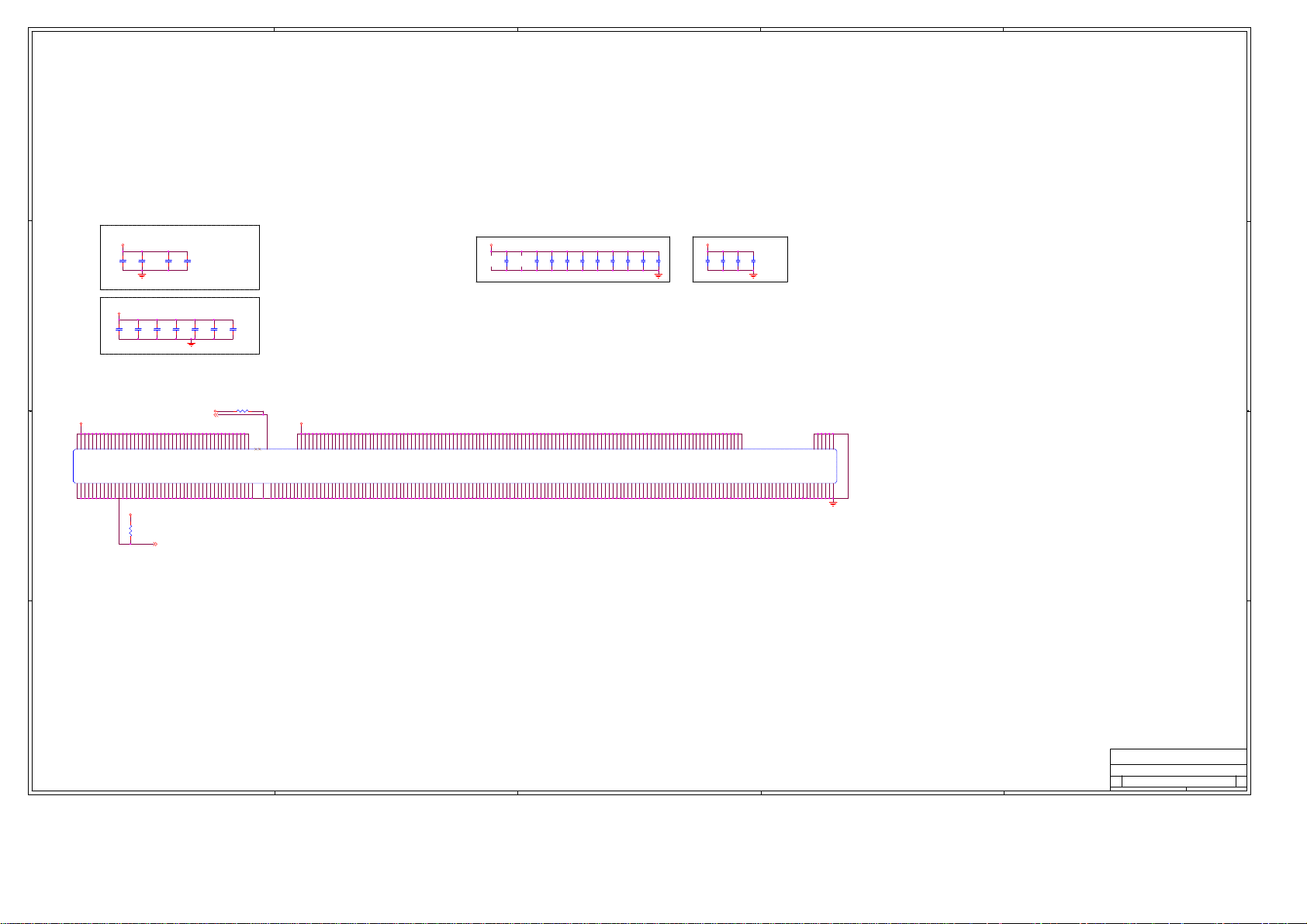

BLOCK DIAGRAM

D D

DDR Terminator

PAGE 9

16x16ncHyperTransport @ 1600MT/s

DDR Terminator

PAGE 15

Sledgehammer DP

( H1 )( H0 )

PAGE 10-13

128 bit

200 - 400 MHz

4 DDR DIMM

Registered

PAGE 14

8 DDR DIMM

Registered

PAGE 7,8

128 bit

200 - 266 MHz

Sledgehammer DP

LINK 0A

PAGE 3-6

LINK 0B

16x16 ncHyperTransport @ 1600MT/s

C C

PCI-X Slot

PCI-X Slot (ZCR)

PAGE 19 PAGE 19

64 bit

66/100/133 MHz

SCSI

AIC-7901X

CH-A

Golem

( 8131 )

Bridge A

PAGE 17,18,20,22

LINK 1

66/100/133 MHz

Bridge B

64 bit

PCI-X Slot

PAGE 21

64 bit

66/100/133 MHz

Broadcom GbE

BCM5704C

PAGE 23,24,25

CK408B Clk Gen.

PAGE 16

8x8 ncHyperTransport @ 400MT/s

IDE Primary

IDE Secondary

USB Port 1/2/3/4

B B

Front Panel

VRM

PAGE 42,43

PAGE 41

PAGE 33

PAGE 33

PAGE 33

EIDE ATA/133

USB 1.1

Flash ROM

Keyboard

& Mouse

PAGE 32

PAGE 34

Thor

( 8111 )

PAGE 26,27,28

W83627HF

LPC SIO

Floppy

PAGE 34

LPC

PAGE 32

Serial

(COM1,2)

PAGE 34

ATI RageXL

W83782D

HW Monitor

Parallel

(PRT)

PAGE 34

PCI Bus 32 bit / 33 MHz

VGA

PAGE 30

PAGE 28

CH-A CH-B CH-C CH-D

SATA

Sil3114

PAGE 31

PCI-32 Slot

PAGE 29

PCI-32 Slot

PAGE 29

A A

8

System Power

PAGE 39

7

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

BLOCK DIAGRAM

Size Document Number Rev

MS-9131

6

5

4

3

Date: Sheet of

2

2 53Monday, January 19, 2004

1

0AC

5

HT0 is for SH0 & Golem connection

+1.2V_VLDT

K10

VLDT_1(1)

J11

VLDT_1(2)

H10

C511

D D

H1L1_H0L1_CADOUT_H[15..0]12

H1L1_H0L1_CADOUT_L[15..0]12

H1L1_H0L1_CLKOUT_H112

C C

B B

A A

H1L1_H0L1_CLKOUT_L112

H1L1_H0L1_CLKOUT_H012

H1L1_H0L1_CLKOUT_L012

H1L1_H0L1_CTLOUT_H012

H1L1_H0L1_CTLOUT_L012

+1.2V_VLDT

0.22u/16V/X7R

+2.5VDIMM_H0 H0_VREF0_DDR

R106

100RST

R105

100RST

4.7u/35V-1206

H1L1_H0L1_CADOUT_H15

H1L1_H0L1_CADOUT_L15

H1L1_H0L1_CADOUT_H14

H1L1_H0L1_CADOUT_L14

H1L1_H0L1_CADOUT_H13

H1L1_H0L1_CADOUT_L13

H1L1_H0L1_CADOUT_H12

H1L1_H0L1_CADOUT_L12

H1L1_H0L1_CADOUT_H11

H1L1_H0L1_CADOUT_L11

H1L1_H0L1_CADOUT_H10

H1L1_H0L1_CADOUT_L10

H1L1_H0L1_CADOUT_H9

H1L1_H0L1_CADOUT_L9

H1L1_H0L1_CADOUT_H8

H1L1_H0L1_CADOUT_L8

H1L1_H0L1_CADOUT_H7

H1L1_H0L1_CADOUT_L7

H1L1_H0L1_CADOUT_H6

H1L1_H0L1_CADOUT_L6

H1L1_H0L1_CADOUT_H5

H1L1_H0L1_CADOUT_L5

H1L1_H0L1_CADOUT_H4

H1L1_H0L1_CADOUT_L4

H1L1_H0L1_CADOUT_H3

H1L1_H0L1_CADOUT_L3

H1L1_H0L1_CADOUT_H2

H1L1_H0L1_CADOUT_L2

H1L1_H0L1_CADOUT_H1

H1L1_H0L1_CADOUT_L1

H1L1_H0L1_CADOUT_H0

H1L1_H0L1_CADOUT_L0

TP3

TP5

C538

C470

C479

C505

1000P/50V/X7R

0.22u/16V/X7R

C331

0.1u

C324

0.1u

C325

1000P/50V/X7R

MEM_GPIO112,33

1000P/50V/X7R

FROM CPU TO DIMM

MEM_GPIO212,33

5

VLDT_1(3)

H8

VLDT_1(4)

K14

VLDT_1(5)

J15

VLDT_1(6)

K16

VLDT_1(7)

J16

VLDT_1(8)

J9

VLDT_1(9)

E14

L1_CADIN_H(15)

E13

L1_CADIN_L(15)

C15

L1_CADIN_H(14)

D15

L1_CADIN_L(14)

E16

L1_CADIN_H(13)

E15

L1_CADIN_L(13)

C17

L1_CADIN_H(12)

D17

L1_CADIN_L(12)

C19

L1_CADIN_H(11)

D19

L1_CADIN_L(11)

E20

L1_CADIN_H(10)

E19

L1_CADIN_L(10)

C21

L1_CADIN_H(9)

D21

L1_CADIN_L(9)

E22

L1_CADIN_H(8)

E21

L1_CADIN_L(8)

C14

L1_CADIN_H(7)

B14

L1_CADIN_L(7)

A16

L1_CADIN_H(6)

A15

L1_CADIN_L(6)

C16

L1_CADIN_H(5)

B16

L1_CADIN_L(5)

A18

L1_CADIN_H(4)

A17

L1_CADIN_L(4)

A20

L1_CADIN_H(3)

A19

L1_CADIN_L(3)

C20

L1_CADIN_H(2)

B20

L1_CADIN_L(2)

A22

L1_CADIN_H(1)

A21

L1_CADIN_L(1)

C22

L1_CADIN_H(0)

B22

L1_CADIN_L(0)

E18

L1_CLKIN_H(1)

E17

L1_CLKIN_L(1)

C18

L1_CLKIN_H(0)

B18

L1_CLKIN_L(0)

A14

L1_CTLIN_H(0)

A13

L1_CTLIN_L(0)

C13

L1_RSVD1

D13

L1_RSVD2

C390

1000P/50V/X7R

+2.5VDUAL

R139

X_1K

R147

100K

H0_MEMRESET1_L

+2.5VDUAL

R138

X_1K

R146

100K

C531

1000P/50V/X7R

U1E

SledgeHammer

C501

1000P/50V/X7R

U36

1

A

2

B

3 4

GND Y

SN74LVC1G08DCKR,SC-70

L1_CADOUT_H(15)

L1_CADOUT_L(15)

L1_CADOUT_H(14)

L1_CADOUT_L(14)

L1_CADOUT_H(13)

L1_CADOUT_L(13)

L1_CADOUT_H(12)

L1_CADOUT_L(12)

L1_CADOUT_H(11)

L1_CADOUT_L(11)

L1_CADOUT_H(10)

L1_CADOUT_L(10)

L1_CADOUT_H(9)

L1_CADOUT_L(9)

L1_CADOUT_H(8)

L1_CADOUT_L(8)

L1_CADOUT_H(7)

L1_CADOUT_L(7)

L1_CADOUT_H(6)

L1_CADOUT_L(6)

L1_CADOUT_H(5)

L1_CADOUT_L(5)

L1_CADOUT_H(4)

L1_CADOUT_L(4)

L1_CADOUT_H(3)

L1_CADOUT_L(3)

L1_CADOUT_H(2)

L1_CADOUT_L(2)

L1_CADOUT_H(1)

L1_CADOUT_L(1)

L1_CADOUT_H(0)

L1_CADOUT_L(0)

L1_CLKOUT_H(1)

L1_CLKOUT_L(1)

L1_CLKOUT_H(0)

L1_CLKOUT_L(0)

L1_CTLOUT_H(0)

L1_CTLOUT_L(0)

L1_RSVD3

L1_RSVD4

C546

4.7u/10V-0805

+2.5VDUAL

5

VCC

4

D11

C11

E9

E10

D9

C9

E7

E8

E5

E6

D5

C5

E3

E4

D3

C3

A11

A12

B10

C10

A9

A10

B8

C8

B6

C6

A5

A6

B4

C4

A3

A4

D7

C7

A7

A8

B12

C12

E11

E12

C604

100u/6.3V/X5R

4

1

2

3 4

H0L1_H1L1_CADOUT_H15

H0L1_H1L1_CADOUT_L15

H0L1_H1L1_CADOUT_H14

H0L1_H1L1_CADOUT_L14

H0L1_H1L1_CADOUT_H13

H0L1_H1L1_CADOUT_L13

H0L1_H1L1_CADOUT_H12

H0L1_H1L1_CADOUT_L12

H0L1_H1L1_CADOUT_H11

H0L1_H1L1_CADOUT_L11

H0L1_H1L1_CADOUT_H10

H0L1_H1L1_CADOUT_L10

H0L1_H1L1_CADOUT_H9

H0L1_H1L1_CADOUT_L9

H0L1_H1L1_CADOUT_H8

H0L1_H1L1_CADOUT_L8

H0L1_H1L1_CADOUT_H7

H0L1_H1L1_CADOUT_L7

H0L1_H1L1_CADOUT_H6

H0L1_H1L1_CADOUT_L6

H0L1_H1L1_CADOUT_H5

H0L1_H1L1_CADOUT_L5

H0L1_H1L1_CADOUT_H4

H0L1_H1L1_CADOUT_L4

H0L1_H1L1_CADOUT_H3

H0L1_H1L1_CADOUT_L3

H0L1_H1L1_CADOUT_H2

H0L1_H1L1_CADOUT_L2

H0L1_H1L1_CADOUT_H1

H0L1_H1L1_CADOUT_L1

H0L1_H1L1_CADOUT_H0

H0L1_H1L1_CADOUT_L0

TP7

TP6

+2.5VDUAL

U32

5

A

VCC

B

GND Y

SN74LVC1G32DBVR

+1.25VTT_H0

C360

0.1u

modified on 1/30

H0L1_H1L1_CADOUT_H[15..0] 12

H0L1_H1L1_CADOUT_L[15..0] 12

H0L1_H1L1_CLKOUT_H1 12

H0L1_H1L1_CLKOUT_L1 12

H0L1_H1L1_CLKOUT_H0 12

H0L1_H1L1_CLKOUT_L0 12

H0L1_H1L1_CTLOUT_H0 12

H0L1_H1L1_CTLOUT_L0 12

C293

C353

0.1u

0.1u

H0_MEMRESET_L 7,8,9,10

3

H0_VTT_SENSE43

+2.5VDIMM_H0

H0_VREF0_DDR

H0_VREF0_DDR

H0_MD[127..64]11

C349

0.1u

3

H0_MDQS3511

H0_MDQS3411

H0_MDQS3311

H0_MDQS3211

H0_MDQS3111

H0_MDQS3011

H0_MDQS2911

H0_MDQS2811

H0_MDQS2711

H0_MDQS2611

H0_MDQS2511

H0_MDQS2411

H0_MDQS2311

H0_MDQS2211

H0_MDQS2111

H0_MDQS2011

H0_MDQS1911

H0_MDQS1711

H0_MDQS1611

H0_MDQS1511

H0_MDQS1411

H0_MDQS1311

H0_MDQS1211

H0_MDQS1111

H0_MDQS1011

H0_MDQS911

H0_MDQS811

H0_MDQS711

H0_MDQS611

H0_MDQS511

H0_MDQS411

H0_MDQS311

H0_MDQS211

H0_MDQS111

H0_MDQS011

+1.25VTT_H0

AC19

VTT1

AE19

VTT2

J19

AE18

AC18

AF18

AF19

AF17

AE16

AF22

AG24

AH25

AG26

AH27

AF23

AH24

AF25

AG27

AF26

AF28

AE29

AH29

AE27

AD26

AD27

AC26

AA26

AA28

AD28

AC27

AB29

AA27

AG25

AF27

AB27

AF24

AG28

AC28

AD29

AA31

AE31

H19

F20

G19

F21

F22

AJ26

AJ29

Y27

Y28

V28

U26

Y26

W27

V27

U27

P28

N29

M26

L28

P27

P26

M27

L27

K29

K27

H28

G29

L26

H27

H26

F27

F26

D29

D27

G27

F28

E27

C27

C26

E25

D24

F23

E26

F25

E24

G23

R27

W29

N27

E29

F24

R28

V26

M28

E28

D25

U31

AJ25

AJ30

M30

H30

C30

B25

T31

AL25

AL29

Y29

M29

H29

C29

C25

J28

J27

J26

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT_SENSE

MEMZN

MEMZP

MEMVREF0

MEMVREF1

MEMDATA(127)

MEMDATA(126)

MEMDATA(125)

MEMDATA(124)

MEMDATA(123)

MEMDATA(122)

MEMDATA(121)

MEMDATA(120)

MEMDATA(119)

MEMDATA(118)

MEMDATA(117)

MEMDATA(116)

MEMDATA(115)

MEMDATA(114)

MEMDATA(113)

MEMDATA(112)

MEMDATA(111)

MEMDATA(110)

MEMDATA(109)

MEMDATA(108)

MEMDATA(107)

MEMDATA(106)

MEMDATA(105)

MEMDATA(104)

MEMDATA(103)

MEMDATA(102)

MEMDATA(101)

MEMDATA(100)

MEMDATA(99)

MEMDATA(98)

MEMDATA(97)

MEMDATA(96)

MEMDATA(95)

MEMDATA(94)

MEMDATA(93)

MEMDATA(92)

MEMDATA(91)

MEMDATA(90)

MEMDATA(89)

MEMDATA(88)

MEMDATA(87)

MEMDATA(86)

MEMDATA(85)

MEMDATA(84)

MEMDATA(83)

MEMDATA(82)

MEMDATA(81)

MEMDATA(80)

MEMDATA(79)

MEMDATA(78)

MEMDATA(77)

MEMDATA(76)

MEMDATA(75)

MEMDATA(74)

MEMDATA(73)

MEMDATA(72)

MEMDATA(71)

MEMDATA(70)

MEMDATA(69)

MEMDATA(68)

MEMDATA(67)

MEMDATA(66)

MEMDATA(65)

MEMDATA(64)

MEMDQS(35)

MEMDQS(34)

MEMDQS(33)

MEMDQS(32)

MEMDQS(31)

MEMDQS(30)

MEMDQS(29)

MEMDQS(28)

MEMDQS(27)

MEMDQS(26)

MEMDQS(25)

MEMDQS(24)

MEMDQS(23)

MEMDQS(22)

MEMDQS(21)

MEMDQS(20)

MEMDQS(19)

MEMDQS(18)

MEMDQS(17)

MEMDQS(16)

MEMDQS(15)

MEMDQS(14)

MEMDQS(13)

MEMDQS(12)

MEMDQS(11)

MEMDQS(10)

MEMDQS(9)

MEMDQS(8)

MEMDQS(7)

MEMDQS(6)

MEMDQS(5)

MEMDQS(4)

MEMDQS(3)

MEMDQS(2)

MEMDQS(1)

MEMDQS(0)

+1.25VTT_H0

R97

X_51

R119 42.2RST

R118 42.2RST

H0_MD127

H0_MD126

H0_MD125

H0_MD124

H0_MD123

H0_MD122

H0_MD121

H0_MD120

H0_MD119

H0_MD118

H0_MD117

H0_MD116

H0_MD115

H0_MD114

H0_MD113

H0_MD112

H0_MD111

H0_MD110

H0_MD109

H0_MD108

H0_MD107

H0_MD105

H0_MD104

H0_MD103

H0_MD102

H0_MD101

H0_MD100

H0_MD99

H0_MD98

H0_MD97

H0_MD96

H0_MD95

H0_MD94

H0_MD93

H0_MD92

H0_MD91

H0_MD90

H0_MD89

H0_MD88

H0_MD87

H0_MD86

H0_MD85

H0_MD84

H0_MD83

H0_MD82

H0_MD81 H0_MD17

H0_MD80

H0_MD79

H0_MD78

H0_MD77

H0_MD76

H0_MD75

H0_MD74

H0_MD73

H0_MD72

H0_MD71

H0_MD70

H0_MD69

H0_MD68

H0_MD67

H0_MD66

H0_MD65

H0_MD64

H0_MDQS35

H0_MDQS34

H0_MDQS33

H0_MDQS32

H0_MDQS31

H0_MDQS30

H0_MDQS29

H0_MDQS28

H0_MDQS27

H0_MDQS26

H0_MDQS25

H0_MDQS24

H0_MDQS23

H0_MDQS22

H0_MDQS21

H0_MDQS20

H0_MDQS19

H0_MDQS18

H0_MDQS17

H0_MDQS16

H0_MDQS15

H0_MDQS14

H0_MDQS13

H0_MDQS12

H0_MDQS11

H0_MDQS10

H0_MDQS9

H0_MDQS8

H0_MDQS7

H0_MDQS6

H0_MDQS5

H0_MDQS4

H0_MDQS3

H0_MDQS2

H0_MDQS1

H0_MDQS0

U1B

MEMCLK_UP_H(3)

MEMCLK_UP_L(3)

MEMCLK_UP_H(2)

MEMCLK_UP_L(2)

MEMCLK_UP_H(1)

MEMCLK_UP_L(1)

MEMCLK_UP_H(0)

MEMCLK_UP_L(0)

MEMCLK_LO_H(3)

MEMCLK_LO_L(3)

MEMCLK_LO_H(2)

MEMCLK_LO_L(2)

MEMCLK_LO_H(1)

MEMCLK_LO_L(1)

MEMCLK_LO_H(0)

MEMCLK_LO_L(0)

MEMCHECK(15)

MEMCHECK(14)

MEMCHECK(13)

MEMCHECK(12)

MEMCHECK(11)

MEMCHECK(10)

SledgeHammer

2

MEMCKE_UP

MEMCKE_LO

RSVD_MA(15)

RSVD_MA(14)

MEMADD(13)

MEMADD(12)

MEMADD(11)

MEMADD(10)

MEMADD(9)

MEMADD(8)

MEMADD(7)

MEMADD(6)

MEMADD(5)

MEMADD(4)

MEMADD(3)

MEMADD(2)

MEMADD(1)

MEMADD(0)

MEMDATA(63)

MEMDATA(62)

MEMDATA(61)

MEMDATA(60)

MEMDATA(59)

MEMDATA(58)

MEMDATA(57)

MEMDATA(56)

MEMDATA(55)

MEMDATA(54)

MEMDATA(53)

MEMDATA(52)

MEMDATA(51)

MEMDATA(50)

MEMDATA(49)

MEMDATA(48)

MEMDATA(47)

MEMDATA(46)

MEMDATA(45)

MEMDATA(44)

MEMDATA(43)

MEMDATA(42)

MEMDATA(41)

MEMDATA(40)

MEMDATA(39)

MEMDATA(38)

MEMDATA(37)

MEMDATA(36)

MEMDATA(35)

MEMDATA(34)

MEMDATA(33)

MEMDATA(32)

MEMDATA(31)

MEMDATA(30)

MEMDATA(29)

MEMDATA(28)

MEMDATA(27)

MEMDATA(26)

MEMDATA(25)

MEMDATA(24)

MEMDATA(23)

MEMDATA(22)

MEMDATA(21)

MEMDATA(20)

MEMDATA(19)

MEMDATA(18)

MEMDATA(17)

MEMDATA(16)

MEMDATA(15)

MEMDATA(14)

MEMDATA(13)

MEMDATA(12)

MEMDATA(11)

MEMDATA(10)

MEMDATA(9)

MEMDATA(8)

MEMDATA(7)

MEMDATA(6)

MEMDATA(5)

MEMDATA(4)

MEMDATA(3)

MEMDATA(2)

MEMDATA(1)

MEMDATA(0)

MEMRESET_L

MEMBANK(1)

MEMBANK(0)

MEMRAS_L

MEMCAS_L

MEMWE_L

MEMCHECK(9)

MEMCHECK(8)

MEMCHECK(7)

MEMCHECK(6)

MEMCHECK(5)

MEMCHECK(4)

MEMCHECK(3)

MEMCHECK(2)

MEMCHECK(1)

MEMCHECK(0)

MEMCS_L(7)

MEMCS_L(6)

MEMCS_L(5)

MEMCS_L(4)

MEMCS_L(3)

MEMCS_L(2)

MEMCS_L(1)

MEMCS_L(0)

2

H0_MEMCLK_H6

G20

H0_MEMCLK_L6

G21

H0_MEMCLK_H4

AE21

H0_MEMCLK_L4

AE20

H0_MEMCLK_H2

L24

H0_MEMCLK_L2

L25

H0_MEMCLK_H0

R23

H0_MEMCLK_L0

T23

H0_MEMCLK_H7

H23

H0_MEMCLK_L7

J23

H0_MEMCLK_H5

AD21

H0_MEMCLK_L5

AD20

H0_MEMCLK_H3

Y23

H0_MEMCLK_L3

AA23

H0_MEMCLK_H1

U25

H0_MEMCLK_L1

U24

H0_MCKEUP

H24

H0_MCKELO

H25

V23

M23

H0_MAA13

AE23

H0_MAA12

J24

H0_MAA11

J25

H0_MAA10

V24

H0_MAA9

K23

H0_MAA8

L23

H0_MAA7

K25

H0_MAA6

M25

H0_MAA5

M24

H0_MAA4

N25

H0_MAA3

N23

H0_MAA2

P23

H0_MAA1

T25

H0_MAA0

V25

H0_MD63

AJ24

H0_MD62

AK25

H0_MD61

AK27

H0_MD60

AJ27

H0_MD59

AL24

H0_MD58

AK24

H0_MD57

AL26

H0_MD56

AL27

H0_MD55

AJ28

H0_MD54

AK30

H0_MD53

AJ31

H0_MD52

AG29

H0_MD51

AL28

H0_MD50

AK28

H0_MD49

AH31

H0_MD48

AG30

H0_MD47

AG31

H0_MD46

AF30

H0_MD45

AD31

H0_MD44

AC30

H0_MD43

AF29

H0_MD42H0_MD106

AF31

H0_MD41

AD30

H0_MD40

AC29

H0_MD39

AB31

H0_MD38

AA29

H0_MD37

Y31

H0_MD36

W31

H0_MD35

AC31

H0_MD34

AA30

H0_MD33

Y30

H0_MD32

V29

H0_MD31

P31

H0_MD30

M31

H0_MD29

L30

H0_MD28

L29

H0_MD27

P29

H0_MD26

N31

H0_MD25

L31

H0_MD24

K31

H0_MD23

J30

H0_MD22

J29

H0_MD21

G31

H0_MD20

F29

H0_MD19

J31

H0_MD18

H31

F31

H0_MD16

F30

H0_MD15

D31

H0_MD14

C31

H0_MD13

B30

H0_MD12

C28

H0_MD11

E31

H0_MD10

E30

H0_MD9

A29

H0_MD8

B28

H0_MD7

B27

H0_MD6

A26

H0_MD5

C24

H0_MD4

A24

H0_MD3

A28

H0_MD2

A27

H0_MD1

A25

H0_MD0

B24

H0_MEMRESET1_L

G25

W25

W23

H0_-MSRASA

Y25

H0_-MSCASA

AA25

Y24

H0_MEMCHECK15

U28

H0_MEMCHECK14

T29

H0_MEMCHECK13

P24

H0_MEMCHECK12

P25

H0_MEMCHECK11

T27

H0_MEMCHECK10

R26

H0_MEMCHECK9

R25

H0_MEMCHECK8

R24

H0_MEMCHECK7

V30

H0_MEMCHECK6

U29

H0_MEMCHECK5

R30

H0_MEMCHECK4

P30

H0_MEMCHECK3

V31

H0_MEMCHECK2

U30

H0_MEMCHECK1

R29

H0_MEMCHECK0

R31

H0_-MCS7

AD23

H0_-MCS6

AE25

H0_-MCS5

AD24

H0_-MCS4

AD25

H0_-MCS3

AC24

H0_-MCS2

AC25

H0_-MCS1

AB25

H0_-MCS0

AA24

H0_MEMCLK_H6 10

H0_MEMCLK_L6 10

H0_MEMCLK_H4 9

H0_MEMCLK_L4 9

H0_MEMCLK_H2 8

H0_MEMCLK_L2 8

H0_MEMCLK_H0 7

H0_MEMCLK_L0 7

H0_MEMCLK_H7 10

H0_MEMCLK_L7 10

H0_MEMCLK_H5 9

H0_MEMCLK_L5 9

H0_MEMCLK_H3 8

H0_MEMCLK_L3 8

H0_MEMCLK_H1 7

H0_MEMCLK_L1 7

H0_MCKEUP 11

H0_MCKELO 11

H0_MAA13 11

H0_MAA12 11

H0_MAA11 11

H0_MAA10 11

H0_MAA9 11

H0_MAA8 11

H0_MAA7 11

H0_MAA6 11

H0_MAA5 11

H0_MAA4 11

H0_MAA3 11

H0_MAA2 11

H0_MAA1 11

H0_MAA0 11

H0_MD[63..0] 11

H0_MEMBAKA1 11

H0_MEMBAKA0 11

H0_-MSRASA 11

H0_-MSCASA 11

H0_-MSWEA 11

H0_MEMCHECK15 11

H0_MEMCHECK14 11

H0_MEMCHECK13 11

H0_MEMCHECK12 11

H0_MEMCHECK11 11

H0_MEMCHECK10 11

H0_MEMCHECK9 11

H0_MEMCHECK8 11H0_MDQS1811

H0_MEMCHECK7 11

H0_MEMCHECK6 11

H0_MEMCHECK5 11

H0_MEMCHECK4 11

H0_MEMCHECK3 11

H0_MEMCHECK2 11

H0_MEMCHECK1 11

H0_MEMCHECK0 11

H0_-MCS7 11

H0_-MCS6 11

H0_-MCS5 11

H0_-MCS4 11

H0_-MCS3 11

H0_-MCS2 11

H0_-MCS1 11

H0_-MCS0 11

1

H0_MEMCLK_H7

H0_MEMCLK_L7

H0_MEMCLK_H6

H0_MEMCLK_L6

H0_MEMCLK_H5

H0_MEMCLK_L5

H0_MEMCLK_H4

H0_MEMCLK_L4

H0_MEMCLK_H3

H0_MEMCLK_L3

H0_MEMCLK_H2

H0_MEMCLK_L2

H0_MEMCLK_H1

H0_MEMCLK_L1

H0_MEMCLK_H0

H0_MEMCLK_L0

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

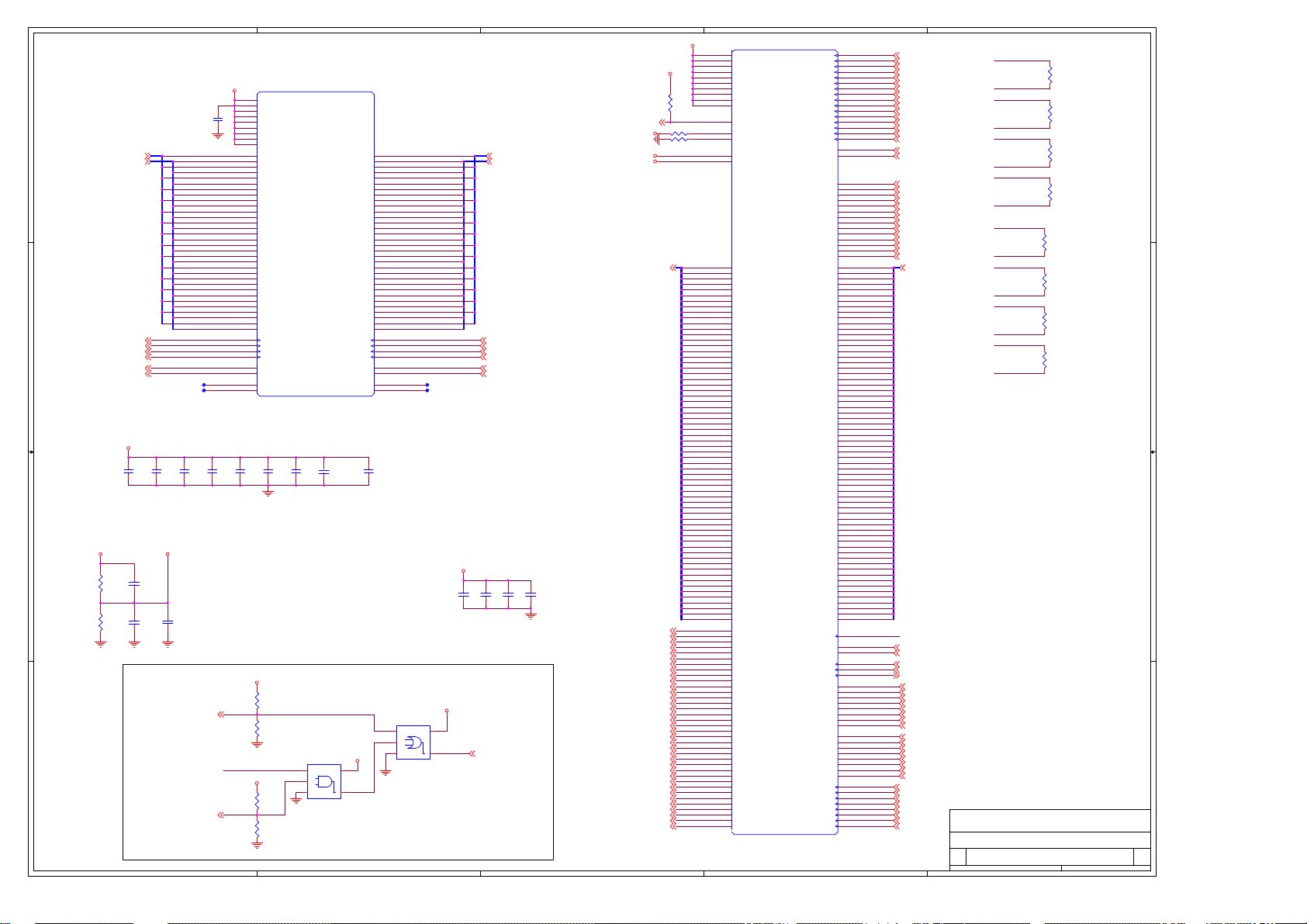

CPU0_K8 DDR & HT

Size Document Number Rev

MS-9131

Date: Sheet of

R92

120RST

R95

120RST

R93

120RST

R94

120RST

R580

120RST

R581

120RST

R585

120RST

R586

120RST

1

3 53Monday, January 19, 2004

0AC

5

4

3

2

1

RSVD_SMBUSC

RSVD_SMBUSD

SledgeHammer

U1C

THERMTRIP_L

THERMDA

THERMDC

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

BP(3)

BP(2)

BP(1)

BP(0)

FBCLKOUT_H

FBCLKOUT_L

DBRDY

SCANOUT_H

SCANOUT_L

TSTOUT

ANALOG3

ANALOG2

ANALOG1

ANALOG0

TDO

AE15

AJ1

AH1

G9

F9

G10

H11

G11

H13

G6

F7

H12

H0_FBCLKOUT_H

G18

H18

H0_FBCLKOUT_L

AE8

H0_DBRDYH0_DBREQ_L

G8

V5

U5

H7

U1_T7

T7

U1_W6

W6

U1_R6

R6

U1_U6

U6

AF9

AE9

THERMTRIP_CPU0_L 33

THERMDA_CPU1 38

VTIN_GND 13,38

H0_VID4 38,48

H0_VID3 38,48

H0_VID2 38,48

H0_VID1 38,48

H0_VID0 38,48

H0_BP3 50

H0_BP2 50

H0_BP1 50

H0_BP0 50

This termination

resistor should

R112

be placed as

80.6RST

close to

Processor as

possible.

H0_TDO 50

modified on 1/30

H0_DBRDY 50

U1_R6

U1_U6

U1_T7

U1_W6

510_8P4R

Routed differentially.

LAYOUT:

Route FBCLKOUT_H/L differentially

with 20/5/5/5/20 for 1.5" to escape the BGA.

RN119

12

34

56

78

H0_VDDA_2.5

C548

4.7u/6.3V/X5R-0805

STRAPPINGS

H0_NC_G14

H0_NC_AE14

H0_NC_AF13

H0_SCANEN

H0_SCANCLK1

H0_BP0

H0_SSENA

H0_SSENB

H0_SCANCLK2

H0_NC_H14

H0_BP1

H0_NC_T4

H0_NC_T3

C545

C527

3300p/50V/X7R

1000P/50V/X7R

R117 820

modified on 3/12

RN118

680_8P4R

RN124

680_8P4R

R116 820

R169 680

+1.2V_VLDT

R170 49.9RST

R168

49.9RST

C542

0.22u/16V

+2.5VDIMM_H0

78

56

34

12

12

34

56

78

C547

100u/6.3V/X5R

LAYOUT:

Route VDDA trace approx. 50 mils wide

(use 2x25 mil traces to exit ball) and

D D

C C

B B

A A

500 mils long.

Routed differentially

with a 20/5/5/5/20.

VERY CLOSE TO CPU

CLKIN0_H

R604

169RST

CLKIN0_L

+1.2V_VLDT

H0_COREFB_H48

H0_COREFB_L48

CPUCLK0_H19

CPUCLK0_L19

H0_DBREQ_L50

H0_SCANCLK150

H0_SCANCLK250

H0_SCANEN50

H0_SSENA50

H0_SSENB50

RESET_CPU0_L13,32

HTSTOP_CPU0_L32

+2.5VDIMM_H0

+2.5VPLL

TMS13,50

TCK13,50

TRST_L13,50

H0_TDI50

PG_CPU044

R135 82

FB9 180nH/1210

R172 43.2RST

R173 43.2RST

C387

C391

H0_NC_T3

H0_NC_T4

H0_NC_AF13

H0_NC_AE14

H0_VDDA_2.5

3900P/50V/X7R

3900P/50V/X7R

H0_NC_G14

H0_NC_H14

CLKIN0_H

CLKIN0_L

G16

H16

G14

H14

AE6

AE7

AD7

AF7

AE10

AE11

AF11

AE13

AE12

AF13

AF15

AE14

G12

F12

AG1

AH2

AJ2

AA6

AC6

C1

D2

C2

E1

D1

L7

L6

K7

J7

T3

T4

L8

K8

J6

H9

N6

VDDA1

VDDA2

VDDA3

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORESENSE_H

CLKIN_H

CLKIN_L

BYPASSCLK_H

BYPASSCLK_L

TMS

TCK

TRST_L

TDI

DBREQ_L

SCANCLK1

SCANCLK2

SCANEN

SCANSHIFTEN

SCANSHIFTENB

SCANIN_H

SCANIN_L

SINGLECHAIN

PLLCHRZ_H

PLLCHRZ_L

DCLKTWO

BURNIN_L

RESET_L

LDTSTOP_L

PWROK

FREE7

FREE11

FREE15

FREE12

FREE21

FREE1

FREE3

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

CPU0_K8 HDT & MISC

Size Document Number Rev

MS-9131

5

4

3

2

Date: Sheet of

4 53Monday, January 19, 2004

1

0AB

5

4

3

2

1

+1.2V_VLDT

N7

VLDT_0(1)

R7

VLDT_0(2)

U7

AA7

W7

M8

P8

V8

Y8

R5

T5

P3

P4

N5

P5

M3

M4

K3

K4

J5

K5

H3

H4

G5

H5

R3

R2

N1

P1

N3

N2

L1

M1

J1

K1

J3

J2

G1

H1

G3

G2

L5

M5

L3

L2

R1

T1

VLDT_0(3)

VLDT_0(4)

VLDT_0(5)

VLDT_0(6)

VLDT_0(7)

VLDT_0(8)

VLDT_0(9)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

C605

D D

G0L0_H0L0_CADOUT_L[15..0]20

C C

G0L0_H0L0_CLKOUT_H120

G0L0_H0L0_CLKOUT_L120

G0L0_H0L0_CLKOUT_H020

G0L0_H0L0_CLKOUT_L020

G0L0_H0L0_CTLOUT_H020 H0L0_G0L0_CTLOUT_H0 20

G0L0_H0L0_CTLOUT_L020

B B

100u/6.3V/X5R

G0L0_H0L0_CADOUT_H15

G0L0_H0L0_CADOUT_L15

G0L0_H0L0_CADOUT_H14

G0L0_H0L0_CADOUT_L14

G0L0_H0L0_CADOUT_H13

G0L0_H0L0_CADOUT_L13

G0L0_H0L0_CADOUT_H12

G0L0_H0L0_CADOUT_L12

G0L0_H0L0_CADOUT_H11

G0L0_H0L0_CADOUT_L11

G0L0_H0L0_CADOUT_H10

G0L0_H0L0_CADOUT_L10

G0L0_H0L0_CADOUT_H9

G0L0_H0L0_CADOUT_L9

G0L0_H0L0_CADOUT_H8

G0L0_H0L0_CADOUT_L8

G0L0_H0L0_CADOUT_H7

G0L0_H0L0_CADOUT_L7

G0L0_H0L0_CADOUT_H6

G0L0_H0L0_CADOUT_L6

G0L0_H0L0_CADOUT_H5

G0L0_H0L0_CADOUT_L5

G0L0_H0L0_CADOUT_H4

G0L0_H0L0_CADOUT_L4

G0L0_H0L0_CADOUT_H3

G0L0_H0L0_CADOUT_L3

G0L0_H0L0_CADOUT_H2

G0L0_H0L0_CADOUT_L2

G0L0_H0L0_CADOUT_H1

G0L0_H0L0_CADOUT_L1

G0L0_H0L0_CADOUT_H0

G0L0_H0L0_CADOUT_L0

U1A

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

SledgeHammer

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

H0L0_G0L0_CADOUT_H15

V4

H0L0_G0L0_CADOUT_L15

V3

H0L0_G0L0_CADOUT_H14

Y5

H0L0_G0L0_CADOUT_L14

W5

H0L0_G0L0_CADOUT_H13

Y4

H0L0_G0L0_CADOUT_L13

Y3

H0L0_G0L0_CADOUT_H12

AB5

H0L0_G0L0_CADOUT_L12

AA5

H0L0_G0L0_CADOUT_H11

AD5

H0L0_G0L0_CADOUT_L11

AC5

H0L0_G0L0_CADOUT_H10

AD4

H0L0_G0L0_CADOUT_L10

AD3

H0L0_G0L0_CADOUT_H9

AF5

H0L0_G0L0_CADOUT_L9

AE5

H0L0_G0L0_CADOUT_H8

AF4

H0L0_G0L0_CADOUT_L8

AF3

H0L0_G0L0_CADOUT_H7

V1

H0L0_G0L0_CADOUT_L7

U1

H0L0_G0L0_CADOUT_H6

W2

H0L0_G0L0_CADOUT_L6

W3

H0L0_G0L0_CADOUT_H5

Y1

H0L0_G0L0_CADOUT_L5

W1

H0L0_G0L0_CADOUT_H4

AA2

H0L0_G0L0_CADOUT_L4

AA3

H0L0_G0L0_CADOUT_H3

AC2

H0L0_G0L0_CADOUT_L3

AC3

H0L0_G0L0_CADOUT_H2

AD1

H0L0_G0L0_CADOUT_L2

AC1

H0L0_G0L0_CADOUT_H1

AE2

H0L0_G0L0_CADOUT_L1

AE3

H0L0_G0L0_CADOUT_H0

AF1

H0L0_G0L0_CADOUT_L0

AE1

AB4

AB3

AB1

AA1

U2

U3

H0L0_G0L0_CADOUT_H[15..0] 20G0L0_H0L0_CADOUT_H[15..0]20

H0L0_G0L0_CADOUT_L[15..0] 20

H0L0_G0L0_CLKOUT_H1 20

H0L0_G0L0_CLKOUT_L1 20

H0L0_G0L0_CLKOUT_H0 20

H0L0_G0L0_CLKOUT_L0 20

H0L0_G0L0_CTLOUT_L0 20

C150

4.7u/35V-1206

+1.2V_VLDT

AB10

AC11

AD10

AD8

AB14

AC15

AB16

AC16

AC9

AG11

AG12

AJ10

AH10

AG9

AG10

AJ8

AH8

AJ6

AH6

AG5

AG6

AJ4

AH4

AG3

AG4

AJ11

AK11

AL9

AL10

AJ9

AK9

AL7

AL8

AL5

AL6

AJ5

AK5

AL3

AL4

AJ3

AK3

AG7

AG8

AJ7

AK7

AL11

AL12

AJ12

AH12

VLDT_2(1)

VLDT_2(2)

VLDT_2(3)

VLDT_2(4)

VLDT_2(5)

VLDT_2(6)

VLDT_2(7)

VLDT_2(8)

VLDT_2(9)

L2_CADIN_H(15)

L2_CADIN_L(15)

L2_CADIN_H(14)

L2_CADIN_L(14)

L2_CADIN_H(13)

L2_CADIN_L(13)

L2_CADIN_H(12)

L2_CADIN_L(12)

L2_CADIN_H(11)

L2_CADIN_L(11)

L2_CADIN_H(10)

L2_CADIN_L(10)

L2_CADIN_H(9)

L2_CADIN_L(9)

L2_CADIN_H(8)

L2_CADIN_L(8)

L2_CADIN_H(7)

L2_CADIN_L(7)

L2_CADIN_H(6)

L2_CADIN_L(6)

L2_CADIN_H(5)

L2_CADIN_L(5)

L2_CADIN_H(4)

L2_CADIN_L(4)

L2_CADIN_H(3)

L2_CADIN_L(3)

L2_CADIN_H(2)

L2_CADIN_L(2)

L2_CADIN_H(1)

L2_CADIN_L(1)

L2_CADIN_H(0)

L2_CADIN_L(0)

L2_CLKIN_H(1)

L2_CLKIN_L(1)

L2_CLKIN_H(0)

L2_CLKIN_L(0)

L2_CTLIN_H(0)

L2_CTLIN_L(0)

L2_RSVD1

L2_RSVD2

SledgeHammer

U1F

L2_CADOUT_H(15)

L2_CADOUT_L(15)

L2_CADOUT_H(14)

L2_CADOUT_L(14)

L2_CADOUT_H(13)

L2_CADOUT_L(13)

L2_CADOUT_H(12)

L2_CADOUT_L(12)

L2_CADOUT_H(11)

L2_CADOUT_L(11)

L2_CADOUT_H(10)

L2_CADOUT_L(10)

L2_CADOUT_H(9)

L2_CADOUT_L(9)

L2_CADOUT_H(8)

L2_CADOUT_L(8)

L2_CADOUT_H(7)

L2_CADOUT_L(7)

L2_CADOUT_H(6)

L2_CADOUT_L(6)

L2_CADOUT_H(5)

L2_CADOUT_L(5)

L2_CADOUT_H(4)

L2_CADOUT_L(4)

L2_CADOUT_H(3)

L2_CADOUT_L(3)

L2_CADOUT_H(2)

L2_CADOUT_L(2)

L2_CADOUT_H(1)

L2_CADOUT_L(1)

L2_CADOUT_H(0)

L2_CADOUT_L(0)

L2_CLKOUT_H(1)

L2_CLKOUT_L(1)

L2_CLKOUT_H(0)

L2_CLKOUT_L(0)

L2_CTLOUT_H(0)

L2_CTLOUT_L(0)

L2_RSVD3

L2_RSVD4

AH14

AJ14

AG16

AG15

AH16

AJ16

AG18

AG17

AG20

AG19

AH20

AJ20

AG22

AG21

AH22

AJ22

AL14

AL13

AK15

AJ15

AL16

AL15

AK17

AJ17

AK19

AJ19

AL20

AL19

AK21

AJ21

AL22

AL21

AH18

AJ18

AL18

AL17

AK13

AJ13

AG13

AG14

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

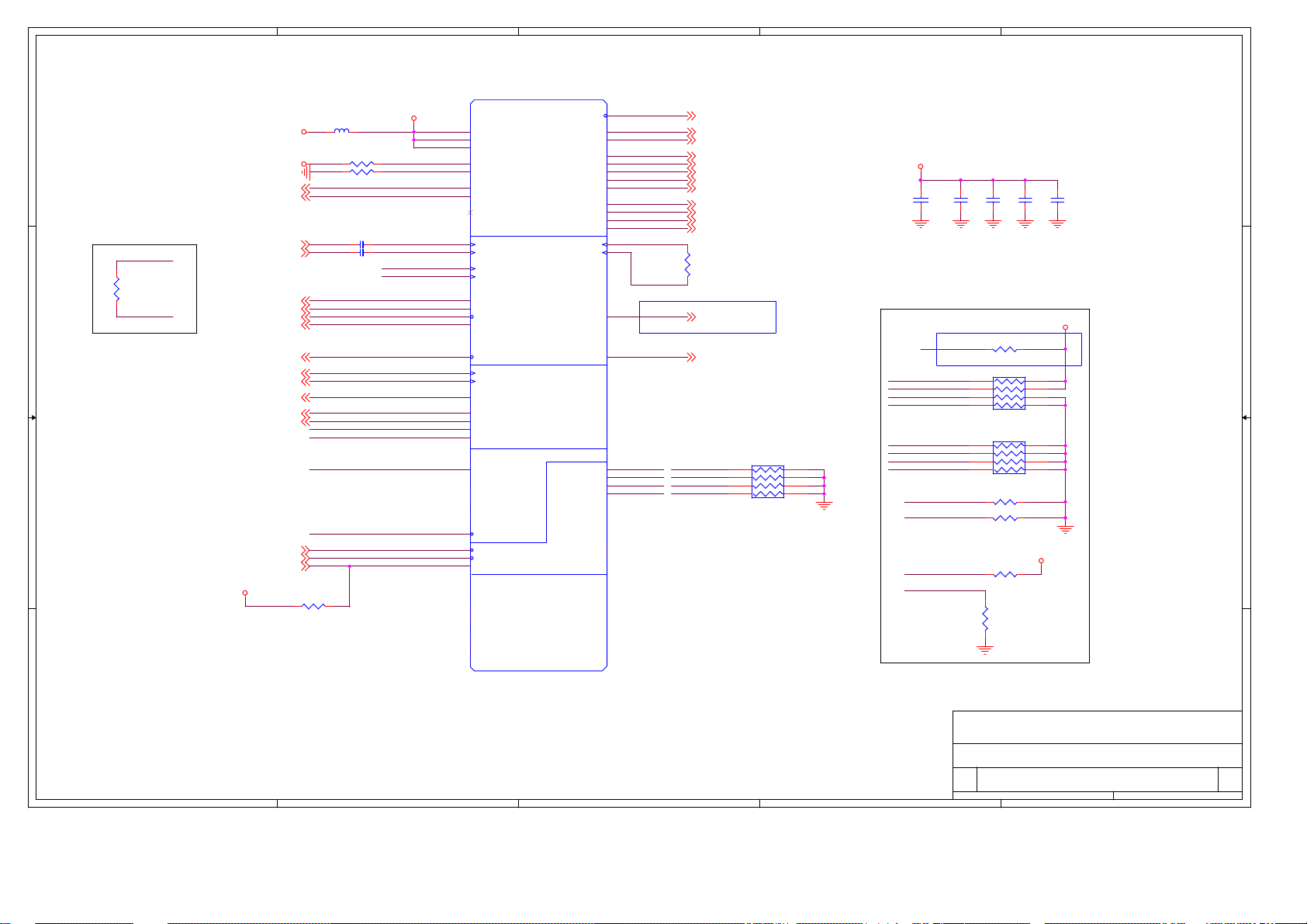

CPU0 HT0&HT2

Size Document Number Rev

MS-9131

5

4

3

2

Date: Sheet of

5 53Monday, January 19, 2004

1

0AB

5

LAYOUT: Place solder side of processor.

VCORE_H0

C931

C1013

22u/6.3v/X5R-1206

D D

C C

22u/6.3v/X5R-1206

LAYOUT: Place clolse to socket.

VCORE_H0

C543

4.7u/35V-1206

4.7u/35V-1206

+2.5VDIMM_H0 VCORE_H0

L19

W21

AA21

J21

U1D

VDDIO1

VDDIO2

VDDIO3

VSS6

VSS7

VSS8

F17

P19

N30F1F2K2P2

M22

VDDIO4

VSS9

4.7u/35V-1206

P22

VDDIO5

VDDIO6

VSS10

VSS11

C499

T22

V22

VDDIO7

VSS12

T13V2AB2

Y22

AB22

VDDIO8

VDDIO9

VSS92

VSS13

C935

22u/6.3v/X5R-1206

AJ23

VDDIO10

VDDIO11

VSS14

VSS15

AF2

C943

22u/6.3v/X5R-1206

C352

C555

4.7u/35V-1206

4.7u/35V-1206

4.7u/35V-1206

AA19

C23

E23

K26

T26

AE28

G26

N26

W26

AE26

AG23

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS93

VSS22

VSS23

VSS24

AK2B3AH3G4L4R4V13W4AC4F5D6H6M7

+5VDUAL

R180

10K

C544

4.7u/35V-1206

K20

D28

K28

T28

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VSS25

VSS26

VSS27

VSS28

VSS29

AB7Y6AD6

-H0_PRESENT 33

C491

AB28

AH28

AH26

VDDIO27

VDDIO28

VSS30

VSS94

J17

AK6B7F14P7V7Y7M6

VDDIO29

VSS31

+2.5VDIMM_H0

R31

D26

K22

A23

U23

AL23

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VSS41

VSS42

VSS43

VSS44

AA8

AF8F8G17K9AB13M9P9

VDDIO45

VSS45

AC21

VDDIO47

VSS46

AD22

VDDIO48

VSS96

X_51RST

AB23

AC23

AF20V6AD12H2AA4

VDDIOFB_L

VDDIOFB_H

VDDIO_SENSE

VSS47

VSS48

VSS50

VSS49

AC22Y9AB9

T9

T18

V18

Y18

K12

F19

VDD1

VDD2

VDD3

VDD4

VDD5

VDD117

VDD118

VDD119

VSS51

VSS52

VSS53

VSS54

VSS55

VSS97

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

AD9

D10

J10

AD13

L10

N10

R10

U10T6AA10

AC10

AK10

H0_VDDIO_SENSE43

G28

N28

W28

AB26

AB20

L21

N21

R21

U21

H22

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO40

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS95

VSS38

VSS39

VSS40

Y13N8R8U8W8

4

EMI

LAYOUT:

Place 1 capacitor every 1-1.5" along VDD_CORE perimiter.

VCORE_H0

C481

C500

1000P/50V/X7R

VDD37

VDD38

VSS100

VSS81

W12

W14

VDD39

VDD40

VSS102

VSS103

AA14

C385

6.8p/50V/NPO

VDD41

VDD42

VDD43

VSS104

VSS105

VSS106

AC14

AH15

AK14

C485

6.8p/50V/NPO

AA9

AB18

VDD44

VDD45

VSS107

VSS108

B15

K15

C362

C465

6.8p/50V/NPO

6.8p/50V/NPO

AH9

W13

M10

P10

T10

V10Y2Y10

AB12

AF10

F11

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VSS109

VSS182

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS183

M15

B23

P15

T15

V15

Y15

AB15

D14

J14

H17

G24

C374

C532

C537

C541

6.8p/50V/NPO

6.8p/50V/NPO

6.8p/50V/NPO

6.8p/50V/NPO

LAYOUT:

Place 1000pF capacitors between VRM & CPU.

VCORE_H0

C366

C386

C536C354

1000P/50V/X7R

1000P/50V/X7R

1000P/50V/X7R

N19

R19

U19

W19

D20

AE4

M20

P20

T20

V20

Y20

AK20

B21

AH21

AK4B5AH5K6P6T8AB6

AF6M2F6D8G7

AB8

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VSS63

VSS64

VSS98

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS99

VSS72

VSS82

VSS83

VSS84

B11

L14

H15J8K11

VSS85

M11

P11

T11

V11

N14

Y11

AA12

N16

AF12

F13

AK8B9K18L9N9R9T2U9W9

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VSS86

VSS87

VSS88

VSS89

VSS101

VSS90

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

G15

F10

VSS80

AD15

K13

U14

M13

AB11

AD11

AH11

G13

J12

N12

R12

U12

R14

C462

6.8p/50V/NPO

L11

N11

R11

VDD57

VDD58

VSS118

VSS119

L16

R16

U16

U11

VDD59

VSS120

W18

6.8p/50V/NPO

W11

AA11

VDD60

VDD61

VSS121

VSS122

AA16

AC17

C509

C529

6.8p/50V/NPO

6.8p/50V/NPO

AD2

D12

M12

P12

T12

V12

Y12

AC13

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VSS123

VSS124

VSS125

VSS126

VSS184

VSS127

VSS128

VSS129

VSS130

AF16

F16

K17

N24

M17

P17

T17

V17

3

AK12

B13

L13D4N13

R13

U13

AA13

AH13

J13

M14

P14

T14J4V14

Y14

AD14

AF14

F15

L15

N15

R15

U15

W15N4AA15

D16

F18

M16

P16

T16

V16

Y16

AD16

AK16U4B17

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD95

VSS131

VSS132

VSS133

VSS134

VSS135

VSS185

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS186

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

Y17

AB17

AD17

D18

J18

W24

L18

N18

R18

U18

W10

AA18

AE17

VSS153

AK18

B19

G30

K19

M19

T19

V19

Y19

AB19

AH19

J20

L20

L17

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VSS187

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS188

VSS163

W30

VSS164

N20

R20

U20

W20

AA20

AC20

AF21

K21

M21

AB24

P21

T21

SledgeHammer

N17

R17

U17

W17

AA17

AH17

M18

P18

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS189

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS190

VSS181

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

V21

Y21

AB21

D22

G22

L22

N22

B26

R22

U22

W22

AA22

AE22

AK22

VSS197

J22

AE24

AK26

B29

AK23

K24

T24

AE30

AK29

D30

K30

T30

AG2E2P13

AB30

2

W16

D23

AH23

VSS5

VSS91

VSS203

VSS202

VSS200

VSS201

VSS198

VSS199

VSS1

VSS2

VSS3

VSS4

AH30

AH7V9L12

AC12

1

B B

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

CPU0_K8 POWER & GND

Size Document Number Rev

MS-9131

5

4

3

2

Date: Sheet of

1

6 53Monday, January 19, 2004

0AD

5

Registered DDR333 SDRAM Sockets

4

3

2

1

D D

DDR1-8_VREF

H0_DR_MD0

H0_DR_MD1

H0_DR_MD2

H0_DR_MD3

H0_DR_MD4

H0_DR_MD5

H0_DR_MD6

H0_DR_MD7

H0_DR_MD8

H0_DR_MD9

H0_DR_MD10

H0_DR_MD11

H0_DR_MD12

H0_DR_MD13

H0_DR_MD14

H0_DR_MD15

H0_DR_MD16

H0_DR_MD17

H0_DR_MD18

H0_DR_MD19

H0_DR_MD20

H0_DR_MD21

H0_DR_MD22

H0_DR_MD23

H0_DR_MD24

H0_DR_MD25

H0_DR_MD26

H0_DR_MD27

H0_DR_MD28

H0_DR_MD29

H0_DR_MD30

H0_DR_MD31

H0_DR_MD32

H0_DR_MD33

H0_DR_MD34

H0_DR_MD35

H0_DR_MD36

H0_DR_MD37

H0_DR_MD38

H0_DR_MD39

H0_DR_MD40

H0_DR_MD41

H0_DR_MD42

H0_DR_MD43

H0_DR_MD44

H0_DR_MD45

H0_DR_MD46

H0_DR_MD47

H0_DR_MD48

H0_DR_MD49

H0_DR_MD50

H0_DR_MD51

H0_DR_MD52

H0_DR_MD53

H0_DR_MD54

H0_DR_MD55

H0_DR_MD56

H0_DR_MD57

H0_DR_MD58

H0_DR_MD59

H0_DR_MD60

H0_DR_MD61

H0_DR_MD62

H0_DR_MD63

C251

0.1u

+2.5VDIMM_H0

H0_DR_MD[63..0]8,9,10,11

C C

B B

H0_DR_-MSWEA8,9,10,11

105

106

109

110

114

117

121

123

126

127

131

133

146

147

150

151

153

155

161

162

165

166

170

171

174

175

178

179

C252

101

102

1000P/50V/X7R

+2.5VDIMM_H0

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

DQ12

DQ13

DQ14

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

DQ20

DQ21

DQ22

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

DQ28

DQ29

DQ30

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

DQ36

DQ37

DQ38

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

DQ44

DQ45

DQ46

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

DQ52

DQ53

DQ54

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

DQ60

DQ61

DQ62

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

NC3

NC4

738467085

VDD0

Channel A

108

120

148

168223054627796

104

112

128

136

143

156

164

172

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

184

PIN

DDR DIMM

SOCKET

SLAVE ADDRESS = 1010000B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

3111826344250586674818993

VSS19

100

116

124

132

139

145

152

1801582

VDDQ14

VDDQ15

CK1#(CK0#)

NC(RESET#)

VSS20

VSS21

160

176

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

CKE0

CKE1

CAS#

RAS#

184

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

DDR2

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

H0_DR_-MCS0 11

H0_DR_-MCS1 11

H0_DR_MDQS0 8,9,10,11

H0_DR_MDQS1 8,9,10,11

H0_DR_MDQS2 8,9,10,11

H0_DR_MDQS3 8,9,10,11

H0_DR_MDQS4 8,9,10,11

H0_DR_MDQS5 8,9,10,11

H0_DR_MDQS6 8,9,10,11

H0_DR_MDQS7 8,9,10,11

H0_DR_MDQS8 8,9,10,11

H0_DR_MAA13 8,9,10,11

H0_DR_MAA0 8,9,10,11

H0_DR_MAA1 8,9,10,11

H0_DR_MAA2 8,9,10,11

H0_DR_MAA3 8,9,10,11

H0_DR_MAA4 8,9,10,11

H0_DR_MAA5 8,9,10,11

H0_DR_MAA6 8,9,10,11

H0_DR_MAA7 8,9,10,11

H0_DR_MAA8 8,9,10,11

H0_DR_MAA9 8,9,10,11

H0_DR_MAA10 8,9,10,11

H0_DR_MAA11 8,9,10,11

H0_DR_MAA12 8,9,10,11

H0_DR_MEMBAKA0 8,9,10,11

H0_DR_MEMBAKA1 8,9,10,11

DM-SMBCLK_1 8,9,10,33

H0_DR_MEMCHECK0 8,9,10,11

H0_DR_MEMCHECK1 8,9,10,11

H0_DR_MEMCHECK2 8,9,10,11

H0_DR_MEMCHECK3 8,9,10,11

H0_DR_MEMCHECK4 8,9,10,11

H0_DR_MEMCHECK5 8,9,10,11

H0_DR_MEMCHECK6 8,9,10,11

H0_DR_MEMCHECK7 8,9,10,11

H0_MEMCLK_H1 3

H0_MEMCLK_L1 3

H0_MEMRESET_L 3,8,9,10

H0_DR_MCKELO 8,9,10,11

H0_DR_MCKEUP 8,9,10,11

H0_DR_-MSCASA 8,9,10,11

H0_DR_-MSRASA 8,9,10,11

H0_DR_MDQS9 8,9,10,11

H0_DR_MDQS10 8,9,10,11

H0_DR_MDQS11 8,9,10,11

H0_DR_MDQS12 8,9,10,11

H0_DR_MDQS13 8,9,10,11

H0_DR_MDQS14 8,9,10,11

H0_DR_MDQS15 8,9,10,11

H0_DR_MDQS16 8,9,10,11

H0_DR_MDQS17 8,9,10,11

+2.5VDIMM_H0

738467085

VDD0

VDD1

VDD2

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

SLAVE ADDRESS = 1010001B

102

NC4

DDR1-8_VREF

H0_DR_MD64

H0_DR_MD65

H0_DR_MD66

H0_DR_MD67

H0_DR_MD68

H0_DR_MD69

H0_DR_MD70

H0_DR_MD71

H0_DR_MD72

H0_DR_MD73

H0_DR_MD74

H0_DR_MD75

H0_DR_MD76

H0_DR_MD77

H0_DR_MD78

H0_DR_MD79

H0_DR_MD80

H0_DR_MD81

H0_DR_MD82

H0_DR_MD83

H0_DR_MD84

H0_DR_MD85

H0_DR_MD86

H0_DR_MD87

H0_DR_MD88

H0_DR_MD89

H0_DR_MD90

H0_DR_MD91

H0_DR_MD92

H0_DR_MD93

H0_DR_MD94

H0_DR_MD95

H0_DR_MD96

H0_DR_MD97

H0_DR_MD98

H0_DR_MD99

H0_DR_MD100

H0_DR_MD101

H0_DR_MD102

H0_DR_MD103

H0_DR_MD104

H0_DR_MD105

H0_DR_MD106

H0_DR_MD107

H0_DR_MD108

H0_DR_MD109

H0_DR_MD110

H0_DR_MD111

H0_DR_MD112

H0_DR_MD113

H0_DR_MD114

H0_DR_MD115

H0_DR_MD116

H0_DR_MD117

H0_DR_MD118

H0_DR_MD119

H0_DR_MD120

H0_DR_MD121

H0_DR_MD122

H0_DR_MD123

H0_DR_MD124

H0_DR_MD125

H0_DR_MD126

H0_DR_MD127

H0_DR_-MSWEA

C271

0.1u

+2.5VDIMM_H0

C268

1000P/50V/X7R

H0_DR_MD[127..64]8,9,10,11

Channel B

108

120

148

168223054627796

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

DDR DIMM

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

3111826344250586674818993

VSS10

104

VDDQ5

VSS11

112

VDDQ6

SOCKET

VSS12

100

128

136

VDDQ7

VDDQ8

184

VSS13

VSS14

116

124

143

VDDQ9

VSS15

132

156

VDDQ10

VDDQ11

VSS16

VSS17

139

164

172

1801582

VDDQ12

VDDQ13

VDDQ14

PIN

NC(RESET#)

VSS18

VSS19

VSS20

145

152

160

176

VDDID

VDDQ15

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

CKE0

CKE1

CAS#

RAS#

VSS21

CS0#

CS1#

CS2#

CS3#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

184

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

DDR1

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

H0_DR_MCKELO

21

H0_DR_MCKEUP

111

65

154

97

107

119

129

149

159

169

177

140

H0_DR_-MCS0 11

H0_DR_-MCS1 11

H0_DR_MDQS18 8,9,10,11

H0_DR_MDQS19 8,9,10,11

H0_DR_MDQS20 8,9,10,11

H0_DR_MDQS21 8,9,10,11

H0_DR_MDQS22 8,9,10,11

H0_DR_MDQS23 8,9,10,11

H0_DR_MDQS24 8,9,10,11

H0_DR_MDQS25 8,9,10,11

H0_DR_MDQS26 8,9,10,11

H0_DR_MAA13 8,9,10,11

H0_DR_MAA0 8,9,10,11

H0_DR_MAA1 8,9,10,11

H0_DR_MAA2 8,9,10,11

H0_DR_MAA3 8,9,10,11

H0_DR_MAA4 8,9,10,11

H0_DR_MAA5 8,9,10,11

H0_DR_MAA6 8,9,10,11

H0_DR_MAA7 8,9,10,11

H0_DR_MAA8 8,9,10,11

H0_DR_MAA9 8,9,10,11

H0_DR_MAA10 8,9,10,11

H0_DR_MAA11 8,9,10,11

H0_DR_MAA12 8,9,10,11

H0_DR_MEMBAKA0 8,9,10,11

H0_DR_MEMBAKA1 8,9,10,11

DM-SMBCLK_1 8,9,10,33DM-SMBDAT_1 8,9,10,33

DM-SMBDAT_1 8,9,10,33

+2.5VDIMM_H0

modified on 1/30

H0_DR_MEMCHECK8 8,9,10,11

H0_DR_MEMCHECK9 8,9,10,11

H0_DR_MEMCHECK10 8,9,10,11

H0_DR_MEMCHECK11 8,9,10,11

H0_DR_MEMCHECK12 8,9,10,11

H0_DR_MEMCHECK13 8,9,10,11

H0_DR_MEMCHECK14 8,9,10,11

H0_DR_MEMCHECK15 8,9,10,11

H0_MEMCLK_H0 3

H0_MEMCLK_L0 3

H0_MEMRESET_L 3,8,9,10

H0_DR_-MSCASA 8,9,10,11

H0_DR_-MSRASA 8,9,10,11

H0_DR_MDQS27 8,9,10,11

H0_DR_MDQS28 8,9,10,11

H0_DR_MDQS29 8,9,10,11

H0_DR_MDQS30 8,9,10,11

H0_DR_MDQS31 8,9,10,11

H0_DR_MDQS32 8,9,10,11

H0_DR_MDQS33 8,9,10,11

H0_DR_MDQS34 8,9,10,11

H0_DR_MDQS35 8,9,10,11

DDR1-8_VREF+2.5VDIMM_H0

C267

R83

A A

5

4

100RST

R80

100RST

0.1u

C273

C274

1000P/50V/X7R

0.1u

3

2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Register DDR DIMM1 & 2

Size Document Number Rev

MS-9131

Date: Sheet of

1

7 53Monday, January 19, 2004

0AC

5

Registered DDR333 SDRAM Sockets

4

3

2

1

VDD4

VSS1

108

VDD5

VSS2

120

148

168223054627796

VDD6

VDD7

VDD8

VSS3

VSS4

VSS5

Channel B

104

112

128

136

143

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

184 PIN

DDR DIMM

SOCKET

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

100

116

124

132

156

164

VDDQ11

VSS17

139

145

172

1801582

VDDQ12

VDDQ13

VSS18

VSS19

152

160

VDDQ14

VDDQ15

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

VSS20

VSS21

176

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

DDR3

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

H0_DR_MCKELO

21

H0_DR_MCKEUP

111

65

154

97

107

119

129

149

159

169

177

140

H0_DR_-MCS2 11

H0_DR_-MCS3 11H0_DR_-MCS3 11

H0_DR_MDQS18 7,9,10,11

H0_DR_MDQS19 7,9,10,11

H0_DR_MDQS20 7,9,10,11

H0_DR_MDQS21 7,9,10,11

H0_DR_MDQS22 7,9,10,11

H0_DR_MDQS23 7,9,10,11

H0_DR_MDQS24 7,9,10,11

H0_DR_MDQS25 7,9,10,11

H0_DR_MDQS26 7,9,10,11

H0_DR_MAA13 7,9,10,11

H0_DR_MAA0 7,9,10,11

H0_DR_MAA1 7,9,10,11

H0_DR_MAA2 7,9,10,11

H0_DR_MAA3 7,9,10,11

H0_DR_MAA4 7,9,10,11

H0_DR_MAA5 7,9,10,11

H0_DR_MAA6 7,9,10,11

H0_DR_MAA7 7,9,10,11

H0_DR_MAA8 7,9,10,11

H0_DR_MAA9 7,9,10,11

H0_DR_MAA10 7,9,10,11

H0_DR_MAA11 7,9,10,11

H0_DR_MAA12 7,9,10,11

H0_DR_MEMBAKA0 7,9,10,11

H0_DR_MEMBAKA1 7,9,10,11

DM-SMBCLK_1 7,9,10,33

DM-SMBDAT_1 7,9,10,33

+2.5VDIMM_H0

H0_DR_MEMCHECK8 7,9,10,11

H0_DR_MEMCHECK9 7,9,10,11

H0_DR_MEMCHECK10 7,9,10,11

H0_DR_MEMCHECK11 7,9,10,11

H0_DR_MEMCHECK12 7,9,10,11

H0_DR_MEMCHECK13 7,9,10,11

H0_DR_MEMCHECK14 7,9,10,11

H0_DR_MEMCHECK15 7,9,10,11

H0_MEMCLK_H2 3

H0_MEMCLK_L2 3

H0_MEMRESET_L 3,7,9,10

H0_DR_-MSCASA 7,9,10,11

H0_DR_-MSRASA 7,9,10,11

H0_DR_MDQS27 7,9,10,11

H0_DR_MDQS28 7,9,10,11

H0_DR_MDQS29 7,9,10,11

H0_DR_MDQS30 7,9,10,11

H0_DR_MDQS31 7,9,10,11

H0_DR_MDQS32 7,9,10,11

H0_DR_MDQS33 7,9,10,11

H0_DR_MDQS34 7,9,10,11

H0_DR_MDQS35 7,9,10,11

Channel A

+2.5VDIMM_H0+2.5VDIMM_H0

D D

H0_DR_MD[63..0]7,9,10,11

C C

B B

H0_DR_-MSWEA7,9,10,11

DDR1-8_VREF

H0_DR_MD0

H0_DR_MD1

H0_DR_MD2

H0_DR_MD3

H0_DR_MD4

H0_DR_MD5

H0_DR_MD6

H0_DR_MD7

H0_DR_MD8

H0_DR_MD9

H0_DR_MD10

H0_DR_MD11

H0_DR_MD12

H0_DR_MD13

H0_DR_MD14

H0_DR_MD15

H0_DR_MD16

H0_DR_MD17

H0_DR_MD18

H0_DR_MD19

H0_DR_MD20

H0_DR_MD21

H0_DR_MD22

H0_DR_MD23

H0_DR_MD24

H0_DR_MD25

H0_DR_MD26

H0_DR_MD27

H0_DR_MD28

H0_DR_MD29

H0_DR_MD30

H0_DR_MD31

H0_DR_MD32

H0_DR_MD33

H0_DR_MD34

H0_DR_MD35

H0_DR_MD36

H0_DR_MD37

H0_DR_MD38

H0_DR_MD39

H0_DR_MD40

H0_DR_MD41

H0_DR_MD42

H0_DR_MD43

H0_DR_MD44

H0_DR_MD45

H0_DR_MD46

H0_DR_MD47

H0_DR_MD48

H0_DR_MD49

H0_DR_MD50

H0_DR_MD51

H0_DR_MD52

H0_DR_MD53

H0_DR_MD54

H0_DR_MD55

H0_DR_MD56

H0_DR_MD57

H0_DR_MD58

H0_DR_MD59

H0_DR_MD60

H0_DR_MD61

H0_DR_MD62

H0_DR_MD63

C215

C218

0.1u

1000P/50V/X7R

+2.5VDIMM_H0 +2.5VDIMM_H0

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VDDQ2

VSS8

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

SLAVE ADDRESS = 1010010B

102

NC4

VSS0

3111826344250586674818993

104

112

128

136

143

156

164

172

1801582

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

184 PIN

DDR DIMM

SOCKET

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

100

VSS20

116

124

132

139

145

152

160

VDDID

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS21

176

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

DDR4

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

H0_DR_-MCS2 11

H0_DR_MDQS0 7,9,10,11

H0_DR_MDQS1 7,9,10,11

H0_DR_MDQS2 7,9,10,11

H0_DR_MDQS3 7,9,10,11

H0_DR_MDQS4 7,9,10,11

H0_DR_MDQS5 7,9,10,11

H0_DR_MDQS6 7,9,10,11

H0_DR_MDQS7 7,9,10,11

H0_DR_MDQS8 7,9,10,11

H0_DR_MAA13 7,9,10,11

H0_DR_MAA0 7,9,10,11

H0_DR_MAA1 7,9,10,11

H0_DR_MAA2 7,9,10,11

H0_DR_MAA3 7,9,10,11

H0_DR_MAA4 7,9,10,11

H0_DR_MAA5 7,9,10,11

H0_DR_MAA6 7,9,10,11

H0_DR_MAA7 7,9,10,11

H0_DR_MAA8 7,9,10,11

H0_DR_MAA9 7,9,10,11

H0_DR_MAA10 7,9,10,11

H0_DR_MAA11 7,9,10,11

H0_DR_MAA12 7,9,10,11

H0_DR_MEMBAKA0 7,9,10,11

H0_DR_MEMBAKA1 7,9,10,11

DM-SMBCLK_1 7,9,10,33

DM-SMBDAT_1 7,9,10,33

+2.5VDIMM_H0

H0_DR_MEMCHECK0 7,9,10,11

H0_DR_MEMCHECK1 7,9,10,11

H0_DR_MEMCHECK2 7,9,10,11

H0_DR_MEMCHECK3 7,9,10,11

H0_DR_MEMCHECK4 7,9,10,11

H0_DR_MEMCHECK5 7,9,10,11

H0_DR_MEMCHECK6 7,9,10,11

H0_DR_MEMCHECK7 7,9,10,11

H0_MEMCLK_H3 3

H0_MEMCLK_L3 3

H0_MEMRESET_L 3,7,9,10

H0_DR_MCKELO 7,9,10,11

H0_DR_MCKEUP 7,9,10,11

H0_DR_-MSCASA 7,9,10,11

H0_DR_-MSRASA 7,9,10,11

H0_DR_MDQS9 7,9,10,11

H0_DR_MDQS10 7,9,10,11

H0_DR_MDQS11 7,9,10,11

H0_DR_MDQS12 7,9,10,11

H0_DR_MDQS13 7,9,10,11

H0_DR_MDQS14 7,9,10,11

H0_DR_MDQS15 7,9,10,11

H0_DR_MDQS16 7,9,10,11

H0_DR_MDQS17 7,9,10,11

738467085

VDD0

VDD1

VDD2

H0_DR_MD[127..64]7,9,10,11

H0_DR_-MSWEA7,9,10,11

DDR1-8_VREF

H0_DR_MD64

H0_DR_MD65

H0_DR_MD66

H0_DR_MD67

H0_DR_MD68

H0_DR_MD69

H0_DR_MD70

H0_DR_MD71

H0_DR_MD72

H0_DR_MD73

H0_DR_MD74

H0_DR_MD75

H0_DR_MD76

H0_DR_MD77

H0_DR_MD78

H0_DR_MD79

H0_DR_MD80

H0_DR_MD81

H0_DR_MD82

H0_DR_MD83

H0_DR_MD84

H0_DR_MD85

H0_DR_MD86

H0_DR_MD87

H0_DR_MD88

H0_DR_MD89

H0_DR_MD90

H0_DR_MD91

H0_DR_MD92

H0_DR_MD93

H0_DR_MD94

H0_DR_MD95

H0_DR_MD96

H0_DR_MD97

H0_DR_MD98

H0_DR_MD99

H0_DR_MD100

H0_DR_MD101

H0_DR_MD102

H0_DR_MD103

H0_DR_MD104

H0_DR_MD105

H0_DR_MD106

H0_DR_MD107

H0_DR_MD108

H0_DR_MD109

H0_DR_MD110

H0_DR_MD111

H0_DR_MD112

H0_DR_MD113

H0_DR_MD114

H0_DR_MD115

H0_DR_MD116

H0_DR_MD117

H0_DR_MD118

H0_DR_MD119

H0_DR_MD120

H0_DR_MD121

H0_DR_MD122

H0_DR_MD123

H0_DR_MD124

H0_DR_MD125

H0_DR_MD126

H0_DR_MD127

C235

0.1u

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

90

63

C238

101

102

1000P/50V/X7R

VDD3

2

DQ0

4

DQ1

6

DQ2

8

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

WP(NC)

WE#

1

VREF

9

NC2

NC3

SLAVE ADDRESS = 1010011B

NC4

VSS0

3111826344250586674818993

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Register DDR DIMM3 & 4

Size Document Number Rev

MS-9131

5

4

3

2

Date: Sheet of

1

8 53Monday, January 19, 2004

0ACustom

5

Registered DDR333 SDRAM Sockets

4

3

2

1

VDD4

VSS1

108

VDD5

VSS2

120

148

168223054627796

VDD6

VDD7

VDD8

VSS3

VSS4

VSS5

Channel B

104

112

128

136

143

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

184 PIN

DDR DIMM

SOCKET

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

100

116

124

132

156

164

VDDQ11

VSS17

139

145

172

1801582

VDDQ12

VDDQ13

VSS18

VSS19

152

160

VDDQ14

VDDQ15

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

VSS20

VSS21

176

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

SDA

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DDR5

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

H0_DR_MCKELO

21

H0_DR_MCKEUP

111

65

154

97

107

119

129

149

159

169

177

140

H0_DR_-MCS4 11

H0_DR_-MCS5 11H0_DR_-MCS5 11

H0_DR_MDQS18 7,8,10,11

H0_DR_MDQS19 7,8,10,11

H0_DR_MDQS20 7,8,10,11

H0_DR_MDQS21 7,8,10,11

H0_DR_MDQS22 7,8,10,11

H0_DR_MDQS23 7,8,10,11

H0_DR_MDQS24 7,8,10,11

H0_DR_MDQS25 7,8,10,11

H0_DR_MDQS26 7,8,10,11

H0_DR_MAA13 7,8,10,11

H0_DR_MAA0 7,8,10,11

H0_DR_MAA1 7,8,10,11

H0_DR_MAA2 7,8,10,11

H0_DR_MAA3 7,8,10,11

H0_DR_MAA4 7,8,10,11

H0_DR_MAA5 7,8,10,11

H0_DR_MAA6 7,8,10,11

H0_DR_MAA7 7,8,10,11

H0_DR_MAA8 7,8,10,11

H0_DR_MAA9 7,8,10,11

H0_DR_MAA10 7,8,10,11

H0_DR_MAA11 7,8,10,11

H0_DR_MAA12 7,8,10,11

H0_DR_MEMBAKA0 7,8,10,11

H0_DR_MEMBAKA1 7,8,10,11

DM-SMBCLK_1 7,8,10,33

DM-SMBDAT_1 7,8,10,33

H0_DR_MEMCHECK8 7,8,10,11

H0_DR_MEMCHECK9 7,8,10,11

H0_DR_MEMCHECK10 7,8,10,11

H0_DR_MEMCHECK11 7,8,10,11

H0_DR_MEMCHECK12 7,8,10,11

H0_DR_MEMCHECK13 7,8,10,11