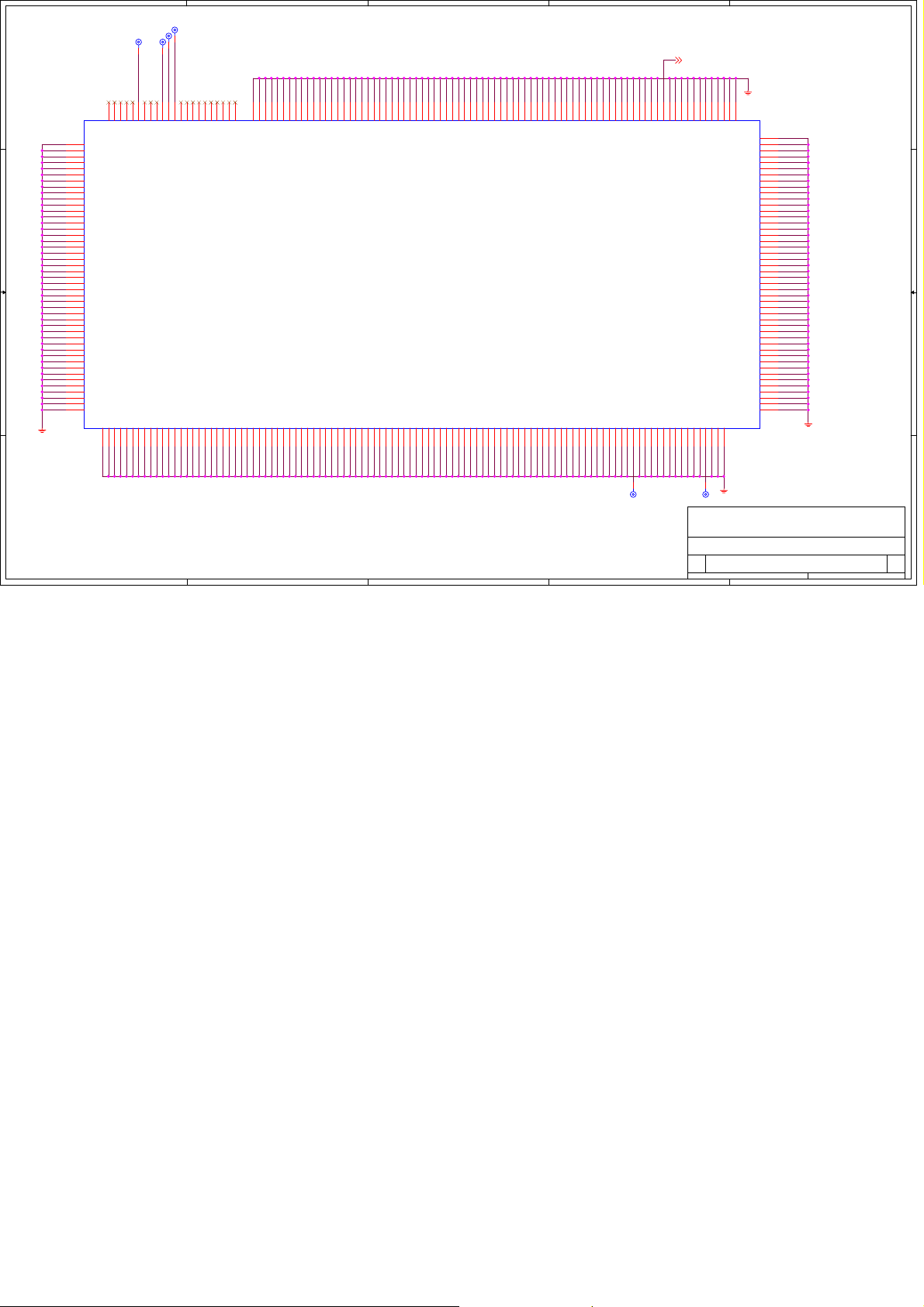

MSI MS-9158 Schematic 1900

5

MSI

MS-9158 REV 0D

4

3

2

1

Alderwood + ICH6R Schematics

D D

Table of Contents

Page

01

02

03

04

05

06

07

08

09

10

11

C C

B B

A A

12

13

14

15

16

17

18

19

20

21

22

23

24 ICH6R - POWER

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

5

Title

Cover / Table of Contents

System Block Diagram

Power Deliver y Bl o ck Di a g ram

System Clock Block Diagram

System Reset Block Diagr a m

System SMBus Block Diagram

DDRII Routing Block Diagram

Inter rupt Block Diagram

Hardware Mon i t or Block Diagram

CK410 - CY28410

Intel LGA775 Signal Block

Intel LGA775 Power

Intel LGA775 GND

Alderwood CPU/PCI Signal

Alderwood Memory Signal

Alderwood Misc/Power Signal

Alderwood Power/Gnd

DDR2 DIMM 1/2

DDR2 DIMM 3/4

DDR2 VTT/ICH6R DECOUPL ING

PCI EXPRESS X16 PORT

ICH6R - PCI, DMI, CPU, IRQ

ICH6R - LPC, ATA, USB, GPIO

PCI_E x1/Mini PCI Slot

PCI Slot1/2

IEEE 1394 Connectors

LAN - Broadcom BCM5751

AC97 Audi o - ALC202/AD1981B

FWH/SATA/PS2 Connectors

USB2.0/SATA Connectors

LPC I/O PC87366

H/W Monitor ADT7468/COM PORT

CPU/SYSTEM FAN

ATX & Front Panel

VRM 10. 1 Intersi l 6556 4Pase

VRM 10.1 Decoupling

DDR2 Power&Regulator Voltage

System P ower Control

PCI Reset & eXDP

IBM1

ABR/PERR/Improper SD

MSIC

GPIO

History

4

Revision History

Revision

History

0A - (xx/xx/xx)

2003/10/16

0B - (xx/xx/xx)

2004/01/13

0C - (xx/xx/xx)

2004/05/19 IBM FireBird Schematics Revision to 0C - Andy Tseng

0D - (xx/xx/xx)

2004/06/11

Start to make up IBM FireBird Schematics - Joe Yu

IBM FireBird Schematics Revision to 0B - Andy Tseng

IBM FireBird Schematics Revision to 0D - Andy Tseng

3

Page

Micro-Star Int'l Co ., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Cover / T ab l e o f C o n t ents

Size Doc u men t Numbe r Re v

MS-9158

2

Date: Sheet of

1

0DCustom

146Thursday, August 26, 2004

5

4

3

2

1

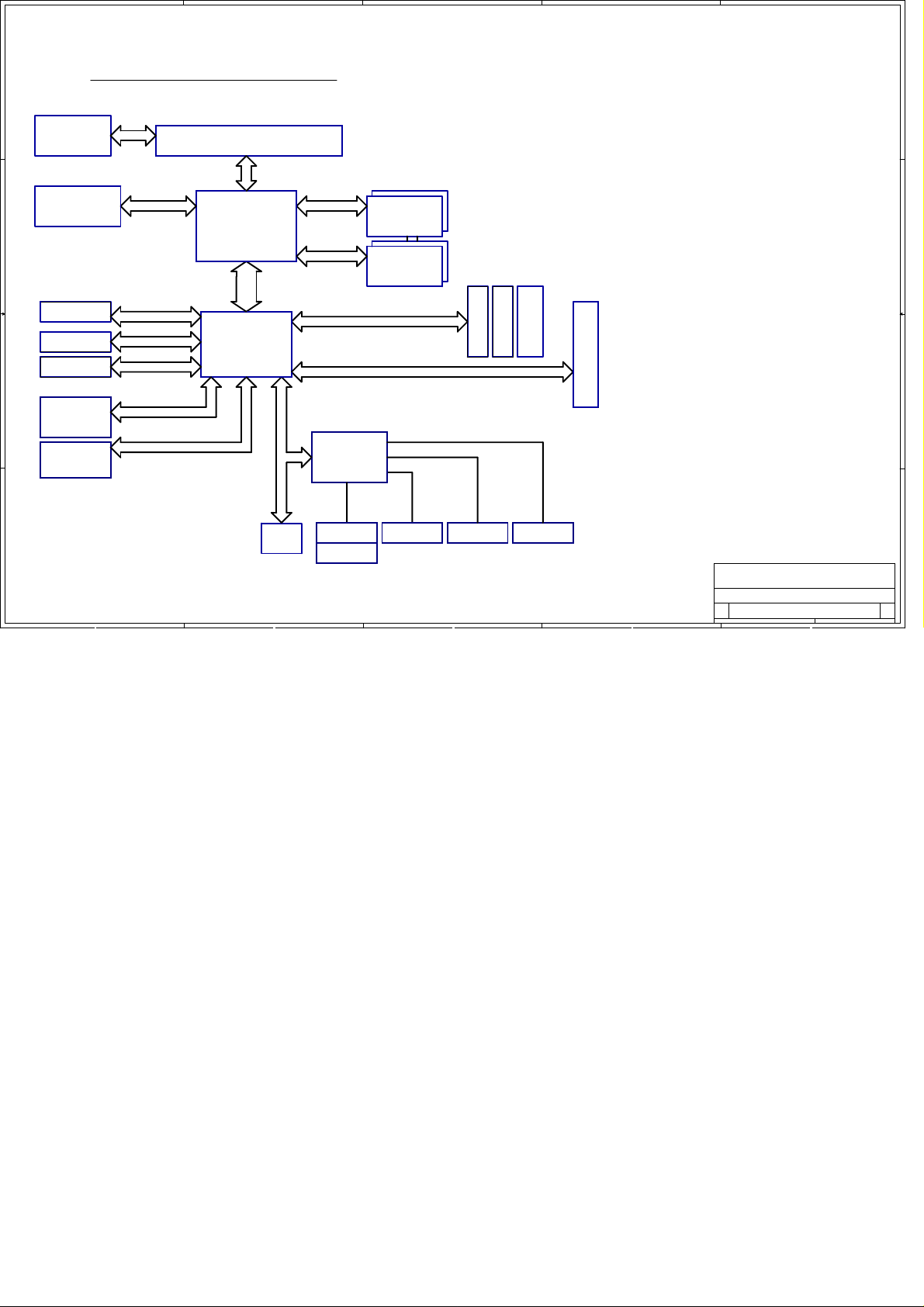

FireBird

D D

External

Graph ics Card

Connector

C C

ATA Primary

SATA 0~3

USB2.0 Port 0~7

B B

MS-9158 SYSTEM BLOCK DIAGRAM

VRM 10.1

Intersil 6556B

4-Phase PWM

ADI1981B/

ALC202A

AC'97 Code c

GIGA LAN

BCM5721

PCI Express X16

BW = 8GB/s

Ultra DMA 66/100

SATA

USB 2.0

AC'97 Link

12.288MHz@1.536MB/s

PCI Express X1

Intel LGA-775

Prescott/Tejas

800/533MHz

Alderwood

(MCH)

PSB

DMI Bus

ICH6R

LPC Bus

DDR2 Channel A

64bit DDR2

400/533MHz

DDR2 Channel B

LPC SIO

NS/PC87366

DDR2 DIMM x2

Modules

DDR2 DIMM x2

Modules

PCI BUS

PCI EXPRESS X1

PCI Slots 1/2

Connector

Mini-PCI

Preliminary Spec

* Intel Alderwood / ICH6R Chipset

* Supporting Tejas/Prescott LGA-775 CPUs

* 6 Layer BTX Form F actor (10.5"X10.4")

* 4 DDR 2 unbuffer ed ECC DIMMs (2 Channel)

* PCI E x p r ess X16 fo r G raphic + PCI Express X1 Slot

* USB 2. 0 (Rear x2, Front x1)

* 2 PCI slots + 1 Mini PCI slot

* AD1981B AC97 codec

* Serial ATA (4 channel) + RAID 0, 1

* IEEE 1394 TI Chip on-board (Rear x1, Front x1)

* Gigab i t L A N B C M 5721 (Support ASF 2.0)

IEEE 1394

TI/TSB43AB23

PCI Express X1 Co nnector

A A

5

FWH

4

PS2 - KB

PS2 - MS

Floppy

Parallel Port

3

Serial Port

Micro-Star Int'l Co ., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System B l o ck D i agram

Size Doc u men t Numbe r Re v

MS-9158

2

Date: Sheet of

1

0DCustom

246Thursday, August 26, 2004

5

4

3

2

1

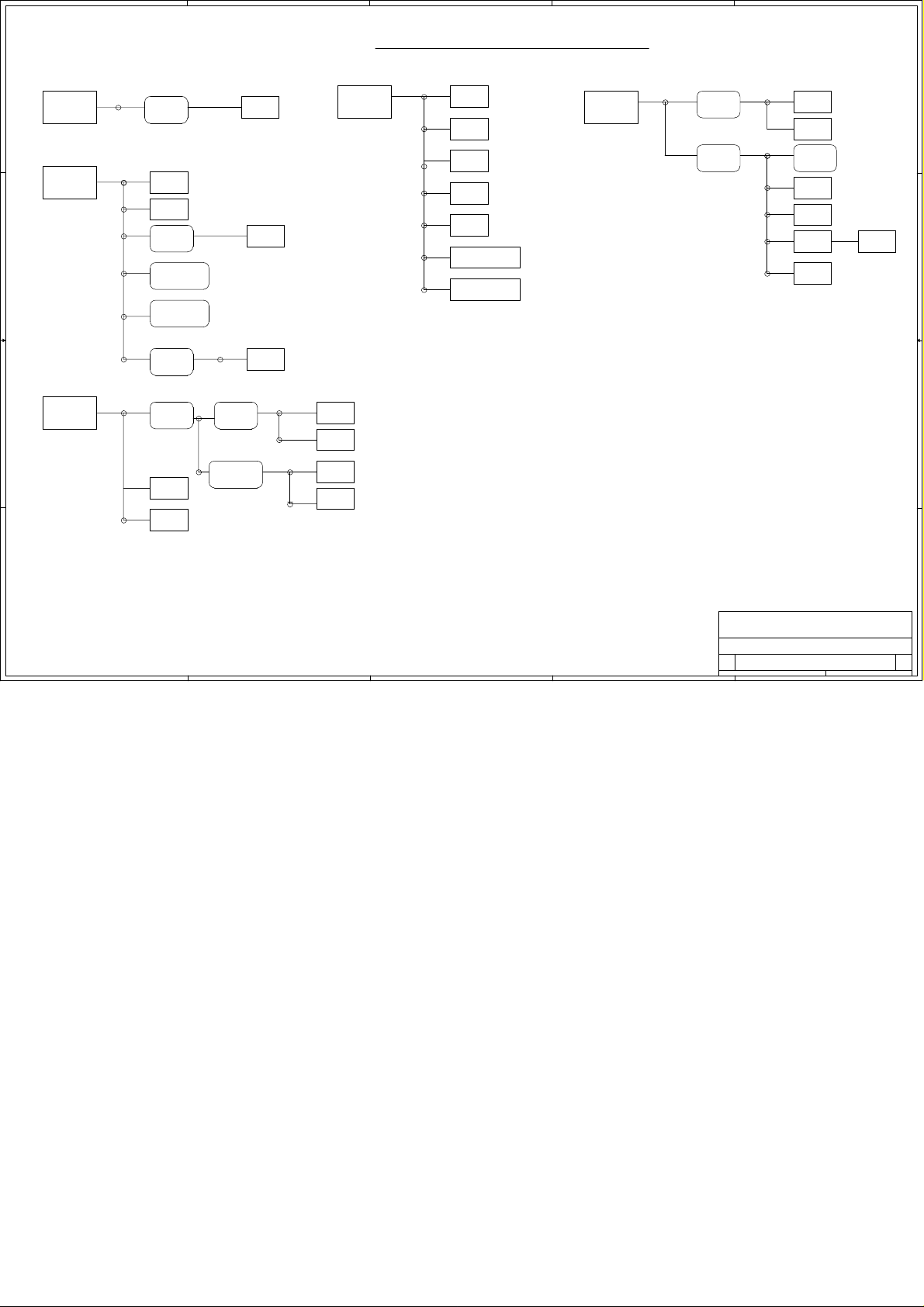

MS-9158 POWER DELIEVERY DIAGRAM

D D

C C

B B

P12V_CPU

31.88A

+12V

20.795A+?

VCC5

21.304A+?

(1.2*95)/(12*0.8)=11.875

11.875A

VRD10.1 CPU

Switch Reg

7A

Fan*3

5.8A

PCI[0:2]

9.5mA+?

P5V_AUD

Linear Reg

4.4A

PCI Express X16

0.5A

PCI Express X1

3A

PWR1394

Power Isolation

5.35A

95.4mA

15A

19.65A

Switch

1394

PCI[0:2]

95A

1.5A

VCC_DDR25VDUAL

Switch

V_1P5_CORE

AD1981B

J1394CON1

1.65A

18A

6.61A

0.86A

VCC3

MCH

DIMMx4

MCH

ICH6

0.56A

0.107A

0.18A

95.4mA

7.6mA

4.4A

0.5A

CK410

FWH

ICH6

1394

PCI[0:2]

PCI Express X16

PCI Express X1

5VSB

1.597A+?

5mA+?

5VDUAL USB*6

Switch

1.592A+?

3VSB

U114

5mA

(Note 3)

?mA

400mA

388mA

6mA

400mA

475mA

(Note 4)

Keyboard

& Mouse

P1V_STBY

Linear Reg

ICH6

ADT7463*2

BCM5721

PCI[0:2]

3mA

EEPROM(U43)

AT25160

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Power Delivery Block Diagram

Size Document Number R e v

MS-9158

5

4

3

2

Date: Sheet of

346Thursday, August 26, 2004

1

0DCustom

5

4

3

2

1

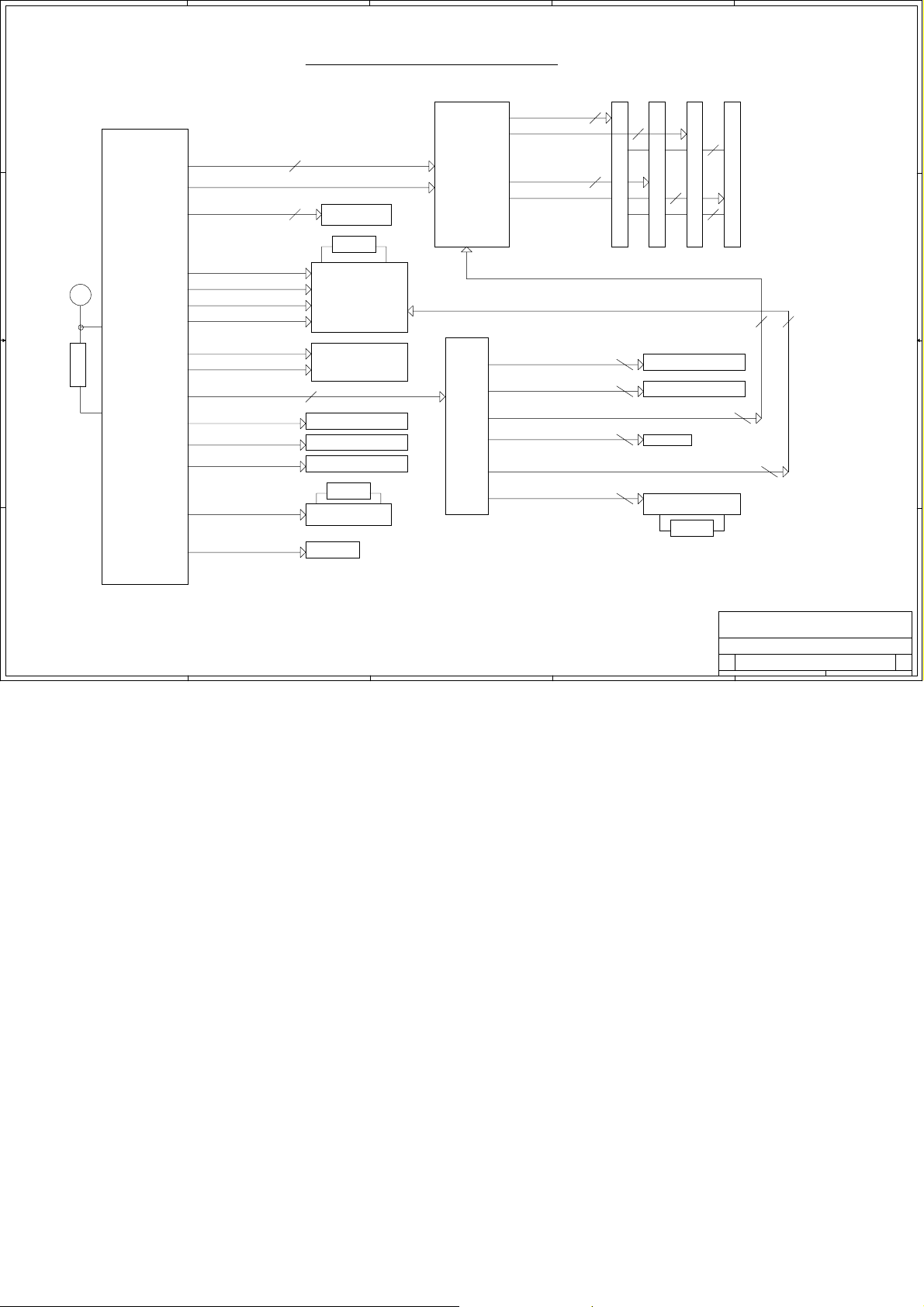

MS-9158 CLOCK BLOCK DIAGRAM

D D

DDR2A_CMDCLK_A0_P/N

DDR2A_CMDCLK_A1_P/N

MCH_BCLK_P/N ( 200MHZ)

CPU0

MCH_100MHZ _CLKP /N

CPU1

ITP_BCLK_P/N (200MHZ)

CPU0

C C

SMA

CONNECTOR

14.318MHZCrystal

B B

3V66_3

USB_48

PCI2

REF0

DOT_48

PCI3

SRC

PCIF0

PCIF1

PCI0

PCIF2

PCI2

ICH_DMI_100MHZ_CLKP/N

ICH_USB_48MHZ_CLK

ICH_33MHZ_CLK

ICH_14MHZ_CLK

SIO_48MHZ_CLK

SIO_33MHZ_CLK

SRC_100MHZ_CLK_P/N

PCI_S LOT0_33MHZ_CLK

PCI_S LOT1_33MHZ_CLK

MPCI_33MHZ_CLK

1394_33MHZ_CLK

FWH_33MHZ_CLK

2

2

eXDP

32.768KHZ

Crystal

ICH6R

SIO

2

PCI 32/33 ( SLOT # 1 )

PCI 32/33 ( SLOT # 2 )

MINI PCI 32/33 ( SLOT # 3 )

24.576MHZ

Crystal

IEEE 1394

FWH

DDR2B_CMDCLK_B0_P/N

MCH

DDR2B_CMDCLK_B1_P/N

SRC1

SRC1#

SRC2

SRC2#

SRC3

SRC3#

SRC4

SRC4#

SRC5

SRC5#

SRC6

SRC6#

EXP_SLOT1_100MHZ_CLK_P/N

EXP_SLOT1_100MHZ_CLK_P/N

MCH_SRC_100MHZ_CL K_P /N

ICHSATA_SRC_100MHZ _CLK_P /N

ICH_SRC_100MHZ_CLK_P/N

LAN_SRC_100MHZ_CLK_P/N

2

2

2

DDR II DIMM #

A1

2

DDR II DIMM #

DDR II DIMM #

A2

B1

2

DDR II DIMM #

B2

2

PCI EXPRESS X16 SLOT # 1

PCI EXPRESS X1 SLOT # 1

SATA

BCM5721

25MHZ

Crystal

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Clock Block Diagram

Size Document Number R e v

MS-9158

5

4

3

2

Date: Sheet of

446Thursday, August 26, 2004

1

0DCustom

5

4

3

2

1

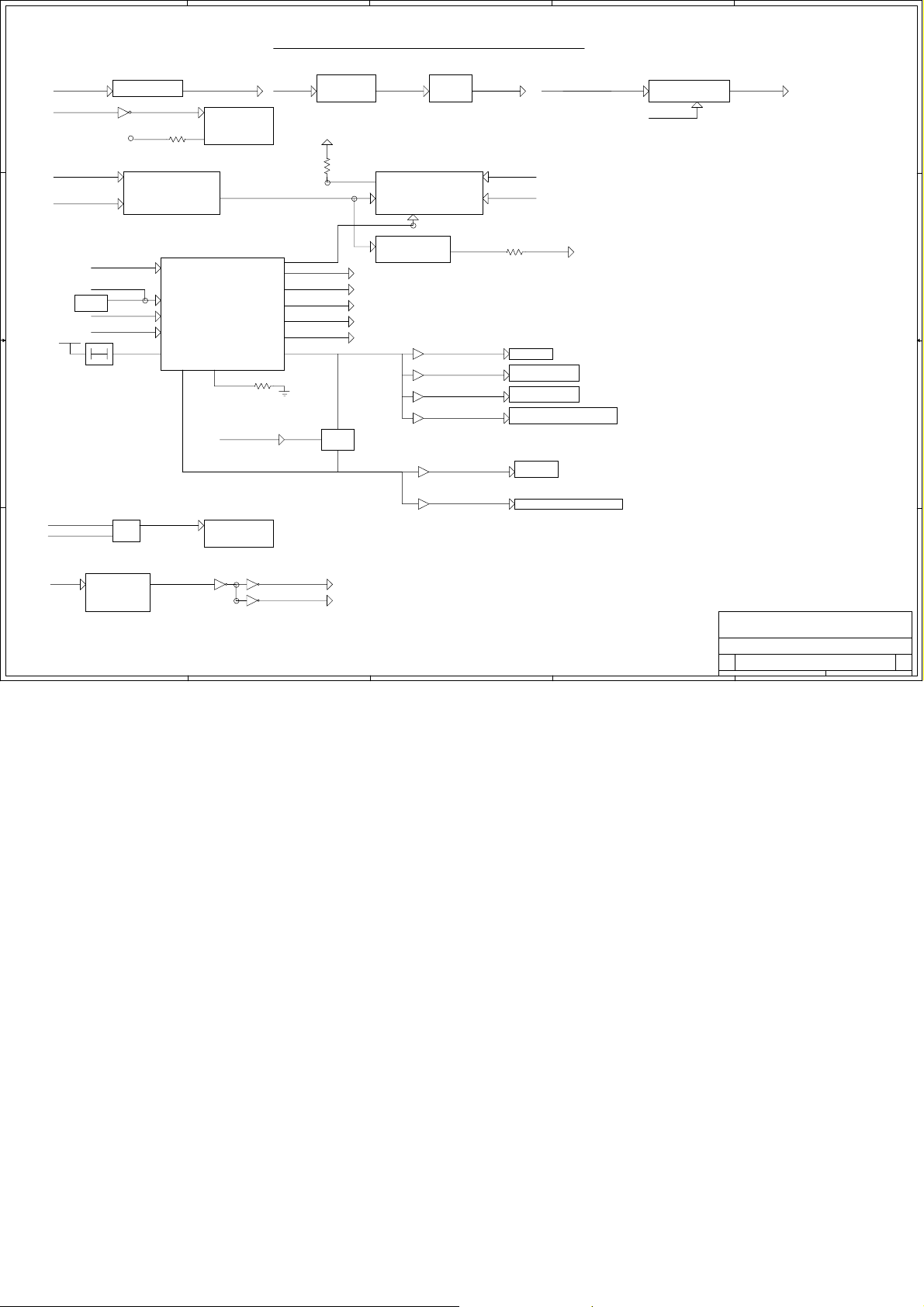

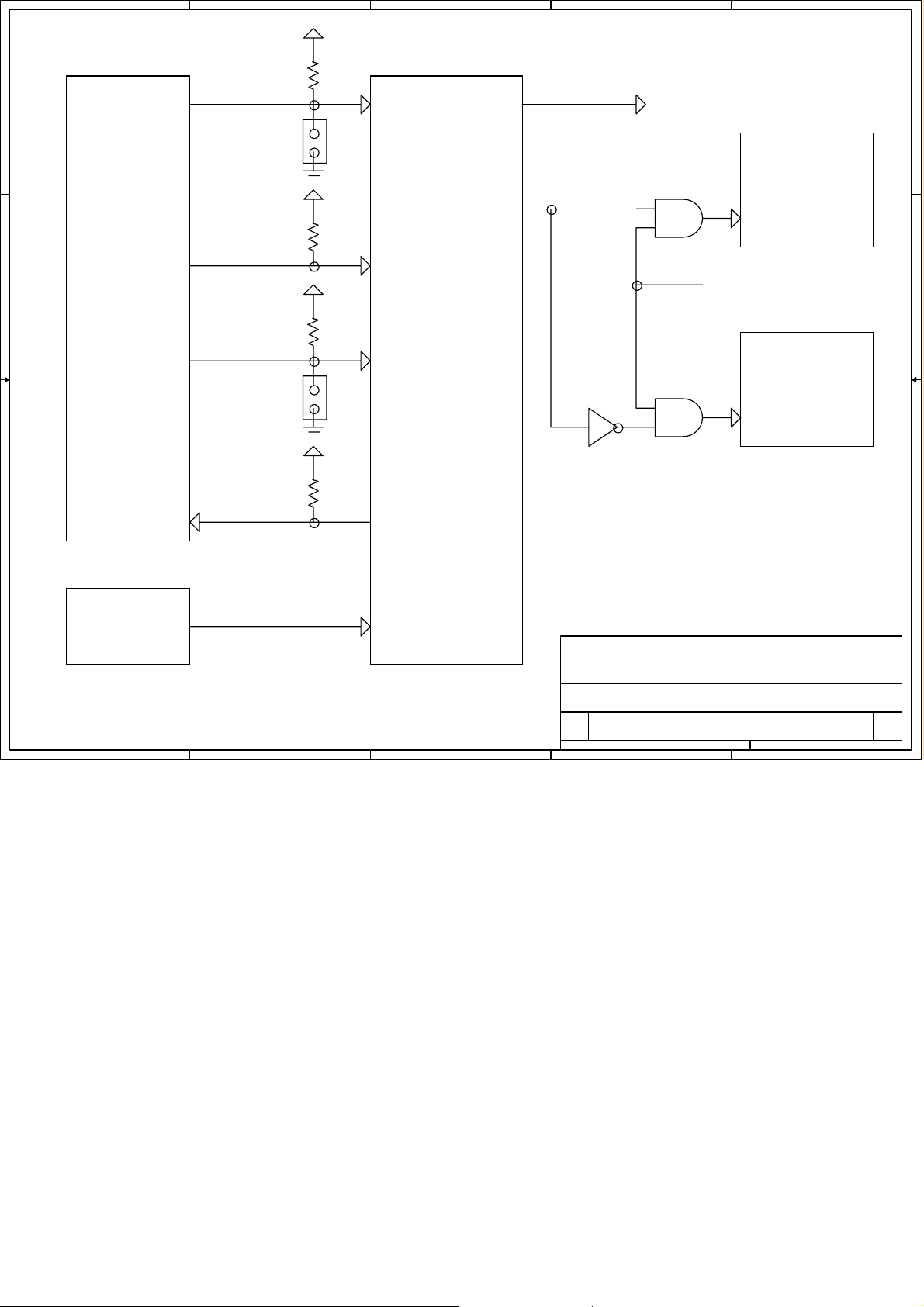

MS-9158 SYSTEM RESET BLOCK D IAGRAM

D D

CPU BSEL[0:2] VTT_PWRGD

BSEL c om p arator

circuit

VTT_GD

ENABLE

1.2V Reg

PWRGD

VTT_PWRGD

VTT_PWRGD VTT_PWRGD_NCK409B_PWR_GD_N

VCC3_CLK

PWROK_N

C C

ICH_PWRBTN_N

FP_RESET_N

ASR SLP_S5_N

CPU_VRD_PWR_GD

SYS_PWR_GD_3_3V

3.3V STBY

RSM_RST_N

PWRGD

RSTIN_NPCIRST_MCH_N

4.7K-ohm

ALDERWOOD

PWRBTN_N

SYS_RESET_N

VRMPWRGD

PWROK

RSMRST_N

CPURST_N

PLTRST_ICH6_N

B B

PWRDWN_N

ICH6

LAN_RST_N

RSM_RST_N

PWR_OK

CK410

SLP_S3_N

SLP_S4_N

SLP_S5_N

Sus_STAT_N

CPU_PWR_GD

PCIRST_N

10K

INI T_N

3.3V

SB_CPU_INIT_N

SLP_S3_N

SLP_S4_N

SUS_STAT_N

CPU_PWR_GD

AND

LOGIC

VTTEN

RESET_N

RESET_N

Voltage

Translation

Logic

Prescott or Tejas

(LGA775 CPU)

INIT_N

ITP_XDP

DBR_N

IDE_RST_N

PCIRST_SIO_FWH_N

PCIRST_1394_N

PCIRST_SLOT_N

VIDPWRGD

PWRGOOD

DBR_RESET_N

PLTRST_MCH_N

VID_GD

VID_PWRGD

CPU_PWR_GD

0-ohm

FP_RESET_N

IDE

RST_N

FWH

RST_N

1394

RST_N PCI 3 2 ( S LO T 1&2& Mi ni P CI )

MCH

CPU_VRD_PWR_GD

VTT_PWRGD

CPU0 VRD

OUTEN

CPU0_VID[5:0]PWR_GD

PLTRST_EXP_SLOT_N PCI EXPRE SS (SLOT # 1)

GPIO_LAN_DIS_N LAN_ENABLE

RSMRST_N

AND

LOGIC

LAN_DIS_N

BCM5721

A A

PS_ON_N PWR_OK PWR_OKPSON_N

Power S upply

5

PS_PWR_GD

BTX_PDG_N

4

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

ABR Block Diagram

Size Document Number R e v

MS-9158

3

2

Date: Sheet of

546Thursday, August 26, 2004

1

0DCustom

5

4

3

2

1

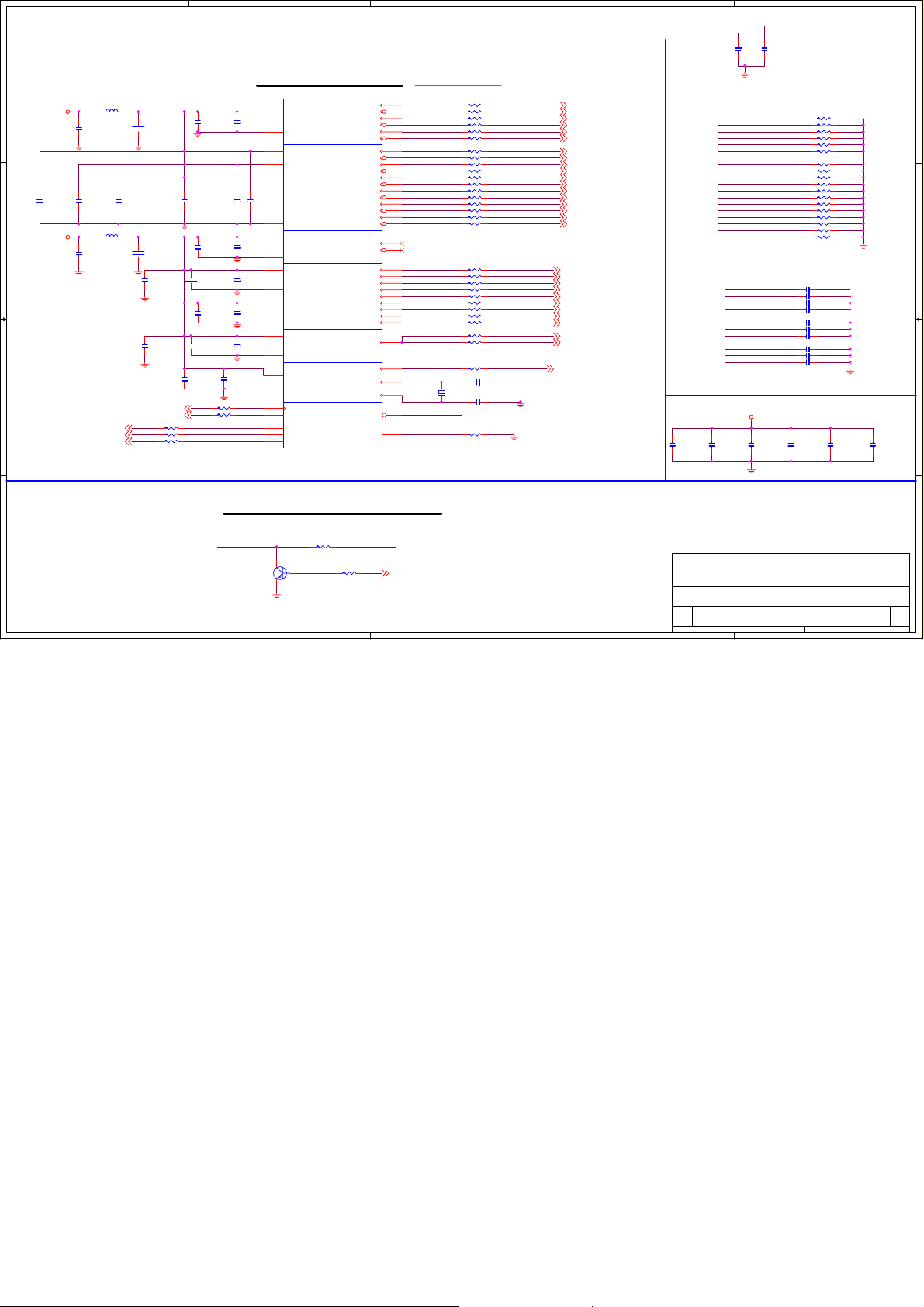

D D

ICH6

BCM

C C

5721 GbE

MS-9158 SMBus Block Diagram

3.3V STBY

R

ICH_SMB*

SMBus

ISOATATION

3.3V

R

DDR CHA

DIMM A1

* Slave Address = 0XA0

DIMM A2

* Slave Address = 0XA2

DDR CHB

DIMM B1

* Slave Address = 0XA4

DIMM B2

* Slave Address = 0XA6

CK410

PCI-Express X16 Slot

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

PCI-Express X1 Slot

HM ADT7463

SMBUS ISOLATE

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

VCC5

VCC5

R

5.1K

PCI 32 / 33 Slot

( SLOT # 1 )

R

5.1K

PCI 32 / 33 Slot

( SLOT # 2 )

B B

A A

Dynamic Bus Addressing fo r I/ O Sl ots

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System SMBus Block Diagram

Size Document Number R e v

MS-9158

5

4

3

2

Date: Sheet of

646Thursday, August 26, 2004

1

0DCustom

5

4

3

2

1

MS-9158 DDRII Routing Block Diagram

D D

DIMMA

CLKP0

CLKN0

CLKP1

CLKN1

CLKP2

CLKN2

CS0

CS2

CKE0

CKE2

ODT0

ODT2

CS1

CS3

CKE1

CKE3

ODT1

ODT3

CLKP3

CLKN3

CLKP4

CLKN4

CLKP5

CLKN5

CS0

CS1

CS2

CS3

C C

B B

ODT0

ODT1

ODT2

ODT3

CKE0

CKE1

CKE2

CKE3

CLKP0

CLKN0

CLKP1

CLKN1

CLKP2

CLKN2

CLKP3

CLKN3

CLKP4

CLKN4

CLKP5

CLKN5

CLKP0

CLKN0

CLKP1

CLKN1

CLKP2

CLKN2

DIMMB

CS0

CS2

ODT0

ODT2

CKE0

CKE2

CS1

CS3

CKE1

CKE3

ODT1

ODT3

CLKP3

CLKN3

CLKP4

CLKN4

CLKP5

CLKN5

Signal

CS0

CS1

CS2

CS3

Signal

CKE0

CKE1

CKE2

CKE3

Relative to

DIMMA1,2

DIMMB1,2

DIMMA3,4

DIMMB3,4

Relative to

DIMMA1,2

DIMMB1,2

DIMMA3,4

DIMMB3,4

DIMM PN

193,76

193,76

193,76

193,76

DIMM PN

52,171

52,171

52

52

*Separate Channel A and B

for clocks

A A

5

A1

4

A2

B1

B2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

DDRII Routing Block Diagram

Size Document Number R e v

MS-9158

3

2

Date: Sheet of

746Thursday, August 26, 2004

1

0DCustom

5

4

3

2

1

D D

MS-9158 INTERRUPT & ERROR LOGIC DIAGRAM

Prescott

Processor

(LGA775)

IERR_N

INIT_N

INTR

C C

F

S

B

B B

MEMORY WRITE ( ALDERWOOD to PROCESSOR )

NMI

SMI_N

CPU0_IERR_N

IGNNE_N

FERR_N

MEMORY WRITE

( ICH6 TO

ALDERWOOD)

FERR_N

IGNNE_N

SMI_N

NMI

INTR

INIT_N

GPI7

DMI

SB_CPU_FERR_N PIRQH_N

SB_CPU_IGNNE_N

ICH_CPU_SMI_N

SB_CPU_NMI

SB_CPU_INTR

SB_CPU_INIT_N

GTL TO 3.3V

TRANSLATION

LOGIC

SB_CPU0_IERR_N

MCH

ALDERWOOD

SIO

SERIRQ

ICH6

IDE IRQ14

IDE Primary

PCI EXPRESS X 1 SLOT

PCI

PIRQF_N

PIRQG_N

PB_PERR_N

PB_SERR_N

PIRQA_N

PIRQB_N

PIRQC_N

PIRQD_N

PIRQE_N

Express

Device # 4

IDSEL = AD25

REQ/GNT # 4

PIRQG_N

PIRQG_N

PIRQH_N

PB_PERR_N

PB_SERR_N

PIRQA_N

PIRQB_N

PIRQC_N

PIRQD_N

PIRQE_N

1394A

Device # 3

IDSEL = AD124

REQ/GNT # 3

Mini PCI-32

SLOT

A

Device # 1

IDSEL = AD22

REQ/GNT # 1

PCI-32 SLOT

B

B

A

Device # 2

IDSEL = AD22

REQ/GNT # 2

PCI-32 SLOT

A

D

C

D

B

C

PCI

Express

A A

5

4

PCI EXPRESS X 16 SLOT

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Interrupt Block Diagram

Size Document Number R e v

MS-9158

3

2

Date: Sheet of

846Thursday, August 26, 2004

1

0DCustom

5

4

3

2

1

MS-9158 HARDWARE MONITOR DIAGRAM

D D

ADT7463 (U25)

CPU VID [ 5 : 0 ]

CPU_TH ERMAL_DIODE

VCORE

C C

B B

A A

VID [ 5 : 0 ]

RTD ( 1

)

VCCP

ALERT#

PWM1

PWM2

PWM3

TACH1

TACH2

TACH3

+3.3V +3.3V

10K 10K

+3.3V

10K

FET

AMP

FET

AMP

FET

AMP

CPU FAN

SYSTEM FAN1

SYSTEM FAN2

FAN1

FAN2

FAN3

HM0_ALERT_N

GPI8

ICH6

INTRUDER_N

intruder switch

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Hardware Monitor Block Diagram

Size Document Number R e v

MS-9158

5

4

3

2

Date: Sheet of

946Thursday, August 26, 2004

1

0DCustom

5

4

3.3V

3

2

1

U1 SIO PC87366

ABR_DISABLE#

D D

GPO

U47 LATTI CE IS P2032E

Wdog_SRST#

RESET SYSTEM

XU1 FWH

FWH1

Primary BIOS

3.3V

FLASH_A20

ID"0000"

RST#

ROM_A20

GPO

C C

3.3V

RST_SIO_FWH_EXP#

XU3 FWH

GPO

BOOT_BLK_REC#

FWH2

BACKUP BIOS

ID"0001"

RST#

3.3V

B B

GPI

ABR_DET

U22 MCH

H_CPURST#

H_CPURST#

(Pin-G23)

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, J ung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Reset Block Diagram

Size Do cu m e n t Num ber R e v

MS-9158

5

4

3

Date : Sheet of

2

10 46Thurs d ay, Augus t 26, 2004

1

0DCustom

5

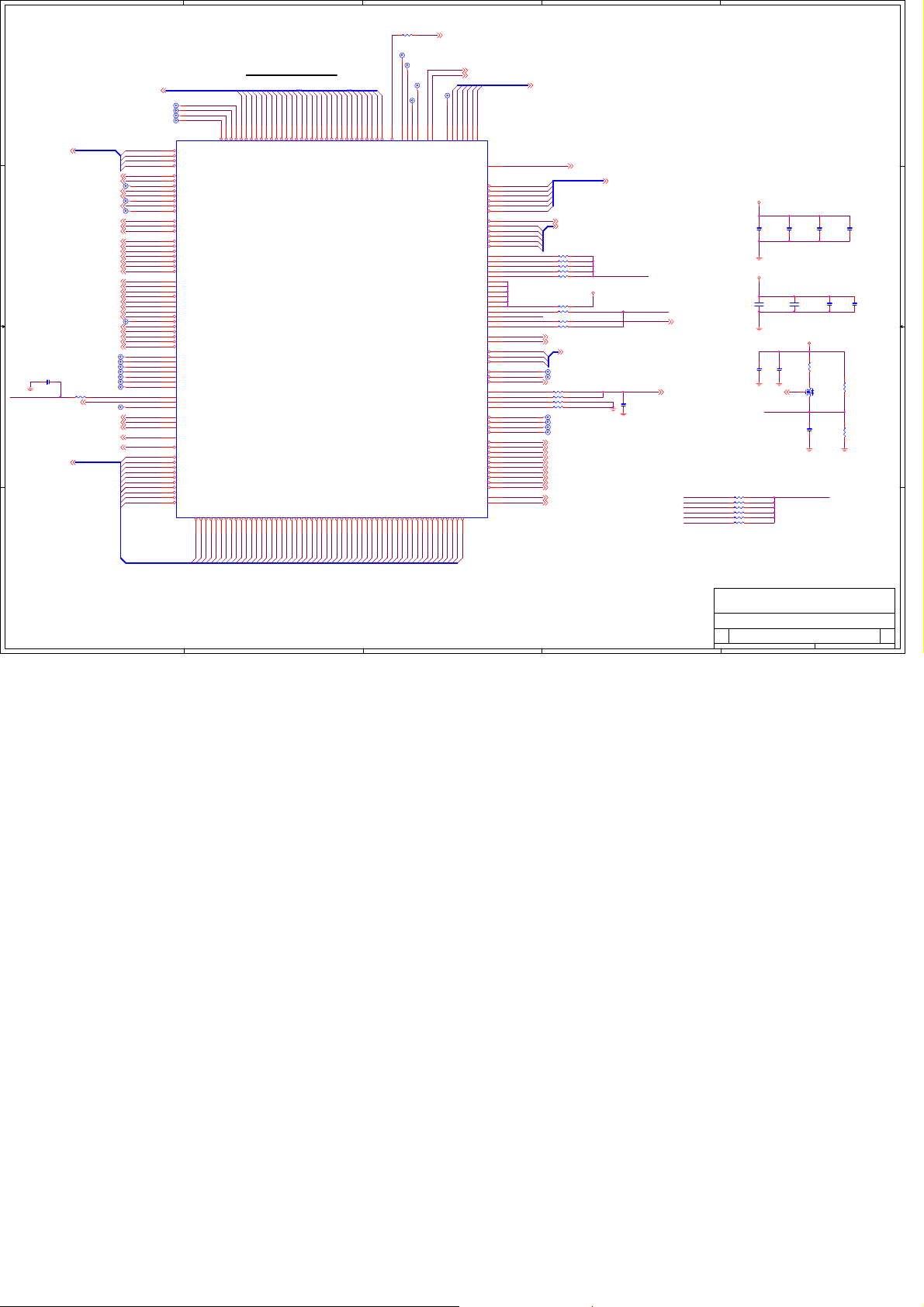

D D

FB6 80-0805-5A

VCC3

CB37

0.1u-25V

C608

C607

1000p-16V

1000p-16V

FB4 80-0805-5A

C C

B B

VCC3

H_FSBSEL012,13,17

H_FSBSEL112,13,17

H_FSBSEL212,13,17

CB36

0.1u-25V

C609

1000p-16V

C152

10u-10V-0805

C126

10u-10V-0805

C611

1000p-16V

C613

1000p-16V

SMB_CLK19,34,42

SMB_DATA19,34,42

R199 10K

R154 10K

C171

0.1u-25V

VCC3VA

C606

1000p-16V

C610

1000p-16V

C517

10u-10V-0805

C612

1000p-16V

C516

10u-10V-0805

C614

1000p-16V

R612 22R

R613 22R

C176

0.1u-25V

SEL0

SEL1

SEL2

C123

0.1u-25V

4

Clock Ge n erat or - C Y28410

42

CPU_VDD

C155

0.1u-25V

45

CPU_GND

CPU2_ITP/SRC7

SRC_VDD

SRC_VDD

SRC_VDD

SRC_GND

VDDA

VSSA

PCI_VDD

PCI_GND

PCI_VDD

PCI_GND

48_VDD

48_GND

REF_VDD

REF_GND

SCLK

SDATA

FSA

FSB/TEST_MODE

FSC/TEST_SEL

CPU2_ITP#/SRC7#

SRC4_SATA

SRC4_SATA#

PCIF0/ITP_EN

VTT_PWRGD#/PD

ICS954101DF

C169

0.1u-25V

C137

0.1u-25V

C151

0.1u-25V

C124

0.1u-25V

C175

0.1u-25V

21

28

34

29

37

38

1

2

7

6

11

13

48

51

46

47

18

16

53

CPU0

CPU0#

CPU1

CPU1#

SRC1

SRC1#

SRC2

SRC2#

SRC3

SRC3#

SRC5

SRC5#

SRC6

SRC6#

DOT96

DOT96#

PCIF1

PCIF2

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

USB_48M

IREF

Trace l ength l ess than 0.5inchs

U16

MCHCLK

44

43

41

40

36

35

19

20

22

23

24

25

26

27

31

30

33

32

14

15

8

9

10

54

55

56

3

4

5

12

52

REF

50

X1

49

X2

17

39

R164 33R

MCHCLK#

R178 33R

R187 33R

CPUCLK

CPUCLK#

R195 33R

R207 33R

ITPCLK

ITPCLK#

R212 33R

R194 33R

CK_PE_SRC1

CK_PE_SRC1#

R201 33R

R211 33R

CK_PE_SRC2

CK_PE_SRC2#

R216 33R

CK_PE_SRC3

R223 33R

R230 33R

CK_PE_SRC3#

CK_PE_SRC4

R256 33R

CK_PE_SRC4#

CK_PE_SRC5

R237 33R

CK_PE_SRC5#

R253 33R

R224 33R

CK_PE_SRC6

CK_PE_SRC6#

R227 33R

PCI clock follow routing direction

PCICLK1

R152 43R

PCICLK0

R163 43R

R172 43R

PCICLK2

PCICLK3

R149 43R

R142 43R

ICHPCLK

FWHPCLK

R135 43R

SIOPCLK

R147 43R

R572 43R

FWHPCLK2 FWH_PCLK2

PERR_ CLK PERR_33MHZ_CLK

R573 43R

SIO48 CK_48M_ICH_SIO

R183 43R

USB48

R181 43R

R155 43R

PLL_XI

Y2

14M-32pf-HC49S-D

PLL_XO

CLK_GD#

IREF

R202 475RSTR191 10K

3

CK_H_MCH

CK_H_ MCH#

CK_H_CPU

CK_H_CPU#

CK_H_ITP

CK_H_ITP#

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

CK_PE_100M_1PORT

CK_PE_100M_1PORT#

CK_PE_100M_MCH

CK_PE_100M_MCH#

CK_ICHSATA

CK_ICHSATA#

CK_PE_100M_ICH

CK_PE_100M_ICH#

CK_PE_100M_LAN

CK_PE_100M_LAN#

PCI_CLK1

PCI_CLK0

1394_33MHZ_CLK

MPCI_CLK

ICH_PCLK

FWH_PCLK

SIO_PCLK

CK_48M_ICH_USB

CK_14M_ICH

22pC130

22pC129

CK_H_MCH 15

CK_H_MCH# 15

CK_H_CPU 12

CK_H_CPU# 12

CK_H_ITP 41

CK_H_ITP# 41

CK_PE_100M_16PORT 22

CK_PE_100M_16PORT# 22

CK_PE_100M_1PORT 26

CK_PE_100M_1PORT# 26

CK_PE_100M_MCH 15

CK_PE_100M_MCH# 15

CK_ICHSATA 24

CK_ICHSATA# 24

CK_PE_100M_ICH 23

CK_PE_100M_ICH# 23

CK_PE_100M_LAN 29

CK_PE_100M_LAN# 29

PCI_CLK1 27

PCI_CLK0 27

1394_33MHZ_CLK 28

MPCI_CLK 26

ICH_PCLK 23

FWH_PCLK 32

SIO_PCLK 33

FWH_PCLK2 43

PERR_33MHZ_CLK 43

CK_48M_ICH_SIO 33

CK_48M_ICH_USB 24

CK_14M_ICH 24

2

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

C528

X_10p

NOPOP NOPOP

C529

X_10p

FOR EMI

CK_H_CPU

CK_H_CPU#

CK_H_MCH

CK_H_ MCH#

CK_H_ITP

CK_H_ITP#

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

CK_PE_100M_1PORT

CK_PE_100M_1PORT#

CK_PE_100M_MCH

CK_PE_100M_MCH#

CK_ICHSATA

CK_ICHSATA#

CK_PE_100M_ICH

CK_PE_100M_ICH#

CK_PE_100M_LAN

CK_PE_100M_LAN#

09/01 ADD C156

1394_33MHZ_CLK

PCI_CLK1

PCI_CLK0

MPCI_CLK

ICH_PCLK

FWH_PCLK

SIO_PCLK

CK_48M_ICH_USB

CK_48M_ICH_SIO

FWH_PCLK2

EMC HF filter capacitors, located close to PLL

VCC3

C143

C194

X_0.1u-25V

NOPOP NOPOP NOPOP

0.1u-25V

C119

0.1u-25V

1

R188 49.9RST

R196 49.9RST

R165 49.9RST

R179 49.9RST

R208 49.9RST

R213 49.9RST

R193 49.9RST

R200 49.9RST

R210 49.9RST

R215 49.9RST

R222 49.9RSTR249 33R

R229 49.9RST

R248 49.9RST

R255 49.9RST

R238 49.9RST

R254 49.9RST

R225 49.9RST

R228 49.9RST

X_10pC146

X_10pC134

X_10pC140

X_10pC132

X_10pC128

X_10pC125

X_10pC131

10pC150

10pC156

X_10pC493

NOPOP

NOPOP

NOPOP

NOPOP

NOPOP

NOPOP

NOPOP

NOPOP

Please close to U1 6 as possible

C139

X_0.1u-25V

C122

0.1u-25V

C190

X_0.1u-25V

Clock Generator VTT Power Down Bl ock

A A

2N3904S

5

R184 10K

Q22

VTTGD

4

R232 10K

VCC3VACLK_GD#

VTT_GD 37,39

Micro-Star Int'l Co., Ltd.

No.69, L i - D e S t, J ung-He City, Taipei Hsien, Taiwan. ht tp://www.m si.com.tw

Title

CK410-CY28410

Size Docu m ent Number Re v

MS-9158

3

Dat e: Sheet

2

11 46Thursday , September 02, 2004

1

0DCustom

of

5

4

3

2

1

R364 0R-0402

CPU SIGNAL BLOCK

D D

H_DBI#[0..3]

H_DBI#[0..3]15

H_ED RDY#15

H_IERR#13,33

H_FERR#23

H_STPCLK#23

H_INIT#23

H_DBSY#15

H_DRDY#15

H_TRDY#15

H_ADS#15

C C

C303 X_ 0.1u-25V

VTT_OUT_RIGHT

B B

A A

H_LOCK#15

H_BNR#15

H_HIT#15

H_HITM#15

H_BPRI#15

H_DEFER#15

H_TDI41

H_TDO41

H_TMS41

H_TRST#41

H_TCK41

THRMDA34

THRMDC34

TRMTRIP#23

H_PROCHOT#13

H_IGNNE#23

ICH_H_SMI#23

H_A20M#23

H_SLP#23

NOPOP

R365 X_62R

LL_ID037

H_FSBSEL011,13,17

H_FSBSEL111,13,17

H_FSBSEL211,13,17

H_PWRGD13,23,41

H_CPURST#13,15,41,43

H_D#[0..63]15

NOPOP

LL_ID0

H_D#[0..63]

H_A#[3..31]15

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

TP46

TP51

TP35

TP45

TP55

TP38

TP47

TP22

TP18

TP9

CPU_BOOT

TP48

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_D#[0..63]

TP54

TP50

TP49

TP52

A8

G11

D19

C20

F2

AB2

AB3

R3

M3

AD3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AD1

AF1

AC1

AG1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

AH2

N5

AE6

C9

G10

D16

A20

Y1

V2

AA2

G29

H30

G30

N1

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

H_A#[3..31]

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

H_A#17

H_A#18

H_A#16

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D31#

D30#

D29#

F15

G15

G14

H_D#30

H_D#31

H_D#29

H_A#9

H_A#11

H_A#12

H_A#15

H_A#14

H_A#13

AC2

L5

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

DBR#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

F14

F12

F11

E13

D13

G13

H_D#24

H_D#23

H_D#27

H_D#26

H_D#28

H_D#25

D14#

E10

D10

D11

C12

H_D#19

H_D#14

H_D#22

H_D#20

H_D#15

H_D#17

H_D#16

H_D#21

H_D#18

H_A#24

H_A#28

H_A#31

H_A#29

H_A#30

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

A35#

A34#

A33#

A32#

A31#

A30#

A29#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

F21

A14

E22

C14

H_D#52

E21

C15

D17

D20

D22

G22

G21

H_D#44

H_D#46

H_D#49

H_D#48

H_D#45

H_D#51

H_D#47

H_D#50

H_D#42

H_D#43

H_A#19

H_A#25

H_A#20

H_A#21

H_A#23

H_A#26

H_A#22

H_A#27

AF4

AF5

AB4

AC5

AB5

AA5

AD6

AA4

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#Y4A19#Y6A18#W6A17#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

F20

H_D#41

D32#

F18

F17

E19

E18

E16

E15

G17

G18

G16

H_D#32

H_D#35

H_D#33

H_D#40

H_D#36

H_D#39

H_D#34

H_D#38

H_D#37

H_A#4

H_A#10

H_A#7

H_A#8

H_A#6

H_A#5

H_A#3

TP100

B12

H_D#13

FP_RST# 24,41,43

TP101

TP57

TP60

AN3

AN5

AN6

AN4

RSVD

RSVD

VSS_SENSE

VCC_SENSE

D13#

D12#D8D11#

D10#

D9#

B10

A11

C11

H_D#10

H_D#9

H_D#12

H_D#11

AJ3

AK3

ITP_CLK1

ITP_CLK0

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

H_D#8

H_D#5

H_D#7

H_D#6

TP58

H_D#4

VID5

AL4

AM5

VID6

H_D#2

H_D#3

ITP_CLKOUT# 41

ITP_CL KO UT 41

VID4

VID3

VID2

AK4

AL6

AM3

VID5#

VID4#

VID3#

GTLREF0

PCREQ#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

B4

H_D#0

H_D#1

VID1

AL5

VID2#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

RSVD

RSVD

BCLK1#

BCLK0#

COMP3

COMP2

COMP1

COMP0

TEJAS

VID[0..5]

VID[0..5] 34,37

VID0

AM2

U22A

VID1#

VID0#

H1

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

H_PCREQ#

G5

H_REQ#4

J6

H_REQ#3

K6

H_REQ#2

M6

H_REQ#1

J5

H_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

RSVD_AK6

AK6

RSVD_G6

G6

G28

F28

H_RS#2

A3

RS2#

H_RS#1

F5

RS1#

H_RS#0

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

CPU_GTLREF 13

H_BPM#[0..5]

H_PCREQ# 15

H_REQ#[0..4] 15

R361 62R-0402

R358 62R-0402

R352 62R-0402

R355 62R-0402

R353 62R-0402

V_FSB_VTT

R276 62R-0402

R362 62R-0402

R522 X_62R-0402

R350 X_62R-0402

CK_H_CPU# 11

CK_H_CPU 11

H_RS#[0..2] 15

TP43

TP44

H_BR#0 13,15

R359 100RST-0402

R349 100RST-0402

R360 60.4RST-0402

R305 60.4RST-0402

TP23

TP19

TP24

TP21

H_ADSTB#1 15

H_ADSTB#0 15

H_DSTBP#3 15

H_DSTBP#2 15

H_DSTBP#1 15

H_DSTBP#0 15

H_DSTBN#3 15

H_DSTBN#2 15

H_DSTBN#1 15

H_DSTBN#0 15

H_NMI 23

H_INTR 23

H_BPM#[0..5] 41

VTT_O UT_LEFT

VTT_O UT_LEFT

VTT_OUT_RIGHT

NOPOP

NOPOP

VTT_O UT_LEFT

C302

X_0.1 u-25V

NOPOP

Place r esistor outside socket cavity. If no room

for variable resistor, then don't place

VTT_OUT_RIGHT 13,37,39,41

VTT_O UT_LEFT 13

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

V_FSB_VTT

V_FSB_VTT

R533 49.9RST

R532 49.9RST

R531 49.9RST

R530 49.9RST

R528 49.9RST

R526 49.9RST

C519

0.1u-25V

C202

10u-10V-1206

C665

0.01u

GTL_DET14,15

H_TESTHI0

C520

0.1u-25V

C203

10u-10V-1206

VCC3

C666

0.1u-25V

VTT_OUT_RIGHT

R565

249RSTTP33

Q66

2N7002E

C488

0.1u-25V

C521

0.1u-25V

C204

0.1u-25V

C522

0.1u-25V

C205

0.1u-25V

R265

110RST-0402

R560

61.9RST-0402

PLACE BPM TERMINATION NEAR CPU

Micro-Star Int'l Co ., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Intel LGA775 Si gn al B lo ck

Size Doc u men t Numbe r Re v

MS-9158

5

4

3

2

Date: Sheet of

1

0DCustom

12 46Thursday, September 02, 2004

5

VCORE

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

VCORE

D D

C C

AF21

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AF19

VCC

AF18

VCC

AF15

VCC

AF14

VCC

AF12

VCC

AF11

VCC

AE9

VCC

AE23

VCC

AE22

VCC

AE21

VCC

AE19

VCC

AE18

VCC

AE15

VCC

AE14

VCC

AE12

VCC

AE11

VCC

AD8

VCC

AD30

VCC

AD29

VCC

AD28

VCC

AD27

VCC

AD26

VCC

AD25

VCC

AD24

VCC

AD23

VCC

AC8

VCC

AC30

VCC

AC29

VCC

AC28

VCC

AC27

VCC

AC26

VCC

AC25

VCC

AC24

VCC

AC23

VCC

AB8

VCC

AA8

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y23

Y24

Y25

Y26

Y27

Y28

Y29

VCORE

Y30

W23

W24

W25

W26

W27

W28

W29

W30

4

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

VCC

VCC

VCC

VCC

U28

U29

U30

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

VCC

VCC

U23

U24

U25

U26

U27

T23

T24

T25

T26

T27

T28

T29

T30

N23

N24

N25

N26

N27

N28

N29

N30

M26

M27

M28

M29

M30

3

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

K30

M23

M24

M25

J11

J12

J13

J14

J15

J18

J19

J20

J21

AM9

AN11

AN12

AN14

AN15

AN18

VCC

VCC

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VTT_OUT_LEFT

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

J10

AN8

AN9

AN26

AN29

AN30

AN19

AN21

VCC

VCC

VCC-IOPLL

VTTPWRGD

VCC

AN25

2

AN22

VCC

VTT_SEL

VCCA

VSSA

RSVD

TEJAS

1

U22B

H_VCCA

A23

H_VSSA

B23

D23

H_VCCIOPLL

C23

A25

VTT

A26

VTT

A27

VTT

A28

VTT

A29

VTT

A30

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTT

B30

VTT

C25

VTT

C26

VTT

C27

VTT

C28

VTT

C29

VTT

C30

VTT

D25

VTT

D26

VTT

D27

VTT

D28

VTT

VCCFUSEPRG

D29

VTT

VIDFUSEPRG

D30

VTT

AM6

VTT_ OUT_RIGHT

AA1

VTT_OUT_ LEFT

J1

F27

F29

R269

R267

0R-0402

0R-0402

VTT_PWR 39

R264 X_1K-0402

NOPOP

VTT_SEL

TEJ/PSC

0

1

RSVD

V_FSB _VTT

VCC3

V_FSB _VTT

B B

DC voltage drop should

be less than 70mV.

A A

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

It support DC current if 100m A.

L11 10uH-0805-0.1A

R277 X_0R-0402

NOPOP NOPOP

L12 10uH-0805-0.1A

R291 X_0R-0402

NOPOP

TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12 MILS

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

V_FSB _VTT

AND CEDAR MILL ARE SUPPORTED

5

R534

0R-0402

R261 470R

R260 470R

R262 470R R270 62R-0402

C223

X_1u-10V

EC17

22u-6.3V-1206

H_FSBSEL1

H_FSBSEL2

EC18

10u-10V-1206

H_FSBSEL0 11,12,17

H_FSBSEL1 11,12,17

H_FSBSEL2 11,12,17

4

H_VCCIOPLL

H_VSSA

C224

X_1u-10V

H_VCCA

NOPOP

VTT_O UT_RIGHT12,37,39,41

VTT_OUT_ LEFT12

VTT_ OUT_RIGHT

R354

100 OHMS OVER 210 OHMS RESISTORS

100RST

R356

210RST

C299

1u-10V

C301

220p-16V-0402

Place at CPU end of routing

VTT_ OUT_RIGHT H_PROCHOT#

VTT_OUT_ LEFTH_FSBSEL0

3

R375 X_120R-0402

R357 62R

R347 62R

R367 62R-0402

NOPOP

H_PWRGD

H_BR#0

H_CPURST#

CPU_GTLREF 12

GTLREF VOLTAGE SHOULD BE

0.67*VTT = 0.8V

H_PROCHOT# 12

H_PWRGD 12,23,41

H_BR#0 12,15

H_CPURST# 12,15,41,43

H_IERR# 12,33

2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Intel LGA775 Power

Size Document Number Re v

MS-9158

Date: Sheet of

13 46Thursday, September 02, 2004

1

0DCustom

5

TP64

TP65

TP67TP66

4

3

2

1

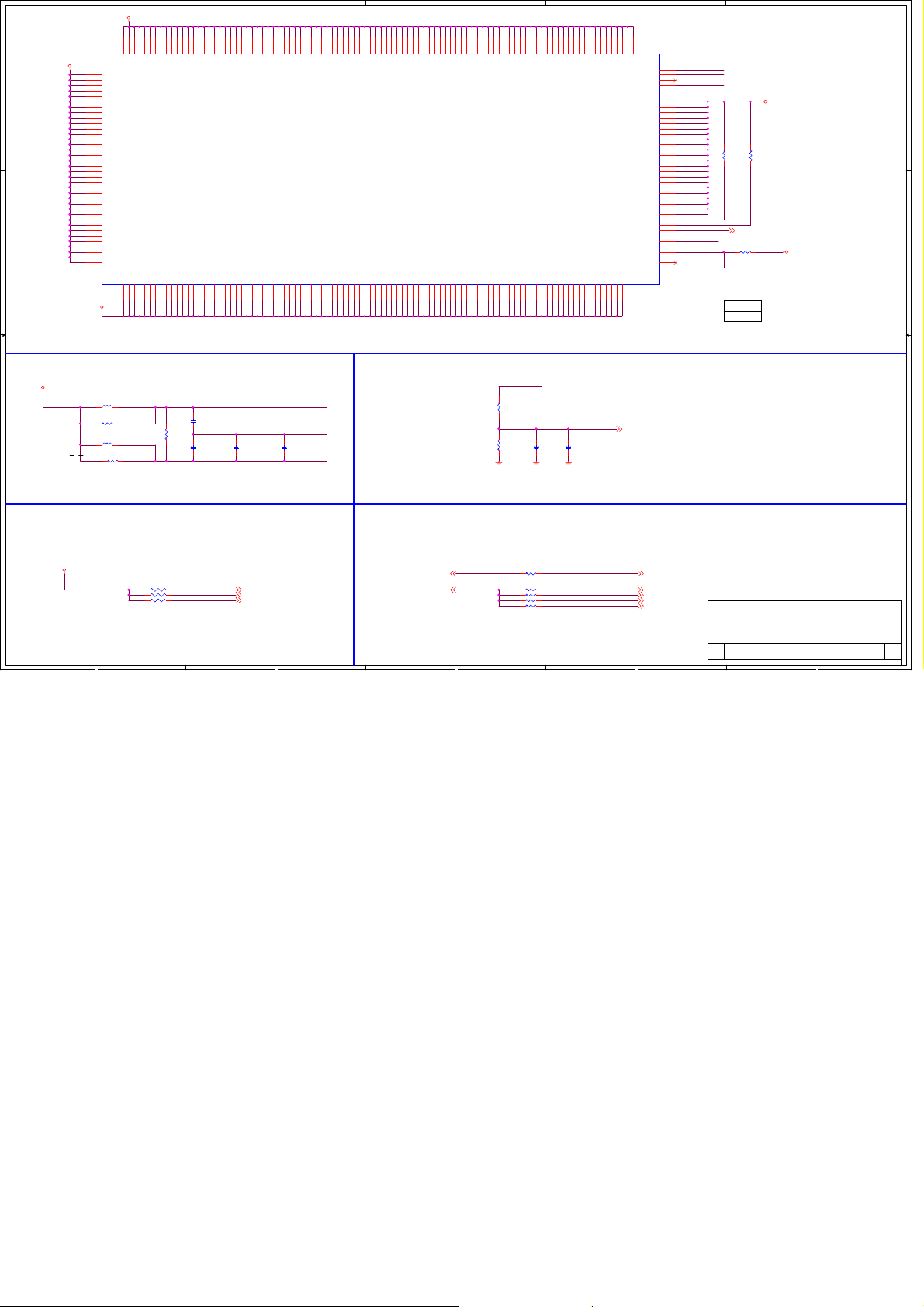

GTL_DET 12 , 15

D D

H29

H25

H26

H27

V30

V29

V28

V27

V26

V25

V24

AC4

AE3

AE4

D14

E23

E24

F23

B13

P5

Y3

J2

T2

H2

RSVD

RSVD

RSVD

RSVDD1RSVD

RSVD

RSVD

RSVDE5RSVDE6RSVDE7RSVD

RSVDF6RSVD

RSVDJ3RSVDN4RSVD

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

AA23

VSS

AA24

VSS

AA25

VSS

AA26

VSS

AA27

VSS

C C

B B

A A

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

VSS

VSS

AA3

VSS

VSS

AA6

VSS

AA7

VSS

AB1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB7

VSS

AC3

VSS

AC6

VSS

AC7

VSS

AD4

VSS

AD7

VSS

VSS

VSS

VSS

VSS

AE2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE5

AE7

AF10

AF13

AF16

AF17

AE29

AE30

COMP4

GTLREF1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF20

AF3

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF30

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

RSVDV1RSVDW1RSVD

COMP5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF6

AF7

AG10

AH1

AG7

AH10

AH13

AH16

AG13

AG16

AG17

AG20

AH17

AG23

AG24

V23

VSSV3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AJ10

AJ13

AH20

AH23

AH24

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

R30

R29

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AJ28

AJ29

AK2

AJ30

AK10

AK13

AK16

AK17

AK5

AK7

AK20

AK23

AL10

AK24

AK27

AK28

AK29

AK30

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL13

AL16

AL17

AL20

AL23

AL24

L30

L29

L28

VSSL3VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AM1

AL27

AL28

K2

L27

L26

L25

L24

L23

K5

VSS

VSS

VSS

VSS

VSS

VSS

VSSK7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

H28

VSS

VSS

VSS

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

GTLREF_SEL

VSS

VSS

VID7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN1

AN2

AM4

AM7

AN10

AN13

AN16

AN17

AN20

AN23

AN24

TP68 TP69

Title

Size Document Number Re v

5

4

3

2

Date: Sheet

H17

H18

H19

H20

H21

H22

H23

H24

VSS

VSS

VSS

VSS

AN27

AN28

U22C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VID_SELECT

VSSB1VSS

AN7

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City , Taipei Hsien, Taiwan. http://www.msi.com.tw

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

VSS

TEJAS

B11

B14

Intel LGA775 GND

MS-9158

14 46Thursd ay , S ept ember 02, 2004

1

0DCustom

of

Loading...

Loading...