MSI MS-9154 lindy_012104

A B C

REV

D

REVISIONS

DESCRIPTIONECO DATE

APPROVED

1

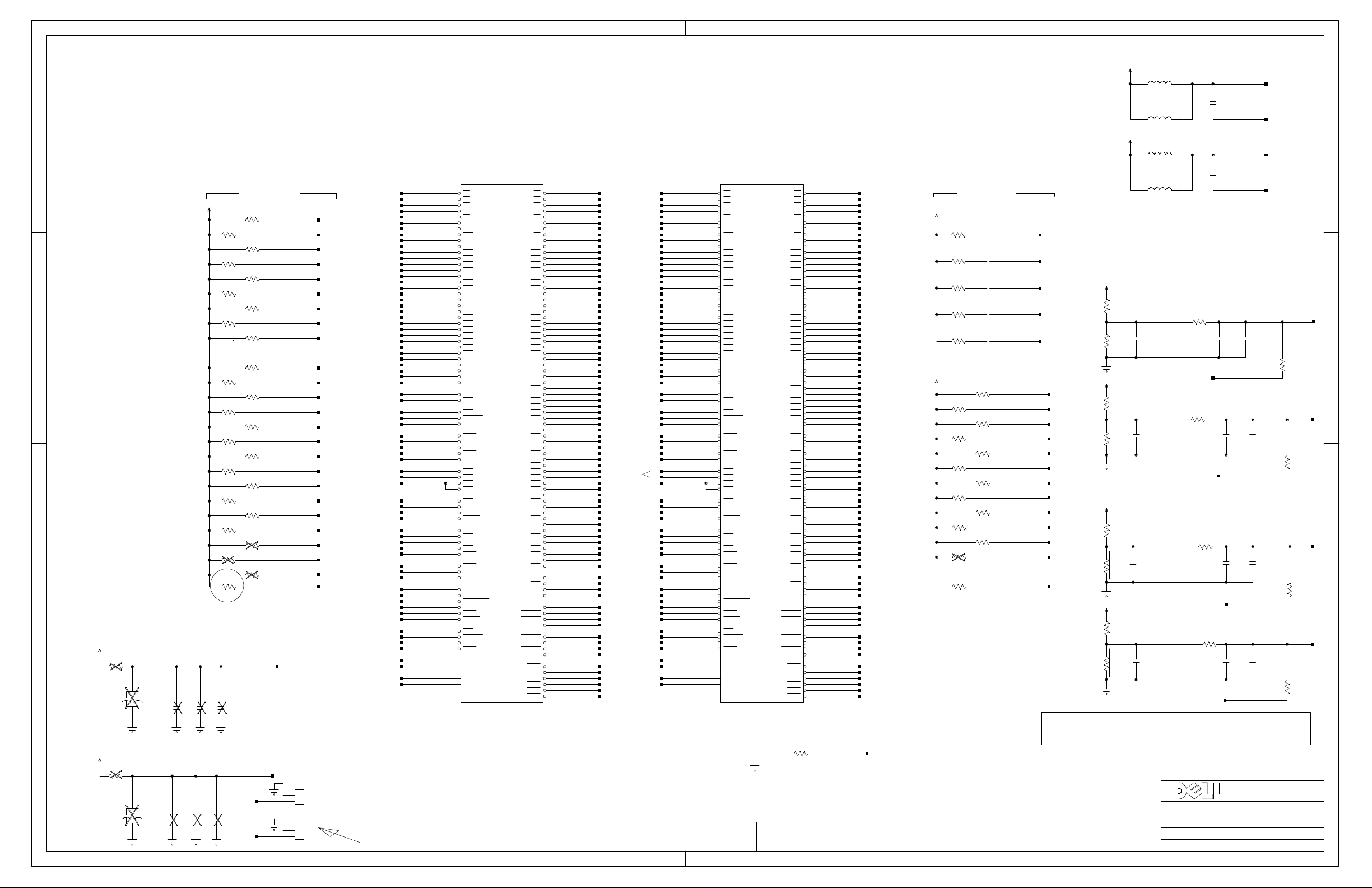

Planar

CPU1

Serial Port

USB 2.0

CPU0

PWB PN: D1656

PWA PN: H1754

(2)

(Nocona/

Jayhawk)

System

Kbd/Mse

Kbd/Mse

H

D

2

M

FLOPPY

USB

C

o

IDE

n

n

VIDEO

87373

CPLD

LPC Bus

ICH5

Video

DVI

Hublink 1.5

PCI 33MHz

USB

(6.4GB/s, 6.4GB/s)

800 MHz

Lindenhurst

MCH

A

C

s

/

B

G

4

ESM 4G RAC

LPC

Smart

3

VU

Firmware

Hub

ESM

BMC

ATI

Video

(RADEON)

Connector

PCI 33MHz

PCI 33MHz

,

X

8

X

e

I

C

P

PCIeX 8X, 4GB/s

(Nocona/

Jayhawk)

1U/2U/5U

DDR2 400 Ch. A (6.4Gb/s)

B-

B-

hi

lo

PCIeX 4X

PCIeX 4X, 2GB/s

PCI 33MHz

2GB/s

V1.8 - 5/22/03

DDR2 400 Ch. B (6.4GB/s)

32/66MHz

PXH

32/66MHz

D

D

I

I

M

M

M

M

3

2

A

A

TABOR

TABOR

D

I

M

M

1

A

D

D

D

I

I

I

M

M

M

M

M

M

3

2

1

B

B

B

Gbit Port 1#

Gbit Port 1#

IPMB

HS3 Connector

PCI Microchannel

TABLE OF CONTENTS

Page 1.

Page 2.

Page 3.

Page 4.

Page 5.

Page 6.

Page 7.

Page 8.

Page 9.

Page 10.

Page 11.

Page 12.

Page 13.

Page 14.

Page 15.

Page 16.

Page 17.

Page 18.

Page 19.

Page 20.

Page 21.

Page 22.

Page 23.

Page 24.

Page 25.

Page 26.

Page 27.

Page 28.

Page 29.

Page 30.

Page 31.

Page 32.

Page 33.

Page 34.

Page 35.

Page 36.

Page 37.

Page 38.

Page 39.

Page 40.

Page 41.

Page 42.

Page 43.

Page 44.

Page 45.

Page 46.

Page 47.

Page 48.

Page 49.

Page 50.

Page 51.

Page 52.

Page 53.

Page 54.

Page 55. FWH

Page 56.

Page 57.

Page 58.

Page 59.

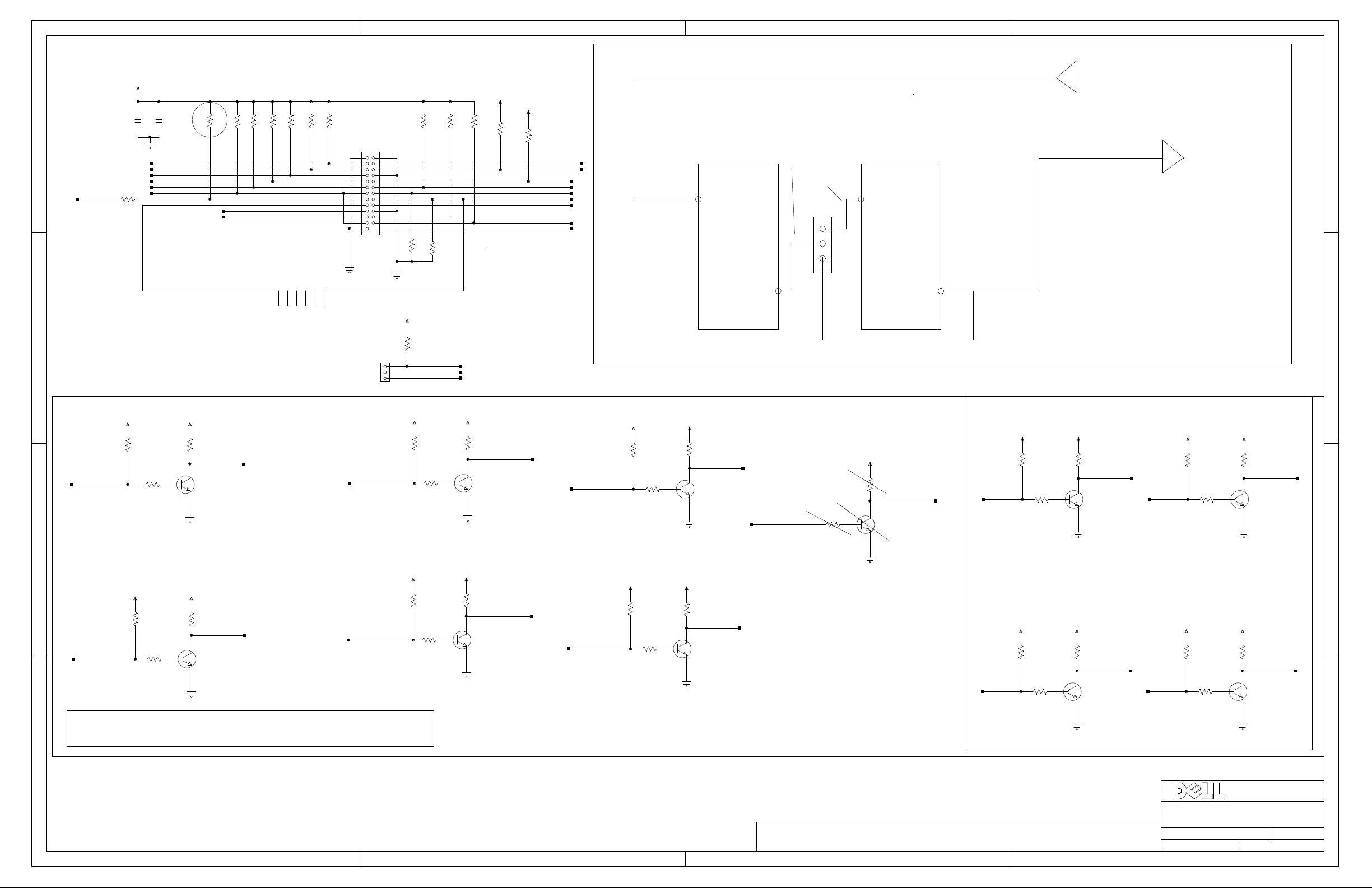

BLOCK DIAGRAM

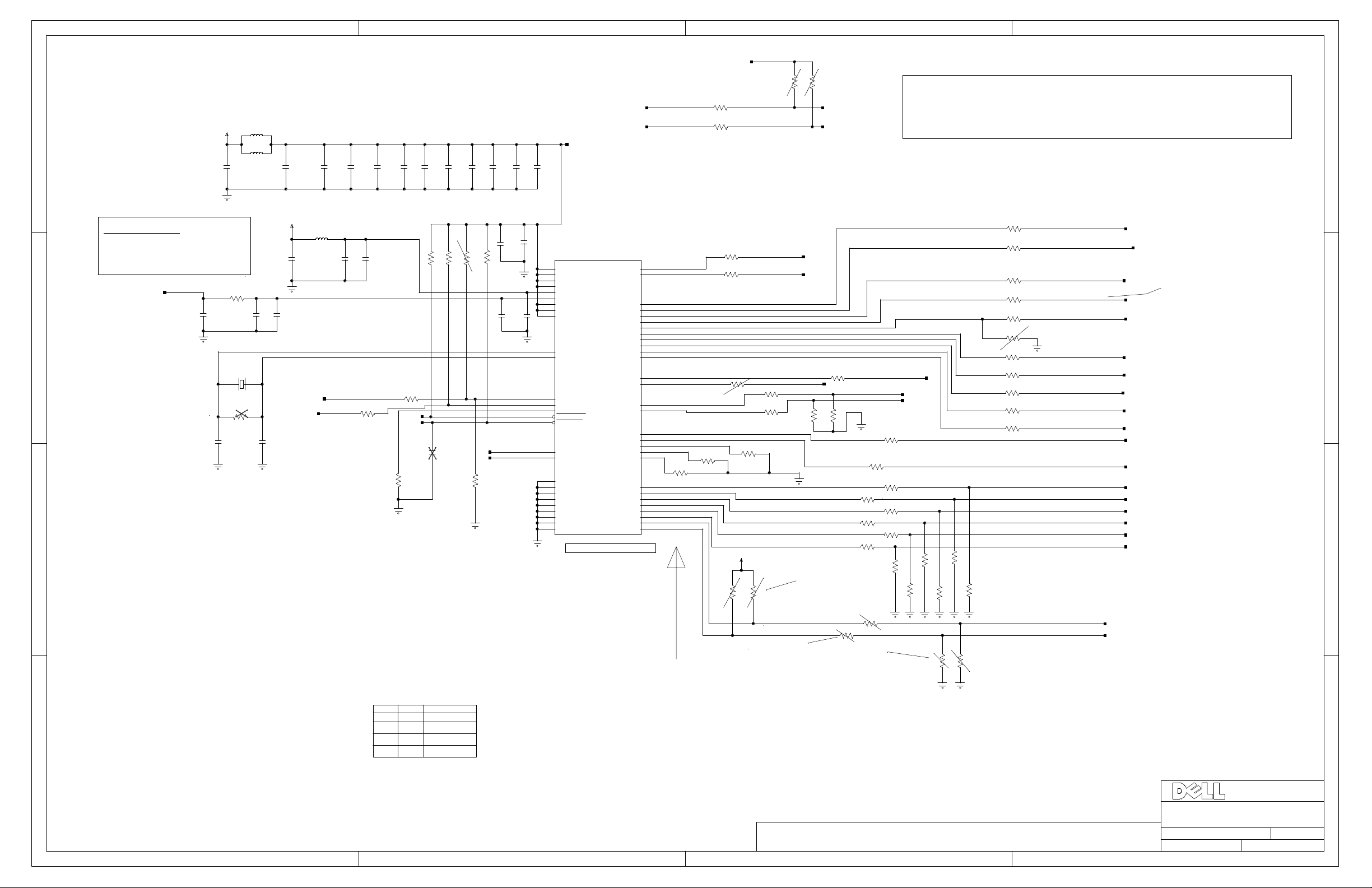

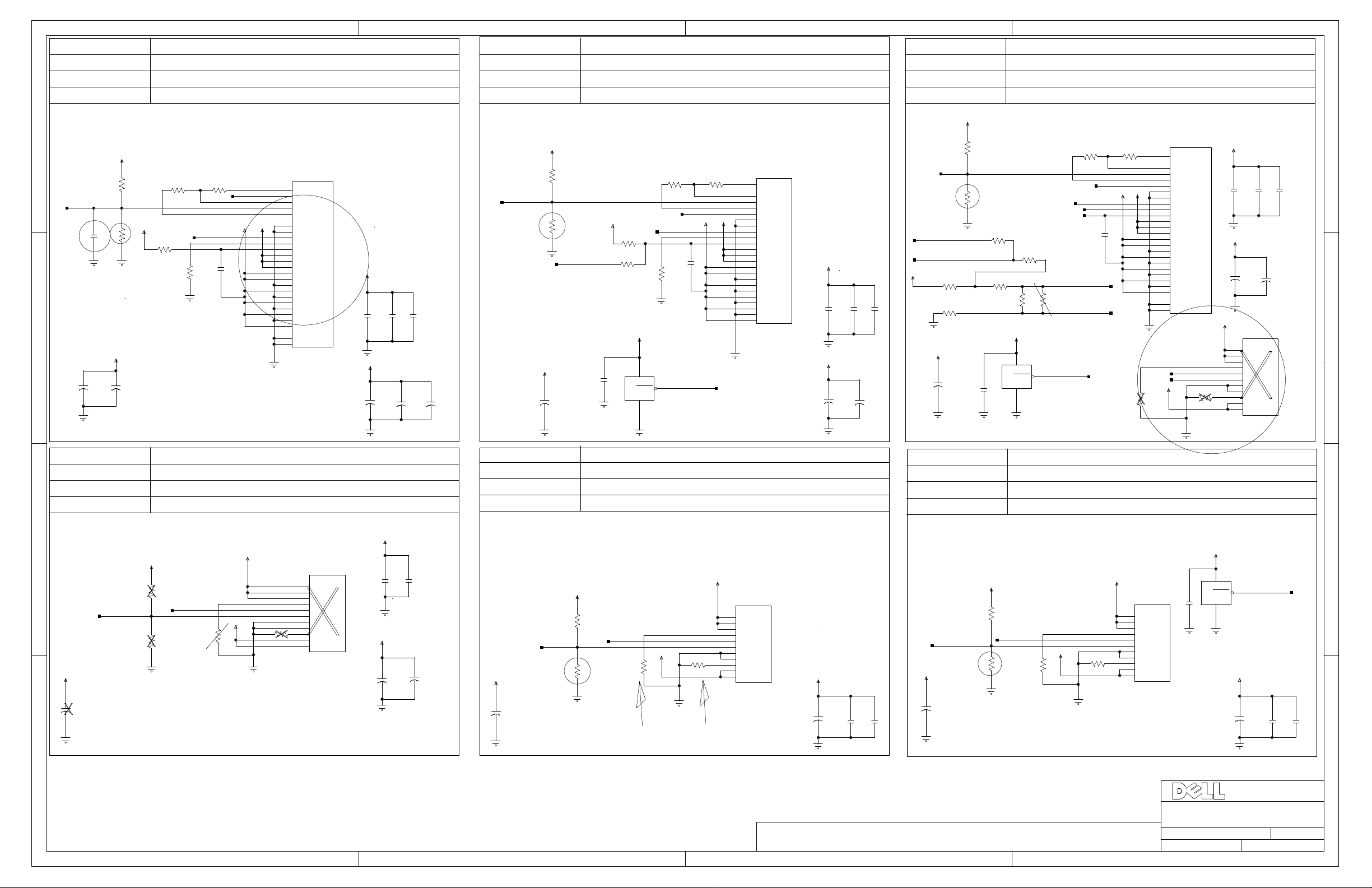

CLOCK DIAGRAM

Clock Synth.

Differential Buffer DB800

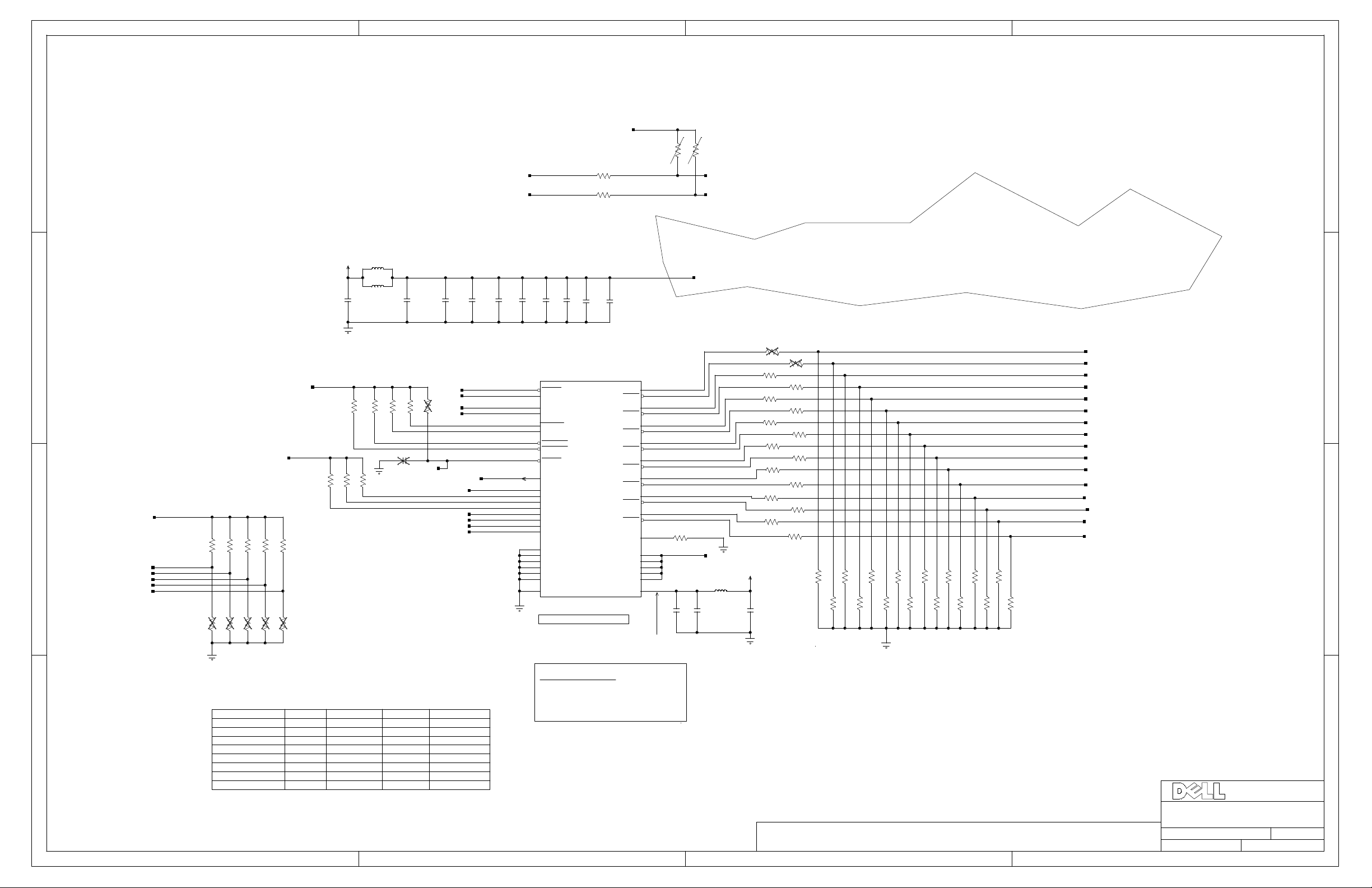

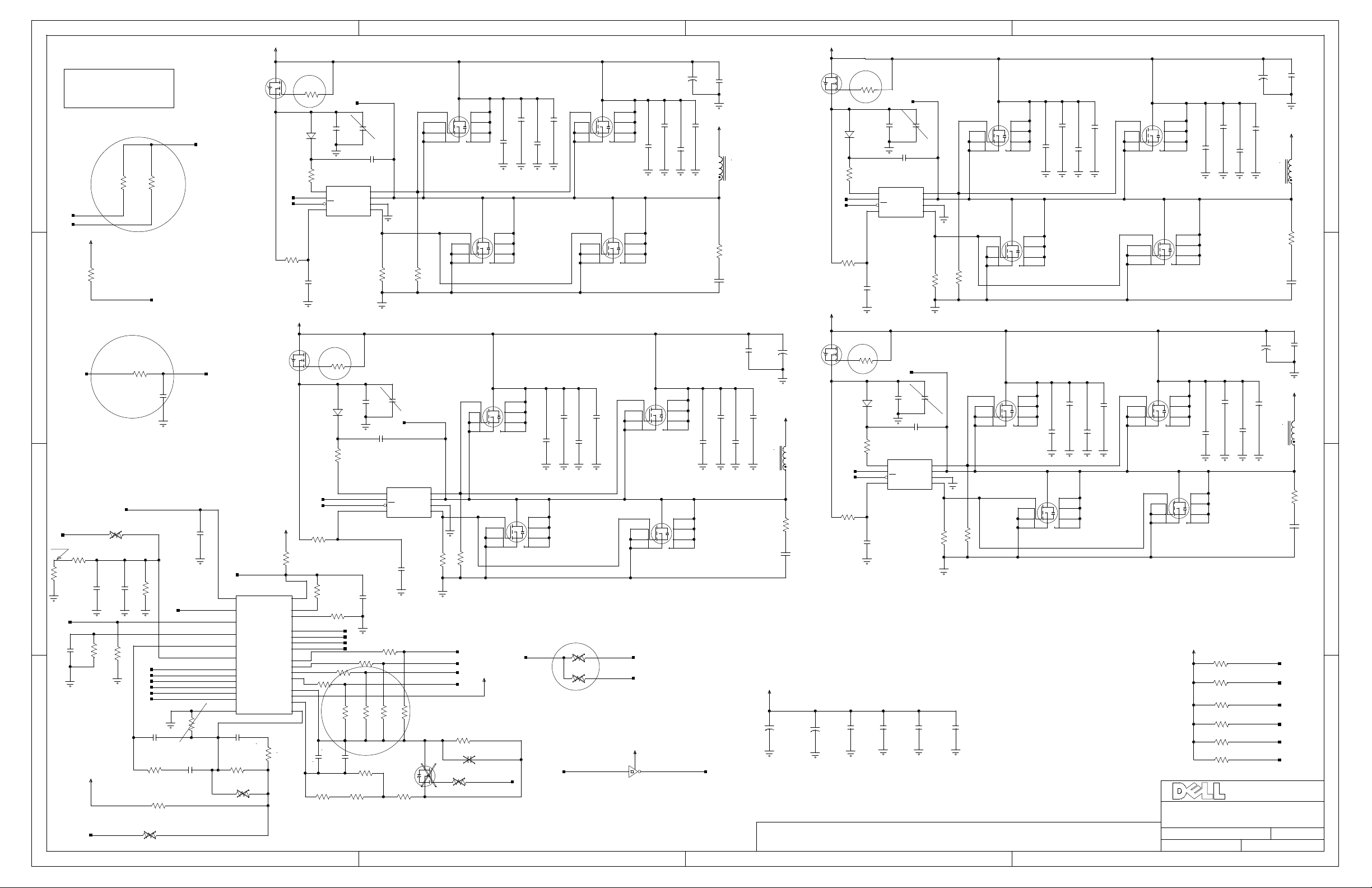

System CPLD

Voltage Regulators

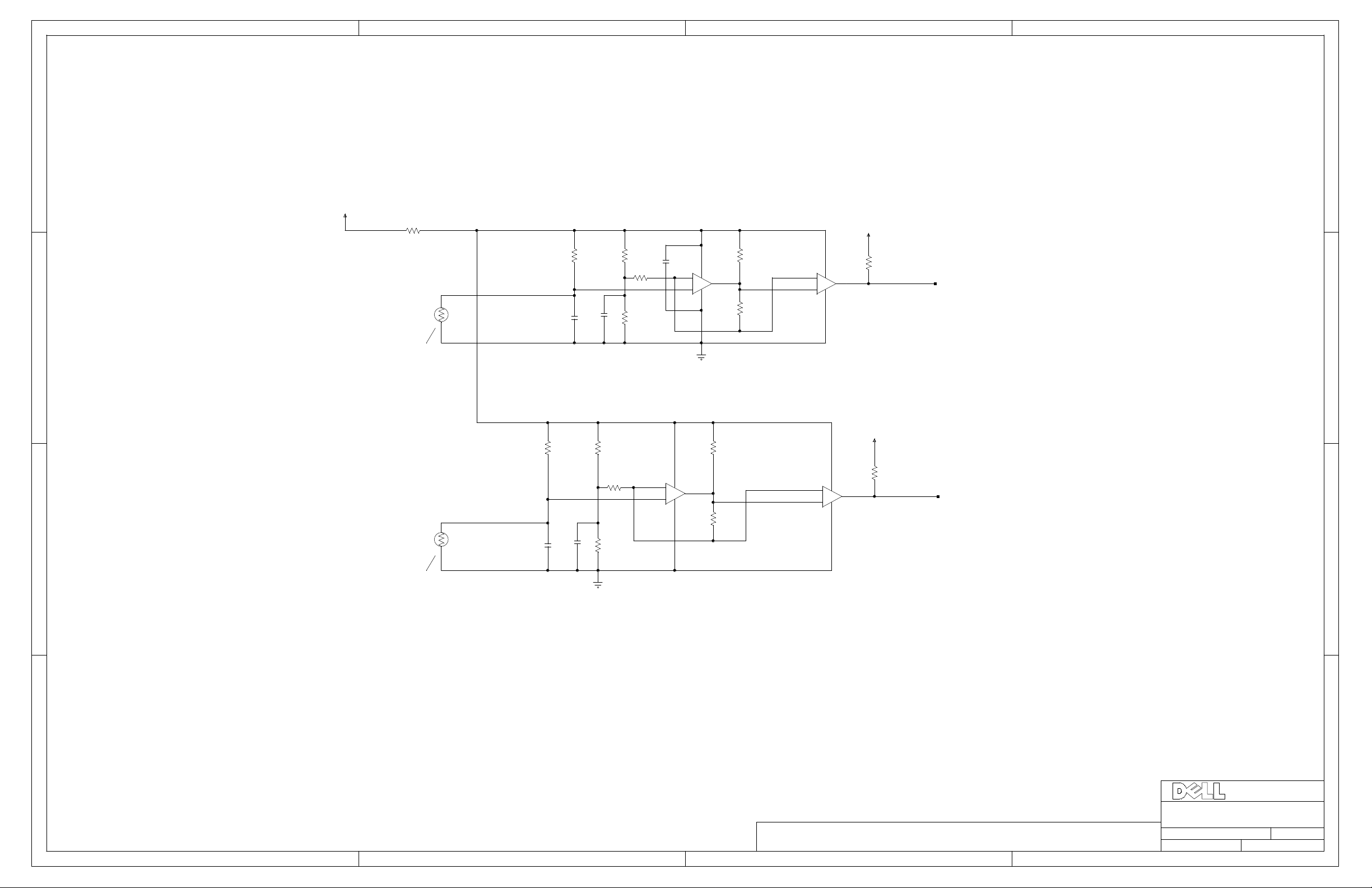

VRD

VRD

VRD

---blank--Processors

Processors

Processors

---blank--ITP 32 & Level Translation Circuits

MCH, memory

MCH, GTL, Exp, Hub-link

MCH, power

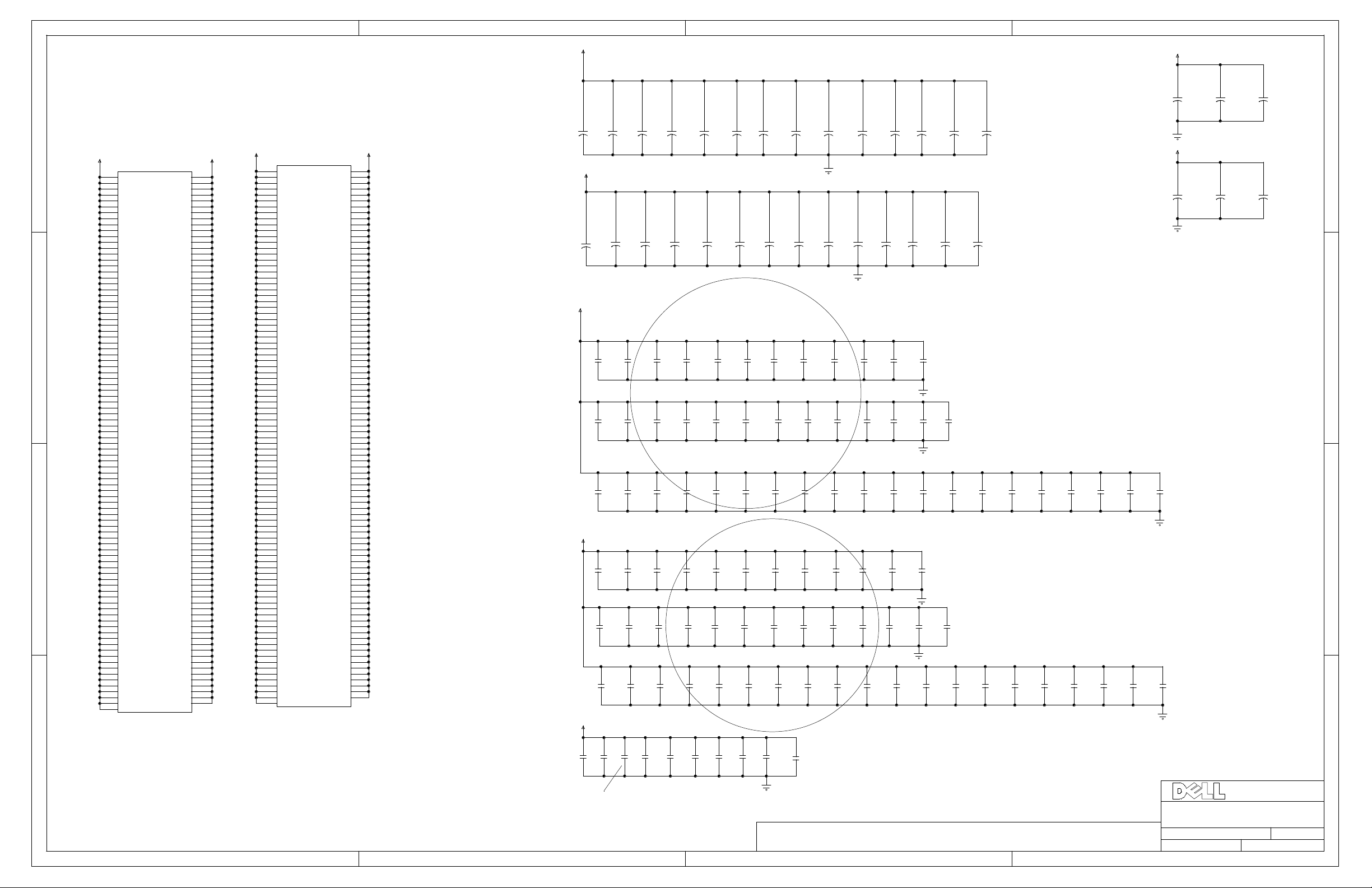

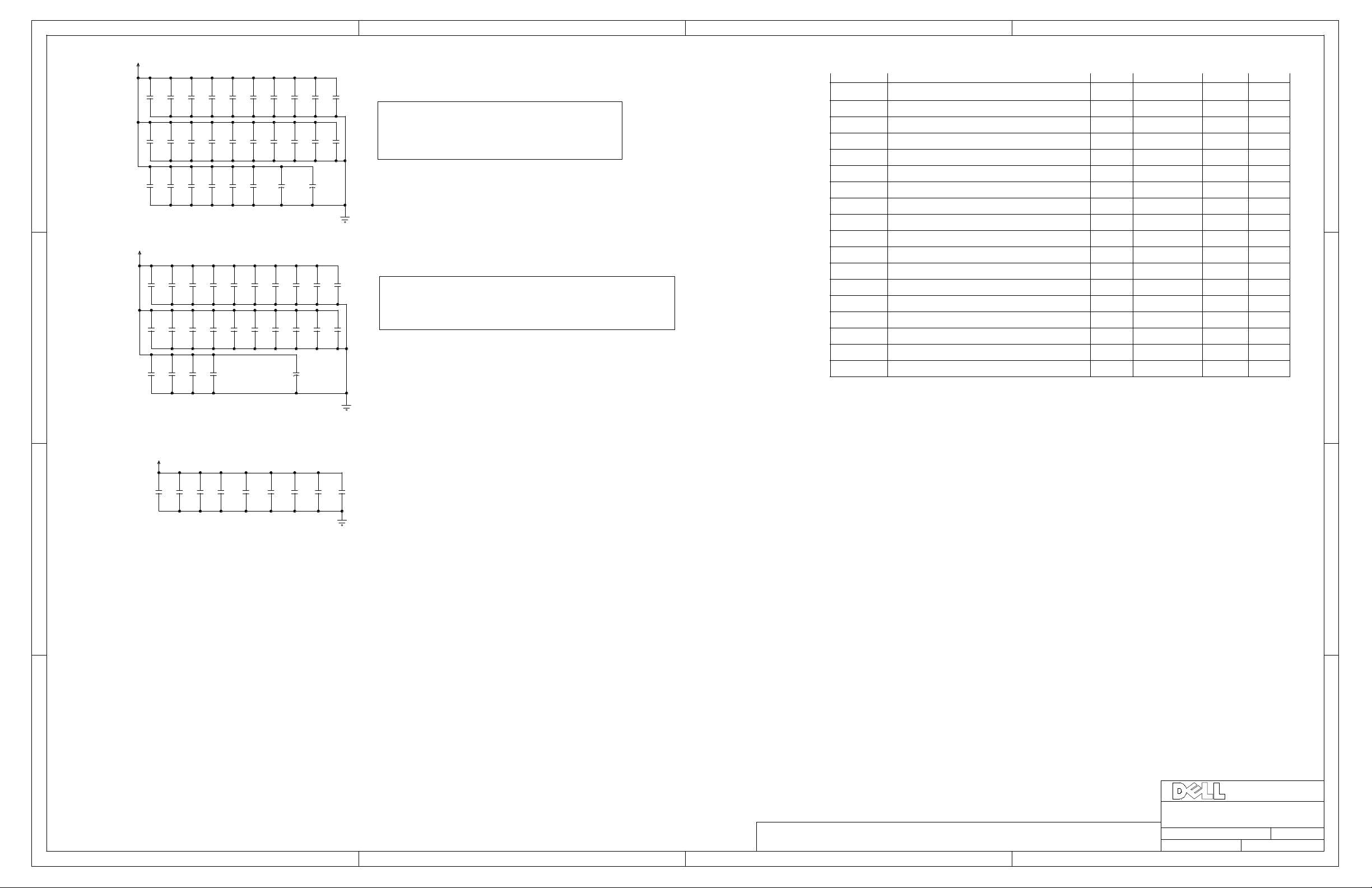

Decoupling Caps

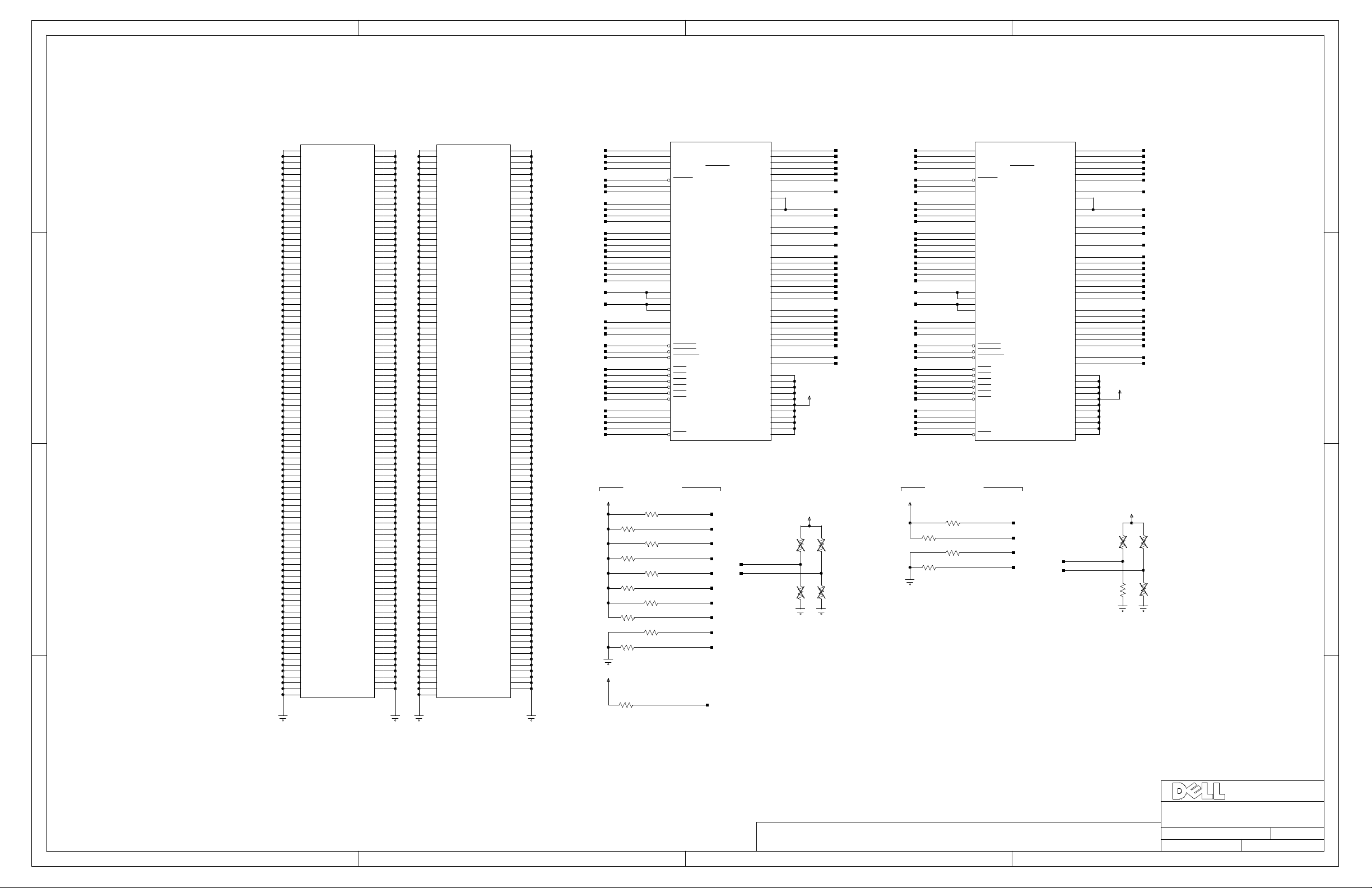

DDR2

DDR2

DDR2, routing diagram

DDR2, VRef

Gigabit Ethernet

Gigabit Ethernet

Gigabit Ethernet

PXH

PXH

PXH

PXH

Connectors

Connectors

ICH5

ICH5

Keyboard, Mouse, COM Ports, I2C MUX/Table

Radeon Video

Radeon Video

Radeon Video

Radeon Video

Super I/O, 373

Battery / Intrusion Detect / RAID Key / VAux Pwrgood

Fans and fan LED's

Parallel Port / ID Button / Rear Cyclops / Speaker

BMC

BMC

BMC

BMC

BMC, Serial Port Muxing

BMC - Serial Port MUXing Diagram

RAC

1.2V Vtt generation

Fan PWM Controllers

MicroVu

VAux reset

USB / Buttons

Spares / Coupons / Hardware

PCI bus p/u's / PCI Debug Slot

Debug Features

1

2

3

1U PWA assembly

2U/5U PWA assembly

4

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

P# F1667

P# H1754

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER

CORP., EXCEPT AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN

ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE

REPRODUCED IN WHOLE OR IN PART AND MUST BE RETURNED TO DELL

COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION

OF THE PURPOSE OF THE LOAN. NEITHER THIS ITEM NOR THE

INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS

NOT HAVING A NEED FOR SUCH USE OR DISCLOSURE CONSISTENT WITH

THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF

DELL COMPUTER CORPORATION.

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

Uniplanar Team:

-Shawn Dube

-Jinsaku Masuyama

-Garnett Thompson

-TJ Thompson

XLBOM Build option table

0 Production Build

9 Prototype Build

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

COMPUTER

CORPORATION

AUSTIN,TEXAS

LINDY PLANAR

DWG NO.

D1660 X03

DATE

1/13/2004 1 OF 61

SHEET

4

REV.

DCBA

B D

CA

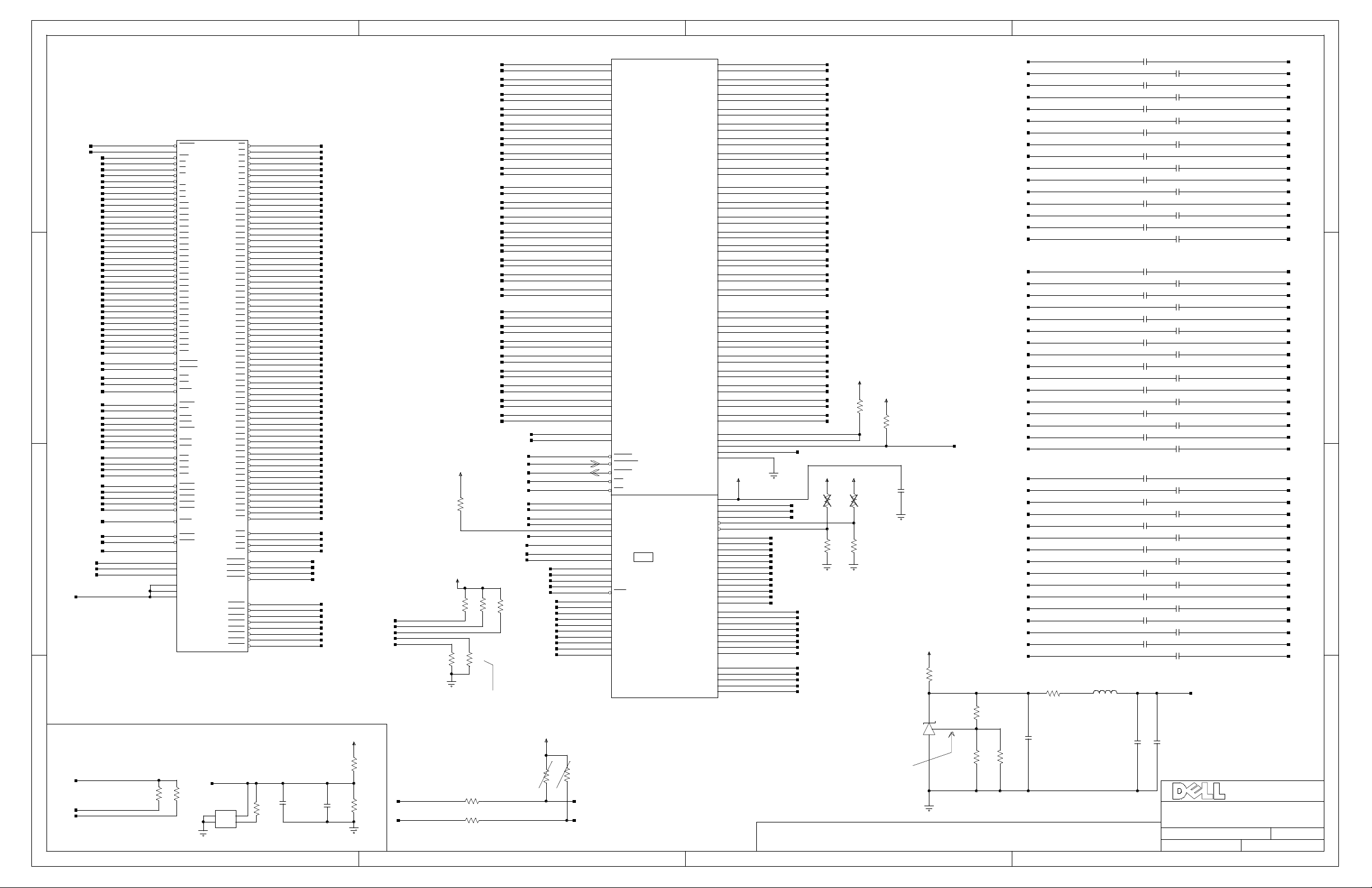

CLOCK DISTRIBUTION

BLOCK DIAGRAM

1-21-2004_9:57

1

2

1

2

3

4 4

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

REV.

X03

A B

TITLE

LINDY PLANAR

DWG NO.

D1660

DATE

DC

COMPUTER

CORPORATION

AUSTIN,TEXAS

SHEET

2 OF 611/13/2004

3

B D

V_3P3_CLK

3

21

4.7K

R1476

R1477

R1420

21

ICH_SEG2_SDA

4,35

1

+3.3V

1 2

C1093

L103

BLM18BD601SN1

L105

BLM18BD601SN1

0.1uF 16V

21

21

1 2

C1094

0.1uF 16V

21

C1209

1 2

C1103

10uF 6.3V

1 2

C1102

0.1uF 16V

C1101

0.1uF 16V

1 2

0.1uF 16V

1 2

C1100

1 2

C1104

0.1uF 16V

0.1uF 16V

1 2

C1099

1 2

C1098

0.1uF 16V

0.1uF 16V

1 2

C1096

V_3P3_CLK

1 2

C1097

0.1uF 16V

3

0.1uF 16V

4,35

ICH_SEG2_SCL

0-5%

R1421

1 2

0-5%

ICH_SEG2_409_SDA

ICH_SEG2_409_SCL

NP*

1 2

4.7K

NP*

CA

1-21-2004_9:57

ECAD Note:

3

3

VCC routing should be from plane, through high-f cap, to pin

1

x00_tj_050503

+3.3V

C1105

21

10uF 6.3V

SUB*_U1084

300OHM, 300 mA

1 2

0.1uF 16V

L129

1 2

ILB_1206

1 2

C1092

V_3P3_CLK_VDD48

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MIL

1 2

C758

0.1uF 16V

V_3P3_CLK_VDDA

10uF 6.3V

x02_sd

R46

4.7K

1 2

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MIL

U1084

300 ohm, 25%, 300mA, 1206

Vishay ILB1206RK301V

KOA CZB2BFL-301P

21

C757

x03_tj_121503

2.2-5%

0.1uF 16V

R606

V_3P3_CLK

3

21

21

C756

C759

0.1uF 16V

2

X10

1 2

14.31818MHz

R947

NP

2 1

1M-5%

50V-10%

2 1

27pF

C1090

May need to tune caps during UT

50V-10%

27pF

12

C1091

CK_FSA

5

CK_FSB

5

R1419

0-5%

R1022

1 2

0-5%

21

R1002

5,59

4,5,59

12

475-1%

IREF = 2.32mA

CK_VTT_PWRGD_N

CK_PWRDWN_N

21

C1326

3

Spread spectrum Controlled through I2C

21

4.7K

R1008

0.1uF 16V

NP*

x00_tj_051203

4.7K

R1018

1 2

NP*

21

R1007

21

C777

1 2

C778

4.7K

R1475

1 2

C779

ICH_SEG2_409_SDA

3

ICH_SEG2_409_SCL

3

1K-1%

1000pF

1000pF

50V-10%

50V-10%

PART_NUMBER=79015

PART_NUMBER=79015

21

1 2

C780

1000pF

1000pF

50V-10%

50V-10%

PART_NUMBER=79015

PART_NUMBER=79015

CK_XTAL_IN

CK_XTAL_OUT

CK_FSA_R

CK_FSB_R

CK_IREF

3

VDD_REF

10

VDD_PCI_1

16

VDD_PCI_2

24

VDD_3V66

55

VDD_ANLG

34

VDD_48MHZ

42

VDD_CPU_1

48

VDD_CPU_2

36

VDD_SRC

4

XTALIN

5

XTALOUT

51

FS_A

56

FS_B

52

IREF

35

VTT_PWRGD

21

PWR_DOWN

30

SDATA

28

SCLK

6

GND_REF

11

GND_PCI_1

17

GND_PCI_2

25

GND_3V66

39

GND_SRC

33

GND_48MHZ

53

GND_IREF

45

GND_CPU

54

GND_ANLG

CK409B for Proto builds

x00_tj_052003

CK409B

3V66_4/VCH

CK409 - TSSOP56

SMBus address = D2h

All clk _R nets have a hidden prop-delay max of 500mil

1

CK_14M_ICHS_R

REF0

2

CK_14M_SIO_R

REF1

7

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

USB

DOT

SRC_P

SRC_N

CK_33M_ICHS_R

8

CK_33M_SIO_R

9

CK_33M_FWH_R

12

CK_33M_SLOT3_R

13

CK_33M_PCI0_DEBUG_R

14

CK_33M_BMC_R

15

CK_33M_CPLD_R

18

CK_33M_DBG_LPC_R

19

CK_33M_VIDEO_R

20

CK_33M_RAC_R

31

CK_48M_USB_ICHS_R

32

CK_48M_SIO_R

CK_100M_DB800_P_R

38

37

CK_100M_DB800_N_R

22

CK_66M_MCH_R

23

CK_66M_ICH_R

26

CK_66M_3V66_2

27

CK_66M_LAI_R

29

41

CK_167M_CPU1_P_R

40

CK_167M_CPU1_N_R

44

CK_167M_CPU2_P_R

43

CK_167M_CPU2_N_R

47

CK_167M_MCH_P_R

46

CK_167M_MCH_N_R

50

CK_167M_ITP_P_R

49

CK_167M_ITP_N_R

PCI_F0

PCI_F1

PCI_F2

3V66_0

3V66_1

3V66_2

3V66_3

CPU_P0

CPU_N0

CPU_P1

CPU_N1

CPU_P2

CPU_N2

CPU_P3

CPU_N3

SUB=SUB23_U1438

R1017

1K-1%

21

R1417

1 2

1K-1%

R956

1 2

33-5%

R957

1 2

33-5%

R1361

1 2

33-5%

R1473

1 2

CK_14M_ICHS

CK_14M_SIO

NC_CK_48M_SIO

R962

NP*

21

33-5%

R963

21

33-5%

R593

21

1K-1%

+3.3V

CK-409 support

Place close to ICH

4.7K

4.7K

R1474

Pop 33ohm, 49.9ohm if CK409B used

POP0121POP01

CPU_STOP#

PCI_STOP#

Populate with CK409B (ITP diferential pair)

Differential pair routing guideline:

6 mil traces / 14 mil spacing

Spacing to other traces: 5W

33

40

33-5%

R142921R1712

1 2

49.9-1%

NP01

R959

21

49.9-1%

R950

33-5%

CK_100M_DB800_P

CK_100M_DB800_N

R961

33-5%

R965

33-5%

R966

33-5%

R967

33-5%

R951

NP01

33-5%

21

CK_48M_USB_ICHS

R960

21

33-5%

21

R952

21

33-5%

21

R968

21

33-5%

21

R969

21

33-5%

21

21

R1036

21

4

4

49.9-1%

21

R1037

33

21

R1039

49.9-1%

NP01

49.9-1%

21

R1035

21

R1033

21

R1038

49.9-1%

R1034

1 2

49.9-1%

NP01

49.9-1%

21

R1040

49.9-1%

49.9-1%

R964

33-5%

R955

33-5%

R954

33-5%

R1362

1 2

33-5%

R949

33-5%

R1416

1K-1%

R1363

33-5%

R1364

1 2

33-5%

R1366

33-5%

R1367

1 2

33-5%

R38

33-5%

21

21

21

21

21

NP*

21

21

21

CK_33M_ICHS

CK_33M_SIO

CK_33M_FWH

CK_33M_SLOT1

CK_33M_PCI0_DEBUG

CK_33M_BMC

CK_33M_CPLD

CK_33M_SMARTVU

CK_33M_VIDEO

CK_33M_RAC

CK_66M_MCH

CK_66M_ICH

CK_167M_CPU1_P

CK_167M_CPU1_N

CK_167M_CPU2_P

CK_167M_CPU2_N

CK_167M_MCH_P

CK_167M_MCH_N

CK_167M_ITP_P

CK_167M_ITP_N

33

40

55

31

58

44

5,59

To CPLD and Mictor header

59

36

50

17

33

11

11

11

11

17

17

15

15

x00_tj_051503

CK409B / CK409 Operation

FSA

0

1

4 4

Freq. latched on VTT_PWRGD

FSB SPEEDFSB

0

100 MHz

200 MHz

10

133 MHz

0

11

166 MHz

ROOM=CLOCK1

2

3

subsys done

A B

Clock CK409B

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

TITLE

LINDY PLANAR

DWG NO.

D1660

DATE

DC

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

SHEET

3 OF 611/13/2004

X03

B D

CA

1-21-2004_9:57

1

ICH_SEG2_SDA

3,35

ICH_SEG2_SCL

3,35

L108

+3.3V

C1114

1 2

BLM18BD601SN1

L107

BLM18BD601SN1

0.1uF 16V

21

21

1 2

C1111

0.1uF 16V

21

C1210

C1110

10uF 6.3V

1 2

0.1uF 16V

1 2

C1109

1 2

C1108

0.1uF 16V

1 2

C1112

0.1uF 16V

C1113

0.1uF 16V

2

R996

R591

1 2

8.2K-5%

x00_tj_051203

21

10K-1%

21

R590

8.2K-5%

R999

1 2

8.2K-5%

R998

10K-1%

1 2

0.1uF 16V

NP*

10K-1%

C1327

21

R997

21

NP

R1480

10K-1%

1 2

3,5,59

3

3

4

4.7K

4

4,31

4,31

x00_sd_051703

CK_100M_DB800_N

CK_100M_DB800_P

ICH_SEG2_800_SCL

ICH_SEG2_800_SDA

SRC_BYPASS/PLL

SRC_PLL_LOW_BW

SRC_STOP_N

SRC_DIV2_N

CK_PWRDWN_N

NC_SRC_LOCK

DB800_OE0

4

DB800_OE4

4

DB800_OE5

4

SLOT7_PWRGD

SLOT6_PWRGD

5

SRC_IN

4

SRC_IN

23

SCLK

24

SDATA

22

BYPASS/PLL

28

PLL_BW

27

SRC_STOP

1

SRC_DIV2

26

PWRDWN

45

LOCK

6

OE_0

14

OE_1

15

OE_2

7

OE_3

43

OE_4

35

OE_5

36

OE_6

44

OE_7

3

GND_3

10

GND_10

18

GND_18

25

GND_25

32

GND_32

40

GND_40

47

GNDA

SMBus address = DCh

V_3P3_SRC

4

V_3P3_SRC

4

21

R592

V_3P3_SRC

4

21

21

3

DB800_OE0

4

DB800_OE4

4

DB800_OE5

4

SLOT7_PWRGD

4,31

SLOT6_PWRGD

4,31

x00_sd_051703

NP

R111

R100

1 2

R112

8.2K-5%

NP

21

R101

1K-1%

R113

1 2

8.2K-5%

NP

R103

1K-1%

1 2

21

R114

8.2K-5%

NP

21

R105

1K-1%

R115

1 2

8.2K-5%

NP

R107

1K-1%

1 2

8.2K-5%1K-1%

R1423

0-5%

R1422

1 2

0-5%

21

1 2

C786

C784

1000pF

50V-10%

0.1uF 16V

PART_NUMBER=79015

x00_tj_051203

DB800

ICS9DB108

PROPAGATION_DELAY=L:S::500

NET_PHYSICAL_TYPE=50MIL

V_3P3_SRC

4

21

ICH_SEG2_800_SDA

ICH_SEG2_800_SCL

1 2

1000pF

50V-10%

PART_NUMBER=79015

8

DIF_0

9

DIF_0

12

DIF_1

13

DIF_1

16

DIF_2

17

DIF_2

20

DIF_3

21

DIF_3

30

DIF_4

29

DIF_4

34

DIF_5

33

DIF_5

38

DIF_6

37

DIF_6

42

DIF_7

41

DIF_7

46

IREF

2

VDD_2

11

VDD_11

19

VDD_19

31

VDD_31

39

VDD_39

48

VDDA

21

4.7K

4.7K

R1479

R1478

1 2

NP*

NP*

Note: If clock ordering changes, BIOS requirements must change

V_3P3_SRC

CK_100M_SATA_P_R

CK_100M_SATA_N_R

CK_100M_MCH_P_R

CK_100M_MCH_N_R

CK_100M_PXH_PLANAR_P_R

CK_100M_PXH_PLANAR_N_R

CK_100M_DOBSON_P_R

CK_100M_DOBSON_N_R

CK_100M_PXH_P_R

CK_100M_PXH_N_R

CK_100M_EXP_LAI_P_R

CK_100M_EXP_LAI_N_R

CK_100M_SLOT1_P_R

CK_100M_SLOT1_N_R

CK_100M_SLOT2_P_R

CK_100M_SLOT2_N_R

DB800_VDDA

R1003

1 2

475-1%

V_3P3_SRC

10uF 6.3V

C1202

21

4

x00_tj_050103

SUB*_U1084

0.1uF 16V

300OHM, 300 mA

C1107

12

4

4

4

L130

1 2

ILB_1206

IREF = 2.32mA

+3.3V

0.1uF 16V

12

NP

1 2

1 2

33-5%

1 2

33-5%

1 2

33-5%

1 2

1 2

33-5%

33-5%

C1106

R976

33-5%

R977

R980

R975

R973

33-5%

R971

33-5%

R1368

R1370

NP

21

21

R978

1 2

33-5%

R979

1 2

33-5%

R981

1 2

33-5%

R974

1 2

33-5%

R972

1 2

33-5%

R970

1 2

33-5%

R1369

33-5%

R1371

33-5%

CK_100M_SATA_P

CK_100M_SATA_N

CK_100M_MCH_P

CK_100M_MCH_N

CK_100M_PXH_PLANAR_P

CK_100M_PXH_PLANAR_N

CK_100M_DOBSON_P

CK_100M_DOBSON_N

CK_100M_PXH_P

CK_100M_PXH_N

CK_100M_EXP_SPARE_P

CK_100M_EXP_SPARE_N

21

R1432

49.9-1%

R1431

49.9-1%

CK_100M_SLOT7_P

CK_100M_SLOT7_N

CK_100M_SLOT6_P

CK_100M_SLOT6_N

21

49.9-1%

21

21

21

R1051

1 2

49.9-1%

R1052

1 2

R1050

1 2

49.9-1%

49.9-1%

R1049

1 2

R1048

1 2

49.9-1%

49.9-1%

R1047

1 2

R1046

1 2

49.9-1%

R1045

49.9-1%

1 2

R1044

1 2

49.9-1%

R1042

49.9-1%

R1043

1 2

49.9-1%

1 2

49.9-1%

R1041

1 2

49.9-1%

R1434

49.9-1%

21

R1433

33

33

17

17

27

27

31

31

31

31

31

31

31

31

31

31

1

2

3

U1084

300 ohm, 25%, 300mA, 1206

Vishay ILB1206RK301V

SATAOE0

OE1 MCH

OE2

Planar PXH

OE3

Dobson

OE4

4 4

PXH

OE5

LAI

OE6

Slot1 ***Note--BIOS should disable for 2U

OE7

Slot2

1U Prod 2U/5U Prod 1U Proto 2U/5U Proto

X X X X

X X X X

X X

X X

X X

X X

XXXX

***Note--BIOS should disable for 2U

subsys done

A B

KOA CZB2BFL-301P

ROOM=CLOCK2

DB800 Differential buffer

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

TITLE

LINDY PLANAR

DWG NO.

D1660

DATE

DC

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

SHEET

4 OF 611/13/2004

X03

B D

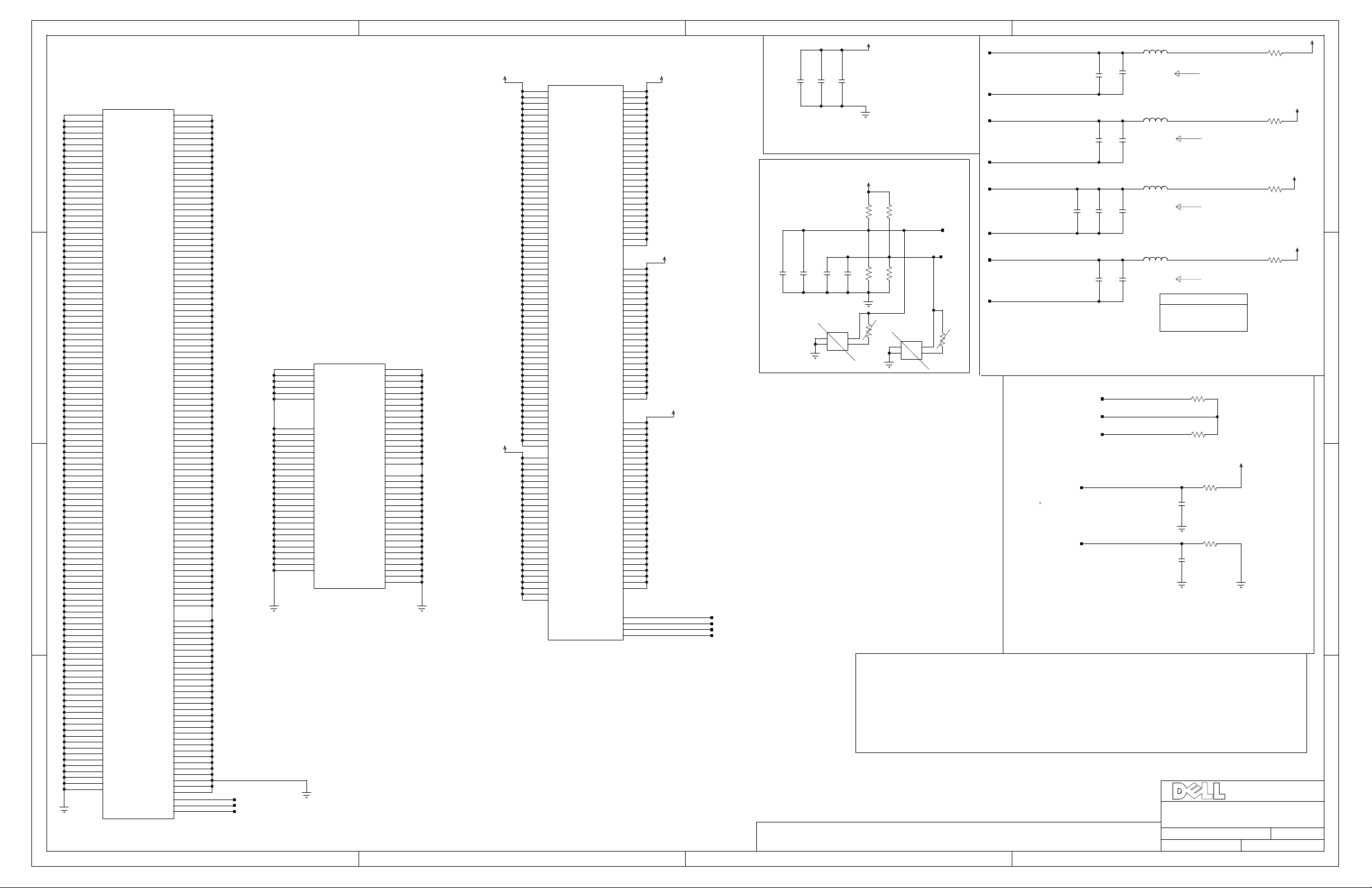

todo check ich_pme will be driven or floated high in time

CA

1-21-2004_9:57

1 2

21

R1769

NP13

R1770

NP02

U64

7,8,59

5

OUTIN

NCEN

x02_sd

R6006

1 2

33-5%

R6007

21

33-5%

21

C559

1000pF

PART_NUMBER=79015

ICH_THRMTRIP

NET_PHYSICAL_TYPE=PWR

+1.8V_AUX

51

0.1uF 16V

43

21

PFAULT_LATCH_N

PFAULT_RESET

+3.3V_AUX

U38

1142

R575

1 2

100-1%

50V-10%

R92

1 2

2.7K-5%

10V-10%

C1624

C1625

1uF

21

44,46

5

+3.3V_AUX

U38

CK_CPLD

3144

BUF_CK_CPLD

VHC14VHC14

5

RC = 0.1 us

F = 2.0MHz

8

RN87

1

1 2

2.7K-5%

2.7K-5%

1 2

2.7K-5%

567

4.7K

432

CPLD_DDR2_RESET

5,59

Q104

3904

ICH_THRMTRIP_N

3

1

33

2

CPLD_H_VID_PWRGOOD_N

5,59

todo....need to check that 3904 has drive strength and gain

CPLD_H_FORCEPR

5

+3.3V_AUX

0.1uF 16V

C1626

21

x00_tj_042803

H2_CPU_PRES_N

5,12,46

H1_CPU_PRES_N

5,12,46

H2_VTT_EN

5,12

H1_VTT_EN

5,12

ROOM=SYSCPLD

R1439

R1438

R426

5,32,46

Q66

3904

1

R583

2.7K-5%

Q65

3904

1

21

Q84

3904

1

BACKPLANE_PRES_N

RISER_PRES_N

5,31

todo, consider slew rate limiting

+1.8V

1 2

301-1%

R1359

DDR2_RESET_N_1

+1.8V

3

301-1%

R1

2

21

Q11

3904

21

DDR2_RESET_N_2

3

1

2

H_VTT_PWRGOOD

3

12

2

3

H_FORCEPR_N

11,12

2

+3.3V_AUX

21

4.7K

R1835

R1834

1 2

x00_sd_052203

x00_tj_052903

20,21

20,21

4.7K

R129

1 2

33-5%

33-5%

1 2

33-5%

1 2

33-5%

33-5%

R1541

R1542

R1543

R1545

R1544

R1546

R6003

R6004

R6002

R6005

21

33-5%

R1376

1 2

33-5%

R1353

1 2

1K-5%

R1375

1 2

33-5%

R1374

21

33-5%

R1373

1 2

.01uF 16V

33-5%

R1381

R1377

21

R1378

R1379

R1380

21

50V-5%

50V-5%

1 2

47pF

C134521C1346

x03_GT_010704

21

SHIFTY_RISER_CLK

33-5%

1 2

SHIFTY_RISER_LATCH

33-5%

21

SHIFTY_RISER_DATA_DN

33-5%

1 2

SHIFTY_BCKPLN_CLK

33-5%

21

SHIFTY_BCKPLN_LATCH

33-5%

1 2

SHIFTY_BCKPLN_DATA_DN

33-5%

21

SHIFTY_BMC_CLK

33-5%

1 2

SHIFTY_BMC_LATCH

33-5%

21

SHIFTY_BMC_DATA_DN

33-5%

1 2

SHIFTY_BMC_DATA_UP

33-5%

point-to-point, no cap needed

50V-5%

1 2 C900

50V-5%

47pF

50V-5%

47pF

1 2 C1342

47pF

50V-5%

1 2 C1343

21 C1341

point-to-point, no cap needed

point-to-point, no cap needed

.01uF 16V

47pF

PCI_RST_BACKPLANE_N

50V-5%

1 2

47pF

21

C1349

C1347

PCI_RST_PLANAR_N

PCI_RST_RISER_N

31

31

31

32

32

32

46

46

46

5

SYSTEM_PWRGOOD_PXH

SYSTEM_PWRGOOD_NIC

SYSTEM_PWRGOOD_FETS

SYSTEM_PWRGOOD_BACKPLANE

SYSTEM_PWRGOOD_RISER

SYSTEM_PWRGOOD_CHIPSET

47pF

21 C1344

PCI_RST_RAC_N

PCI_RST_MCH_N

x02_sd

50

17

27,40,55,58,59

31

32

28

24,25

24,35,41

32

31

17,33

just for dumbview

just for dumbview

P3975SYSTEM_CPLD

PROG-PART SPEC 14967

DISK PROG

BLANK PART

P3976

1Y852

+3.3V_AUX

x00_sd_051903

x00_sd_051903

22uF 6.3V

C742

21

SYSTEM_PWRGOOD_ESM

44,46,50

SYSTEM_PWRGOOD_NIC_R

5

SYSTEM_PWRGOOD_FETS_R

5

SYSTEM_PWRGOOD_BACKPLANE_R

5

SYSTEM_PWRGOOD_RISER_R

5

SYSTEM_PWRGOOD_CHIPSET_R

5,59

SYSTEM_PWRGOOD_PXH_R

5

PCI_RST_MCH_N_R

5

PCI_RST_PLANAR_N_R

5

PCI_RST_RISER_N_R

5

PCI_RST_BACKPLANE_N_R

5

PCI_RST_RAC_N_R

5

BACKPLANE_PRES_N

5,32,46

RISER_PRES_N

5,31

SHIFTY_RISER_DATA_UP

31,59

CK_FSA

3

SHIFTY_RISER_DATA_DN_R

5,59

SHIFTY_RISER_CLK_R

5,59

SHIFTY_RISER_LATCH_R

5,59

CK_FSB

3

BUF_CK_CPLD

5

CK_33M_CPLD

3,59

INTRUSION_COVER_VAUX_N

x03b_sd

41

CK_32K_VAUX_SYSCPLD

33

SHIFTY_BMC_DATA_UP

5

SHIFTY_BMC_DATA_DN_R

5

CPLD_DDR2_RESET

5,59

3.3VAUX_PWRGOOD

41

H2_PROCHOT_3V

15

H1_PROCHOT_3V

15

H2_THERMTRIP_3V

15,46

H1_THERMTRIP_3V

15,46

H2_IERR_3V

15,46

H1_IERR_3V

15,46

ITP_DBR_N

15

SHIFTY_BMC_CLK_R

5

SHIFTY_BMC_LATCH_R

5

ICH_THRMTRIP

5

SHIFTY_BCKPLN_CLK_R

5,59

SHIFTY_BCKPLN_LATCH_R

5,59

SHIFTY_BCKPLN_DATA_DN_R

5,59

SHIFTY_BCKPLN_DATA_UP

32,59

5V_PWRGOOD

6,59

5V_RISER_PWRGOOD

6

RISER_PWRGOOD

31,59

DC2DC_CPUVTT_EN

6,51,59

DC2DC_1V5_EN

6,59

DC2DC_1V8_EN

6,59

DC2DC_3V3_EN

6,59

DC2DC_5V_EN

6,59

0.1uF 16V

0.1uF 16V

1 2

C15

C13

21

0.1uF 16V

1 2

C1421C16

x02_tj_092203

+3.3V_AUX

1K-5%

NC_SC_NC18

NC_SC_NC20

NC_SC_NC31

NC_SC_NC33

NC_SC_NC34

NC_SC_NC42

NC_SC_NC44

NC_SC_NC46

NC_SC_NC48

NC_SC_NC66

NC_SC_NC75

NC_SC_NC106

NC_SC_NC107

NC_SC_NC114

0.1uF 16V

1 2

R1382

143

140

138

136

134

133

132

131

130

129

106

107

114

108

123

144

1uF 6.3V

C277

21

17

IO_1_1

16

IO_1_2

15

IO_1_3

14

IO_1_4

13

IO_1_5

12

IO_1_6

11

IO_1_11

10

IO_1_12

9

IO_1_13

7

IO_1_14

6

IO_1_15_GTS1

5

IO_1_16_GTS0

19

IO_2_1

21

IO_2_2

22

IO_2_3

23

IO_2_4

24

IO_2_5

25

IO_2_6

26

IO_2_11

28

IO_2_12

30

IO_2_13_GCK0

32

IO_2_14_GCK1

35

IO_2_15_CDRST

38

IO_2_16_GCK2

4

IO_3_1

3

IO_3_2_GTS3

2

IO_3_3_GTS2

IO_3_4_GSR

IO_3_5

IO_3_6

IO_3_7

IO_3_11

IO_3_12

IO_3_13

IO_3_14

IO_3_15

IO_3_16

39

IO_4_1_DGE

40

IO_4_2

41

IO_4_3

43

IO_4_4

45

IO_4_5

49

IO_4_6

50

IO_4_7

51

IO_4_11

52

IO_4_12

53

IO_4_13

54

IO_4_14

56

IO_4_15

57

IO_4_16

18

NC_18

20

NC_20

31

NC_31

33

NC_33

34

NC_34

42

NC_42

44

NC_44

46

NC_46

48

NC_48

66

NC_66

75

NC_75

NC_106

NC_107

NC_114

29

GND_29

36

GND_36

47

GND_47

62

GND_62

72

GND_72

89

GND_89

90

GND_90

99

GND_99

GND_108

GND_123

GND_144

1uF 6.3V

C27821C279

1 2

1uF 6.3V

SYSTEM_CPLD

XC2C128 TQFP144

SUB*_P3975

256 macrocell flavor

1uF 6.3V

C659

1 2

IO_5_1

IO_5_2

IO_5_3

IO_5_4

IO_5_5

IO_5_6

IO_5_7

IO_5_11

IO_5_12

IO_5_13

IO_5_14

IO_5_15

IO_5_16

IO_6_1

IO_6_2

IO_6_3

IO_6_4

IO_6_5

IO_6_6

IO_6_11

IO_6_12

IO_6_13

IO_6_14

IO_6_15

IO_6_16

IO_7_1

IO_7_2

IO_7_3

IO_7_4

IO_7_5

IO_7_6

IO_7_7

IO_7_11

IO_7_12

IO_7_13

IO_7_14

IO_7_15

IO_7_16

IO_8_1

IO_8_2

IO_8_3

IO_8_4

IO_8_5

IO_8_6

IO_8_11

IO_8_12

IO_8_13

IO_8_14

IO_8_15

IO_8_16

TCK

TDI

TDO

TMS

VCC_JTAG

VCC_1

VCC_37

VCC_84

VCCIO1_27

VCCIO1_55

VCCIO1_73

VCCIO1_93

VCCIO2_109

VCCIO2_127

VCCIO2_141

NC_135

NC_137

NC_139

NC_142

94

95

96

97

98

100

101

102

103

104

105

110

111

92

91

88

87

86

85

83

82

81

80

79

78

112

113

115

116

117

118

CPLD_H_VID_PWRGOOD_N

119

120

121

124

125

126

128

77

DC2DC_5V_RISER_EN

76

I2C_SEG2_VAUX_SDA

I2C_SEG2_VAUX_SCL

74

71

70

69

68

64

61

60

59

58

67

CPLD_TCK

63

CPLD_TDI

122

CPLD_TD1

65

CPLD_TMS

8

1

37

84

27

55

73

93

109

127

141

135

NC_SC_NC135

137

NC_SC_NC137

139

NC_SC_NC139

142

NC_SC_NC142

44,46

PS1_PWRGOOD

PS2_PWRGOOD

DEBUG_JUMPER_1

DEBUG_JUMPER_0

DEBUG_LED_3

DEBUG_LED_2

DEBUG_LED_1

DEBUG_LED_0

ICH_PWRBTN_N

ICH_PME_N

PFAULT_LATCH_N_R

PFAULT_RESET

RISER_EXP_PME_N

VRD1_THERMTRIP_N

PCI_RST_ICH_N

VCORE_EN_R VCORE_EN

VCORE1_PWRGOOD

VCORE2_PWRGOOD

CPLD_H_FORCEPR

VRD2_THERMTRIP_N

ICH_PWR_ON_REQ

RESET_BTN_N

PS1_ENABLE_N

PS2_ENABLE_N

LPC_LFRAME_N

PME_NIC_CPLD_N

H2_CPU_PRES_N

H1_CPU_PRES_N

RISER_PCI_PME_N

CK_VTT_PWRGD_N

H1_BSEL0_3V_N

H1_BSEL1_3V_N

H2_BSEL0_3V_N

H2_BSEL1_3V_N

CPU_VTT_PWRGOOD

1V5_PWRGOOD

1V8_PWRGOOD

3V3_PWRGOOD

CK_PWRDWN_N

B_1U_2U5U

LPC_LAD3

LPC_LAD2

LPC_LAD1

LPC_LAD0

H2_VTT_EN

H1_VTT_EN

5,31,32,40,46

5,40

46

5,31,32,40,46

31,59

31,59

59

59

x00_sd_52903 - removed 2 leds

59

59

59

59

33,41,44,56,59

33,41

5

5

x03b_sd

31,41

9,46

33,59

33-5%

7,59

8,59

5

x02_sd

9,46

33,40,41,44,59

56

31,59

31,59

33,40,44,55,59

33,40,44,55,59

33,40,44,55,59

33,40,44,55,59

33,40,44,55,59

5,59

28

5,12,46

5,12,46

5,12

5,12

x03b_sd

31,41

3,59

6

44,45,59

44,45,59

15

15

15

15

6,51

6,59

6,59

6,59

3,4,59

+3.3V_AUX

+3.3V_AUX

R1790

R1791

PFAULT_LATCH_N_R

5

PROPAGATION_DELAY=L:S::2000

PFAULT_RESET_R

PROPAGATION_DELAY=L:S::2500

21

R1865

+3.3V_AUX

8.2K-5%

8.2K-5%

2

GND

TPS72118DBV

NP*

1 2

8.2K-5%8.2K-5%

21

NP*

SYSTEM_PWRGOOD_PXH_R

5

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_NIC_R

5

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_FETS_R

5

PROPAGATION_DELAY=L:S::2000

1

2

3

SYSTEM_PWRGOOD_BACKPLANE_R

5

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_RISER_R

5

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_CHIPSET_R

5,59

PROPAGATION_DELAY=L:S::2000

PCI_RST_RAC_N_R

5

PROPAGATION_DELAY=L:S::2000

PCI_RST_MCH_N_R

5

PROPAGATION_DELAY=L:S::2000

PCI_RST_PLANAR_N_R

5

PROPAGATION_DELAY=L:S::2000

PCI_RST_RISER_N_R

5

PROPAGATION_DELAY=L:S::2000

PCI_RST_BACKPLANE_N_R

5

PROPAGATION_DELAY=L:S::2000

SHIFTY_RISER_CLK_R

5,59

PROPAGATION_DELAY=L:S::2000

SHIFTY_RISER_LATCH_R

5,59

PROPAGATION_DELAY=L:S::2000

SHIFTY_RISER_DATA_DN_R

5,59

PROPAGATION_DELAY=L:S::2000

SHIFTY_BCKPLN_CLK_R

5,59

PROPAGATION_DELAY=L:S::2200

SHIFTY_BCKPLN_LATCH_R

5,59

PROPAGATION_DELAY=L:S::2200

SHIFTY_BCKPLN_DATA_DN_R

5,59

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_CLK_R

5

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_LATCH_R

5

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_DATA_DN_R

5

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_DATA_UP_R

46

PROPAGATION_DELAY=L:S::2200

x03_GT_010704

+3.3V_AUX

J14

1

5,32,40

5,40

CPLD_TCK

CPLD_TDO

CPLD_TDI

CPLD_TMS

5,31,32,40,46

4 4

5,31,32,40,46

2

3

4

5

6

CPLD JTAG Chain

subsys done

DELETED DDR CLOCK CHIP AND PCI CLOCK CHIP

ADDED COOLRUNNER II CPLD FROM YOSIMITE

A B

p/u for TCK at SIO

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

NP*

31,46

CPLD_TD2

CPLD_BYPASS

1 2

NP*

CPLD_TDO

5,32,40

TITLE

LINDY PLANAR

DWG NO.

D1660

DATE

1/13/2004 5 OF 61

DC

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

SHEET

X03

1

2

3

TYPE

INPUT

OUTPUT

DESTINATION

70W VERTICAL

+12V

+1.8V

DDR II, MCH

ROOM=DC2DC_1P8V

1

+12V

R73

8.2K-5%

1 2

+

270uF

0.1uF 16V

+12V

16V-20%

1 2

X03_GT_011804

21

R132

3.3K-5%

+

C606

270uF

2 1

16V-20%

+1.8V

1 2

1V8_PWRGOOD

5,59

C1805

X03_GT_010704

Enable is driven to required state

from CPLD at all times.

2

12

C605

R463

0-5%

R546

1 2

0-5%

+1.8V DC2DC

R290

1 2

NC_DC2DC_1P8V_2

422-1%

+12V

+1.8V

DC2DC_1V8_EN

5,59

21

C588

R547

1 2

0-5%

NP

1000pF

50V-10%

PART_NUMBER=79015

MOD., 24 PIN, 72W, VERTICAL

DC2DC_1P8V

1

+RS

2

RSVD

3

-RS

4

PWRGD

5

PWRGD_SET

K

7

VSS_0

8

VSS_1

9

OUTEN

10

-SENCE

11

+SENSE

12

12V_IN_0

13

12V_IN_1

14

12V_IN_2

15

VOUT_0

16

VOUT_1

17

VSS_2

18

VOUT_2

19

VSS_3

20

VOUT_3

21

VSS_4

22

VOUT_4

23

VSS_5

24

VOUT_5

MH1

GND_MH1

MH2

GND_MH2

DC/DC CONVERTER

x00_gt_062603

+1.8V

16V-10%

4.7uF

C600

21

+1.8V

12

+

C268

16V-10%

4.7uF

C601

21

12

680uF

C26912C270

6.3V-20%

25V-20%

.1uF

C611

21

x00_tj_051203

x02_tj_121503

+

680uF

6.3V-20%

+

680uF

6.3V-20%

B D

TYPE

INPUT

OUTPUT

DESTINATION

100W HORIZONTAL

+12V

+3.3V

RISER's

ROOM=DC2DC_3P3V

+12V

R74

todo should this really be NC? -shawn

3V3_PWRGOOD

5,6,59

X03_GT_011804

Enable is driven to required state

from CPLD at all times.

1 2

21

R133

31

+3.3V DC2DC

8.2K-5%

+3.3V

3.3K-5%

x00_sd_051703

3P3V_RISER_SENSE

R1580

R1430

1 2

2-1%

RISER

+12V

1 2

C1627

C1568

2 1

+

270uF

16V-20%

0.1uF 16V

X00_GT_052203

2-1%

21

+3.3V

2

VCC

GND

3

DS1818

1 2

21.5K-1%

DC2DC_3V3_EN

5,59

21

R301

U24

1

RESET

SUB=SUB*_Y1351

R1572

NC_DC2DC_3P3V_6

C1501

1 2

PART_NUMBER=79015

NP

0-5%

3V3_PWRGOOD

R1488

10K-1%

+3.3V

1000pF

50V-10%

DC2DC_3P3V

21

1

+RS

K

3

-RS

4

PWRGD

5

PWRGD_SET

6

RESERVED

7

+12V

5,6,59

VSS_7

8

VSS_8

9

OUTEN

10

-SENSE

11

+SENSE

12

12VIN_12

13

12VIN_13

14

12VIN_14

15

VCC_15

16

VCC_16

17

VSS_17

18

VCC_18

19

VSS_19

20

VCC_20

21

VSS_21

22

VCC_22

23

VSS_23

24

VCC_24

100W-25A DC-DC

MOD.-25 pin, HORIZONTAL

+3.3V

16V-10%

4.7uF

+3.3V

4V-20%

820uF

+

21

1 2

C602

C287

CA

16V-10%

4.7uF

21

4V-20%

820uF

+

x00_tj_051203

25V-20%

C603

.1uF

C619

21

1 2

C288

TYPE

INPUT

OUTPUT

DESTINATION

ROOM=DC2DC_5V

5,6,59

X03_GT_011804

SENSE_5V_BACKPLANE_1U

32

SENSE_5V_BACKPLANE_2U5U

32

VCC

5V_PWRGOOD

R1752

2-1%

R562

1 2

0-5%

21

+12V

R75

1 2

21

R134

8.2K-5%

Enable is driven to required state

from CPLD at all times.

3.3K-5%

x03b_sd

NP13

R1750

1 2

0-5%

R273

21

10-1%

x03_sd_sense

BACKPLANE

+12V

+

C610

270uF

2 1

16V-20%

DS1818

1 2

C1650

0.1uF 16V

Sub to DS1811R-5 (+5V, 5% part)

100W VERTICAL

+12V

+5V

BACKPLANE

+5V DC2DC

R462

12

0-5%

NC_DC2DC_5V_6

DC2DC_5V_EN

5,6,59

DC2DC_5V_SENSE_GND

6

DC2DC_5V_SENSE

6

21

C590

NP

DC2DC_5V_SENSE

5,6,59

511-1%

VCC

2

VCC

RESET

GND

3

R1751

2-1%

1 2

U59

21

10K-1%

R275

R274

NP*

21

DC2DC_5V_SENSE_GND

1

5V_PWRGOOD

SUB=SUB*_1F826

1 2

VCC

1000pF

50V-10%

6

6

R466

0-5%

+12V

NP

R1848

1 2

DC2DC_5V

1

+RS

K

3

-RS

4

PWRGD

5

RSVD_1

6

RSVD_2

7

VSS_0

8

VSS_1

9

OUTEN

10

-SENCE

11

+SENSE

12

12V_IN_0

13

12V_IN_1

14

12V_IN_2

15

VOUT_0

16

VOUT_1

17

VSS_2

18

VOUT_2

19

VSS_3

20

VOUT_3

21

VSS_4

22

VOUT_4

23

VSS_5

24

VOUT_5

MH1

GND_MH1

MH2

GND_MH2

DC/DC CONVERTER

MOD. 073_20821_03

SUB=SUB*_H0778

DC2DC_5V_EN

5,6,59

5V_PWRGOOD

5,6,59

+12V

309-1%

NP

R1849

1 2

0-5%

1-21-2004_9:57

VCC

16V-10%

16V-10%

4.7uF

4.7uF

C60421C607

21

VCC

12

+

680uF

C271

6.3V-20%

VCC

DC2DC_5V_1U

NP

1

VCC_1

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

8

VSS_8

9

PWRGD_SET

10

12VIN_10

11

12VIN_11

40W-15A DC-DC

SIP11

x00_tj_051203

25V-20%

.1uF

12

+

680uF

C272

X00_GT_061203

1

C620

21

6.3V-20%

2

TYPE

INPUT

OUTPUT

DESTINATION

40W VERTICAL

+12V

+1.2V

CPU1, CPU2, MCH

ROOM=DC2DC_CPU_VTT

Enable is driven to required state

3

from CPLD at all times.

CPU_VTT_PWRGOOD

5,51

+12V

NP

16V-20%

1 2

270uF

+

C138

+12V

NP

R1137

8.2K-5%2.7K-5%

1 2

5,51,59

NP

R1148

1 2

ECAD: Place 1 560uF cap by each CPU

CPU VTT

+CPU_VTT

DC2DC_CPUVTT_EN

+12V

NP*

R543

1 2

x02_tj_091903

27.4K-1%

NP*

R225

1 2

26.7-1%

& one by regulator

DC2DC_CPUVTT

NP

1

VCC_1

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

8

VSS_8

9

PWRGD_SET

10

12VIN_10

11

12VIN_11

40W-15A DC-DC

SIP11

+CPU_VTT

10V-10%

2 1

C591

.1uF

+CPU_VTT

+

C349

2 1

560uF+4V-20%

4V-20%

16V-10%

4.7uF

21

C350

2 1

C608

560uF

TYPE

INPUT +12V

OUTPUT

DESTINATION

ROOM=DC2DC_1P5V

Enable is driven to required state

from CPLD at all times.

1V5_PWRGOOD

5,59

+12V

X03_GT_011804

16V-20%

1 2

270uF

C1566

+

40W HORIZONTAL

+1.5V

MCH, ICH5

+1.5V DC2DC

+12V

R77

8.2K-5%

1 2

21

R136

Substitute from 3.92K to 3.57K to tweak 1.5V to 1.53V

5,59

3.3K-5%

x03_tj_010904

DC2DC_1V5_EN

R70

1 2

+12V

3.57K-1%

R1489

26.7K-1%

SUB*_5N443

Substitute 26.1K, 1%

+1.5V

DC2DC_1P5V

1

VCC_1

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

8

VSS_8

21

9

PWRGD_SET

10

12VIN_10

11

12VIN_11

40W-15A DC-DC

MOD.-13 pin, HORIZONTAL

+1.5V

4V-20%

820uF

+

1 2

C1497

10V-10%

2 1

.1uF

16V-10%

C1575

4.7uF

TYPE

INPUT

OUTPUT

DESTINATION

ROOM=DC2DC_RISER5V

Enable is driven to required state

from CPLD at all times.

+12V

R76

8.2K-5%

1 2

21

R135

5

3.3K-5%

21

C1585

5,6

+12V

16V-20%

270uF

+

5V_RISER_PWRGOOD

X03_GT_011804

1 2

C1569

40W HORIZONTAL

+12V

+5V

MCH, ICH5

DC2DC_5V_RISER_EN

R32

1 2

+12V

309-1%

1 2

+5.0V Riser

DC2DC_RISER5V

1

VCC_1

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

R106

0-5%

8

VSS_8

9

PWRGD_SET

10

12VIN_10

11

12VIN_11

40W-15A DC-DC

MOD.-13 pin, HORIZONTAL

5V DC2DC

+5.0V Riser

1 2

C1651

DS1818

0.1uF 16V

Sub to DS1811R-5 (+5V, 5% part)

U34

2

VCC

RESET

GND

3

+5.0V Riser

1

5V_RISER_PWRGOOD

SUB=SUB*_1F826

12

+

680uF

C633

6.3V-20%

10V-10%

.1uF

2 1

16V-10%

C1576

4.7uF

5,6

C1586

21

4 4

3

subsys done

A B

DC2DC REGULATORS

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

COMPUTER

CORPORATION

TITLE

AUSTIN,TEXAS

LINDY PLANAR

DWG NO.

D1660

DATE

1/13/2004 6 OF 61

SHEET

DC

REV.

X03

B D

+12V +12V

SUB*_16155

VRD BOM Changes:

X02_TJ_081803

X02_TJ_110503

1

VRD1_PWM3A

7

VRD1_PWM4A

7

+3.3V

8.2K-5%

R4502

21

VCORE1_PWRGOOD

21

220K

R197221R1973

X02_TJ_081803

VRD1_VCC

220K

5,7,59

7

X03_GT_011804

Q86

3

FT2N7002LT1

1

2

7

7

5.1-5%

2 1

R260

R1985

1 2

1K-5%

1N914

2-1%

VRD1_PWM1A

DRV1_OD

.22uF 25V

20%

21

X03_GT_011804

.22uF 25V

20%

1 3

D9

R240

21

VRD1_DRV1

1

BST

2

IN

3

OD

4

VCC

ADP3418

C484

Phase 1

ROOM = VRD1_PHASE1

VRD1_PHASE1B_SENSE

7

x03_sd

50V-10%

1000pF

C852

C491

1 2

21

25V-20%

DRVH

SW

PGND

DRVL

C466

.1uF

8

7

6

5

NP*

21

R433

1 2

VRD1_UGATE1

VRD1_LGATE1

4.7K

R451

1 2

4.7K

Q41

9

4

D

3

2

G

S

1

NC

FDS7096N3

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

5

6

7

8

Q21

9

4

D

3

2

G

S

1

NC

FDS7066SN3

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

1 2

20%

5

6

7

8

25V-20%

.1uF

C488

C1680

21

25V-20%

.1uF

16V-10%

4.7uF

C1682

21

21

C1681

Q24

9

4

D

3

2

G

S

1

FDS7096N3

SUB*_N1930

Q20

4

3

2

G

1

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

9

5

D

6

7

S

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

+12V

21

R233

R1980

220K

VCORE_EN

C1727

NP

21

1 2

100-5%

R1846

7,12

7,12

7,12

7,12

7,12

7,12

C300

2 1

47pF

50V-5%

R250

24K-5%

1 2

R1821

1 2

0-5%

X03_GT_011804

DRV1_OD

1 2

C1807

33pF 50V

5,7,59

H1_VID0

H1_VID1

H1_VID2

H1_VID3

H1_VID4

H1_VID5

12

330pF 50V

R311

VRD1_VCCSENSE

0-5%

21

C462

VCORE1_PWRGOOD

VRD1_VSSSENSE

100K-1%

R289

NP*

21

C708

12

7

.1uF

25V-20%

SUB=NP

7

11

EN

10

PWRGD

15

ILIMIT

12

DELAY

9

COMP

7

FBRTN

5

VID0

4

VID1

3

VID2

2

VID3

1

VID4

6

VID5

19

GND

C479

12

680pF 50V

R278

1K-1%

R288

1 2

100K-1%

SUB*_16155

X02_TJ_110503

VRD1_VCC

VRD1_CTRL

ADP3168

21

RAMPADJ

R305

1 2

+12V

10-5%

VCC

PWM1

PWM2

PWM3

PWM4

SW1

SW2

SW3

SW4

CSSUM

CSREF

CSCOMP

300-5%

1 2

R13

28

14

13

RT

27

26

25

24

23

22

21

20

17

16

18

8

FB

Q87

3

FT2N7002LT1

1

2

7

7

5.1-5%

2 1

R261

487K-1%

VRD1_PWM1A

VRD1_PWM2A

VRD1_PWM3A

VRD1_PWM4A

R310

1 2

0-5%

50V-10%

3300pF

SUB*_1U388

R147

15.8K-1%

1 2

1 2

VRD1_PWM3A

DRV1_OD

R271

1 2

1 2

200K-1%

C720

R1987

1K-5%

X03_GT_011804

1 3

1N914

D7

1 2

2-1%

R243

R299

7

7

7

7

R303

21

0-5%

73.2K-1%

1 2

.01uF 16V

1 2

R306

21

1 2

0-5%

THERMISTOR

.22uF 25V

20%

21

VRD1_DRV3

16V-10%

.47uF

21

R315

1 2

0-5%

73.2K-1%

R291

C710

R85

1 2

41.2K-1%

Phase 3

ROOM = VRD1_PHASE3

x03_sd

50V-10%

1000pF

C854

C490

NP*

21

VRD1_PHASE3B_SENSE

7

C467

21

.1uF

25V-20%

4.7K

R437

1 2

VRD1_UGATE3

VRD1_LGATE3

4.7K

1

BST

2

IN

3

OD

4

VCC

ADP3418

.22uF 25V

1 2

20%

C483

DRVH

PGND

DRVL

8

7

SW

6

5

R457

1 2

C9

X00_GT_062103

Redraw Only- NEED INDEPENDENT CHECK before MODEM!

R314

21

73.2K-1%

1 2

R286

0-5%

1 2

73.2K-1%

R284

1 2

R81

1 2

R285

NP

VRD1_PHASE1B_SENSE

VRD1_PHASE2B_SENSE

VRD1_PHASE3B_SENSE

VRD1_PHASE4B_SENSE

X03_GT_011804

3

D

2

S

7

7

7

+CPU_VID1

7

R407

1 2

0-5%

C334

NP

1 2

.047uF

Q7

16V-10%

2N7002

R484

NP

21

1

G

4.7K

24.9K-1%

Q38

9

4

D

3

2

G

S

1

NC

FDS7096N3

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

ALT_LLINE

5

6

7

8

Q40

9

4

D

3

2

G

S

1

NC

FDS7066SN3

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

7

7,8

16V-10%

25V-20%

.22uF 25V

1 2

20%

4.7uF

C481

2 1

25V-20%

C1692

.1uF

2 1

.1uF

C1693

2 1

C1694

Redraw Only- NEED INDEPENDENT CHECK before MODEM!

5

6

7

8

FDS7066N3 is local. Waiting on library symbol.

X03_GT_011904

R1717

NP

VRD1_PWM1A

1 2

68K-5%

R1718

NP

68K-5%

GPO_ALT_LLINE_N

33

VRD1_PWM3A

21

VRD1_PWM4A

+3.3V_AUX

U61

131412

VHC14

x00_sd_052903

2

DRV1_OD_R

7

PWM Control Circuitry

ROOM = VRD1_CTRL

5,8,59

x00_sd_061603 - providing sensing

3

4 4

X00_GT_052203

H1_VSSSENSE

12

VRD1_VSSSENSE_MID

R304

1 2

R1851

0-5%

0-5%

21

SUB=SUB*_4053P

DRV1_OD_R

7

SUB=SUB*_75EEC

.047uF 25V

249K-1%

C714

1 2

20%

+CPU_VID1

12

R1820

NP

1 2

0-5%

VRD1_VSSSENSE

1uF

1 2

C1728

25V-10%

1 2

127K-1%

R255

H1_VCCSENSE

X00_GT_052203

50V-10%

1000pF

PART_NUMBER=79015

1 2

25V-20%

.22uF 25V

20%

21

Q39

4

3

2

G

1

FDS7096N3

Q25

4

3

2

G

1

FDS7066SN3

SUB*_T1564

7

7

SUB=SUB*_P1355

C336

16V-10%

C1683

.1uF

21

25V-20%

C489

.1uF

21

9

5

D

6

7

S

8

NC

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

9

5

D

6

7

S

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

ALT_LLINE

12

+

4.7uF

21

C1684

.22uF 25V

20%

16V-10%

4.7uF

560uF

4V-20%

C1685

+CPU_VID1

0.6uH, 27Amp

VERTICAL

R152

1 2

C276

1 2

16V-10%

4.7uF

C487

21

7,8

2 1

C303

L3

12

3-5%

.001UF

C1695

2 1

25V-20%

.1uF

50V-10%

SUB*_16155

X02_TJ_110503

SUB=SUB*_N1453

SUB=SUB*_P1355

16V-10%

4.7uF

25V-20%

.1uF

C1696

2 1

2 1

C305

2 1

C1697

12

+

C337

560uF

+CPU_VID1

SUB*_16155

X02_TJ_110503

4V-20%

L1

VERTICAL

0.6uH, 27Amp

1 2

SUB=SUB*_N1453

3-5%

R171

1 2

21

C282

.001UF

50V-10%

Input Filtering

+12V

SUB=SUB*_P1355

12

+

C582

270uF

C725

16V-20%

INTEGRATED VRD 10.1 VOLTAGE

REGULATOR FOR PROC_1

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

A B

12

+

Q88

3

FT2N7002LT1

1

2

1N914

2-1%

7

7

5.1-5%

2 1

R258

+12V

Q89

3

FT2N7002LT1

1

2

5.1-5%

R257

560uF

4V-20%

CA

VRD1_PWM2A

DRV1_OD

7

7

C2

1 2

1 2

1 3

R244

21

20%

1 2

12

20%

R1986

1K-5%

X03_GT_011804

20%

D11

1

BST

2

IN

3

OD

4

VCC

.22uF 25V

C482

21

R1988

1K-5%

X03_GT_011804

1N914

D10

31

1 2

2-1%

R236

VRD1_PWM4A

DRV1_OD

.22uF 25V

C8

21

21

C3

.1uF

50V-20%

Phase 2

ROOM = VRD1_PHASE2

VRD1_PHASE2B_SENSE

7

.22uF 25V

50V-10%

1000pF

C853

C579

1 2

25V-20%

VRD1_PHASE2

ADP3418

C471

.1uF

21

DRVH

PGND

DRVL

SW

21

x03_sd

8

7

6

5

NP*

R434

1 2

VRD1_LGATE2

Phase 4

ROOM = VRD1_PHASE4

VRD1_PHASE4B_SENSE

7

.22uF 25V

50V-10%

1000pF

C855

C578

20%

1

VRD1_UGATE4

BST

2

IN

3

OD

4

VCC

.1uF

21

C465

1 2

.1uF

25V-20%

VRD1_DRV4

DRVH

PGND

DRVL

ADP3418

C21

1 2

50V-20%

SUB=SUB*_4053P

21

x03_sd

SW

1uF

25V-10%

8

7

6

5

4.7K

NP*

VRD1_LGATE4

21

R430

R454

4.7K

1 2

21

R428

4.7K

1uF

C12

1 2

25V-10%

SUB=SUB*_4053P

4

3

2

1

FDS7096N3

SUB*_N1930

4.7K

Q36

9

5

D

6

7

G

S

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

Q37

9

4

D

3

2

G

S

1

FDS7066SN3

SUB*_T1564

Q34

9

4

D

3

2

G

S

1

NC

FDS7096N3

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

16V-10%

.22uF 25V

1 2

20%

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

5

6

7

.22uF 25V

8

20%

Q33

9

4

D

3

2

G

S

1

NC

FDS7066SN3

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

4.7uF

2 1

C581

16V-10%

4.7uF

C485

1 2

5

6

7

8

C1686

25V-20%

.1uF

C1698

2 1

25V-20%

25V-20%

.1uF

C1687

2 1

.1uF

12

C1688

2 1

25V-20%

.1uF

C1699

12

C1700

Q27

9

4

D

3

2

G

S

1

NC

FDS7096N3

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

Q26

4

3

2

G

1

FDS7066SN3

Q35

4

3

2

G

1

FDS7096N3

SUB*_N1930

16V-10%

4.7uF

.22uF 25V

20%

21

.22uF 25V

20%

2 1

C580

16V-10%

4.7uF

C486

5

6

7

8

9

5

D

6

7

S

8

NC

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

9

5

D

6

7

S

8

NC

21

PKG_TYPE=SO8_P9DR_FRCHLD

Q32

9

4

5

D

6

3

7

2

G

S

8

1

NC

FDS7066SN3

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

VID Termination

+CPU_VTT

TITLE

LINDY PLANAR

DWG NO.

DATE

DC

D1660

R28

1 2

499-1%

R27

1 2

499-1%

R26

1 2

499-1%

R25

1 2

499-1%

R16

1 2

499-1%

R15

1 2

499-1%

1-21-2004_9:57

SUB=SUB*_P1355

12

+

C343

25V-20%

C1689

C1691

2 1

.1uF

25V-20%

C1690

2 1

.1uF

SUB=SUB*_P1355

12

C338

25V-20%

C1701

2 1

C1703

.1uF

12

25V-20%

C1702

.1uF

12

H1_VID0

H1_VID1

H1_VID2

H1_VID3

H1_VID4

H1_VID5

COMPUTER

CORPORATION

AUSTIN,TEXAS

SHEET

7 OF 611/13/2004

16V-10%

4.7uF

560uF

4V-20%

+CPU_VID1

L2

R163

C281

16V-10%

+

560uF

4V-20%

+CPU_VID1

L4

C280

7,12

7,12

7,12

7,12

7,12

7,12

REV.

2 1

C308

0.6uH, 27Amp

1 2

3-5%

1 2

1 2

.001UF

4.7uF

2 1

C302

1 2

21

R153

21

X03

VERTICAL

SUB=SUB*_N1453

50V-10%

VERTICAL

0.6uH, 27Amp

SUB=SUB*_N1453

3-5%

.001UF

50V-10%

1

2

3

B D

CA

+12V

SUB*_P1355

Q90

SUB*_16155

VRD BOM Changes:

X02_TJ_081803

X02_TJ_110503

1

VRD2_VCC

21

220K

220K

R197021R1971

VRD2_PWM3A

8

VRD2_PWM4A

8

+3.3V

8.2K-5%

R4503

21

X02_TJ_081803

VCORE2_PWRGOOD

2

8

DRV2_OD_R

R1981

220K

X03_GT_011804

21

1 2

C1808

5,8,59

33pF 50V

X03_GT_011804

DRV2_OD

8

8

3

FT2N7002LT1

1

2

8

8

5.1-5%

2 1

R264

SUB*_16155

X02_TJ_110503

R1989

1 2

1K-5%

1N914

2-1%

VRD2_PWM1A

DRV2_OD

.22uF 25V

20%

21

X03_GT_011804

VRD2_PHASE1B_SENSE

8

.22uF 25V

1 3

20%

D25

R247

21

VRD2_DRV1

1

BST

2

IN

3

OD

4

VCC

ADP3418

C599

+12V

Q91

3

FT2N7002LT1

2

PWM Control Circuitry

ROOM = VRD2_CTRL

VCORE_EN

5,7,59

R1822

NP

VRD2_VSSSENSE

1uF

1 2

C1729

25V-10%

249K-1%

1 2

R256

H2_VCCSENSE

X00_GT_052203

1 2

0-5%

50V-10%

1000pF

C1730

21

PART_NUMBER=79015

127K-1%

1 2

R235

H2_VSSSENSE

12

R318

3

1 2

0-5%

SUB=SUB*_4053P

DRV2_OD_R

8

SUB*_75EEC

.047uF 25V

C715

1 2

20%

4 4

+CPU_VID2

12

21

.1uF

C473

25V-20%

1 2

100-5%

R1847

11

EN

10

VCORE2_PWRGOOD

5,8,59

VRD2_VSSSENSE

H2_VID0

8,12

H2_VID1

8,12

H2_VID2

8,12

H2_VID3

8,12

H2_VID4

8,12

H2_VID5

8,12

C301

2 1

47pF

50V-5%

R252

12

24K-5% 1K-1%

330pF 50V

R348

1 2

VRD2_VCCSENSE

0-5%

R1823

NP

1 2

0-5%

100K-1%

21

C709

12

15

R297

NP*

12

19

9

7

5

4

3

2

1

6

PWRGD

ILIMIT

DELAY

COMP

FBRTN

VID0

VID1

VID2

VID3

VID4

VID5

GND

VRD2_VCC

8

VRD2_CTRL

ADP3168

C480

12

680pF 50V

R279

R296

NP

1 2

100K-1%

RAMPADJ

21

VCC

PWM1

PWM2

PWM3

PWM4

SW1

SW2

SW3

SW4

CSSUM

CSREF

CSCOMP

RT

FB

R328

1 2

28

14

13

27

26

25

24

23

22

21

20

17

16

18

8

+12V

10-5%

300-5%

1 2

R14

VRD2_PWM1A

VRD2_PWM2A

VRD2_PWM3A

VRD2_PWM4A

R347

1 2

0-5%

487K-1%

50V-10%

3300pF

Phase 1

ROOM = VRD2_PHASE1

x03_sd

50V-10%

1000pF

C856

C648

1 2

1

5.1-5%

2 1

R316

0-5%

21

C476

.1uF

25V-20%

8

DRVH

7

SW

6

PGND

5

DRVL

R1992

1 2

1K-5%

1N914

2-1%

VRD2_PWM3A

8

DRV2_OD

8

R267

1 2

R272

R300

1 2

200K-1%

8

8

8

8

R350

1 2

21

0-5%

73.2K-1%

1 2

R298

SUB*_54672

.01uF 16V

C721

1 2

1 2

SUB*_1U388

R148

15.8K-1% 0-5%

THERMISTOR

NP*

21

VRD2_UGATE1

VRD2_LGATE1

R487

4.7K

1 2

X03_GT_011804

8

1 3

D12

1 2

R248

1

BST

2

IN

3

OD

4

VCC

16V-10%

.47uF

C11

21

R349

0-5%

73.2K-1%

1 2

R295

SUB*_54672

C711

1 2

41.2K-1%

R332

1 2

21

Q70

9

4

5

D

6

3

7

2

G

S

8

1

NC

FDS7096N3

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

4

3

2

1

FDS7066SN3

R494

4.7K

1 2

Phase 3

ROOM = VRD2_PHASE3

VRD2_PHASE3B_SENSE

.22uF 25V

50V-10%

x03_sd

1000pF

C858

C647

20%

21

VRD2_DRV3

ADP3418

.22uF 25V

20%

21

73.2K-1%

1 2

R293

SUB*_54672

R87

C477

.1uF

25V-20%

DRVH

SW

PGND

DRVL

C598

1 2

73.2K-1%

1 2

R294

SUB*_54672

24.9K-1%

NP*

21

21

8

VRD2_UGATE3

7

6

5

VRD2_LGATE3

R500

4.7K

1 2

VRD2_PHASE1B_SENSE

VRD2_PHASE2B_SENSE

VRD2_PHASE3B_SENSE

VRD2_PHASE4B_SENSE

X03_GT_011804

R86

1 2

NP

Q43

9

D

G

S

NC

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

R493

4.7K

1 2

8

8

8

8

3

D

2

S

.22uF 25V

1 2

20%

5

6

7

8

Q62

9

4

3

2

G

S

1

FDS7096N3

SUB*_N1930

+CPU_VID2

Q8

2N7002

1

G

16V-10%

4.7uF

C1704

2 1

25V-20%

C624

2 1

.1uF

5

D

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

4

3

2

1

FDS7066SN3

R418

1 2

0-5%

R501

NP

4.7K

25V-20%

C1706

2 1

.1uF

C1705

.22uF 25V

1 2

20%

Q67

9

D

G

S

NC

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

8

NP

21

16V-10%

4.7uF

C594

5

6

7

8

VRD2_PWM1A

C335

1 2

.047uF

16V-10%

ALT_LLINE

C1732

2 1

25V-20%

.1uF

Q44

9

4

3

2

G

S

1

FDS7096N3

SUB*_N1930

Q42

4

3

2

G

1

FDS7066SN3

25V-20%

2 1

.1uF

C1722

2 1

X03_GT_011904

R1715

NP

1 2

68K-5%

R1716

NP

68K-5%

7

5

D

6

7

8

NC

20%

PKG_TYPE=SO8_P9DR_FRCHLD

9

5

D

6

7

S

8

NC

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

4

C1723

3

2

1

FDS7096N3

VRD2_PWM3A

21

VRD2_PWM4A

16V-10%

4.7uF

.22uF 25V

C646

1 2

Q63

9

D

G

S

NC

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

C1707

2 1

25V-20%

.1uF

5

6

7

8

Q45

9

4

D

3

2

G

S

1

NC

FDS7066SN3

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

8

8

25V-20%

.1uF

C1708

2 1

.22uF 25V

20%

21

5

6

7

8

2 1

subsys done

16V-10%

4.7uF

2 1

+

560uF

4V-20%

0.6uH, 27Amp

L17

C326

SUB=SUB*_N1453

SUB*_16155

X02_TJ_110503

C344

C1709

+CPU_VID2

VERTICAL

12

12

3-5%

R172

1 2

C283

1 2

.001UF

50V-10%

SUB*_P1355

16V-10%

4.7uF

2 1

+

560uF

4V-20%

+CPU_VID2

C328

SUB*_16155

X02_TJ_110503

16V-10%

4.7uF

2 1

C623

C1724

25V-20%

2 1

.1uF

25V-20%

2 1

.1uF

C1725

12

C424

C1726

L5

0.6uH, 27Amp

1 2

3-5%

R182

1 2

21

C299

.001UF

FDS7066N3 is local. Waiting on library symbol.

INTEGRATED VRD 10.1 VOLTAGE

REGULATOR FOR PROC_2

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

A B

+12V

Q92

3

FT2N7002LT1

R1990

1 2

1

1K-5%

2

1 3

1N914

D38

2-1%

R249

21

VRD2_PWM2A

8

DRV2_OD

8

5.1-5%

2 1

R263

.22uF 25V

20%

21

+12V

Q93

3

FT2N7002LT1

R1991

1 2

1

1K-5%

2

1N914

31

1 2

2-1%

VERTICAL

SUB=SUB*_N1453

8

8

VRD2_PWM4A

DRV2_OD

5.1-5%

12

R262

.22uF 25V

20%

50V-10%

21

Input Filtering

+12V

SUB*_P1355

C583

+

2 1

270uF

16V-20%

C820

12

+

560uF

ROOM = VRD2_PHASE2

X03_GT_011804

VRD2_PHASE2B_SENSE

8

.22uF 25V

50V-10%

C650

1 2

20%

C478

.1uF

25V-20%

VRD2_DRV2

1

BST

2

IN

3

OD

4

VCC

ADP3418

C595

Phase 4

ROOM = VRD2_PHASE4

VRD2_PHASE4B_SENSE

8

.22uF 25V

50V-10%

1000pF

C649

20%

D34

R246

C10

4V-20%

21

1

BST

2

IN

3

OD

4

VCC

C6

C475

1 2

.1uF

25V-20%

VRD2_DRV4

ADP3418

.1uF

1 2

50V-20%

21

Phase 2

x03_sd

1000pF

C857

NP*

21

21

8

DRVH

7

SW

6

PGND

5

DRVL

VRD2_LGATE2

R490

4.7K

1 2

x03_sd

C859

NP*

8

DRVH

7

SW

6

PGND

5

DRVL

21

R486

4.7K

21

C7

.1uF

50V-20%

SUB*_4053P

R495

1 2

VRD2_LGATE4

21

R485

C23

1 2

4.7K

4.7K

1uF

25V-10%

Q52

9

4

3

2

G

S

1

FDS7096N3

SUB*_N1930

Q50

9

4

3

2

G

S

1

FDS7096N3

SUB*_N1930

VRD2_UGATE4

Q49

4

3

2

G

1

FDS7066SN3

C22

1 2

SUB*_4053P

5

D

6

7

8

NC

20%

PKG_TYPE=SO8_P9DR_FRCHLD

Q56

9

4

D

3

2

G

S

1

NC

FDS7066SN3

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

5

D

6

7

8

NC

20%

PKG_TYPE=SO8_P9DR_FRCHLD

9

5

D

6

7

S

8

NC

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

1uF

25V-10%

16V-10%

4.7uF

.22uF 25V

C652

1 2

5

6

7

8

16V-10%