MSI MS-9141 Schematic 1400

5

4

3

2

1

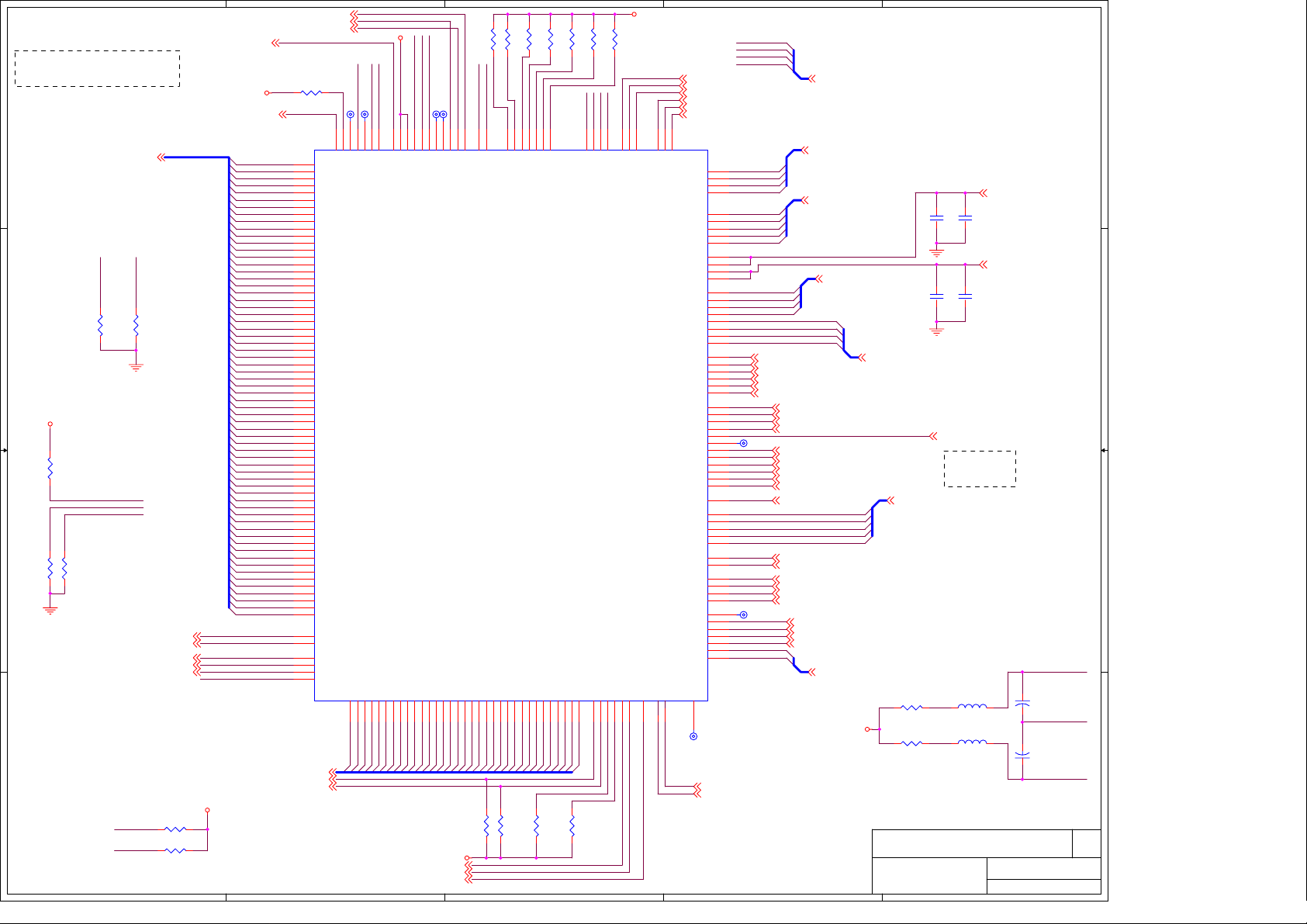

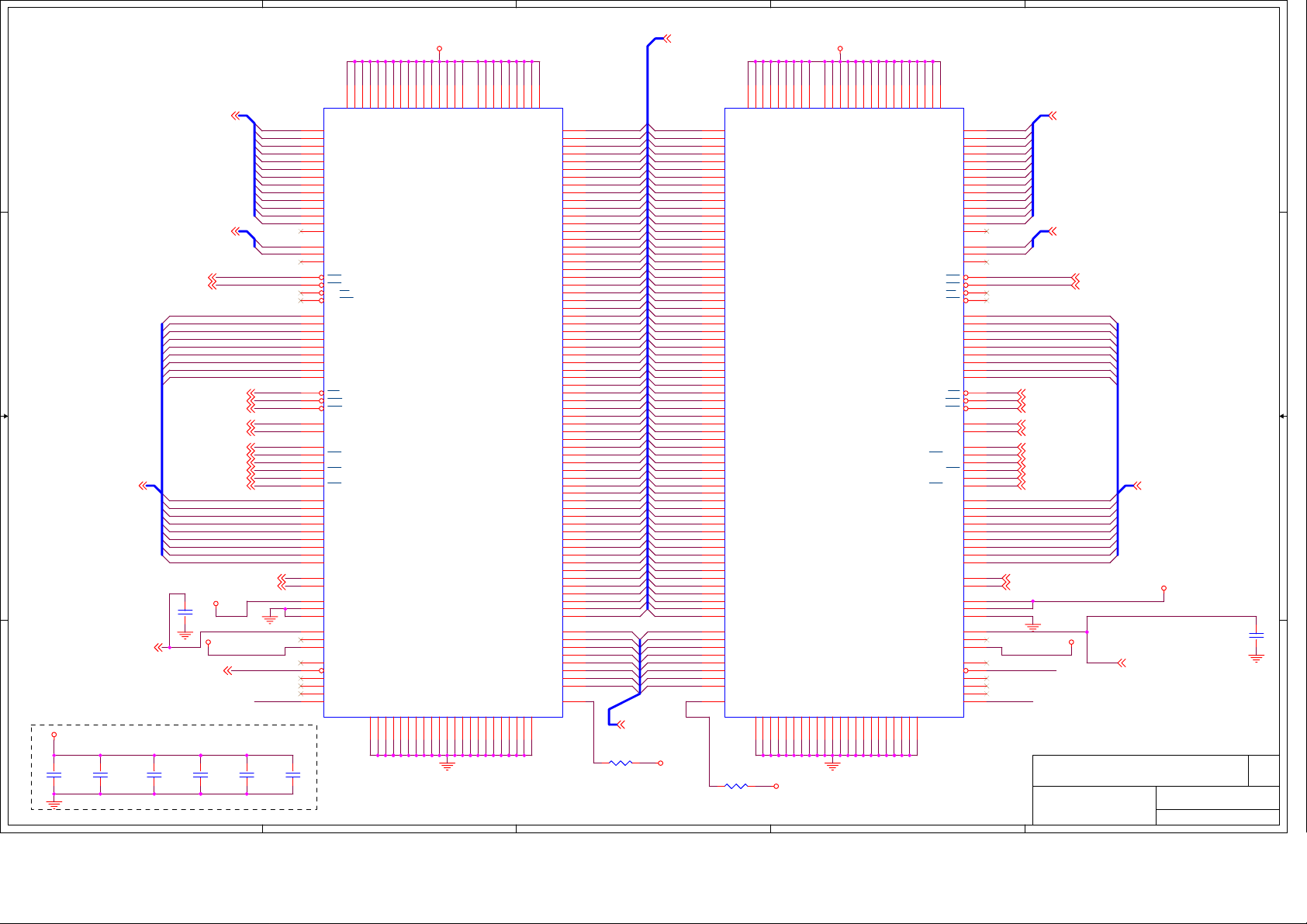

INTEL (R) PLACER CHIPSET

MS-9141

D D

DUAL PRESTONIA PROCESSORS SCHEMATICS

01 INDEX

02 BLOCK DIAGRAM

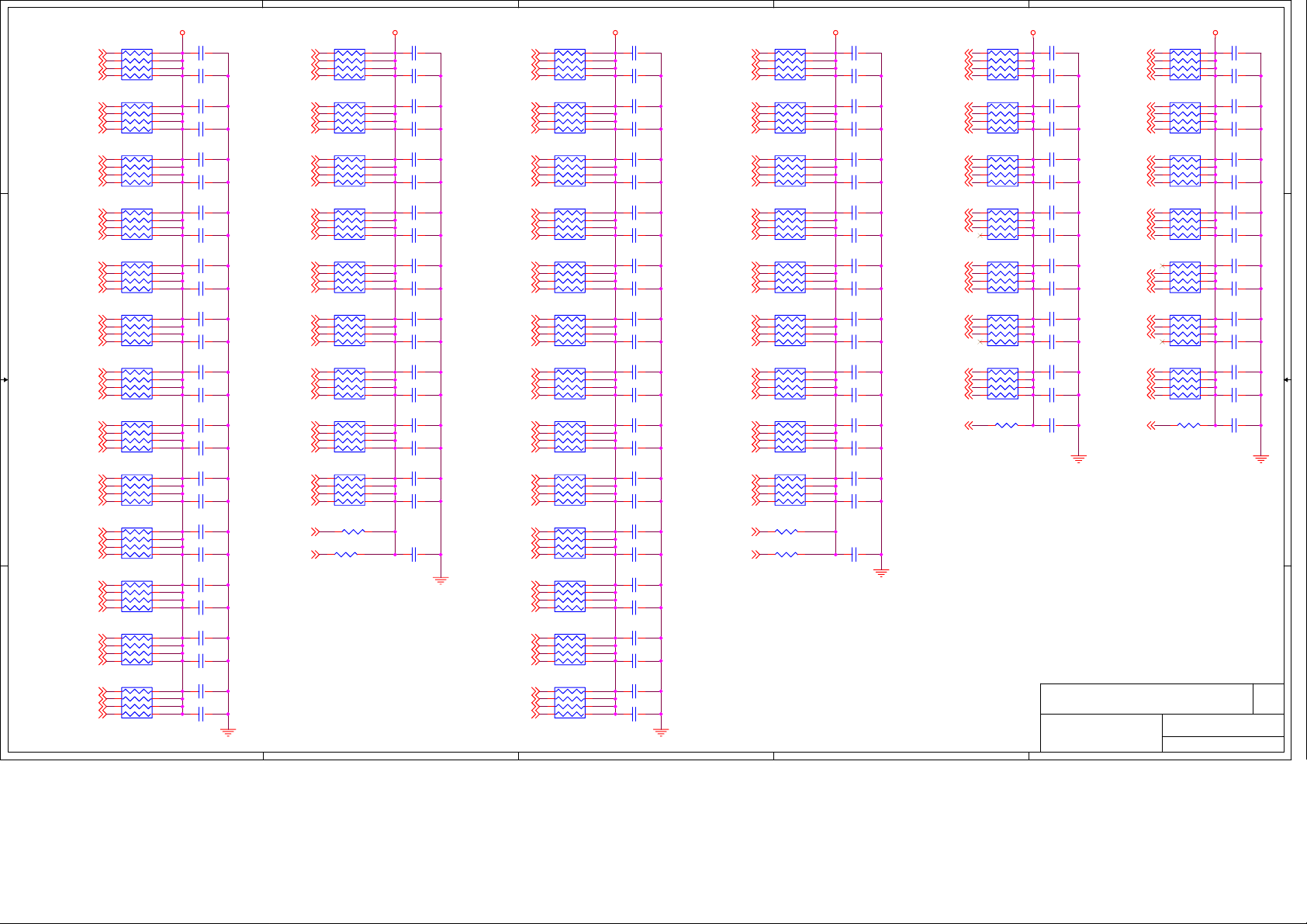

03 CPU 1_SIGNAL

04 CPU 1_POWER

05 CPU 2_SIGNAL

06 CPU 2_POWER

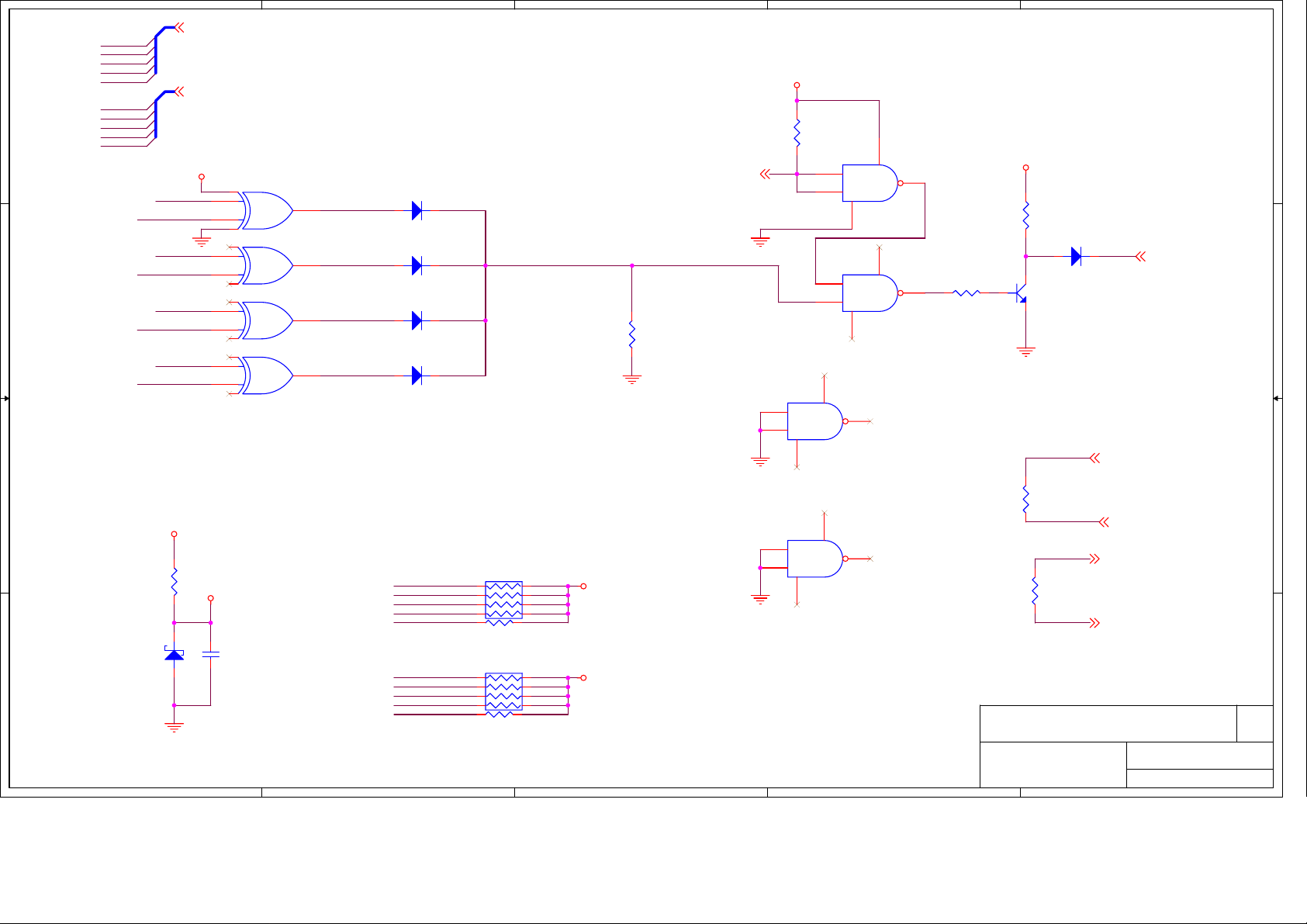

07 VID COMPARE

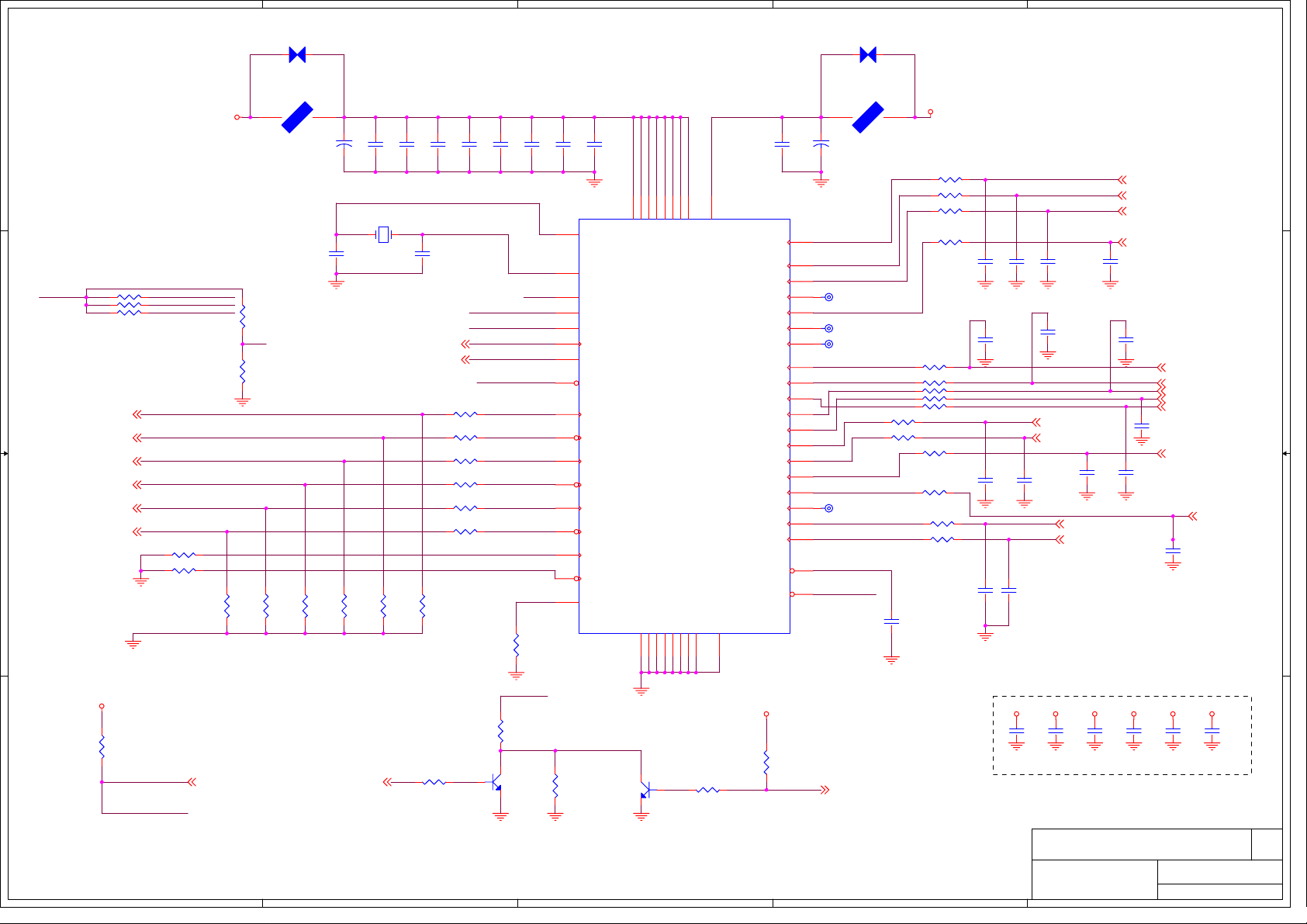

08 CLOCK

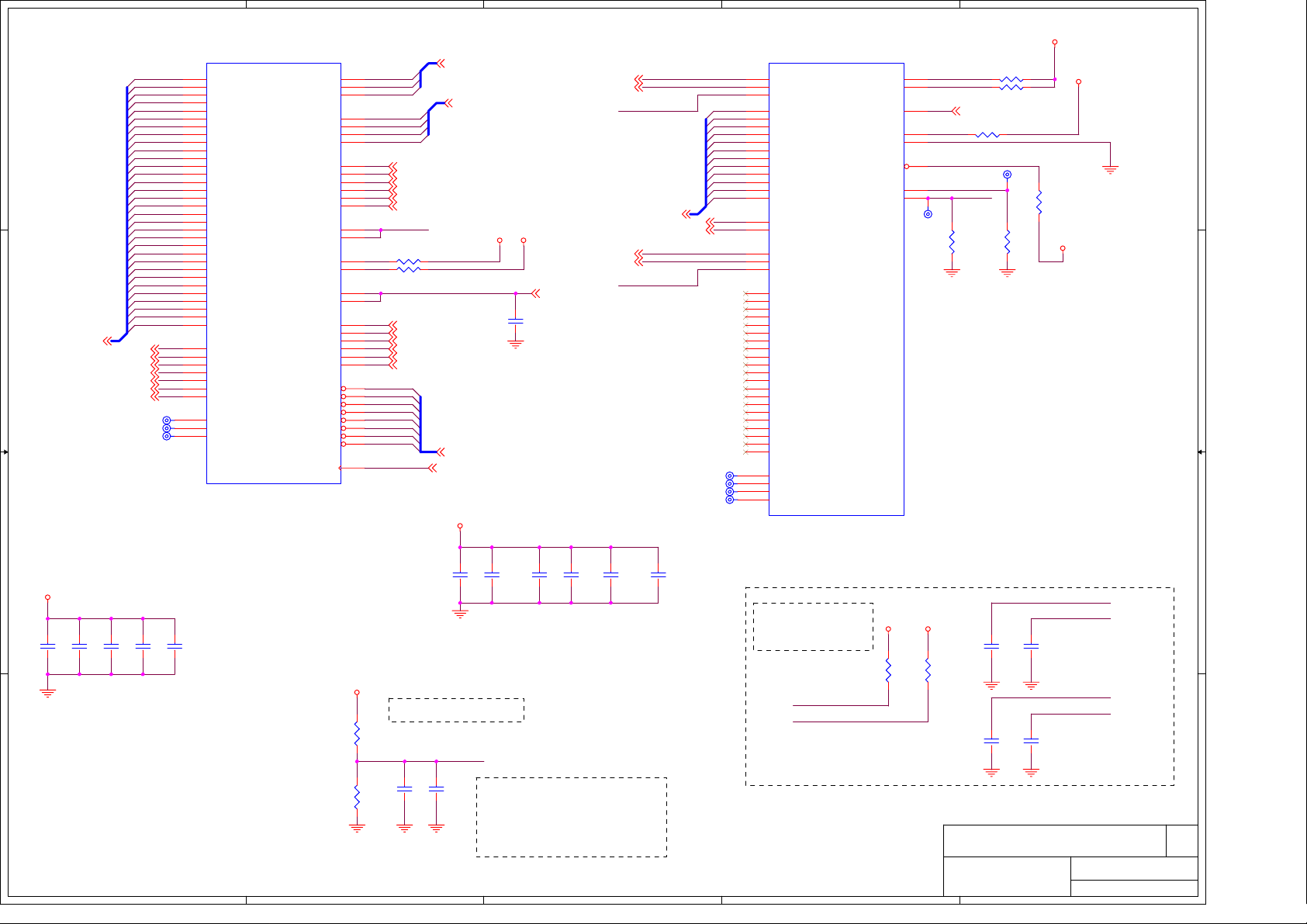

09 MCH_HOST

C C

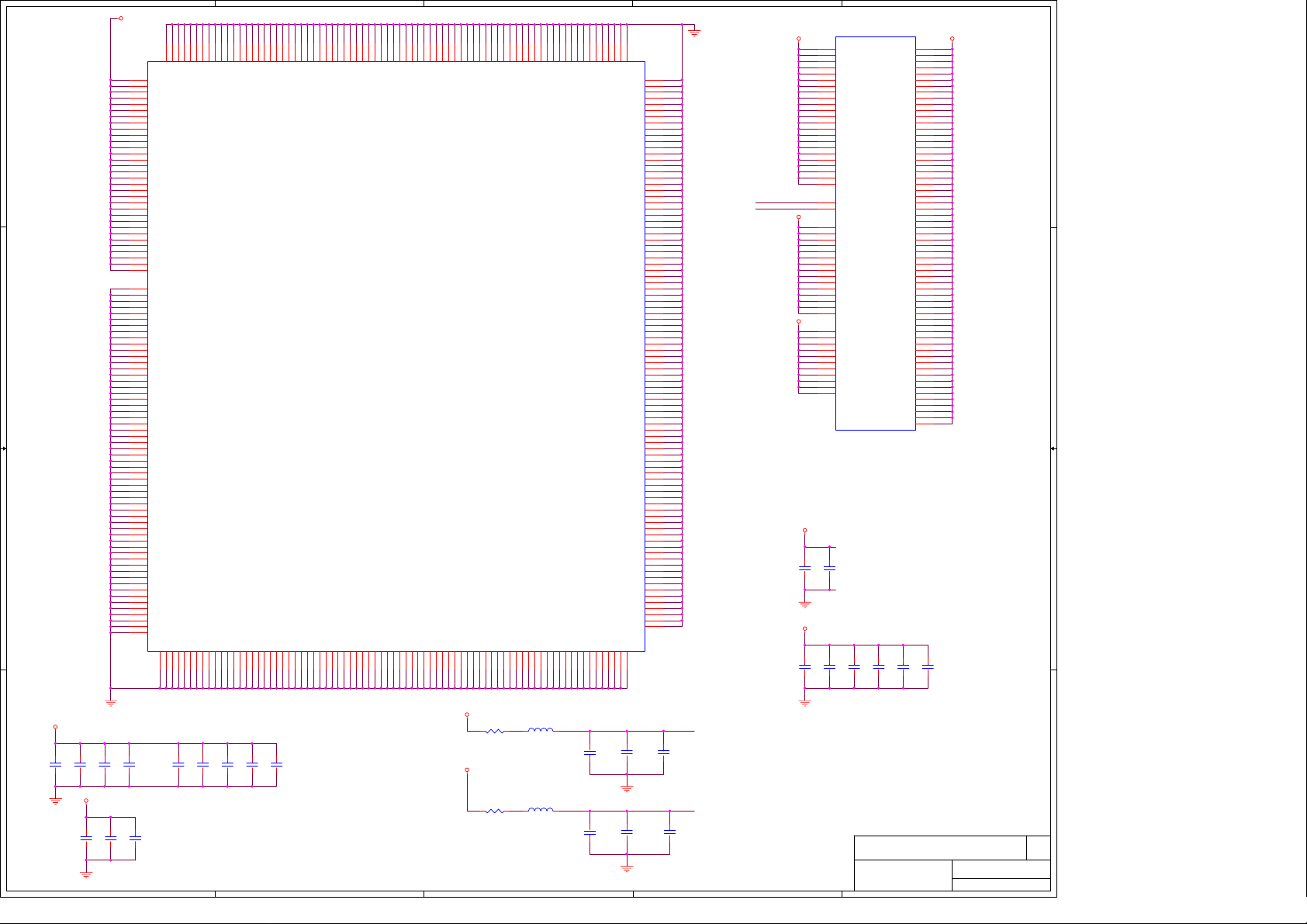

10 MCH_AGP&HLA&HLB

11 MCH_DDR CHA&CHB

12 MCH_POWER&GND

13 DDR CHA DIMMS

14 DDR CHB DIMMS

15 DDR CHA&CHB PARALLEL TERM

16 DDR VREFS&DECOUPLING

17 AGP 8X CONNECTOR

18 AGP>L+&HUBLINK VREFS

19 ICH4-1

20 ICH4-2

B B

21 ICH4-3

22 ICH4 PULL UP

32 FWH

33 COM PORT

34 PRINTER PORT

35 KB&MS

36 SYSTEM FANS

37 POWER CONNECTOR

38 FRONT PANNEL

39 AD1885

40 SPEAKER OUT MIC&LINE IN

41 SMBUS ISOLATION

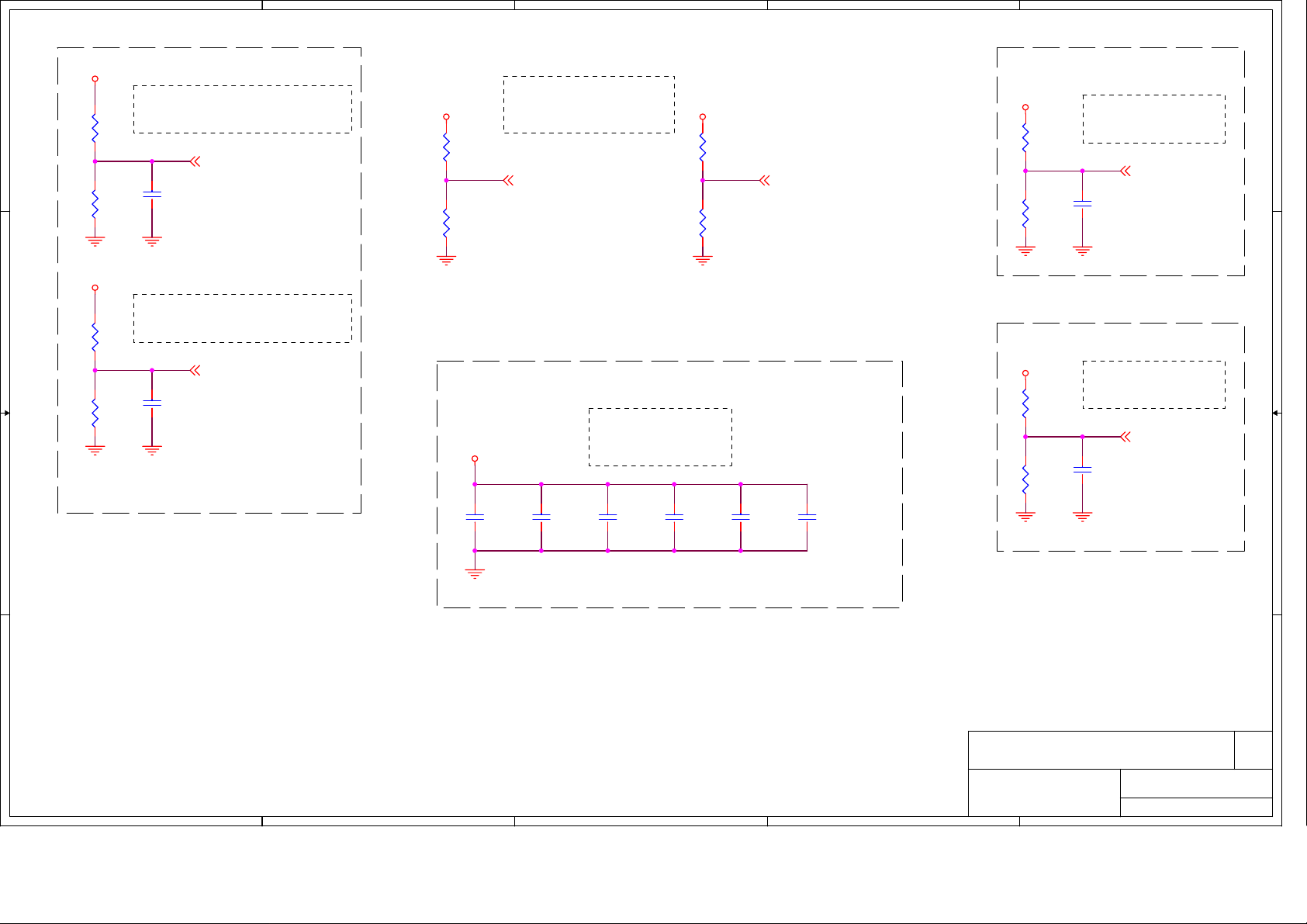

42 Mechanical Part

43 ACPI CIRCUIT

44 SYSTEM VOLTAGE REGULATOR

45 +2.5V REGULATOR

46 LAN1 82540

47 LAN1 82540#2

48 LAN2 82551

49 LAN2 82551#2

50 CLOCK DIAGRAM

51 GENERAL SPEC

52 MANUAL PART

23 CPU VRM

24 PCI32 SLOT1

25 PCI32 SLOT2

26 PCI32 SLOT3

27 PCI32 SLOT4

28 SIO(PC87366)

29 SIO HARDWARE MONITOR

30 IDE

31 USB

A A

Title

Document Number

5

4

3

2

Micro Star Restricted Secret

INDEX

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Last Revision Date:

Tuesday, March 18, 2003

Sheet

152

1

Rev

00E

of

5

4

3

2

1

PRESTONIA PROCESSOR PRESTONIA PROCESSOR

SOCKET 604 CPU1 SOCKET 604 CPU2

D D

p3~4 p5~6 p28 p8

VRD 9.1

DDR DIMM 1

DDR DIMM 3

CLOCK GEN

CHANNEL A

PLACER MCH

C C

AGP 8X/4X

p18

ICH4

p20~23

p9~12

CHANNEL B

p13 p13

IDE Primary

IDE Secondary

p42

p42

DDR DIMM 2

p14 p14

DDR DIMM 4

USB 2.0

PORTx6

B B

p43

FLOPPY

PARALLEL PORT

SERIAL PORT

COM1

SERIAL PORT

COM2

p40

p46

p45

LPC SIO

NS/PC87366

FWH(8Mbit)

Onboard

AC'97 Codec

p28

p32

PCI 32 SLOT

PCI 32 SLOT

PCI 32 SLOT

PCI 32 SLOT

p39p45

p24

p25

p26

p27

GIGA LAN

82540

p46~47

A A

10/100 LAN

82551

5

4

3

2

p46~47

Title

Document Number

Micro Star Restricted Secret

BLOCK DIAGRAM

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Last Revision Date:

Tuesday, March 18, 2003

Sheet

252

1

Rev

00E

of

5

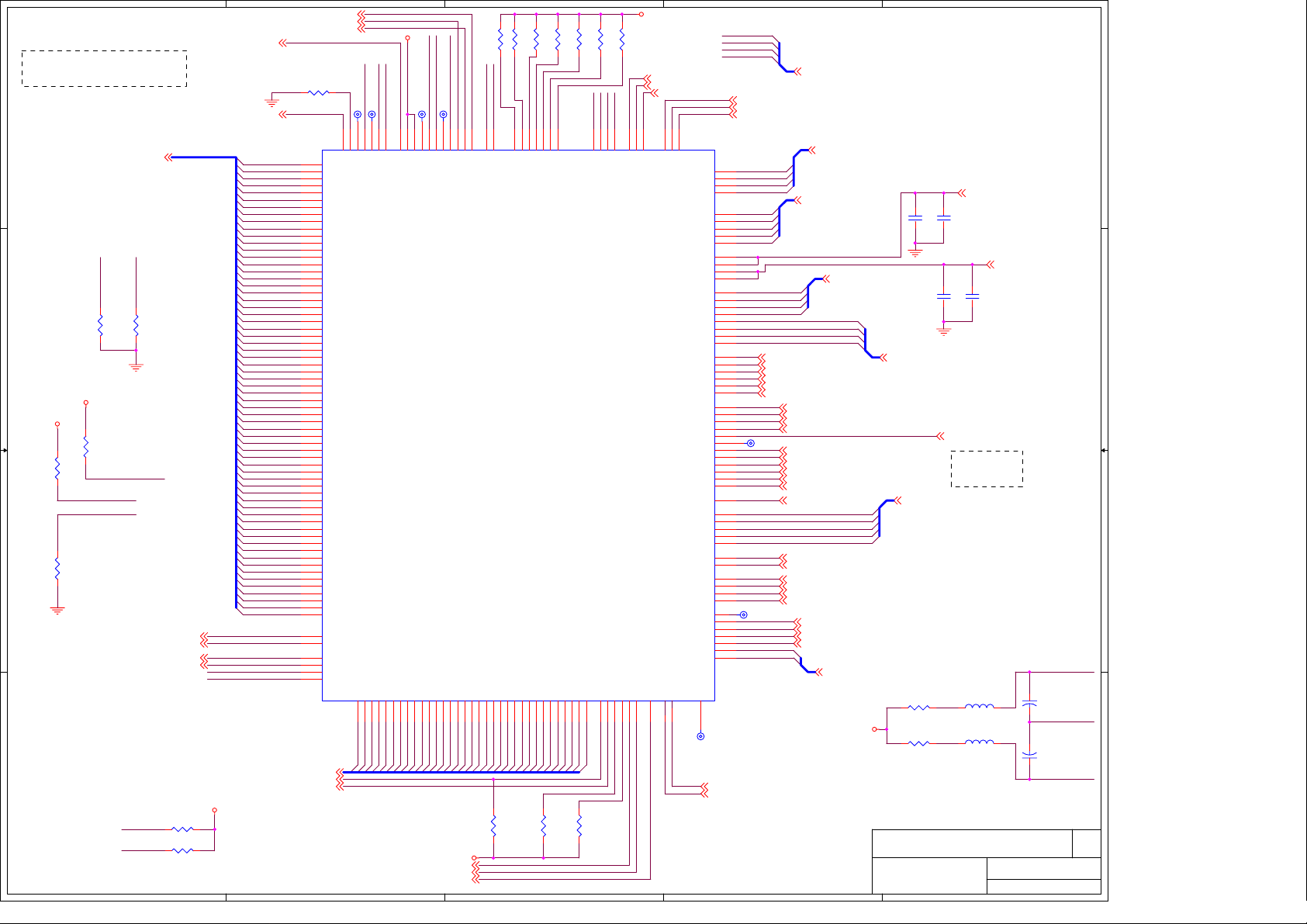

CPU_SM_WP<5,20>

CPU THERMAL SENSOR SMBUS = 30

CPU IDROM SMBUS = A8

VCC_CORE

CPU0_BSEL0

CPU0_BSEL1

+3_3V

SKTOCC_0_L<8>

D D

FSB_HD_L[0..63]<5,9>

CPU0_COMP1

CPU0_COMP0

R91

R38

49.9-1%

CPU0_BSEL1

CPU0_BSEL0

5

49.9-1%

CPU0_BSEL0<8>

FSB_AP0_L<5,9>

FSB_AP1_L<5,9>

P0_BCLK0<8>

P0_BCLK1<8>

R151 1K

R178 1K

C C

+3_3V

R25

1K

CPU0_FSTR0_AB28

CPU0_FSTR0_Y29

CPU0_FSTR0_AA28

R30

B B

A A

R29

1K

1K

FSB_HD_L0

FSB_HD_L1

FSB_HD_L2

FSB_HD_L3

FSB_HD_L4

FSB_HD_L5

FSB_HD_L6

FSB_HD_L7

FSB_HD_L8

FSB_HD_L9

FSB_HD_L10

FSB_HD_L11

FSB_HD_L12

FSB_HD_L13

FSB_HD_L14

FSB_HD_L15

FSB_HD_L16

FSB_HD_L17

FSB_HD_L18

FSB_HD_L19

FSB_HD_L20

FSB_HD_L21

FSB_HD_L22

FSB_HD_L23

FSB_HD_L24

FSB_HD_L25

FSB_HD_L26

FSB_HD_L27

FSB_HD_L28

FSB_HD_L29

FSB_HD_L30

FSB_HD_L31

FSB_HD_L32

FSB_HD_L33

FSB_HD_L34

FSB_HD_L35

FSB_HD_L36

FSB_HD_L37

FSB_HD_L38

FSB_HD_L39

FSB_HD_L40

FSB_HD_L41

FSB_HD_L42

FSB_HD_L43

FSB_HD_L44

FSB_HD_L45

FSB_HD_L46

FSB_HD_L47

FSB_HD_L48

FSB_HD_L49

FSB_HD_L50

FSB_HD_L51

FSB_HD_L52

FSB_HD_L53

FSB_HD_L54

FSB_HD_L55

FSB_HD_L56

FSB_HD_L57

FSB_HD_L58

FSB_HD_L59

FSB_HD_L60

FSB_HD_L61

FSB_HD_L62

FSB_HD_L63

FSB_HA_L[3..35]<5,9>

SMB_ALERT_CPU_L<5,20>

SMBUS_CPU_DATA<5,7>

R154 51-1%

SOCKET_604

CPU0_BR0_L<5,9>

CPU1_BR0_L<5>

4

SMBUS_CPU_CLK<5,7>

TP7

A3B5D26

CPU1A

Y26

D0#

AA27

D1#

AA25

AD27

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AD10

AD8

AC9

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AC5

AA8

AB6

AA3

AB3

Y24

Y23

AE9

E10

ODTEN

D2#

SKTOCC#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

Y9

D62#

D63#

AP0#

D9

AP1#

Y4

BCLK0

W5

BCLK1

BSEL0

BSEL1

4

VSSA_P0

TP8

AA5

B27

VSSA

VSSSENSE

A3#

A4#

A22

A20

B18

FSB_HA_L4

FSB_HA_L3

FSB_HA_L5

VCCIOPLL_P0

VCCA_P0

AD4

AB4

VCCA

VCCIOPLL

VCCSENSE

A5#

A6#

A7#

A8#

C18

A19

C17

FSB_HA_L6

FSB_HA_L8

FSB_HA_L7

+3_3V

CPU0_FSTR0_Y29

AD29

AE29

AE28

Y29

SM_WP

SM_VCC1

SM_VCC0

TP9

CPU0_FSTR0_AA28

AA28

AB28

SM_TS_A1

SM_TS_A0

SM_EP_A2

TP10

AB29

AA29

AC29

SM_DAT

SM_EP_A1

SM_EP_A0

AC28

AD28

SM_CLK

SM_ALERT

R14951R150

CPU0_COMP1

CPU0_COMP0

E16

AD16

COMP1

COMP0

Prestonia 604

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

D17

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

FSB_HA_L13

FSB_HA_L14 CPU0_FSTR0_AB28

FSB_HA_L18

FSB_HA_L19

FSB_HA_L16

FSB_HA_L17

49.9-1%

FSB_HA_L22

FSB_HA_L20

FSB_HA_L23

FSB_HA_L21

R39

FSB_HA_L25

FSB_HA_L24

FSB_HA_L11

FSB_HA_L10

FSB_HA_L12

FSB_HA_L9

FSB_HA_L15

VCC_CORE

FSB_BNR_L<4,5,9>

FSB_BPRI_L<5,9>

FSB_BINIT_L<4,5,9>

51

W6W7W8Y6AA7

TESTHI0

TESTHI1

TESTHI2

TESTHI3

A25#

A26#

A27#

A28#

D13A9B8

E13

FSB_HA_L27

FSB_HA_L28

FSB_HA_L29

FSB_HA_L26

R24

49.9-1%

3

R146

R152

R145

51

51

51

AD5

AE5

TESTHI4

TESTHI5

TESTHI6

A29#

A30#

A31#

A32#

A33#

A34#

D12

C11B7A6A7C9C8D20

FSB_HA_L32

FSB_HA_L30

FSB_HA_L31

FSB_HA_L35

FSB_HA_L33

FSB_HA_L34

R143

R144

49.9-1%

49.9-1%

3

R141

51

FSB_DEP_L2

FSB_DEP_L1

FSB_DEP_L3

FSB_DEP_L0

AE17

AC15

AE19

DP3#

DP2#

DP1#

A35#

BR0#

BR1#

F12

AC18

DP0#

BR2#

E11

D10

BR3#

R133

51

E25

F20

C24

TDO

BNR#

D23

VCC_CORE

E24

TDI

TCK

BPRI#

BINIT#

F11

E19

F24

A25

TMS

TRST#

TRDY#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

STPCLK#

THERMTRIP#

PWRGD

PROCHOT#

IGNNE#

RESET#

MCERR#

DEFER#

ADSTB0#

ADSTB1#

DBSY#

DRDY#

F18

E18

ITP_TDO_P0 <4,5>

ITP_TDI_P0 <4>

ITP_TCK_P <4,5>

FSB_TRDY_L <5,9>

ITP_TRST_L <4,5>

ITP_TMS_P <4,5>

AB9

DBI3#

AE12

DBI2#

AD22

DBI1#

AC27

DBI0#

F3

VID0

E3

VID1

D3

VID2

C3

VID3

B3

VID4

F9

F23

W9

W23

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

F6

BPM0#

F8

BPM1#

E7

BPM2#

F5

BPM3#

E8

BPM4#

E4

BPM5#

AE6

SLP#

D4

C27

SMI#

F26

AB7

B25

D6

INIT#

G23

LINIT1

B24

LINIT0

E27

FERR#

C26

F27

A20M#

Y8

B19

REQ0#

B21

REQ1#

C21

REQ2#

C20

REQ3#

B22

REQ4#

A17

LOCK#

D7

C6

RSP#

F21

RS2#

D22

RS1#

E21

RS0#

E5

IERR#

C23

A23

HITM#

E22

HIT#

D19

ADS#

FSB_ADSTB_L0

F17

FSB_ADSTB_L1

F14

KEY604

AE30

TP13

FSB_DRDY_L <5,9>

FSB_DBSY_L <5,9>

2

FSB_DEP_L0

FSB_DEP_L1

FSB_DEP_L2

FSB_DEP_L3

FSB_DBI_L3

FSB_DBI_L2

FSB_DBI_L1

FSB_DBI_L0

VID_P0_0

VID_P0_1

VID_P0_2

VID_P0_3

VID_P0_4

FSB_HDSTBP_L3

FSB_HDSTBP_L2

FSB_HDSTBP_L1

FSB_HDSTBP_L0

FSB_HDSTBN_L3

FSB_HDSTBN_L2

FSB_HDSTBN_L1

FSB_HDSTBN_L0

CPU_BPM_L_0 <4,5>

CPU_BPM_L_1 <4,5>

CPU_BPM_L_2 <4,5>

CPU_BPM_L_3 <4,5>

CPU_BPM_L_4 <4,5>

CPU_BPM_L_5 <4,5>

TP11

TP12

2

FSB_DEP_L[0..3] <5,9>

FSB_DBI_L[0..3] <5,9>

VID_P0_[0..4] <7,23>

FSB_HDSTBP_L[0..3] <5,9>

CPU_CPUSLP_L <4,5,19>

CPU_STPCLK_L <4,5,19>

CPU_SMI_L <4,5,19>

CPU_THERMTRIP_L <4,5,21>

CPU_INIT_L <4,5,19,32>

CPU_LINIT1_NMI <4,5,19>

CPU_LINIT0_INTR <4,5,19>

CPU_FERR_L <4,5,19>

CPU_IGNNE_L <4,5,19>

CPU_A20M_L <4,5,19>

FSB_CPURST_L <4,5,9>

FSB_REQ_L0

FSB_REQ_L1

FSB_REQ_L2

FSB_REQ_L3

FSB_REQ_L4

FSB_LOCK_L <5,9>

FSB_MCERR_L <4,5,9>

FSB_RSP_L <5,9>

FSB_RS2_L <5,9>

FSB_RS1_L <5,9>

FSB_RS0_L <5,9>

FSB_DEFER_L <5,9>

FSB_HITM_L <4,5,9>

FSB_HIT_L <4,5,9>

FSB_ADS_L <5,9>

FSB_ADSTB_L[0..1] <5,9>

VCC_CORE

FSB_HDSTBN_L[0..3] <5,9>

CPU_PWR_GD <4,5,20>

FSB_REQ_L[0..4] <5,9>

R167 1

R137 1

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C176

C42

220p

220p

C45

C225

220p

220p

PLACE CLOSE

CPU1.AB7

L14 4.7uH-0805

1 2

L13 4.7uH-0805

1 2

CPU 1_SIGNAL

1

GTL_VREF2_P0 <18>

GTL_VREF1_P0 <18>

VCCA_P0

C261

22u-10V

VSSA_P0

C251

22u-10V

VCCIOPLL_P0

Last Revision Date:

Tuesday, March 18, 2003

Sheet

352

1

Rev

00E

of

5

VCC_CORE

D D

C C

B B

A A

CPU1B

W27

W25

SOCKET_604

5

A14

A18

A24

A28

B12

B20

B26

B29

C10

C16

C22

C28

D14

D18

D24

D29

E12

E20

E26

E28

F10

F16

F22

F29

G24

G26

G28

H23

H25

H27

H29

K23

K25

K27

K29

L24

L26

L28

M23

M25

M27

M29

N23

N25

N27

N29

P24

P26

P28

R23

R25

R27

GN33

GN34

GN35

GN36

GN37

GN38

GN39

GN40

A2

VCC

A8

VCC

VCC

VCC

EMI_GND1

EMI_GND2

VCC

VCC

B6

VCC

VCC

VCC

VCC

VCC

C2

VCC

C4

VCC

VCC

VCC

VCC

VCC

D8

VCC

VCC

VCC

VCC

VCC

E2

VCC

E6

VCC

VCC

VCC

VCC

VCC

F4

VCC

VCC

VCC

VCC

VCC

G2

VCC

G4

VCC

G6

VCC

G8

VCC

VCC

VCC

VCC

H3

VCC

H5

VCC

H7

VCC

H9

VCC

VCC

VCC

VCC

VCC

J2

VCC

J4

VCC

J6

VCC

J8

VCC

J24

VCC

J26

VCC

J28

VCC

K3

VCC

K5

VCC

K7

VCC

K9

VCC

VCC

VCC

VCC

VCC

L2

VCC

L4

VCC

L6

VCC

L8

VCC

VCC

VCC

VCC

M3

VCC

M5

VCC

M7

VCC

M9

VCC

VCC

VCC

VCC

VCC

N3

VCC

N5

VCC

N7

VCC

N9

VCC

VCC

VCC

VCC

VCC

P2

VCC

P4

VCC

P6

VCC

P8

VCC

VCC

VCC

VCC

R3

VCC

R5

VCC

R7

VCC

R9

VCC

VCC

VCC

VCC

VCC

VCC

EMI_GND10

GN42

GN41

VSS

VSS

VSS

EMI_GND3

EMI_GND11

GN43

GN44

VSS

EMI_GND4

EMI_GND5

EMI_GND6

EMI_GND7

EMI_GND8

EMI_GND9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

Prestonia_PWR

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

EMI_GND12

EMI_GND13

EMI_GND14

EMI_GND15

EMI_GND16

GN45

GN46

GN47

GN48

A5

A11

A21

A27

A29

B2

B9

B15

B17

B23

B28

C7

C13

C19

C25

C29

D2

D5

D11

D21

D27

D28

E9

E15

E17

E23

E29

F2

F7

F13

F19

F25

F28

G3

G5

G7

G9

G25

G27

G29

H2

H4

H6

H8

H24

H26

H28

J3

J5

W29

Y2

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

4

CPU1C

M24

M26

M28

TP103

W24

W26

W28

AA15

AA17

AA23

AB11

AB21

AB27

AC2

AC7

AC13

AC19

AC25 AD3

SOCKET_604

4

GN21

GN22

GN23

GN24

GN25

GN26

GN27

GN28

GN29

GN30

GN31

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

J29

K24

K26

K28

L23

L25

L27

L29

N24

N26

N28

P23

P25

P27

P29

R24

R26

R28

T23

T25

T27

T29

U24

U26

U28

V23

V25

V27

V29

W2

W4

Y13

Y19

Y25

AA2

AA9

AB5

MTG_GND21

MTG_GND22

MTG_GND23

MTG_GND24

GN1

MTG_GND1

GN2

MTG_GND2

GN3

MTG_GND3

GN4

MTG_GND4

GN5

MTG_GND5

GN6

MTG_GND25

MTG_GND6

VSS

K2

VSS

K4

VSS

K6

VSS

K8

VSS

VSS

VSS

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

VSS

VSS

VSS

VSS

M2

VSS

M4

VSS

M6

VSS

M8

VSS

VSS

VSS

VSS

N2

VSS

N4

VSS

N6

VSS

N8

VSS

VSS

VSS

VSS

P3

VSS

P5

VSS

P7

VSS

P9

VSS

VSS

VSS

VSS

VSS

R2

VSS

R4

VSS

R6

VSS

R8

VSS

VSS

VSS

VSS

T3

VSS

T5

VSS

T7

VSS

T9

VSS

VSS

VSS

VSS

VSS

U2

VSS

U4

VSS

U6

VSS

U8

VSS

VSS

VSS

VSS

V3

VSS

V5

VSS

V7

VSS

V9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y5

VSS

Y7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

GN32

MTH_GND26

MTG_GND27

MTG_GND28

MTG_GND29

MTG_GND30

MTG_GND31

MTG_GND32

Prestonia_PWR

MTG_GND7

MTG_GND8

MTG_GND9

MTG_GND10

MTG_GND11

MTG_GND12

MTG_GND13

GN7

GN8

GN9

GN10

GN11

GN12

GN13

3

TP14

A1

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD0

RSVD1

GAL_VDD4

GAL_VDD5

GAL_VDD6

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

GAL_VSS33

GAL_VSS34

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD11

RSVD12

RSVD13

RSVD9

RSVD10

RSVD14

RSVD15

RSVD16

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MTG_GND14

MTG_GND15

MTG_GND16

MTG_GND17

MTG_GND18

MTG_GND19

MTG_GND20

GN14

GN15

GN16

GN17

GN18

GN19

GN20

CPU1_DIODE_P

CPU1_DIODE_N

FOR PRESTONIA 604 ONLY

3

NOCONA_A4_P0

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

A15

A16

A26

B1

C5

D25

W3

Y3

Y27

Y28

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

VCC_CORE

NOCONA_C1_P0

NOCONA_AC30_P0

TP15

TP16

TP17

TP18

NOCONA_C5_P0

TP19

TP20

TP21

CPU1_DIODE_P

CPU1_DIODE_N

TP22

TP23

TP24

TP25

TP26 C162

CPU1_DIODE_P <28>

CPU1_DIODE_N <28>

C230

1u-0805

C219

1u-0805

C246

1u-0805

C164

22u-1210

C138

22u-1210

C232

1u-0805

C43

1u-0805

C48

1u-0805

C177

1u-0805

C114

X_0.1u

C121

X_0.1u

C186

0.1u

C55

0.1u

C239

0.1u

C240

0.1u

C231

0.1u

C139

0.1u

C961

0.1u

C964

0.1u

C967

0.1u

C972

0.1u

C969

0.1u

C140

0.1u

0.1u

C44

0.1u

C970

0.1u

C152

0.1u

C161

0.1u

C236

0.1u

2

C71-8210211-F06

C270

820-2.5V

C523

820-2.5V

C272

820-2.5V

C271

820-2.5V

C6

820-2.5V

C275

820-2.5V

C7

X_820-2.5V

C267

820-2.5V

C522

820-2.5V

C12

820-2.5V

C49

1u-0805

C1413

820-2.5V

C1414

820-2.5V

C244

22u-1206

C178

22u-1206

C33

22u-1206

C39

22u-1206

C38

22u-1206

C67

22u-1206

C160

22u-1206

C481

22u-1206

C150

22u-1206

C40

22u-1206

C51

22u-1206

C34

22u-1206

C111

22u-1206

C71-221061E-S03

2

C1009

0.1u

C57

0.1u

C151

0.1u

C957

0.1u

C955

0.1u

C956

0.1u

C966

0.1u

C968

0.1u

C56

0.1u

C187

0.1u

C218

0.1u

C247

0.1u

C165

0.1u

C973

0.1u

C962

0.1u

C975

0.1u

C965

0.1u

C974

0.1u

C971

0.1u

C976

0.1u

1

R80 220

R882 X_40.2-1%

R881 X_40.2-1%

R879 X_40.2-1%

R880 X_40.2-1%

R883 X_40.2-1%

R116 40.2-1%

R107 40.2-1%

R110 40.2-1%

R153 40.2-1%

R106 40.2-1%

R136 40.2-1%

R82 220

R113 220

R86 220

R99 220

R105 51

R104 220

R135 220

R81 220

R27 75-1%

R96 150-1%

R229 40.2-1%

R230 75-1%

R95 100

R72 100

R87 301-1%

R88 27.4-1%

R28 681-1%

INTEL recommand:22u*20+1u*8

INTEL OS-CON *9~10

CPU_A20M_L <3,5,19>

C1034 X_47p

C1020 X_47p

C1004 X_47p

C1010 X_47p

C1046 X_47p

FSB_BINIT_L <3,5,9>

FSB_BNR_L <3,5,9>

FSB_HITM_L <3,5,9>

FSB_HIT_L <3,5,9>

FSB_MCERR_L <3,5,9>

CPU_BPM_L_0 <3,5>

CPU_BPM_L_1 <3,5>

CPU_BPM_L_2 <3,5>

CPU_BPM_L_3 <3,5>

CPU_BPM_L_4 <3,5>

CPU_BPM_L_5 <3,5>

CPU_IGNNE_L <3,5,19>

CPU_INIT_L <3,5,19,32>

CPU_LINIT1_NMI <3,5,19>

CPU_LINIT0_INTR <3,5,19>

FSB_CPURST_L <3,5,9>

CPU_CPUSLP_L <3,5,19>

CPU_STPCLK_L <3,5,19>

CPU_SMI_L <3,5,19>

ITP_TDO_P0 <3,5>

ITP_TDI_P0 <3>

ITP_TMS_P <3,5>

ITP_TDO_P1 <5>

CPU_THERMTRIP_L <3,5,21>

CPU_FERR_L <3,5,19>

CPU_PWR_GD <3,5,20>

ITP_TCK_P <3,5>

ITP_TRST_L <3,5>

NOCONA_C5_P0 NOCONA_A4_P0

NOCONA_C1_P0

TESTLOW

NOCONA_AC30_P0

SLEW_CTRL

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

R914

49.9-1%

R919

X_49.9-1%

R917

0

CPU 1_POWER

1

Last Revision Date:

Tuesday, March 18, 2003

Sheet

VCC_CORE

Rev

00E

452

of

5

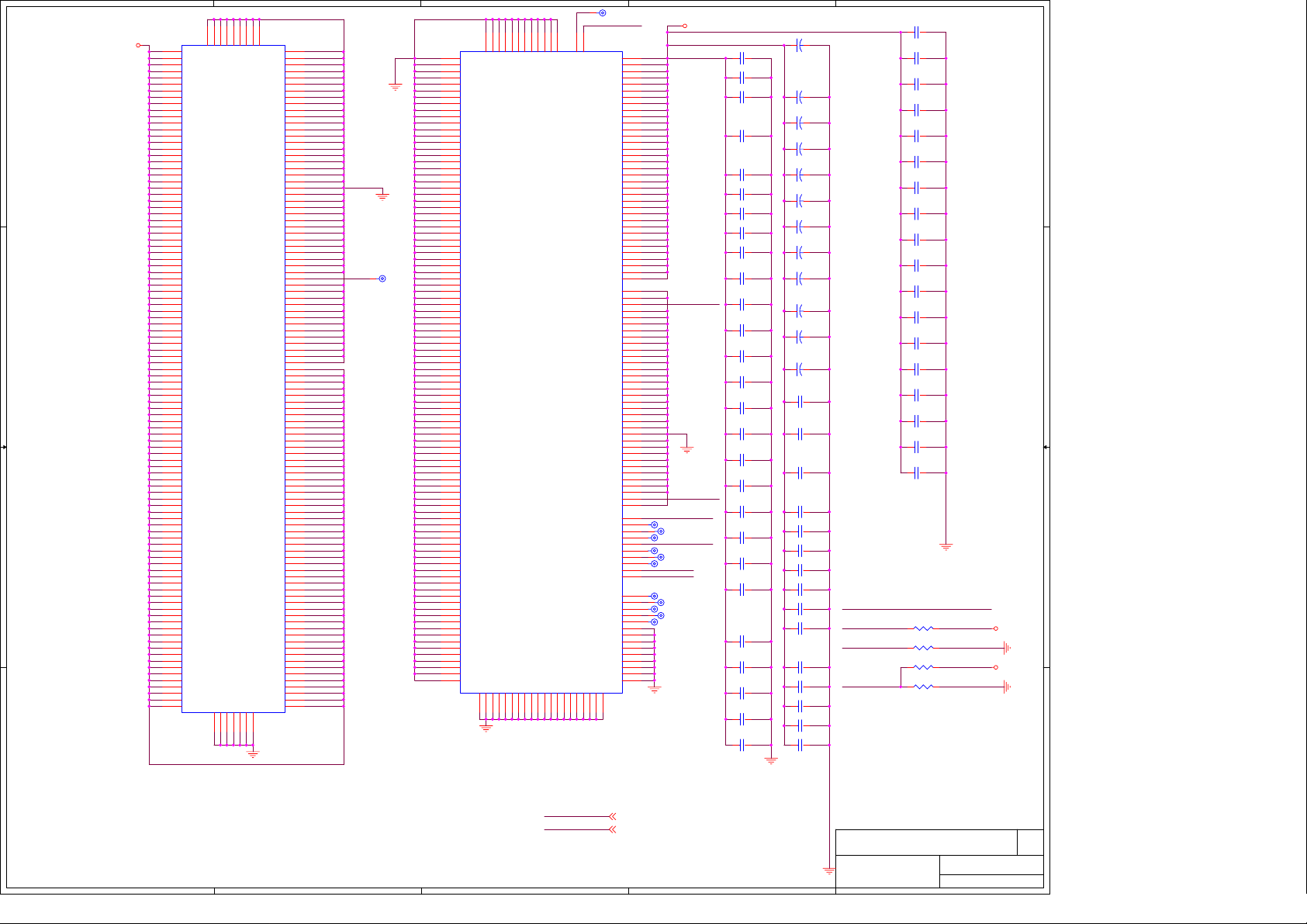

CPU_SM_WP<3,20>

CPU THERMAL SENSOR SMBUS = 32

CPU IDROM SMBUS = AA

CPU1_BSEL0

CPU1_BSEL1

+3_3V

SKTOCC_1_L<7>

FSB_HD_L0

FSB_HD_L1

FSB_HD_L2

FSB_HD_L3

FSB_HD_L4

FSB_HD_L5

FSB_HD_L6

FSB_HD_L7

FSB_HD_L8

FSB_HD_L9

FSB_HD_L10

FSB_HD_L11

FSB_HD_L12

FSB_HD_L13

FSB_HD_L14

FSB_HD_L15

FSB_HD_L16

FSB_HD_L17

FSB_HD_L18

FSB_HD_L19

FSB_HD_L20

FSB_HD_L21

FSB_HD_L22

FSB_HD_L23

FSB_HD_L24

FSB_HD_L25

FSB_HD_L26

FSB_HD_L27

FSB_HD_L28

FSB_HD_L29

FSB_HD_L30

FSB_HD_L31

FSB_HD_L32

FSB_HD_L33

FSB_HD_L34

FSB_HD_L35

FSB_HD_L36

FSB_HD_L37

FSB_HD_L38

FSB_HD_L39

FSB_HD_L40

FSB_HD_L41

FSB_HD_L42

FSB_HD_L43

FSB_HD_L44

FSB_HD_L45

FSB_HD_L46

FSB_HD_L47

FSB_HD_L48

FSB_HD_L49

FSB_HD_L50

FSB_HD_L51

FSB_HD_L52

FSB_HD_L53

FSB_HD_L54

FSB_HD_L55

FSB_HD_L56

FSB_HD_L57

FSB_HD_L58

FSB_HD_L59

FSB_HD_L60

FSB_HD_L61

FSB_HD_L62

FSB_HD_L63

FSB_HA_L[3..35]<3,9>

D D

FSB_HD_L[0..63]<3,9>

CPU1_COMP0

CPU1_COMP1

R200

R197

49.9-1%

CPU1_BSEL0

CPU1_BSEL1

5

49.9-1%

FSB_AP0_L<3,9>

FSB_AP1_L<3,9>

P1_BCLK0<8>

P1_BCLK1<8>

R313 1K

R314 1K

C C

+3_3V

+3_3V

R195

1K

R196

CPU1_FSTR1_AA29

1K

CPU1_FSTR1_AB28

CPU1_FSTR1_AA28

B B

A A

R202

1K

4

SMB_ALERT_CPU_L<3,20>

SMBUS_CPU_DATA<3,7>

SMBUS_CPU_CLK<3,7>

R329 51-1%

CPU2A

AA27

AA25

AD27

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AD10

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

SOCKET_604

CPU1_BR0_L<3>

CPU0_BR0_L<3,9> FSB_DRDY_L <3,9>

AD8

AC9

AC8

AD7

AE7

AC6

AC5

AA8

AB6

AA3

AB3

TP27

A3B5D26

Y26

D0#

D1#

Y24

Y23

AE9

E10

ODTEN

D2#

SKTOCC#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

Y9

D62#

D63#

AP0#

D9

AP1#

Y4

BCLK0

W5

BCLK1

BSEL0

BSEL1

4

VSSA_P1

VCCIOPLL_P1

TP28

AA5

B27

AD4

VSSA

VSSSENSE

VCCSENSE

A3#

A4#

A5#

A22

A20

B18

C18

FSB_HA_L6

FSB_HA_L5

FSB_HA_L3

FSB_HA_L4

+3_3V

VCCA_P1

AB4

AD29

VCCA

VCCIOPLL

A6#

A7#

A8#

A19

C17

D17

FSB_HA_L8

FSB_HA_L9

FSB_HA_L7

R327

51

CPU1_FSTR1_AA28

TP29

TP138

CPU1_FSTR1_AA29

AE29

SM_WP

SM_VCC1

AE28

SM_VCC0

CPU1_FSTR1_AB28

Y29

AA28

AB28

AB29

SM_TS_A1

SM_TS_A0

SM_EP_A2

AA29

AC29

AC28

SM_DAT

SM_EP_A1

SM_EP_A0

AD28

SM_CLK

SM_ALERT

CPU1_COMP0

CPU1_COMP1

E16

AD16

COMP1

COMP0

Prestonia 604

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

FSB_HA_L19

FSB_HA_L17

FSB_HA_L18

49.9-1%

FSB_HA_L23

FSB_HA_L21

FSB_HA_L20

FSB_HA_L22

R198

FSB_HA_L24

FSB_HA_L13

FSB_HA_L12

FSB_HA_L11

FSB_HA_L10

VCC_CORE

FSB_BNR_L<3,4,9>

FSB_BPRI_L<3,9>

FSB_BINIT_L<3,4,9>

FSB_HA_L14

FSB_HA_L16

FSB_HA_L15

R328

51

W6W7W8Y6AA7

TESTHI0

TESTHI1

A24#

A25#

A26#

E14

D13A9B8

FSB_HA_L27

FSB_HA_L26

FSB_HA_L25

3

R312

51

AD5

AE5

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

A27#

A28#

A29#

A30#

A31#

E13

D12

C11B7A6A7C9C8D20

FSB_HA_L28

FSB_HA_L31

FSB_HA_L30

FSB_HA_L29

R324

49.9-1%

3

R310

51

A32#

A33#

A34#

FSB_HA_L32

FSB_HA_L33

FSB_HA_L34

R311

R260

51

51

FSB_DEP_L1

FSB_DEP_L3

FSB_DEP_L2

AE17

AC15

AE19

DP3#

DP2#

DP1#

A35#

BR0#

BR1#

F12

FSB_HA_L35

R331

49.9-1%

R259

51

FSB_DEP_L0

E25

C24

AC18

TDI

TDO

DP0#

BR2#

BR3#

BNR#

BPRI#

E11

D10

F20

D23

VCC_CORE

ITP_TDO_P1 <4>

ITP_TDO_P0 <3,4>

ITP_TCK_P <3,4>

E19

F24

A25

E24

TCK

TMS

TRST#

TRDY#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

STPCLK#

THERMTRIP#

PWRGD

PROCHOT#

IGNNE#

RESET#

MCERR#

DEFER#

ADSTB0#

ADSTB1#

BINIT#

DBSY#

DRDY#

F11

F18

E18

AB9

DBI3#

AE12

DBI2#

AD22

DBI1#

AC27

DBI0#

F3

VID0

E3

VID1

D3

VID2

C3

VID3

B3

VID4

F9

F23

W9

W23

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

F6

BPM0#

F8

BPM1#

E7

BPM2#

F5

BPM3#

E8

BPM4#

E4

BPM5#

AE6

SLP#

D4

C27

SMI#

F26

AB7

B25

D6

INIT#

G23

LINIT1

B24

LINIT0

E27

FERR#

C26

F27

A20M#

Y8

B19

REQ0#

B21

REQ1#

C21

REQ2#

C20

REQ3#

B22

REQ4#

A17

LOCK#

D7

C6

RSP#

F21

RS2#

D22

RS1#

E21

RS0#

E5

IERR#

C23

A23

HITM#

E22

HIT#

D19

ADS#

F17

F14

KEY604

AE30

TP32

FSB_DBSY_L <3,9>

FSB_DEP_L0

FSB_DEP_L1

FSB_DEP_L2

FSB_DEP_L3

FSB_TRDY_L <3,9>

ITP_TRST_L <3,4>

ITP_TMS_P <3,4>

FSB_DBI_L3

FSB_DBI_L2

FSB_DBI_L1

FSB_DBI_L0

VID_P1_0

VID_P1_1

VID_P1_2

VID_P1_3

VID_P1_4

FSB_HDSTBP_L3

FSB_HDSTBP_L2

FSB_HDSTBP_L1

FSB_HDSTBP_L0

FSB_HDSTBN_L3

FSB_HDSTBN_L2

FSB_HDSTBN_L1

FSB_HDSTBN_L0

TP31

FSB_ADSTB_L0

FSB_ADSTB_L1

2

FSB_DEP_L[0..3] <3,9>

VID_P1_[0..4] <7>

CPU_BPM_L_0 <3,4>

CPU_BPM_L_1 <3,4>

CPU_BPM_L_2 <3,4>

CPU_BPM_L_3 <3,4>

CPU_BPM_L_4 <3,4>

CPU_BPM_L_5 <3,4>

CPU_CPUSLP_L <3,4,19>

CPU_STPCLK_L <3,4,19>

CPU_SMI_L <3,4,19>

CPU_THERMTRIP_L <3,4,21>

TP30

CPU_INIT_L <3,4,19,32>

CPU_LINIT1_NMI <3,4,19>

CPU_LINIT0_INTR <3,4,19>

CPU_FERR_L <3,4,19>

CPU_IGNNE_L <3,4,19>

CPU_A20M_L <3,4,19>

FSB_CPURST_L <3,4,9>

FSB_LOCK_L <3,9>

FSB_MCERR_L <3,4,9>

FSB_RSP_L <3,9>

FSB_RS2_L <3,9>

FSB_RS1_L <3,9>

FSB_RS0_L <3,9>

FSB_DEFER_L <3,9>

FSB_HITM_L <3,4,9>

FSB_HIT_L <3,4,9>

FSB_ADS_L <3,9>

2

FSB_DBI_L[0..3] <3,9>

FSB_HDSTBP_L[0..3] <3,9>

FSB_REQ_L0

FSB_REQ_L1

FSB_REQ_L2

FSB_REQ_L3

FSB_REQ_L4

FSB_ADSTB_L[0..1] <3,9>

VCC_CORE

Title

Document Number

GTL_VREF2_P1 <18>

C493

C300

220p

220p

C320

220p

FSB_HDSTBN_L[0..3] <3,9>

CPU_PWR_GD <3,4,20>

PLACE CLOSE

CPU2.AB7

FSB_REQ_L[0..4] <3,9>

R319 1

R318 1

L24 4.7uH-0805

1 2

L23 4.7uH-0805

1 2

Micro Star Restricted Secret

CPU 2_SIGNAL

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

GTL_VREF1_P1 <18>

C495

220p

Last Revision Date:

Tuesday, March 18, 2003

Sheet

552

1

VCCA_P1

C491

22u-10V

VSSA_P1

C490

22u-10V

VCCIOPLL_P1

of

Rev

00E

5

CPU2B

GN33

GN34

GN35

GN36

GN37

GN38

GN39

GN40

EMI_GND2

EMI_GND3

EMI_GND4

EMI_GND5

EMI_GND6

EMI_GND7

EMI_GND8

Prestonia_PWR

EMI_GND10

EMI_GND11

EMI_GND12

EMI_GND13

EMI_GND14

EMI_GND15

EMI_GND16

GN42

GN43

GN44

GN45

GN46

GN47

GN48

GN41

VSS

VSS

VSS

VSS

EMI_GND9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_CORE

D D

C C

B B

A2

VCC

A8

VCC

A14

VCC

A18

VCC

A24

EMI_GND1

VCC

A28

VCC

B6

VCC

B12

VCC

B20

VCC

B26

VCC

B29

VCC

C2

VCC

C4

VCC

C10

VCC

C16

VCC

C22

VCC

C28

VCC

D8

VCC

D14

VCC

D18

VCC

D24

VCC

D29

VCC

E2

VCC

E6

VCC

E12

VCC

E20

VCC

E26

VCC

E28

VCC

F4

VCC

F10

VCC

F16

VCC

F22

VCC

F29

VCC

G2

VCC

G4

VCC

G6

VCC

G8

VCC

G24

VCC

G26

VCC

G28

VCC

H3

VCC

H5

VCC

H7

VCC

H9

VCC

H23

VCC

H25

VCC

H27

VCC

H29

VCC

J2

VCC

J4

VCC

J6

VCC

J8

VCC

J24

VCC

J26

VCC

J28

VCC

K3

VCC

K5

VCC

K7

VCC

K9

VCC

K23

VCC

K25

VCC

K27

VCC

K29

VCC

L2

VCC

L4

VCC

L6

VCC

L8

VCC

L24

VCC

L26

VCC

L28

VCC

M3

VCC

M5

VCC

M7

VCC

M9

VCC

M23

VCC

M25

VCC

M27

VCC

M29

VCC

N3

VCC

N5

VCC

N7

VCC

N9

VCC

N23

VCC

N25

VCC

N27

VCC

N29

VCC

P2

VCC

P4

VCC

P6

VCC

P8

VCC

P24

VCC

P26

VCC

P28

VCC

R3

VCC

R5

VCC

R7

VCC

R9

VCC

R23

VCC

R25

VCC

R27

VCC

W27

VCC

W25

VCC

SOCKET_604

A A

A5

A11

A21

A27

A29

B2

B9

B15

B17

B23

B28

C7

C13

C19

C25

C29

D2

D5

D11

D21

D27

D28

E9

E15

E17

E23

E29

F2

F7

F13

F19

F25

F28

G3

G5

G7

G9

G25

G27

G29

H2

H4

H6

H8

H24

H26

H28

J3

J5

W29

Y2

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

4

CPU2C

J7

VSS

J9

VSS

J23

VSS

J25

VSS

J27

VSS

J29

VSS

K2

VSS

K4

VSS

K6

VSS

K8

VSS

K24

VSS

K26

VSS

K28

VSS

L3

VSS

L5

VSS

L7

VSS

L9

VSS

L23

VSS

L25

VSS

L27

VSS

L29

VSS

M2

VSS

M4

VSS

M6

VSS

M8

VSS

M24

VSS

M26

VSS

M28

VSS

N2

VSS

N4

VSS

N6

VSS

N8

VSS

N24

VSS

N26

TP105

VSS

N28

VSS

P3

VSS

P5

VSS

P7

VSS

P9

VSS

P23

VSS

P25

VSS

P27

VSS

P29

VSS

R2

VSS

R4

VSS

R6

VSS

R8

VSS

R24

VSS

R26

VSS

R28

VSS

T3

VSS

T5

VSS

T7

VSS

T9

VSS

T23

VSS

T25

VSS

T27

VSS

T29

VSS

U2

VSS

U4

VSS

U6

VSS

U8

VSS

U24

VSS

U26

VSS

U28

VSS

V3

VSS

V5

VSS

V7

VSS

V9

VSS

V23

VSS

V25

VSS

V27

VSS

V29

VSS

W2

VSS

W4

VSS

W24

VSS

W26

VSS

W28

VSS

Y5

VSS

Y7

VSS

Y13

VSS

Y19

VSS

Y25

VSS

AA2

VSS

AA9

VSS

AA15

VSS

AA17

VSS

AA23

VSS

AB5

VSS

AB11

VSS

AB21

VSS

AB27

VSS

AC2

VSS

AC7

VSS

AC13

VSS

AC19

VSS

AC25 AD3

VSS VSS

SOCKET_604

3

TP104

NOCONA_A4_P1

A1

GN21

GN22

GN23

GN24

GN25

GN26

GN27

GN28

MTH_GND26

MTG_GND21

MTG_GND22

MTG_GND23

MTG_GND24

MTG_GND25

MTG_GND27

MTG_GND28

MTG_GND1

MTG_GND2

MTG_GND3

MTG_GND4

MTG_GND5

MTG_GND6

MTG_GND7

MTG_GND8

GN1

GN2

MTG_GND9

GN3

GN4

GN5

GN6

GN7

GN8

GN9

GN29

GN30

GN31

GN32

MTG_GND29

MTG_GND30

MTG_GND31

MTG_GND32

Prestonia_PWR

MTG_GND10

MTG_GND11

MTG_GND12

MTG_GND13

GN10

GN11

GN12

GN13

GN14

MTG_GND14

MTG_GND15

GN15

GN16

A4

GAL_VDD1

GAL_VDD2

GAL_VDD3

RSVD0

RSVD1

GAL_VDD4

GAL_VDD5

GAL_VDD6

GAL_VDD7

GAL_VDD8

GAL_VDD9

GAL_VDD10

GAL_VDD11

GAL_VDD12

GAL_VDD13

GAL_VDD14

GAL_VDD15

GAL_VDD16

GAL_VDD17

GAL_VDD18

GAL_VDD19

GAL_VDD20

GAL_VDD21

GAL_VDD22

GAL_VDD23

GAL_VDD24

GAL_VDD25

GAL_VDD26

GAL_VDD27

GAL_VDD28

GAL_VDD29

GAL_VDD30

GAL_VDD31

GAL_VDD32

GAL_VDD33

GAL_VDD34

GAL_VDD35

GAL_VSS1

GAL_VSS2

GAL_VSS3

GAL_VSS4

GAL_VSS5

GAL_VSS6

GAL_VSS7

GAL_VSS8

GAL_VSS9

GAL_VSS10

GAL_VSS11

GAL_VSS12

GAL_VSS13

GAL_VSS14

GAL_VSS15

GAL_VSS16

GAL_VSS17

GAL_VSS18

GAL_VSS19

GAL_VSS20

GAL_VSS21

GAL_VSS22

GAL_VSS23

GAL_VSS24

GAL_VSS25

GAL_VSS26

GAL_VSS27

GAL_VSS28

GAL_VSS29

GAL_VSS30

GAL_VSS31

GAL_VSS32

GAL_VSS33

GAL_VSS34

MTG_GND16

MTG_GND17

MTG_GND18

GN17

GN18

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD11

RSVD12

RSVD13

RSVD9

RSVD10

RSVD14

RSVD15

RSVD16

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MTG_GND19

MTG_GND20

GN19

GN20

A30

B4

B31

C30

D1

D31

E30

F1

F31

G30

H1

H31

J30

K1

K31

L30

M1

M31

N1

N31

P30

R1

R31

T30

U1

U31

V30

W1

W31

Y30

AA1

AA31

AB30

AC31

AD30

A31

B30

C1

C31

D30

E1

E31

F30

G1

G31

H30

J1

J31

K30

L1

L31

M30

N30

P1

P31

R30

T1

T31

U30

V1

V31

W30

Y1

Y31

AA30

AB1

AB31

AC30

AD31

NOCONA_A15_P1

A15

A16

A26

B1

NOCONA_C5_P1

C5

D25

W3

Y3

Y27

CPU2_DIODE_N

Y28

AC1

AD1

AE4

AE15

AE16

AE27

AE21

AE11

AE2

AD23

AD17

AD15

AD9

NOCONA_C1_P1

NOCONA_AC30_P1

TP33

TP34

TP35

TP36

TP37

TP38

CPU2_DIODE_P

TP39

TP40

TP41

TP42

TP43

VCC_CORE

2

1

C321

C358

1u-0805

C324

1u-0805

C313

1u-0805

C377

1u-0805

C403

1u-0805

C372

22u-1210

C391

22u-1210

C496

1u-0805

C1051

0.1u

C363

0.1u

C381

0.1u

C401

0.1u

C362

0.1u

C404

0.1u

C409

0.1u

C354

0.1u

C400

0.1u

C380

0.1u

C315

0.1u

C311

0.1u

C316

0.1u

C293

0.1u

C1019

0.1u

C54

0.1u

C317

0.1u

C388

0.1u

C122

0.1u

C269

820-2.5V

C524

820-2.5V

C521

820-2.5V

C520

820-2.5V

C9

820-2.5V

C274

820-2.5V

C8

820-2.5V

C292

820-2.5V

C329

X_820-2.5V

C11

820-2.5V

C10

X_820-2.5V

C273

820-2.5V

C488

22u-1206

C410

22u-1206

C373

22u-1206

C487

22u-1206

C376

22u-1206

C350

22u-1206

C415

22u-1206

C498

22u-1206

C489

22u-1206

C323

22u-1206

C304

22u-1206

C305

22u-1206

C136

22u-1206

C351

22u-1206

C37

10 mils 10 mils

NOCONA_C5_P1 NOCONA_A4_P1

NOCONA_A15_P1

FORCEPR#

NOCONA_C1_P1

TESTLOW

NOCONA_AC30_P1

SLEW_CTRL

22u-1206

0.1u

C229

0.1u

C353

0.1u

C494

0.1u

C1030

0.1u

C1011

0.1u

C1041

0.1u

C1040

0.1u

C1033

0.1u

C1061

0.1u

C1027

0.1u

C1056

0.1u

C1050

0.1u

C1036

0.1u

C1018

0.1u

C995

0.1u

C993

0.1u

C990

0.1u

R912

49.9-1%

R913

49.9-1%

R920

X_49.9-1%

R918

0

VCC_CORE

VCC_CORE

NOPOP FOR NOCONA

CPU2_DIODE_P

CPU2_DIODE_N

FOR PRESTONIA 604 ONLY

5

4

3

CPU2_DIODE_P <28>

CPU2_DIODE_N <28>

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

CPU 2_POWER

Last Revision Date:

Tuesday, March 18, 2003

Sheet

1

Rev

00E

652

of

5

4

3

2

1

VID_P0_[0..4] <3,23>

VID_P0_0

VID_P0_1

VID_P0_2

VID_P0_3

VID_P0_4

+5V

VID_P1_[0..4] <5>

D D

C C

VID_P1_0

VID_P1_1

VID_P1_2

VID_P1_3

VID_P1_4

VID_P0_0

VID_P1_0

VID_P0_1

VID_P1_1

VID_P0_2

VID_P1_2

VID_P0_3

VID_P1_3

+3_3V

U52A

14

1

2

7

74LCX86-SO14

U52B

14

4

5

7

74LCX86-SO14

U52C

14

9

10

7

74LCX86-SO14

U52D

14

12

13

7

74LCX86-SO14

R866

1K

SKTOCC_1_L<5>

D57

3

A C

1

2

74F00-SOIC14

7

3

14

U51A

1N4148S

D51

6

8

11

A C

1N4148S

D50

A C

1N4148S

D47

A C

1N4148S

14

U51B

R867

4

5

74F00-SOIC14

7

6

1 2

R862 4.7K

4.7K

1 2

14

U51C

9

10

74F00-SOIC14

7

8

LOW ENABLE

B

+5V

12

R863

8.2K

Q80

E C

MMBT3904

D3

A C

1N4148S

VRM_OUTEN_L <23>

SMBCLK <8,13,14,24,25,26,27,41,43>

B B

+12V

12

R858

VCCT

1K-1206

3.3V

RLZ3.3B-S-LL34

A A

5

D58

A C

C940

1000p

VID_P0_2

VID_P1_2

VID_P0_3

VID_P1_3

VID_P0_4

VID_P0_0

VID_P1_0

VID_P0_1

VID_P1_1

VID_P1_4

4

7 8

5 6

3 4

1 2

1 2

R828 1K

RN101 8P4R-1K

RN102 8P4R-1K

1 2

3 4

5 6

7 8

1 2

R822 1K

VCCT

VCCT

3

12

13

14

U51D

74F00-SOIC14

7

11

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

R947

0

1 2

SMBUS_CPU_CLK <3,5>

SMBDATA <8,13,14,24,25,26,27,41,43>

R948

0

1 2

SMBUS_CPU_DATA <3,5>

Micro Star Restricted Secret

VID COMPARE

Last Revision Date:

Tuesday, March 18, 2003

Sheet

752

1

Rev

00E

of

5

4

3

2

1

CP6

X_COPPER

S2

R370

X_10K

R388

4.7K

FB19

X_80-0805

R366

49.9-1%

R365

49.9-1%

VCC3_CLK

C620

22u-1206

14M-32pf-HC49S-D

C612

X_10p

R364

49.9-1%

VRM_GD<23>

Y2

C626

0.1u

SMBDATA<7,13,14,24,25,26,27,41,43>

SMBCLK<7,13,14,24,25,26,27,41,43>

R363

49.9-1%

4

C627

0.1u

R362

49.9-1%

R474

10K

C629

0.1u

CLK_GEN_1

CLK_GEN_2

C585

X_10p

R393 33

R394 33

R395 33

R396 33

R397 33

R398 33

12

C628

C581

0.1u

0.1u

MULT0

FSB_FREQ_SEL

S2

CPU_VRD_PWR_GD_L

P0_BCLK0_R

P0_BCLK1_R

P1_BCLK0_R

P1_BCLK1_R

MCH_BCLK0_R

MCH_BCLK1_R

CPU3_R

CPU3_L_R

R387

475-1%

VCC3_CLK

R438

10K

Q52

B

MMBT3904

E C

C582

C562

C561

0.1u

0.1u

0.1u

U21

2

XTAL_IN

3

XTAL_OUT

43

MULT0

55

S1

40

S2

30

SCLK

29

SDATA

28

PWR_GD#

52

CPU0

51

CPU0#

49

CPU1

48

CPU1#

45

CPU2

44

CPU2#

54

CPU3

53

CPU3#

42

IREF

475 FOR 50 ohm

impedance

CPU_VRD_PWR_GD_L

R456

X_1K

1

8

14

19

32

37

VDD_PCI

VDD_PCI

VDD_REF

VDD_3V66

VDD_3V66

SM bus addr.=D2h

GND_REF

GND_3V66

GND_PCI

GND_PCI

4

9

15

20

31

Q53

B

E C

MMBT3904

3

D D

VCC3_CLK

C C

R369 4.7K

R444 4.7K

R399 4.7K

differential 100 ohm

single ended 50 ohm

+3_3V

MULT0

PWRDWN_L

CLK_PCISTOP_L

4.75/7/25

P0_BCLK0<3>

P0_BCLK1<3>

P1_BCLK0<5>

P1_BCLK1<5>

MCH_BCLK0<9>

MCH_BCLK=P?_BCLK+0.282"

MCH_BCLK1<9>

R392 10K

B B

+3_3V

A A

R368 10K

R367

49.9-1%

R1557

10K

CPU0_BSEL0 <3>

FSB_FREQ_SEL

5

46

50

VDD_CPU

VDD_CPU

VDD_48MHZ

GND_3V66

GND_48MHZ

GND_IREF

GND_CPU

36

41

47

R477

10K

VCC3_CLKA

26

VDD_CORE

3V66_0

3V66_1/VCH

66BUF0/3V66_2

66BUF1/3V66_3

66BUF2/3V66_4

66IN/3V66_5

PCI_F0

PCI_F1

PCI_F2

USB_48MHZ

DOT_48MHZ

PWR_DWN#

PCI_STOP#

GND_CORE

ICS-CY28329-SSOP56

27

ICS-932S203AF

3VDUAL

12

REF0

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

1 2

C617

0.1u

56

33

35

21

22

23

24

10

11

12

13

16

17

18

5

6

7

39

38

25

34

R476

1k

ICH4_14MHZ_CLK_R

MCH_66MHZ_CLK_R

ICH4_66MHZ_CLK_R

AGP_66MHZ_CLK_R

PWRDWN_L

CLK_PCISTOP_L

CP5

X_COPPER

FB17

C615

X_80-0805

22u-1206

TP44

TP45

TP46

PCI0_33MHZ_CLK_R

PCI1_33MHZ_CLK_R

FWH_33MHZ_CLK_R

SIO_33MHZ_CLK_R

R452 33

R453 33

ICH4_33MHZ_CLK_R

TP48

ICH4_USB_48MHZ_CLK_R

DOT_48MHZ_CLK_R

SKTOCC_0_L <3>

+3_3V

Width/Space=6/24 for all clock on layer 8

R386 33

R402 33

R391 33

R447 33

R448 33

R450 33

R451 33

R449 33

R446 33

R1592 33

C655

1u

2

R455 33

R389 33

R390 33

C539

X_10p

C646

X_10p

C651

X_10p

C540

X_10p

C542

C573

X_10p

X_10p

C647

X_10p

PCI3_33MHZ_CLK <25>

PCI4_33MHZ_CLK <26>

C652

X_10p

ICH4_48MHZ_CLK <20>

SIO_48MHZ_CLK <28>

C541

X_10p

C633

C125

0.1u

0.1u

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C1272

X_10p

+3_3V +3_3V +3_3V +3_3V+3_3V +3_3V

C937

0.1u

Micro Star Restricted Secret

ICH4_14MHZ_CLK <20>

MCH_66MHZ_CLK <10>

ICH4_66MHZ_CLK <20>

L=A

L=A-0.184"

L=A+0.243"

AGP_66MHZ_CLK <17>

C654

X_10p

C649

X_10p

W/S=6/24

C650

X_10p

C648

X_10p

C928

0.1u

L=A-4.189"

PCI0_33MHZ_CLK <46>

PCI1_33MHZ_CLK <48>

FWH_33MHZ_CLK <32>

SIO_33MHZ_CLK <28>

PCI2_33MHZ_CLK <24>

ICH4_33MHZ_CLK <19>

B=A-0.157"

PCI5_33MHZ_CLK <27>

C645

X_10p

C173

C597

0.1u

0.1u

around clock for EMI

CLOCK

Last Revision Date:

Tuesday, March 18, 2003

Sheet

852

1

of

B-2.5"

B-2.5"

B

B

B

Rev

00E

5

4

3

2

1

FSB_ADSTB_L[0..1]<3,5>

DEVRST_L1<43>

R194 100

+3_3V

F3

F2

H4

G4

C9

C8

B6

B7

A8

A7

D1

E1

U16A

ADS#

AP0#

AP1#

BINIT#

BNR#

BPRI#

BREQ0#

CPURST#

DEP0#

DEP1#

DEP2#

DEP3#

DBSY#

DEFER#

DINV0#

DINV1#

DINV2#

DINV3#

DRDY#

HITM#

HIT#

HTRDY#

HREQ4#

HREQ3#

HREQ2#

HREQ1#

HREQ0#

HLOCK#

XERR#

RS0#

RS1#

RS2#

RSP#

HXRCOMP

HXSWNG

HYRCOMP

HYSWNG

MCH

R228 4.7K

J16

J17

HCLKINP

HCLKINN

HA3#

HA4#

HA5#

H15

F11D8E9

J24

J18

RSTIN#

TESTIN#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

G11D7F9A4E7C5B4B3A5D5H12

FSB_ADSTB_L1

FSB_ADSTB_L0

C6

H9

HADSTB0#

HADSTB1#

MCH_HOST I/F

HA16#

HA17#

HA18#

HA19#

HA20#

J12

J11E6F6H6G8

FSB_HD_L6

FSB_HD_L3

FSB_HD_L5

FSB_HD_L4

FSB_HD_L2

FSB_HD_L0

FSB_HD_L1

B31

G25

C29

C30

G26

A29

D29

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

H10J9F5D4J8G7H7E3C2C3G5

FSB_HD_L7

A31

FSB_HD_L8

B30

HD7#

HA28#

FSB_HD_L9

E28

HD8#

HA29#

FSB_HD_L10

D28

HD9#

HD10#

HA30#

HA31#

FSB_HD_L12

FSB_HD_L11

D26

E25

HD11#

HD12#

HA32#

HA33#

FSB_HD_L14

FSB_HD_L13

F27

G23

HD13#

HD14#

HA34#

HA35#

E4

FSB_HD_L15

FSB_HD_L16

H24

A28

HD15#

HD16#

CCVREF

B9

FSB_HD_L18

FSB_HD_L17

B28

B27

HD17#

HD18#

HDVREF3

HDVREF2

A11

A22

FSB_HD_L19

FSB_HD_L20

C27

A26

HD19#

HD20#

HDVREF1

HDVREF0

F21

F24

FSB_HD_L22

FSB_HD_L21

C26

B25

HD21#

HD22#

HAVREF0

HAVREF1

F8

D2

FSB_HD_L24

FSB_HD_L23

A25

H22

HD23#

HD24#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

FSB_HD_L25

D23

FSB_HD_L26

F23

FSB_HD_L27

C24

FSB_HD_L28

D22

FSB_HD_L29

E24

FSB_HD_L30

E22

FSB_HD_L31

G20

FSB_HD_L32

A23

FSB_HD_L33

B22

FSB_HD_L34

C23

FSB_HD_L35

D20

FSB_HD_L36

B24

FSB_HD_L37

C21

FSB_HD_L38

D19

FSB_HD_L39

A20

FSB_HD_L40

B18

FSB_HD_L41

B19

FSB_HD_L42

E19

FSB_HD_L43

C18

FSB_HD_L44

H19

FSB_HD_L45

E18

FSB_HD_L46

H18

FSB_HD_L47

G19

FSB_HD_L48

F17

FSB_HD_L49

F18

FSB_HD_L50

G17

FSB_HD_L51

A17

FSB_HD_L52

D17

FSB_HD_L53

D16

FSB_HD_L54

A16

FSB_HD_L55

B16

FSB_HD_L56

C14

FSB_HD_L57

D14

FSB_HD_L58

B13

FSB_HD_L59

C12

FSB_HD_L60

B12

FSB_HD_L61

A14

FSB_HD_L62

B15

FSB_HD_L63

A13

FSB_HDSTBN_L0

E27

FSB_HDSTBN_L1

G22

FSB_HDSTBN_L2

B21

FSB_HDSTBN_L3

C17

FSB_HDSTBP_L0

F26

FSB_HDSTBP_L1

H21

FSB_HDSTBP_L2

C20

FSB_HDSTBP_L3

E16

FSB_HD_L[0..63] <3,5>

FSB_HDSTBN_L[0..3] <3,5>

FSB_HDSTBP_L[0..3] <3,5>

D D

FSB_ADS_L<3,5>

FSB_AP0_L<3,5>

FSB_AP1_L<3,5>

FSB_BINIT_L<3,4,5>

FSB_BNR_L<3,4,5>

FSB_BPRI_L<3,5>

CPU0_BR0_L<3,5>

FSB_CPURST_L<3,4,5>

FSB_DEP_L[0..3]<3,5>

C C

B B

FSB_DBSY_L<3,5>

FSB_DEFER_L<3,5>

FSB_DBI_L[0..3]<3,5>

FSB_DRDY_L<3,5>

FSB_HITM_L<3,4,5>

FSB_HIT_L<3,4,5>

FSB_TRDY_L<3,5>

FSB_REQ_L[0..4]<3,5>

FSB_LOCK_L<3,5>

FSB_MCERR_L<3,4,5>

FSB_RS0_L<3,5>

FSB_RS1_L<3,5>

FSB_RS2_L<3,5>

FSB_RSP_L<3,5>

R247

R226

24.9-1%

24.9-1%

HXRCOMP

HYRCOMP

MCH_BCLK1<8>

MCH_BCLK0<8>

FSB_DEP_L0

FSB_DEP_L1

FSB_DEP_L2

FSB_DEP_L3

FSB_DBI_L0

FSB_DBI_L1

FSB_DBI_L2

FSB_DBI_L3

FSB_REQ_L4

FSB_REQ_L3

FSB_REQ_L2

FSB_REQ_L1

FSB_REQ_L0

HSWNG0

HSWNG1

A10

B10

F15

F12

D10

H16

H25

D25

A19

C15

E15

D13

D11

G14

E10

H13

G13

G10

E12

F14

E13

C11

G16

F20

E21

GTL_VREF_MCH <18>

FSB_HA_L28

FSB_HA_L27

FSB_HA_L11

FSB_HA_L12

FSB_HA_L4

FSB_HA_L5

FSB_HA_L3

FSB_HA_L6

FSB_HA_L7

FSB_HA_L8

FSB_HA_L14

FSB_HA_L10

FSB_HA_L13

FSB_HA_L9

FSB_HA_L15

FSB_HA_L16

FSB_HA_L17

FSB_HA_L18

FSB_HA_L19

FSB_HA_L20

FSB_HA_L21

FSB_HA_L22

FSB_HA_L23

FSB_HA_L24

FSB_HA_L25

FSB_HA_L26

FSB_HA_L29

FSB_HA_L30

FSB_HA_L31

FSB_HA_L32

FSB_HA_L33

FSB_HA_L34

FSB_HA_L35

FSB_HA_L[3..35] <3,5>

C405

0.01u

VCC_CORE

C331

C309

VCC_CORE VCC_CORE

A A

301-1%

HSWNG0

R232

R233

150-1%

C346

0.01u

5

4

R219

301-1%

R220

150-1%

HSWNG1

C336

0.01u

3

C344

0.1u

0.1u

C370

0.1u

0.1u

2

C378

C417

0.1u

C408

0.1u

MCH_HOST

C326

0.1u

0.1u

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C477

C476

0.1u

0.1u

Last Revision Date:

Tuesday, March 18, 2003

Sheet

952

1

C339

0.1u

Rev

00E

of

5

U16F

AGP_AD31

AGP_AD30

AGP_AD29

AGP_AD28

AGP_AD27

D D

C C

AGP_AD[0..31]<17>

AGP_AD26

AGP_AD25

AGP_AD24

AGP_AD23

AGP_AD22

AGP_AD21

AGP_AD20

AGP_AD19

AGP_AD18

AGP_AD17

AGP_AD16

AGP_AD15

AGP_AD14

AGP_AD13

AGP_AD12

AGP_AD11

AGP_AD10

AGP_AD9

AGP_AD8

AGP_AD7

AGP_AD6

AGP_AD5

AGP_AD4

AGP_AD3

AGP_AD2

AGP_AD1

AGP_AD0

AGP_DBI_LO<17>

AGP_DBI_HI<17>

AGP_RBF<17>

AGP_WBF<17>

AGP_DEVSEL<17>

AGP_IRDY<17>

AGP_SERR<17>

TP49

TP50

TP51

AA3

AA2

AL10

M6

M2

M3

N2

N1

M5

P1

N4

T1

N7

T4

P6

N8

P7

P9

R9

R8

V8

T7

U7

U6

V6

V5

W8

W1

W5

W2

W4

Y1

Y3

Y4

M8

M9

J3

K5

W7

V9

Y7

L9

GAD31

GAD30

GAD29

GAD28

GAD27

GAD26

GAD25

GAD24

GAD23

GAD22

GAD21

GAD20

GAD19

GAD18

GAD17

GAD16

GAD15

GAD14

GAD13

GAD12

GAD11

GAD10

GAD9

GAD8

GAD7

GAD6

GAD5

GAD4

GAD3

GAD2

GAD1

GAD0

GDBI_LO

GDBI_HI/PIPE*

RBF

WBF

GDEVSEL

GIRDY

GSERR

RSV

RSV

RSV

MCH

GCBE3

GCBE2

GCBE1

GCBE0

GREQ

GGNT

GFRAME

GTRDY

GPAR

GSTOP

PSWNG_AGP1

PSWNG_AGP0

PRCOMP_AGP1

PRCOMP_AGP0

PREF_AGP1

PREF_AGP0

AD_STB0F

AD_STB0S

AD_STB1F

AD_STB1S

SB_STBF

SB_STBS

SBA7#

SBA6#

SBA5#

SBA4#

SBA3#

SBA2#

SBA1#

SBA0#

GCLKIN

ST2

ST1

ST0

4

J5

H3

H1

AGP_C_BE_L3

R2

AGP_C_BE_L2

T8

AGP_C_BE_L1

U9

AGP_C_BE_L0

U1

J6

K8

Y6

AB2

AA5

AB1

U4

N5

P4

T5

T2

U3

V3

V2

P3

R3

L3

K2

AGP_SBA_L7

L6

AGP_SBA_L6

L7

AGP_SBA_L5

L4

AGP_SBA_L4

L1

AGP_SBA_L3

K1

AGP_SBA_L2

K4

AGP_SBA_L1

J2

AGP_SBA_L0

K7

Y9

AGP_ST2

AGP_ST1

AGP_ST0

AGP_REQ <17>

AGP_GNT <17>

AGP_FRAME <17>

AGP_TRDY <17>

AGP_PAR <17>

AGP_STOP <17>

AGP_VSWNG

R270 43.2-1%

R283 43.2-1%

AGP_ADSTB0F <17>

AGP_ADSTB0S <17>

AGP_ADSTB1F <17>

AGP_ADSTB1S <17>

AGP_SBSTBF <17>

AGP_SBSTBS <17>

AGP_ST[0..2] <17>

AGP_C_BE_L[0..3] <17>

+1_5V

AGP_SBA_L[0..7] <17>

MCH_66MHZ_CLK <8>

+1_3V

+1_5V

AGP_VREF <17,18>

C428

0.01u

3

U16G

HIA_VSWNG_MCH<18>

HIA_VREF_MCH<18>

HIB_VSWNG_MCH<18>

HIB_VREF_MCH<18>

HIA_VSWNG_MCH

HIA_VREF_MCH

HIA_RCOMP_MCH

HI_A[0..11]<19>

HIA_STBF<19>

HIA_STBS<19>

HIB_VSWNG_MCH

HIB_VREF_MCH

HIB_RCOMP_MCH

TP139

TP140

TP141

TP142

HI_A11

HI_A10

HI_A9

HI_A8

HI_A7

HI_A6

HI_A5

HI_A4

HI_A3

HI_A2

HI_A1

HI_A0

AD2

AE1

AC1

AA6

AC6

AE2

AB7

AA9

AB8

AA8

AC7

AC4

AD3

AC3

AB4

AD5

AB5

AJ4

AG6

AF7

AL2

AF6

AG3

AG5

AF4

AK3

AL1

AJ3

AK2

AJ1

AH1

AH2

AD9

AF1

AF3

AE5

AE7

AD6

AC9

AG2

AD8

AE4

AE8

AH4

AH5

HI_A_PSWNG

HI_A_PREF

HI_A_PRCOMP

HI_A11

HI_A10

HI_A9

HI_A8

HI_A7

HI_A6

HI_A5

HI_A4

HI_A3

HI_A2

HI_A1

HI_A0

HI_A_PSTRBF

HI_A_PSTRBS

HI_B_PSWNG

HI_B_PREF

HI_B_PRCOMP

HI_B21

HI_B20

HI_B18

HI_B17

HI_B16

HI_B15

HI_B14

HI_B13

HI_B12

HI_B11

HI_B10

HI_B9

HI_B8

HI_B7

HI_B6

HI_B5

HI_B4

HI_B3

HI_B2

HI_B1

HI_B0

HI_B_PSTRBF

HI_B_PSTRBS

HI_B_PUSTRBF

HI_B_PUSTRBS

MCH

2

SMB_SCL

SMB_SDA

PWRGD

TDIOANODE

TDIOCATHODE

XORMODE#

NC

NC

J21

J20

J23

Y11

W11

G1

R6

R5

TP130

12 mil

TP_MCH_NC_R6

TP_MCH_NC_R5

R269 4.7k

R268 4.7k

SYS_PWR_GD_3_3V <20,43>

R1579 4.7k

6 mil

R304

51-1%

TP129

R288

51-1%

1

+3_3V

+3_3V

R293

8.2K

+3_3V

B B

+1_5V

C427

C446

C432

C570

C425

0.1u

0.1u

0.1u

0.1u

0.1u

MCH_AGP_DECPL

+1_5V

1u-0805

C454

C465

1u-0805

PLACE WITHIN 1" OF MCH

R284

1.43K-1%

C429

0.1u

AGP_VSWNG

C430

0.01u

AGP_VSWNG:

8X:800mV 4X:VREF=750mV

SILICON WILL IGNORE VSWNG IN 4X

AND CONNECT IT TO VREF IN THE

SILICON.

796 mV

A A

5

R281

1.62K-1%

4

C1045

0.1u

C435

0.1u

C1404

0.1u

3

C1405

0.1u

PLACE THESE

COMPONENTS WITHIN

0.5" OF THE MCH

24.9 ohm for +1.2V

43.2 ohm for +1.5V

6 mil

HIA_RCOMP_MCH

6 mil

HIB_RCOMP_MCH

2

+1_3V +1_3V

R299

31.2-1%

C451

R276

31.2-1%

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

0.01u

C453

0.01u

Micro Star Restricted Secret

HIA_VSWNG_MCH

HIA_VREF_MCH

C452

4.7u

HIB_VSWNG_MCH

HIB_VREF_MCH

C439

0.01u

MCH_AGP&HLA&HLB

Last Revision Date:

Tuesday, March 18, 2003

Sheet

1

10 52

of

Rev

00E

5

6 mil

6 mil

L25

DQ_A0

J27

DQ_A1

J29

DQ_A2

L27

DQ_A3

M25

DQ_A4

G29

DQ_A5

K28

DQ_A6

M26

DQ_A7

P25

DQ_A8

R25

DQ_A9

R26

DQ_A10

R27

DQ_A11

T25

DQ_A12

M29

DQ_A13

P27

DQ_A14

P28

DQ_A15

V26

DQ_A16

U27

DQ_A17

W25

DQ_A18

W29

DQ_A19

V25

DQ_A20

U28

DQ_A21

W26

DQ_A22

W28

DQ_A23

AA25

DQ_A24

AB25

DQ_A25

AC28

DQ_A26

AD29

DQ_A27

AA26

DQ_A28

AB26

DQ_A29

AC27

DQ_A30

AE29

DQ_A31

AE21

DQ_A32

AE20

DQ_A33

AH23

DQ_A34

AG21

DQ_A35

AJ25

DQ_A36

AJ24

DQ_A37

AH22

DQ_A38

AJ22

DQ_A39

AE18

DQ_A40

AJ19

DQ_A41

AJ18

DQ_A42

AH17

DQ_A43

AF18

DQ_A44

AK20

DQ_A45

AG17

DQ_A46

AE17

DQ_A47

AE15

DQ_A48

AF15

DQ_A49

AG15

DQ_A50

AE14

DQ_A51

AK15

DQ_A52

AK14

DQ_A53

AJ13

DQ_A54

AG14

DQ_A55

AG12

DQ_A56

AH10

DQ_A57

AF12

DQ_A58

AE11

DQ_A59

AH11

DQ_A60

AJ10

DQ_A61

AG11

DQ_A62

AE12

DQ_A63

AF25

CB_A7

AG26

CB_A6

AE24

CB_A5

AE26

CB_A4

AE23

CB_A3

AG27

CB_A2

AF26

CB_A1

AF27

CB_A0

AG33

ODTCOMP

AG32

DVREF_A

L24

DDR_STRAP

DDR_STRAP

U16C

MCH

MCH_DDR CHA

GND for registered

DDR

CHA_DQ[0..63]<13,15> CHB_DQ[0..63]<14,15>

D D

C C

B B

CHA_CB[0..7]<13,15>

A A

CHA_VREF<13,16>

CHA_DQ0

CHA_DQ1

CHA_DQ2

CHA_DQ3

CHA_DQ4

CHA_DQ5

CHA_DQ6

CHA_DQ7

CHA_DQ8

CHA_DQ9

CHA_DQ10

CHA_DQ11

CHA_DQ12

CHA_DQ13

CHA_DQ14

CHA_DQ15

CHA_DQ16

CHA_DQ17

CHA_DQ18

CHA_DQ19

CHA_DQ20

CHA_DQ21

CHA_DQ22

CHA_DQ23

CHA_DQ24

CHA_DQ25

CHA_DQ26

CHA_DQ27

CHA_DQ28

CHA_DQ29

CHA_DQ30

CHA_DQ31

CHA_DQ32

CHA_DQ33

CHA_DQ34

CHA_DQ35

CHA_DQ36

CHA_DQ37

CHA_DQ38

CHA_DQ39

CHA_DQ40

CHA_DQ41

CHA_DQ42

CHA_DQ43

CHA_DQ44

CHA_DQ45

CHA_DQ46

CHA_DQ47

CHA_DQ48

CHA_DQ49

CHA_DQ50

CHA_DQ51

CHA_DQ52

CHA_DQ53

CHA_DQ54

CHA_DQ55

CHA_DQ56

CHA_DQ57

CHA_DQ58

CHA_DQ59

CHA_DQ60

CHA_DQ61

CHA_DQ62

CHA_DQ63

CHA_CB7

CHA_CB6

CHA_CB5

CHA_CB4

CHA_CB3

CHA_CB2

CHA_CB1

CHA_CB0

R184 402-1%

PLACE CLOSE

TO MCH < 0.5"

5

C287

0.1u

4

4

DM8/DQS_A17

DM7/DQS_A16

DM6/DQS_A15

DM5/DQS_A14

DM4/DQS_A13

DM3/DQS_A12

DM2/DQS_A11

DM1/DQS_A10

DM0/DQS_A9

DQS_A8

DQS_A7

DQS_A6

DQS_A5

DQS_A4

DQS_A3

DQS_A2

DQS_A1

DQS_A0

CMDCLK_A0

CMDCLK_A0#

CMDCLK_A1

CMDCLK_A1#

CMDCLK_A2

CMDCLK_A2#

CMDCLK_A3

CMDCLK_A3#

CMDCLK_A4

CMDCLK_A4#

CMDCLK_A5

CMDCLK_A5#

CMDCLK_A6/CS_A5#

CMDCLK_A6#/CS_A4#

CMDCLK_A7

CMDCLK_A7#

CKE_A3

CKE_A2

CKE_A1

CKE_A0

MA_A13

MA_A12

MA_A11

MA_A10

MA_A9

MA_A8

MA_A7

MA_A6

MA_A5

MA_A4

MA_A3

MA_A2

MA_A1

MA_A0

BA_A1

BA_A0

RAS_A#

CAS_A#

WE_A#

CS_A3#

CS_A2#

CS_A1#

CS_A0#

DRCOMPVREF_V

DRCOMPVREF_H

DRCOMP_V

DRCOMP_H

RCVENOUT_A#

AH29

AJ9

AH14

AH19

AG23

AB28

V27

N28

H28

AH28

AK8

AJ15

AG18

AF21

AB29

V29

N29

K26

AF24

AG24

AE22

AF22

AK21

AJ21

AF19

AE19

K25

J26

D31

D32

AG8

AG9

AJ6

AJ7

K31

N26

J33

K29

AM9

P33

R32

AM22

R30

Y27

T29

AA32

Y30

AA30

AC24

AD26

AG30

AH25

AH20

AE16