MSI MS-9130 9130_100&A

5

4

3

2

1

Title

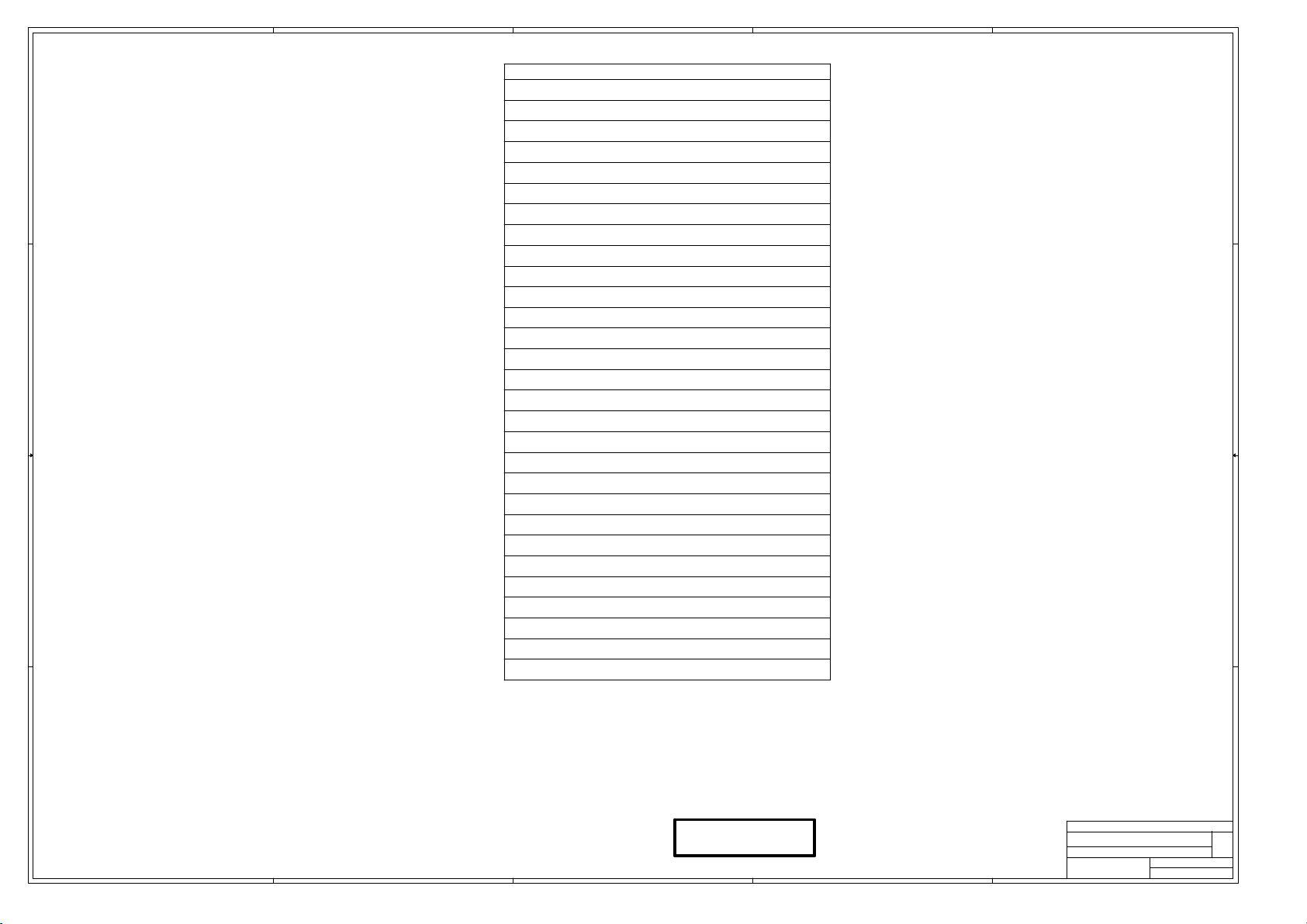

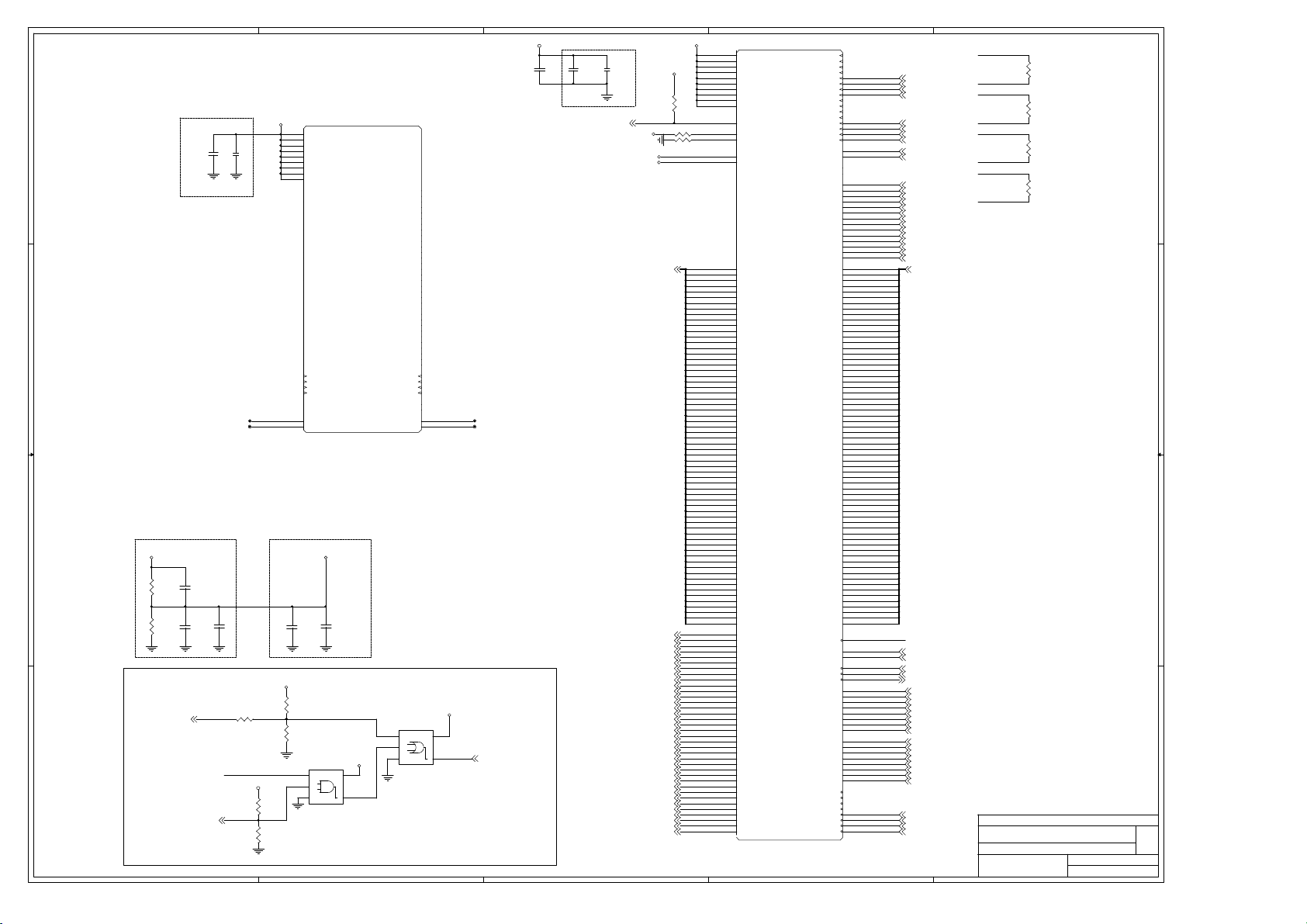

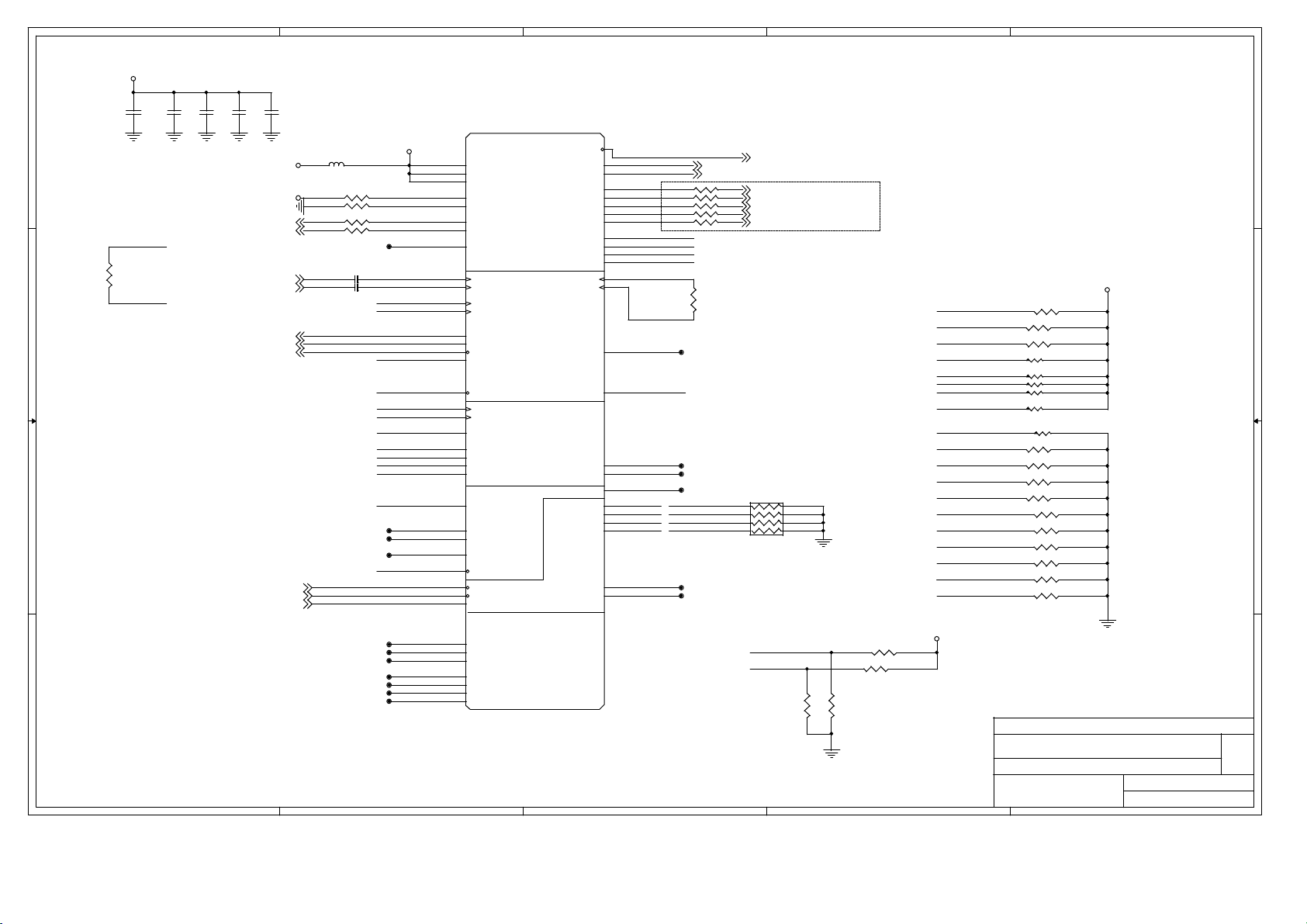

Cover Sheet

MS-9130 VER:100 ATX

D D

*Dual AMD PGA940 K8-Processor

(DDR 333)

*VIA K8T400M / VT8237 Chipset

(AGP 8X / VLink 8X)

*Winbond 83627HF LPC I/O

*BCM 5705 Giga/100/10 Bit LAN Support

*USB 2.0 support (integrated into VT8237)

Block Diagram

GPIO SPEC

Clock Synthesizer

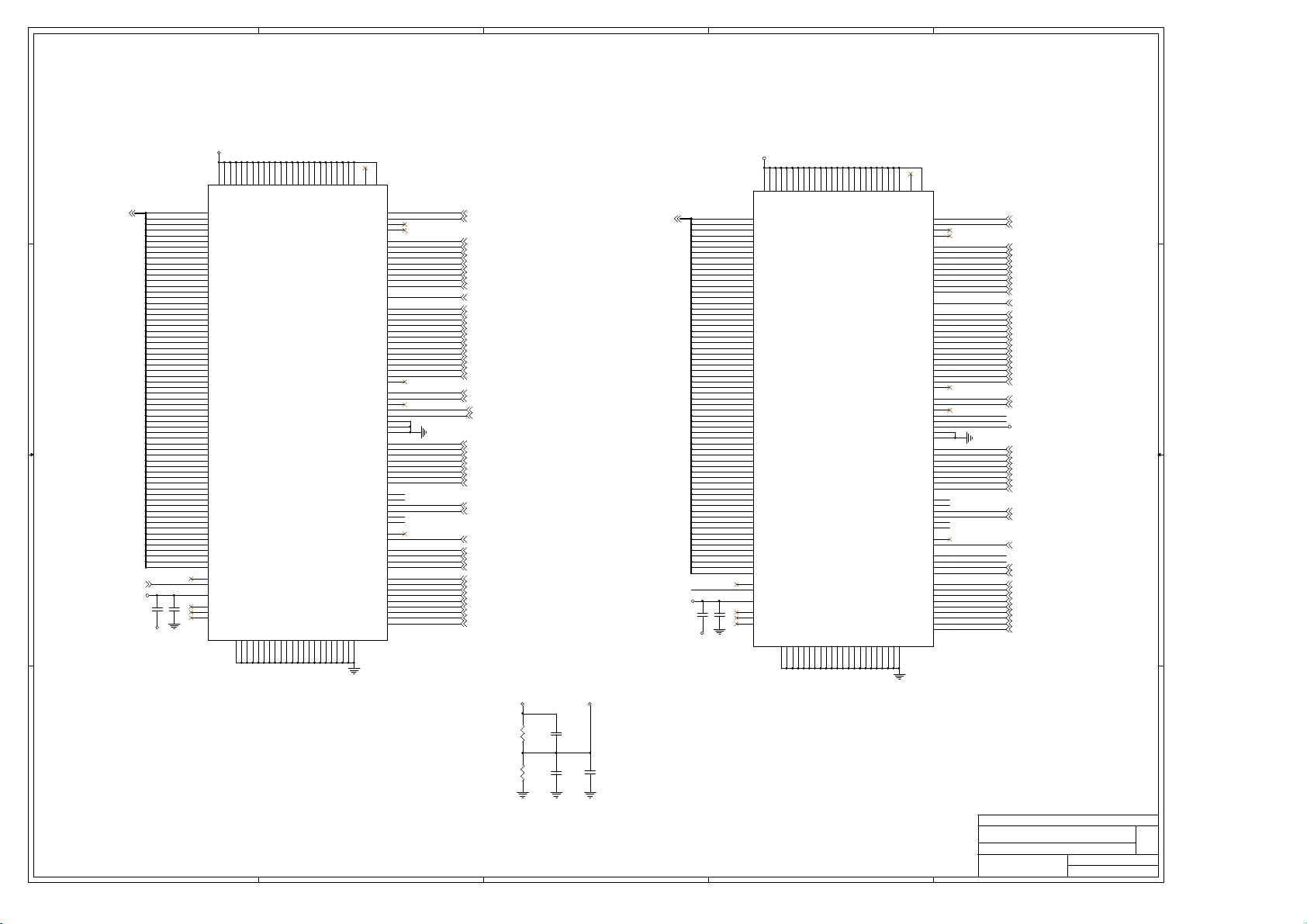

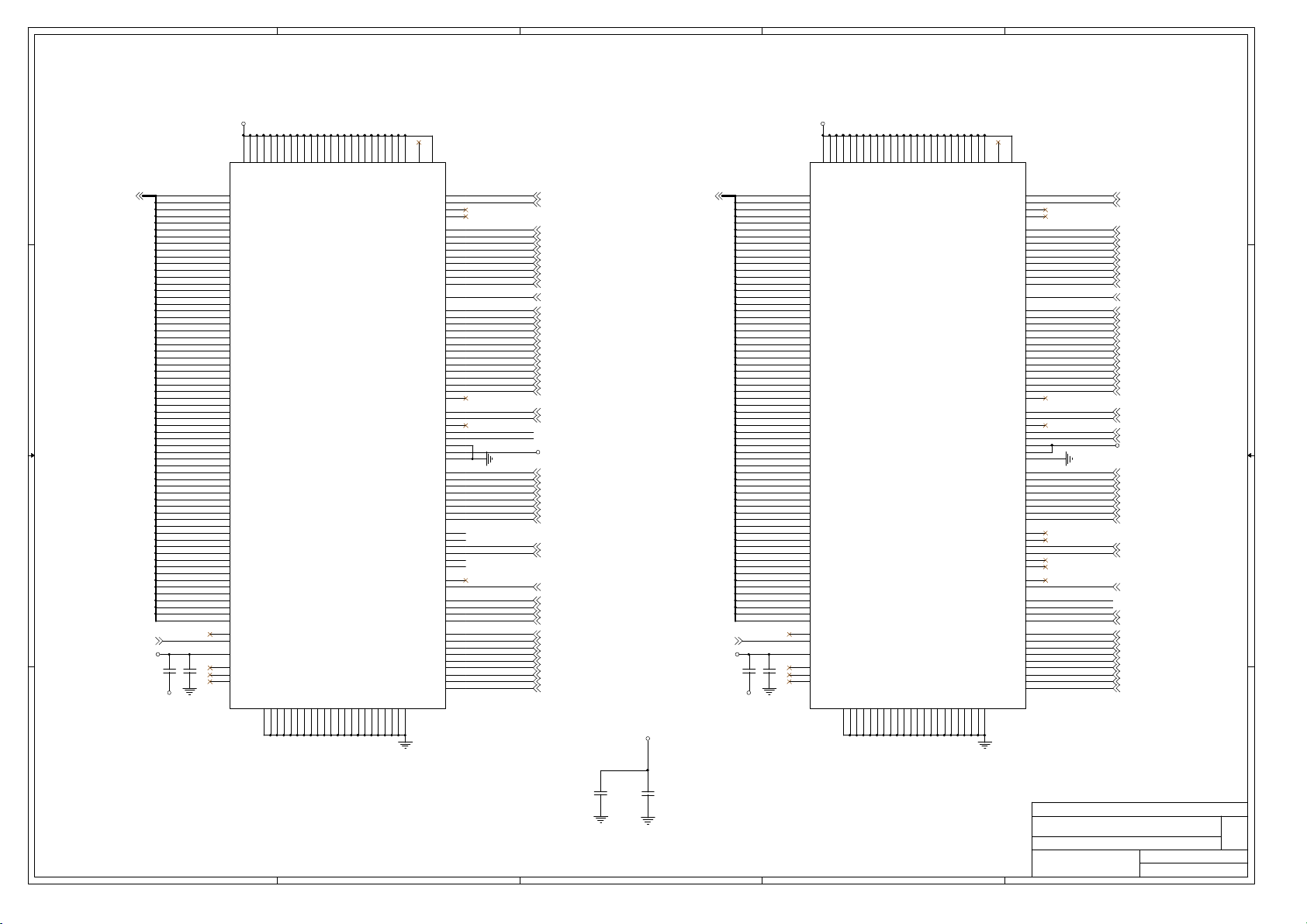

AMD K8 -> CPU 0

System Memory

DDR DIMM 1 & 2 & 3 & 4

DDR Terminations R & C

AMD K8 -> CPU 1

NB VIA K8T400M/VER:0.4 (HT)

K8 Vcore

AGP PRO SLOT 8X

VT8237

C C

*ALC201A S/W Audio

*DDR DIMM * 4

PCI Connectors * 4

AC'97 S/W Audio

IDE ATA 66/100 Connectors * 2

Front USB Port *2

*AGP PRO SLOT * 1 ( 8X )

*PCI SLOT * 4

Rear USB Port *2

LPC I/O W83627HF & Floppy

Hardware monitor & FAN

BIOS ROM & VCORE ADJUSTING

Keyboard/Mouse Connectors

LPT/COM Port

Giga-Bit LAN BCM5705

B B

Giga-Bit LAN-RJ45

ACPI Power CONTROLLER (MS-6)

SYSTEM VOLTAGE REGULATOR

Front Panel & POWER OK CIRCUIT

Decoupling Cap.

OPTION PARTS

Page

1

2

3

4

5,6,7,8

9,10

11

12,13,14,15

16,17,18

19

20

21,22,23

24,25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

A A

Micro Star Restricted Secret

MS9130-100

5

4

3

2

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

Cover Sheet

MS-9130

Last Revision Date:

Sheet

Thursday, July 17, 2003

1 41

of

Rev

100

5

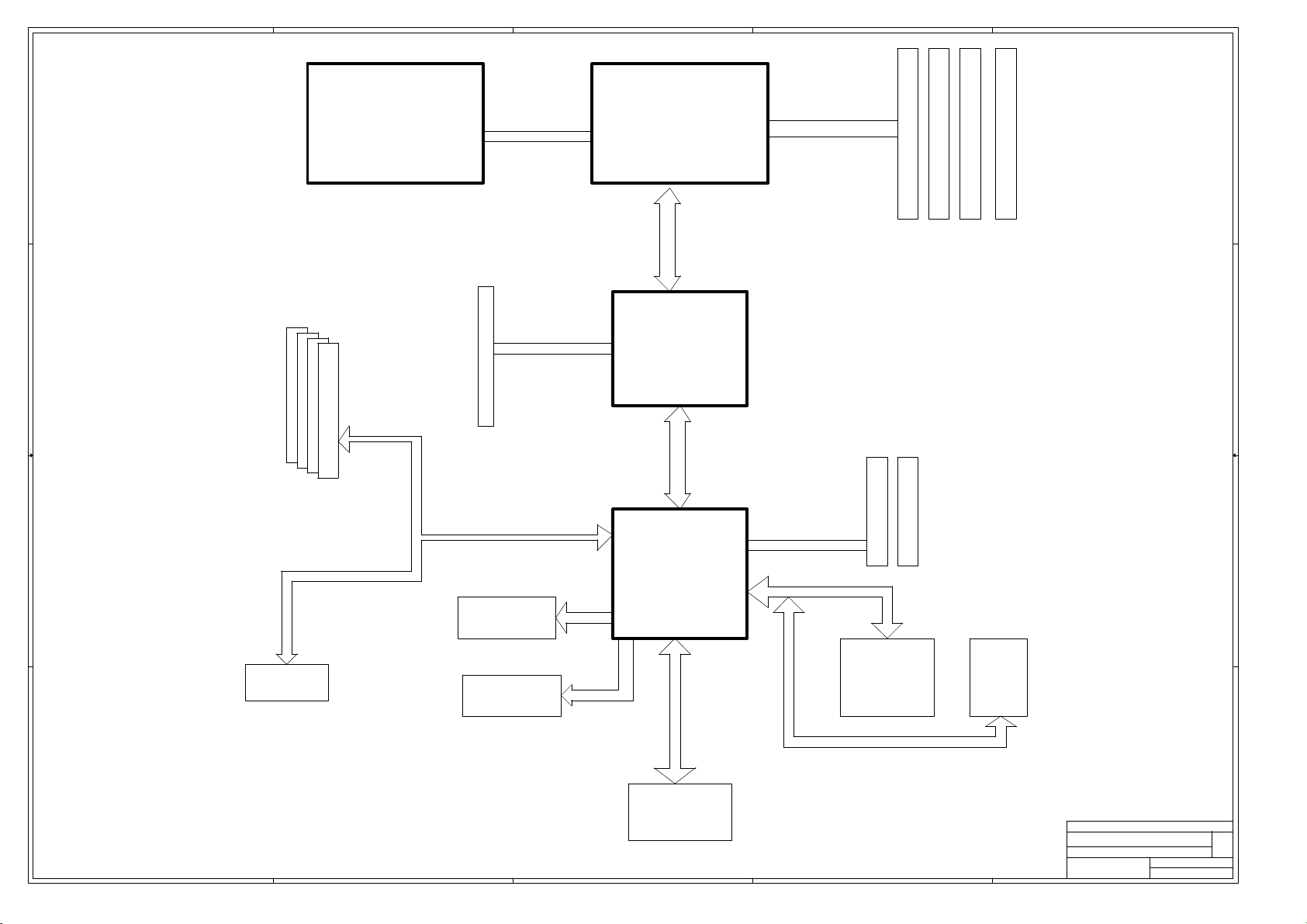

Block Diagram

4

3

2

1

D D

AMD K8 Socket 940

HT

AMD K8 Socket 940

DDR333

CPU 0CPU 1

HT

A

G

AGP 8X /Fast Write

C C

4 PCI Slots

P

S

L

O

T

PCI-33

B B

AC97 => S/W Audio

ALC202A / 2 channel

AC97

VIA

K8T400M

VLINK

VT8237

Dual ATA

100/133

LPC BUS

IDE Slot

==>ATA66,100,133 *2

DDR * 4

USB

SUPER I/O

Giga Bit LAN

BCM5705

A A

5

4

SERIAL ATA *2

3

USB

Dual USB 1.1 OHCI

/2.0 EHCI 8 Ports

==> Front-Port *4 ,

Back-Port *2

W83627HF

2

FWH

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

Block Diagram

MS-9130

Last Revision Date:

Sheet

Thursday, July 17, 2003

2 41

of

Rev

100

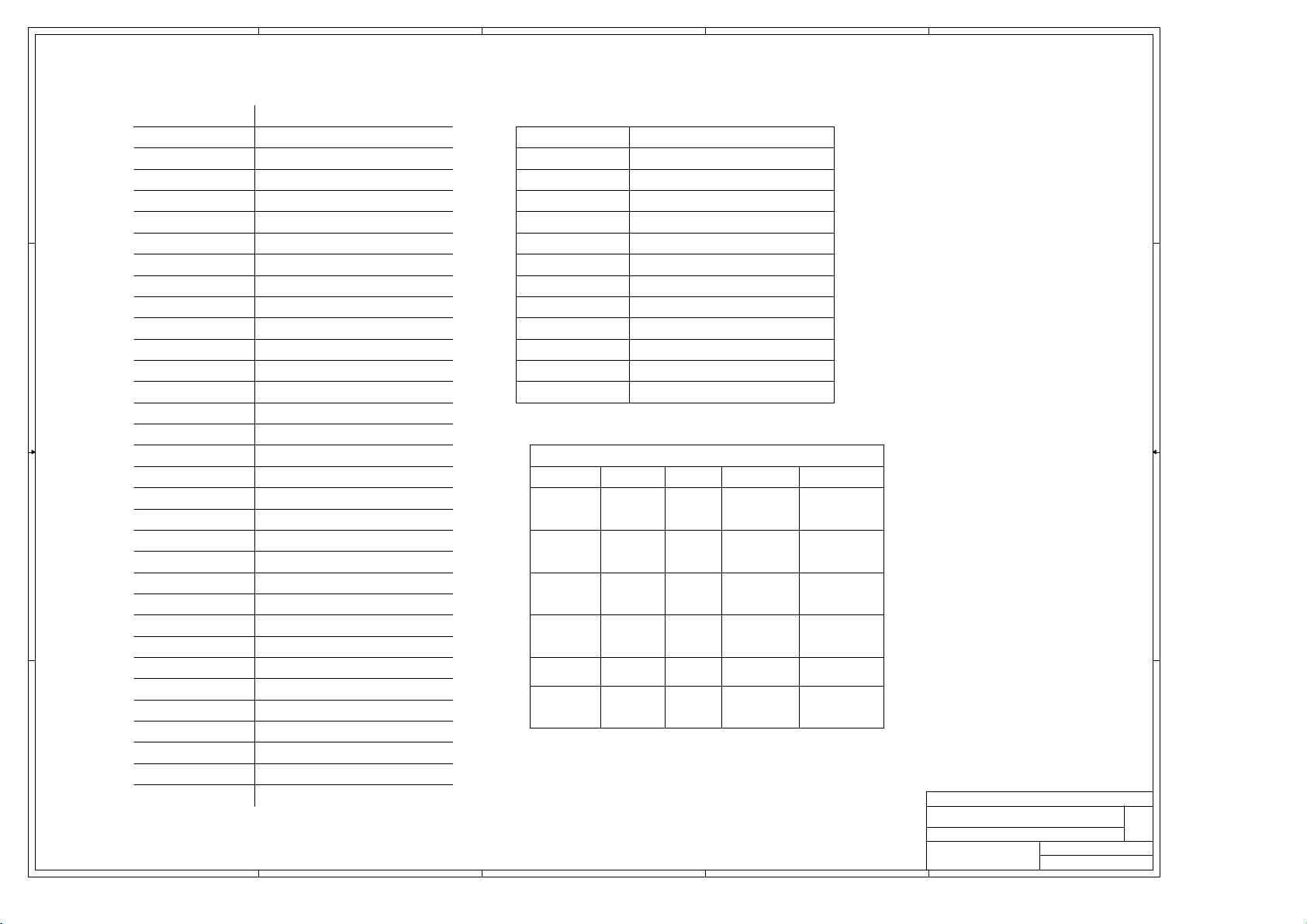

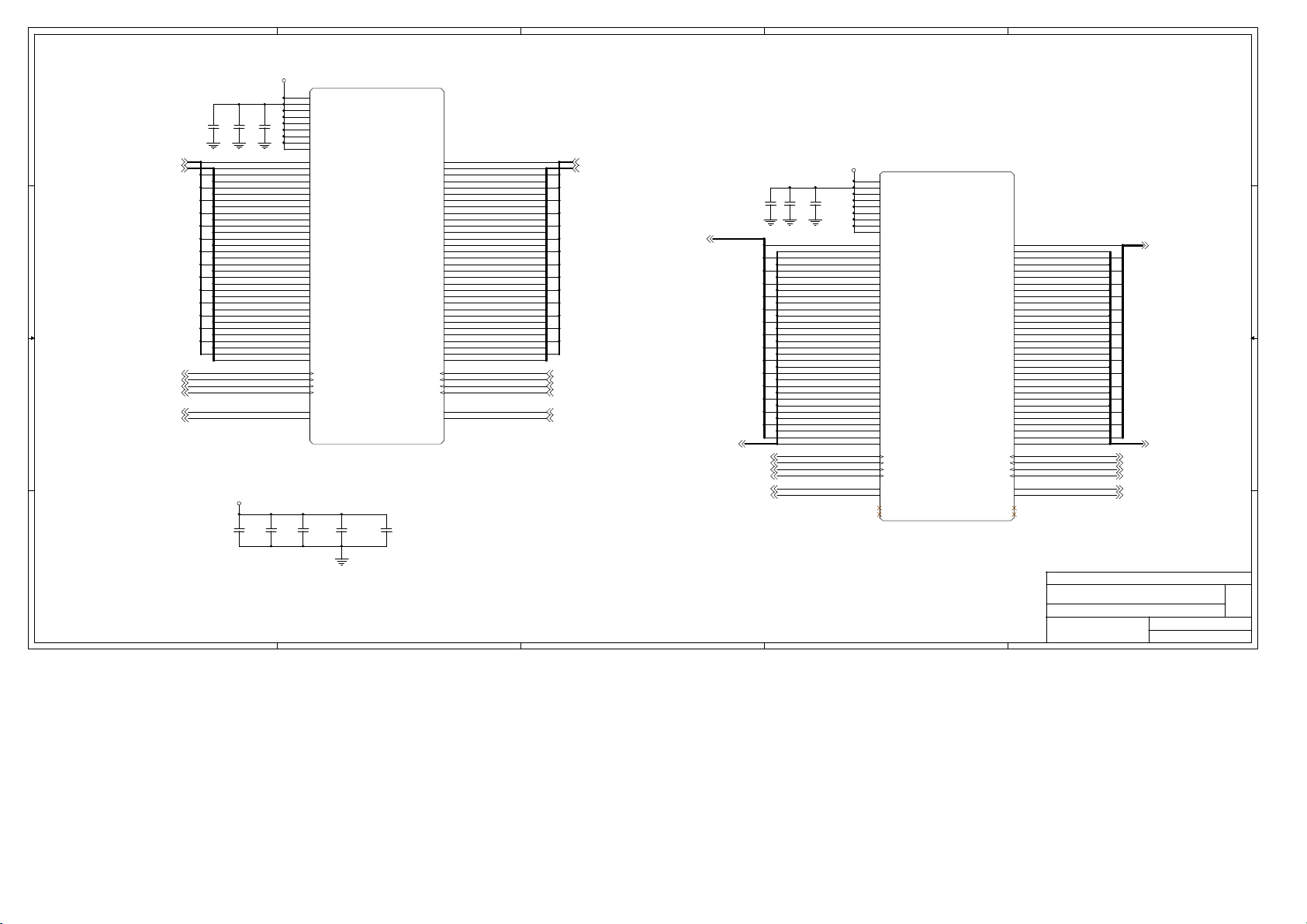

AD22

5

GPIO FUNCTION

4

3

2

1

PIN NAME

D D

GPO0 (VSUS33)

GPO1/SUSA#(VSUS33)

GPO2/SUSB#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/SLP#

GPO8/GPI8/IPBIN0

GPO9/GPI9/IPBIN1

C C

GPO10/GPI10/IPBRDFR

GPO11/GPI11/IPBRDCK

GPO12/GPI12/INTE#

GPO13/GPI13/INTF#

GPO14/GPI14/INTG#

GPO15/GPI15/INTH#

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

GPO19/SA19/STRAP

B B

GPO20/GPI20

/ACSDIN2/PCS0#/EI

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/IOR#

GPO23/GPI23/DPSLP

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOC

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

GPO28/GPI28/

VIDSEL

GPO29/GPI29/

A A

VRDSLP

GPO30/GPI30/GPIOD

GPO31/GPI31/GPIOE

5

Function define

NA

NA

SUSB#

SUSST#

(Exteranl Pull up to 3VDUAL)

NA

(Exteranl Pull up to VCC3)

NA

(Exteranl Pull up to VCC3)

NA

LDTSTOP#

NA

NA

NA

NA

NA

NA

NA

NA

LDT Freq Strapping Bit0

LDT Freq Strapping Bit1

LDT Width (Low=8 Bit)

Fast Command (Low=Disable)

POWERF1

POWERF2

NA

ROMLOCK

NA

NA

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

NA

NA

NA

NA

4

VT8237 GPIO Function Define

PIN NAME Function define

GPI0

GPI1

NA

(Exteranl Pull up to VBAT)

ATADET0=>Detect IDE1 ATA100/66

GPI2/EXTSMI# EXTSMI#

GPI3/RING# RING#

GPI4/LID#

GPI5/BATLOW#

ATADET1=>Detect IDE2 ATA100/66

(Exteranl Pull up to 3VDUAL)

NA

POWERF3GPI6/AGPBZ#

NA

GPI7/REQ#5

GPI16/INTRUDER#

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/IORDY

(Exteranl Pull up to 3VDUAL)

(Exteranl Pull up to VBAT)

NA

(Exteranl Pull up to 3VDUAL)

NA

THRM#

NA

(Exteranl Pull up to VCC3)

PCI Routing

DEVICES

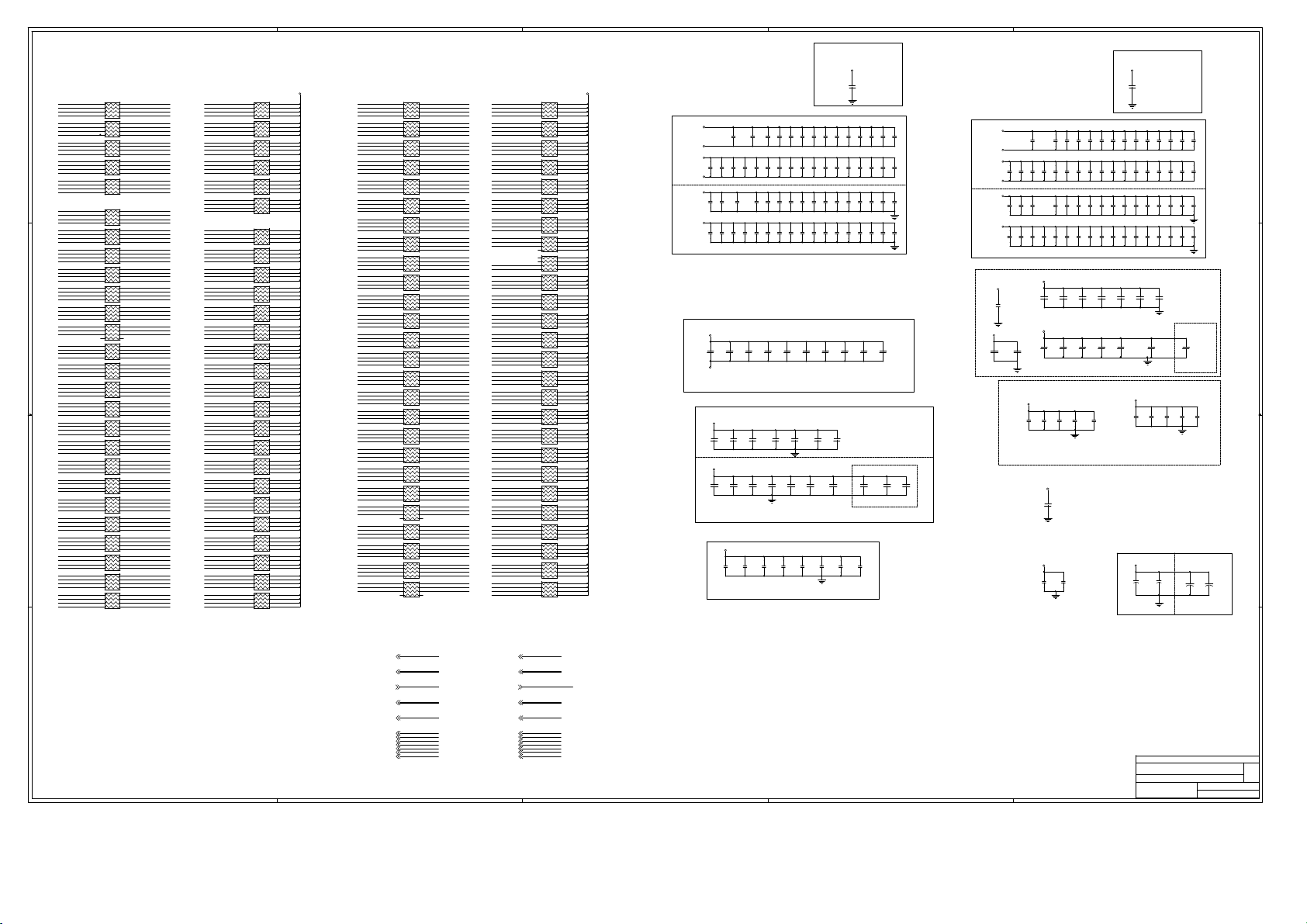

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

Giga-Bit

LAN

INT#

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D PGNT#1

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

INT#A

3

IDSEL

AD16

AD17

AD18

AD19

AD22

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#1

PREQ#2

PGNT#2

PREQ#3

PGNT#3

PREQ#4

PGNT#4

CLOCK

PCICLK1

PCICLK2

PCICLK3

PCICLK4

GLAN_PCLK

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

GPIO Spec.

MS-9130

Last Revision Date:

Thursday, July 17, 2003

Sheet

3 41

1

Rev

100

of

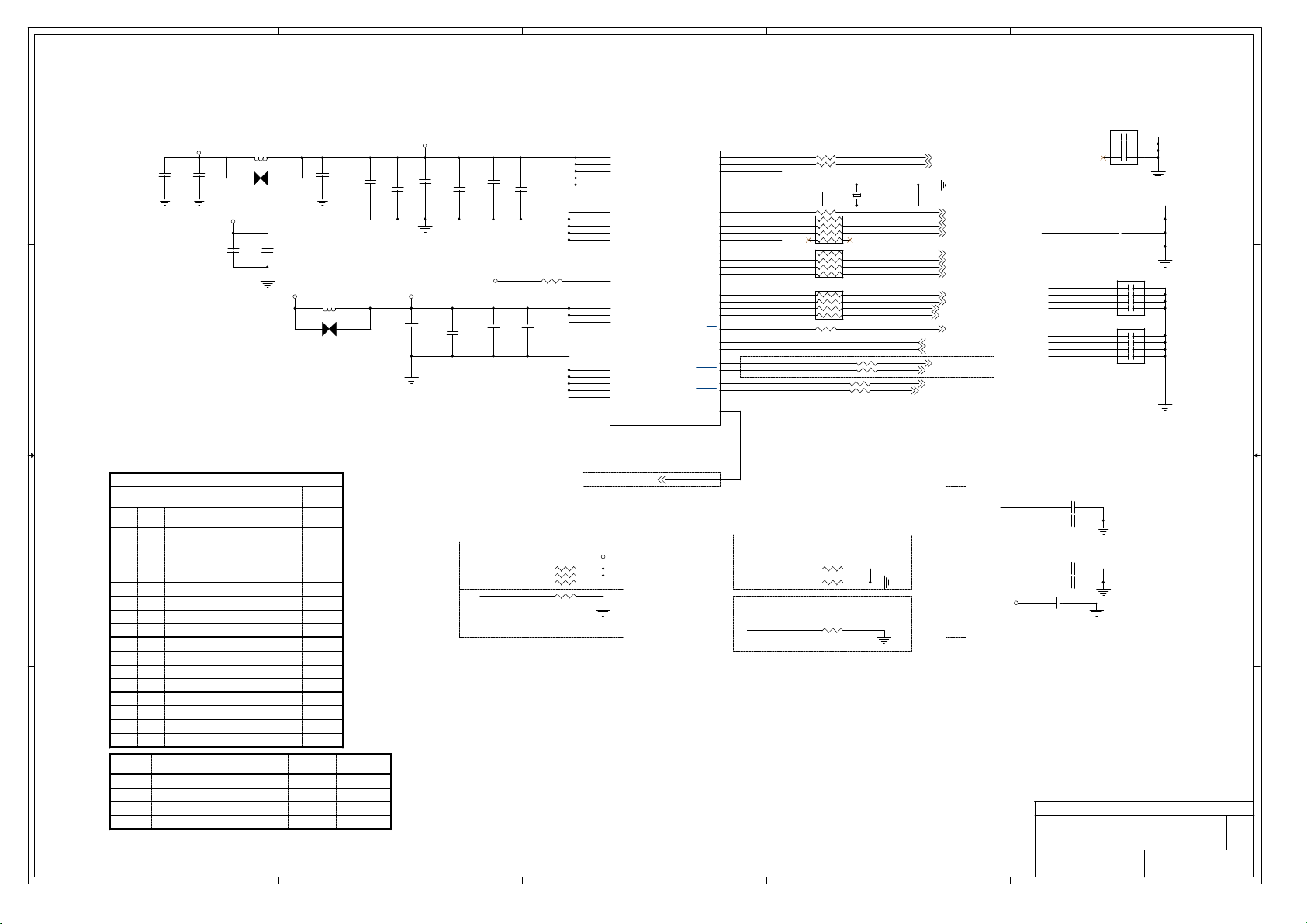

5

4

3

2

1

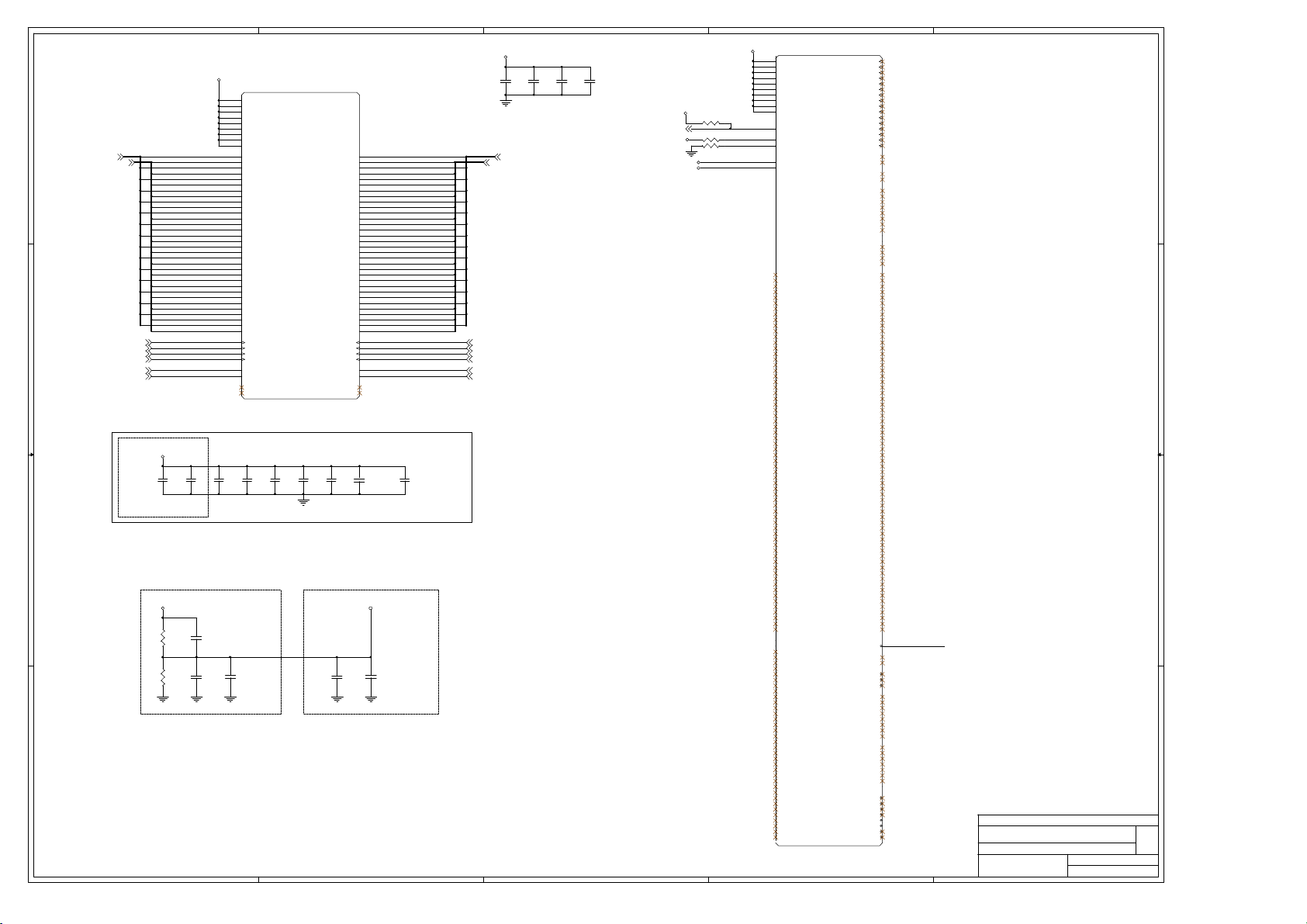

Clock Synthesizer

CN13

7 8

5 6

3 4

1 2

8P4C-10P

C256 X_10P

C257 X_10P

C258 X_10P

C259 X_10P

CN14

7 8

5 6

3 4

1 2

X_8P4C-10P

X_8P4C-10P

1 2

3 4

5 6

7 8

CN15

CPUCLK1_H

CPUCLK1_L

Near CK-Gen in 0.5" .

CPUCLK0_H

CPUCLK0_L

C268 104P

VCLK

GCLK_NB

GCLK_SLOT

USBCLK_SB

SIO48M

SB_OSC14

APICCLK

PCICLK1

PCICLK2

PCICLK3

PCICLK4

FWH_PCI

SBPCLK

GLAN_PCLK

SIOPCLK

C624 X_5P/X7R

C625 X_5P/X7R

C266 X_5P/X7R

C267 X_5P/X7R

U20

ICS950403

46

VDD_46

9

VDD_9

16

VDD_16

19

VDD_19

38

VDD_38

35

VDD_35

10

VSS_10

47

VSS_47

15

VSS_15

20

VSS_20

34

VSS_34

39

VSS_39

32

PD#

2

VDD_2

29

VDD_29

43

VDDA

5

VSS_5

27

VSS_27

30

VSS_30

33

VSSF

42

VSSA

Only support in ICS950402

CLK_RESET#39

CLKVCC3

FS0/REF0

FS1/REF1

FS2/REF2

XIN

XOUT

48MHZ

ModeAHTT66_0

ModeBHTT66_1

HT66_2

PCI33_9_HT66_3

PCI33_10

PCI33_0

PCI33_1

PCI33_2

PCI33_3

PCISTOP_PCI33_6

PCI33_F

PCI33_5

PCI33_4

24_48MHZ/SEL

SDATA

SCLK

CPUT_0

CPUC_0

CPUT_1

CPUC_1

SPREAD

FS0

1

FS1

48

FS2

45

CLKX1

3

CLKX2

4

31

MODEA

6

MODEB

7

8

R_PCICLK9

11

R_PCICLK10

12

R_PCICLK0

13

R_PCICLK1

14

R_PCICLK2

17

R_PCICLK3

18

R_PCICLK6 FWH_PCI

24

R_PCICLKF

23

R_PCICLK5

22

R_PCICLK4

21

SEL_24

28

SMBDATA1

26

SMBCLK1

25

41

40

37

36

44

ModeA,B=0:0 ( Set Pin 7,8 clock

-> 66 MHz Pin11->33Mhz )

"24_48MHZ/SEL" Freq.-Out select pin

=> Low->48MHz , Hi->24MHz .

( Internal pull-up via 100K ohm )

RN52 8P4R-22

RN53 8P4R-22

R_CPU_CLK

-R_CPU_CLK

MODEB

MODEA

SEL_24

R267 22

R268 22

R269 33

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

1 2

3 4

5 6

7 8

R271 33

R274 15RST

R275 15RST

R277 10K

R280 10K

R282 10K

X2 14.318MHZ

C255 10P

RN51

8P4R-22

R272 15RST

R273 15RST

SB_OSC14

APICCLK

SBPCLK

GLAN_PCLK

SIOPCLK

SB_OSC14 22

APICCLK 23

USBCLK_SB48MHZ

VCLK

GCLK_NB

GCLK_SLOT

PCICLK1

PCICLK2

PCICLK3

PCICLK4

SIO48M

SMBDATA1 9,10,22,24,25,35,37

SMBCLK1 9,10,22,24,25,35,37

CPUCLK0_H 6

CPUCLK0_L 6

CPUCLK1_H 13

CPUCLK1_L 13

USBCLK_SB 21

VCLK 23

GCLK_NB 17

GCLK_SLOT 20

PCICLK1 24

PCICLK2 24

PCICLK3 25

PCICLK4 25

FWH_PCI 32

SBPCLK 23

GLAN_PCLK 35

SIOPCLK 30

SIO48M 30

VCC3

Decoupling Cap for CPU Clock

C248

X_104P

4.7u/0805

C262

CLKVCC3

C252

X_104P

CLKVDDA

C249

104P

C253

104P

CLKVCC3

C263

104P

C250

X_104P

C264

X_104P

C254

104P

R270 X_10K

C265

X_104P

D D

C C

VCC3

C245

104P C251 10P

C246

104P

FB10 X_120S/0805

CP22

X_COPPER

VCC3

C260

X_104P

C261

X_104P

VCC3

C247

4.7u/0805

FB11 X_120S/0805

CP23

X_COPPER

ICS950402

Strapping CPU

FS0FS2FS3

0 0 0 0

FS1

0 0 0

B B

0 0 0

0 0

0 0 0

0 0

0 0

0

***

1

1 1

1 1

1 1 1

1 1

1 1 1

1

1 1

1

1 1

1 1

1 1 1

0 0 0

0 0

0 0

0

0 0

0

1 1 1

1 1 1 1

100.90

1

133.90

168.00

202.00

100.20

133.50

166.70

200.40

150.00

180.00

210.00

240.00

270.00

233.33

0

266.67

300.00

MHz

HTT

PCI

MHz

MHz

67.27 33.63

66.95

33.48

67.20

33.60

67.33 66.80

33.67

33.40

66.75

33.38

66.68

33.34

66.80

33.40

60.00

33.00

60.00

33.00

70.00

35.00

60.00

30.00

67.50

33.75

66.67

33.33

66.67

33.33

75.00

37.50

"FS0~FS3" are all internal

pull-up via 100K ohm ..

FS0

FS2

FS1

48MHZ

"48MHZ" is "FS3" in ICS950402 ,

But not in cy28330 .

R276 10K

R278 10K

R279 10K

R281 10K

A A

***

ModeA ModeB

0 0

0 1

1 0

1 1

5

Pin6 Pin7

HTTCLK0

ModeA In

HTTCLK1 HTTCLK2 PCICLK10

HTTCLK1 HTTCLK2 HTTCLK3

Pin8 Pin11

PCICLK7 PCICLK8 PCICLK9 PCICLK10

ModeA In

PCICLK8 PCICLK9 PCICLK10

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

4

3

2

http://www.msi.com.tw

CLOCK GENERATOR

MS-9130

Last Revision Date:

Thursday, July 17, 2003

Sheet

1

4 41

Rev

100

of

5

HT0 is for SH0 & Golem connection

VDD_12_A

K10

VLDT_1(1)

VDD_25_SUS

R345

X_1K

R346

100K

closed to F22 pinclosed to AF22 pin

J11

VLDT_1(2)

H10

VLDT_1(3)

H8

VLDT_1(4)

K14

VLDT_1(5)

J15

VLDT_1(6)

K16

VLDT_1(7)

J16

VLDT_1(8)

J9

VLDT_1(9)

E14

L1_CADIN_H(15)

E13

L1_CADIN_L(15)

C15

L1_CADIN_H(14)

D15

L1_CADIN_L(14)

E16

L1_CADIN_H(13)

E15

L1_CADIN_L(13)

C17

L1_CADIN_H(12)

D17

L1_CADIN_L(12)

C19

L1_CADIN_H(11)

D19

L1_CADIN_L(11)

E20

L1_CADIN_H(10)

E19

L1_CADIN_L(10)

C21

L1_CADIN_H(9)

D21

L1_CADIN_L(9)

E22

L1_CADIN_H(8)

E21

L1_CADIN_L(8)

C14

L1_CADIN_H(7)

B14

L1_CADIN_L(7)

A16

L1_CADIN_H(6)

A15

L1_CADIN_L(6)

C16

L1_CADIN_H(5)

B16

L1_CADIN_L(5)

A18

L1_CADIN_H(4)

A17

L1_CADIN_L(4)

A20

L1_CADIN_H(3)

A19

L1_CADIN_L(3)

C20

L1_CADIN_H(2)

B20

L1_CADIN_L(2)

A22

L1_CADIN_H(1)

A21

L1_CADIN_L(1)

C22

L1_CADIN_H(0)

B22

L1_CADIN_L(0)

E18

L1_CLKIN_H(1)

E17

L1_CLKIN_L(1)

C18

L1_CLKIN_H(0)

B18

L1_CLKIN_L(0)

A14

L1_CTLIN_H(0)

A13

L1_CTLIN_L(0)

C13

L1_RSVD1

D13

L1_RSVD2

H0_VREF0_DDR

C324

0.1u

R343

X_1K

R344

100K

U29

1

A

2

B

3 4

GND Y

SN74LVC1G08DCKR,SC-70

D D

0.22u/16V/X7R

C319

C318

1000P/50V/X7R

SOLDER SIDE

C C

TP1

TP3

B B

A A

VDD_25_SUS

C316

R339

100RST

0.1u

C322

R341

100RST

MEM_GPIO122

FROM CPU TO DIMM

C323

1000P/50V/X7R

0.1u

R465 0

H0_MEMRESET1_L

VDD_25_SUS

MEM_GPIO222

5

SledgeHammer

C325

1000P/50V/X7R

VDD_25_SUS

VCC

4

VTT_DDR_SUS

C307

4.7u/0805

U27E

L1_CADOUT_H(9)

L1_CADOUT_L(9)

L1_CADOUT_H(8)

L1_CADOUT_L(8)

L1_CADOUT_H(7)

L1_CADOUT_L(7)

L1_CADOUT_H(6)

L1_CADOUT_L(6)

L1_CADOUT_H(5)

L1_CADOUT_L(5)

L1_CADOUT_H(4)

L1_CADOUT_L(4)

L1_CADOUT_H(3)

L1_CADOUT_L(3)

L1_CADOUT_H(2)

L1_CADOUT_L(2)

L1_CADOUT_H(1)

L1_CADOUT_L(1)

L1_CADOUT_H(0)

L1_CADOUT_L(0)

L1_CLKOUT_H(1)

L1_CLKOUT_L(1)

L1_CLKOUT_H(0)

L1_CLKOUT_L(0)

L1_CTLOUT_H(0)

L1_CTLOUT_L(0)

L1_RSVD3

L1_RSVD4

D11

C11

E9

E10

D9

C9

E7

E8

E5

E6

D5

C5

E3

E4

D3

C3

A11

A12

B10

C10

A9

A10

B8

C8

B6

C6

A5

A6

B4

C4

A3

A4

D7

C7

A7

A8

B12

C12

E11

E12

TP2

TP4

L1_CADOUT_H(15)

L1_CADOUT_L(15)

L1_CADOUT_H(14)

L1_CADOUT_L(14)

L1_CADOUT_H(13)

L1_CADOUT_L(13)

L1_CADOUT_H(12)

L1_CADOUT_L(12)

L1_CADOUT_H(11)

L1_CADOUT_L(11)

L1_CADOUT_H(10)

L1_CADOUT_L(10)

VDD_25_SUS

U28

1

5

A

VCC

2

B

3 4

GND Y

5

SN74LVC1G32DBVR

H0_MEMRESET_L 9,10

modified on 1/30

4

C320

0.22u/16V/X7R

SOLDER SIDE

3

VTT_SENSE12

3

C321

1000P/50V/X7R

VDD_25_SUS

H0_VREF0_DDR

H0_VREF0_DDR

H0_MD[127..64]11

VTT_DDR_SUS

H0_MDQS3511

H0_MDQS3411

H0_MDQS3311

H0_MDQS3211

H0_MDQS3111

H0_MDQS3011

H0_MDQS2911

H0_MDQS2811

H0_MDQS2711

H0_MDQS2611

H0_MDQS2511

H0_MDQS2411

H0_MDQS2311

H0_MDQS2211

H0_MDQS2111

H0_MDQS2011

H0_MDQS1911

H0_MDQS1711

H0_MDQS1611

H0_MDQS1511

H0_MDQS1411

H0_MDQS1311

H0_MDQS1211

H0_MDQS1111

H0_MDQS1011

H0_MDQS911

H0_MDQS811

H0_MDQS711

H0_MDQS611

H0_MDQS511

H0_MDQS411

H0_MDQS311

H0_MDQS211

H0_MDQS111

H0_MDQS011

VTT_DDR_SUS

AC19

VTT1

AE19

VTT2

J19

VTT3

H19

VTT4

F20

VTT5

G19

VTT6

AE18

VTT7

AC18

R333

X_51

R335 42.2RST

R336 42.2RST

H0_MD127

H0_MD126

H0_MD125

H0_MD124

H0_MD123

H0_MD122

H0_MD121

H0_MD120

H0_MD119

H0_MD118

H0_MD117

H0_MD116

H0_MD115

H0_MD114

H0_MD113

H0_MD112

H0_MD111

H0_MD110

H0_MD109

H0_MD108

H0_MD107

H0_MD105

H0_MD104

H0_MD103

H0_MD102

H0_MD101

H0_MD100

H0_MD99

H0_MD98

H0_MD97

H0_MD96

H0_MD95

H0_MD94

H0_MD93

H0_MD92

H0_MD91

H0_MD90

H0_MD89

H0_MD88

H0_MD87

H0_MD86

H0_MD85

H0_MD84

H0_MD83

H0_MD82

H0_MD81 H0_MD17

H0_MD80

H0_MD79

H0_MD78

H0_MD77

H0_MD76

H0_MD75

H0_MD74

H0_MD73

H0_MD72

H0_MD71

H0_MD70

H0_MD69

H0_MD68

H0_MD67

H0_MD66

H0_MD65

H0_MD64

H0_MDQS35

H0_MDQS34

H0_MDQS33

H0_MDQS32

H0_MDQS31

H0_MDQS30

H0_MDQS29

H0_MDQS28

H0_MDQS27

H0_MDQS26

H0_MDQS25

H0_MDQS24

H0_MDQS23

H0_MDQS22

H0_MDQS21

H0_MDQS20

H0_MDQS19

H0_MDQS18

H0_MDQS17

H0_MDQS16

H0_MDQS15

H0_MDQS14

H0_MDQS13

H0_MDQS12

H0_MDQS11

H0_MDQS10

H0_MDQS9

H0_MDQS8

H0_MDQS7

H0_MDQS6

H0_MDQS5

H0_MDQS4

H0_MDQS3

H0_MDQS2

H0_MDQS1

H0_MDQS0

AF18

AF19

AF17

AE16

AF22

AG24

AH25

AG26

AH27

AF23

AH24

AF25

AJ26

AG27

AF26

AF28

AE29

AJ29

AH29

AE27

AD26

AD27

AC26

AA26

AA28

AD28

AC27

AB29

AA27

W27

AG25

AF27

AB27

W29

AF24

AG28

AC28

AJ25

AJ30

AD29

AA31

AL25

AL29

AE31

F21

F22

Y27

Y28

V28

U26

Y26

V27

U27

P28

N29

M26

L28

P27

P26

M27

L27

K29

K27

H28

G29

L26

J28

H27

H26

F27

F26

D29

D27

G27

F28

E27

C27

C26

E25

D24

F23

E26

F25

E24

G23

R27

N27

J27

E29

F24

R28

V26

M28

J26

E28

D25

U31

M30

H30

C30

B25

T31

Y29

M29

H29

C29

C25

VTT8

VTT9

VTT10

VTT_SENSE

MEMZN

MEMZP

MEMVREF0

MEMVREF1

MEMDATA(127)

MEMDATA(126)

MEMDATA(125)

MEMDATA(124)

MEMDATA(123)

MEMDATA(122)

MEMDATA(121)

MEMDATA(120)

MEMDATA(119)

MEMDATA(118)

MEMDATA(117)

MEMDATA(116)

MEMDATA(115)

MEMDATA(114)

MEMDATA(113)

MEMDATA(112)

MEMDATA(111)

MEMDATA(110)

MEMDATA(109)

MEMDATA(108)

MEMDATA(107)

MEMDATA(106)

MEMDATA(105)

MEMDATA(104)

MEMDATA(103)

MEMDATA(102)

MEMDATA(101)

MEMDATA(100)

MEMDATA(99)

MEMDATA(98)

MEMDATA(97)

MEMDATA(96)

MEMDATA(95)

MEMDATA(94)

MEMDATA(93)

MEMDATA(92)

MEMDATA(91)

MEMDATA(90)

MEMDATA(89)

MEMDATA(88)

MEMDATA(87)

MEMDATA(86)

MEMDATA(85)

MEMDATA(84)

MEMDATA(83)

MEMDATA(82)

MEMDATA(81)

MEMDATA(80)

MEMDATA(79)

MEMDATA(78)

MEMDATA(77)

MEMDATA(76)

MEMDATA(75)

MEMDATA(74)

MEMDATA(73)

MEMDATA(72)

MEMDATA(71)

MEMDATA(70)

MEMDATA(69)

MEMDATA(68)

MEMDATA(67)

MEMDATA(66)

MEMDATA(65)

MEMDATA(64)

MEMDQS(35)

MEMDQS(34)

MEMDQS(33)

MEMDQS(32)

MEMDQS(31)

MEMDQS(30)

MEMDQS(29)

MEMDQS(28)

MEMDQS(27)

MEMDQS(26)

MEMDQS(25)

MEMDQS(24)

MEMDQS(23)

MEMDQS(22)

MEMDQS(21)

MEMDQS(20)

MEMDQS(19)

MEMDQS(18)

MEMDQS(17)

MEMDQS(16)

MEMDQS(15)

MEMDQS(14)

MEMDQS(13)

MEMDQS(12)

MEMDQS(11)

MEMDQS(10)

MEMDQS(9)

MEMDQS(8)

MEMDQS(7)

MEMDQS(6)

MEMDQS(5)

MEMDQS(4)

MEMDQS(3)

MEMDQS(2)

MEMDQS(1)

MEMDQS(0)

U27B

MEMCLK_UP_H(3)

MEMCLK_UP_L(3)

MEMCLK_UP_H(2)

MEMCLK_UP_L(2)

MEMCLK_UP_H(1)

MEMCLK_UP_L(1)

MEMCLK_UP_H(0)

MEMCLK_UP_L(0)

MEMCLK_LO_H(3)

MEMCLK_LO_L(3)

MEMCLK_LO_H(2)

MEMCLK_LO_L(2)

MEMCLK_LO_H(1)

MEMCLK_LO_L(1)

MEMCLK_LO_H(0)

MEMCLK_LO_L(0)

MEMCHECK(15)

MEMCHECK(14)

MEMCHECK(13)

MEMCHECK(12)

MEMCHECK(11)

MEMCHECK(10)

MEMCHECK(9)

MEMCHECK(8)

MEMCHECK(7)

MEMCHECK(6)

MEMCHECK(5)

MEMCHECK(4)

MEMCHECK(3)

MEMCHECK(2)

MEMCHECK(1)

MEMCHECK(0)

SledgeHammer

2

MEMCKE_UP

MEMCKE_LO

RSVD_MA(15)

RSVD_MA(14)

MEMADD(13)

MEMADD(12)

MEMADD(11)

MEMADD(10)

MEMADD(9)

MEMADD(8)

MEMADD(7)

MEMADD(6)

MEMADD(5)

MEMADD(4)

MEMADD(3)

MEMADD(2)

MEMADD(1)

MEMADD(0)

MEMDATA(63)

MEMDATA(62)

MEMDATA(61)

MEMDATA(60)

MEMDATA(59)

MEMDATA(58)

MEMDATA(57)

MEMDATA(56)

MEMDATA(55)

MEMDATA(54)

MEMDATA(53)

MEMDATA(52)

MEMDATA(51)

MEMDATA(50)

MEMDATA(49)

MEMDATA(48)

MEMDATA(47)

MEMDATA(46)

MEMDATA(45)

MEMDATA(44)

MEMDATA(43)

MEMDATA(42)

MEMDATA(41)

MEMDATA(40)

MEMDATA(39)

MEMDATA(38)

MEMDATA(37)

MEMDATA(36)

MEMDATA(35)

MEMDATA(34)

MEMDATA(33)

MEMDATA(32)

MEMDATA(31)

MEMDATA(30)

MEMDATA(29)

MEMDATA(28)

MEMDATA(27)

MEMDATA(26)

MEMDATA(25)

MEMDATA(24)

MEMDATA(23)

MEMDATA(22)

MEMDATA(21)

MEMDATA(20)

MEMDATA(19)

MEMDATA(18)

MEMDATA(17)

MEMDATA(16)

MEMDATA(15)

MEMDATA(14)

MEMDATA(13)

MEMDATA(12)

MEMDATA(11)

MEMDATA(10)

MEMDATA(9)

MEMDATA(8)

MEMDATA(7)

MEMDATA(6)

MEMDATA(5)

MEMDATA(4)

MEMDATA(3)

MEMDATA(2)

MEMDATA(1)

MEMDATA(0)

MEMRESET_L

MEMBANK(1)

MEMBANK(0)

MEMRAS_L

MEMCAS_L

MEMWE_L

MEMCS_L(7)

MEMCS_L(6)

MEMCS_L(5)

MEMCS_L(4)

MEMCS_L(3)

MEMCS_L(2)

MEMCS_L(1)

MEMCS_L(0)

2

G20

G21

AE21

AE20

H0_MEMCLK_H3

L24

H0_MEMCLK_L3

L25

H0_MEMCLK_H2

R23

H0_MEMCLK_L2

T23

H23

J23

AD21

AD20

H0_MEMCLK_H1

Y23

H0_MEMCLK_L1

AA23

H0_MEMCLK_H0

U25

H0_MEMCLK_L0

U24

H0_MCKEUP

H24

H0_MCKELO

H25

V23

M23

AE23

J24

J25

V24

K23

L23

K25

M25

M24

N25

N23

P23

T25

V25

AJ24

AK25

AK27

AJ27

AL24

AK24

AL26

AL27

AJ28

AK30

AJ31

AG29

AL28

AK28

AH31

AG30

AG31

AF30

AD31

AC30

AF29

AF31

AD30

AC29

AB31

AA29

Y31

W31

AC31

AA30

Y30

V29

P31

M31

L30

L29

P29

N31

L31

K31

J30

J29

G31

F29

J31

H31

F31

F30

D31

C31

B30

C28

E31

E30

A29

B28

B27

A26

C24

A24

A28

A27

A25

B24

H0_MEMRESET1_L

G25

W25

W23

H0_-MSRASA

Y25

H0_-MSCASA

AA25

Y24

H0_MEMCHECK15

U28

H0_MEMCHECK14

T29

H0_MEMCHECK13

P24

H0_MEMCHECK12

P25

H0_MEMCHECK11

T27

H0_MEMCHECK10

R26

H0_MEMCHECK9

R25

H0_MEMCHECK8

R24

H0_MEMCHECK7

V30

H0_MEMCHECK6

U29

H0_MEMCHECK5

R30

H0_MEMCHECK4

P30

H0_MEMCHECK3

V31

H0_MEMCHECK2

U30

H0_MEMCHECK1

R29

H0_MEMCHECK0

R31

AD23

AE25

AD24

AD25

AC24

AC25

AB25

AA24

H0_MAA13

H0_MAA12

H0_MAA11

H0_MAA10

H0_MAA9

H0_MAA8

H0_MAA7

H0_MAA6

H0_MAA5

H0_MAA4

H0_MAA3

H0_MAA2

H0_MAA1

H0_MAA0

H0_MD63

H0_MD62

H0_MD61

H0_MD60

H0_MD59

H0_MD58

H0_MD57

H0_MD56

H0_MD55

H0_MD54

H0_MD53

H0_MD52

H0_MD51

H0_MD50

H0_MD49

H0_MD48

H0_MD47

H0_MD46

H0_MD45

H0_MD44

H0_MD43

H0_MD42H0_MD106

H0_MD41

H0_MD40

H0_MD39

H0_MD38

H0_MD37

H0_MD36

H0_MD35

H0_MD34

H0_MD33

H0_MD32

H0_MD31

H0_MD30

H0_MD29

H0_MD28

H0_MD27

H0_MD26

H0_MD25

H0_MD24

H0_MD23

H0_MD22

H0_MD21

H0_MD20

H0_MD19

H0_MD18

H0_MD16

H0_MD15

H0_MD14

H0_MD13

H0_MD12

H0_MD11

H0_MD10

H0_MD9

H0_MD8

H0_MD7

H0_MD6

H0_MD5

H0_MD4

H0_MD3

H0_MD2

H0_MD1

H0_MD0

H0_-MCS3

H0_-MCS2

H0_-MCS1

H0_-MCS0

H0_MEMCLK_H3 10

H0_MEMCLK_L3 10

H0_MEMCLK_H2 9

H0_MEMCLK_L2 9

H0_MEMCLK_H1 10

H0_MEMCLK_L1 10

H0_MEMCLK_H0 9

H0_MEMCLK_L0 9

H0_MCKEUP 11

H0_MCKELO 11

H0_MAA13 11

H0_MAA12 11

H0_MAA11 11

H0_MAA10 11

H0_MAA9 11

H0_MAA8 11

H0_MAA7 11

H0_MAA6 11

H0_MAA5 11

H0_MAA4 11

H0_MAA3 11

H0_MAA2 11

H0_MAA1 11

H0_MAA0 11

H0_MD[63..0] 11

H0_MEMBAKA1 11

H0_MEMBAKA0 11

H0_-MSRASA 11

H0_-MSCASA 11

H0_-MSWEA 11

H0_MEMCHECK15 11

H0_MEMCHECK14 11

H0_MEMCHECK13 11

H0_MEMCHECK12 11

H0_MEMCHECK11 11

H0_MEMCHECK10 11

H0_MEMCHECK9 11

H0_MEMCHECK8 11H0_MDQS1811

H0_MEMCHECK7 11

H0_MEMCHECK6 11

H0_MEMCHECK5 11

H0_MEMCHECK4 11

H0_MEMCHECK3 11

H0_MEMCHECK2 11

H0_MEMCHECK1 11

H0_MEMCHECK0 11

H0_-MCS3 11

H0_-MCS2 11

H0_-MCS1 11

H0_-MCS0 11

H0_MEMCLK_H3

H0_MEMCLK_L3

H0_MEMCLK_H2

H0_MEMCLK_L2

H0_MEMCLK_H1

H0_MEMCLK_L1

H0_MEMCLK_H0

H0_MEMCLK_L0

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

R332

(BOT)120RST

R334

(BOT)120RST

R337

(BOT)120RST

R338

(BOT)120RST

Micro Star Restricted Secret

CPU0_K8 DDR & HT

1

MS-9130

1

Last Revision Date:

Thursday, July 17, 2003

Sheet

5 41

Rev

100

of

5

VDDA25

C326

4.7u/0805

D D

C327

1000P/50V/X7R

Routed differentially

with a 20/5/5/5/20.

3300p/50V/X7R

VERY CLOSE TO CPU

CLKIN0_H

R360

(BOT)169RST

PS_ON#A39

CLKIN0_L

-LDTSTOP

PS_ON#A

5

C C

B B

A A

C328

VDD_12_A

VCC2_5

C329

0.22u/16V

-CPURST13,39

-LDTSTOP13,16,23

CPU_GD13,37

R374 680

CT6

100u/10V

VDDA_25

C647 0.1u

COREFB_H13,19

COREFB_L13,19

CPUCLK0_H4

CPUCLK0_L4

R368 680

Q46

2N7002S

FB12 180nH/1210

TMS13

TCK13

TRST_L13

VCC2_5

C681

33P

R351 43.2RST

R353 43.2RST

R356 0

R358 0

3900P/50V/X7R

C330

C331

TMS

TCK

TRST_L

C682

33P

4

VDDA25

TP5

3900P/50V/X7R

H0_NC_G14

H0_NC_H14

H0_TDI

H0_DBREQ_L

H0_SCANCLK1

H0_SCANCLK2

H0_SCANEN

H0_SSENA

H0_SSENB

H0_NC_T3

H0_NC_T4

H0_NC_AF13

TP9

TP10

TP11

H0_NC_AE14

TP14

TP15

TP16

TP17

TP18

TP19

TP20

4

LAYOUT:

Route VDDA trace approx. 50 mils wide

(use 2x25 mil traces to exit ball) and

500 mils long.

CLKIN0_H

CLKIN0_L

G16

H16

G14

H14

AE6

AE7

AD7

AF7

AE10

AE11

AF11

AE13

AE12

AF13

AF15

AE14

G12

F12

AG1

AH2

AJ2

AA6

AC6

C1

D2

C2

E1

D1

L7

L6

K7

J7

T3

T4

L8

K8

J6

H9

N6

VDDA1

VDDA2

VDDA3

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORESENSE_H

CLKIN_H

CLKIN_L

BYPASSCLK_H

BYPASSCLK_L

TMS

TCK

TRST_L

TDI

DBREQ_L

SCANCLK1

SCANCLK2

SCANEN

SCANSHIFTEN

SCANSHIFTENB

SCANIN_H

SCANIN_L

SINGLECHAIN

PLLCHRZ_H

PLLCHRZ_L

DCLKTWO

BURNIN_L

RESET_L

LDTSTOP_L

PWROK

FREE7

FREE11

FREE15

FREE12

FREE21

FREE1

FREE3

SledgeHammer

U27C

RSVD_SMBUSC

RSVD_SMBUSD

THERMTRIP_L

THERMDA

THERMDC

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

BP(3)

BP(2)

BP(1)

BP(0)

FBCLKOUT_H

FBCLKOUT_L

TDO

DBRDY

SCANOUT_H

SCANOUT_L

TSTOUT

ANALOG3

ANALOG2

ANALOG1

ANALOG0

3

AE15

AJ1

AH1

G9

F9

G10

H11

G11

H13

G6

F7

H12

H0_FBCLKOUT_H

G18

H18

H0_FBCLKOUT_L

AE8

H0_DBRDY

G8

V5

U5

H7

U1_T7

T7

U1_W6

W6

U1_R6

R6

U1_U6

U6

AF9

AE9

3

THERMTRIP_CPU_L

THERMDA_CPU1 30,31

VTIN_GND 13,30

R350 0

R352 0

R354 0

R355 0

R357 0

H0_BP3

H0_BP2

H0_BP1

H0_BP0

R359

80.6RST

LAYOUT:

Route FBCLKOUT_H/L differentially

with 20/5/5/5/20 for 1.5" to escape the BGA.

TP6

TP42

TP7

TP8

U1_R6

U1_U6

U1_T7

U1_W6

TP12

TP13

Routed differentially.

VID4 19

VID3 19,32

VID2 19,32

VID1 19,32

VID0 19,32

This termination

resistor should

be placed as

close to

Processor as

possible.

RN55

12

34

56

78

510_8P4R

VCC2_5

modified on 1/30

2

R348

2

1

R347 X0

1K

Q45 2N3904S

VCC2_5

THERMTRIP_CPU113

R349

4.7K

R444 1K

VCC2_5

Q49 2N3904S

STRAPPINGS

H0_NC_G14

H0_NC_AE14

H0_NC_AF13

H0_TDI

H0_DBREQ_L

H0_DBRDY

H0_NC_H14

H0_SCANEN

H0_SCANCLK1

H0_SCANCLK2

H0_SSENA

H0_SSENB

H0_BP3

H0_BP2

H0_BP1

H0_BP0

H0_NC_T4

H0_NC_T3

49.9RST

R361 820

R362 680

R363 680

R364 1K

R365 1K

R366 1K

R367 820

R369 680

R370 680

R371 680

R372 680

R373 680

R466 X_680

R467 X_680

R468 680

R469 680

R379

THRM# 22,30,37

R445

4.7K

R376 49.9RST

R378 X_49.9RST

R380

X_49.9RST

VCC2_5

VCC2_5

VDD_12_A

Micro Star Restricted Secret

Title

CPU0_K8 HDT & MISC

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-9130

Last Revision Date:

Thursday, July 17, 2003

Sheet

6 41

1

Rev

100

of

5

4

3

2

1

VDD_12_A

N7

VLDT_0(1)

R7

VLDT_0(2)

U7

D D

H0_CADIN[15..0]12

H0_CADIN#[15..0]12

C C

H0_CLKIN#112

H0_CLKIN#012

B B

H0_CTLIN#012

CT7

C648

C649

0.22u/X7R

H0_CADIN15

H0_CADIN#15

H0_CADIN14

H0_CADIN#14

H0_CADIN13

H0_CADIN#13

H0_CADIN12

H0_CADIN#12

H0_CADIN11

H0_CADIN#11

H0_CADIN10

H0_CADIN#10

H0_CADIN9

H0_CADIN#9

H0_CADIN8

H0_CADIN#8

H0_CADIN7

H0_CADIN#7

H0_CADIN6

H0_CADIN#6

H0_CADIN5

H0_CADIN#5

H0_CADIN4

H0_CADIN#4

H0_CADIN3

H0_CADIN#3

H0_CADIN2

H0_CADIN#2

H0_CADIN1

H0_CADIN#1

H0_CADIN0

H0_CADIN#0

H0_CLKIN1

H0_CLKIN#1

H0_CLKIN0

H0_CLKIN#0

H0_CTLIN0

H0_CTLIN#0

103P

100u/10V

H0_CLKIN112

H0_CLKIN012

H0_CTLIN012

W7

M8

P8

AA7

V8

Y8

R5

T5

P3

P4

N5

P5

M3

M4

K3

K4

J5

K5

H3

H4

G5

H5

R3

R2

N1

P1

N3

N2

L1

M1

J1

K1

J3

J2

G1

H1

G3

G2

L5

M5

L3

L2

R1

T1

VLDT_0(3)

VLDT_0(4)

VLDT_0(5)

VLDT_0(6)

VLDT_0(7)

VLDT_0(8)

VLDT_0(9)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

VDD_12_A

C310

C309

C308

0.22u/16V/X7R

A A

5

0.22u/16V/X7R

1000P/50V/X7R

SledgeHammer

C311

1000P/50V/X7R

U27A

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

CT5

100u/10V

4

H0_CADOUT15

V4

H0_CADOUT#15

V3

H0_CADOUT14

Y5

H0_CADOUT#14

W5

H0_CADOUT13

Y4

H0_CADOUT#13

Y3

H0_CADOUT12

AB5

H0_CADOUT#12

AA5

H0_CADOUT11

AD5

H0_CADOUT#11

AC5

H0_CADOUT10

AD4

H0_CADOUT#10

AD3

H0_CADOUT9

AF5

H0_CADOUT#9

AE5

H0_CADOUT8

AF4

H0_CADOUT#8

AF3

H0_CADOUT7

V1

H0_CADOUT#7

U1

H0_CADOUT6

W2

H0_CADOUT#6

W3

H0_CADOUT5

Y1

H0_CADOUT#5

W1

H0_CADOUT4

AA2

H0_CADOUT#4

AA3

H0_CADOUT3

AC2

H0_CADOUT#3

AC3

H0_CADOUT2

AD1

H0_CADOUT#2

AC1

H0_CADOUT1

AE2

H0_CADOUT#1

AE3

H0_CADOUT0

AF1

H0_CADOUT#0

AE1

H0_CLKOUT1

AB4

H0_CLKOUT#1

AB3

H0_CLKOUT0

AB1

H0_CLKOUT#0

AA1

H0_CTLOUT0

U2

H0_CTLOUT#0

U3

H0_CADOUT[15..0] 12

H0_CADOUT#[15..0] 12

H0_CLKOUT1 12

H0_CLKOUT#1 12

H0_CLKOUT0 12

H0_CLKOUT#0 12

H0_CTLOUT0 12

H0_CTLOUT#0 12

VDD_12_A

AB10

VLDT_2(1)

AC11

VLDT_2(2)

AD10

C650

0.22u/16V/X7R

L0_CADIN15

L0_CADIN#15

L0_CADIN14

L0_CADIN#14

L0_CADIN13

L0_CADIN#13

L0_CADIN12

L0_CADIN#12

L0_CADIN11

L0_CADIN#11

L0_CADIN10

L0_CADIN#10

L0_CADIN9

L0_CADIN#9

L0_CADIN8

L0_CADIN#8

L0_CADIN7

L0_CADIN#7

L0_CADIN6

L0_CADIN#6

L0_CADIN5

L0_CADIN#5

L0_CADIN4

L0_CADIN#4

L0_CADIN3

L0_CADIN#3

L0_CADIN2

L0_CADIN#2

L0_CADIN1

L0_CADIN#1

L0_CADIN0

L0_CADIN#0

L0_CLKIN1

L0_CLKIN#1

L0_CLKIN0

L0_CLKIN#0

L0_CTLIN0

L0_CTLIN#0

C651

103P

C332

4.7u/1206

L0_CADIN[15..0]16

L0_CADIN#[15..0]16

L0_CLKIN116

L0_CLKIN#116

L0_CLKIN016

L0_CLKIN#016

L0_CTLIN016

L0_CTLIN#016

AB14

AC15

AB16

AC16

AG11

AG12

AH10

AG10

AK11

AH12

AD8

AC9

AJ10

AG9

AJ8

AH8

AJ6

AH6

AG5

AG6

AJ4

AH4

AG3

AG4

AJ11

AL9

AL10

AJ9

AK9

AL7

AL8

AL5

AL6

AJ5

AK5

AL3

AL4

AJ3

AK3

AG7

AG8

AJ7

AK7

AL11

AL12

AJ12

VLDT_2(3)

VLDT_2(4)

VLDT_2(5)

VLDT_2(6)

VLDT_2(7)

VLDT_2(8)

VLDT_2(9)

L2_CADIN_H(15)

L2_CADIN_L(15)

L2_CADIN_H(14)

L2_CADIN_L(14)

L2_CADIN_H(13)

L2_CADIN_L(13)

L2_CADIN_H(12)

L2_CADIN_L(12)

L2_CADIN_H(11)

L2_CADIN_L(11)

L2_CADIN_H(10)

L2_CADIN_L(10)

L2_CADIN_H(9)

L2_CADIN_L(9)

L2_CADIN_H(8)

L2_CADIN_L(8)

L2_CADIN_H(7)

L2_CADIN_L(7)

L2_CADIN_H(6)

L2_CADIN_L(6)

L2_CADIN_H(5)

L2_CADIN_L(5)

L2_CADIN_H(4)

L2_CADIN_L(4)

L2_CADIN_H(3)

L2_CADIN_L(3)

L2_CADIN_H(2)

L2_CADIN_L(2)

L2_CADIN_H(1)

L2_CADIN_L(1)

L2_CADIN_H(0)

L2_CADIN_L(0)

L2_CLKIN_H(1)

L2_CLKIN_L(1)

L2_CLKIN_H(0)

L2_CLKIN_L(0)

L2_CTLIN_H(0)

L2_CTLIN_L(0)

L2_RSVD1

L2_RSVD2

U27F

L2_CADOUT_H(15)

L2_CADOUT_L(15)

L2_CADOUT_H(14)

L2_CADOUT_L(14)

L2_CADOUT_H(13)

L2_CADOUT_L(13)

L2_CADOUT_H(12)

L2_CADOUT_L(12)

L2_CADOUT_H(11)

L2_CADOUT_L(11)

L2_CADOUT_H(10)

L2_CADOUT_L(10)

L2_CADOUT_H(9)

L2_CADOUT_L(9)

L2_CADOUT_H(8)

L2_CADOUT_L(8)

L2_CADOUT_H(7)

L2_CADOUT_L(7)

L2_CADOUT_H(6)

L2_CADOUT_L(6)

L2_CADOUT_H(5)

L2_CADOUT_L(5)

L2_CADOUT_H(4)

L2_CADOUT_L(4)

L2_CADOUT_H(3)

L2_CADOUT_L(3)

L2_CADOUT_H(2)

L2_CADOUT_L(2)

L2_CADOUT_H(1)

L2_CADOUT_L(1)

L2_CADOUT_H(0)

L2_CADOUT_L(0)

L2_CLKOUT_H(1)

L2_CLKOUT_L(1)

L2_CLKOUT_H(0)

L2_CLKOUT_L(0)

L2_CTLOUT_H(0)

L2_CTLOUT_L(0)

L2_RSVD3

L2_RSVD4

AH14

AJ14

AG16

AG15

AH16

AJ16

AG18

AG17

AG20

AG19

AH20

AJ20

AG22

AG21

AH22

AJ22

AL14

AL13

AK15

AJ15

AL16

AL15

AK17

AJ17

AK19

AJ19

AL20

AL19

AK21

AJ21

AL22

AL21

AH18

AJ18

AL18

AL17

AK13

AJ13

AG13

AG14

L0_CADOUT15

L0_CADOUT#15

L0_CADOUT14

L0_CADOUT#14

L0_CADOUT13

L0_CADOUT#13

L0_CADOUT12

L0_CADOUT#12

L0_CADOUT11

L0_CADOUT#11

L0_CADOUT10

L0_CADOUT#10

L0_CADOUT9

L0_CADOUT#9

L0_CADOUT8

L0_CADOUT#8

L0_CADOUT7

L0_CADOUT#7

L0_CADOUT6

L0_CADOUT#6

L0_CADOUT5

L0_CADOUT#5

L0_CADOUT4

L0_CADOUT#4

L0_CADOUT3

L0_CADOUT#3

L0_CADOUT2

L0_CADOUT#2

L0_CADOUT1

L0_CADOUT#1

L0_CADOUT0

L0_CADOUT#0

L0_CLKOUT1

L0_CLKOUT#1

L0_CLKOUT0

L0_CLKOUT#0

L0_CTLOUT0

L0_CTLOUT#0

L0_CADOUT[15..0] 16

L0_CADOUT#[15..0] 16

L0_CLKOUT1 16

L0_CLKOUT#1 16

L0_CLKOUT0 16

L0_CLKOUT#0 16

L0_CTLOUT0 16

L0_CTLOUT#0 16

SledgeHammer

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

CPU0_K8 HT0 & HT2

MS-9130

Last Revision Date:

Thursday, July 17, 2003

Sheet

1

7 41

of

Rev

100

5

D D

LAYOUT: Place solder side of processor.

VCORE

C345

X_(BOT)SP-CAP,220u/2V

C C

4.7u/1206

C347

4.7u/1206

4.7u/1206

4

C346

X_(BOT)SP-CAP,220u/2V

LAYOUT: Place clolse to socket.

C349

C350

C351

C352

4.7u/1206

4.7u/1206

4.7u/1206

4.7u/1206

4.7u/1206

3

EMI

LAYOUT:

Place 1 capacitor every 1-1.5" along VDD_CORE perimiter.

VCORE

C674

C678

4.7u/1206

BULK / Decopuling

Place on CPU Solder side

VCORE

C12

C13

0.22u/16V/X7R

C14

0.22u/16V/X7R

0.22u/16V/X7R

VCORE

C333

6.8p/50V/NPO

C334

6.8p/50V/NPO

Buck-decoupling Mid-Freq. decoupling Cap. ( 7 * 4.7uF / 1206 X7R )

4.7u/1206

VCORE

C615

C619

4.7u/1206

C353

2

C336

C335

6.8p/50V/NPO

6.8p/50V/NPO

LAYOUT:

Place 1000pF capacitors between VRM & CPU.

VCOREVCORE

C354

1000P/50V/X7R

C337

6.8p/50V/NPO

C355

1000P/50V/X7R

C338

6.8p/50V/NPO

C356

1000P/50V/X7R

C339

6.8p/50V/NPO

C357C348

1000P/50V/X7R

C340

6.8p/50V/NPO

C341

6.8p/50V/NPO

C342

6.8p/50V/NPO

C344

C343

6.8p/50V/NPO

6.8p/50V/NPO

Buck-decoupling Mid-Freq. decoupling Cap. ( 7 * 4.7uF / 1206 X7R )

VCORE

C47

4.7u/1206

PLEASE THESE PARTS UNDER SOLDER SIDE OF U27

1

AD22

VDDIO47

VSS46

VDDIO48

VSS96

AB23

VSS47

AC23

VDDIOFB_H

AF20V6AD12H2AA4

VDDIOFB_L

VDDIO_SENSE

VSS48

VSS50

VSS51

VSS52

VSS53

VSS49

AC22Y9AB9

AD9

D10

T9

VCORE

T18

V18

Y18

K12

F19

N19

R19

U19

W19

D20

AE4

M20

P20

T20

V20

Y20

AK20

B21

AH21

AK4B5AH5K6P6T8AB6

AF6M2F6D8G7

AB8

AK8B9K18L9N9R9T2U9W9

AA9

AB18

AH9

W13

M10

P10

T10

V10Y2Y10

AB12

AF10

F11

L11

N11

R11

U11

W11

AA11

AD2

D12

M12

P12

T12

V12

Y12

AC13

AK12

B13

L13D4N13

R13

U13

AA13

AH13

J13

M14

P14

T14J4V14

Y14

AD14

AF14

F15

L15

N15

R15

U15

W15N4AA15

D16

F18

M16

P16

T16

V16

Y16

AD16

AK16U4B17

VDD1

VDD2

VDD3

VDD4

VDD5

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD117

VDD118

VDD119

VSS54

VSS55

VSS97

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS98

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS99

VSS72

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS101

VSS90

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS100

VSS81

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS182

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS183

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS184

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS185

VSS136

VSS137

VSS138

VSS139

VSS140

J10

AD13

L10

N10

R10

U10T6AA10

AC10

AK10

B11

L14

H15J8K11

M11

P11

T11

V11

N14

Y11

AA12

N16

AF12

F13

G15

F10

AD15

K13

U14

M13

AB11

AD11

AH11

G13

J12

N12

R12

U12

R14

W12

W14

AA14

AC14

AH15

AK14

B15

K15

M15

B23

P15

T15

V15

Y15

AB15

D14

J14

H17

G24

L16

R16

U16

W18

AA16

AC17

AF16

F16

K17

N24

M17

P17

T17

V17

3

VSS141

Y17

AB17

AD17

D18

J18

W24

L18

N18

R18

U18

W10

AA18

AE17

VDD95

VSS142

VSS143

VSS144

VSS186

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

AK18

B19

G30

K19

M19

T19

V19

Y19

AB19

AH19

J20

L20

L17

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VSS187

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS188

VSS163

W30

VSS164

N20

R20

U20

W20

AA20

AC20

AF21

K21

M21

AB24

P21

T21

SledgeHammer

N17

R17

U17

W17

AA17

AH17

M18

P18

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS189

VSS172

VSS173

VSS174

VSS175

VSS176

V21

Y21

2

VSS177

AB21

D22

G22

L22

N22

B26

R22

U22

W22

AA22

AE22

AK22

J22

AG2E2P13

W16

D23

AH23

VSS5

VSS91

VSS203

VSS202

VSS200

VSS201

VSS178

VSS179

VSS180

VSS190

VSS181

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS1

VSS2

VSS3

AE24

AK26

B29

AK23

K24

VSS4

T24

AE30

AK29

D30

K30

T30

AB30

AH30

AH7V9L12

AC12

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

CPU0 _K8 POWER & GND

MS-9130

Last Revision Date:

Thursday, July 17, 2003

Sheet

8 41

of

Rev

100

VDD_25_SUS

L19

W21

AA21

J21

M22

P22

T22

V22

Y22

AB22

AJ23

AA19

C23

E23

K26

T26

AE28

G26

N26

W26

AE26

AG23

K20

D28

K28

T28

AB28

AH28

AH26

G28

N28

W28

AB26

AB20

L21

N21

R21

U21

H22

D26

K22

A23

U23

AL23

U27D

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

B B

A A

5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS92

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS93

T13V2AB2

AF2

AK2B3AH3G4L4R4V13W4AC4F5D6H6M7

VSS22

F17

P19

N30F1F2K2P2

VDDIO32

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS94

VSS31

VSS32

VSS33

VSS34

AB7Y6AD6

J17

AK6B7F14P7V7Y7M6

VDDIO33

VSS35

VDDIO34

VSS36

VDDIO35

VDDIO36

VDDIO37

VSS37

VSS95

VSS38

Y13N8R8U8W8

VDDIO38

VSS39

VDDIO40

VSS40

VDDIO41

VSS41

AC21

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VSS42

VSS43

VSS44

VSS45

AA8

AF8F8G17K9AB13M9P9

4

5

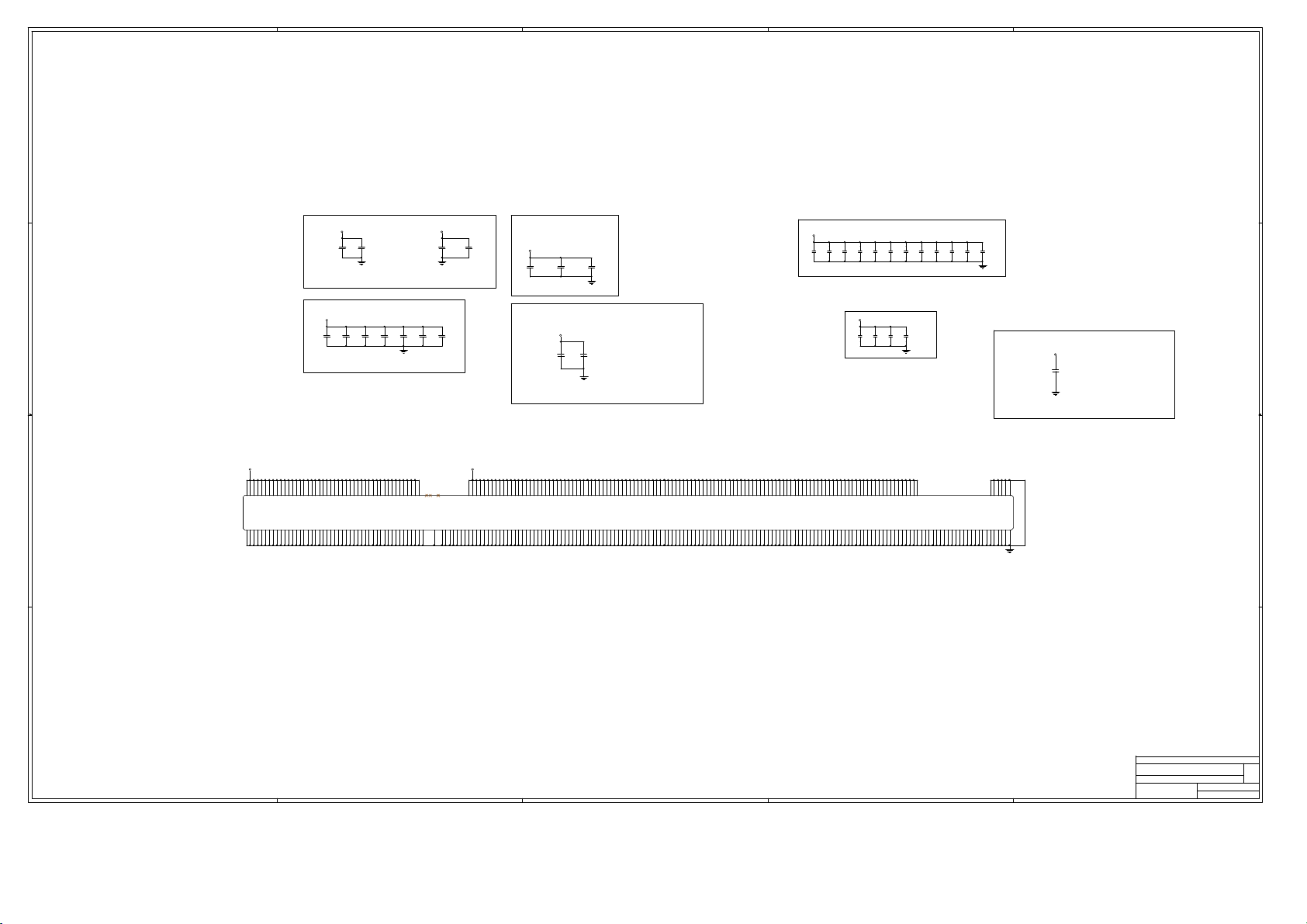

Registered DDR333 SDRAM

Sockets

4

3

2

1

D D

VDD_25_SUS

738467085

VDD0

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

DDR_VREF

1000P/50V/X7R

H0_DR_MD0

H0_DR_MD1

H0_DR_MD2

H0_DR_MD3

H0_DR_MD4

H0_DR_MD5

H0_DR_MD6

H0_DR_MD7

H0_DR_MD8

H0_DR_MD9

H0_DR_MD10

H0_DR_MD11

H0_DR_MD12

H0_DR_MD13

H0_DR_MD14

H0_DR_MD15

H0_DR_MD16

H0_DR_MD17

H0_DR_MD18

H0_DR_MD19

H0_DR_MD20

H0_DR_MD21

H0_DR_MD22

H0_DR_MD23

H0_DR_MD24

H0_DR_MD25

H0_DR_MD26

H0_DR_MD27

H0_DR_MD28

H0_DR_MD29

H0_DR_MD30

H0_DR_MD31

H0_DR_MD32

H0_DR_MD33

H0_DR_MD34

H0_DR_MD35

H0_DR_MD36

H0_DR_MD37

H0_DR_MD38

H0_DR_MD39

H0_DR_MD40

H0_DR_MD41

H0_DR_MD42

H0_DR_MD43

H0_DR_MD44

H0_DR_MD45

H0_DR_MD46

H0_DR_MD47

H0_DR_MD48

H0_DR_MD49

H0_DR_MD50

H0_DR_MD51

H0_DR_MD52

H0_DR_MD53

H0_DR_MD54

H0_DR_MD55

H0_DR_MD56

H0_DR_MD57

H0_DR_MD58

H0_DR_MD59

H0_DR_MD60

H0_DR_MD61

H0_DR_MD62

H0_DR_MD63

C358

VDD_25_SUS

C359

1000P/50V/X7R

H0_DR_MD[63..0]10,11

C C

B B

H0_DR_-MSWEA10,11

Channel A

108

120

148

168223054627796

104

112

128

136

143

156

164

172

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

184

PIN

DDR DIMM

SOCKET

SLAVE ADDRESS = 1010000B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

3111826344250586674818993

VSS18

100

116

124

132

139

145

152

1801582

VDDQ13

VDDQ14

VSS19

VSS20

160

176

VDDQ15

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

VSS21

VDDID

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

CKE0

CKE1

CAS#

RAS#

184

CS0#

CS1#

CS2#

CS3#

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

DDR1

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

SMBCLK1

SMBDATA1

H0_DR_-MCS0 11

H0_DR_-MCS1 11

H0_DR_MDQS0 10,11

H0_DR_MDQS1 10,11

H0_DR_MDQS2 10,11

H0_DR_MDQS3 10,11

H0_DR_MDQS4 10,11

H0_DR_MDQS5 10,11

H0_DR_MDQS6 10,11

H0_DR_MDQS7 10,11

H0_DR_MDQS8 10,11

H0_DR_MAA13 10,11

H0_DR_MAA0 10,11

H0_DR_MAA1 10,11

H0_DR_MAA2 10,11

H0_DR_MAA3 10,11

H0_DR_MAA4 10,11

H0_DR_MAA5 10,11

H0_DR_MAA6 10,11

H0_DR_MAA7 10,11

H0_DR_MAA8 10,11

H0_DR_MAA9 10,11

H0_DR_MAA10 10,11

H0_DR_MAA11 10,11

H0_DR_MAA12 10,11

H0_DR_MEMBAKA0 10,11

H0_DR_MEMBAKA1 10,11

SMBCLK1 4,10,22,24,25,35,37

SMBDATA1 4,10,22,24,25,35,37

H0_DR_MEMCHECK0 10,11

H0_DR_MEMCHECK1 10,11

H0_DR_MEMCHECK2 10,11

H0_DR_MEMCHECK3 10,11

H0_DR_MEMCHECK4 10,11

H0_DR_MEMCHECK5 10,11

H0_DR_MEMCHECK6 10,11

H0_DR_MEMCHECK7 10,11

H0_MEMCLK_H0 5

H0_MEMCLK_L0 5

H0_MEMRESET_L 5,10

H0_DR_MCKELO 10,11

H0_DR_MCKEUP 10,11

H0_DR_-MSCASA 10,11

H0_DR_-MSRASA 10,11

H0_DR_MDQS9 10,11

H0_DR_MDQS10 10,11

H0_DR_MDQS11 10,11

H0_DR_MDQS12 10,11

H0_DR_MDQS13 10,11

H0_DR_MDQS14 10,11

H0_DR_MDQS15 10,11

H0_DR_MDQS16 10,11

H0_DR_MDQS17 10,11

VDD_25_SUS

738467085

VDD0

VDD1

H0_DR_MD[127..64]10,11

H0_DR_MD64

H0_DR_MD65

H0_DR_MD66

H0_DR_MD67

H0_DR_MD68

H0_DR_MD69

H0_DR_MD70

H0_DR_MD71

H0_DR_MD72

H0_DR_MD73

H0_DR_MD74

H0_DR_MD75

H0_DR_MD76

H0_DR_MD77

H0_DR_MD78

H0_DR_MD79

H0_DR_MD80

H0_DR_MD81

H0_DR_MD82

H0_DR_MD83

H0_DR_MD84

H0_DR_MD85

H0_DR_MD86

H0_DR_MD87

H0_DR_MD88

H0_DR_MD89

H0_DR_MD90

H0_DR_MD91

H0_DR_MD92

H0_DR_MD93

H0_DR_MD94

H0_DR_MD95

H0_DR_MD96

H0_DR_MD97

H0_DR_MD98

H0_DR_MD99

H0_DR_MD100

H0_DR_MD101

H0_DR_MD102

H0_DR_MD103

H0_DR_MD104

H0_DR_MD105

H0_DR_MD106

H0_DR_MD107

H0_DR_MD108

H0_DR_MD109

H0_DR_MD110

H0_DR_MD111

H0_DR_MD112

H0_DR_MD113

H0_DR_MD114

H0_DR_MD115

H0_DR_MD116

H0_DR_MD117

H0_DR_MD118

H0_DR_MD119

H0_DR_MD120

H0_DR_MD121

H0_DR_MD122

H0_DR_MD123

H0_DR_MD124

H0_DR_MD125

H0_DR_MD126

H0_DR_MD127

H0_DR_-MSWEA

DDR_VREF

1000P/50V/X7R

C360

VDD_25_SUS

C361

1000P/50V/X7R

VDD2

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

SLAVE ADDRESS = 1010001B

102

NC4

Channel B

108

120

148

168223054627796

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

DDR DIMM

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

3111826344250586674818993

VSS10

104

VDDQ5

VSS11

112

VDDQ6

VDDQ7

SOCKET

VSS12

VSS13

100

128

116

136

VDDQ8

184

VSS14

124

143

VDDQ9

VDDQ10

VSS15

VSS16

132

156

164

VDDQ11

PIN

VSS17

139

145

172

VDDQ12

VDDQ13

VSS18

VSS19

152

1801582

VDDQ14

VDDQ15

NC(RESET#)

VSS20

VSS21

160

176

VDDID

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

FETEN

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CKE0

CKE1

CAS#

RAS#

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DDR2

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

H0_DR_MCKELO

H0_DR_MCKEUP

SMBCLK1

SMBDATA1

H0_DR_-MCS0 11

H0_DR_-MCS1 11

H0_DR_MDQS18 10,11

H0_DR_MDQS19 10,11

H0_DR_MDQS20 10,11

H0_DR_MDQS21 10,11

H0_DR_MDQS22 10,11

H0_DR_MDQS23 10,11

H0_DR_MDQS24 10,11

H0_DR_MDQS25 10,11

H0_DR_MDQS26 10,11

H0_DR_MAA13 10,11

H0_DR_MAA0 10,11

H0_DR_MAA1 10,11

H0_DR_MAA2 10,11

H0_DR_MAA3 10,11

H0_DR_MAA4 10,11

H0_DR_MAA5 10,11

H0_DR_MAA6 10,11

H0_DR_MAA7 10,11

H0_DR_MAA8 10,11

H0_DR_MAA9 10,11

H0_DR_MAA10 10,11

H0_DR_MAA11 10,11

H0_DR_MAA12 10,11

H0_DR_MEMBAKA0 10,11

H0_DR_MEMBAKA1 10,11

VDD_25_SUS

H0_DR_MEMCHECK8 10,11

H0_DR_MEMCHECK9 10,11

H0_DR_MEMCHECK10 10,11

H0_DR_MEMCHECK11 10,11

H0_DR_MEMCHECK12 10,11

H0_DR_MEMCHECK13 10,11

H0_DR_MEMCHECK14 10,11

H0_DR_MEMCHECK15 10,11

H0_MEMCLK_H2 5

H0_MEMCLK_L2 5

H0_MEMRESET_L 5,10

H0_DR_-MSCASA 10,11

H0_DR_-MSRASA 10,11

H0_DR_MDQS27 10,11

H0_DR_MDQS28 10,11

H0_DR_MDQS29 10,11

H0_DR_MDQS30 10,11

H0_DR_MDQS31 10,11

H0_DR_MDQS32 10,11

H0_DR_MDQS33 10,11

H0_DR_MDQS34 10,11

H0_DR_MDQS35 10,11

DDR_VREFVDD_25_SUS

C362

R382

100RST

0.1u

C363

A A

5

4

R383

100RST

C364

1000P/50V/X7R

0.1u

Micro Star Restricted Secret

Title

CPU0 Register DDR DIMM1 & 2

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

MS-9130

1

Last Revision Date:

Sheet

Thursday, July 17, 2003

9 41

of

Rev

100

5

4

3

2

1

Registered DDR333 SDRAM

Sockets

Channel A

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

90

63

C368

101

102

1000P/50V/X7R

VDD_25_SUS

738467085

VDD0

VDD1

VDD2

VDD3

2

DQ0

4

DQ1

6

DQ2

8

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

WP(NC)

WE#

1

VREF

9

NC2

NC3

SLAVE ADDRESS = 1010011B

NC4

VSS0

3111826344250586674818993

VDD_25_SUS

D D

H0_DR_MD[63..0]9,11

C C

B B

H0_DR_-MSWEA9,11

H0_DR_MD0

H0_DR_MD1

H0_DR_MD2

H0_DR_MD3

H0_DR_MD4

H0_DR_MD5

H0_DR_MD6

H0_DR_MD7

H0_DR_MD8

H0_DR_MD9

H0_DR_MD10

H0_DR_MD11

H0_DR_MD12

H0_DR_MD13

H0_DR_MD14

H0_DR_MD15

H0_DR_MD16

H0_DR_MD17

H0_DR_MD18

H0_DR_MD19

H0_DR_MD20

H0_DR_MD21

H0_DR_MD22

H0_DR_MD23

H0_DR_MD24

H0_DR_MD25

H0_DR_MD26

H0_DR_MD27

H0_DR_MD28

H0_DR_MD29

H0_DR_MD30

H0_DR_MD31

H0_DR_MD32

H0_DR_MD33

H0_DR_MD34

H0_DR_MD35

H0_DR_MD36

H0_DR_MD37

H0_DR_MD38

H0_DR_MD39

H0_DR_MD40

H0_DR_MD41

H0_DR_MD42

H0_DR_MD43

H0_DR_MD44

H0_DR_MD45

H0_DR_MD46

H0_DR_MD47

H0_DR_MD48

H0_DR_MD49

H0_DR_MD50

H0_DR_MD51

H0_DR_MD52

H0_DR_MD53

H0_DR_MD54

H0_DR_MD55

H0_DR_MD56

H0_DR_MD57

H0_DR_MD58

H0_DR_MD59

H0_DR_MD60

H0_DR_MD61

H0_DR_MD62

H0_DR_MD63

DDR_VREF

C365

1000P/50V/X7R

C366

1000P/50V/X7R

VDD_25_SUS VDD_25_SUS

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VDDQ2

VSS8

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

SLAVE ADDRESS = 1010010B

102

NC4

VSS0

VSS1

3111826344250586674818993

104

112

128

136

143

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

184 PIN

DDR DIMM

SOCKET

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

100

116

124

132

156

164

VDDQ10

VDDQ11

VSS16

VSS17

139

145

172

1801582

VDDQ12

VDDQ13

VSS18

VSS19

152

160

VDDQ14

VSS20

176

VDDID

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

CKE0

CKE1

CAS#

RAS#

VSS21

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DDR3

DDRDIMM_184

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

SMBCLK1

SMBDATA1

H0_DR_-MCS2 11

H0_DR_MDQS0 9,11

H0_DR_MDQS1 9,11

H0_DR_MDQS2 9,11

H0_DR_MDQS3 9,11

H0_DR_MDQS4 9,11

H0_DR_MDQS5 9,11

H0_DR_MDQS6 9,11

H0_DR_MDQS7 9,11

H0_DR_MDQS8 9,11

H0_DR_MAA13 9,11

H0_DR_MAA0 9,11

H0_DR_MAA1 9,11

H0_DR_MAA2 9,11

H0_DR_MAA3 9,11

H0_DR_MAA4 9,11

H0_DR_MAA5 9,11

H0_DR_MAA6 9,11

H0_DR_MAA7 9,11

H0_DR_MAA8 9,11

H0_DR_MAA9 9,11

H0_DR_MAA10 9,11

H0_DR_MAA11 9,11

H0_DR_MAA12 9,11

H0_DR_MEMBAKA0 9,11

H0_DR_MEMBAKA1 9,11

VDD_25_SUS

H0_DR_MEMCHECK0 9,11

H0_DR_MEMCHECK1 9,11

H0_DR_MEMCHECK2 9,11

H0_DR_MEMCHECK3 9,11

H0_DR_MEMCHECK4 9,11

H0_DR_MEMCHECK5 9,11

H0_DR_MEMCHECK6 9,11

H0_DR_MEMCHECK7 9,11

H0_MEMCLK_H1 5

H0_MEMCLK_L1 5

H0_MEMRESET_L 5,9

H0_DR_MCKELO 9,11

H0_DR_MCKEUP 9,11

H0_DR_-MSCASA 9,11

H0_DR_-MSRASA 9,11

H0_DR_MDQS9 9,11

H0_DR_MDQS10 9,11

H0_DR_MDQS11 9,11

H0_DR_MDQS12 9,11

H0_DR_MDQS13 9,11

H0_DR_MDQS14 9,11

H0_DR_MDQS15 9,11

H0_DR_MDQS16 9,11

H0_DR_MDQS17 9,11

DDR_VREF

DDR_VREF

1000P/50V/X7R

H0_DR_MD64

H0_DR_MD65

H0_DR_MD66

H0_DR_MD67

H0_DR_MD68

H0_DR_MD69

H0_DR_MD70

H0_DR_MD71

H0_DR_MD72

H0_DR_MD73

H0_DR_MD74

H0_DR_MD75

H0_DR_MD76

H0_DR_MD77

H0_DR_MD78

H0_DR_MD79

H0_DR_MD80

H0_DR_MD81

H0_DR_MD82

H0_DR_MD83

H0_DR_MD84

H0_DR_MD85

H0_DR_MD86

H0_DR_MD87

H0_DR_MD88

H0_DR_MD89

H0_DR_MD90

H0_DR_MD91

H0_DR_MD92

H0_DR_MD93

H0_DR_MD94

H0_DR_MD95

H0_DR_MD96

H0_DR_MD97

H0_DR_MD98

H0_DR_MD99

H0_DR_MD100

H0_DR_MD101

H0_DR_MD102

H0_DR_MD103

H0_DR_MD104

H0_DR_MD105

H0_DR_MD106

H0_DR_MD107

H0_DR_MD108

H0_DR_MD109

H0_DR_MD110

H0_DR_MD111

H0_DR_MD112

H0_DR_MD113

H0_DR_MD114

H0_DR_MD115

H0_DR_MD116

H0_DR_MD117

H0_DR_MD118

H0_DR_MD119

H0_DR_MD120

H0_DR_MD121

H0_DR_MD122

H0_DR_MD123

H0_DR_MD124

H0_DR_MD125

H0_DR_MD126

H0_DR_MD127

C367

H0_DR_MD[127..64]9,11

H0_DR_-MSWEA9,11

VDD4

VSS1

108

VDD5

VSS2

120

148

168223054627796

VDD6

VDD7

VDD8

VSS3

VSS4

VSS5

Channel B

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

DDR DIMM

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

104

112

128

136

143

156

164

172

1801582

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10